PRELIMINARY ENGINEERING SPECIFICATION

I/O MANAGER DEVICE

FE3040

|     |            |      |           |            | R. Chung              | 7/21/8      |

|-----|------------|------|-----------|------------|-----------------------|-------------|

| REV | ECO        | DE   | SCRIPTION |            | APPR                  | DATE        |

|     | SIGNATURES | DATE | TITLE     |            | ERN DIGIT             |             |

| -   |            |      |           | CLASS CODE | BASE NUMBER<br>000610 | REV<br>X2.3 |

|     |            |      |           | SCALE:     | SHEET 1 0             | F 32        |

This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written authorization from WESTERN DIGITAL CORPORATION.

# FE3040 DEVICE FEATURES

- generates chip selects for hard disk, floppy, 8042, 80287, and NMI

- generates programmable chip selects for four additional devices

- individually programmable wait state generation for I/O ports and system board memory

- maps main and EGA BIOS into one physical PROM

- generates fast IOCS16 for 16 bit I/O ports

- glitchless clock switching circuitry for processor and DMA

- bus-compatibility clock switching for I/O card accesses

- "Hot" reset generation for quick 80286 switch from protected to real mode

- Alternate Gate A20 generation

- 68 pin PLCC package

The FE3040 device is designed to reduce chip count, increase flexibility, and provide improved operating speed and functionality when used with other Western Digital peripheral chips on a PC-AT compatible system board.

Chip count is reduced by integrating appropriate random logic and logic formerly implemented with PALs. Flexibility is retained by making the PAL type logic software programmable, so that characteristics may be changed by different versions of BIOS ROMs or through a BIOS ROM set-up program. Programmability also greatly reduces the number of jumpers on the system board.

A major function of the FE3040 is to generate chip select decodes for peripheral chips on the system board, for instance, the floppy controller, hard disk controller, serial, and parallel port chips. System operating speed may be optimized by tailoring the number of processor wait states to each individual peripheral device. An early generation of the IOCS16 signal is also provided, since this signal is in a critical timing path in high speed AT compatibles.

|                                                                                                                                                                 |    | ERN DIGITA            |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------|-------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | 96 | BASE NUMBER<br>000610 | REV<br>X2.3 |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |    | SHEET 2 01            | F 32        |

To reduce chip count and improve performance, particularly when an EGA graphics controller is placed on the system board, seperate blocks of ROM may be mapped into a single physical ROM. For instance, the EGA BIOS and standard BIOS may be placed into the same pair of ROM chips or into a single 16 bit wide ROM. Besides reducing chip count, EGA operating speed will be improved, since EGA BIOS will be accessed 16 bits at a time. To improve BIOS performance, ROM code may be copied into excess RAM, and the BIOS ROM mapped out and replaced by RAM 16K bytes at a time. (Excess RAM is the 384K left over after the lower 640K out of a 1 MB RAM is used).

Clock switching circuitry is included, which provides glitch free switching between two unrelated clocks under BIOS control. In addition, the processor clock output frequency may be programmed to be divided by two. The clocks will typically be at a frequency of 12 MHz to 24 MHz. In addition, the clock may be programmed to automatically divide by 2 when expansion cards are accessed, to provide compatibility with slow expansion cards while allowing full speed execution when accessing system board RAM, ROM, and I/O.

|                                                                                                                                                                 |                  | ERN DIGITA            | · - · · · · · · · · · · · · · · · · · · |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-----------------------------------------|--|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3                             |  |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 3 OF            | F 32                                    |  |

#### UPDATE HISTORY

REV X2.3: Added Alternate Gate A20 function to chip select C, enabled by control register FFF07.

Added RAM control register FFF58, providing ability to deselect on-board RAM between 256K-640K or 512K-640K.

Changed default wait states for on-board ROM from 2 wait states to 1 wait state; register FFF50.

Pin 33 has been renamed IORDY from IORDY-. It's function has not been redefined.

The CSFP-, CSF, CSHD-, CSPRGA-, CSPRGB-, CSPRGC-, CSPRGD-, CS8042-, CS287-, CSNMI-, GTCK-, and D3-D0 pins will have a 2 mA drive capability rather than 4 mA.

REV X2.2: Changed output drive specification from 4 mA to 2 mA for certain output pins. See sheet 29, DC Operating Characteristics.

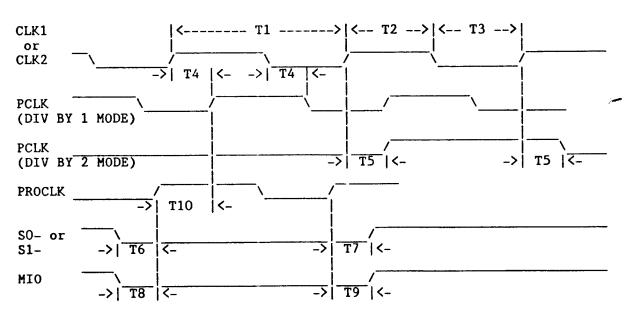

Changed timing parameters T4-T7, T14, T16, T20, T24, T26. Changed T8 and T9 reference from PCLK to PROCLK. Added timing parameter T10. See sheet 30, AC Operating Characteristics.

Redefined SEL field in the Processor Clock Select Register, FFF62.

- REV X2.1: The EPROM/RAM swap control registers FFF53-FFF56 bit definitions have changed. The function specified by control bit 0 has been swapped with control bit 3, and bit 2 swapped with bit 1.

- REV X2.0: Added bus cycle clock switching, controlled by register FFF62.

Added "Hot" reset function to chip select D. Added control register at FFF07.

The port control registers FFF08, FFF10, FFF18, and FFF20 will generate up to 6 wait states rather than 8. The zero wait state line will no longer be asserted for the 1 or 2 wait state case.

The CSFPO- and CSFPC- floppy controller select pins have been combined into a single pin, CSF.

|                                                                                                                                                                 | WESTERN DIGITAL  |                       |             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|--|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |  |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 4 0             | F 32        |  |

REV X2.0: (continued)

Pin 29 was spare, now is AO. Pin 2 was ADDRO, now is MIO. Pin 48 was SYSCLK, now is S1-. Pin 46 was DMACLK, now is PROCLK. Pin 54 was CSPRGD-, now is SYSCLK. Pin 58 was CSFPC-, now is CSPRGD-.

REV X1.3: External RAM and I/O Wait State Control register FFF61 deleted. The External RAM and I/O Wait State Control has been simplified and integrated into register FFF50.

Address pin AO, pin 29, has been deleted and is now a spare pin.

The default DMA clock rate has been changed from the selected clock divided by 8 to the selected clock divided by 2.

REV X1.2: Floppy and hard disk chip selects are now fixed in function. The three floppy and one hard disk chip select pins had alternate functions as programmable chip selects E, F, G, and H.

Programmable ports A, B, C, and D now have four address range choices, rather than eight. Also, the A8 address bit may be masked, rather than the A9 address bit. The Port I/O Address registers are reset to all zeroes by master reset, rather than preset to all ones.

The External I/O Wait State Control register (FFF48) has been deleted. The external I/O wait state control has been simplified and is now coded in register FFF61, the External RAM Wait State Control register.

The Clock1/Clock2 SELect bit in the DMA Clock Select register (FFF63) has been moved from bit 0 to bit 1.

REV X1.1: Added version number register (FFF01).

|                                                                                                                                                                 | WESTERN DIGITAL  |                       |             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|--|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |  |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 5 01            | F 32        |  |

|                                                                                                                                                                 | WESTERN DIGITA   |                       |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 6 O             | F 32        |

|                                                                                                                                                                 | WESTERN DIGIT    |                       |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 7 OF            | F 32        |

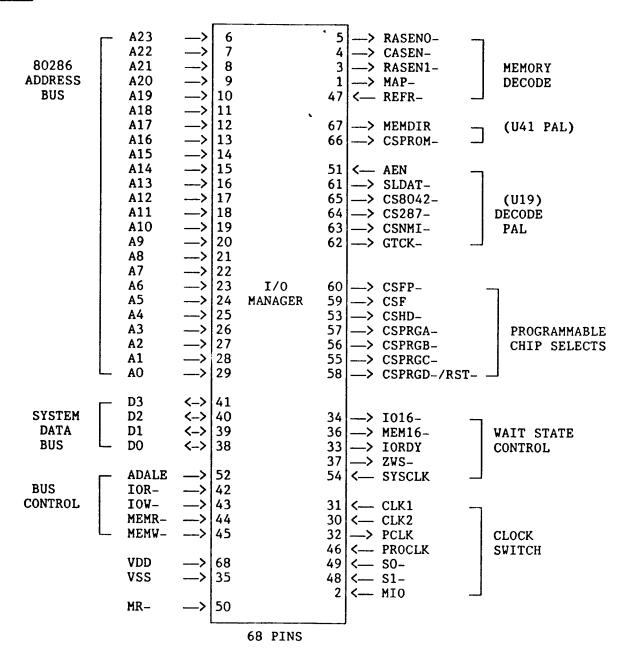

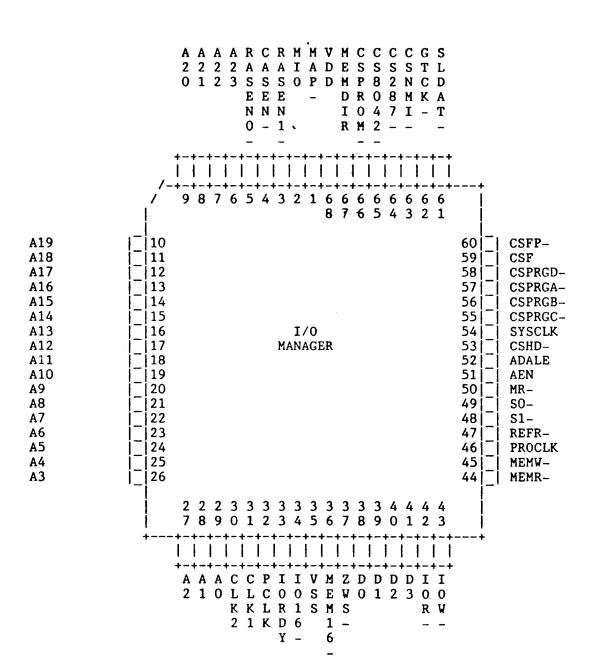

# 80286 INTERFACE

This interface port connects with the 80286 address lines and the 80286 bus status lines. By connecting directly to the 80286 and by duplicating a portion of the 82288 bus controller logic, early determination of memory or I/O accesses may be made, as well as whether the access will be 8 bits or 16 bits.

| PIN<br>NUMBER                                                                      | MNEMONIC                                                                                             | I/0                                                                                         | FUNCTION                              |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------|

| 6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20 | A23<br>A22<br>A21<br>A20<br>A19<br>A18<br>A17<br>A16<br>A15<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9 | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | FUNCTION  80286 ADDRESS LINE          |

| 21<br>22<br>23<br>24                                                               | A8<br>A7<br>A6<br>A5                                                                                 | I<br>I<br>I                                                                                 | · · · · · · · · · · · · · · · · · · · |

| 25<br>26<br>27                                                                     | A4<br>A3<br>A2                                                                                       | I                                                                                           | • • •                                 |

| 28<br>29                                                                           | A1<br>AO                                                                                             | I                                                                                           | 80286 ADDRESS LINE                    |

|                                                                                                                                                                 | WESTERN DIGITAL  |                       |             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|--|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |  |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 8 01            | 32          |  |

# DATA BUS INTERFACE AND BUS CONTROL

The data bus port is 4 bits wide, which should connect to the EDATA data bus. The upper 4 bits should be ignored when reading the control registers.

| PIN<br>NUMBER        | MNEMONIC             | 1/0                      | FUNCTION                                              |

|----------------------|----------------------|--------------------------|-------------------------------------------------------|

| 41<br>40<br>39<br>38 | D3<br>D2<br>D1<br>D0 | I/0<br>I/0<br>I/0<br>I/0 | CONTROL REGISTER DATA LINE CONTROL REGISTER DATA LINE |

| 42                   | IOR-                 | I                        | SYSTEM I/O READ COMMAND SIGNAL                        |

| 43                   | IOW-                 | I                        | SYSTEM I/O WRITE COMMAND SIGNAL                       |

| 44                   | MEMR-                | I                        | SYSTEM MEMORY READ COMMAND SIGNAL                     |

| 45                   | MEMW-                | I                        | SYSTEM MEMORY WRITE COMMAND SIGNAL '                  |

| 52                   | ADALE                | I                        | SYSTEM ADDRESS LATCH ENABLE SIGNAL 'OR'ED WITH ADSTB  |

| 54                   | SYSCLK               | I                        | SYSTEM CLOCK (PROCESSOR CLOCK DIVIDED BY TWO)         |

|                                                                                                                                                                 | WESTERN DIGITAL  |                       |             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|--|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |  |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 9 01            | 32          |  |

# I/O CHIP SELECT CONTROL

This logic section generates chip selects for standard system board functions such as the 8042 keyboard controller, 80287 math coprocessor, floppy controller, and hard disk controller. It also generates chip selects for up to 4 additional I/O ports which may have programmable addresses and wait state characteristics.

| PIN<br>NUMBER | PIN<br>NAME | 1/0 | FUNCTION                                                                          |

|---------------|-------------|-----|-----------------------------------------------------------------------------------|

| 57            | CSPRGA-     | 0   | PROGRAMMABLE CHIP SELECT A                                                        |

| 56            | CSPRGB-     | 0   | PROGRAMMABLE CHIP SELECT B                                                        |

| 55            | CSPRGC-     | 0   | PROGRAMMABLE CHIP SELECT C                                                        |

| 58            | CSPRGD-     | 0   | PROGRAMMABLE CHIP SELECT D OR HOT RESET OUTPUT                                    |

| 59            | CSF         | 0   | FLOPPY DISK CONTROLLER OPERATION OR<br>CONFIGURATION REGISTER SELECT              |

| 60            | CSFP-       | 0   | FLOPPY DISK CHIP SELECT                                                           |

| 53            | CSHD-       | 0   | HARD DISK CONTROLLER CHIP SELECT                                                  |

| 65            | CS8042-     | О   | 8042 KEYBOARD CONTROLLER SELECT                                                   |

| 64            | CS287-      | 0   | 80287 ARITHMETIC COPROCESSOR SELECT                                               |

| 63            | CSNMI-      | 0   | NMI LOGIC                                                                         |

| 62            | GTCK-       | 0   | ENABLE MEMORY PARITY AND I/O CHECK. GATED EXTERNALLY WITH I/O READ AND I/O WRITE. |

| 34            | 1016-       | 0   | EARLY IOCS16 SIGNAL FOR SYSTEM BOARD I/O PORTS                                    |

| 33            | IORDY       | 0   | PROGRAMMABLE WAIT STATE LINE FOR SYSTEM BOARD I/O PORTS                           |

| 37            | zws-        | 0   | ZERO WAIT STATE LINE                                                              |

| 36            | MEM16-      | 0   | 16 BIT MEMORY SIGNAL                                                              |

| 61            | SLDAT-      | 0   | DIRECTION OF DATA TRANCEIVER - DATA TO EDATA BUS                                  |

| 51            | AEN         | I   | SYSTEM AEN SIGNAL                                                                 |

|                                                                                                                                                                 |                  | ERN DIGITA            |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 | SHEET 10 OF      |                       | F 32        |

The IORDY pin will normally be at a high state. It will go low when generating wait states. This pin should be AND'ed, with the bus signal IOCHRDY.

The following table lists the data work size, I/O addresses, and chip selects generated for each variable port type.

The Port A, B, C, and D addresses are fully programmable, with the choice of either using nine I/O addresses for decode, or masking the A8 address bit (for instance, for decoding dual serial ports). The LSB (AO) address is always ignored. The lower 2, 3, or 4 bits of the address may also be ignored so that 2, 4, 8, or 16 bytes may be allocated for the port.

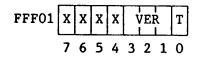

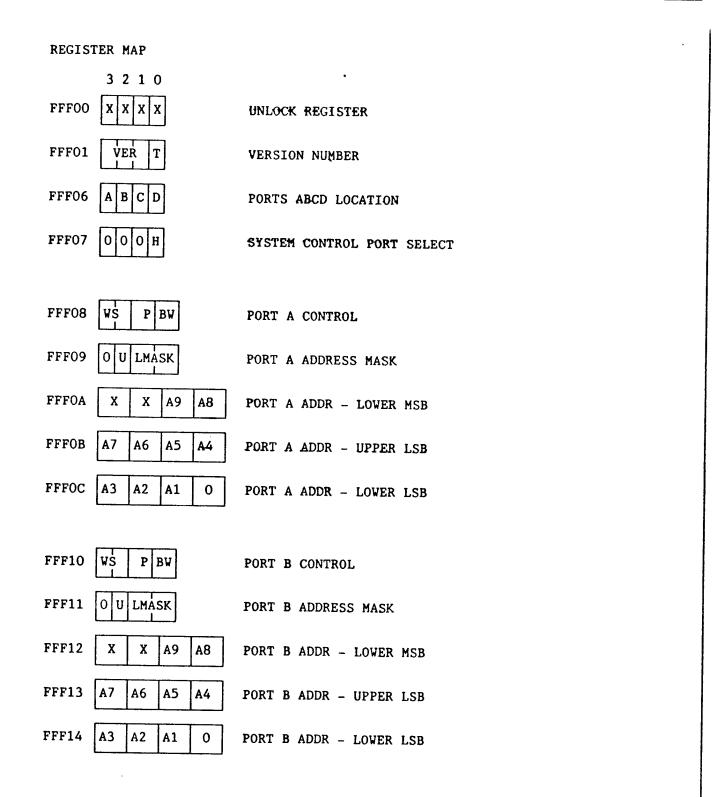

All FE3040 control registers are accessed by first writing eight times to address FFF00 (in an area allocated for ROM BIOS). Any memory access outside of the ROM BIOS address space, either data access or instruction fetch, will abort the unlocking process. Once unlocked, memory accesses outside of the ROM BIOS area may be made without affecting the unlocked state. When unlocked, the address space from FFF01 to FFFFE becomes register controls for the FE3040 device. The controls are locked again by reading location FFFFF.

A Version Number register provides information on the version of the I/O Manager chip. It also contains a bit which toggles between 'O' and '1' which provides indication that the register set has been unlocked.

#### **VERSION NUMBER**

T: toggles between 0 and 1 with every read access of the Version Number register.

V: 001 when T=0: 001 when T=1

|                                                                                                                                                                |                          | WESTERN DIGITAL       |             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|-------------|--|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclose to anyone other than WDC employees without the written | d 96                     | BASE NUMBER<br>000610 | REV<br>X2.3 |  |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                | GITAL CORPORATION. SHEET |                       | F 32        |  |

System board devices may be located on the EDATA bus rather than on the I/O expansion slot DATA bus. The SLDAT- signal which controls the DATA to EDATA bus direction is affected by the two port location registers. This option is available for peripheral devices which cannot directly drive the high current I/O slot DATA bus. Note, however, that DMA transfers cannot be made to devices on the EDATA bus.

The SLDAT- signal is active (low) when IOR- is active and address bits A8 and A9 are low, or the PORTS ABCD location register indicates that an addressed port is on the EDATA bus.

PORTS ABCD LOCATION REGISTER

FFF06 X X X X A B C D

7 6 5 4 3 2 1 0

IF A=O THEN THE PORT A DEVICE IS ON THE DATA BUS. IF A=1 THEN THE PORT A DEVICE IS ON THE EDATA BUS. THE SAME CODING IS USED FOR PORTS B,C, AND D.

THE PORT LOCATION REGISTER IS CLEARED BY A MASTER RESET.

The CSPRGC- pin (Port C) may be redefined to provide an alternate gate A20 function which is generated faster than the gate A20 signal provided by the 8042 keyboard controller. When defined as an alternate gate A20 signal, writing a '1' to bit 1 of I/O port 092 will cause the CSPRGC- pin to go to a low state.

The CSPRGD- pin (Port D) may be redefined to provide a "hot" reset function, to provide a fast switch from protected mode to real mode, by setting the "H" bit of the System Control Port register. Writing a '1' to bit 0 of I/O port 092 will generate an active low reset pulse 32 PCLKs wide, 128 PCLKs after writing to port 092. A reset pulse will be generated only when the bit is changed from a 0 to a 1.

SYSTEM CONTROL PORT SELECT

FFF07 X X X X 0 0 A H 7 6 5 4 3 2 1 0

IF A=1 THEN THE CSPRGC- PIN BECOMES THE ALTERNATE GATE A20 FUNCTION. IF H=1 THEN THE CSPRGD- PIN BECOMES THE HOT RESET FUNCTION. THIS REGISTER IS CLEARED BY A MASTER RESET.

WESTERN DIGITAL

CORPORATION

This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written authorization from WESTERN DIGITAL CORPORATION.

CLASS CODE BASE NUMBER 000610 X2.3

SHEET 12 OF 32

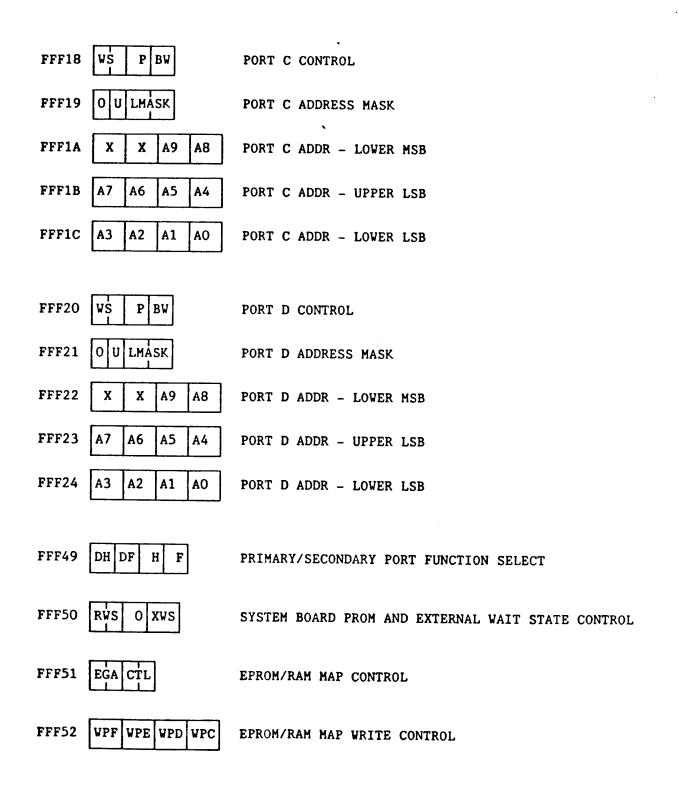

PORT CONTROL REGISTERS

| X | Х | X | X | WS  | P | BW |

|---|---|---|---|-----|---|----|

| 7 | 6 | 5 | 4 | 3 2 | 1 |    |

| WS | BW=0<br>8 BIT PORT | BW=1<br>16 BIT PORT |

|----|--------------------|---------------------|

| 00 | 2 W.S.             | 1 W.S.              |

| 01 | 4 W.S.             | 1 W.S.              |

| 10 | 6 W.S.             | 2 W.S.              |

| 11 | 6 W.S.             | 2 W.S.              |

| PORT | PORT CONTROL<br>REGISTER ADDRESS |

|------|----------------------------------|

| A    | FFF08                            |

| B    | FFF10                            |

| C    | FFF18                            |

| D    | FFF20                            |

FOR PORTS A, B, C, AND D, IF P=0 THEN THE OUTPUT IS DISABLED (ALWAYS HIGH).

THE PORT CONTROL REGISTERS ARE CLEARED BY A MASTER RESET.

The A, B, C, and D port chip selects are enabled with the P bit. If the P bit is O, then the port chip select bit will always be at an inactive (high) state. These ports are disabled after master reset.

|                                                                                                                                                                 | WESTERN DIGITAL  |                       |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 13 O            | F 32        |

PORT ADDRESS MASK REGISTERS

| x x x | Х | 0 | U | LMASK |

|-------|---|---|---|-------|

|-------|---|---|---|-------|

7 6 5 4 3 2 1 0

| LMASK | ADI | DRE | SS I | BIT | S C | OMP | AREI      | )  |    |   |

|-------|-----|-----|------|-----|-----|-----|-----------|----|----|---|

| 00    | A9  | A8  | A7   | A6  | Α5  | A4  | А3        | A2 | A1 | Х |

| 01    | A9  | 8A  | A7   | A6  | Α5  | A4  | <b>A3</b> | A2 | X  | X |

| 10    | A9  | 8A  | A7   | A6  | Α5  | A4  | <b>A3</b> | X  | X  | Х |

| 11    | A9  | 8A  | A7   | A6  | Α5  | A4  | X         | X  | X  | X |

U = 0 : INCLUDE A8 IN ADDRESS COMPARISON

| LMASK    | ADD | RESS | BIT  | S C | OMP | AREI | D |   |   |

|----------|-----|------|------|-----|-----|------|---|---|---|

| 00<br>01 |     | X A7 |      |     |     |      |   |   |   |

| 10       |     | X A  |      |     |     |      |   |   |   |

| 11       | A9  | X A7 | 7 A6 | A5  | A4  | X    | X | X | X |

U = 1 : IGNORE A8 IN ADDRESS COMPARISON

THE PORT ADDRESS MASK REGISTER IS CLEARED BY A MASTER RESET.

| PORT | PORT CONTROL<br>REGISTER ADDRESS |

|------|----------------------------------|

| A    | FFF09                            |

| B    | FFF11                            |

| C    | FFF19                            |

| D    | FFF21                            |

|                                                                                                                                                                |    | RN DIGITAL            |             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------|-------------|--|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclose to anyone other than WDC employees without the written | 96 | BASE NUMBER<br>000610 | REV<br>X2.3 |  |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                |    | SHEET 14 O            | F 32        |  |

PORT ADDR - LOWER MSB

7 6 5 4 3 2 1

PORT ADDR - UPPER LSB

X X X A7 A6 A5 A4

0

76543 2

|      | PORT I/O | ADDRESS I | REGISTERS |

|------|----------|-----------|-----------|

| PORT | A9-A8    | A7-A4     | A3-A0     |

| Α    | FFFOA    | FFFOB     | FFF0C     |

| В    | FFF12    | FFF13     | FFF14     |

| C    | FFF1A    | FFF1B     | FFF1C     |

| D    | FFF22    | FFF23     | FFF24     |

The four Port A I/O Address registers are set to all zeroes by a master reset.

This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written authorization from WESTERN DIGITAL CORPORATION.

WESTERN DIGITAL

CORPORATION

CLASS CODE BASE NUMBER REV

96 000610 X2.3

SHEET 15 OF 32

The following table lists the I/O addresses and chip selects generated for each fixed port type. The number of wait states for the fixed ports is set by the External I/O Wait State Control register. The IOCS16- signal is generated only on accesses to the hard disk controller data port. The chip selects are not gated with IOR- or IOW-. The floppy controller operations register select and configuration register select may be generated from the CSF and CSHD- pins. The operations register is being accessed when CSF is active (high) and CSHD- is inactive (high). The configuration register is being accessed when both CSF and CSHD- are active.

| PORT      | BIT<br>SIZE | I/O<br>ADDRESS     | ACTIVE<br>PIN | FUNCTION                                                                          |

|-----------|-------------|--------------------|---------------|-----------------------------------------------------------------------------------|

| FLOPPY    | 8           | 3F2<br>372         | CSF           | FDC OPERATION SELECT. 3F2 IS PRIMARY ADDRESS, 372 IS SECONDARY ADDRESS.           |

|           | 8           | 3F4-3F5<br>374-375 | CSFP-         | 3F4-3F5 ARE PRIMARY ADDRESSES,<br>374-375 ARE SECONDARY.                          |

|           | 8           | 3F6<br>376         | CSHD-         | HARD DISK CONTROLLER CHIP SELECT. 3F6 IS PRIMARY ADDRESS, 376 IS SECONDARY.       |

| -         | 8           | 3F7<br>377         | CSF<br>CSHD-  | CSHD- AND CSF PINS WILL BE ASSERTED.<br>3F7 IS PRIMARY ADDRESS, 377 IS SECONDARY. |

| 80287     | 8           | 0EO-OFF            | CS287-        | 80287 CHIP SELECT.                                                                |

| 8042      | 8           | 060-06E<br>(EVEN)  | CS8042-       | 8042 CHIP SELECT.                                                                 |

| NMI LOGIC | 8           | 070-07E<br>(EVEN)  | CSNMI-        | NMI LOGIC SELECT.                                                                 |

| PARITY CK | 8           | 061-06F<br>(0DD)   | GTCK-         | PARITY CHECK SELECT AND PORT B CLOCK. EXTERNAL LOGIC MUST SEPERATE THE SIGNALS.   |

| HARD DISK | 16          | 1F0<br>170         | CSHD-         | HDC CHIP SELECT - DATA PORT ACCESS. 1FO IS PRIMARY ADDRESS, 170 IS SECONDARY.     |

|           | 8           | 1F1-1F7<br>171-177 | CSHD-         | HDC CHIP SELECT - TASK FILE. 1F1-1F7<br>ARE PRIMARY ADDRESSES, 171-177 SECONDARY. |

|                                                                                                          | WESTERN CORPORA  |                       |             |

|----------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |

| to anyone other than WDC employees without the written authorization from WESTERN DIGITAL CORPORATION.   |                  | SHEET 16 O            | F 32        |

# PRIMARY/SECONDARY PORT FUNCTION SELECT

FFF49

X X X X DH DF H F 7 6 5 4 3 2 1 0

DH=0 : Enable CSHD- output

DH=1 : Disable CSHD- output (always high)

DF=0 : Enable CSFP- and CSF outputs

DF=1 : Disable CSFP- and CSF outputs (always high)

H=0 : Primary hard disk port addressH=1 : Secondary hard disk port address

F=0 : Primary floppy disk port address F=1 : Secondary floppy disk port address

DH, DF, H, and F are cleared to '0' by master reset

WESTERN DIGITAL

CORPORATION

This information is confidential and proprietary to

WDC and shall not be reproduced or further disclosed

to anyone other than WDC employees without the written

authorization from WESTERN DIGITAL CORPORATION.

CLASS CODE 96 000610 X2.3

SHEET 17 OF 32

# MEMORY DECODE CONTROL

TWo RAS enable pins are available for controlling two 16 bit wide banks of system board RAM. A single CAS enable is provided; external circuitry must gate CASEN- with AO to enable the low or high bytes of memory. During a refresh cycle, both RAS enables will be active (ignoring the RAM configuration register FFF57) and CASEN will stay inactive. The MEMDIR signal is a logic '1' only when MEMR- is active and RASENO-, RASEN1-, or CSPROM- is active.

| PIN<br>NUMBER | MNEMONIC | 1/0 | FUNCTION                                                                           |

|---------------|----------|-----|------------------------------------------------------------------------------------|

| 5             | RASENO-  | 0   | RAS ENABLE FOR DRAM MEMORY BANK O                                                  |

| 3             | RASEN1-  | 0   | RAS ENABLE FOR DRAM MEMORY BANK 1                                                  |

| 4             | CASEN-   | 0   | CAS ENABLE FOR DRAM MEMORY BANKS 0 AND 1                                           |

| 1             | MAP-     | 0   | RAM MAP SIGNAL                                                                     |

| 47            | REFR-    | I   | MEMORY REFRESH SIGNAL                                                              |

| 67            | MEMDIR   | 0   | CONTROLS DIRECTION PIN OF 245 MEMORY LATCH, HIGH WHEN READING ON-BOARD RAM OR ROM. |

| 66            | CSPROM-  | 0   | BIOS PROM SELECT                                                                   |

| WESTERN DIC                                                                                                                                                     |                  |                       |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 18 O            | F 32        |

| PORT      |    | MEMORY<br>ADDRESS                            | i e            | FUNCTION                                                                                                                                                                       |

|-----------|----|----------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIOS PROM | 16 | OFOOOO-<br>OFFFFF                            | CSPROM-        | BIOS PROM ALSO SELECTED WHEN ADDRESS IS FF0000 TO FFFFFF.                                                                                                                      |

|           | 16 | 0C0000-<br>0C3FFF<br>0R<br>0C0000-<br>0C7FFF | CSPROM-<br>MAP | IF EGA BIOS MAPPING IS ENABLED, THEN BOTH CSPROM AND MAP PINS WILL BE ACTIVE WHEN OCOOOO-OC3FFF, THE EGA BIOS AREA, OR OCOOOO-OC7FFF, AN EXTENDED EGA BIOS AREA, IS ADDRESSED. |

SYSTEM BOARD PROM AND EXTERNAL WAIT STATE CONTROL REGISTER

| FFF50 | Х | X | X | X | RV | IS | 0 | XWS |

|-------|---|---|---|---|----|----|---|-----|

|       | 7 | _ | _ | _ |    | _  | 1 |     |

| RWS |        |

|-----|--------|

| 00* | 1 W.S. |

| 01  | 2 W.S. |

| 10  | 4 W.S. |

| 11  | 6 W.S. |

\* : DEFAULT AFTER MASTER RESET

XWS=0\*: 1 W.S FOR 16 BIT I/O, 4 W.S. FOR 8 BIT I/O 1: 6 W.S. FOR 8 OR 16 BIT I/O

The system BIOS address space is from F0000 to FFFFF. If the EGA BIOS is to be mapped, then the BIOS ROM chip select is also active when the region from C0000 to C3FFF is addressed, along with the MAP signal pin. The BIOS PROM size and number of wait states will then apply to both regions F0000-FFFFF and C0000-C3FFF.

The ROM memory is assumed to be 16 bits wide. If the ROM memory is actually implemented with 8 bit wide ROM chips, then the MEMCS16 output must be externally gated with the CSPROM signal. The RWS field specifies the number of wait states for the system ROM.

The XWS bit is used to program the minimum number of wait states for external RAM and external I/O. The FE3000 wait state generator will generate 1 wait state for 16 bit devices and 4 wait states for 8 bit devices. If the XWS bit is '0', then the FE3000 will generate the wait states. If the XWS bit is '1', then the FE3040 will extend the wait states to six for both 8 bit and 16 bit external devices.

|                                                                                                          | WESTERN DIGITAL  |                       |             |

|----------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |

| to anyone other than WDC employees without the written authorization from WESTERN DIGITAL CORPORATION.   |                  | SHEET 19 O            | F 32        |

## EPROM/RAM MAP CONTROL REGISTER

FFF51 X X X X EGA CTL 7 6 5 4 3 2 1 0

- EGA = 00: PROM chip select will be active when address is OFO000-OFFFFF or FF0000-FFFFFF. Default case after master reset.

- 01: Map OCOOOO-OC3FFF (16K EGA ROM area) to OF8000-OFBFFF so both can be placed in same physical rom.

When OCOOOO-OC3FFF is addressed then both PROM Chip Select and MAP pins will be active.

- 10: Map OCOOOO-OC7FFF (32K EGA ROM area) to OF8000-OFFFFF so both can be placed in same physical rom.

When OCOOOO-OC7FFF is addressed then both PROM Chip Select and MAP pins will be active.

- - 01: Swap RAM for EPROM in CO000-FFFFF, in 16K pages (requires minimum 1 MByte RAM). Ram swapping will override EGA mapping.

- 10: No EPROM/RAM swapping, map 384K (A0000-FFFFF) of RAM to extended memory. This mode is supported for three memory configurations: 1) bank 0 = 256K by 16, bank 1 = 256K by 16

2) bank 0 = 256K by 16, bank 1 = 1M by 16

3) bank 0 = 1M by 1, no bank 1

- 11: Swap RAM for EPROM in E0000-FFFFF, enableable in 16K pages (requires minimum 1 Mbyte RAM). Map 256K (A0000-DFFFF) of RAM to extended memory. This mode is supported for three memory configurations: 1) bank 0 = 256K by 16, bank 1 = 256K by 16

2) bank 0 = 256K by 16, bank 1 = 1M by 16

3) bank 0 = 1M by 1, no bank 1

|                                                                                                                                                                 | WESTERN DIGITAL  |                       |             |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|--|--|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |  |  |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 20 01           | F 32        |  |  |

Write protection is accomplished by not asserting CASEN when MEMW is active.

## EPROM/RAM MAP WRITE CONTROL REGISTER

FFF52 X X X X WPF WPE WPD WPC 7 6 5 4 3 2 1 0

WPF=1: WRITE PROTECT FFFFF-F0000 WPE=1: WRITE PROTECT EFFFF-E0000 WPD=1: WRITE PROTECT DFFFF-D0000 WPC=1: WRITE PROTECT CFFFF-C0000

#### EPROM/RAM SWAP CONTROL REGISTER

FFF53 X X X X ENFO ENF4 ENF8 ENFC

ENFC = 1 : SWAP FC000-FFFFF ENF8 = 1 : SWAP F8000-FBFFF ENF4 = 1 : SWAP F4000-F7FFF ENF0 = 1 : SWAP F0000-F3FFF

# EPROM/RAM SVAP CONTROL REGISTER

FFF54 X X X X ENEO ENE4 ENE8 ENFC

7 6 5 4 3 2 1 0

ENEC = 1 : SWAP ECOOO-EFFFF ENE8 = 1 : SWAP E8000-EBFFF ENE4 = 1 : SWAP E4000-E7FFF ENEO = 1 : SWAP E0000-E3FFF

## EPROM/RAM SWAP CONTROL REGISTER

FFF55 X X X X ENDO END4 END8 ENDC

7 6 5 4 3 2 1 0

ENDC = 1 : SWAP DC000-DFFFF END8 = 1 : SWAP D8000-DBFFF END4 = 1 : SWAP D4000-D7FFF END0 = 1 : SWAP D0000-D3FFF

## EPROM/RAM SWAP CONTROL REGISTER

FFF56 X X X ENCO ENC4 ENC8 ENCC

ENCC = 1 : SWAP CC000-CFFFF ENC8 = 1 : SWAP C8000-CBFFF ENC4 = 1 : SWAP C4000-C7FFF ENC0 = 1 : SWAP C0000-C3FFF

THESE REGISTERS ARE CLEARED BY MASTER RESET.

WESTERN DIGITAL

CORPORATION

This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written authorization from WESTERN DIGITAL CORPORATION.

WESTERN DIGITAL

CLASS CODE BASE NUMBER 000610 X2.3

SHEET 21 OF 32

RAM CONFIGURATION REG

BNK 1 BNK O FFF57 X SZ SZ

BANK O SZ=00: NO RAM PRESENT

SZ=01 : RESERVED SZ=10 : 256K DRAM SZ=11 : 1MBIT DRAM

BANK 1 SZ=00: NO RAM PRESENT

SZ=01 : 64K DRAM SZ=10 : 256K DRAM SZ=11 : 1MBIT DRAM

AFTER MASTER RESET, BANK1 SZ=00, BANK0 SZ=10

NOTE: 64K DRAM IS SUPPORTED ONLY IN BANK 1 AND ONLY WHEN BANK O SZ=10.

RAM CONTROL REG

FFF58

XXXSDXCULLEE

SD=1: DISABLE MEM FROM 512K TO 640K XC=1: EXCHANGE RASENO AND RASEN1

UL=1: MEMORY CONTROL SIGNALS UNLATCHED

EE=1: DISABLE MEM FROM 256K TO 640K

# REGISTER CLEARED BY MASTER RESET.

When the SD bit is set, on-board memory will be disabled when addressed between 512K and 640K, to support certain SDLC controller cards. When the EE bit is set, on-board memory will be disabled when addressed between 256K and 640K, to support EEMS expanded memory boards. When the XC bit is set, RASENO and RASEN1 signals are exchanged, to simplify the determination of RAM type in bank 1 at boot-up time. When the UL bit is set, the RASENO-, RASEN1-, CASEN-, MEM16-, MEMOLD CORPON and MAP pins are uplateded rather than being latehed by MEMDIR-, CSPROM-, and MAP- pins are unlatched, rather than being latched by ADALE.

ON-BOARD RAM

WAIT STATE CONTROL REG

FFF60

BNK 1 BNK 0  $X \mid X \mid$ X WS WS

BANK O WS = 00 : O WAIT STATES

= 01 : 1 WAIT STATE \* = 10 : 2 WAIT STATES = 11 : 3 WAIT STATES

BANK 1 WS = 00 : 0 WAIT STATES

= 01 : 1 WAIT STATE \* = 10 : 2 WAIT STATES = 11 : 3 WAIT STATES

\* : DEFAULT AFTER MASTER RESET

WESTERN DIGITAL CORPORATION CLASS CODE BASE NUMBER REV 96 000610 X2.3 SHEET 22 OF

This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written authorization from WESTERN DIGITAL CORPORATION.

#### CLOCK SWITCH CONTROL

This logic section provides glitchless clock switching between two clocks under CPU control. CLK1 is immediately selected for the processor clock, without glitch suppression, when the reset pin is asserted. CLK1 divided by 2 is immediately selected for the DMA clock, without glitch suppression, when the reset pin is asserted.

If CLK2 has not gone high since master reset, clock switching from CLK1 to CLK2 is inhibited. If the CLK2 pin is not used, it should be tied to ground.

Two bus compatibility clock switch modes are available when the SEL field is 01 or 11. In both modes, on board memory is accessed at the full clock speed, while DMA transfers are made at half speed. In the medium speed mode, external I/O devices (devices on the I/O bus) are accessed at half the clock rate, while on board I/O devices are accessed at full speed. External memory is also accessed at full speed.

In the slowest speed mode, all external memory and all I/O, both on board and external, is accessed at half speed.

For board test purposes, the PCLK pin may be tristated. Refer to the next section for a description of the test mode.

| PIN<br>NUMBER | MNEMONIC | I/0 | FUNCTION                                        |

|---------------|----------|-----|-------------------------------------------------|

| 50            | MR-      | I   | MASTER RESET                                    |

| 31            | CLK1     | Ι   | INPUT CLOCK 1                                   |

| 30            | CLK2     | I   | INPUT CLOCK 2                                   |

| 32            | PCLK     | 0   | PROCESSOR CLOCK, SWITCHED BETWEEN CLK1 AND CLK2 |

|                                                                                                                                                                 | WESTERN DIGITAL  |                       |             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|--|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |  |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 23 OI           | 32          |  |

## PROCESSOR CLOCK SELECT REGISTER

FFF62

X X X X VAR SEL

7 6 5 4 3 2 1 0

VAR = 00\*: NORMAL CLOCK

01 : MEDIUM SPEED BUS COMPATIBLE CLOCK SWITCH MODE 10 : SLOWEST SPEED BUS COMPATIBLE CLOCK SWITCH MODE

11 : RESERVED

SEL = 00\*: SELECT CLK1 DIVIDED BY 2 FOR PCLK

= 10 : SELECT CLK1 FOR PCLK

= 01 : SELECT CLK2 DIVIDED BY 2 FOR PCLK

= 11 : SELECT CLK2 FOR PCLK

\* : DEFAULT AFTER MASTER RESET

WESTERN DIGITAL

CORPORATION

This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written authorization from WESTERN DIGITAL CORPORATION.

WESTERN DIGITAL

CLASS CODE BASE NUMBER REV 000610 X2.3

SHEET 24 OF 32

#### TEST MODE

All output pins will become tristated if MEMR- and MEMW- are active simultaneously while MR- is active. The outputs will remain tristated if MR- is brought inactive while MEMR- and MEMW- are both active. The outputs will become active drivers again when MR- is brought low without both MEMR- and MEMW- active. This "all output tristate" mode allows an in-circuit board tester to drive the FE3040 output pins.

The PCLK pin will become tristated if IOR- and MEMW- are active simultaneously while MR- is active. The PCLK pin will remain tristated if MR- is brought inactive while IOR- and MEMW- are both active. The PCLK pin will become an active driver again when MR- is brought low without both IOR- and MEMW- active.

|                                                                                                                                                                 | -                | ERN DIGITA            |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 25 O            | F 32        |

|                                                                                                                                                                 |    | ERN DIGITA            |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------|-------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | 96 | BASE NUMBER<br>000610 | REV<br>X2.3 |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |    | SHEET 26 OI           | 32          |

|                                                                                                                                                                 | WESTERN DIGITAL  |                       |             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|--|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |  |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 27 O            | F 32        |  |

| FFF53 | ENFC ENF8 ENF4 ENFO | EPROM/RAM SWAP CONTROL          |

|-------|---------------------|---------------------------------|

| FFF54 | ENEC ENE8 ENE4 ENEO | EPROM/RAM SWAP CONTROL          |

| FFF55 | ENDC END8 END4 END0 | EPROM/RAM SWAP CONTROL          |

| FFF56 | ENCC ENC8 ENC4 ENCO | EPROM/RAM SWAP CONTROL          |

| FFF57 | BNK 1 BNK 0 SZ SZ   | RAM CONFIGURATION               |

| FFF58 | X X X X SD XC UL EE | RAM CONTROL REG                 |

| FFF60 | BNK 1 BNK 0 WS WS   | ON-BOARD RAM WAIT STATE CONTROL |

| FFF62 | VAR SEL             | PROCESSOR CLOCK SELECT          |

| FFFFF | xxxx                | LOCK REGISTER                   |

|                                                                                                                                                                 |                  | ERN DIGITA            | · <del></del> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|---------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3   |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 28 0            | F 32          |

| SYMBOL | CHARACTERISTIC                         | MIN | MAX  | UNITS | CONDITIONS                                             |

|--------|----------------------------------------|-----|------|-------|--------------------------------------------------------|

| IIL    | INPUT LEAKAGE                          |     | +-10 | UA    | VIN=.4 TO VCC                                          |

| 102    | TRISTATE AND OPEN DRAIN OUTPUT LEAKAGE |     | +-10 | UA    | VOUT=.4 TO VCC                                         |

| VIH    | INPUT HIGH VOLTAGE                     | 2.0 | -    | v     | •                                                      |

| VIL    | INPUT LOW VOLTAGE                      |     | .8   | v     | -                                                      |

| ıcc    | SUPPLY CURRENT                         | -   | 50   | MA    | ALL OUTPUTS OPEN, INPUTS AT 2.0V, CLKOUT=SYSCLK=12 MHZ |

FOR OUTPUTS CSFP-, CSF, CSHD-, CSPRGA-, CSPRGB-, CSPRGC-, CSPRGD-/RST-, CS8042-, CS287-, CSNMI-, GTCK-, AND D3-D0

| SYMBOL | CHARACTERISTIC      | MIN | MAX | UNITS | CONDITIONS |

|--------|---------------------|-----|-----|-------|------------|

| voн    | OUTPUT HIGH VOLTAGE | 2.4 |     | v     | IOUT=-2 MA |

| VOL    | OUTPUT LOW VOLTAGE  | † - | .4  | v     | IOUT=2 MA  |

FOR OUTPUTS RASENO-, CASEN-, RASEN1-, MAP-, MEMDIR, CSPROM-, SLDAT-, IO16-, EMM16-, IORDY, ZWS-, PCLK

| SYMBOL | CHARACTERISTIC      | MIN | MAX | UNITS | CONDITIONS |

|--------|---------------------|-----|-----|-------|------------|

| voн    | OUTPUT HIGH VOLTAGE | 2.4 |     | v     | IOUT=-4 MA |

| VOL    | OUTPUT LOW VOLTAGE  |     | .4  | v     | IOUT=4 MA  |

|                                                                                                                                                                 |                  | ERN DIGITA            |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-------------|

| This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written | CLASS CODE<br>96 | BASE NUMBER<br>000610 | REV<br>X2.3 |

| authorization from WESTERN DIGITAL CORPORATION.                                                                                                                 |                  | SHEET 29 01           | 32          |

# AC TIMING CHARACTERISTICS load capacitance=50 pF each output

## CLOCK TIMING

FE3040

| SYMBOL     | CHARACTERISTIC `            | MIN | МАХ      | UNITS                                        | CONDITIONS    |

|------------|-----------------------------|-----|----------|----------------------------------------------|---------------|

| T1         | CLK1, CLK2 CYCLE            | 40  |          | NS                                           |               |

| Т2         | CLK1, CLK2 HIGH PULSE WIDTH | 16  |          | NS                                           |               |

| т3         | CLK1, CLK2 LOW PULSE WIDTH  | 16  |          | NS                                           |               |

| Т4         | CLK1, CLK2 TO PCLK          |     | 38       | NS                                           | DIV BY 1 MODE |

| Т5         | CLK1, CLK2 TO PCLK          |     | 38       | NS                                           | DIV BY 2 MODE |

| Т6         | SO-,S1- SETUP TO PROCLK     | -4  | Ī        | NS                                           |               |

| <b>T</b> 7 | SO-,S1- HOLD FROM PROCLK    |     | 20       | NS                                           |               |

| Т8         | MIO SETUP TO PROCLK         | 10  |          | NS                                           |               |

| Т9         | MIO HOLD FROM PROCLK        |     | 10       | NS                                           |               |

| т10        | PCLK SETUP TO PROCLK        | 5   | 28       | NS                                           | 7             |

| <u> </u>   | <u> </u>                    | İ   | <u> </u> | <u>†                                    </u> |               |

This information is confidential and proprietary to WDC and shall not be reproduced or further disclosed to anyone other than WDC employees without the written authorization from WESTERN DIGITAL CORPORATION.

WESTERN DIGITAL CLASS CODE BASE NUMBER REV 000610 X2.3

009581 🗸 \_ \_