# SL9151 80286 Page Interleave Memory Controller

**PRELIMINARY**

#### **FEATURES**

- · Supports 80286 based designs.

- 16, 20 or 25 MHz Options.

- Enhanced Fast Page Mode/Page Interleave DRAM Controller.

- Hardware support for EMS LIM 4.0 standard and EEMS.

- Supports up to 8 M byte of on board memory.

- Programmable Shadow RAM feature of 128K or 256K.

- Programmable 2 or 4 way Memory Interleaving Option.

- Programmable Wait State Options.

- Can use 256K x 1, 256K x 4, and 1 M x 1 DRAMs or a mix.

- Supports 120ns and 80ns DRAMs at 16 MHz, 80ns and 60ns at 20 MHz and 60ns and 40ns at 25MHz.

- Programmable Registers for changing switch settings.

- Selectable Wait States for Slower DRAMs.

- Selectable remapping of 640K 1 M RAM to top of the address space.

- Advanced CMOS Technology.

- 100 pin Flatpack.

#### DESCRIPTION

The SL9151 Memory Controller is a second generation integration of the most popular 80286 system level features. Both EMS LIM 4.0 and EEMS are now available on the chip. Programmable registers are available for controlling 2 or 4 way memory interleave options. In addition, earlier features have been expanded and optimized for higher performance.

The SL9151, along with the SL925X and SL935X provide complete PC/AT solutions by utilizing the same core logic chips. It is designed using advanced 1.5 micron, double layer metal CMOS process and is offered in a 100 pin plastic flatpack package.

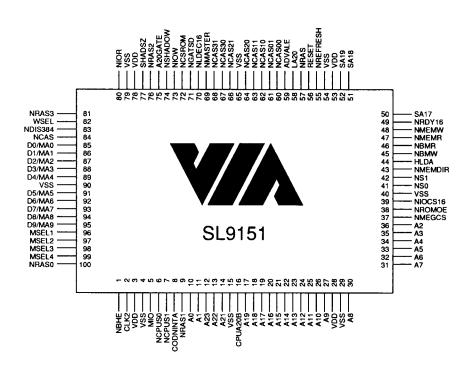

### **PINOUT**

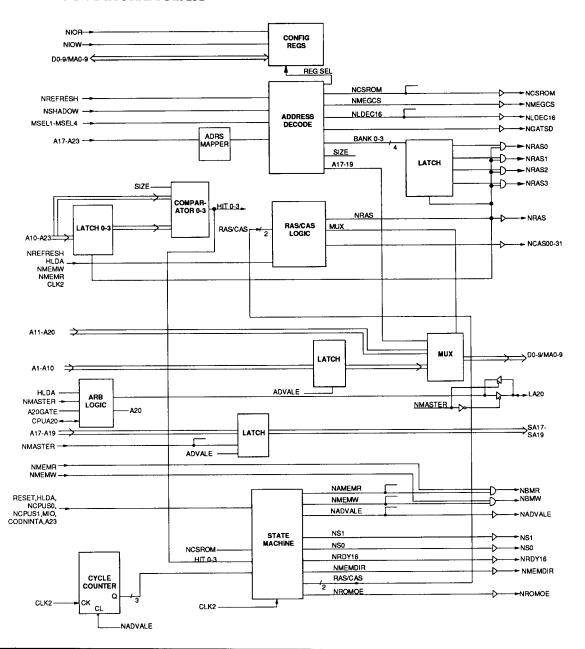

### **BLOCK DIAGRAM SL9151**

### DESCRIPTION

### **ROM/RAM DECODE**

The device provides all necessary circuitry to decode on board RAM/ROM cycles. User can select one to four banks using 256K, 1MB, or a mix of both using regular or Static Column or Fast Page DRAMs.

The system can be configured for 512K Bytes to 8M Bytes. The bank selection code & sizes are as follows:

| Total On     | Memory in Each Bank |             |      |             |     | Switch S | Operation |       |                              |

|--------------|---------------------|-------------|------|-------------|-----|----------|-----------|-------|------------------------------|

| Board Memory | Bank3               | nk3 Bank2 l |      | Bank1 Bank0 |     | Msel3    | Msel2     | Msel1 | Mode                         |

| 512K         |                     |             |      | 512K        | 0   | 0        | 0         | 0     | Non interleaved              |

| 1M           |                     |             | 512K | 512K        | 0   | 0        | 0         | 1 1   | Non interleaved              |

| 1.5M         |                     | 512K        | 512K | 512K        | 0   | 0        | 1         | 0     | Non interleaved              |

| 2M           | 512K                | 512K        | 512K | 512K        | 0   | Ó        | 1         | 1     | Non Interleaved              |

| 3M           |                     | 2M          | 512K | 512K        | 0   | 1        | 1         | ٥     | Non Interleaved              |

| 5M           | 2M                  | 2M          | 512K | 512K        | 0   | 1        | 1         | 1     | Non Interleaved              |

| 2M           |                     |             |      | 2M          | 1   | ۱,       | ١،        | ١،    | Non Interleaved              |

| 4M           |                     |             | 2M   | 2M          | 1   | Ιi       | ١ŏ        | l i   | Non Interleaved              |

| 6M           |                     | 2M          | 2M   | 2M          | 1   | l i      | Ιĭ        | Ιò    | Non interleaved              |

| 8M           | 2M                  | 2M          | 2M   | 2M          | 1   | 1        | 1         | 1     | Non interleaved interleaved: |

| 1M           |                     |             | 512K | 512K        | 1 1 | ٥        | 0         | ٥     | 2 Way                        |

| 2M           | 512K                | 512K        | 512K | 512K        | 1   | Ŏ        | ō         | 1     | 4 Way                        |

| 4M           |                     |             | 2M   | 2M          | ١,  | ١,       | ۱,        |       | 2 Way                        |

| 8M           | 2M                  | 2M          | 2M   | 2M          | i   | ŏ        | i         | 1     | 4 Way                        |

Table 1

When NDIS384 input is tied low, the 384K remap to the top of the memory space is disabled.

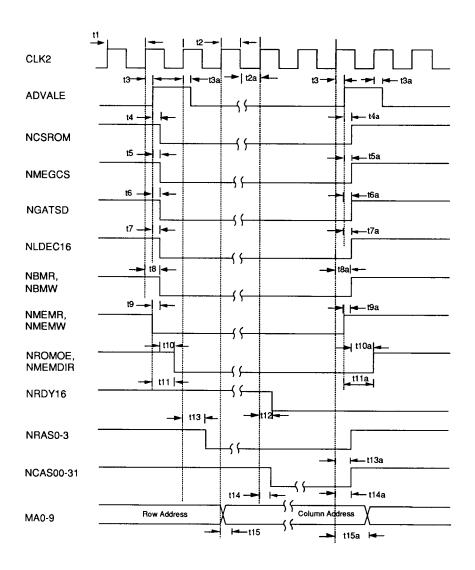

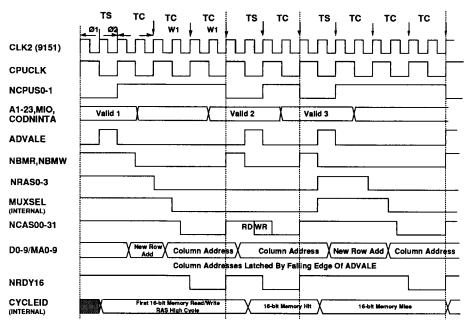

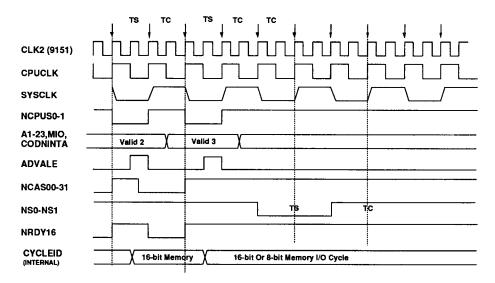

When CPU accesses the memory for the first time, the controller runs a page miss memory cycle and asserts RAS and CAS low at appropriate times (Fig. 1). RAS is left low, CAS is returned high at the end of the cycle and the current row address is stored in an internal register. During all subsequent cycles, row addresses are compared with previous value stored in the register. If a match (hit) is detected, then the RAS is held low and CAS is strobed immediately. If a mismatch (miss) is detected then RAS is brought high for 3 CLK2 cycles before reasserting low, and new row address is stored in the row address register. The controller will now run an 0/2 or 1/3 wait state memory cycle depending on the switch setting WSEL1 (Fig. 1, Fig. 2).

Page is automatically sized to 2KB if any 256K DRAMs are used and to 4KB if only 1M DRAMs are used.

CPU Addresses A11-A20 are passed onto MA0-9 as latched row addresses whereas A1-A10 are latched on the falling edge of ADVALE and passed onto MA0-9 as column addresses at appropriate time. NRAS, MUXSEL (internal), and NCAS00-31 are separated by one CLK2 period as shown in the timing diagram (fig.1). This latching of column addresses allows the use of static column DRAMs as well.

### ROM/RAM CONTROL

SL9151 provides all the circuitry needed to generate RAM/ROM controls. Row Address Strobe (NRAS0-3), Column Address Strobe (NCAS00-31), RAM Read/Write (NBMR, NBMW) ready for 16 bit on board RAM read/write (NRDY16) and non on-board memory/IO cycle status (NS0, NS1) are generated at appropriate times as shown in the timing diagram.

| МЮ                         | CODNINTA                   | CPUNS0                | CPUNS1  | ADDRESS | CYCLE TYPE                                                                                                   |

|----------------------------|----------------------------|-----------------------|---------|---------|--------------------------------------------------------------------------------------------------------------|

| 1<br>1<br>1<br>1<br>0<br>0 | 0<br>0<br>1<br>1<br>0<br>1 | 0<br>0<br>1<br>0<br>0 | 1 0 0 1 |         | MEM CODE READ<br>HALT/SHUTDOWN<br>MEM DATA READ<br>MEM DATA WRITE<br>INTA<br>I/O DATA READ<br>I/O DATA WRITE |

Table 2

The chip allows for use of slower DRAMs with selectable wait states. The wait states for a 16 bit memory miss can be set using the following table.

| CPU<br>SPEED | WSEL1 | WAIT S<br>Page Miss |   | MEMORY<br>SPEED (NS) |

|--------------|-------|---------------------|---|----------------------|

| 16           | 1     | 3                   | 1 | 120                  |

|              | 0     | 2                   | 0 | 80                   |

| 20           | 1     | 3                   | 1 | 80                   |

|              | 0     | 2                   | 0 | 60                   |

| 25           | 1     | 3                   | 1 | 60                   |

| L            | 0     | 2                   | 0 | 40                   |

Table 3

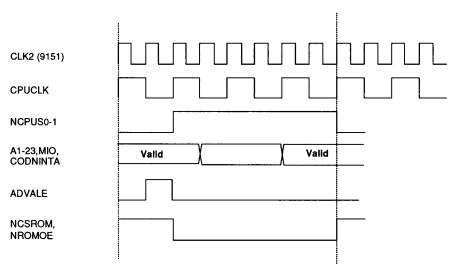

ROM controls, NCSROM and NROMOE, are asserted low at appropriate time when address 0E0000h-0FFFFFh or FE0000h-FFFFFh is decoded during a memory cycle. The timing relationship is shown in the timing diagram. If Shadow RAM option is used by strapping NSHADOW pin low, the subsequent ROM code reads will be treated as RAM reads and ROM controls are disabled. BIOS customization is required to activate this option at boot time. NSHADOW option only affects the 128K/256K region immediately below 1 Meg, depending on the state of SHADSZ pin.

#### **REFRESH**

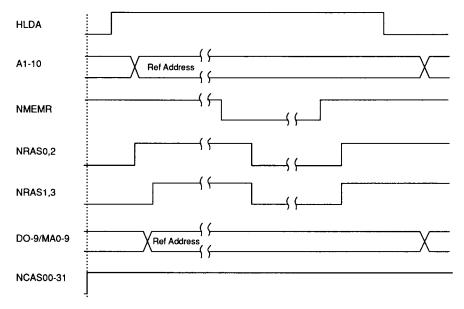

The SL9151 provides support for DRAM refresh. During refresh NRAS0-3 are deasserted and then asserted low, NCAS is inhibited high, the current bus state is ignored, and a refresh address generated by SL9025 Address Controller are passed from A Bus to MA Bus.

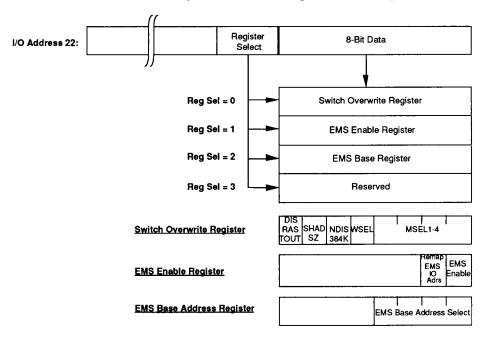

### **INTERNAL REGISTERS**

16 Bit I/O write to address 22 writes a byte of data to one of 4 registers as selected by Data Bits 8 and 9.

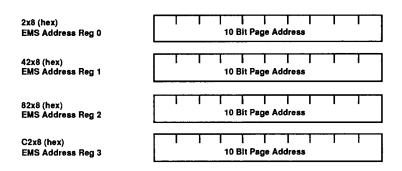

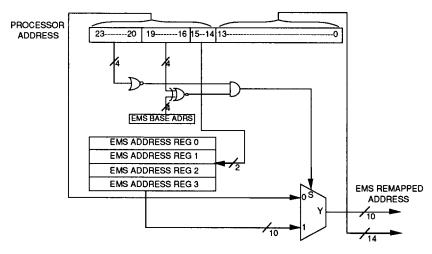

There are 4 EMS address registers of 10 bits width each, at the addresses: 2x8, 42x8, 82x8 and C2x8. X is 0 or 1 as defined by EMS Enable Register Bit 1. They each contain the Page Address for EMS Remapped Page.

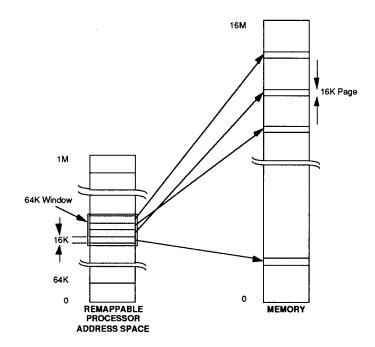

The remapping is shown in the diagrams.

### **EMS REMAPPING**

EMS Base Address can be set to any 64K boundary in the first 1 Meg address space of the processor. Then four 16K pages above that (base-address) can be mapped to any 16K boundary in the 16 Meg space.

# **PIN DESCRIPTION SL9151**

| SYMBOL                                | PIN                                                         | ТҮРЕ | DESCRIPTION                                                                                                                                                  |  |

|---------------------------------------|-------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A1-A16                                | 11,36,35,34,<br>33,32,31,30,<br>27,26,25,24,<br>23,22,21,20 | I    | CPU Address Bus.                                                                                                                                             |  |

| A17-A23                               | 19,18,17,14,<br>13,12                                       | I    | CPU Address Bus.                                                                                                                                             |  |

| A20GATE                               | 75                                                          | I    | CPUA20 is forced LOW when A20GATE is LOW and itransmitted as generated by CPU when A20GATE is HIGH.                                                          |  |

| ADVALE                                | 59                                                          | 0    | Advanced Address Latch Enable. It latches local bus address for the system bus.                                                                              |  |

| CLK2                                  | 2                                                           | I    | CLK2 from SL9011 System Controller. CPU should get inverted CLK2.                                                                                            |  |

| CODNINTA                              | 8                                                           | I    | CPU status signal.                                                                                                                                           |  |

| CPUA20B                               | 16                                                          | I/O  | CPU Address 20 or LA20.                                                                                                                                      |  |

| D0-9/MA0-9                            | 85,86,87,88,<br>89,91,92,93,<br>94,95                       | I/O  | DRAM address bus. Data Bus for writing to the programmable registers for EMS and option select registers.                                                    |  |

| HLDA                                  | 44                                                          | I    | Asserted to signal that the CPU has relinquished control of the bus to the requesting device.                                                                |  |

| LA20                                  | 58                                                          | I/O  | Decoded 20-bit address bit used to generate address decode for 1 M RAMs.                                                                                     |  |

| MIO                                   | 5                                                           | I    | CPU Output signal. When HIGH, it indicates a memory cycle, when LOW it indicates an I/O cycle. It is used to generate memory and I/O signals for the system. |  |

| MSEL1-4                               | 96,97,98,99                                                 | I    | On-board DRAM memory size and type select.<br>Internally pulled down. See Table 1.                                                                           |  |

| NBMR                                  | 46                                                          | 0    | Buffered Memory Read signal.                                                                                                                                 |  |

| NBMW                                  | 45                                                          | О    | Buffered Memory Write signal.                                                                                                                                |  |

| NCAS                                  | 84                                                          | О    | Logical Or of all CAS00-31 signals.                                                                                                                          |  |

| NCAS00,01,<br>10, 11,20, 21<br>30, 31 | 60-64, 66-68                                                | 0    | Memory Column Address Strobe. Asserted LOW when either CPU or DMA is accessing the memory.                                                                   |  |

# PIN DESCRIPTION SL9151 (Cont'd.)

| SYMBOL   | PIN         | TYPE | DESCRIPTION                                                                                                                                                                                                    |  |  |

|----------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          |             |      |                                                                                                                                                                                                                |  |  |

| NCPUS0,1 | 6,7         | I    | CPU status signal.                                                                                                                                                                                             |  |  |

| NCSROM   | 72          | О    | LOW assert Read Only Memory Chip select.                                                                                                                                                                       |  |  |

| NDIS384  | 83          | I    | Optional Disable for 684K - 1M [384K] remap. When LOW disables remap.                                                                                                                                          |  |  |

| NGATSD   | 71          | 0    | Control for an external data buffer used for writing from XD Bus to XD/MA inputs only during I/O write cycles. This signal may be used to enable a 74245 type device. When LOW the 74245 may enable this data. |  |  |

| NIOCS16  | 39          | I/O  | 16 Bit I/O cycle indication.                                                                                                                                                                                   |  |  |

| NIOR     | 80          | I/O  | Input/Output Read is an active LOW bi-directional pin for the AT System bus. It is an output for CPU and DMA cycles and an input during an external master bus cycle.                                          |  |  |

| NIOW     | 73          | I/O  | Input/Output Write is an active LOW bi-directional pin for the AT System bus. It is an output for CPU and DMA cycles and an input during an external master bus cycle.                                         |  |  |

| NSHADOW  | 74          | I    | Selectable Option for Shadow RAMs. When LOW enables Shadow RAM feature.                                                                                                                                        |  |  |

| NLDEC16  | 70          | O    | Decode for on-board high speed 16-bit RAM.                                                                                                                                                                     |  |  |

| NMASTER  | 69          | I    | Asserted when an external device has control of the AT Bus.                                                                                                                                                    |  |  |

| NMEGCS   | 37          | 0    | Decode for lower 1M of RAM.                                                                                                                                                                                    |  |  |

| NMEMDIR  | 43          | 0    | Direction select between D Bus and MD Bus. Read when LOW, generated by SL9011 System Controller.                                                                                                               |  |  |

| NMEMR    | 47          | I    | LOW assert Memory Read signal from SL9011 System Controller.                                                                                                                                                   |  |  |

| NMEMW    | 48          | I    | LOW assert Memory Write signal from SL9011 System Controller.                                                                                                                                                  |  |  |

| NRAS     | 57          | O    | LOW assert Row Address Strobe.                                                                                                                                                                                 |  |  |

| NRAS0-3  | 100,9,76,81 | 0    | Row Address Strobes for Banks 0, 1, 2 and 3 for the on-board memory. Asserted LOW during CPU or DMA cycle for memory access.                                                                                   |  |  |

# PIN DESCRIPTION SL9151 (Cont'd.)

| SYMBOL     | PIN                        | ТҮРЕ | DESCRIPTION                                                       |

|------------|----------------------------|------|-------------------------------------------------------------------|

| NRDY16     | 49                         | 0    | Asserted LOW to signal the end of 16 bit on board memory cycle.   |

| NREFRESH   | 55                         | I    | On-board RAM refresh signal.                                      |

| NROMOE     | 38                         | 0    | Enables ROM Output during ROM read cycles.                        |

| NS0,1      | 41,42                      | О    | 80286 compatible status signals for the SL9011 System Controller. |

| RESET      | 56                         | I    | Active HIGH reset from system controller.                         |

| SA17,18,19 | 50,51,52                   | O    | System Address Bus.                                               |

| SHADSZ     | 77                         | I    | Selects Shadow Memory Size. 0 = 128K. 1 = 256K.                   |

| WSEL       | 82                         | I    | Wait-state Select Options. Internally pulled up. See Table 3.     |

| VDD        | 3,28,53,78                 | -    | +5V. Power.                                                       |

| VSS        | 4,15,29,40,<br>54,65,79,90 | -    | 0V. Ground.                                                       |

### **AC TIMING DIAGRAMS SL9151**

Fig. 1 16 Bit On Board/Local Memory Cycles Timing Diagram

Fig. 2 Timing Diagram for I/O and Off Board Memory Cycles

### **ACTIMING DIAGRAMS SL9151**

Fig. 3. ROM Cycle

Fig. 4. Refresh Cycle

## ABSOLUT MAXIMUM RATINGS SL9151 \*note 1

| PARAMETERS     | SYMBO | L MIN.      | MAX.   | UNITS |  |

|----------------|-------|-------------|--------|-------|--|

|                |       |             |        |       |  |

| Supply Voltage | Vdd   | 5           | 6.0    | V     |  |

| Input Voltage  | V1    | 5           | VDD+.5 | V     |  |

| Output Voltage | Vo    | 5           | VDD+.5 | V     |  |

| Output Current | Ios   | -40         | +40    | mA    |  |

| Output Current | Ios   | <b>-4</b> 0 | +80    | mA    |  |

| Output Current | Ios   | -60         | +120   | mA    |  |

| Output Current | Ios   | -90         | +180   | mA    |  |

| Storage Temp.  | TSTL  | <b>-4</b> 0 | +125   | °C    |  |

| Storage Temp.  | TBIOS | -25         | +85    | °C    |  |

# RECOMMENDED OPERATING CONDITIONS

| PARAMETERS     | SYMBOL | MIN. | MAX. | UNITS |

|----------------|--------|------|------|-------|

| Supply Voltage | Vdd    | 4.75 | 5.25 | V     |

| Temperature    | TA     | 0    | 70   | °C    |

<sup>\*</sup> NOTES:

<sup>1.</sup> Permanent device damage may occur if device ratings are exceeded. Reliability may be affected by sustained exposure to absolute maximum values.

# DC CHARACTERISTICS SL9151

$(TA = 0 \circ C \text{ to } 70 \circ C, VDD = 5V + 5\%)$

| PARAMETERS                            | SYMBOL | MIN.   | MAX.     | UNITS          | CONDITIONS             |

|---------------------------------------|--------|--------|----------|----------------|------------------------|

|                                       |        |        |          |                |                        |

| Power Supply Current                  | Idds   | 0      | 100      | μΑ             | Steady state*          |

| Output High Voltage for Normal Output | Vон    | 4.0    | $V_{DD}$ | V              | IOH = -2 mA            |

| (IOL = 3.2  mA)                       |        |        |          |                |                        |

| Output High Voltage for Driver Output | Vон    | 4.0    | VDD      | V              | IOH = -2 mA            |

| (IOL = 8 mA)                          |        |        |          |                |                        |

| Output High Voltage for Driver Output | Vон    | 4.0    | $V_{DD}$ | V              | IOH = - 4 mA           |

| (IOL = 12 mA)                         |        |        |          |                |                        |

| Output High Voltage for Driver Output | Vон    | 4.0    | Vdd      | V              | IOH = -8 mA            |

| (IOL = 24 mA)                         |        |        |          |                |                        |

| Output Low Voltage for Normal Output  | Vol    | Vss    | 0.4      | v              | IOL = 3.2 mA           |

| (IOL = 3.2  mA)                       |        |        |          |                |                        |

| Output Low Voltage for Driver Output  | Vol    | Vss    | 0.4      | v              | IOL = 8 mA             |

| (IOL = 8 mA)                          |        |        |          |                |                        |

| Output Low Voltage for Driver Output  | Vol    | Vss    | 0.4      | V              | IOL = 12.0 mA          |

| (IOL = 12 mA)                         |        |        |          |                |                        |

| Output Low Voltage for Driver Output  | Vol    | Vss    | 0.5      | V              | IOL = 24.0  mA         |

| (IOL = 24mA)                          |        |        |          |                |                        |

| Input High Voltage for Normal Input   | Vih    | 2.2    |          | V              |                        |

| Input Low Voltage for Normal Input    | Vil    |        | 0.8      | V              |                        |

| Input High Voltage for CMOS Input     | Vih    | 0.7Vdd |          | V              |                        |

| Input Low Voltage for CMOS Input      | Vil    |        | 0.3VD    | DΫ             |                        |

| Input Leakage Current                 | Ili    | -10    | 10       | μΑ             | VI = 0 - VDD           |

| Input Leakage Current                 | ILZ    | -10    | 10       | <i>.</i><br>μΑ | Tri-state VI = 0 - VDD |

| Input Pull-up/Down Resistor           | RP     | 25     | 100      | ΚΩ             | VIH = VDD              |

| r,                                    | _      |        |          |                | VIL = VSS              |

### NOTES:

\* VIH = VDD, VIL = Vss

RAS0-RAS3, NBMR, NBMW, SA17-SA19

LA17-LA23, MA0-MA9 A1-A16, A17-A23 = 24 mA (typical)

= 12 mA

= 8 mA

# AC CHARACTERISTICS SL9151

$(TA = 0 \circ C \text{ to } 70 \circ C, VDD = 5V \pm 5\%)$

| SYMBOL | DESCRIPTION                              | MIN. | MAX. | UNITS |

|--------|------------------------------------------|------|------|-------|

| t1     | CLK2 Period                              | 25   | _    | ns    |

| t2     | CLK2 High Duration                       | 7    | -    | ns    |

| t2a    | CLK2 Low Duration                        | 7    | -    | ns    |

| t3     | CLK2 to ADVALE (Low to High)             | 5    | 20   | ns    |

| t3a    | CLK2 to ADVALE (High to Low)             | 5    | 20   | ns    |

| t4     | ADVALE to NCSROM (High to Low)           | 5    | 15   | ns    |

| t4a    | ADVALE to NCSROM (Low to High)           | 5    | 15   | ns    |

| t5     | ADVALE to NMEGCS (High to Low)           | 5    | 15   | ns    |

| t5a    | ADVALE to NMEGCS (Low to High)           | 5    | 15   | ns    |

| t6     | ADVALE to NGATSD (High to Low)           | 5    | 15   | ns    |

| t6a    | ADVALE to NGATSD (Low to High)           | 5    | 15   | ns    |

| t7     | ADVALE to NLDEC16 (High to Low)          | 5    | 15   | ns    |

| t7a    | ADVALE to NLDEC16 (Low to High)          | 5    | 15   | ns    |

| t8     | CLK2 to NBMR, NBMW (High to Low)         | 5    | 12   | ns    |

| t8a    | CLK2 to NBMR, NBMW (Low to High)         | 5    | 12   | ns    |

| t9     | NMEMR, NMEMW to NBMR, NBMW (High to Low) | 5    | 10   | ns    |

| t9a    | NMEMR, NMEMW to NBMR, NBMW (Low to High) | 5    | 10   | ns    |

| t10    | NBMR to NROMOE (High to Low)             | 0    | 12   | ns    |

| t10a   | NBMR to NROMOE (Low to High)             | 0    | 12   | ns    |

| t11    | NMEMR to NROMOE (High to Low)            | 5    | 15   | ns    |

| t11a   | NMEMR to NROMOE (Low to High)            | 5    | 15   | ns    |

| t12    | CLK2 to NRDY16                           | 5    | 12   | ns    |

| t13    | CLK2 to NRAS0-NRAS3 (High to Low)        | 5    | 12   | ns    |

| t13a   | CLK2 to NRAS0-NRAS3 (Low to High)        | 5    | 12   | ns    |

| t14    | CLK2 to NCAS00-31 (High to Low)          | 5    | 12   | ns    |

| t14a   | CLK2 to NCAS00-31 (Low to High)          | 5    | 12   | ns    |

| t15    | CLK2 to MA0-MA9 Delay                    | 5    | 15   | ns    |

### **ACTIMING DIAGRAMS SL9151**