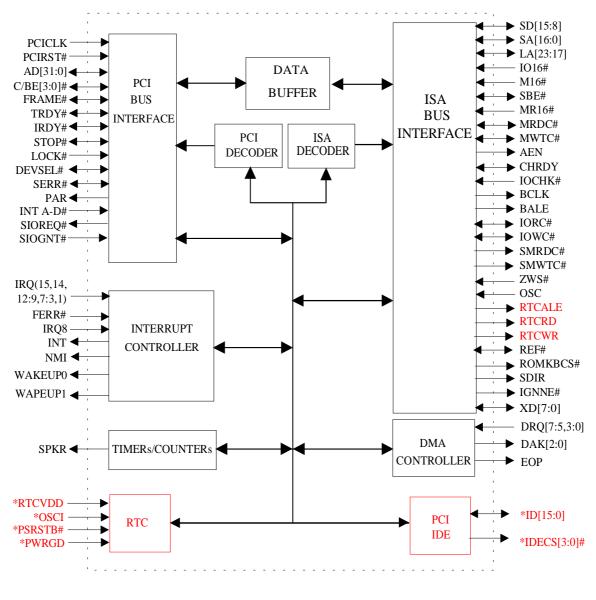

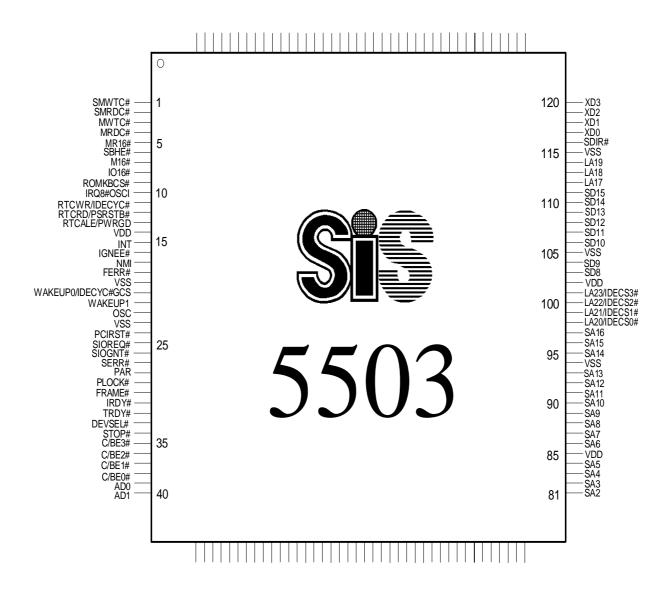

# 1 5501/5502/5503 Overview

| SiS5501 | PCI/ISA Cache Memory Controller ( <b>PCMC</b> ) |

|---------|-------------------------------------------------|

| SiS5502 | PCI Local Data Buffer (PLDB)                    |

| SiS5503 | PCI System I/O ( <b>PSIO</b> )                  |

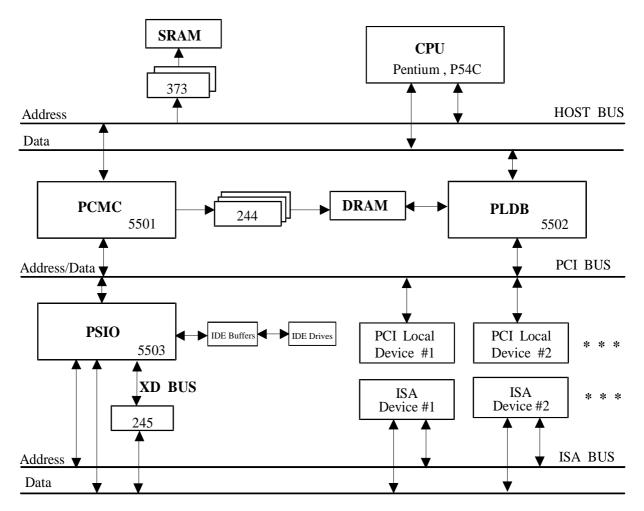

A whole set of the SiS5501, 5502, and 5503 provides fully integrated support for the Pentium/P54C PCI/ISA system. The chipset is developed by using a very high level of function integration and system partitioning. With the SiS5501, SiS5502, and SiS5503 chipset, only 12 TTLs (include 3 DRAM address buffer) are required to implement a low cost, high performance, Pentium/P54C PCI/ISA system. Figure 1 shows the system block diagram.

Figure 1.1 System Block Diagram

# 2. SiS5501

# 2.1 Features

- Supports the 510\60, 567\66, 735\90, 815\100 MHz and 75 MHz Pentium Processor

- Supports M1 and Other Pentium Compatible CPU

- Supports the Pipelined Address Mode of the Pentium or the P54C Processor

- Integrated Second Level (L2) Cache Controller

- Write Through and Write Back Cache Modes

- 8 bits or 7 bits Tag with Direct Mapped Organization

- Supports Standard and Burst SRAMs

- Supports 64 KBytes to 2 MBytes Cache Sizes

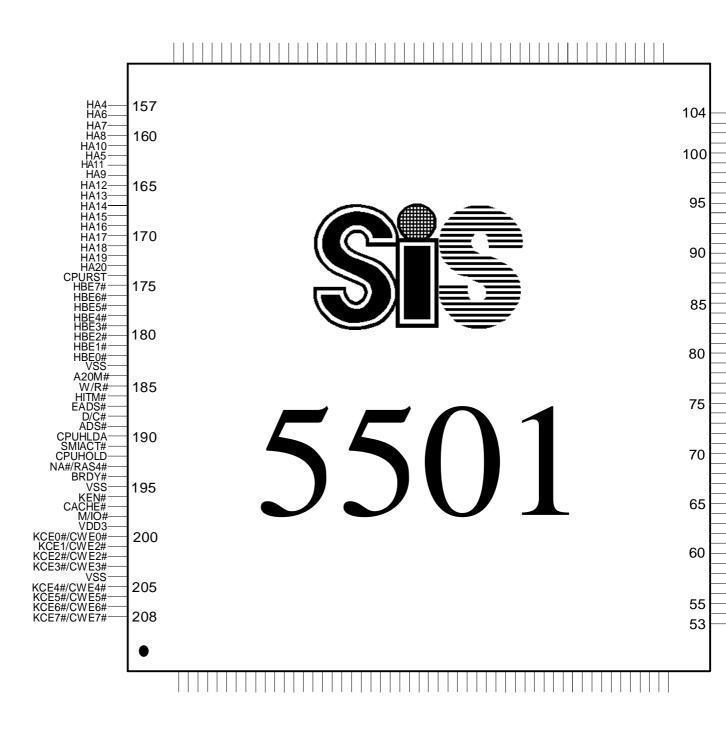

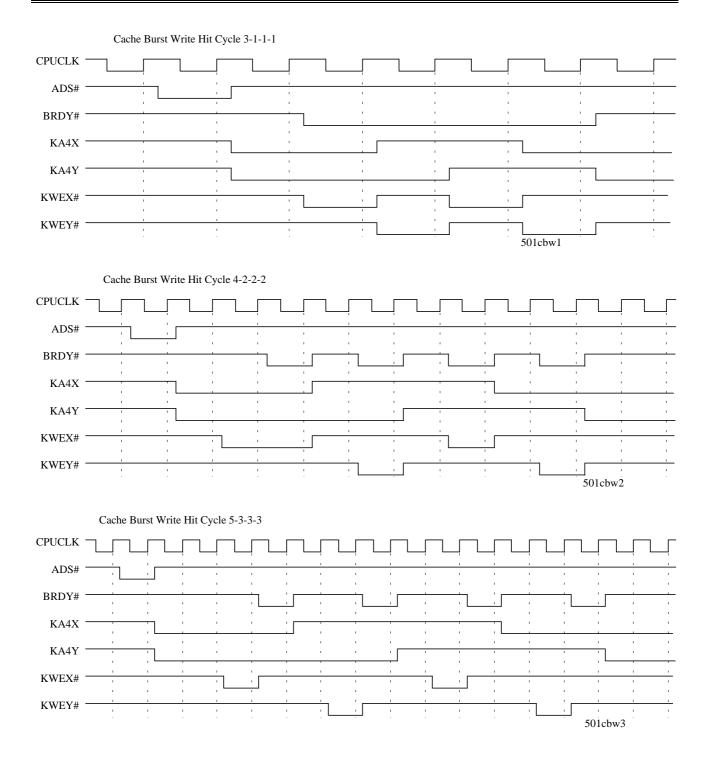

- Cache Read/Write Cycle of 3-2-2-2 or 4-2-2-2 Using Standard SRAMs at 66 MHz

- Cache Read/Write Cycle of 3-1-1-1 Using Burst SRAMs at 66 MHz

- Integrated DRAM Controller

- Supports 8 Banks of SIMMs up to 512 MBytes of Cacheable Main Memory

- Supports " Table- Free " DRAM Configuration

- Concurrent Write Back

- CAS#-before-RAS# Transparent DRAM Refresh

- Supports 256K/512K/1M/2M/4M/16M xN 70ns Fast Page Mode and EDO DRAM

- The Fastest Burst Cycle Speed for FP and EDO are 6-3-3-3 and 6-2-2-2 respectively

- Programmable CAS# driving Current

- Programmable DRAM Speed

- Two Programmable Non-Cacheable Regions

- Option to Disable Local Memory in Non-Cacheable Regions

- Shadow RAM in Increments of 16 KBytes

- Supports Pentium/P54C SMM Mode

- Supports CPU Stop Clock

- Provides High Performance PCI Arbiter

- Supports Four PCI Masters

- Supports Rotating Priority Mechanism

- Hidden Arbitration Scheme Minimizes Arbitration Overhead

- Integrated PCI Bridge

- Translates the CPU Cycles into the PCI Bus Cycles

- Provides CPU-to-PCI Read Assembly and Write Disassembly Mechanism

- Translates Sequential CPU-to-PCI Memory Write Cycles into PCI Burst Cycles

- PCI Burst Write in the Pace of X-2-2-2-....

- PCI Burst Read L2 Cache in X-2-2-2-....

- PCI Burst Read DRAM in X-3-2-3-2-....

- Cache Snoop Filters Ensure Data Coherency and Minimize Snoop Frequency

- Meet PCI Specification Buffer Strength

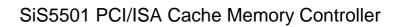

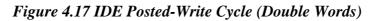

- 208-Pin PQFP Package

- 0.6µm CMOS Technology

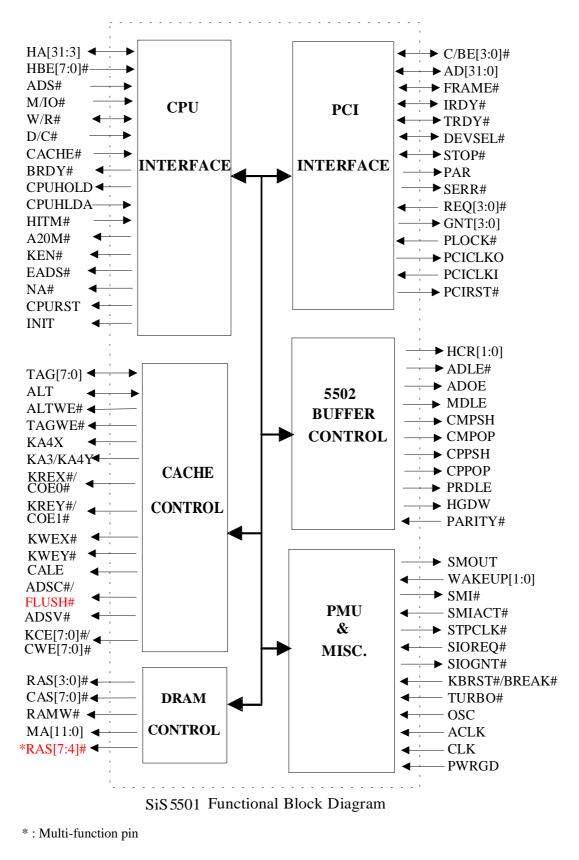

# 2.2 Functional Block Diagram

3

Preliminary V2.0 April 2, 1995

Silicon Integrated Systems Corporation

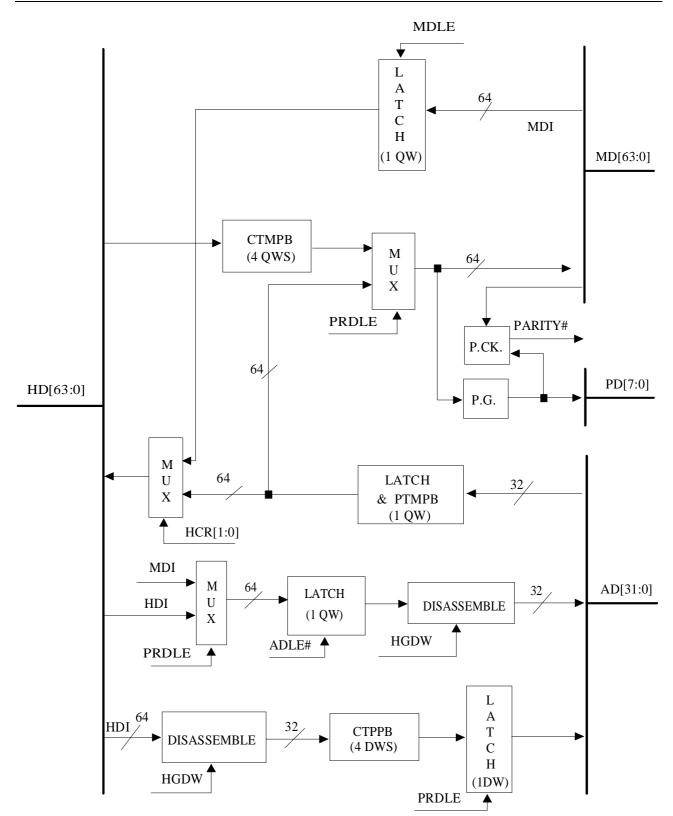

# 2.3 General Description

The SiS5501(PCMC) bridges between the host bus and the PCI local bus. The SiS5501 (PCMC) monitors each cycle initiated by the CPU, and forwards it to the PCI bus if the CPU cycle does not target the local memory. For the CPU or the PCI bus to the local memory cycles, the built-in Cache and DRAM Controller assume control to the secondary cache, DRAMs, and the SiS5502 (PLDB). The SiS5501 (PCMC) also guides the SiS5502 (PLDB) for correct data flow. All of the Green PC functions are provided.

## 2.4 CPU Interface

The SiS5501 is designed to support Pentium/P54C CPU host interface at 66.667/60/50 MHz. The host data bus and the DRAM bus are 64-bit wide.

The SiS5501 supports the pipelined addressing mode of the Pentium/P54C CPU by issuing the next address signal, NA#. NA# is only generated in two cases: a) burst read L2 cache or DRAM, and b) single read DPAM

b) single read DRAM.

The PCMC supports the CPU L1 write back(WB) or write through(WT) cache and the PCMC L2 WB or WT cache. The L1 cache is snooped by the assertion of EADS# when the CPU is put in the HOLD state.

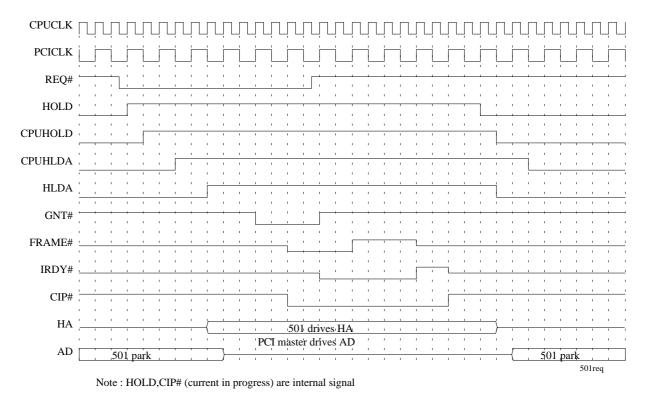

The PCMC issues CPUHOLD to the Pentium/P54C CPU in response to the assertion of PCI master requests(REQ[3:0]#, and SIOREQ#). Upon receiving the CPUHLDA from the CPU, it does not immediately assert GNT[3:0]# or SIOGNT# until both the CPU to PCI posted write buffer and the Memory write buffer are empty. During inquire cycles, the CPUHOLD may be negated temporarily to allow the CPU to write back the inquired hit modified line to L2 or DRAM.

## 2.5 Cache Controller

The built-in L2 Cache Controller uses a direct-mapped, bank-interleaved/non-interleaved scheme, which can be configured as either in the write through or write back mode. Both standard and burst SRAMs are supported.

Table 1 shows the cache sizes that are supported by the SiS5501, with the corresponding TAG RAM sizes, data RAM sizes, and cacheable memory sizes. Tables 2 and 3 summarize the performance and options when either the standard SRAMs or the Burst SRAMs are used.

| Table I    |           |         |           |                |             |

|------------|-----------|---------|-----------|----------------|-------------|

| Cache Size | Data RAM  | Tag RAM | Alter RAM | Cacheable Size | Interleaved |

| 64K        | 8Kx8x8    | 2Kx8    | 2Kx1      | 16M            | No          |

| 128K       | 8Kx8x16   | 4Kx8    | 4Kx1      | 32M            | Yes         |

| 256K       | 32Kx8x8   | 8Kx8    | 8Kx1      | 64M            | No          |

| 512K       | 32Kx8x16  | 16Kx8   | 16Kx1     | 128M           | Yes         |

| 512K       | 64Kx8x8   | 16Kx8   | 16Kx1     | 128M           | No          |

| 1M         | 128Kx8x8  | 32Kx8   | 32Kx1     | 256M           | No          |

| 1M         | 64Kx8x16  | 32Kx8   | 32Kx1     | 256M           | Yes         |

| 2M         | 128Kx8x16 | 64Kx8   | 64Kx1     | 512M           | Yes         |

Table 1

The PCMC also provides an alternative to save the dirty SRAM chip. This is accomplished by sharing the alter bit with tag address bits in the same 8-bit wide TAG RAM. System uses this implementation supports 7 tag address bits and 1 dirty bit. By doing so, the cacheable local memory sizes are reduced to half of the original sizes as indicated in Table 1.

In reality, the L2 Cacheable DRAM Size is determined by:

1) Max. L2 Cacheable Size as described in table 1.

2) Non-cacheable Area defined in register 57h, 58h, 59h and 5Ah and

3) C, D, E, F Segment Cachability defined in register 53h, 54h, 55h, and 56h.

But, the L1 Cacheable size is only determined by 2), 3), and the maximum DRAM size, i.e., 512M bytes. Thus, the cycles with address ranging over the L2 Cacheable Size but within the 512M bytes can also be cacheable to L1. The behavior of KEN# is ruled by the L1 Cacheability. Note that only code of C, D, E, F segment is cacheable to L1/L2, and the data portion of C, D, E, F segment is not cacheable to L1/L2.

| Cycle type   | 66,60 MHz          | 50MHz              |

|--------------|--------------------|--------------------|

| Burst read   | 3/ <u>4</u> -1-1-1 | 3/ <u>4</u> -1-1-1 |

|              | 3/4-2-2-2          | 3/4-2-2-2          |

| Burst write  | 3/ <u>4</u> -1-1-1 | 3/ <u>4</u> -1-1-1 |

|              | 3/4-2-2-2          | 3/4-2-2-2          |

| Single read  | 3/4                | 3/ <u>4</u>        |

| Single write | 3/4                | 3/ <u>4</u>        |

| Table 2 Burst SRAM Speed Setting | 5 |

|----------------------------------|---|

|----------------------------------|---|

*Note* :

1: The burst SRAM speed for 66/60 MHz is 9 ns. For 50MHz, it is 12 ns.

5

2:  $\underline{\mathbf{X}}$ -Y-Y-Y is the recommended setting.

|                        | 66 MHz |      | 60 MHz |      | 50MHz |      |

|------------------------|--------|------|--------|------|-------|------|

| cache configuration    | Tag    | Data | Tag    | Data | Tag   | Data |

| 3-1-1-1 interleave     |        |      |        |      | 15ns  | 15ns |

| 3-1-1-1 non-interleave |        |      |        |      |       |      |

| 3-2-2-2 interleave     | 15ns   | 15ns | 15ns   | 15ns | 20ns  | 20ns |

| 3-2-2-2 non-interleave | 15ns   | 15ns | 15ns   | 15ns | 20ns  | 20ns |

| 3-3-3-3 interleave     | 15ns   | 15ns | 15ns   | 15ns | 20ns  | 20ns |

| 3-3-3-3 non-interleave | 15ns   | 15ns | 15ns   | 15ns | 20ns  | 20ns |

| 4-1-1-1 interleave     | 15ns   | 12ns | 15ns   | 12ns | 20ns  | 15ns |

| 4-1-1-1 non-interleave |        |      |        |      |       |      |

| 4-2-2-2 interleave     | 15ns   | 15ns | 20ns   | 20ns | 20ns  | 20ns |

| 4-2-2-2 non-interleave | 15ns   | 15ns | 20ns   | 20ns | 20ns  | 20ns |

| 4-3-3-3 interleave     | 15ns   | 20ns | 20ns   | 20ns | 20ns  | 20ns |

| 4-3-3-3 non-interleave | 15ns   | 20ns | 20ns   | 20ns | 20ns  | 20ns |

| 5-1-1-1 interleave     | 20ns   | 12ns | 20ns   | 12ns | 20ns  | 15ns |

| 5-1-1-1 non-interleave |        |      |        |      |       |      |

| 5-2-2-2 interleave     | 20ns   | 15ns | 20ns   | 20ns | 20ns  | 20ns |

| 5-2-2-2 non-interleave | 20ns   | 15ns | 20ns   | 20ns | 20ns  | 20ns |

| 5-3-3-3 interleave     | 20ns   | 20ns | 20ns   | 20ns | 20ns  | 20ns |

| 5-3-3-3 non-interleave | 20ns   | 20ns | 20ns   | 20ns | 20ns  | 20ns |

**Table 3** Asynchronous SRAM speed setting (apply to read and write cycle)

# 2.6 DRAM Controller

The 5501 can support 8 rows of DRAM, and memory size from 2 MBytes up to 512 MBytes. Each populated bank could be single or double sided 64 bits FP DRAM or EDO (Extended Data Output) DRAM. It is also permissible to mix FP DRAM bank and EDO DRAM bank without any order. The installed DRAM type can be 256K x 36, 512K x 36, 1M x 36, 2M x 36, 4M x 36 or 16M x 36 SIMMs. However, since RAS 5 shares the same signal of MA 11, Bank 5 should be excluded if 16 M x 36 DRAM is used.

DBR 8~0 (DRAM Boundary Register, register 79h and 77h~70h) are used to configure the total amount of memory. In DBR 7~0, bit 7~0 corresponds to host address 28~21 and DBR 8 bit 7~0 is used to compare against the host address 29 of bank 7~0. Contents in these registers reflect the boundary address, that means the value programmed to the last DBR will be the DRAM size in the system.

| Preliminary V2.0                            | April 2, 1995          | 6 | Silicon Integrated Systems Corporation   |

|---------------------------------------------|------------------------|---|------------------------------------------|

| <b>1</b> i Citilitititititi y <b>i 2</b> .0 | 11pitt <b>2</b> , 1775 | 0 | Silleon fillegraiea Systemis corporation |

The following 2 examples show how the DBR registers be used to determine the memory size.

#### Example 1:

The system memory is populated as 2 banks of single-sided 1M x 36 DRAM, which are located at Bank 1 and 3. This yields 16 M Bytes DRAM totally. The DBR registers are programmed as follows:

| DBR1 = 04h $DBR2 = 04h$ | DBR 8 bit 0 = 0<br>DBR 8 bit 1 = 0<br>DBR 8 bit 2 = 0 | ; empty<br>; 8 M Bytes for Bank 1<br>; empty | ; 8 M ] | Byt | es to  | tally | totally<br>Bytes |

|-------------------------|-------------------------------------------------------|----------------------------------------------|---------|-----|--------|-------|------------------|

| totally                 |                                                       |                                              | 163     |     |        | . 11  |                  |

| DBR3 = 08h              | DBR 8 bit $3 = 0$                                     | ; 8 M Bytes for Bank 3                       | ; 16 M  | B   | ytes t | otall | У                |

| DBR4 = 08h              | DBR 8 bit $4 = 0$                                     | ; empty                                      |         | ;   | 16     | Μ     | Bytes            |

| totally                 |                                                       |                                              |         |     |        |       |                  |

| DBR5 = 08h              | DBR 8 bit $5 = 0$                                     | ; empty                                      |         | ;   | 16     | Μ     | Bytes            |

| totally                 |                                                       |                                              |         |     |        |       |                  |

| DBR6 = 08h              | DBR 8 bit 6 = 0                                       | ; empty                                      |         | ;   | 16     | Μ     | Bytes            |

| totally                 |                                                       |                                              |         |     |        |       |                  |

| DBR7 = 08h              | DBR 8 bit 7 = 0                                       | ; empty                                      |         | ;   | 16     | Μ     | Bytes            |

| totally                 |                                                       |                                              |         |     |        |       |                  |

#### Example 2:

The system memory is populated as 4 banks of single-sided 16 M x 36 DRAM, which are located from Bank 0 to 3. This yields 512 M Byte DRAM totally. The DBR registers are programmed as follows:

|            | DBR 8 bit $0 = 0$ | ; 128 M Bytes for Bank 0 | ; 128 M Bytes totally |

|------------|-------------------|--------------------------|-----------------------|

| DBR1 = 80h | DBR 8 bit 1 = 0   | ; 128 M Bytes for Bank 1 | ; 256 M Bytes totally |

| DBR2 = C0h | DBR 8 bit $2 = 0$ | ; 128 M Bytes for Bank 2 | ; 384 M Bytes totally |

| DBR3 = 00h | DBR 8 bit 3 = 1   | ; 128 M Bytes for Bank 3 | ; 512 M Bytes totally |

| DBR4 = 00h | DBR 8 bit 4 = 1   | ; empty                  | ; 512 M Bytes         |

| totally    |                   |                          |                       |

| DBR5 = 00h | DBR 8 bit 5 = 1   | ; empty                  | ; 512 M Bytes         |

| totally    |                   |                          |                       |

| DBR6 = 00h | DBR 8 bit 6 = 1   | ; empty                  | ; 512 M Bytes         |

| totally    |                   |                          |                       |

| DBR7 = 00h | DBR 8 bit 7 = 1   | ; empty                  | ; 512 M Bytes         |

| totally    |                   |                          |                       |

The 12-bit multiplexed row/column address MA[11:0] allows the PCMC to support 256K, 1M, 4M, and 16M 70ns fast page mode DRAMs.

Table 4. shows the corresponding request address bits used in column address and row address for the DRAM.

7

Preliminary V2.0 April 2, 1995

| able 4. Why Generation Table |     |     |     |     |     |     |     |     |     |     |     |     |

|------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Body                         | 25  | бk  | 51  | 2k  | 11  | М   | 21  | М   | 4]  | М   | 16  | Μ   |

| Туре                         |     |     |     |     |     |     |     |     |     |     |     |     |

| MA                           | CAS | RAS |

| MA0                          | A3  | A12 | A3  | A12 | A3  | A22 | A3  | A22 | A3  | A22 | A3  | A22 |

| MA1                          | A4  | A13 | A4  | A13 | A4  | A13 | A4  | A13 | A4  | A24 | A4  | A24 |

| MA2                          | A5  | A14 | A5  | A26 |

| MA3                          | A6  | A15 |

| MA4                          | A7  | A16 |

| MA5                          | A8  | A17 |

| MA6                          | A9  | A18 |

| MA7                          | A10 | A19 |

| MA8                          | A11 | A20 |

| MA9                          | NA  | NA  | NA  | A21 | A12 | A21 | A12 | A21 | A12 | A21 | A12 | A21 |

| MA1                          | NA  | A23 | A13 | A23 | A13 | A23 |

| 0                            | NA  | A14 | A25 |

| MA1                          |     |     |     |     |     |     |     |     |     |     |     |     |

| 1                            |     |     |     |     |     |     |     |     |     |     |     |     |

**Table 4.** MA Generation Table

To improve the CPU write DRAMs performance, there is a one level built-in CPU-to-Memory posted write buffer with 4 QWs deep (CTMPB). All the single writes and the burst writes are buffered. In the CPU read miss/line fill cycle, the write-back data from the L2 cache are also buffered into the CTMPB. At the same time, the PCMC starts reading from the DRAMs. The buffered data are written to the DRAMs when the read cycle completes. With this concurrent write back policy, many wait states are eliminated. However, any other cycle targeting the DRAMs will be suspended until the CTMPB is empty.

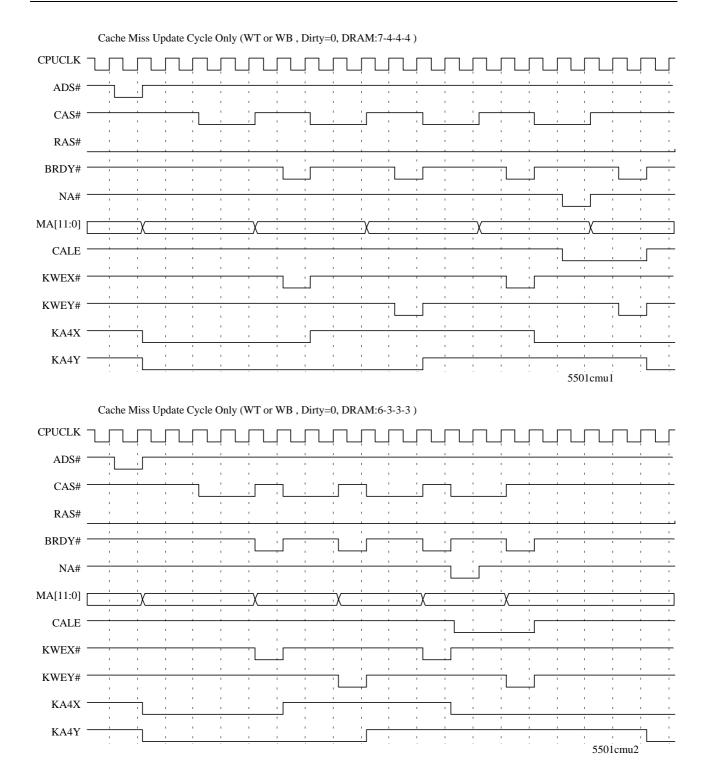

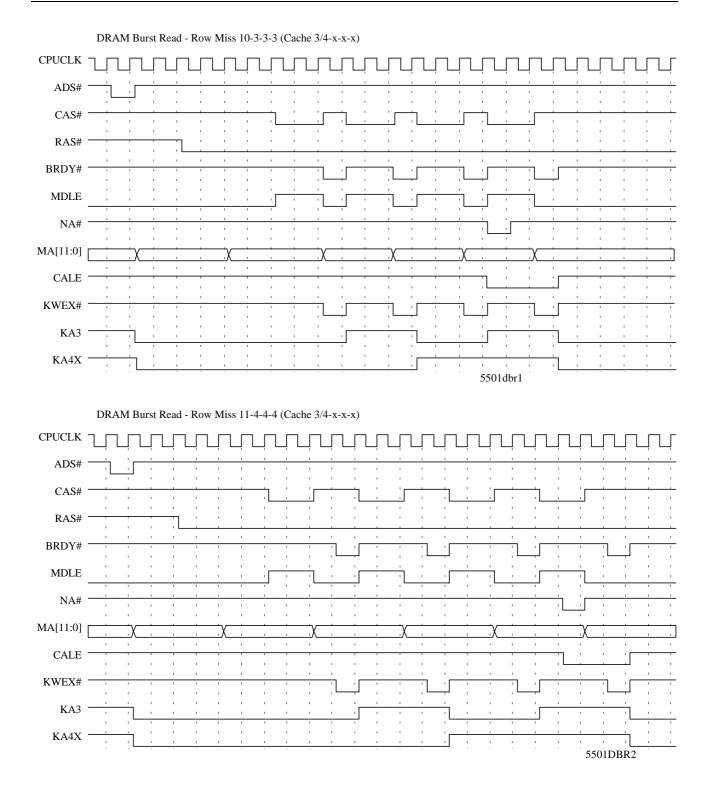

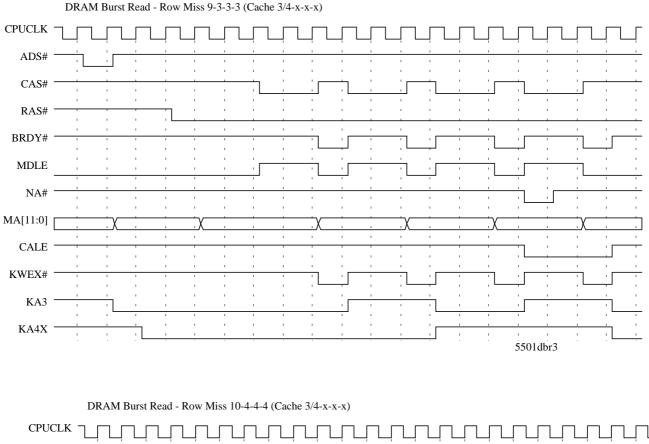

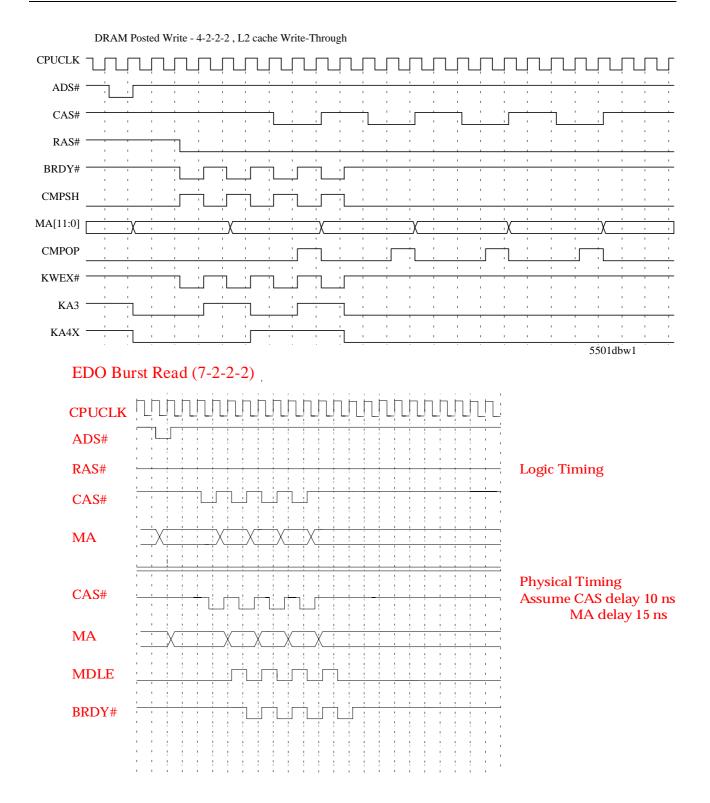

Table 5 outlines the read and write DRAM cycle performance based on 70ns DRAMs.

8

| Cycle type         | 66,60 MHz           | 50MHz          | DRAM Type               |  |  |  |  |  |

|--------------------|---------------------|----------------|-------------------------|--|--|--|--|--|

| read               | <u>6/9/12-3-3-3</u> | 6/9/12-3-3-3   | standard page mode      |  |  |  |  |  |

| (page hit/row miss | 7/10/13-4-4-4       | 7/10/13-4-4-4  | standard page mode      |  |  |  |  |  |

| /page miss)        | 6/9/12-2-2-2        | 6/9/12-2-2-2   | EDO                     |  |  |  |  |  |

|                    | 7/10/13-2-2-2       | 7/10/13-2-2-2  | EDO                     |  |  |  |  |  |

| posted write       | <u>3/4/5-1-1-1</u>  | 3/4/5-1-1-1    | standard page mode, EDO |  |  |  |  |  |

| (CPU> Buffer)      | 3/4/5-2-2-2         | 3/4/5-2-2-2    | standard page mode, EDO |  |  |  |  |  |

|                    | 3/4/5-3-3-3         | 3/4/5-3-3-3    | standard page mode, EDO |  |  |  |  |  |

| write retire rate  | <u>3</u> /4/5       | <u>3</u> /4/5  | standard page mode      |  |  |  |  |  |

| (Buffer> DRAM)     | $\overline{2}$      | $\overline{2}$ | EDO                     |  |  |  |  |  |

Table 5

DRAM Performance

Note:

1:  $\underline{X-Y-Y-Y}$  is the recommended setting.

|                                       | Register    | 66MHz | 60MHz | 50MHz |

|---------------------------------------|-------------|-------|-------|-------|

| read CAS pulse width                  | 50h bit 7-6 | 2T    | 2T    | 2T    |

| write CAS pulse width                 | 50h bit 5   | 2T    | 2T    | 2T    |

| CAS precharge time <sup>1</sup>       | 53h bit 7   | 1T/2T | 1T/2T | 1T    |

| RAS precharge time                    | 53h bit 1   | 4T    | 4T    | 4T    |

| RAS to CAS delay time                 | 53h bit 2   | 3T    | 3T    | 3T    |

| refresh RAS active time               | 52h bit 0   | 5T    | 5T    | 4T    |

| DRAM write push to CAS delay          | 5Bh bit 3   | 1T    | 1T    | 1T    |

| EDO DRAM CAS pulse width <sup>2</sup> | 7Ch bit 1   | 1T/2T | 1T/2T | 1T    |

| EDO DRAM CAS precharge time           | 7Ch bit 0   | 1T/2T | 1T/2T | 1T    |

Note:

- 1. The burst DRAM read hit cycle is 6-3-3-3 when the CAS precharge time is 1T. If the CAS precharge time is 2T, the burst DRAM read hit cycle is increased to 7-4-4-4.

- 2. When EDO type DRAMs are installed and register 7Ch bits[1:0] are set to "11" (1T), the burst DRAM read hit cycle is 6-2-2-2. The standard Fast Page mode DRAM timing is applied, if register 7Ch bits[1:0] are set to "00". In fact, 5501 can detect the EDO type DRAM and applies optimal timing automatically.

# 2.7 PCI Arbiter

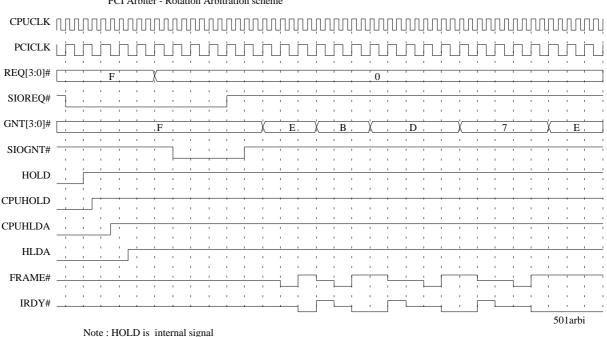

The SiS5501 contains a high performance hidden arbitration scheme that allows efficient bus sharing among five PCI Masters and the CPU. Note that one PCI master is reserved for the PSIO chip.

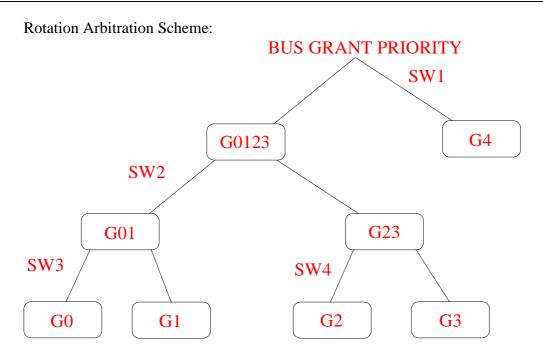

The SiS5501 employs the priority rotation scheme that is done at two different layers. The first layer is shared between PSIO and four PCI Masters as a group. The second layer consists of four PCI masters with equal priority. Arbitration is done at both layers. The winner of arbitration among the four PCI masters arbitrates the PCI bus against PSIO. Fair rotation scheme applies only at layer level. The arbitration scheme assures that ISA master or DMA channels (represented by PSIO) access the bus with minimal latency. The PSIO is given a high level of priority to assure compatibility with traditional ISA expansion boards that require short bus latency. This implementation together with PCI Programmable Bursting Address Counter guarantees ISA device will not be starved during PCI master long bursting cycle. For example, When the maximum bursting length is 512 bytes, the maximum arbitration latency for PSIO, and PCI master is about 12us, and 40us respectively. The following two figures detail the rotation arbitration structure and its corresponding timing diagram.

#### Notation:

SW1: is the switch for path from node G4 or G0123 to BUS GRANT PRIORITY

SW2: is the switch for path from node G01 or G23 to node G0123

SW3: is the switch for path from node G0 or G1 to node G01

SW4: is the switch for path from node G2 or G3 to node G23

G01, G23, G0123: are intermediate nodes

G4: is the bus request from PSIO

G0, G1, G2, G3: are the bus requests from PCI device 0, device 1, device 2, device 3 respectively.

Initial Path Parking: SW1 : BUS GRANT PRIORITY-G4 SW2 : G0123-G01 SW3 : G01-G0 SW4 : G23-G2

Rule of Rotating Priority for Bus Arbitration:

• BUS GRANT PRIORITY will choose a path whenever it encounters an optional path.

10

- PCI bus will be granted as Daisy Chain

- Path switches will be toggled from BUS GRANT PRIORITY to any request node (G4, G0, G1, G2, G3) if any of them have been utilized

Example: Initial Priority: G4, G01, G0, G2

PSIO(G4) Request Bus SIOGNT# is asserted

SW1 is toggled to G0123 (since it has been utilized) Priority change to G0, G1, G2, G3, G4

Preliminary V2.0 April 2, 1995

Silicon Integrated Systems Corporation

- 2. PSIO, REQ3, REQ2, REQ1, REQ0 are requesting bus GNT0# is asserted

SW1, SW2 and SW3 are toggled to G4, G23 and G1 respectively (since they have been utilized)

Priority change to G4, G2, G3, G1, G0

- REQ3, REQ2, REQ1, REQ0 are active GNT2# is asserted SW2, SW4 are toggled to G01 and G3 respectively (since they have been utilized) Priority change to G4, G1, G0, G3, G2

- 4. REQ3, REQ2, REQ1, REQ0 are active GNT1# is asserted

SW2, SW3 are toggled to G23 and G0 respectively (since they have been utilized)

Priority change to G4, G3, G2, G0, G1

- 5. REQ3, REQ2, REQ1, REQ0 are active GNT3# is asserted

SW2, SW4 are toggled to G01 and G2 respectively (since they have been utilized)

Priority change to G4, G0, G1, G2, G3

- 6. During 3-5 if there is a request comes from PSIO, the Arbiter will grant bus to PSIO.

A PCI master can burst so long as the target can source/sink the data, and no other agent requests the bus. However, PCI specifies two mechanisms that cap a master's tenure in the presence of other requests, so that predictable bus acquisition latency can be achieved. One is the Master Latency Timer(LT) that is not implemented into the PCMC, the other is the Target

11

Preliminary V2.0 April 2, 1995

Silicon Integrated Systems Corporation

PCI Arbiter - Rotation Arbitration scheme

Initiated Termination. In the SiS5501, a Programmable Bursting Address Counter(PBAC) is implemented to disconnect the PCI master during the long bursting cycle. In this way, high throughput is maintained, and the bus latency is still kept reasonably small. Note that the bursting length is naturally applied to PCI master to local memory accessing. When PCI master accesses non-local memory target, the master and target should together have the responsibility of maintaining reasonable latency, but not the system arbiter does.

The PCI arbiter asserts only one GNT# at any time. The 5501 has also implemented a time-out counter to prevent faulty device hugging the bus. If the PCI bus is granted to a PCI device and the bus is currently idle, 16 PCI clocks is the limitation that device should assert FRAME# during the period of time. If time-out occurs, the arbiter will mask request line, therefore desserts GNT#. When this happens, all PCI devices start arbitration again. Note that PSIO is free to this constraint.

The 5501 PCI master will also mask the PSIO request to the arbiter if the PCI LOCK# is asserted to keep ISA master or DMA channels target latency within specification. The 5501 PCI arbiter is also allowed to force system back to CPU each time after SIOREQ# is serviced. This function is disabled by default, and can be enabled by set bit 7 of register 6F in the PCMC Configuration space.

# 2.8 PCI Bridge

#### 2.8.1 PCI Master Controller

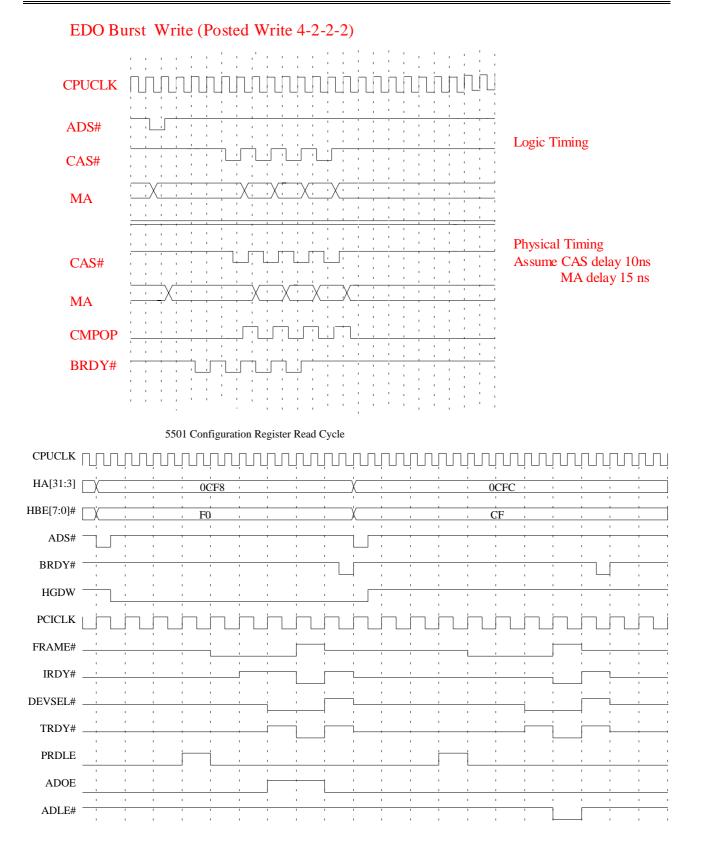

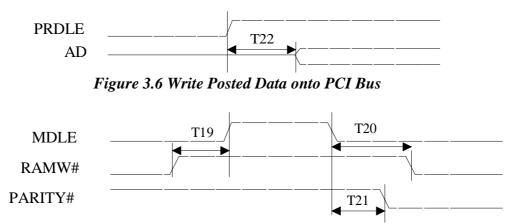

The PCI Master Controller forwards the CPU cycles not targeting the local memory to the PCI bus. In the case of a 64-bit CPU request or a misaligned 32-bit CPU request, the PCMC assumes the read assembly and write disassembly control. A 4 level posted write buffer (CTPPB) is implemented to improve the CPU to PCI memory write performance. Except for on-board memory write cycles, any cycles forwarded to the PCI bus will be suspended until the CTPPB is empty. For PCI bus memory write cycles, the CPU data are pushed into the CTPPB if it is not full. The pushed data are, at later time, written to the PCI bus. If the consecutive written data are in DW incremental sequence, they will be transferred to the PCI bus in a burst manner. The burst transfer rate is always X-2-2-2-... until 128 DWs are exhausted.

The PCI master interface can read data from or write data to the PCI bus at the utmost speed of 1 wait state. This is due to the fact that the PCMC drives the PCI bus address and the PLDB drives the PCI bus data. That necessitates a turn around cycle between the address and the data phases.

The PCMC provides a mechanism for converting standard I/O cycles on the CPU bus to Configuration cycles on the PCI bus. Configuration Mechanism #1 in PCI Specification 2.0 page 61 is used to do the cycle conversion.

The PCMC always intercepts the first interrupt acknowledge cycle from CPU bus, and forwards the second interrupt acknowledge cycle onto the PCI bus.

|                  | A :1 0 1005   | 10 |                                        |

|------------------|---------------|----|----------------------------------------|

| Preliminary V2.0 | April 2, 1995 | 12 | Silicon Integrated Systems Corporation |

#### 2.8.2 PCI Slave Controller

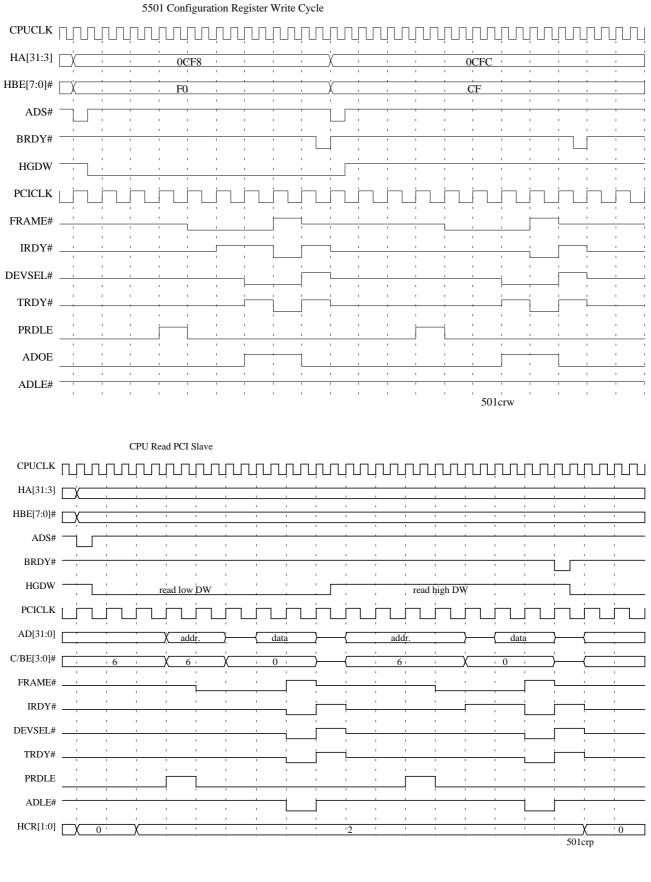

The SiS5501 operates as a slave on the PCI bus whenever a PCI master requests an access to the SiS5501 resource such as Cache, DRAM and the SiS5501 Internal registers. Note that the internal registers can only be accessed by the SiS5501 itself when in CPU cycle. In the SiS550x PCI/ISA system, the CPU is placed in HOLD state before granting the PCI bus to a PCI master. The following figure shows the behavior of CPUHOLD/CPUHLDA in response to PCI masters requests. Only linear ordered PCI cycles are supported by the PCMC PCI slave interface.

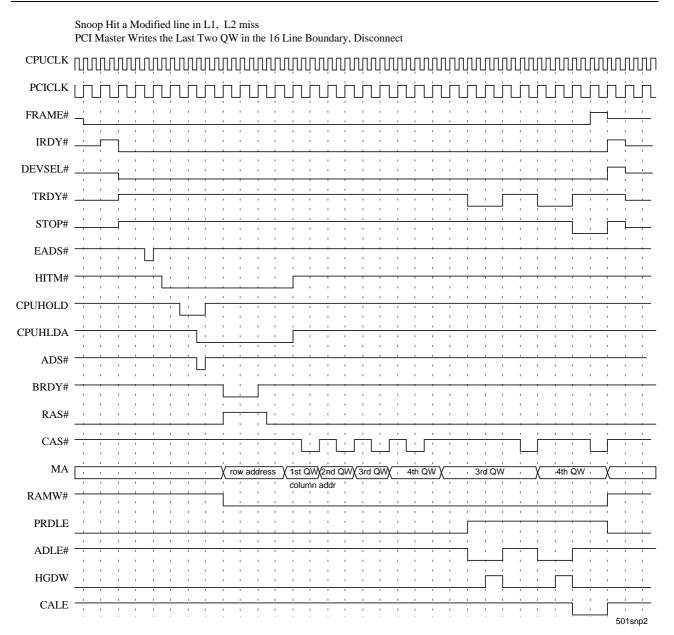

A PCI master to the local memory access is not conducted until the snoop cycle has completed. The snoop cycle is used to inquire the first level cache to maintain coherency between first level and second level caches and main memory. Snoop cycles are performed by driving the PCI master address onto the CPU bus and asserting EADS#. Depending on the status of HITM# two clocks after the assertion of EADS#, PCMC conducts the PCI master cycles as table 8 outlines.

| Table /                |                       |                                           |

|------------------------|-----------------------|-------------------------------------------|

| PCI Master Read Cycle  |                       |                                           |

| L1                     | L2                    | Data Transfer                             |

| Miss (or Unmodified)   | Miss                  | Data transfer from DRAM to PCI            |

| Miss (or Unmodified)   | Hit (Dirty or !Dirty) | Data transfer from L2 to PCI              |

| HitM                   | Miss                  | Data is first written back from L1 to     |

|                        |                       | DRAM. Then, PCI master gets data from     |

|                        |                       | DRAM.                                     |

| HitM                   | Hit (Dirty or !Dirty) | Data is first written back from L1 to L2. |

|                        |                       | Then, PCI master gets data from L2. The   |

|                        |                       | line is marked dirty in the L2.           |

| PCI Master write Cycle |                       |                                           |

| L1                     | L2                    | Data Transfer                             |

| Miss (or Unmodified)   | Miss                  | Data transfer from PCI to DRAM            |

| Miss (or Unmodified)   | Hit (Dirty or !Dirty) | Data transfer from PCI to DRAM and L2.    |

|                        |                       | The Dirty bit is not changed.             |

| HitM                   | Miss                  | Data is first written back from L1 to     |

|                        |                       | DRAM. Then, PCI master writes data to     |

|                        |                       | DRAM.                                     |

| HitM                   | Hit (Dirty or !Dirty) | Data is first written back from L1 to L2. |

|                        |                       | Then, PCI master writes data to L2 and    |

|                        |                       | DRAM. The Line is marked dirty in the L2. |

|                        |                       |                                           |

A snoop filter is implemented to prevent the need of multiple inquires to the same line if the line was inquired previously. To support snoop filter, a Snoop Address Latch (SAL) and a Line Comparator are implemented. The line comparator is used to determine if the New Address (NA) is the same as the content of the SAL. If it is not, the NA is loaded into the SAL, and a snoop cycle is issued. In addition, a Valid bit in association with the SAL is used to ensure the snoop filtering is effective only when HLDA is asserted. The simplified filter algorithm is:

- 1) Write Back Mode

- a) if NA=SAL in a PCI master write cycle, the PCMC only issues EADS#. It does not wait for the status of HITM#.

- b) if NA=SAL in a PCI master read cycle, no snoop cycle nor EADS# is issued.

- c) if NA≠SAL in a PCI master cycle, the PCMC issues a snoop cycle by EADS#, and then monitors the status of HITM#.

- d) During a burst transaction, the PCMC automatically generates a snoop cycle when the address advances across a new line.

2) Write Through Mode

In the following two cases, the PCMC only generates EADS#. It ignores the logic of HITM#. a) if NA=SAL in a PCI master write cycle, and

b) During a burst transaction, the address advances across a new line.

| Den alternation many V/2 () | Amuil 2 1005  | 14 | Cilian Internet of Contant Commention  |

|-----------------------------|---------------|----|----------------------------------------|

| Preliminary V2.0            | April 2, 1995 | 14 | Silicon Integrated Systems Corporation |

#### Table 7

In the SiS550x, the INV signal of P54C should be connected to W/R# that is driven by the SiS5501 in the PCI master cycle. In this way, the SiS5501 can invalidate the line that is currently inquired via the assertion of EADS# in the PCI master write cycles.

The PCMC slave interface supports PCI burst transfers. A burst transfer will be disconnected (retry) if the transfer goes across the 512 bytes(or 1 KBytes selected by Register 5Dh, bit 5) address boundary. This is due to the fact that the address generator, to support the burst transfer, can only address 512 or 1K bytes. In this way, at most 32 cache lines can be uninterruptedly transferred if they are in I, S, or E state in the L1 cache.

Another reason for the constraint is that page miss may occur only once during the entire bursting transaction since the maximum bursting length is always within the page size in any of the used DRAM.

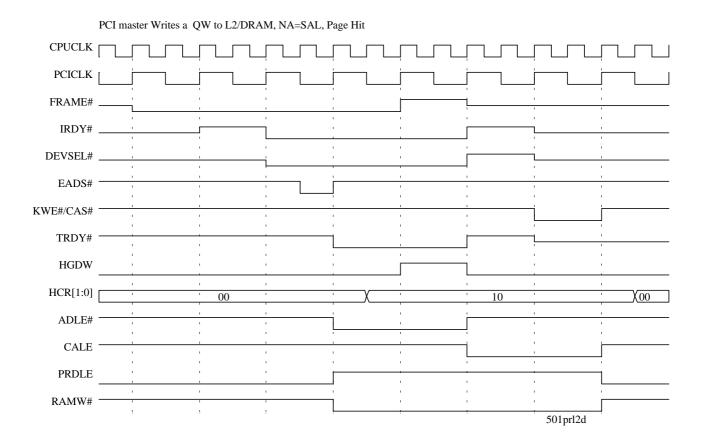

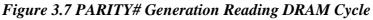

The PCI master writes are buffered in the one QW deep PCI to Memory posted write buffer (PTMPB). The PCMC always packs an aligned QW PCI write data into the write buffer, and then retires it into the DRAM array or the L2 cache. The PCI master write performance, to the utmost, is X-2-2-2- ...

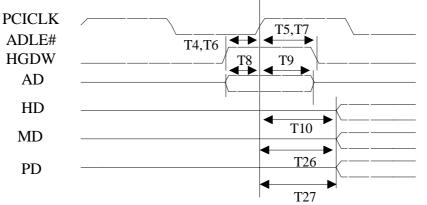

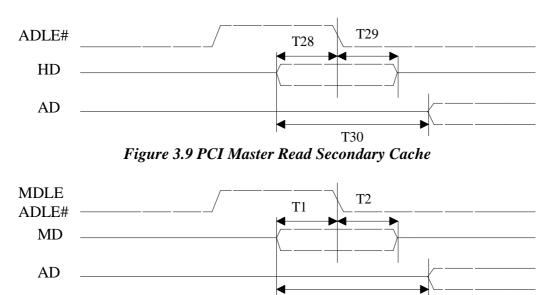

The PCI master reads are through a QW read buffer with which the burst transfers can perform in the pace of X-2-2-2-... (from the L2 cache), or X-3-2-3-2-... (from the DRAMs).

Concurrent refresh will still be performed when CPU is put into Hold state. If the DRAM is idle, refresh can be conducted at any time. If refresh request occurs at the same time that a PCI master wants to access DRAM, an arbitration scheme is employed to resolve the conflict. The refresh request may thus get service while the PCI master accessing is suspended until refresh cycle is completed. Although refresh may win the DRAM bus, at most one refresh cycle may be conducted for each individual PCI transaction, i.e. for each Frame# initiating. On the other hand, refresh may be also deferred until the DRAM is idle. In SiS550x system, the refresh may be postponed for no more than 24 us in the worst case when a PCI master is reading the whole 32 lines through one burst transaction.

#### 2.8.3 PCI Bus Speed Setting

The following settings apply to all system environment, even though the system is running at 66MHz while the PCI bus is running at 33MHz.

#### Table 8 PCI bus setting

|                                               | Register  | Setting | Unit   |

|-----------------------------------------------|-----------|---------|--------|

| latency from ADS# to monitor local memory     | 5Ch bit 7 | 2T      | CPUCLK |

| status                                        |           |         |        |

| CAS# pulse width in PCI master write cycle    | 5Ch bit 4 | 1T      | PCICLK |

| latency from the disarming of "full" to the   | 5Ch bit 3 | 1T      | CPUCLK |

| assertion of BRDY# for the pending CPU to     |           |         |        |

| PCI write cycle                               |           |         |        |

| latency from reading L2/DRAM to the assertion | 5Dh bit 4 | 1T      | PCICLK |

| of TRDY# in PCI master read cycles            |           |         |        |

| latency from packing one Qword into PTMPB     | 5Dh bit 3 | 1T      | PCICLK |

| to the assertion of CAS#(or KWE#)             |           |         |        |

| latency from TRDY# to BRDY# in CPU            | 5Dh bit 2 | 2T      | CPUCLK |

| read/write PCI slave cycles                   |           |         |        |

# 2.9 Green PC Function

The following paragraphs are the PMU ( Power Management Unit ) features description:

#### 2.9.1 Power States

The PMU provides different power management states, which are described in the following sections.

#### (i) Monitor Standby State

The Monitor will be blanked and the external devices are turned off through SMOUT when the Monitor standby timer expires.

Monitor Standby monitors the following events:

IRQ 1-15 HOLD NMI

Each IRQ has two sets of mask bits, one for wake up mask, and the other for standby mask. The HOLD includes the PCI local masters and the ISA master request. Each event is maskable. If no event happens during the monitored period and the timer expires, an SMI is generated and the monitor enters the standby state.

Once the Monitor is in the standby state, any event from IRQ1-15, NMI or HOLD will cause an SMI which brings the Monitor back to the normal state.

The time slot of the Monitor standby timer is programmable to 6.6sec, 0.84sec, 13.3ms, 1.6ms.

#### (ii) System Standby State

If the system standby timer expires, an SMI is generated for the system to enter the system standby state. The following events happen:

STPCLK# is asserted to stop the CPU clock The hard disk drives spindle motors can be turned off The serial, parallel ports or the programmable I/O port can be turned off

Once the STPCLK# is asserted, any events from IRQ1-15, NMI, HOLD, INIT will cause the STPCLK# be de-asserted. If any of the Hard disk motors, serial, parallel or programmable I/O ports were turned off, they will be back to the normal state only when they are accessed.

System Standby monitored events (each event is maskable) Programmable I/O ports (one is a 10-bit I/O port, another is a16-bit I/O port) IRQ 1-15 (each has 2 sets of mask bits as for Monitor Standby State) HOLD NMI Hard Disk ports (1F0-1F7h, 3F6-3F7h, 170-17Fh, 320-32Fh) Serial ports (2F8-2FFh, 3F8-3FFh, 2E8-2EFh, 3E8-3EFh) Parallel ports (278-27Fh, 378-37Fh, 3BC-3BEh) A0000-AFFFFh or B0000-BFFFFh Address trap (Video RAM) C0000-C7FFFh Address trap (Video BIOS) 3Bx-3Dxh (Video I/O port)

The time slot of the System standby timer is programmable to 9 sec, 1.1 sec, 70ms, and 8.85ms.

#### (iii) Throttling state

In throttling state, STPCLK# is asserted and de-asserted periodically. This function is maskable. The throttling timer (Registers 61h and 62h) is programmable and the time slot is 35us.

#### 2.9.2 Break Switch SMI

Whenever the break switch is pressed, it caused an SMI to enter or leave power saving state. The signal from the break switch is a level trigger signal which lasts for more than 3 CPU clocks.

#### 2.9.3 Software SMI

If the software SMI enable bit is set and a '1' is written to bit 1 of Register 60h, an SMI# is generated and the software SMI service routine is invoked. The bit 1 of Register 60h should be cleared at the end of the SMI handler.

#### 2.9.4 Shadow Register

In order to support "suspend to HDD" function, all necessary shadow registers are implemented into 5503. For more detailed information, please refer to "5503 Register Description"

| Preliminary V2.0 | Anril 2 1995         | 17 | Silicon Integrated Systems Corporation |

|------------------|----------------------|----|----------------------------------------|

| 1 Tenninary V2.0 | <i>April 2, 1775</i> | 17 | Suicon miegraiea Systems Corporation   |

# 2.10 Configuration Registers

There are two sets of registers in the PCMC, I/O mapped registers and the PCI configuration space registers.

### 2.10.1 I/O Mapped Registers

The SiS5501 uses PCI configuration space access mechanism #1. This mechanism defines two registers, CONFIG\_ADDRESS (CF8h) register and CONFIG\_DATA (CFCh) register. Both CONFIG\_ADDRESS and CONFIG\_DATA are read/write registers, and the length is DWORD. The mechanism is to write a value into CONFIG\_ADDRESS first, then read or write to CONFIG\_DATA. The write to CONFIG\_ADDRESS specifies the PCI bus, device on that bus, and the configuration register in that device being accessed. The read or write to CONFIG\_DATA will cause the host bridge to translate the CONFIG\_ADDRESS value to the requested configuration cycle.

The definition of CONFIG\_ADDRESS register is described below:

#### Register 0CF8h CONFIG\_ADDRESS Register

| 31 30      | 24  | 23 16               | 15         | 11           | 10          | 8       | 7                                    | 2 1  | 0 |      |

|------------|-----|---------------------|------------|--------------|-------------|---------|--------------------------------------|------|---|------|

| Reserve    | ed  | Bus Number          | Dev<br>Nur | vice<br>nber | Func<br>Num |         | Register Numbe                       | er 0 | 0 |      |

| ▲I         | Ena | ble bit $('1' = er$ | abled,     | '0' =        | disabled    | )       |                                      |      |   |      |

| Bit 31     |     |                     | 0          |              |             | ,       | e accesses to CO<br>cycles on the PC |      | _ | DATA |

| Bits 30:24 |     | Reserved, rea       | d only     | , and        | must r      | eturn   | 0's when read.                       |      |   |      |

| Bits 23:16 |     | Choose a spec       | cific P    | CI bu        | s in the    | syster  | n.                                   |      |   |      |

| Bits 15:11 |     | Choose a spec       | cific d    | evice        | on the l    | ous.    |                                      |      |   |      |

| Bits 10:8  |     | Choose a spec       | cific fu   | inctio       | n in a d    | levice. |                                      |      |   |      |

| Bits 7:2   |     | Choose a DW         | ORD        | in the       | e device    | 's conf | figuration space                     | •    |   |      |

| Bits 1:0   |     | read only and       | must       | retur        | 'n 0's w    | hen re  | ead.                                 |      |   |      |

|            |     |                     |            |              |             |         | host bridge wil<br>read to 0CF8h, th |      |   |      |

A full Dword I/O write to address 0CF8h, the host bridge will load the data into CONFIG\_ADDRESS register. Also, a full Dword I/O read to 0CF8h, the host bridge gets the data from CONFIG\_ADDRESS register. Any non-Dword writes or reads to 0CF8h are treated as normal PCI I/O cycles. When the host bridge of SiS5501 sees an I/O access that falls inside the Dword beginning at CONFIG\_DATA address, it checks the enable bit of the CONFIG\_ADDRESS register. If bit 31 of CONFIG\_ADDRESS register is 1, the I/O cycle is translated into a configuration cycle.

There are two types of configuration cycle determined by bus number. If the Bus Number is zero, the configuration cycle will be Type 0. If the Bus Number is non-zero, the configuration cycle will be Type 1.

For Type 0 configuration cycle, AD[1:0] is driven to "00" during the address phase of the cycle. The host bridge decodes the device number of CONFIG\_ADDRESS to assert only one "1" on the AD[31:11] and copies bits [10:2] of CONFIG\_ADDRESS to AD[10:2] directly. For instance, when accessing the configuration registers of SiS5501, because 5501 is considered device 0 on bus 0, AD11 will be high, and bits[10:2] of CONFIG\_ADDRESS are copied to AD[10:2] directly. Never use AD11 as the IDSEL line for any other PCI target device since it is reserved for PCMC. The 5501 responds to configuration by asserting DEVSEL#.

For type 1 configuration cycle, AD[1:0] is driven to "01" and bits[31:2] of CONFIG\_ADDRESS are copied to AD[31:2] directly during the address phase of the cycle.

The byte-enables for the data phase of both types 0 and type 1 configuration cycles are copied from the HBE[7:4]# directly.

The following programming sequences is an example of writing register 51h in PCMC and of reading register 5Ch, 5Dh, 5Eh and 5Fh in PCMC.

write 51h: MOV EAX, 80000050h OUT 0CF8h, EAX MOV AL, DATA OUT 0CFDh, AL read 5Ch, 5Dh, 5Eh and 5Fh: MOV EAX, 8000005Ch OUT 0CF8h, EAX

IN 0CFCh

Register 0CF9h Turbo and Reset Control Register.

#### Bits 7:5 Reserved

#### Bit 4 INIT Enable

When this bit is set to 1 ,the PCMC drives INIT during software reset. When this bit is cleared to 0, the PCMC drives CPURST during software reset, and INIT is inactive.

#### Bit 3 CPU BIST Enable.

When this bit is set to 1 and bit 4 as well as bit 1 are enabled, a subsequent initiation of the CPU hard reset through bit 2 of this register enables the Built

| Preliminary V2.0                               | April 2, 1995 | 19 | Silicon Integrated Systems Corporation |

|------------------------------------------------|---------------|----|----------------------------------------|

| <b>1</b> • • • • • • • • • • • • • • • • • • • |               |    |                                        |

In Self Test(BIST) mode of the CPU. The PCMC also drives the INIT during the hard reset.

#### Bit 2 Reset CPU.

There are two types of resets to the CPU: a hard reset using the CPURST signal and a soft reset using the INIT signal. If bit 1 of this register is set to 1 and bit 2 transitions from 0 to 1, the PCMC initiates a hard reset. A hard reset through this register thus requires two write operations to this register: the first write operation writes a 1 to bit 1 and a 0 to bit 2. The second write operation writes a 1 to bit 1 and a 1 to bit 2. When bit 1 of this register is 0 and bit 2 transitions from 0 to 1, the PCMC initiates a soft reset. The sequence to initiate a soft reset through this register is identical to that of a hard reset except a 0 is written to bit 1 in the first write operation.

#### Bit 1 Enable System Hard Reset.

When this bit is set to 1 and bit 2 transitions from 0 to 1, the PCMC initiates a hard reset to the CPU. When this bit is 0 and bit 2 transitions from 0 to 1, the PCMC initiates a soft reset to the CPU.

#### Bit 0 Select Turbo /DeTurbo Mode

There are two ways to enter Deturbo mode. One is through software; another is hardware.

- Software Deturbo: Set Reg. 5Bh bit 1 to 1, Reg. 65h bit 3 to 1, Reg. 78h bit 2 to 0 and pull GNT#3 high, then set Reg. CF9h bit 0 to 1.

- Hardware Deturbo: Set Reg. 5Bh bit 1 to 1, Reg. 65h bit 3 to 1, Reg. 78h bit 2 to 0 and pull GNT#3 high, then press deturbo switch.

#### 2.10.2 PCI Configuration Space Mapped Registers

| Register 00h    | Vendor ID - low byte  |

|-----------------|-----------------------|

| <b>Bits 7:0</b> | 39h                   |

| Register 01h    | Vendor ID - high byte |

| <b>Bits 7:0</b> | 10h                   |

| Register 02h    | Device ID - low byte  |

| <b>Bits 7:0</b> | 06h                   |

| Register 03h    | Device ID - high byte |

| <b>Bits 7:0</b> | 04h                   |

| Register 04h    | Command - low byte    |

| Bit 7           | Reserved              |

Preliminary V2.0 April 2, 1995

| Bit 6        | Respond to parity.                                                                                                              |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|

|              | This bit is always 0 since the PCMC does not support parity checking on the PCI bus                                             |

| Bits 5:4     | Reserved                                                                                                                        |

| Bit 3        | Enable special cycle.                                                                                                           |

|              | This bit is always 0 since the PCMC does not issue special cycle.                                                               |

| Bit 2        | Enable bus master.                                                                                                              |

|              | This bit is always 1, allowing the PCMC to serve as a PCI bus master.                                                           |

| Bit 1        | Enable response to memory access.                                                                                               |

|              | 0: Disables PCI master's accesses to local memory                                                                               |

|              | 1: Enables PCI master's accesses to local memory                                                                                |

| Bit 0        | Enable response to I/O access.                                                                                                  |

|              | This bit is always 0 since the PCMC does not respond to any PCI I/O cycles. The PCMC only responds to CPU initiated I/O cycles. |

| Register 05h | Command - high byte                                                                                                             |

| Bits 7:0     | Reserved                                                                                                                        |

| Register 06h | Status - low byte                                                                                                               |

| Bits 7:0     | Reserved                                                                                                                        |

| Register 07h | Status - high byte                                                                                                              |

| Bit 7        | Detected parity error.                                                                                                          |

|              | This bit is always 0 since the PCMC does not support parity checking on the PCI bus.                                            |

| Bit 6        | Signaled system error.                                                                                                          |

|              | This bit is set when the PCMC asserts SERR#. This bit is cleared by writing a 1 to it.                                          |

| Bit 5        | Received master abort.                                                                                                          |

|              | This bit is set by the PCMC whenever it terminates a transaction with master abort. This bit is cleared by writing a 1 to it.   |

| Bit 4        | Received target abort.                                                                                                          |

|              | This bit is set when a CPU to PCI transaction is terminated with target abort.<br>This bit is cleared by writing a 1 to it.     |

| Bit 3        | Signaled target abort.                                                                                                          |

|              | This bit is always 0 since the PCMC will not terminate a transaction with target abort.                                         |

#### **Bits 2:1 DEVSEL#** Timing **DEVT**.

The two bits define the timing to assert DEVSEL#. The PCMC asserts the DEVSEL# signal within three clocks after the assertion of FRAME#. The default value is DEVT=10. In fact, the PCMC always asserts DEVSEL# in medium timing except in CPU writes to I/O port 64h or 60h.

- Bit 0 Reserved

- Register 08h **Revision Identification.**

- **Bits 7:0** 00h.

- Register 0B~09h Class Code

- Bits 23:0 060000h

- **Register 0Eh Header Type**

- **Bits 7:0 00h**

- **Register 50h**

| Bits 7:6 | DRAM Read CAS Pulse Width                                     |

|----------|---------------------------------------------------------------|

|          | 00:4T                                                         |

|          | 01 : 3T                                                       |

|          | 10 : 2T                                                       |

|          | 11 : Reserved                                                 |

| Bit 5    | DRAM Write CAS Pulse Width                                    |

|          | 0:3T                                                          |

|          | 1:2T                                                          |

| Bit 4    | MA Timing Setting                                             |

|          | 0: Normal operation. (MD is changed on the CAS# rising edge.) |

|          | 1: Advance 1T than normal operation.                          |

|          | When using EDO DRAM, this bit must set to 0.                  |

| Bit 3    | Reserved                                                      |

| Bit 2    | Cache Toggle /Linear burst mode selection                     |

|          | 0: Toggle mode                                                |

|          | 1: Linear burst mode                                          |

| Bits 1:0 | DRAM type selection                                           |

|          | 00: 256k x N                                                  |

|          |                                                               |

Preliminary V2.0 April 2, 1995 22

01: 1M x N 10: 4M x N 11: 16M x N

## **Register 51h**

| Bit 7        | L2 Cache Exist or not                  |

|--------------|----------------------------------------|

|              | 0 : Not Exist                          |

|              | 1 : Exist                              |

| Bit 6        | L2 Cache Enable                        |

|              | 0 : Disable                            |

|              | 1 : Enable                             |

| Bit 5        | SRAM type (Standard or Burst)          |

|              | 0 : Standard SRAM                      |

|              | 1 : Burst SRAM                         |

| Bit 4        | L2 Cache WT/WB Policy                  |

|              | 0 : Write-Through mode                 |

|              | 1 : Write-Back mode                    |

| Bits 3:1     | L2 Cache Size                          |

|              | 000 : 64KB                             |

|              | 001 : 128KB                            |

|              | 010 : 256KB                            |

|              | 011 : 512KB                            |

|              | 100 : 1MB                              |

|              | 101 : 2MB                              |

|              | 11x : Reserved                         |

| Bit 0        | CPU L1 Cache Write-Back Enable         |

|              | 0 : Disable                            |

|              | 1 : Enable                             |

| Register 52h |                                        |

| Bits 7:6     | Standard SRAM Cache speed (Read/Write) |

|              | 00 : 5-x-x-x Slower                    |

|              | 01 : 4-x-x-x Faster                    |

|              | 10 : 3-x-x-x Fastest                   |

|              | 11 : Reserved                          |

|              |                                        |

Preliminary V2.0 April 2, 1995

| Bits 5:4     | Standard/Burst SRAM x Setting (Burst Read/Write cycle )                                                                                                                                                                                                                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 00 : 3T                                                                                                                                                                                                                                                                 |

|              | x1:1T                                                                                                                                                                                                                                                                   |

|              | 10 : 2T                                                                                                                                                                                                                                                                 |

| Bit 3        | Cache Interleave Enable                                                                                                                                                                                                                                                 |

|              | 0 : Disable                                                                                                                                                                                                                                                             |

|              | 1 : Enable                                                                                                                                                                                                                                                              |

| Bit 2        | Burst SRAM Cache Burst Cycle                                                                                                                                                                                                                                            |

|              | 0 : 4-x-x-x                                                                                                                                                                                                                                                             |

|              | 1 : 3-x-x-x                                                                                                                                                                                                                                                             |

| Bit 1        | Cache Sizing Enable                                                                                                                                                                                                                                                     |

|              | 0: Normal Operation                                                                                                                                                                                                                                                     |

|              | 1: Always Cache hit to enable Cache Sizing for BIOS                                                                                                                                                                                                                     |

| Bit 0        | Refresh RAS Active time                                                                                                                                                                                                                                                 |

|              | 0 : 6T                                                                                                                                                                                                                                                                  |

|              | 1 : 5T                                                                                                                                                                                                                                                                  |

| Register 53h |                                                                                                                                                                                                                                                                         |

| Bit 7        | DRAM CAS precharge time                                                                                                                                                                                                                                                 |

|              | 0 : 2T                                                                                                                                                                                                                                                                  |

|              | 1 : 1T                                                                                                                                                                                                                                                                  |

| Bit 6        | Shadow RAM Read Enable                                                                                                                                                                                                                                                  |

|              | 0 : Disable                                                                                                                                                                                                                                                             |

|              | 1 : Enable                                                                                                                                                                                                                                                              |

|              | When this bit is enabled, the F segment is shadowed by default.                                                                                                                                                                                                         |

|              | Before shadowing, BIOS should not turn on the bit so that reading F segment is always forwarded to PCI bus.                                                                                                                                                             |

| Bit 5        | Shadow RAM Write Protection Enable                                                                                                                                                                                                                                      |

|              | 0 : Disable                                                                                                                                                                                                                                                             |

|              | 1 : Enable                                                                                                                                                                                                                                                              |

|              | After porting the shadowed segment into DRAM, this bit can be set so that the corresponding shadowed segment is not writable. Under such circumstances, the cycle which intends to write the segment is treated as non-local memory cycle, and is forwarded to PCI bus. |

Preliminary V2.0April 2, 199524Silicon Integrated Systems Corporation

| Bit 4        | Shadow RAM Enable for PCI Master Accesses                                         |

|--------------|-----------------------------------------------------------------------------------|

|              | 0 : Disable                                                                       |

|              | 1 : Enable                                                                        |

| Bit 3        | F0000h - FFFFFh Shadow RAM Cacheable                                              |

|              | 0 : Non-Cacheable                                                                 |

|              | 1 : Cacheable                                                                     |

|              | Note that only code is cacheable to L2/L1 when this bit is set.                   |

| Bit 2        | RAS to CAS delay time                                                             |

|              | 0:4T                                                                              |

|              | 1: 3T                                                                             |

| Bit 1        | RAS precharge time                                                                |

|              | 0:5T                                                                              |

|              | 1:4T                                                                              |

| Bit 0        | Enable host to CTMPB push rate to be X-1-1-1                                      |

|              | 0 : Enable                                                                        |

|              | 1 : Disable.                                                                      |

|              | When this bit is disabled, the push rate is defined by bit [5:4] of register 52h. |

| Register 54h | E Segment Setting                                                                 |

| Bit 7        | E0000h - E3FFFh Shadow RAM Enable                                                 |

| Bit 6        | E4000h - E7FFFh Shadow RAM Enable                                                 |

| Bit 5        | E8000h - EBFFFh Shadow RAM Enable                                                 |

| Bit 4        | EC000h - EFFFFh Shadow RAM Enable                                                 |

| Bit 3        | E0000h - E3FFFh Shadow RAM Cacheable                                              |

| Bit 2        | E4000h - E7FFFh Shadow RAM Cacheable                                              |

| Bit 1        | E8000h - EBFFFh Shadow RAM Cacheable                                              |

| Bit 0        | EC000h - EFFFFh Shadow RAM Cacheable                                              |

| Register 55h | D Segment Setting                                                                 |

| Bit 7        | D0000h - D3FFFh Shadow RAM Enable                                                 |

| Bit 6        | D4000h - D7FFFh Shadow RAM Enable                                                 |

| Bit 5        | D8000h - DBFFFh Shadow RAM Enable                                                 |

Preliminary V2.0 April 2, 1995

| Bit 4        | DC000h - DFFFFh Shadow RAM Enable                 |

|--------------|---------------------------------------------------|

| Bit 3        | D0000h - D3FFFh Shadow RAM Cacheable              |

| Bit 2        | D4000h - D7FFFh Shadow RAM Cacheable              |

| Bit 1        | D8000h - DBFFFh Shadow RAM Cacheable              |

| Bit 0        | DC000h - DFFFFh Shadow RAM Cacheable              |

| Register 56h | C Segment Setting                                 |

| Bit 7        | C0000h - C3FFFh Shadow RAM Enable                 |

| Bit 6        | C4000h - C7FFFh Shadow RAM Enable                 |

| Bit 5        | C8000h - CBFFFh Shadow RAM Enable                 |

| Bit 4        | CC000h - CFFFFh Shadow RAM Enable                 |

| Bit 3        | C0000h - C3FFFh Shadow RAM Cacheable              |

| Bit 2        | C4000h - C7FFFh Shadow RAM Cacheable              |

| Bit 1        | C8000h - CBFFFh Shadow RAM Cacheable              |

| Bit 0        | CC000h - CFFFFh Shadow RAM Cacheable              |

| DIU          | CC0001 - CFFFFII Shauow RAM Cacheable             |

| Register 57h |                                                   |

| Bit 7        | Allocation of Non-cacheable Area #1               |

|              | 0 : Local DRAM                                    |

|              | 1 : AT Bus. The local DRAM is disabled.           |

| Bit 6        | Non-cacheable Area #1 Enable                      |

|              | 0 : Disable                                       |

|              | 1 : Enable                                        |

| Bits 5:3     | Size of Non-Cacheable Area #1 (within 128 MBytes) |

|              | 000 : 64KB                                        |

|              | 001 : 128KB                                       |

|              | 010 : 256KB                                       |

|              | 011 : 512KB                                       |

|              | 100 : 1MB                                         |

|              | 101 : 2MB                                         |

|              | 110 : 4MB                                         |

|              | 111 : 8MB                                         |

| 1::          | Annel 2 1005 26 Siling Internet of Sectors Commen |

Preliminary V2.0 April 2, 1995

#### **Register 58h**

Bits 7~0 A23 ~ A16 of Non-Cacheable Area #1 (within 128 MBytes)

#### **Register 59h**

| Bit 7    | Allocation of Non-cacheable Area #2                    |  |  |

|----------|--------------------------------------------------------|--|--|

|          | 0 : Local DRAM                                         |  |  |

|          | 1 : AT Bus. The local DRAM is disabled.                |  |  |

| Bit 6    | Non-cacheable Area #2 Enable                           |  |  |

|          | 0 : Disable                                            |  |  |

|          | 1 : Enable                                             |  |  |

| Bits 5:3 | Size of Non-Cacheable Area #2 (within 128 MBytes)      |  |  |

|          | 000 : 64KB                                             |  |  |

|          | 001 : 128KB                                            |  |  |

|          | 010 : 256KB                                            |  |  |

|          | 011 : 512KB                                            |  |  |

|          | 100 : 1MB                                              |  |  |

|          | 101 : 2MB                                              |  |  |

|          | 110 : 4MB                                              |  |  |

|          | 111 : 8MB                                              |  |  |

| Bits 2:0 | A26 ~ A24 of Non-Cacheable Area #2 (within 128 MBytes) |  |  |

#### **Register 5Ah**

| Bits 7:0 | A23 ~ A16 of Non-Cacheable Area #2 (within 128 MB) | ytes) |

|----------|----------------------------------------------------|-------|

|----------|----------------------------------------------------|-------|

#### **Register 5Bh**

#### Bit 7 Fast Gate A20 Emulation Enable

- 0 : Disable

- 1 : Enable

The sequence to generate A20M# is: write D1h to I/O port 64h followed by I/O write to port 60h with data 00h. When this bit is enabled, the SiS5501 responds the cycle by asserting DEVSEL# in slowest timing. Otherwise, the cycle is subtractively decoded by SiS 5503, and then is passed to 8042 on the ISA bus.

#### Bit 6 Fast Reset Emulation Enable

Preliminary V2.0 April 2, 1995 27 Silicon Integrated Systems Corporation

|                     | 0 : Disable                                                                                                                                        |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 1 : Enable                                                                                                                                         |

|                     | The Fast reset command is I/O write to port 64h with data 1111XXX0b.                                                                               |

|                     | After the command is issued, the assertion of INIT or CPURST is delayed by 2us or 6us which can be programmed in bit 5, and is held for 25 CPUCLK. |

| Bit 5               | Fast Reset Latency Control                                                                                                                         |

|                     | 0 : 2us                                                                                                                                            |

|                     | 1 : 6us                                                                                                                                            |

| Bit 4               | Slow Refresh Enable (1:4)                                                                                                                          |

|                     | 0 : Normal Refresh                                                                                                                                 |

|                     | 1 : Slow Refresh                                                                                                                                   |

| Bit 3               | DRAM Write Push to CAS delay                                                                                                                       |

|                     | 0:2T                                                                                                                                               |

|                     | 1 : 1T                                                                                                                                             |

| Bit 2               | De-turbo Hold time                                                                                                                                 |

|                     | 0 : Hold 4 us                                                                                                                                      |

|                     | 1 : Hold 8 us (Every 12 us)                                                                                                                        |

| Bit 1               | De-turbo Switch Enable                                                                                                                             |

|                     | 0 : Always turbo, ignore the status of De-turbo Switch                                                                                             |

|                     | 1 : De-turbo Switch Enable                                                                                                                         |

| Bit 0               | CAS Driving Current Control Bit 0 ( Please refer to Reg. 5Eh Bit 0 for details)                                                                    |

| <b>Register 5Ch</b> |                                                                                                                                                    |

| Bit 7               | Latency from ADS# to Monitor Local Memory Status                                                                                                   |

|                     | 0:3T                                                                                                                                               |

|                     | 1:2T                                                                                                                                               |

Depending on the setting of this bit, the PCI master bridge in the SiS5501 may monitor the local memory status from the inside local memory decoder either by the end of T2 or T3. If the CPU initiates a PCI cycle, it is determined to be converted to PCI side from this point. Specifically, BRDY# is always returned to CPU one CPUCLK later if the CTPPB is not full, for post memory write cycles. Thus, this bit also affects the CPU to PCI Post write speed. When it is set to 0, the Post write rate is 5T for each double word. When it is set to 1, the rate is 4T per double word. For a Qword PCI memory write, the post write rate is 7T(bit7=1), or 8T(bit7=0).

Preliminary V2.0April 2, 199528Silicon Integrated Systems Corporation

| Bit 6        | Enable Refresh Cycle when CPU is hold                                                                 |

|--------------|-------------------------------------------------------------------------------------------------------|

|              | 0 : Disable                                                                                           |

|              | 1 : Enable                                                                                            |

| Bit 5        | Enable Snoop Filter                                                                                   |

|              | 0 : Disable                                                                                           |

|              | 1 : Enable                                                                                            |

| Bit 4        | CAS# Pulse Width in PCI master write cycle                                                            |

|              | 0:1T                                                                                                  |

|              | 1:2T                                                                                                  |

| Bit 3        | Latency from the disarming of "Full" to the assertion of BRDY# for the pending CPU to PCI write cycle |

|              | 0 : 1T                                                                                                |

|              | 1:2T                                                                                                  |