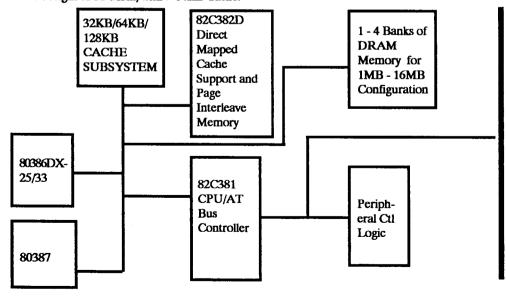

# HiD/386 AT CHIPSET HIGH INTEGRATION DIRECT MAPPED CACHE AT 82C381/82C382D-25/33

100% IBM PC/AT Compatible 386/AT Chipset for 25 and 33 MHz systems

Designed to provide the most cost-effective, high performance Cache based 386/AT with high integration

Advanced Memory Controller design

- Direct support for 64KB, 128KB and larger-Cache Subsystems

- Implements sophisticated DRAM Controller with Paging in odd banks and 2/4 way Page Interleaving with even banks

- o BIOS Shadow Ram

- o 256K Relocation to top of Memory

- Non-Cacheable programmable memory regions, and GateA20 support

The HiD/386 Chipset, 82C381 and 82C382D, support high integration implementations of Direct Mapped Cache with 32KB/64KB/128KB Cache for 25 and 33 MHz 386/AT Personal Computers. Combined with the 82C206 Integrated Peripherals Controller, it integrates the 386/AT motherboard to under 20 devices, plus memory. It is designed to cost reduce discrete and CHIPS' CS8230 based 82385 Cache 386/AT designs, as well as boost the performance of these designs to 33 MHz, with >64KB Cache.

Software configurable Command Delays, Wait States and Memory Organization

Synchronous AT Bus Clock with programmable CPU Clock divide options: by 2, by 3 and by 4

Complete AT/386 system board requires only 20 components plus memory

Single EPROM configuration

Targeted at very high performance 32-bit power PCs and file-server designs

Low power, high speed 1.2u CMOS Technology

The 82C381 provides system control logic and data bus conversion logic. The control logic consists of 386 CPU control logic, AT Bus cycle control, 387 Numeric Processor control logic, synchronous clock divide logic and control of the local peripheral bus. The data bus conversion logic consists of various 8, 16, 32 bit conversions for ROM cycles, AT bus cycles and memory cycles.

Page 1

The 82C382D performs the Memory Management functions for the HiD/AT chipset. It is designed to optimize cost of high performance 386/AT systems with 64KB, 128KB or larger Direct Mapped Cache Memory. It also implements logic to maintain compatibility in the AT environment . It provides a Page Interleave backend for main DRAM memory, in order to improve performance during miss cycles. It also has features for reducing system cost.

It minimizes Cache Memory cost by allowing the use of slow SRAM; by supporting single EPROM BIOS configurations; putting DRAM on the local bus and consequently reducing DRAM speeds by 15ns typically; and by remapping 256K of DRAM between 640K and 1024K to top of main memory.

It provides a very flexible implementation of paging for the main DRAM memory. For even bank configurations, it provides 2-way or 4-way interleaving; for odd banks it provides paging. This provides a flexible approach to increasing the size of the local memory as software demands increase, without imposing a penalty on performance.

Finally, memory performance is optimised by shadow RAM techniques for BIOS ROMs; concatenated pages for multiple bank configurations; paging for odd banks; and variable page size for larger DRAMs.

#### System Architecture

The HiD/AT chipset is compatible with the 82C206 Integrated Peripherals Controller. Consequently, with the 82C206, a very high integration and very high performance 386/AT can be implemented. A typical motherboard can be designed with less than 20 devices plus memory.

For larger AT designs, targeted at file-servers and departmental computers, designs with 8 or more slots can be supported with external AT bus drivers.

#### Ordering Information

82C381-25 or 82C381-33 = 386/AT Advanced CPU Controller for 25 MHz and 33 MHz respectively

82C382D-25 or 82C382D-33 = 386/AT Direct Mapped/ Page Interleave Memory Controller for 25 MHz and 33 MHz respectively

HiD/386-25 = 25 MHz Direct Mapped 82C381-25 and 82C382D -25 chipset

HiD/386-33 = 33 MHz Direct Mapped 82C381-33 and 82C382D-33 chipset

DK/HiD-386 = 25 MHz Development Kit with 1MB DRAM and 386-25

(See Development Kit Price list for complete details)

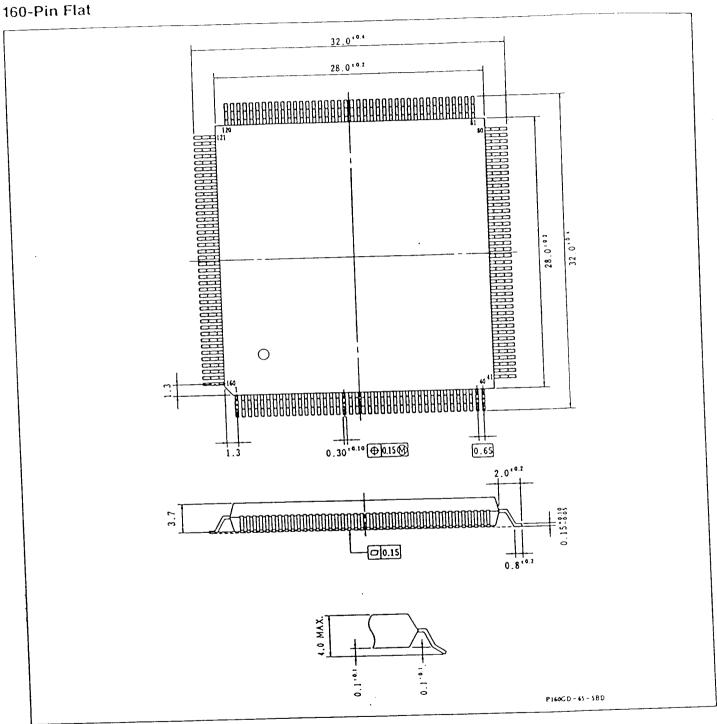

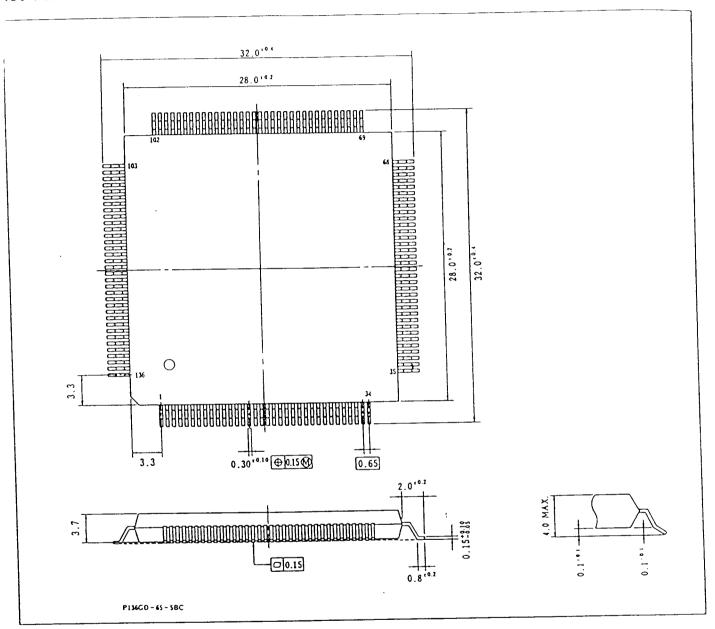

| Order Number | Speed    | Package Type |  |

|--------------|----------|--------------|--|

| F82C381D     | -25, -33 | PFP-160 pins |  |

| F82C382D     | -25,-33  | PFP-136 pins |  |

| DK/HiD-386   | -25      | Baby AT      |  |

# OPTi, Inc

2700 Augustine Drive, Suite #165, Santa Clara, CA 95054 Phone: 408-980-8178, FAX: 408-980-8860

IBM, AT and PC/XT are registered trademarks of International Business Machines. 386 is a trademark of Intel Corporation Copyright 1989 OPT, Inc.

### 82C381 B AT/386 High Integration CPU Controller

#### V1.1, December 12, 1989

1.0 The HiD/386 Chipset consists of the 82C381\_B and 82C382\_B. Together, they are designed to implement high performance, highly integrated, 386/AT Personal Computers operating at 20, 25 and 33 MHz. The 82C381\_B provides CPU control and Bus Conversion functions, while the 82C382\_B provides Direct Mapped Cache Control (of any size) and 1-16MB of Page Interleave Memory Control. With an Integrated Peripherals Controller like the 82C206 (available from Texas Instruments, Siemens, Chips and Technologies, UMC, Winbond, etc) or VL82C100 (from VLSI Technology), a highly integrated, compact 386/AT can be implemented.

#### 2. Overview

The 82C381\_B performs the CPU interface, AT system bus interface and data path control. It provides the following features to 386/AT systems:

- \* Software programmable AT bus clock & CPU clock.

- \* CPU interface & bus control.

- \* OS/2 Alternate Hot RESET support.

- \* Optimized programmable stretched AT Bus clock.

- \* Port B register.

- \* Built-in direct-mapped, flexible cache size cache controller.

#### 2.0 Functional Description

The 82C381\_B CPU Controller consists of the following functional sub-modules:

- \* Reset and Shut Down Logic.

- \* Clock Generation and Selection Logic.

- \* CPU State Machine and AT Bus State Machine.

- \* Bus Arbitration Logic, DMA/Master and Refresh Logic.

- \* Port B Register and NMI Logic.

- \* Configuration Registers.

- \* Data Bus Conversion and Data Path Control Logic.

- \* Data Buffers and Latches.

- \* Parity Generation/detection Logic.

- \* Cache Controller Logic.

#### 2.1 Reset and Shut Down Logic

Two reset inputs RST1# and RST2# are provided on the 82C381\_B chip. RST1# is the Power Good signal from the power supply. When RST1# is low, the 82C381 B asserts CPURST for

CPU reset and SYSRST for system reset. RST2# is generated from the 8042 keyboard controller when a CPU warm reset is required. CPURST is also activated by the 82C381\_B when a shut down condition is detected from CPU status. Additionally, a low to high transition in REG00<5> causes CPURST to be active after the current I/O command goes inactive and a HALT instruction has been executed. Both CPURST and SYSRST are asserted for at least 128 CLK2 cycles and is synchronized with respect to CLK2 to meet the setup and hold time requirements of the 80386 CPU.

#### 2.2 Clock Generation

The 82C381\_B provides two set of synchronous clocks: CLK and ATCLK, and OSC and OSC/12. It has two input clocks, CLK2IN and OSX1. CLK2IN is driven from a TTL crystal oscillator, running at a maximum of 3X the processor clock frequency. OSX1 is the input of a 14.31818 MHz crystal to generate the OSC and OSC/12 clock.

The 82C381\_B generates the processor clock, CLK, for driving the 82C382\_B memory controller, 80386 CPU, 80387 Coprocessor and 80385 Cache controller. CLK can be derived from CLK2IN or from ICLK which is CLK2IN/2, CLK2IN/3 or CLK2IN/4, and is used internally as the clock of AT Bus State Machine. ATCLK is always half frequency of ICLK. Note that when CLK is derived from CLK2IN, ICLK can be derived from any of the CLK2IN/2, CLK2IN/3 and CLK2IN/4.

#### 2.3 CPU and AT Bus State Machine

In order to achieve maximum performance of the 80386 CPU and maintain 100% IBM PC/AT compatibility, it is desirable to run the local memory at the rated maximum CPU frequency and the AT bus at a slower clock frequency. The two state machines maintain a synchronous protocol, at all times.

#### 2.3.1 CPU State Machine

The interface to the 80386 requires interpretation of the status lines D/C#, W/R# and M/IO# from CPU during phase 1 of T2/T1P and generation of READY# during phase 2 of T2/T2P to the CPU upon completion of the cycle. 82C382\_B acts as the arbitrator by sending AF32# to 82C381\_B as a flag to trigger the AT Bus State Machine. A low AF32# indicates a 82C382\_B local memory cycle, the AT Bus State Machine stays idle, and the CPU State Machine terminates itself by monitoring the active READY# signal from outside. A high AF32# triggers the AT Bus State Machine, and upon completion of the instruction, a synchronized READY# terminates the CPU State Machine as well as all external devices including CPU and 82C382\_B.

#### 2.3.2 AT Bus State Machine

The AT Bus State Machine gains control when the 82C382\_B's Decoding Logic decodes a non-local memory cycle. It uses BCLK which is twice the frequency of AT system clock ATCLK. It also performs the necessary synchronization of control and status signals between the AT bus and the processor. The 82C381\_B supports 8 and 16 bit memory or I/O devices located on the AT bus.

An AT bus cycle is initiated by asserting ALE in AT-TS1 state. On the trailing edge of ALE, M16# is sampled for a memory cycle to determine the bus size. It then enters AT-TC state and provides the command signal. For an I/O cycle, IO16# is sampled after the trailing edge of ALE till the end of the command. Typically, the wait state for an AT 8/16 bit transaction is 5/1 respectively. The command cycle is extended when CHRDY is detected inactive, or is terminated when zero wait state request signal NOWS# from the AT bus is active. Upon expiration of the wait states, the AT State Machine terminates itself and passes internal READY to CPU State Machine for outputting synchronous READY# to the 80386.

A one in REG00<4> enables stretched ATCLK. From the beginning of a bus cycle, ATCLK stays high until it receives AF32# from 82C382\_B. An AT bus cycle then starts immediately without waiting for the synchronization of ATCLK in order to maximise performance. A local memory cycle drops ATCLK to zero.

#### 2.4 Bus Arbitration Logic, DMA/Master and Refresh Logic

The 82C381\_B provides arbitration between the CPU, DRAM refresh logic and DMA/Master devices. It handles HRQ and RFSHRQ by generating HOLD request to the CPU. The CPU will respond to an active HOLD signal by asserting HLDA and placing most of its output and I/O pins in a high impedance state after completing its current bus cycle. After the CPU relinquishes the bus, the 82C381\_B responds by issuing RFSH# or HLDAO depending on the requesting device.

The arbitration between Refresh and DMA/Master is based on FIFO (first in first out) priority. However, RFSHRQ will be internally latched and serviced immediately after DMA/Master finishes its request if RFSHRQ is queued behind HRQ. HRQ has to remain active to be serviced if RFSHRQ comes first.

During a refresh cycle, the refresh address is put out on the XAO-XA9 address lines, and XMR# is active 2 SYSCLK after RFSH# is active.

DMA and Bus Master share the same request pin HRQ. After the 82C381 B receives HRQ it asserts HOLD request to the CPU.

Upon finishing the current cycle, the CPU relinquishes the bus by asserting HLDA. The 82C381\_B issues HLDAO to the requesting device to start gaining control of the bus. During an active HLDAO period the only way to distinguish between DMA and Bus Master request is to monitor the DMA8# and DMA16# signals. DMA8#/DMA16# active indicates an 8-bit/16-bit DMA transfer, while if both are inactive, it means it is a Master cycle.

#### 2.5 Numeric Processor Interface

Incorporated in the 82C381\_B is the circuitry to interface a 80387 Numeric Coprocessor to 80386. The circuitry handles the decoding required for selecting and resetting the Numeric Coprocessor, handling CPBUSY# and CPERR# signals from Coprocessor to the CPU, and generating interrupt signals for error handling.

82C381\_B samples ERROR# pin from Coprocessor during power on reset. A low indicates an 80387 is present, and any further Coprocessor cycles will be terminated by an active READY# from the 80387. Otherwise, the 82C381\_B is responsible for the READY# return for all the Coprocessor cycles.

While executing a task, the Coprocessor issues a CPBUSY# signal to the 82C381\_B and it is passed on to the CPU as BUSY#. If during this busy period, a numeric coprocessor error CPERR# occurs, it results in an internal latching of the BUSY# output and assertion of IRQ13 for a NP exception request. The latched BUSY# stays active until cleared by an I/O write cycle to address OFOH or OF1H. IRQ13 is cleared only when CPERR# from Coprocessor is inactive, which can be achieved by executing a coprocessor instruction FNINIT to clear the ERROR status. The Coprocessor is reset through the CPRST output, which can be activated by a system reset or by performing a write operation to I/O port OF1H. This reset signal is synchronized with CLK and lasts for 128 cycles.

#### 2.6 Port B and NMI Logic

The 82C381\_B provides access to Port B, IO port address 61H, defined for the PC/AT as shown in Table 1.1.

| Bits | READ/WRITE | FUNCTION                             |

|------|------------|--------------------------------------|

| 7    | R          | PCK - System parity check            |

| 6    | R          | IOCHCK - IO channel check            |

| 5    | R          | OUT2 - Timer 2 out                   |

| 4    | R          | REFDET - Refresh detect              |

| 3    | R/W        | ENAIOCK - Enable I/O channel check   |

| 2    | R/W        | ENBRAMPCK - Enable RAM parity check  |

| 1    | R/W        | SPKRDATA - Speaker data              |

| 0    | R/W        | TIM2GATESPK - Timer 2 gate (speaker) |

|      |            |                                      |

#### Table 1.1

At power-on time, the NMI is disabled. However, it can be enabled or disabled by writing to IO port 70H with data bit 7 equal to zero or one respectively. An NMI occurs when NMI is enabled, ENAIOCK/ENBRAMPCK is enabled and an IOCHCK or PCK occurs.

#### 2.7 Configuration Registers

There are two bytes of configuration registers in the 82C381\_B: REG00 and REG01. An indexing scheme is used to reduced the I/O ports required to access all the registers required for 82C381\_B & 82C382\_B and also avoids possible mistakes by incorrect programming. Writing to or reading from these registers involves two steps:

- 1. OUT to port 22H with the index addressing value that a particular register is to be written to or read from.

- 2. OUT or IN from port 24H for the write to or read from operation.

# 2.7.1 Register Description

| DE | ~^ | Λ |

|----|----|---|

| КĽ | Gυ | v |

| D7   1 | D6   I | 05   D | 4   D3     | D2 | 2   I | D1 | D0          |                                             |    |  |

|--------|--------|--------|------------|----|-------|----|-------------|---------------------------------------------|----|--|

|        |        |        | <br> -<br> |    |       |    | ><br>><br>> | ATCLK<br>TURBO<br>STRETO<br>FAST F<br>ENWTC | CH |  |

| Bits | Function                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 6  | Cache Controller Enable and Multiplex pins Control.  Default is 00.  00 Cache Controller disabled; PPCS#=1,SPCS#=1,NPCS#=1  NPCLK active (Default)  01 Cache Controller disabled; PPCS#,SPCS#,NPCS#  active if selected, NPCLK active  10 External cache controller installed; PPCS#, SPCS#  NPCS# active if selected, NPCLK active  11 On-chip cache controller installed; PPCS#=CAOE#  SPCS#=CAWE#,NPCS#=TAGW#,NPCLK=CSL# |

| 5    | Alternate hot CPU reset. A low to high transition in this bit activates a CPU reset. Once active, it remains active until cleared by another write. Default is 0.                                                                                                                                                                                                                                                           |

| 4    | ATCLK stretch enable.Default is 0.                                                                                                                                                                                                                                                                                                                                                                                          |

| 3    | TURBO Clock Select. A zero selects CLKIN as the CPU clock, and a one enables the HIGH pin to select the CPU clock. If HIGH pin has been enabled, then a low on this pin selects CLKIN as CPU clock (high speed mode), and a high on this pin selects ICLK as                                                                                                                                                                |

- speed mode), and a high on this pin selects in the CPU clock(low speed mode). Default is 0.

- 2, 1 | ICLK clock select. Default is 00.

- 00 ICLK = CLKIN/4.

- ICLK = CLKIN/3.01

- ICLK = CLKIN/2.

- 11 Reserved

- Master byte swap enable.Default is 0.

| D7   D6   D5   D4   D3   D2   D1   D0 | REG01 |        |         |         |         |                               |                      |

|---------------------------------------|-------|--------|---------|---------|---------|-------------------------------|----------------------|

|                                       | D7    | D6   I | D5   D4 | D3   D2 | D1   D0 |                               |                      |

|                                       |       |        |         |         | ><br>>  | RESERVI<br>RESERVI<br>RESERVI | ED<br>ED<br>ED<br>ED |

| Bits | Function                                                                                                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Cache controller Flush#. A one activates FLUSH# pin output to the Cache Controller, and zero deactivates FLUSH#. Default is 1.                                                                           |

| 1    | RESET3 Control. A one generates RESET3 on receiving a RESET2 only after a HALT instruction is detected by the 82C381_B. A zero generates a RESET3 immediately after receiving a RESET2. Default is zero. |

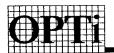

### 2.8 Data Bus Conversion and Data Path Control Logic

The 82C381 performs data conversion when CPU's 32/16 bit instruction accesses 16/8 bit devices on AT Bus, or when DMA/MASTER accesses local DRAM or devices on AT Bus. It also provides all the control signals necessary to set the data flow path for external buffers.

The following table shows the data paths for various system cycles:

|                                                                                                                                                                                                                  | :                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| CPU Cycle                                                                                                                                                                                                        | Data Path                                                                                            |

| Low word AT bus 16-bit access High word AT bus 16-bit access 1st byte AT bus 8-bit access 2nd byte AT bus 8-bit access 3rd byte AT bus 8-bit access 4th byte AT bus 8-bit access Local DRAM or 387 access        | C/D E/F G/H A/B E/F G/H D F H C F H B F H A F H A,B,C,D tri-stated                                   |

| 8-bit DMA Cycle                                                                                                                                                                                                  | Data Path                                                                                            |

| Local DRAM 1st byte access Local DRAM 2nd byte access Local DRAM 3rd byte access Local DRAM 4th byte access AT bus 8-bit memory access AT bus 16-bit memory 1st byte access AT bus 16-bit memory 2nd byte access | D F H C F H B F H A F H H tri-stated H - F - E - G                                                   |

| 16-bit DMA Cycle                                                                                                                                                                                                 | Data Path                                                                                            |

| Local DRAM low word access<br>Local DRAM high word access<br>AT bus 16-bit memory access                                                                                                                         | C/D E/F G/H<br>A/B E/F G/H<br>G,H tr-stated                                                          |

| Master Cycle                                                                                                                                                                                                     | Data Path                                                                                            |

| Local DRAM low word access Local DRAM high word access AT bus 16-bit access AT bus 1st byte 8-bit access AT bus 2nd byte 8-bit access                                                                            | C/D E/F G/H A/B E/F G/H G,H tri-stated G,H tristated G - E - F - H (default) G,H tristated(optional) |

#### 2.9 Data Latches

The 82C381 provides data latches for all AT read cycles, not only for bus conversion, but also for the AT cycle read command which may be terminated before CPU samples the data.

#### 2.10 Parity Generation/Detection Logic

For local DRAM write cycle, the 82C381\_B generates even parity for each of the four bytes of the CPU 32 bit data. These valid parity bits are stored in the local DRAMs. During a local memory read access, the 82C381 checks for parity validation for each byte read. If the parity is detected as being odd, and if bit2 of Port B is 0, bit7 of Port B is set and NMI will be issued, if it is not masked.

If the cache enable bits, bit 6 & 7 in the REG00, are enabled, the parity checking circuitry will check the parity validation on a four bytes basis for every local DRAM read cycle, since the memory controller reads four bytes at a time to update cache.

#### 2.11 Cache Controller Logic

The 82C381\_B supports direct map/write-through cache memory control logic. This cache implementation provides a very flexible and low cost alternative for a simple, high performance cache system.

There are three factors that the system designer must take into consideration when he implements a cache system with this chip set. They are:

TAG-RAM Line size Cache memory

#### 1) TAG-RAM

The TAG-RAM is implemented outside of the chip which increases the flexibility in the system design. Standard fast SRAM coupled with a comparator generates the tag HIT or MISS status. Depending on the total cache memory required and the line size selected, the designer can select the TAG-RAM from 4Kx4, 8Kx8 or 16Kx4 SRAMs. For example, in a 64k cache memory design, to cache upto 8M bytes local memory, you select 16-bytes as line size and two 4kx4 SRAMs for TAG; or in a 64k cache memory design, to cache upto 16M bytes local memory, you select 16-bytes as line size and two 16kx4 SRAMs to serve as TAG; or in a 128k cache memory design which caches upto 16M bytes local memory, you use line size is 16-bytes, and one 8kx8 or two 16kx4 SRAM for TAG. The selection is very flexible.

Another factor in selecting the TAG-RAM is the SRAM speed. 15-ns TAG RAM is required for the 33MHZ 386 cache system; while a 25-ns TAG RAM is reuired for the 25MHZ 386 cache system. Compared with the cost of current cache controllers, the cost of the TAG RAM used with the 381 is very low.

#### 2) Line size

A programmable register inside the 382 allows the user to select the cache memory line size between 8-bytes and 16-bytes. Normally, a larger line size increase the hit rate, but also requires more time to update the cache memory during read miss cycles. The burst read implementation for the miss cycle reduces the overhead, thereby increasing the system performance.

#### 3) Cache memory

The chip set allows the system designer to utilize any size cache SRAMS. The development kit schematics show 8Kx8s, however, most other SRAMs should be usable.

In addition, the SRAM access times are quite relaxed. To implement a 25-MHZ 386 cache system, 35ns cache memory is required; and, 25 ns cahe memory is reuired for the 33-MHZ 386 cache system.

#### 2.11.1 TAG RAM invalidation

The Index register 01 bit 0 controls the TAG RAM's invalidation. After power-up, the bit is set logic high which forces the FLUSH# pin low. The cache control logic monitors this signal internally and generates TAGWE# during local DRAM read cycles which will force the TAG RAM invalid while the POST performs memory read/write checking automatically.

A driver is required to enable the cache function. This should first disable FLUSH#, next enable the cache control function inside the 381 and 382, then select the line size and finally, disable the NCA# signal.

In normal applications, to invalidate the TAG RAM, a driver is required to enable FLUSH# and then perform a number of read operations of local DRAM, equal to the TAG RAM size; e.g. 16K times if 16Kx4 SRAMs are used as TAG RAM.

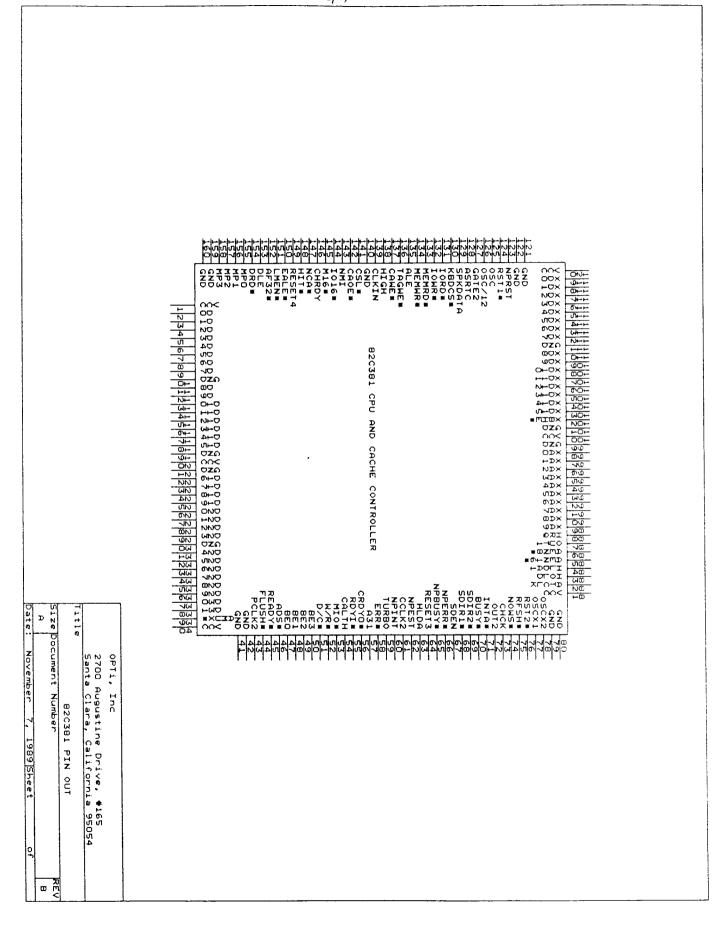

# 82C381 B PIN DESCRIPTION

| T Pin<br>y NO.<br>p<br>e<br><u>Clocks</u> | Symbol  | Description                                                                                                                      |

|-------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------|

| I 139                                     | CLKIN   | Oscillator clock input from a TTL crystal oscillator having a frequency equal to twice the rated CPU clock                       |

| B 43<br>82C381_B.                         | PCLK2   | PROCESSOR CLOCK output from the                                                                                                  |

| I 77                                      | OSCX1   | Input from 14.3 MHz Crystal                                                                                                      |

| O 78                                      | OSCX2   | Output to 14.3 MHz Crystal                                                                                                       |

| 0 125                                     | OSC     | 14.3 MHz Oscillator output must be buffered by a 244 driver to provide 24 ma drive.                                              |

| 0 126                                     | OSC/12  | 1/12 of 14.3 MHZ oscillator frequency.                                                                                           |

| O 82                                      | ATCLK   | AT System Clock output drives the SYSCLK line on the AT bus I/O Channel.                                                         |

| I 61                                      | CCLK2   | This Input Pin is the buffered PCLK2. It is derived from the same buffer as the CPU CLK2.                                        |

| Control S                                 | Signals |                                                                                                                                  |

| I 46                                      | ADS*    | Status input from CPU. This active low signal indicates the CPU is starting a cycle.                                             |

| I 51                                      | D/C*    | Data/Code status from CPU. Indicates data transfer operations when high, or control operations (code fetch, halt, etc.) when low |

| I 52                                      | W/R*    | Write/Read status from CPU. It indicates a write cycle if high and read cycle if low.                                            |

| I 53                                      | MIO*    | Memory/IO status from CPU. If high it indicates a memory cycle. If low, it indicates an I/O cycle.                               |

| B 50-47                                   | BE<3:0> | Byte Enable from CPU; during non-cpu cycles, they reflect the XAO, XA1                                                           |

OPTi, Inc., 2700 Augustine Dr, #165, Santa Clara, CA 95054 (408) 980-8178 FAX: 408-980-8860

status.

| в 45  | READY* | Ready as an output is driven low to terminate the current CPU cycle. During all other cycles, it is an input from the 82C382_B or 387. It is an open collector output requiring an external pull-up resistor. It is connected to 80386 READY* pin indirectly and with the 387's RDYO*. |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I 124 | RST1*  | Resetl is an active low input generated<br>by the power good signal of the power<br>supply. When low, it activates Reset3<br>and Reset4. RST1* is latched internally                                                                                                                   |

| I 76  | RST2*  | Active low input generated from the 8042 Keyboard Controller for a "warm reset" not requiring the system power to be shut down. It forces a CPU reset by activating RESET3.                                                                                                            |

| O 64  | RESET3 | Power on Reset or active high output to<br>the 80386 when RESET2 is active. It is<br>also activated when a shutdown<br>condition in the CPU is detected.                                                                                                                               |

| O 149 | RESET4 | System reset output used to reset the AT Bus, 82C206, 8042 Keyboard Controller, 82C382_B Memory Controller. It is synchronized with the CPU clock.                                                                                                                                     |

| I 63  | HLDA   | HOLD ACKNOWLEDGE from CPU in response to a hold request. It indicates to the requesting master that the CPU has relinquished the bus. When active, it forces commands (IOR*, IOW*, MEMR*, MEMW*) to be tristated.                                                                      |

| O 83  | HOLD   | CPU HOLD request is an active high output to the CPU. It is activated during DMA, Master and refresh cycles.                                                                                                                                                                           |

| O 84  | HLDA1  | Hold Acknowledge 1 is an active high output when the bus is granted in response to Hold Request.                                                                                                                                                                                       |

| I 88  | HRQ    | Hold Request is an active high input when DMA/Master requests a bus cycle.                                                                                                                                                                                                             |

| I 86  | AEN8*  | Address Enable 8 bit DMA transfer is active low input from one of the two 8237s to enable the address latches.                                                                                                                                                                         |

| I        | 85       | AEN16*     | Address Enable 16 bit DMA transfer is active low input from one of the two DMA controllers to enable the address latches.                                                                                                             |

|----------|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 143      | NMI        | Non Maskable Interrupt is an active high output to the NMI pin of the CPU.                                                                                                                                                            |

| Т        | 135      | ALE        | Address latch enable for AT Bus. It controls the address latches driving the AT bus. It is tri-stated during master cycles.                                                                                                           |

| 0        | 150      | EALE*      | Early address latch enable is an active low output used to latch the CPU A23-A2 lines to the XA23-XA2 AT bus lines.                                                                                                                   |

| 0        | 71       | INTA*      | Interrupt Acknowledge is an active low output to the 82C2O6 interrupt controller.                                                                                                                                                     |

| В        | 102      | XBHE*      | Byte High Enable is an active low signal which indicates transfer of data on the upper byte of the data bus. It is an output when the CPU is in control of the bus, and is an input when the DMA controller is in control of the bus. |

| I        | 152      | AF32*      | AF32 is an active low signal that indicates that a bus cycle is a local bus access.                                                                                                                                                   |

| I        | 55       | RDYI*      | CPU ready input.                                                                                                                                                                                                                      |

| <u>S</u> | ystem Bu | <u>ses</u> |                                                                                                                                                                                                                                       |

| В        | 119-112  | XD0-XD7    | X Data Bus bits <0:7>                                                                                                                                                                                                                 |

| В        | 110-103  | XD8-XD15   | X Data Bus bits <8:15>                                                                                                                                                                                                                |

| В        | 98-89    | XAO-XA9    | X Address Bus bits <0:9>; they are output pins for refresh cycles.                                                                                                                                                                    |

| I        | 2-9      | D0-D7      | CPU Data Bus bits <0:7>                                                                                                                                                                                                               |

| I        | 11-18    | D8-D15     | CPU Data Bus bits <8:15>                                                                                                                                                                                                              |

| I        | 22-29    | D16-D23    | CPU Data Bus bits <16:23>                                                                                                                                                                                                             |

| I        | 31-38    | D24-D31    | CPU Data Bus bits <24:31>                                                                                                                                                                                                             |

| I        | 57              | A31          | CPU Address Data bus bit <31>                                                                                                                                                                             |  |  |  |  |  |

|----------|-----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| В        | 155-158         | MP0-MP3      | Memory Parity Bits for the 4 bytes of System Memory. These are inputs during memory read operations and output during memory write operations                                                             |  |  |  |  |  |

| Nı       | meric P         | rocessor Int | <u>cerface</u>                                                                                                                                                                                            |  |  |  |  |  |

| 0        | 60              | NPINT        | Numeric Coprocessor Interrupt is an active high output. It is an interrupt request from the numeric processor and is connected to IRQ13 of the 82C206.                                                    |  |  |  |  |  |

| 0        | 62              | NPEST        | 387 installed signal.                                                                                                                                                                                     |  |  |  |  |  |

| I        | 65              | NPBUSY*      | Numeric Coprocessor Busy is an active low input indicating that a 387 command currently being executed. It is used to generate the BUSY signal to the CPU.                                                |  |  |  |  |  |

| 0        | 70              | BUSY*        | Active low BUSY to the CPU, initiated by the Numeric Coprocessor indicating that it is busy.                                                                                                              |  |  |  |  |  |

| I        | 66              | NPERR*       | Numeric Coprocessor Error is an active low input indicating that an unmasked error condition exists.                                                                                                      |  |  |  |  |  |

| 0        | 123             | NPRST        | Numeric Coprocessor reset is an active high reset. It is active when RESET4 is active or when a write operation is made to Port OF1H. In the later case, it is active for the half period of the command. |  |  |  |  |  |

| 0        | 58              | ERR*         | 386 error signal. It reflects the NPERR* signal during the period from RESET4* active to first ADS*. After the first ADS*, it stays high.                                                                 |  |  |  |  |  |

| <u>C</u> | Cache Interface |              |                                                                                                                                                                                                           |  |  |  |  |  |

| 0        | 44              | FLUSH*       | Tag Ram Invalidation control signal. It is programmable through INDEX Register 01 bit 0.                                                                                                                  |  |  |  |  |  |

| I        | 54              | CALTH        | CPU Status signals latch enable. It is from the 385 and is used to synchronize status signals with the 385                                                                                                |  |  |  |  |  |

| <del>▀▘▘</del> |        |                                                                                                                                                                                                                            |

|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |        | signals. For Direct Map Cache implementations, this signal should be tied low.                                                                                                                                             |

| т 56           | CRDY0* | Ready output in Direct Map Cache systems. It is an open drain output and becomes active at the end of the last T-state of a read hit cycle.                                                                                |

| O 136          | TAGWE* | Tag Ram Write Enable. It is used to update the tag ram's validation. Note, that when FLUSH* is active, a local DRAM read will force this signal active                                                                     |

| 0 137          | CAWE*  | Cache Memory Write Enable. A write hit and cachable cycle, this signal will be activated which updates the contents inside the cache memory.                                                                               |

| O 141          | CSL*   | Cache Memory Chip Selects control. A read miss and cachable cycle will activate this signal which forces all the chip selects of cache memory to low.                                                                      |

| 0 142          | CAOE*  | Cache Memory Output enable. A memory read hit and cachable cycle activates this signal.                                                                                                                                    |

| I 147          | NCA*   | Non Cachable signal from the 82C382_B. This signal is used to indicate that the cache function is not enabled.                                                                                                             |

| I 148          | НІТ*   | Hit or miss signal from Tag Ram. This is used to determine whether the current memory cycle is from cache memory or not.                                                                                                   |

| I 39           | AMUX*  | Indicates whether the 385 is installed (active low) or not.                                                                                                                                                                |

| AT Bus S       | ignals |                                                                                                                                                                                                                            |

| I 146          | CHRDY  | I/O Channel Ready is an active high input from the AT Bus. When low it indicates a not ready condition and inserts wait states in AT-I/O or AT-memory cycles. When high, it allows termination of the current AT-bus cycle |

| I 145          | M16*   | Memory Chip Select 16 is an active low input from the AT Bus indicating a 16-bit transfer. If high, it implies an 8-bit transfer.                                                                                          |

OPTi, Inc., 2700 Augustine Dr, #165, Santa Clara, CA 95054 (408) 980-8178 FAX: 408-980-8860

| ] |                |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---|----------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 144            | IO16*       | I/O Channel Select 16 is an active low input from the AT Bus indicating a 16-bit I/O transfer. If high it implies an 8-bit transfer.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ] | I 74           | NOWS*       | No Wait States is an active low input<br>from the AT bus, causing immediate<br>termination of the current AT Bus cycle<br>Memories capable of zero wait states,<br>use this line to speed up memory cycles                                                                                                                                                                                                                                                                                                                                                        |

| - | I 73           | СНСК        | I/O Channel Check is an active low input from the AT bus causing an NMI to be generated if enabled. It is used to signal an I/O error condition from a device residing on the AT bus.                                                                                                                                                                                                                                                                                                                                                                             |

| I | В 133          | MEMRD*      | AT Bus memory read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1 | В 134          | MEMWR*      | AT Bus memory write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| J | В 132          | IOWR*       | AT Bus I/O write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ] | В 131          | IORD*       | AT Bus I/O read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ] | Miscellan      | eous        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | I 59           | TURBO       | The TURBO Input Pin enables an external switch to control the speed of the CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                |             | A low select high speed operation and a high select low speed operation. Note, Bit 3 in Configuration Register 0 needs to enable the HIGH pin function. The default state of Bit 3 is to disable the HIGH pin function.                                                                                                                                                                                                                                                                                                                                           |

|   | I 154          | DRD*        | A low select high speed operation and a high select low speed operation. Note, Bit 3 in Configuration Register 0 needs to enable the HIGH pin function. The default state of Bit 3 is to disable                                                                                                                                                                                                                                                                                                                                                                  |

|   | I 154<br>I 153 | DRD*        | A low select high speed operation and a high select low speed operation. Note, Bit 3 in Configuration Register 0 needs to enable the HIGH pin function. The default state of Bit 3 is to disable the HIGH pin function.  Data Read is an active low output used to transfer data from the memory bus to the local CPU bus. If high it sets the data path from the local CPU                                                                                                                                                                                       |

|   |                |             | A low select high speed operation and a high select low speed operation. Note, Bit 3 in Configuration Register 0 needs to enable the HIGH pin function. The default state of Bit 3 is to disable the HIGH pin function.  Data Read is an active low output used to transfer data from the memory bus to the local CPU bus. If high it sets the data path from the local CPU bus to the memory bus.  Data Latch Enable is an active high output to enable the local memory                                                                                         |

|   | I 153          | DLE         | A low select high speed operation and a high select low speed operation. Note, Bit 3 in Configuration Register 0 needs to enable the HIGH pin function. The default state of Bit 3 is to disable the HIGH pin function.  Data Read is an active low output used to transfer data from the memory bus to the local CPU bus. If high it sets the data path from the local CPU bus to the memory bus.  Data Latch Enable is an active high output to enable the local memory data buffer.                                                                            |

|   | I 153<br>I 138 | DLE<br>HIGH | A low select high speed operation and a high select low speed operation. Note, Bit 3 in Configuration Register 0 needs to enable the HIGH pin function. The default state of Bit 3 is to disable the HIGH pin function.  Data Read is an active low output used to transfer data from the memory bus to the local CPU bus. If high it sets the data path from the local CPU bus to the memory bus.  Data Latch Enable is an active high output to enable the local memory data buffer.  Tie to high for proper operation.  Local Memory Enable signal. It is used |

|      | <b>                                      </b> |        |                                                                                                                                                               |

|------|-----------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                               |        | used to gate the 8254 compatible tone signal of the 82C206 to the speaker.                                                                                    |

| 0 1  | 30                                            | KBDCS* | 8042 Keyboard Controller chip select is an active low.                                                                                                        |

| 0 1: | 28                                            | ASRTC  | Address Strobe to Real Time Clock is an active high signal used on the 82C2O6.                                                                                |

| 0 1  | 27                                            | GATE2  | Timer Gate 2 is an active high output that enables the 8254 counter timer in the 82C206 to enable the tone signal for the speaker.                            |

| I 8  | 7                                             | OUT1   | Refresh Request generated by the 82C206. It is activated normally every 15.6us to refresh the DRAMs.                                                          |

| т 7  | 5                                             | RFSH*  | System refresh control. It is an active low open collector output from 82C381_B.                                                                              |

| I 7  | 2                                             | OUT2   | Active high output from 8254 timer. It can be read from Port B.                                                                                               |

| 0 6  | 9                                             | SDIR2* | System Data Bus direction for the high byte. A low sets the data path from the SD bus to the XD bus. A high sets the data path from the XD bus to the SD bus. |

| O 6  | 8                                             | SDIR1* | System Data Bus direction for the low byte. A low sets the data path from the SD bus to the XD bus. A high sets the data path from the XD bus to the SD bus.  |

| 0 6  | 57                                            | SDEN   | System Data Bus (AT bus) buffer enable control. It is active high.                                                                                            |

# Power and Ground

| I | 120,100<br>81,40,20<br>1                                                         |     | +5V    |

|---|----------------------------------------------------------------------------------|-----|--------|

| Ι | 10,19,<br>21,30,<br>41,42,<br>79,80,<br>99,101,<br>111,121<br>122,159<br>160,140 | Vss | Ground |

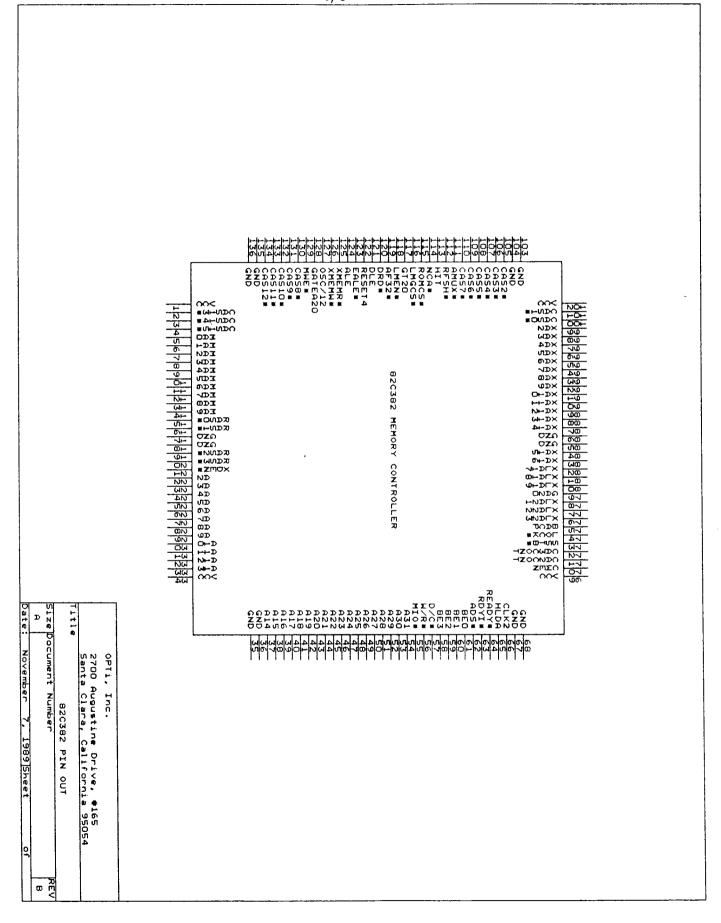

#### 82C382 B 386/AT High Integration Direct Mapped/Page

#### Interleave Controller

#### v1.1, December 12, 1989

1.0 The HiD/386 Chipset consists of the 82C381\_B and 82C382\_B. Together, they are designed to implement high performance, highly integrated, 386/AT Personal Computers running at 25 MHz and 33 MHz. The 82C381\_B provides CPU control and Bus Conversion funtions, while the 82C382\_B provides Direct Mapped Cache Control of any size (note, 64KB design on Development Kit board available) and 1-16MB of Page Interleave Memory Control.

#### 2.0 Overview

The 82C382\_B performs the memory control functions in 386 based AT-compatible systems. The 82C382\_B is designed and optimized for the 25/33 MHZ 386 bus architecture. It supports two types of Memory Subsystem implementations - with and without cache. In either case, the DRAM Memory Controller is a page mode, interleaved memory design, which allows 0 wait state performance on most memory accesses. The benefit for cost-sensitive 386/AT designs is that there is minimum performance penalty for not using Cache; while in a Cache based system, performance is enhanced due to fewer wait states during cache miss cycles.

The 82C382\_B supports a large range of DRAM memory configurations in order to provide flexibility to the OEM in spec'ing his products. It provides shadow RAM support for BIOS ROMs in order to increase system performance; and finally, it includes system cost saving features such as putting DRAM on the local bus, consequently reducing DRAM speed requirements, a single EPROM for BIOS, and address remapping of the unused 256K between 640K to 1M to the top of the system memory.

#### 2.0.1 Page/Interleaved Operation

During DRAM read or write cycles, a row address and a column address is required. In most DRAMs, the row address access time is longer the column address access time. Therefore bus performance can be improved by using page-mode DRAM operation. Memory locations sharing the same row address are in the same memory page, therefore only a new column address is required. In page-mode operation, the row address strobe, RAS\*, can be kept active, and only a new CAS\* needs to be generated, thus reducing memory cycle time. In a four bank configuration, a maximum of four pages of memory can be kept active at a time, since each bank has an independent RAS\*.

The effectiveness of page-mode operation depends heavily on the page-size. A larger page size increases the chance of page hit. Therefore, if the pages for the four banks are concatenated, the effective hit space is quadrupled. Consequently, system performance is further improved. The 82C382\_B interleaves the pages of each bank in order to increase the effective hit space.

The 82C382\_B supports both two and four way page/interleaved mode. If four way interleaved mode is used, the DRAMs used in each of the four banks must be identical.

#### FUNCTIONAL DESCRIPTION

#### 2.1 Introduction

The 82C382\_B is a highly integrated VLSI chip for the INTEL 386 32-bit microprocessor. It interfaces to the 82C381\_B and provides the most cost-effective and highest performance system design for AT-compatible 386 based systems.

The 82C382 B consists of five functional blocks:

- 1) Memory Interface Logic

- 2) Cache Interface Logic

- 3) System Interface Logic

- 4) Configuration Registers

- 5) Address Latches

Each functional block is described in the following sections.

### 2.2 Memory Interface Logic

The local DRAM system can be configured from one upto four banks of 256K X 36-Bits OR 1M X 36-Bits each. Each bank of memory is further divided into four 8-bit banks with one additional bit for parity.

### 2.2.1 DRAM Bank Configuration

The 82C382\_B provides tremendous flexibility in configurations for on-board memory. Table 2.1 lists the possible memory configuration.

|             |       | DRAM TY | PE.        |       |              |        |

|-------------|-------|---------|------------|-------|--------------|--------|

| CFG         | Bank0 | Bank1   | Bank2      | Bank3 | <u>Total</u> | Memory |

|             |       |         |            |       |              |        |

| 1           | 0     | 0       | 0          | 0     | 0            |        |

| 2           | 256K  | 0       | 0          | 0     | 1M           |        |

| 2<br>3      | 256K  | 256K    | 0          | 0     | 2M           |        |

| 4           | 256K  | 256K    | 256K       | 0     | 3M           |        |

| 5           | 256K  | 256K    | 256K       | 256K  | 4 M          |        |

| 4<br>5<br>6 | 1M    | 0       | 0          | 0     | 4 M          |        |

| 7           | 256K  | 1M      | 0          | 0     | 5M           |        |

| 8           | 1M    | 256K    | 0          | 0     | 5M           |        |

| 9           | 256K  | 256K    | 1M         | · 0   | 6M           |        |

| 10          | 256K  | 1M      | 256K       | 0     | 6M           |        |

| 11          | 1M    | 256K    | 256K       | 0     | 6M           |        |

| 12          | 256K  | 256K    | 1M         | 256K  | 7M           |        |

| 13          | 256K  | 1M      | 256K       | 256K  | 7 M          |        |

| 14          | 1M    | 256K    | 256K       | 256K  | 7M           |        |

| 15          | 1M    | 1M      | 0          | 0     | 8M           |        |

| 16          | 256K  | 1M      | 1M         | 0     | 9 <b>M</b>   |        |

| 17          | 1M    | 1M      | 256K       | 0     | 9M           |        |

| 18          | 1M    | 256K    | 1M         | 0     | 9 M          |        |

| 19          | 256K  | 256K    | 1 <b>M</b> | 1M    | 10M          |        |

| 20          | 256K  | 1M      | 1M         | 256K  | 10M          |        |

| 21          | 1M    | 1M      | 256K       | 256K  | 10M          |        |

| 22          | 1M    | 256K    | 1M         | 256K  | 10M          |        |

| 23          | 1M    | 1.M     | 1M         | 0     | 12M          |        |

| 24          | 256K  | 1M      | 1M         | 1M    | 13M          |        |

| 25          | 1M    | 1M      | 1M         | 256K  | 13M          |        |

| 26          | 1M    | 256K    | 1M         | 1M    | 13M          |        |

| 27          | 1M    | 1M      | 1M         | 1M    | 16M          |        |

Page/interleaving is possible only for those combinations with similar pairs or quartet of DRAMs. otherwise, page mode is used. For example, in Cfg4, bank0 and bank1 are 2-way page-interleaved and bank2 is page mode only; while in Cfg 5 bank0-3 are 4-way page-interleaved.

#### 2.2.2 DRAM and EPROM Control Logic

DRAM and EPROM control logic in the 82C382\_B is responsible for the generation of RAS\*, CAS\*, MWE\*, the memory address for DRAM accesses and the generation of ROMCS\* for EPROM accesses. The DRAM read cycle can be completed in 0 to 3 wait states and the write cycle in 0 or 1 wait states as programmed by software in the configuration register. The EPROM can be accessed in either an 8-bit or 16-bit cycle.

# 2.2.3 Shadow RAM and Memory Remapping

Since access to local RAM is much faster than EPROM, the 82C382\_B provides shadow RAM capability. With this feature data from slow devices like ROM and EPROM memories are copied into RAM to speed up memory accesses. The 82C382\_B has built in support for shadowing different areas of memory - system BIOS, video BIOS, and adapter BIOS.

The shadow RAM feature is setup by bits in configuration registers. First, the ROM contents must be copied to the shadow RAM area. Next the shadow RAM enable bit is set in the configuration register. For system BIOS and video BIOS, once the bit is set, the RAM areas become read only. For the adapter BIOS area, the user can select the area to be read only or read/write by setting the write protect bit in the configuration register.

If the adapter BIOS area is not shadowed, the 82C382\_B can remap 256KB of memory (A0000H - BFFFFH and D0000H to EFFFFH) to the top of system memory.

2.2.3.1 Algorithm for turning on Shadow RAM with Rev B.

The Procedure to copy the ROM to Shadow RAM and enable the Shadow RAM is the following:

#### F0000H-FFFFFH

- 1. Read from System BIOS ROM and Write to the Local DRAM since the default state of Bit 7 CFG REG 11H enable this.

- 2. After finishing the copy to local DRAM, in order to write protect the Shadow RAM and enable the future accesses to the Shadow RAM (instead of ROM), reset Bit 7 CFG REG 11H to 0.

#### E0000H-EFFFFH

Case 1. This region is System Board BIOS

- 1. Enable System Board BIOS reads by resetting Bit 5 of CFG REG 11H to 0; enable write to Local DRAM by setting Bit 6 of CFG REG 15H to 1.

- 2. Read from the System Board BIOS and write to Local DRAM.

- 3. Set the appropriate bits <4:7> in CFG REG 12H in order to enable shadow RAM for the selected blocks.

- 4. Set Bit 5 in CFG REG 11H to enable shadow RAM. Write Protect the Shadow RAM by setting Bit 3 in CFG REG 11H to 1.

- 5. Reset Bit 6 in CFG REG 15H to write protect the local DRAM in the C0000H-EFFFFH region.

Case 2. This region is on the AT Channel.

- 1. Enable AT Channel reads by setting Bit 5 of CFG REG 11H to 1 (default state); enable write to Local DRAM by setting Bit 6 of CFG REG 15H to 1.

- 2. Read from the AT Channel and write to Local DRAM.

- 3. Set the appropriate bits <4:7> in CFG REG 12H in order to enable shadow RAM for the selected blocks. Write Protect the Shadow RAM by setting Bit 3 in CFG REG 11H to 1.

- 4. Reset Bit 6 in CFG REG 15H to write protect the local DRAM in the C0000H-EFFFFH region.

#### C0000H-DFFFFH

- 1. Enable write to Local DRAM by setting Bit 6 of CFG REG 15H to 1.

- 2. Read from the AT channel and write to the local DRAM.

- 3. Set the appropriate bits <0:3> in CFG REG 12H for D0000H-DFFFFH and <0:3> in CFG REG 15H for C0000H-CFFFFH in order to enable shadow RAM for the selected blocks. Write Protect the Shadow RAM by setting Bit 4 in CFG REG 11H to 1 for D0000H-DFFFFH and by setting Bit 5 in CFG REG 15H to 1 for C0000H-CFFFFH.

- 4. Reset Bit 6 in CFG REG 15H to write protect the local DRAM in the C0000H-EFFFFH region.

- 2.3 Cache Interface Logic

In order to achieve the highest possible performance, the 82C382\_B supports a Cache interface. This cache is a direct mapped write-through architecture and can be of any size. The user can set two blocks of non-cacheable areas through software programmable registers.

#### 2.4 System Interface Logic

The 82C382\_B generates DDIR\*, DLTACH, LOCAL\*, ENXD\* for system control. DDIR\* controls the direction of data flow in and out of the data buffer inside of the 82C381\_B. DLTACH latches the DRAM data for parity check purpose. LOCAL\* is issued for local memory accesses. XDEN\* is activated for I/O accesses to the internal registers of 82C382 B.

### 2.4.1 Memory Subsystem Design Specifications

The following tables describe the access timings for the Memory subsystem. Note, PWS stands for the Programmed Wait States in the Configuration Register.

a. Page Interleave Mode, Cache not installed, CPU running in Pipeline Mode

| Cycle | Page Active | Page Inactive | Page Miss |

|-------|-------------|---------------|-----------|

| Read  | 0+PWS       | 1+PWS         | 3+PWS     |

| Write | 0+PWS       | 0+PWS         | 2+PWS     |

b. Page Interleave Mode, Cache not installed, CPU running in non-Pipeline Mode

| Cycle | Page Active | Page Inactive | Page Miss |

|-------|-------------|---------------|-----------|

| Read  | 1+PWS       | 2+PWS         | 4+PWS     |

| Write | 1+PWS       | 1+PWS         | 3+PWS     |

c. Direct Mapped Cache installed, CPU always running in non-Pipeline mode

| Cycle | Cache Hit    | Cache Miss   |

|-------|--------------|--------------|

| Read  | 0            | Same as DRAM |

| Write | Same as DRAM | Same as DRAM |

#### d. SRAM Timing for Direct Mapped Cache

| Clock (MHz) | TAG RAM Speed | Cache RAM | Comparator |

|-------------|---------------|-----------|------------|

| 20          | 35ns          | 45ns      | 15ns       |

| 25          | 25ns          | 35ns      | 11ns       |

| 33          | 15ns          | 25ns      | 5.5ns      |

# e. DRAM Timing

| Clock (MHz) | 1 Wait State | 0 Wait State                  |

|-------------|--------------|-------------------------------|

| 20          | 120ns        | 100ns(CAS* access time<=48ns) |

| 25          | 100ns        | 80ns(CAS* access time<=30ns)  |

| 33          | 80ns         | 60ns(CAS* access time<=21ns)  |

# 2.4.2. Direct Mapped Cache Design Options

| Cache<br>Size |    | e TAG Field<br>e Address<br>es | Comparator Address |                     |

|---------------|----|--------------------------------|--------------------|---------------------|

| 32K           | 8  | A3-A14                         | A2-A14             | A15-A23 + Valid Bit |

|               | 16 | A4-A14                         | A2-A14             | A15-A23 + Valid Bit |

| 64K           | 8  | A3-A15                         | A2-A15             | A16-A23 + Valid Bit |

|               | 16 | A4-A15                         | A2-A15             | A16-A23 + Valid Bit |

| 128K          | 8  | A3-A16                         | A2-A16             | A17-A23 + Valid Bit |

|               | 16 | A4-A16                         | A2-A16             | A17-A23 + Valid Bit |

| 256K          | 8  | A3-A17                         | A2-A17             | A18-A23 + Valid Bit |

|               | 16 | A4-A17                         | A2-A17             | A18-A23 + Valid Bit |

| 512K          | 8  | A3-A18                         | A2-A18             | A19-A23 + Valid Bit |

|               | 16 | A4-A18                         | A2-A18             | A19-A23 + Valid Bit |

Note: If you only want to have 0-8MB Cacheable, then the Comparator Address most significant bit A23 can be dropped to A22.

| Comparator  | Address  |     |     | > |              |           |

|-------------|----------|-----|-----|---|--------------|-----------|

|             |          |     |     |   | Exclusive OR | >HIT/Miss |

| TAG Field A | Address> | TAG | RAM | > |              |           |

Cache RAM Address----> CACHE RAM ----> D0-D31

2.4.3 Memory Address Line Contents for different Memory Configurations

Depending on the Memory Configuration programmed in Configuration register 13H, the 82C382\_B puts out different physical address bits out on the MAO-MA9 lines, as shown in the table below. This information may be used to put in dynamic memory configuration into the BIOS.

|                                       | Memory Address Lines - MA |            |           |           |           |           |           |           |           |           |

|---------------------------------------|---------------------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|                                       | 9                         | 8          | 7         | 6         |           |           | 3         |           | 1         | 0         |

| 256K                                  | DRAM                      | , PAG      | E MODI    | <u>E</u>  |           |           |           |           |           |           |

| RAS<br>CAS                            | <u>-</u><br>-             | A19<br>A10 | A18<br>A9 |           |           | A15<br>A6 |           | A13<br>A4 |           | A11<br>A2 |

| <u>1M D</u>                           | RAM,                      | PAGE 1     | MODE      |           |           |           |           |           |           |           |

|                                       | A21<br>A11                | A19<br>A10 | A18<br>A9 |           | A16<br>A7 | A15<br>A6 | A14<br>A5 | A13<br>A4 |           | A20<br>A2 |

| <u>256K</u>                           | DRAM                      | , 2-W      | AY PA     | GE IN     | TERLE     | AVE M     | ODE       |           |           |           |

| RAS<br>CAS                            | -                         | A19<br>A10 | A18<br>A9 | A17<br>A8 |           |           | A14<br>A5 |           |           | A20<br>A2 |

| <u>1M D</u>                           | RAM,                      | 2-WAY      | PAGE      | INTE      | RLEAV     | E MOD     | E         |           |           |           |

|                                       | A22<br>A11                | A19<br>A10 | A18<br>A9 | A17<br>A8 | A16<br>A7 | A15<br>A6 |           | A13<br>A4 |           | A20<br>A2 |

| 256K DRAM, 4-WAY PAGE INTERLEAVE MODE |                           |            |           |           |           |           |           |           |           |           |

| RAS<br>CAS                            | <u>-</u>                  |            | A18<br>A9 | A17<br>A8 |           |           | A14<br>A5 |           |           | A20<br>A2 |

| 1M DRAM, 4-WAY PAGE INTERLEAVE MODE   |                           |            |           |           |           |           |           |           |           |           |

| RAS<br>CAS                            | A22<br>A11                | A19<br>A10 | A18<br>A9 | A17<br>A8 | A16<br>A7 | A15<br>A6 | A14<br>A5 | A23<br>A4 | A21<br>A3 | A20<br>A2 |

2.4.4 Configuring Memory Configuration using DIP Switches

With Rev B, the OEM can set the value of Configuration Reg 13H and the Read and Write Wait states under hardware control. The values are read into the 82C382\_B-B during RESET4# on MAO-MA7. The 386DM Rev 2 schematic shows the logic required.

This feature is necessary only in the following two cases:

-if the OEM does not want to use Dynamic Memory Configuration, which is normally available in most OPTi

configured BIOS like AMI, AWARD or Phoenix's. It is generally recommended to use Dynamic Memory Configuration rather than the Hardware configuration approach because of End-User conveniences.

-if the OEM does not want to use the 82C206 with its built in additional 64 bytes of CMOS RAM for storing configuration data; then the OEM can use a DALLAS Semiconductor style RTC, with some other peripheral chip, since now there is no requirement to store configuration data in battery backed up CMOS RAM.

OEMs who use Generic BIOSes, can use the hardware configuration approach with a software driver, which can be put in the Autoexec.bat file in order to configure the chipset into the proper state.

The Bit and Pin assignments are:

```

MA0 = Pin #5 = CFG REG 13H Bit 0

MA1 = Pin #6 = CFG REG 13H Bit 1

MA2 = Pin #7 = CFG REG 13H Bit 2

MA3 = Pin #8 = CFG REG 14H Bit 5

MA4 = Pin #9 = CFG REG 13H Bit 4

MA5 = Pin #10 = CFG REG 13H Bit 5

MA6 = Pin #11 = CFG REG 13H Bit 6

MA7 = Pin #12 = CFG REG 14H Bit 6

```

In systems that do not use a Configuration Switch, the MAO-MA7 lines should be pulled up during RESET4#. This can be done with pull-up resistors on the MAO-MA7 lines.

#### 2.5 Configuration Registers

There are thirteen configuration registers in the 82C382\_B - REG0-REG12. The registers are accessed through IO ports 22H and 24H. Location 22H is the "Index Address". This address corresponds to the specific register which points to the required data value accessed through port 24H. Thus, reading or writing to a specific register is a two step operation:

- 1) write to I/O port 22H with the register index.