# PAGE MODE MEMORY CONTROLLER SL9350

**PRELIMINARY**

#### **FEATURES**

- 16, 20, 25 MHz Options.

- Enhanced fast page mode design.

- Programmable wait state options.

- Shadow Ram feature.

- Supports 16 M byte of on board memory.

- Can use 256K x 1, 1 Meg x 1, and 256K x 4 DRAMs or a mix.

- Supports 100 ns DRAMs at 16 MHz and 80 ns at 20 MHz.

- Automatic remapping of 640K 1 M RAM to top of the address space.

- Advance CMOS Technology.

- 100 pin Flatpack.

October 1988

LOGICSTAR, Inc. (415) 651-2796 4160-B Technology Drive Fremont, CA 94538

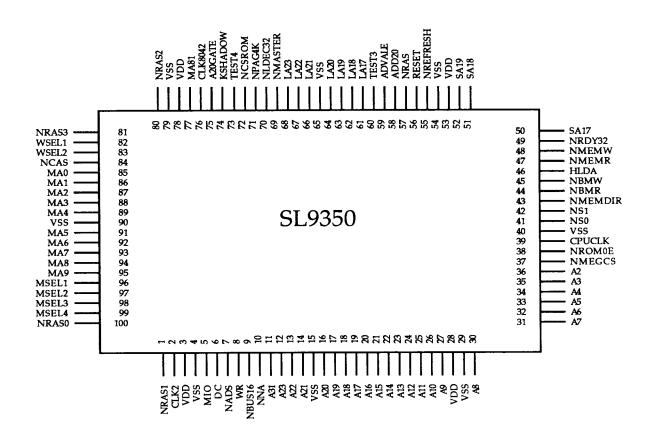

### **PINOUT**

2

SL9350

## **PIN DESCRIPTION SL9350**

| SYMBOL    | PIN                                                      | ТҮРЕ | DESCRIPTION                                                                                                                                                                                     |  |  |  |

|-----------|----------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A2-A16    | 36,35,34,33,<br>32,31,30,27,<br>26,25,24,23,<br>22,21,20 | I    | CPU address bus.                                                                                                                                                                                |  |  |  |

| A17-A23   | 19,18,17,16,<br>14,13,12                                 | I/O  | CPU address bus.                                                                                                                                                                                |  |  |  |

| A31       | 11                                                       | I/O  | CPU address bus.                                                                                                                                                                                |  |  |  |

| A20GATE   | 75                                                       | I/O  | CPUA20 is forced low when A20GATE is low and is transmitted as generated by CPU when A20GATE is high.                                                                                           |  |  |  |

| ADD20     | 58                                                       | 0    | Decoded 20-bit address bit used to generate address decode for 1 M RAMs.                                                                                                                        |  |  |  |

| ADVALE    | 59                                                       | I    | Advanced address latch enable from memory controller. It latches local bus address for the system bus.                                                                                          |  |  |  |

| CLK2      | 2                                                        | I    | Double frequency clock signal for synchronous operation. It is divided by two to get the processor clock.                                                                                       |  |  |  |

| CLK8042   | 76                                                       | I    | 7 MHz clock, generates 10µs RAS TIMOUT.                                                                                                                                                         |  |  |  |

| CPUCLK    | 39                                                       | I    | Derived from CPUCLK2. It is half the frequency of CLK2.                                                                                                                                         |  |  |  |

| DC        | 6                                                        | I    | Status signal. Differentiates between Data and Control instructions.                                                                                                                            |  |  |  |

| HLDA      | 46                                                       | I    | Asserted to signal that the CPU has relinquished control of the bus to the requesting device.                                                                                                   |  |  |  |

| KSHADOW   | 74                                                       | I    | Keyboard controller selectable option for Shadow RAMs.                                                                                                                                          |  |  |  |

| LA17-LA23 | 61,62,63,64,<br>66,67,68                                 | I/O  | Local address bus.                                                                                                                                                                              |  |  |  |

| MA0-MA9   | 85,86,87,88,<br>89,91,92,93,<br>94,95                    | 0    | RAM address bus.                                                                                                                                                                                |  |  |  |

| MA81      | 77                                                       | 0    | RAM address select pin for 1M RAMs.                                                                                                                                                             |  |  |  |

| MIO       | 5                                                        | I    | Memory Input/Output is the signal from the CPU. When high, it indicates a memory cycle, when low it indicates an I/O cycle. It is being used to generate memory and I/O signals for the system. |  |  |  |

## PIN DESCRIPTION SL9350 (Cont'd)

|                     | -           |      |                                                                                                                                                                            |  |  |  |

|---------------------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SYMBOL              | PIN         | ТҮРЕ | DESCRIPTION                                                                                                                                                                |  |  |  |

| MSEL1-4 96,97,98,99 |             | I    | On-board Fast RAM memory size and type select.                                                                                                                             |  |  |  |

| NADS                | 7           | I    | Low assert address status signal. Asserted when Address Bus outputs are valid.                                                                                             |  |  |  |

| NBMR                | 44          | О    | Buffered Memory Read signal.                                                                                                                                               |  |  |  |

| NBMW                | 45          | O    | Buffered Memory Write signal.                                                                                                                                              |  |  |  |

| NBUS16              | 9           | O    | Bus size 16. Activates 16-bit data bus operation; data transferred on the lower 16 bits of the data bus and an extra cycle is provided for transfers of more than 16 bits. |  |  |  |

| NCSROM              | 72          | 0    | Low assert read only memory chip select.                                                                                                                                   |  |  |  |

| NLDEC32             | 70          | I    | Decode signal for on-board local high-speed RAM.                                                                                                                           |  |  |  |

| NMASTER             | 69          | I    | Asserted when an external device has control of the A Bus.                                                                                                                 |  |  |  |

| NMCAS               | 84          | 0    | Memory column address strobe. Asserted when either CPU or DMA is accessing the memory.                                                                                     |  |  |  |

| NMEGCS              | 37          | 0    | Select decode for lower 1M of RAM.                                                                                                                                         |  |  |  |

| NMEMDIR             | 43          | О    | Direction select between D Bus and MD Bus. Read who low, generated by AT system controller SL9010, write when high for non 32-bit.                                         |  |  |  |

| NMEMR               | 47          | I    | Read memory.                                                                                                                                                               |  |  |  |

| NMEMW               | 48          | I    | Write memory.                                                                                                                                                              |  |  |  |

| NNA                 | 10          | I    | Next address. Asserted for address pipe-lining. Enable CPU to put out address and status signals for the next E cycle during the current cycle.                            |  |  |  |

| NPAG4K              | 71          | I    | Active low page size = 4K option; when 1M DRAMs are used. Left high for 256Ks or mixes.                                                                                    |  |  |  |

| NRAS                | 57          | 0    | Low assert Row address strobe.                                                                                                                                             |  |  |  |

| NRAS0-3             | 100,1,80,81 | 0    | Row address strobes for Banks 0,1,2, &3 for the on-board memory. Generated during CPU or DMA cycle for memory access.                                                      |  |  |  |

|                     |             |      |                                                                                                                                                                            |  |  |  |

SL9350

# PIN DESCRIPTION SL9350 (Cont'd)

| SYMBOL   | PIN                        | ТҮРЕ | DESCRIPTION                                                                         |  |  |  |

|----------|----------------------------|------|-------------------------------------------------------------------------------------|--|--|--|

| NRDY32   | 49                         | 0    | Asserted one clock cycle after NNA is asserted at the end of a 32-bit memory cycle. |  |  |  |

| NREFRESH | 55                         | I    | On-board RAM refresh signal. Generated from REFREQ input.                           |  |  |  |

| NROM0E   | 38                         | O    | Enables ROM output during ROM read cycles.                                          |  |  |  |

| NS0,1    | 41,42                      | О    | 80286 compatible status signals for the AT system controller SL9010.                |  |  |  |

| RESET    | 56                         | I    | Active high reset from system controller.                                           |  |  |  |

| SA17     | 50                         | 0    | System Address Bus.                                                                 |  |  |  |

| SA18,19  | 51,52                      | I/O  | System Address Bus.                                                                 |  |  |  |

| TEST3    | 60                         | I    | Optional disable for 684K - 1M [384K] remap.                                        |  |  |  |

| TEST4    | 73                         | I    | Test Pin - Not connected.                                                           |  |  |  |

| VDD      | 3,28,53,78                 | -    | +5V. Power.                                                                         |  |  |  |

| VSS      | 4,15,29,40,<br>54,65,79,90 | -    | 0V. Ground.                                                                         |  |  |  |

| WR       | 8                          | I    | Status signal write when high.                                                      |  |  |  |

| WSEL1,2  | 82,83                      | I    | Wait-state select options.                                                          |  |  |  |

# DC CHARACTERISTICS SL9350

$(TA = 0 \circ C \text{ to } 70 \circ C, VDD = 5V \pm 5\%)$

| PARAMETERS                            | SYMBOL | MIN.   | MAX. | UNITS | CONDITIONS             |

|---------------------------------------|--------|--------|------|-------|------------------------|

|                                       |        |        |      | •     |                        |

| Power Supply Current                  | IDDS   | 0      | 100  | μΑ    | Steady state*          |

| Output High Voltage for Normal Output | Vон    | 4.0    | VDD  | V     | IOH = -2 mA            |

| (IOL = 3.2  mA)                       |        |        |      |       |                        |

| Output High Voltage for Driver Output | Vон    | 4.0    | VDD  | V     | IOH = -2 mA            |

| (IOL = 8 mA)                          |        |        |      |       |                        |

| Output High Voltage for Driver Output | Vон    | 4.0    | VDD  | V     | IOH = - 4 mA           |

| (IOL = 12  mA)                        |        |        |      |       |                        |

| Output High Voltage for Driver Output | Vон    | 4.0    | VDD  | V     | IOH = -8 mA            |

| (IOL = 24  mA)                        |        |        |      |       |                        |

| Output Low Voltage for Normal Output  | Vol    | Vss    | 0.4  | V     | IOL = 3.2  mA          |

| (IOL = 3.2  mA)                       |        |        |      |       |                        |

| Output Low Voltage for Driver Output  | Vol    | Vss    | 0.4  | V     | IOL = 8 mA             |

| (IOL = 8 mA)                          |        |        |      |       |                        |

| Output Low Voltage for Driver Output  | Vol    | Vss    | 0.4  | V     | IOL = 12.0 mA **       |

| (IOL = 12  mA)                        |        |        |      |       |                        |

| Output Low Voltage for Driver Output  | Vol    | Vss    | 0.5  | V     | IOL = 24.0 mA **       |

| (IOL = 24mA)                          |        |        |      |       |                        |

| Input High Voltage for Normal Input   | VIH    | 2.2    |      | V     |                        |

| Input Low Voltage for Normal Input    | VIL    |        | 0.8  | V     |                        |

| Input High Voltage for CMOS Input     | VIH    | 0.7VDD |      | V     |                        |

| Input Leakage Current                 | Ili    | -10    | 10   | μΑ    | VI = 0 - VDD           |

| Input Leakage Current                 | ILZ    | -10    | 10   | μΑ    | Tri-state VI = 0 - VDD |

| Input Pull-up/Down Resistor           | Rp     | 25     | 100  | KΩ    | VIH = VDD              |

#### NOTES:

SL9350 6

<sup>\*</sup> VIH = VDD, VIL = Vss

<sup>\*\*</sup> With Certain restrictions on pin assignment.

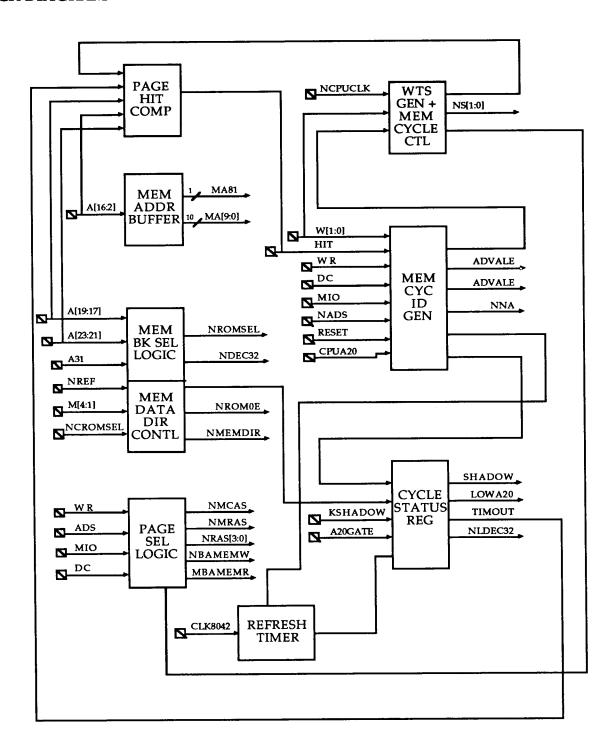

## **BLOCK DIAGRAM**

# PAGE MODE MEMORY CONTROLLEI SL935(

PRELIMINAR'

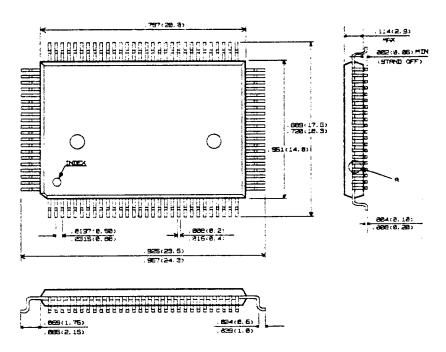

# **Package Information**

#### 100 Pin Flat Pack

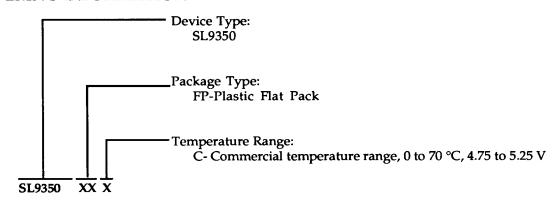

## **ORDERING INFORMATION**

IBM, AT are the trademarks of International Business Machines. Intel is a trademark of Intel Corporation.

LOGICSTAR reserves the right to make changes in specifications at any time without notice. The information furnished by LOGICSTAR in this publication is believed to be accurate and reliable. However, no responsibility is assumed by LOGICSTAR for its use; nor for any infringements of patents or other rights of third parties resulting from its use.

October 1988

Copyright 1988 Logicstar, Inc.

LOGICSTAR Inc. (415) 651-2796 4160-B Technology Dr.

Fremont CA 94538

ي 🛴 ١١٥٠)