# 82230/82231 HIGH INTEGRATION AT\*-COMPATIBLE CHIP SET

- **Fully IBM PC-AT\* System Compatible**

- Two Chip Set Replaces the Major Logic Functions of the IBM PC-AT Motherboard Including the Functions of all the Microprocessor Peripherals:

- 8259A Programmable Interrupt Controller (Master)

- 8259A Programmable Interrupt Controller (Slave)

- 8254 Programmable Interval Timer

- 8284A Clock Generator

- 82284 Clock Generator & Ready Interface

- 82288 Bus Controller

- -8237 DMA Controller (2)

- 6818 Real Time Clock

- 74LS612 Memory Mapper

- Includes:

- Refresh Generation Logic

- Refresh/DMA Arbitration

- Address/Data Bus Control

- 16- to 8-Bit Conversion Logic

- Memory Refresh Controller Drives Up to 4 Mb DRAMs

- Numeric Processor Control Logic

- Up to 12 MHz System Clock Utilizing RAMs with Zero Wait States

- Single +5V Power Supply

- CHMOS Technology

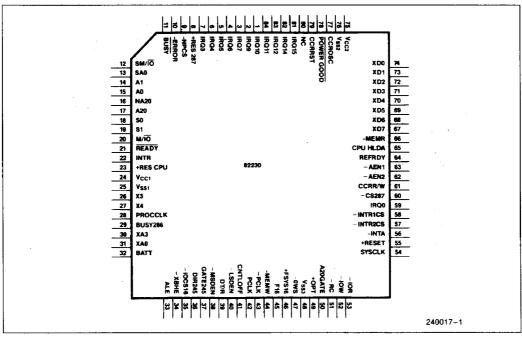

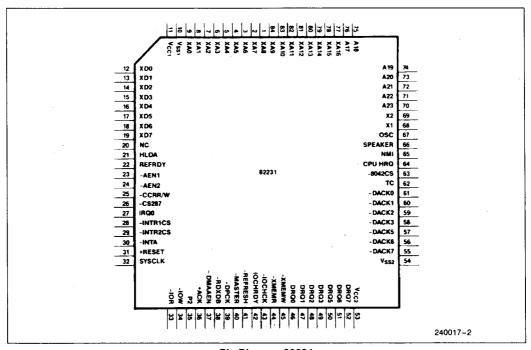

- 84 Pin PLCC Packages (See Packaging Specification Order #231369-004)

1

The 82230 and 82231 are a two-chip implementation of LSI/MSI/SSI logic controlling the IBM Personal Computer AT. The devices provide a low power, highly integrated PC-AT design solution that may be applied to any 80286-based system.

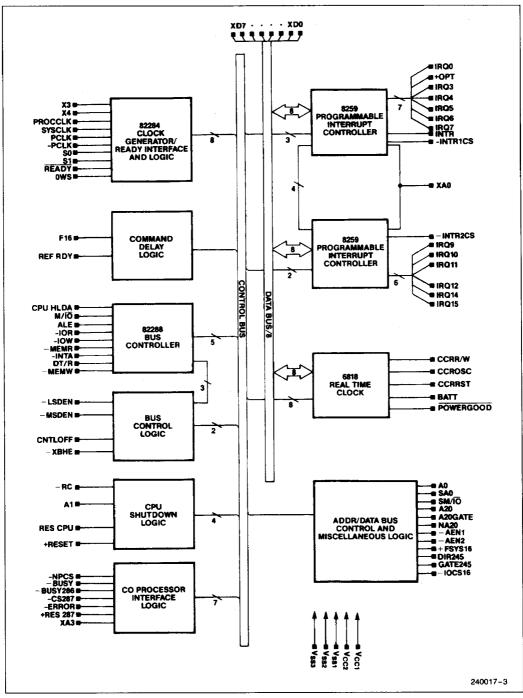

The 82230 performs the functions of the 82284 Clock Generator & Ready Interface, 82288 Bus Controller for 80286 processors, 6818 Real Time Clock/RAM, and the Master-Slave implementation of the dual 8259A Programmable Interrupt Controllers as well as Command Delay, Shut Down, Address/Data Bus Control and Ready Generation logic.

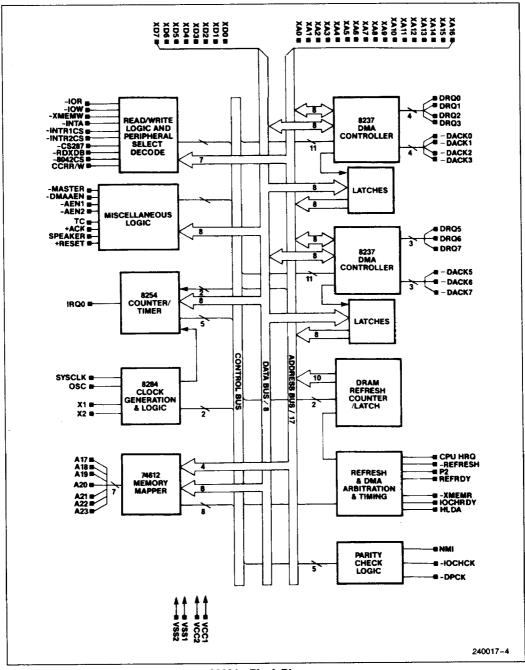

The 82231 includes the 8254 Programmable Interval Timer, 8284A Clock Generator, LS612 Memory Mapper and the dual 8237 DMA Controller functions as well as Refresh Generation and Refresh/DMA Arbitration Logic.

#### NOTE:

"+" and "-" in front of signal names is consistent with PC-AT Documentation.

\*PC-AT is a Trademark of International Business Machine Corporation.

82230-Block Diagram

82231-Block Diagram

Pin Diagram 82230

Pin Diagram 82231

# **82230 PIN DESCRIPTION**

| Symbol Pin<br>No. |          | Туре | Description                                                                                                                                                                                                                                 |  |  |  |

|-------------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AO                | 15       | 1    | ADDRESS 0 input from the CPU. It is used to generate SA0.                                                                                                                                                                                   |  |  |  |

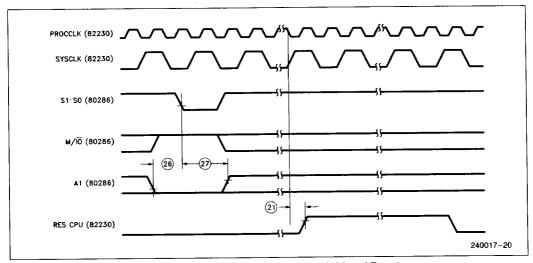

| A1                | 14       | 1    | ADDRESS 1 input from the CPU. It is used in conjunction with M/IO, S0 and S1 to detect a CPU Shutdown condition.                                                                                                                            |  |  |  |

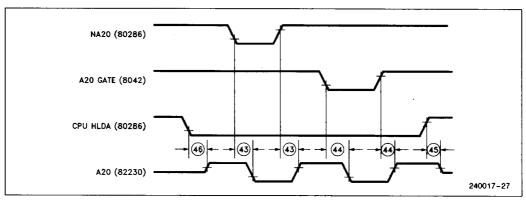

| A20               | 17       | 0    | ADDRESS 20 is the A20 (NA20) line from the CPU after conditioning by the A20GATE signal. During a CPU Hold A20 goes to a high impedance state.                                                                                              |  |  |  |

| A20GATE           | 50       | 1    | A20GATE from the Keyboard Controller is used to force A20 low. When A20GATE is low, A20 on the CPU Address Bus is forced low. When A20GATE is high, A20 follows the CPU Address 20. Tie directly to the P21 Pin of the Keyboard Controller. |  |  |  |

| – AEN2<br>– AEN1  | 62<br>63 |      | ADDRESS ENABLE 1 & 2 from DMA's 1 & 2, respectively. The signal is the result of the DMA's AEN pin NAND'd with — MASTER. Tie directly from the — AEN1 and — AEN2 pins of 82231.                                                             |  |  |  |

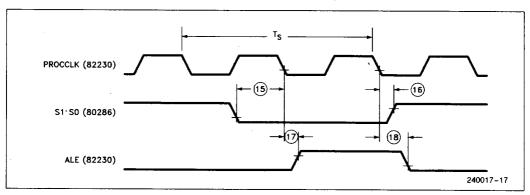

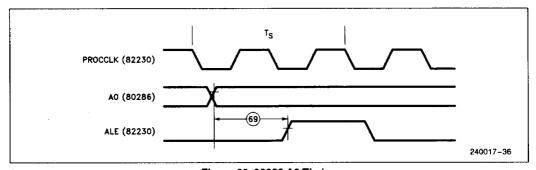

| ALE               | 33       | 0    | ADDRESS LATCH ENABLE is an active high signal that controls the address latches used to hold addresses during bus cycles. ALE is held inactive for Halt bus cycles.                                                                         |  |  |  |

| BATT              | 32       | ı    | BATTERY Power to the Clock Calendar and RAM.                                                                                                                                                                                                |  |  |  |

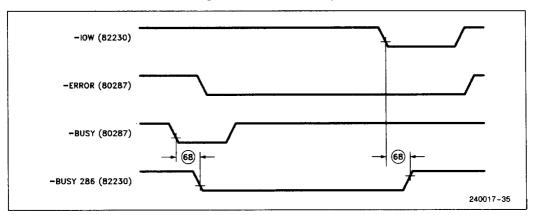

| - BUSY286         | 29       | 0    | <ul> <li>BUSY286 is an active low output indicating the<br/>operating condition of the 80287 coprocessor to the<br/>processor. It is normally tied to the processor — BUSY<br/>pin.</li> </ul>                                              |  |  |  |

| -BUSY             | 11       |      | <ul> <li>BUSY is an active low input from the 80287 to indicate<br/>that it is currently executing a command. It is used to<br/>generate the —BUSY286 output signal.</li> </ul>                                                             |  |  |  |

| CCROSC            | 77       | 1    | CLOCK CALENDAR OSCILLATOR; 32.768 KHz signal.                                                                                                                                                                                               |  |  |  |

| CCRRST            | 79       | "    | CLOCK CALENDAR RESET signal for the Real Time Clock. This is an active low input.                                                                                                                                                           |  |  |  |

| CCRR/W            | 61       | ı    | CLOCK CALENDAR READ/WRITE signal for the Real Time Clock. A high enables READ/WRITE operation to the real-time clock. Tie directly from the CCRR/W Pin of 82231.                                                                            |  |  |  |

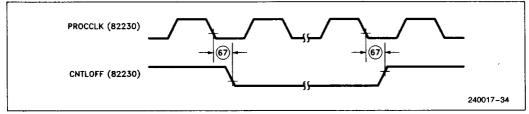

| CNTLOFF           | 41       | 0    | CONTROL OFF is used to enable the low byte data bus latch during byte accesses. This signal is active high.                                                                                                                                 |  |  |  |

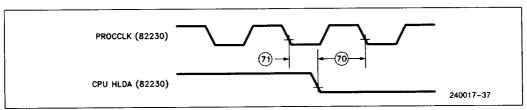

| CPU HLDA          | 65       | I    | CPU HOLD ACKNOWLEDGE is an active high input from the processor. An active condition indicates that the CPU has relinquished the bus to another bus master in the system.                                                                   |  |  |  |

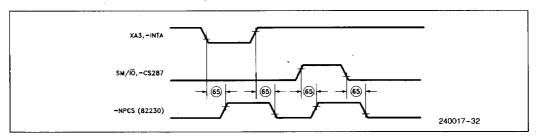

| -CS287            | 60       | I    | CHIP SELECT 287 is used to derive the NPCS signal. Tie directly from the CS287 pin of 82231.                                                                                                                                                |  |  |  |

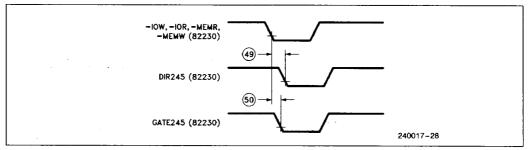

| DIR245            | 36       | 0    | DIRECTION-245 controls the high to low byte and low to high byte conversion during data transfers to and from 8-bit peripherals.                                                                                                            |  |  |  |

| Symbol    | Symbol Pin<br>No. |     | Description                                                                                                                                                                                                                                                                           |  |

|-----------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

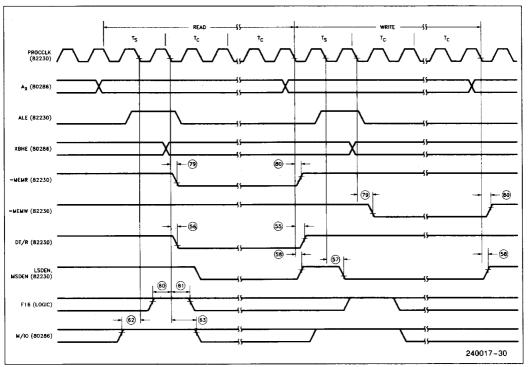

| DT/R      | 39                | 0   | DATA TRANSMIT/RECEIVE establishes the data direction to and from the local data bus. When high, this output signals a CPU write bus cycle. A low indicates a CPU read bus cycle is being performed. This signal is always high when no bus cycle is active.                           |  |

| -ERROR    | 10                | 1   | ERROR is a negative edge triggered input from the numeric processor indicating that an unmasked error condition exists. Tie directly from the —ERROR Pin of the 80287.                                                                                                                |  |

| F16       | 45                | 1   | F16 is an active high input indicating a word memory access. It is used to inhibit command delays for memory accesses.                                                                                                                                                                |  |

| +FSYS16   | 46                | ı   | A latched version of F16.                                                                                                                                                                                                                                                             |  |

| - GATE245 | 37                | 0   | GATE245 is an active low output. When active it enables the bus transceiver that performs the high to low byte conversion with the DIR245 signal. Conversion does not take place if A0 = 0 which indicates a word transfer.                                                           |  |

| -INTA     | 56                | 0   | INTERRUPT ACKNOWLEDGE instructs an interrupting device that its interrupt request is being acknowledged. This signal is active low. — INTA is tri-stated when CPU HLDA is high and CNTLOFF is low. Tie directly to the — INTA pin of 82231.                                           |  |

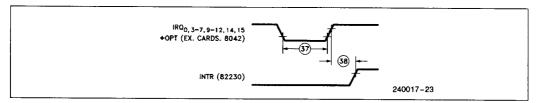

| INTR      | 22                | 0   | INTERRUPT REQUEST is connected directly to the CPU's interrupt pin. INTR is active high, and is generated when a valid interrupt request has been asserted.                                                                                                                           |  |

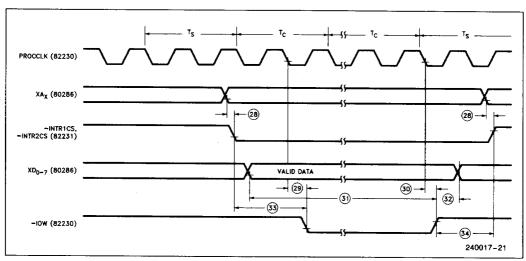

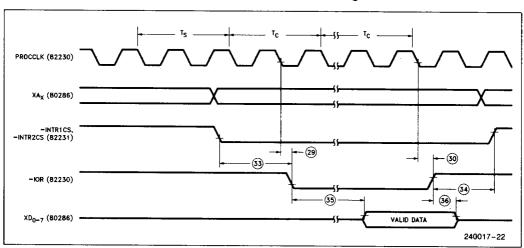

| -INTR1CS  | 58                |     | INTERRUPT CONTROLLER 1 (MASTER) CHIP SELECT is an active low input that is used to select the Interrupt Controller as an I/O device. This allows communication between the master interrupt controller and the CPU via the 'X' Data Bus. Tie directly from the —INTR1CS pin of 82231. |  |

| -INTR2CS  | 57                |     | INTERRUPT CONTROLLER 2 (SLAVE) CHIP SELECT is an active low input that is used to select the Interrupt Controller as an I/O device. This allows communication between the slave interrupt controller and the CPU via the 'X' data bus. Tie directly from the —INTR2CS Pin of 82231.   |  |

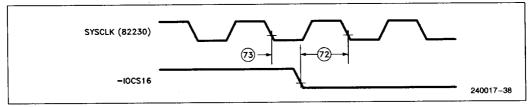

| -IO CS 16 | 35                | l   | I/O 16-BIT CHIP SELECT signals the system that the current data transfer is a 16-bit, one wait-state, I/O cycle. It is derived from an address decode and is an active low signal.                                                                                                    |  |

| -IOR      | 53                | 1/0 | I/O READ signal instructs a selected I/O device to drive its data onto the data bus. The -IOR signal is active low. It is tri-stated when CPU HLDA is high and CNTLOFF if low.                                                                                                        |  |

| -IOW      | 52                | 1/0 | I/O WRITE signal instructs a selected I/O device to read the data on the data bus. The -IOW signal is active low. It is tri-stated when CPU HLDA is high and CNTLOFF is low.                                                                                                          |  |

| Symbol                                                | Symbol Pin Ty                |     | Description                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-------------------------------------------------------|------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IRQ0                                                  | 59                           | ı   | INTERRUPT REQUEST 0 (system timer) receives interrupt requests from channel 0 of the timer/counter. Tie directly from the IRQ0 pin of 82231.                                                                                                                                                                                                                                                        |  |  |  |

| IRQ7-IRQ3<br>IRQ10-IRQ9<br>IRQ12-IRQ11<br>IRQ15-IRQ14 | 3-7<br>1-2<br>83-84<br>81-82 | 1   | INTERRUPT REQUESTS 3-7, 9-12, and 14-15 are used to signal the CPU that an I/O device needs attention. The interrupt requests are prioritized with IRQ9-IRQ12 and IRQ14-IRQ15 having the highest priority (IRQ9 highest) and IRQ3-IRQ7 having the lowest priority (IRQ7 lowest). IRQn signals are active high. The requesting signal is held high until the CPU acknowledges the interrupt request. |  |  |  |

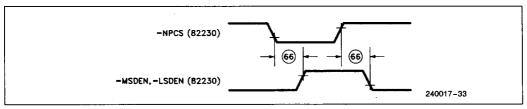

| -LSDEN                                                | 40                           | О   | LEAST SIGNIFICANT DATA ENABLE is an active low output. When active, it enables the transceiver/receiver connected to the least significant byte of the local data bus.                                                                                                                                                                                                                              |  |  |  |

| -MEMR                                                 | 66                           | 1/0 | MEMORY READ COMMAND instructs a memory device to drive data onto the data bus. This signal is active low.  – MEMR is active on all memory read cycles. It is tristated when CPU HLDA is high and CNTLOFF Output is low.                                                                                                                                                                             |  |  |  |

| - MEMW                                                | 44                           | 1/0 | MEMORY WRITE COMMAND instructs a memory device to read the data on the data bus. This signal is active low. — MEMW is active on all memory write cycles. It is tri-stated when CPU HLDA is high and CNTLOFF Output is low.                                                                                                                                                                          |  |  |  |

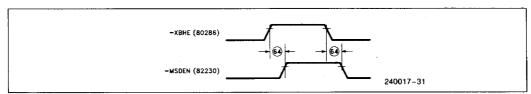

| -MSDEN                                                | 38                           | 0   | MOST SIGNIFICANT DATA ENABLE is an active low output. When active, it enables the transceiver connected to the most significant byte of the local data bus.                                                                                                                                                                                                                                         |  |  |  |

| M/ĪŌ                                                  | 20                           | 1   | MEMORY-INPUT OUTPUT is the M/IO signal from the CPU. When high, it indicates a memory access. When low, it indicates an I/O access. It is used to generate the memory and I/O signals for the system.                                                                                                                                                                                               |  |  |  |

| NA20                                                  | 16                           |     | NA20 is the CPU address 20. 82230 conditions this signal with A20GATE to produce A20. NA20 is tied directly from the CPU A20 output.                                                                                                                                                                                                                                                                |  |  |  |

| NC                                                    | 80                           |     | Do Not Connect.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| - NPCS                                                | 9                            | 0   | NUMERICAL PROCESSOR CHIP SELECT is an active low output used to select the 80287 Numerical Processor. It is tied directly to the NPS1 pin of the 80287.                                                                                                                                                                                                                                             |  |  |  |

| + OPT                                                 | 49                           | ı   | KEYBOARD OUTPUT BUFFER FULL is an active high signal from the Keyboard Controller P24 Pin. The signa is an interrupt request (IRQ1) signaling a full keyboard buffer.                                                                                                                                                                                                                               |  |  |  |

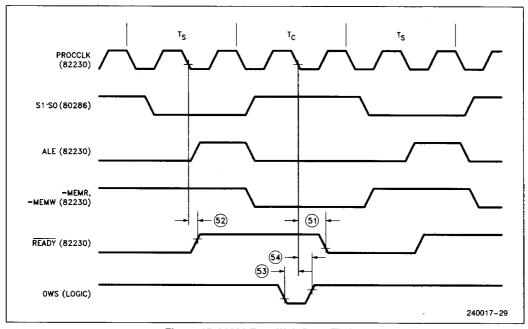

| -ows                                                  | 47                           | ı   | ZERO WAIT STATE option. When pulled active (low), the current processor cycle can be terminated.                                                                                                                                                                                                                                                                                                    |  |  |  |

| Symbol        | Symbol Pin<br>No. |   | Description                                                                                                                                                                                                                                                                                                             |  |  |

|---------------|-------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PCLK          | 42                | 0 | PERIPHERAL CLOCK is half the frequency of PROCCLK. It is used to clock peripheral controllers, specifically XTAL1 of the Keyboard Controller.                                                                                                                                                                           |  |  |

| -PCLK         | 43                | 0 | PERIPHERAL CLOCK INVERTED is the inverse of PCLK. It has been made available specifically for XTAL2 of the Keyboard Controller.                                                                                                                                                                                         |  |  |

| PROCCLK       | 28                | 0 | PROCESSOR CLOCK provides the clock signal for the CPU and 80287 Numerical Processor. It is equal to the frequency of the crystal across pins X3 and X4. Tie directly to the CLK Pins of the 80286 and 80287.                                                                                                            |  |  |

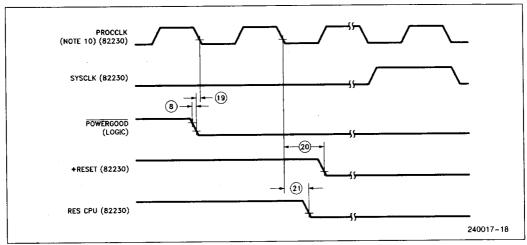

| POWER<br>GOOD | 78                | ļ | POWER GOOD is an active low input that indicates that system power is sufficient to maintain the integrity of the system. If high, it will force a system reset.                                                                                                                                                        |  |  |

| RC            | 51                | ı | RESET CPU from the keyboard controller P21 Pin.                                                                                                                                                                                                                                                                         |  |  |

| READY         | 21                | 0 | READY is an active low output which signals that the current bus cycle is to be completed. S0, S1, POWER GOOD, and 0WS control the READY.                                                                                                                                                                               |  |  |

| REFRDY        | 64                | 1 | REFRESH/IO-CHANNEL-READY is generated by 82231. It is used to preset the READY Interface Asynchronous READY (ARDY).                                                                                                                                                                                                     |  |  |

| + RES 287     | 8                 | 0 | RESET 80287 is the reset signal for the 80287<br>Numerical Processor.                                                                                                                                                                                                                                                   |  |  |

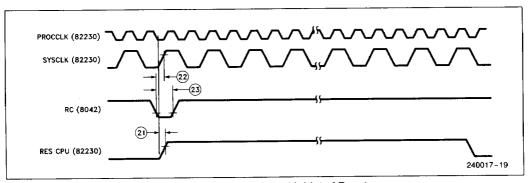

| RES CPU       | 23                | 0 | RESET CPU is the reset signal for the CPU. Active high, RESCPU is generated when either POWERGOOD or RC become active, or when the CPU generates a shut down status by forcing M/IO high. S0, S1 and A1 low. If this signal is initiated by RC, or by M/IO, S0, S1 and A1, it will remain active for 16 PROCCLK cycles. |  |  |

| + RESET       | 55                | 0 | RESET (SYSTEM) is an active high output derived from the POWER GOOD input. + RESET is used to force the system into an initial state. When + RESET is active, READY will also be active (Low).                                                                                                                          |  |  |

| S0, S1        | 18, 19            | I | STATUS inputs from the CPU. The status signals are used by the bus controller to determine the state of the CPU.                                                                                                                                                                                                        |  |  |

| SA0           | 13                | 0 | ADDRESS 0 of the CPU bus. SA0 outputs A0 from the CPU during local CPU cycles. During a CPU Hold SA0 goes to a high impedance state so that another master on the expansion bus can take control. During an interrupt acknowledge this signal will be forced low.                                                       |  |  |

| SM/ĪŌ         | 12                | ı | SYSTEM MEMORY-INPUT OUTPUT is the M/IO signal from the CPU, conditioned by ALE.                                                                                                                                                                                                                                         |  |  |

| SYSCLK        | 54                | 0 | SYSTEM CLOCK is the result of PROCCLK divided by two, thus synchronized to the processor's T-states. It may be used to clock peripheral devices that must be synchronized to the CPU.                                                                                                                                   |  |  |

| Symbol                                                   | Symbol Pin No. |     | Description                                                                                                                                                                                                                                                               |  |  |  |

|----------------------------------------------------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>CC1</sub><br>V <sub>CC2</sub>                     | 24<br>75       |     | POWER: +5V supply.                                                                                                                                                                                                                                                        |  |  |  |

| V <sub>SS1</sub><br>V <sub>SS2</sub><br>V <sub>SS3</sub> | 25<br>76<br>48 |     | GROUND.                                                                                                                                                                                                                                                                   |  |  |  |

| X3<br>X4                                                 | 26<br>27       | 0   | CRYSTAL inputs used to generate PROCCLK and SYSCLK. The crystal frequency must be twice the processor clock frequency. Alternatively, an oscillator may be connected to X3.                                                                                               |  |  |  |

| XA0                                                      | 31             | 1   | ADDRESS 0 is used by the 8259A to decipher command words the CPU issues. XA0 works in conjunction with the read, write and chip select signals to the interrupt controller in determining whether the CPU wishes to issue a command or read the status of the controller. |  |  |  |

| хаз                                                      | 30             | ı   | ADDRESS 3 is used for generating the chip select and reset signals for the 80287.                                                                                                                                                                                         |  |  |  |

| -XBHE                                                    | 34             | 1/0 | BUS HIGH ENABLE is an active low signal which is used by 82230 to generate the MSDEN signal.                                                                                                                                                                              |  |  |  |

| XD7-XD0 67-74 I/O                                        |                | 1/0 | Data Bus 0-7 for the peripheral bus. The direction of the bus is determined by the -RDXDB signal from 82231. It is used by the 8259A to decipher command words the CPU issues.                                                                                            |  |  |  |

# **82231 PIN DESCRIPTION**

| Symbol           | Symbol Pin<br>No. |   | Description                                                                                                                                                                                                                                |  |  |

|------------------|-------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| -8042CS          | 63                | 0 | 8042 CHIP SELECT is an active low, chip select signal for the Keyboard Controller.                                                                                                                                                         |  |  |

| A23-A17          | 70-76             | 0 | A23-A17 are the Address bits 17-23 of the CPU Address bus. They are outputs directly from the Memory Mapper Pins MO1-MO7 and supply page information during DMA transfers. These outputs are tri-stated unless HLDA and — MASTER are high. |  |  |

| + ACK            | 36                | 0 | ACKNOWLEDGE is an active low output. When active it enables the bus transceiver between the system and peripheral (XBUS) bus. + ACK is used in conjunction with - RDXDB which controls the direction of the bus transceiver.               |  |  |

| – AEN1<br>– AEN2 | 23<br>24          | 0 | ADDRESS ENABLE FROM DMAs 1 & 2, respectively. The signal is the result of the DMA's AEN signal NAND'd with — MASTER. Tie directly to the — AEN1 and — AEN2 pins of 82230.                                                                  |  |  |

| CCRR/W           | 25                | 0 | CLOCK CALENDAR READ/WRITE signal for the real-<br>time clock. A high enables READ/WRITE operations to<br>the real-time clock. Tie directly to the CCRR/W pin of<br>82230.                                                                  |  |  |

| CPU HRQ          | 64                | 0 | CPU HOLD REQUEST is an active high output indicating a DMA request to the CPU. It is also active during refresh cycles. CPU HRQ is normally connected to the 80286 HOLD Pin.                                                               |  |  |

| Symbol               | Symbol Pin No. |     | Description                                                                                                                                                                                                                                                                                                     |  |  |

|----------------------|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| -CS287               | 26             | 0   | CHIP SELECT 287 is used by 82230 to derive the —NPCS signal. Tie directly to the —CS287 pin of 82230.                                                                                                                                                                                                           |  |  |

| -DACK0-3<br>-DACK5-7 | 61-58<br>57-55 | 0 0 | DMA ACKNOWLEDGE 0-3 and 5-7 are used to acknowledge DMA requests (DRQ0-3 & 5-7). The output signal is an active low.                                                                                                                                                                                            |  |  |

| -DMAAEN              | 37             | 0   | DMA ADDRESS ENABLE is an active low signal and is active when an I/O device is making a DMA access to system memory or during refresh.                                                                                                                                                                          |  |  |

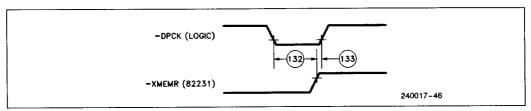

| - DPCK               | 39             | I   | DATA PARITY CHECK is used to generate NMI. This input is active low.                                                                                                                                                                                                                                            |  |  |

| DRQ0-3<br>DRQ5-7     | 46-49<br>50-52 | 1   | DMA REQUEST 0-3 & 5-7 are synchronous channel requests used by peripheral devices and I/O processors to gain DMA service. The requests are prioritized with DRQ0 having the highest and DRQ7 having the lowest priorities. A DRQ line must be held active (high) until the corresponding DACK line goes active. |  |  |

| HLDA                 | 21             | 1   | HOLD ACKNOWLEDGE is an active high input that is equivalent to CPU HLDA. An active condition inidicates that the CPU has relinquished the bus to another bus master in the system.                                                                                                                              |  |  |

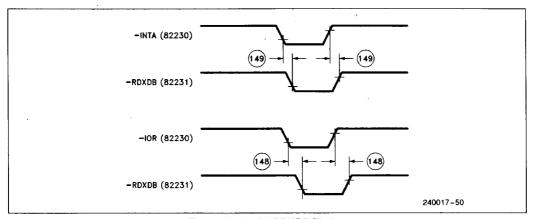

| - INTA               | 30             | l   | INTERRUPT ACKNOWLEDGE instructs an interrupting device that its interrupt is being acknowledged, and the device may place its interrupt vector onto the data bus. This input signal is active low. —INTA is used by 82231 in the generation of —RDXDB. Tie directly from 82230 Pin 56.                          |  |  |

| -INTR1CS             | 28             | 0   | INTERRUPT CONTROLLER 1 (MASTER) CHIP SELECT is an active low output that is used by 82230 to select the Interrupt Controller as an I/O device. This allows communication between the Master Interrupt Controller and the CPU via the 'X' Data Bus. Tie directly to the —INTR1CS pin of 82230.                   |  |  |

| -INTR2CS             | 29             | 0   | INTERRUPT CONTROLLER 2 (SLAVE) CHIP SELECT is an active low output that is used by 82230 to select the Interrupt Controller as an I/O device. This allows communication between the Slave Interrupt Controller and the CPU via the 'X' Data Bus. Tie directly to the — INTR2CS Pin of 82230.                    |  |  |

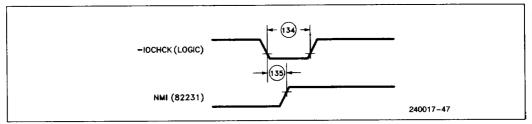

| -IOCHCK              | 43             | l   | I/O CHANNEL CHECK is an active low input. It is used to indicate an uncorrectable system error. It provides the system with parity error information about memory or devices on the I/O channel.                                                                                                                |  |  |

| IOCHRDY              | 42             | ı   | I/O CHANNEL READY is generated by an I/O device When low it indicates a 'not ready' condition and force the insertion of wait states in I/O or Memory accessed by the I/O device. When active (high), it will allow the completion of a memory or an I/O access by the I/O device.                              |  |  |

| Symbol   | Pin<br>No. | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|----------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| -IOR     | 33         | 1/0  | I/O READ signal instructs a selected I/O device to drive its data onto the data bus. The —IOR signal is active low. It is used for data transfers between the CPU and I/O devices and by DMA transfers.                                                                                                                                                                                                     |  |  |

| -IOW     | 34         | 1/0  | I/O WRITE signal instructs a selected I/O device to read the data on the data bus. The —IOW signal is active low. It is used for data transfers between the CPU and I/O devices and by DMA transfers.                                                                                                                                                                                                       |  |  |

| IRQ0     | 27         | 0    | INTERRUPT REQUEST 0 (System Timer) from Channel 0 of the Timer/Counter. Tie directly to the IRQ0 Pin of 82230.                                                                                                                                                                                                                                                                                              |  |  |

| - MASTER | 40         | 1    | <ul> <li>MASTER is an active low input used in conjunction with a DRQ line to gain control of the system. A DMA controller or processor on the I/O channel may issue a DRQ to a DMA channel and receive a — DACK. The I/O processor may then activate — MASTER which will allow it to control the system address, data, and control lines.</li> </ul>                                                       |  |  |

| NC       | 20         |      | Do Not Connect.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| NMI      | 65         | 0    | NON-MASKABLE INTERRUPT is an active high output that is connected to the CPU NMI pin.                                                                                                                                                                                                                                                                                                                       |  |  |

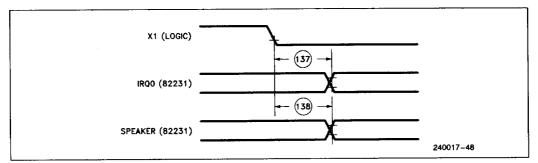

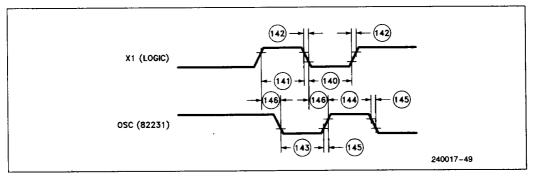

| OSC      | 67         | 0    | OSCILLATOR output is the clock frequency of the crystal connected across X1-X2. It is the OSC output from the Clock Generator.                                                                                                                                                                                                                                                                              |  |  |

| P2       | 35         | 0    | P2 is an active high output indicating that a valid refresh address is available on the XA bus.                                                                                                                                                                                                                                                                                                             |  |  |

| RDXDB    | 38         | 0    | READ X-DATA BUS controls the direction of the bidirectional buffer between the least significant byte of the 'S' Data Bus and the 'X' Data Bus. — RDXDB is used in conjunction with + ACK to control XBUS activity. When + ACK is active (low) and — RDXDB is low, data is to be read from the peripheral bus. When + ACK is active (low) and — RDXDB is high, data is to be written to the peripheral bus. |  |  |

| REFRDY   | 22         | 0    | REFRESH/IO-CHANNEL-READY is generated by<br>+ REFRESH OR'd with IOCHRDY. It is used by 82230<br>to preset the Clock Generator & Ready Interface<br>Asynchronous Ready (ĀRDY).                                                                                                                                                                                                                               |  |  |

| -REFRESH | 41         | 1/0  | REFRESH is an active low output used to initiate a refresh cycle for the dynamic RAMs.                                                                                                                                                                                                                                                                                                                      |  |  |

| + RESET  | 31         | ŀ    | RESET (SYSTEM) is an active high input from 82230.<br>+ RESET is used to force 82231, as well as the system<br>into an initial state. Tie directly from 82230 Pin 55.                                                                                                                                                                                                                                       |  |  |

| SPEAKER  | 66         | 0    | SPEAKER DATA is an output of the Programmable interval timer tone signal used to drive the speaker.                                                                                                                                                                                                                                                                                                         |  |  |

| SYSCLK   | 32         | ı    | SYSTEM CLOCK input from 82230. It is used to synchronize 82231 to the system. Tie directly from 82230 SYSCLK Pin.                                                                                                                                                                                                                                                                                           |  |  |

| TC       | 62         | 0    | TERMINAL COUNT provides a pulse when the terminal count for any DMA channel is reached.                                                                                                                                                                                                                                                                                                                     |  |  |

| Symbol                               | Symbol Pin No.     |                 | Description                                                                                                                                                                                                 |  |  |

|--------------------------------------|--------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>CC1</sub><br>V <sub>CC2</sub> | 11<br>53           |                 | POWER: +5V supply.                                                                                                                                                                                          |  |  |

| V <sub>SS1</sub><br>V <sub>SS2</sub> | 10<br>54           |                 | GROUND.                                                                                                                                                                                                     |  |  |

| X1<br>X2                             | 68<br>69           | 0               | CRYSTAL inputs for the internal oscillator used to generate clocking for I/O devices. A parallel resonant fundamental frequency mode crystal is required. An alternative oscillator may be connected to X1. |  |  |

| XA8-XA0<br>XA9<br>XA16-XA10          | 1-9<br>84<br>77-83 | 1/0<br>1/0<br>0 | XBUS ADDRESSES 0-16 are the peripheral addresses for the local I/O bus.                                                                                                                                     |  |  |

| XD0-XD7                              | 12–19              | 1/0             | Data Bus 0-7 for the peripheral bus. The direction of the bus is determined by the - RDXDB signal from 82231.                                                                                               |  |  |

| -XMEMR                               | 44                 | 1/0             | MEMORY READ signal indicating a DMA read operation from peripheral devices or memory.                                                                                                                       |  |  |

| ~XMEMW                               | 45                 | 0               | MEMORY WRITE signal indicating a DMA write operation to peripheral devices or memory. It is tri-stated except during DMA transfers.                                                                         |  |  |

## **FUNCTIONAL DESCRIPTION**

#### Introduction

The 82230 and 82231 are a two-chip implementation of LSI/MSI/SSI logic controlling the IBM Personal Computer AT. The devices provide a low power, highly integrated PC-AT design solution that may also be applied to any 80286-based system. With the 82230 and 82231, a PC-AT system can be designed to operate at 12 MHz with zero wait state RAM accesses.

These standard cell products contain most of the logic peripheral to the microprocessors and memory on the "standard" AT motherboard. The LSI peripherals which support the AT design reside as supercells on the 82230/82231 chips. These peripherals are compatible with the products they replace and the user should refer to the standard product data sheets for additional information on the operation of these devices.

The PC-AT schematics in the IBM PC-AT Technical Reference Manual are also a good source of information about the 82230/82231's internal logic.

The 82230 performs the functions of the 82284 Clock Generator & Ready Interface, 82288 Bus Controller, 6818 Real Time Clock/RAM, and the Master-Slave implementation of the dual 8259A Programmable Interrupt Controllers as well as Command Delay, Shut Down, Address/Data Bus Control and Ready Generation logic.

The 82231 includes the 8254 Programmable Interrupt Timer, 8284A Clock Generator, LS612 Memory Mapper and the dual 8237 DMA Controller functions as well as Refresh Generation and Refresh/DMA Arbitration Logic.

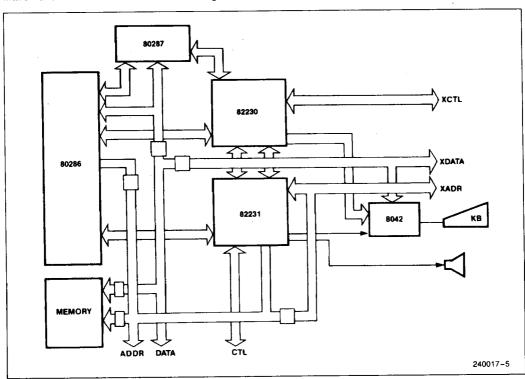

#### PC-AT BLOCK DIAGRAM

The block diagram is shown below in Figure 1 which shows the 82230 and 82231 being used in a PC-AT compatible design. Note how the basic structure of the PC-AT is retained in the design. The five address busses and four data busses are present. The 82230 and 82231 'sit' on the X Address and Data Busses and monitor the status and control line outputs from the 80286 in order to operate the peripheral supercells.

Figure 1. Block Diagram of 82230 and 82231 for PC/AT

A brief description of each of the basic PC-AT busses is included in order to show how a system design using the 82230/82231 allows for the retention of the PC-AT bus structure.

#### **ADDRESS BUSSES**

The 82230/82231 allows a straightforward PC-AT design which preserves the five basic address busses. System designers can interact with these busses, create new busses, or eliminate busses, depending upon design objectives. Each bus must be independently buffered and separated by buffers/latches. Most handshake signals are generated by the 82330/82331.

The Local Address Bus is comprised of the 24 address pins emanating from the 80286. External buffers are required in order to separate the local address bus from the system address bus. A0, however, is input directly into the 82230 and is used in conjunction with XBHE in order to enable the appropriate memory bank. The 82230 inputs CPU address bit NA20 and outputs A20.

The System Address Bus is the main AT address bus. This is a latched version of the local address bus, and is a 20-bit bus. SA0 is an output of the 82230 and SA1-SA19 are latched from the local address bus. The latch signal is ALE, which is generated by the 82288 supercell in the 82230. CPU HLDA, generated by the 80286 and active high, should be used as the output enable signal.

The Memory Address Bus applies to the RAM on the PC-AT system board only. It is a multiplexed version of the System Address Bus with nine address lines, MAO-MA8. External multiplexers are used to generate the row and column addresses.

The X Address Bus is separated from the System Address Bus. The X address lines are input/outputs into the 82230/82231. The X Address Bus is a motherboard address bus which is used to address ROM (BIOS) and motherboard I/O. In addition, the X Address Bus generates addresses for DMA and memory refresh.

The L Address Bus is an unlatched 7-bit address bus. LA17-LA23 can allow a PC-AT design up to 16 MBytes of address space. The L Address Bus should be made available at the expansion bus connector.

#### **DATA BUSSES**

The Local Data Bus is the name for the data bus lines emanating directly from the 80286. The local data bus has 16 lines, D0-D15. Because the 80286 can do word and byte transfers and because word transfers need not be aligned, it is necessary to design a bus interface which differentiates between the high bus byte and the low bus byte.

The System Data Bus is the main data bus of a PC-AT system and interfaces with all other data busses. The 82230 and 82231 are designed to control these interfaces in order to simplify system design and maximize bus flexibility.

The Memory Data Bus interfaces both DRAM and ROM. It is a 16-bit bus and connects with the System Data Bus through buffers.

The X Data Bus is the bus intended primarily for system board I/O functions. It interfaces to functions such as the DMA controllers, Interrupt controllers, Keyboard controller, and Real Time Clock.

#### 82230/82231 Interface

The 82230 and 82231 are relatively independent of each other; the 82230 generates most of the timing and control signals and the 82231 controls the X Address Bus for DMA and refresh. Both chips have additional functions but because of the desire to partition the system design such that the 82230 and the 82231 could be assembled in low cost 84-pin PLCC packages, each chip relies on the other for certain functions. This entails introducing dedicated interface signals between the 82230 and 82231 into a system design. The 82230/82231 interface requires 14 pins on each device and these pins are described below.

- REFRDY is generated by the 82231 and used to tell the 82230 to insert wait-states in response to the 82231 input IOCHRDY. IOCHRDY is active high.

- AEN1 and AEN2 are signals generated by the 82231 which indicate DMA byte (AEN1) or word (AEN2) transfers, and are used by the 82230 to generate bus buffer control signals.

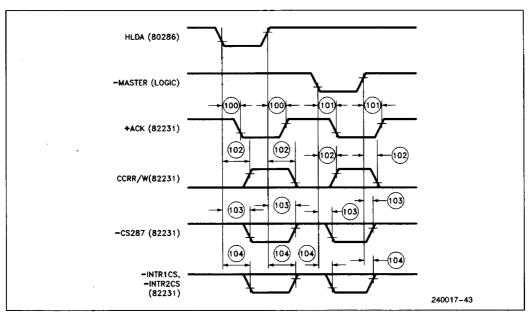

- CCRR/W is generated by the 82231 and used by the 82230 as part of the 6818 chip select.

- INTR1CS and INTR2CS are generated by the 82231 and used by the 82230 as the interrupt controller chip selects.

- CS287 is generated by the 82231 and is used by the 82230 to generate 80287 control signals.

- IRQ0 is the output of the 8254 timer 0 on the 82231 and is connected to interrupt request 0 on the master interrupt controller in the 82230.

1

- + RESET is generated by the 82230 in response to POWERGOOD and is used by the 82231 for initialization.

- SYSCLK is PROCCLK divided by two.

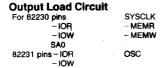

- INTA, -MEMR, -IOR, and -IOW are commands generated by the 82230 in response to the 80286 status inputs S0 and S1, and are used by the 82231 as basic system commands.

## **Coprocessor Interface**

The 82230 contains a coprocessor interface logic block to allow interfacing with an 80287 math coprocessor. The coprocessor interface includes the IBM PC-AT compatible error handling hardware.

## **Memory Operations**

When the 82230 and 82231 are used in a PC-AT system design, the system can be designed to operate with the full 16 MBytes of memory that the 24 address lines of the 80286 allow.

The 82230/82231 chipset normally operates with one wait state inserted for memory operations and four wait-states inserted for I/O operations. The number of wait states may be increased for slow memory or I/O devices, or decreased if use of high-speed memory or I/O devices is desired in order to provide higher system performance.

During normal operation, the number of ROM accesses are relatively few compared to RAM accesses, so ROM subsystem speed does not significantly affect system performance. When designing high performance PC-AT systems, it should be verified that the ROM subsystem is fast enough for operation. Note also that older versions of the IBM BIOS may not operate in systems faster than 8 MHz. Modifications of both RAM and ROM subsystem performance are covered in detail in the Intel 286EX Application Note.

## **System Clocks and Oscillators**

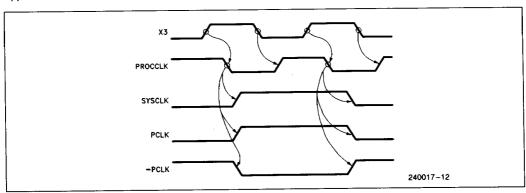

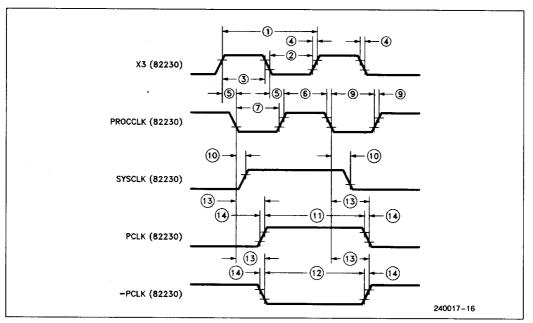

Because of the high level of integration of the 82230/82231, several different clock frequencies are present on the chips. Figure 2 shows the relationships between the various clock signals.

PROCCLK is the main system clock which is used in a PC-AT system to generate all the basic system and bus timings. The clock is generated by the 82230 and operates at twice the system clock frequency. See Table 1 for processor clock capacitance. The tolerance of the PROCCLK oscillator is independent of the 82230/82231 and is primarily determined by the requirements of the 80286 and 80287 processors. For reliable operation at the specified  $V_{\rm DD}$  and temperature condition, the processor timing specifications must not be exceeded.

Table 1. Recommended Fundamental Mode Crystal Characteristics and Recommended Load Capacitance for PROCCLK

| Oscillator | Crystal<br>Freq. | C <sub>LOAD</sub> (pF) | C <sub>IN</sub> (pF)<br>X3 | C <sub>OUT</sub> (pF)<br>X4 |

|------------|------------------|------------------------|----------------------------|-----------------------------|

| PROCCLK    | 12 MHz           | 20                     | 30                         | 10                          |

| PROCCLK    | 16 MHz           | 20                     | 30                         | 10                          |

| PROCCLK    | 20 MHz           | 20                     | 27                         | 8                           |

| PROCCLK    | 24 MHz           | 20                     | 22                         | 8                           |

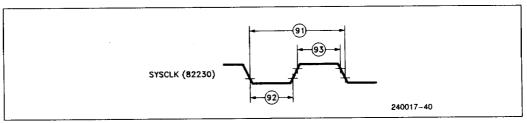

SYSCLK is PROCCLK divided by two, and should be used as the expansion bus clock. SYSCLK is an output of the 82230. To ensure compatibility with expansion cards, SYSCLK should not be above 8 MHz.

X1 is an input to the 82231 which is 12 times the frequency used to clock the three counters in the 8254 timer on the 82231. In order to be compatible with AT hardware and software, it should be a 14.318 MHz fundamental mode crystal with C<sub>LOAD</sub> = 32 pF, and a 27 pF capacitor should be placed in series with the crystal. Alternately, a 14 MHz funda-

Figure 2. 82230 Clock Timing

mental mode crystal (C<sub>LOAD</sub> = 32 pF) may be trimmed with a 5-50 pF trimmer capacitor in series for high accuracy applications such as NTSC or RS170 video-compatibility with chroma colorburst.

Note that the trim cap must be adjusted with a low-capacitance nylon or teflon tuning wand for accurate trimming. Tolerance for this clock is 0.1% or less for non-video or non time-critical use, 0.01% or greater if used for video color-burst or time-critical applications.

The CCR clock is the low-frequency oscillator used to clock the 6818 Clock/Calendar/RAM on the 82230. CCROSC tolerance is variable and dependent upon real-time clock accuracy requirements. See Table 2 for CCROSC clock tolerance and accuracy.

Table 2. CCROSC Tolerance/Accuracy

| Tolerance           | Accuracy                               |

|---------------------|----------------------------------------|

| 0.001% or<br>10 ppm | 5 minutes/year trimming required       |

| 0.01% or<br>100 ppm | 1 minute/week no<br>trimming required  |

| 0.02% or<br>200 ppm | 2 minutes/week no<br>trimming required |

| 0.05% or<br>500 ppm | 5 minutes/week no trimming required    |

#### **EXTERNAL OSCILLATORS**

External CMOS output drive oscillators may be used for either PROCCLK or OSC. Simply connect the external oscillator outputs to PROCCLK inputs X1 or X3. TTL output oscillators may be used if the output drive  $V_{OH}$  is greater than 4.1V; pull-up resistors will generally suffice. The oscillator invertor outputs X2 and X4 may be left open, or may be used to drive one moderate rise-time CMOS load if needed.

#### **ABSOLUTE MAXIMUM RATINGS\***

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

## 82230/82231 DC CHARACTERISTICS

$V_{CC} = 5V \pm 5\%$ ,  $V_{BAT} = 2.8V$  to  $V_{CC}$ ,  $T_A = 0$ °C to +70°C

| Parameter                                                                              | Conditions                                                        | Min                      | Max      | Units    |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|----------|----------|

| V <sub>IL</sub>                                                                        |                                                                   |                          | 0.5      | ٧        |

| V <sub>IH</sub>                                                                        |                                                                   | 2.0                      |          | ٧        |

| V <sub>IL</sub><br>82230 Pins 26, 77, 78, 79<br>82231 Pins 41, 42, 68                  |                                                                   |                          | 0.5      | ٧        |

| V <sub>IH</sub><br>82230 Pins 26, 77, 78, 79<br>82231 Pins 41, 42, 68                  |                                                                   | V <sub>CC</sub> - 0.5    |          | ٧        |

| V <sub>IH</sub><br>82230 Pin 47                                                        |                                                                   | V <sub>CC</sub> - 0.5(1) |          | V        |

| I <sub>IO</sub>                                                                        | V <sub>IN</sub> = 0                                               | -100                     |          | μΑ       |

| l <sub>10</sub><br>82230 Pins 26, 77, 78, 79                                           | $V_{IN} = 0$                                                      | -10                      |          | μА       |

| 111                                                                                    | $V_{IN} = V_{CC}$                                                 |                          | 10       | μΑ       |

| I <sub>OH</sub><br>Except for 82231 Pin 41 <sup>(2)</sup>                              | V <sub>OH</sub> = 2.4                                             |                          | -4       | mA       |

| loL                                                                                    | $V_{OL} = 0.45V$                                                  | 4                        |          | mA       |

| I <sub>OL</sub><br>82230 Pins 13, 28, 44, 52, 53<br>54, 56, 66<br>82231 Pins 33 34, 67 | V <sub>OL</sub> = 0.45V                                           | 16                       |          | mA       |

| I <sub>OL</sub><br>82231 Pin 41                                                        | $V_{OL} = 0.45V$                                                  | 18                       |          | mA       |

| loz                                                                                    | $V_O = 0$ to $V_{CC}$                                             | -10                      | +10      | μА       |

| I <sub>CC</sub> 82230                                                                  | F = 10 MHz<br>F = 12 MHz                                          | -                        | 55<br>60 | mA<br>mA |

| I <sub>CC</sub> 82231                                                                  | F = 10 MHz<br>F = 12 MHz                                          |                          | 45<br>50 | mA<br>mA |

| I <sub>CC</sub> 82230<br>from Battery                                                  | F = 32.768 KHz<br>V <sub>BAT</sub> = 5V<br>V <sub>CC</sub> = 0V   |                          | 25       | μА       |

| I <sub>CC</sub> 82230<br>from Battery                                                  | F = 32.768 KHz<br>V <sub>BAT</sub> = 2.8V<br>V <sub>CC</sub> = 0V |                          | 20       | μΑ       |

#### NOTES:

<sup>1.</sup> -0WS (82230 Pin 47) is driven by an open collector output. It is pulled up to CMOS voltage levels of  $V_{CC} = 0.5$ V by a pullup resistor.

<sup>2. -</sup>REFRESH (82231 Pin 41) is an open collector output.

<sup>3.</sup> CCROSC is the only signal that should switch in the battery back up mode. For back up operation with  $V_{BATT} < 4.75V$ , CCROSC, POWERGOOD and CCRRST input levels  $V_{IL}/V_{IH}$  should be 10% and 90% of  $V_{BATT}$ , respectively.

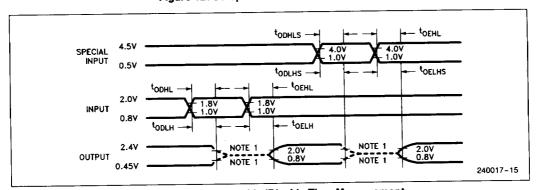

# 82230 AC CHARACTERISTICS ( $V_{DD} = 5V \pm 5\%$ , $T_A = 0^{\circ}C$ to $70^{\circ}C$ )

| Symbol    | Parameter                                  | 10      | MHz | 12      | MHz      | Units    | Notes   |

|-----------|--------------------------------------------|---------|-----|---------|----------|----------|---------|

| -Figure   |                                            | Min     | Max | Min     | Max      |          | Hotes   |

| 53-15     | -0WS Setup Time to PROCCLK ↓               | 25      |     | 25      |          | ns       | 13      |

| 54-15     | -0WS Hold Time from PROCCLK ↓              | 0       |     | 0       |          | ns       | 13      |

|           | -0WS Setup Time to PROCCLK ↓               | 36      |     | 36      |          | ns       | 11      |

|           | -0WS Hold Time from PROCCLK ↓              | 0       |     | 0       |          | ns       | 11      |

| 69–22     | A0 Setup Time to ALE A0 Hold Time from ALE | 30<br>0 |     | 25<br>0 | :        | ns<br>ns |         |

| 26-6      | A1 Setup Time to S1, S0                    | 27      |     | 22      |          | ns       |         |

| 27-6      | A1 Hold Time from S1, S0                   | 0       |     | 0       |          | ns       |         |

| 43-13     | A20 Delay from NA20                        |         | 27  |         | 22       | ns       |         |

| 44-13     | A20 Delay from A20GATE                     |         | 37  |         | 32       | ns       |         |

| 45-13     | A20 Disable Delay from CPUHLDA↑            |         | 35  |         | 30       | ns       | 4       |

| 46-13     | A20 Enable Delay from CPUHLDA ↓            |         | 35  |         | 30       | ns       |         |

| 17-3      | ALE Active Delay from PROCCLK ↓            |         | 25  |         | 23       | ns       |         |

| 18-3      | ALE Inactive Delay from PROCCLK ↓          |         | 30  |         | 25       | ns       |         |

| 68-21     | BUSY286 Delay from BUSY, -IOW              |         | 35  |         | 35       | ns       |         |

|           | CCROSC High Time                           | 25      |     | 25      |          | μs       | 5       |

|           | CCROSC Low Time                            | 25      |     | 25      | i        | μs       | 5       |

|           | CCROSC Input Rise/Fall Time                |         | 20  |         | 20       | ns       | 12      |

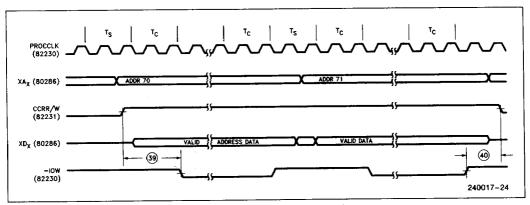

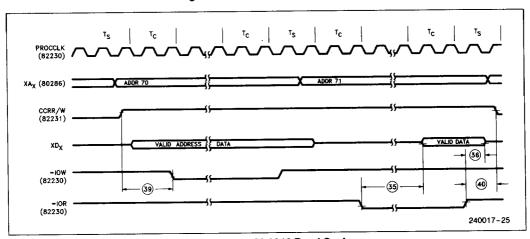

| 39-10, 11 | CCRR/W Setup Time to IOR/IOW ↓             | 0       |     | 0       |          | ns       |         |

| 40-10, 11 | CCRR/W Hold Time from IOR/IOW ↑            | 17      |     | 15      |          | ns       |         |

|           | CCRRST Pulse Width                         | 100     |     | 83      |          | ns       |         |

| 67-20     | CNTLOFF Delay from PROCCLK ↓               |         | 30  |         | 25       | ns       |         |

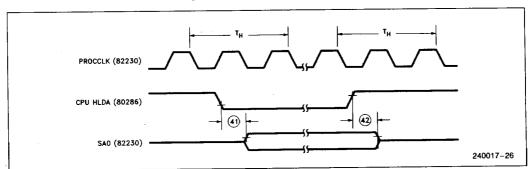

| 70-23     | CPUHLDA Setup Time to PROCCLK ↓            | 20      |     | 15      |          | ns       |         |

| 71-23     | CPUHLDA Hold Time from PROCCLK ↓           | 0       |     | 0       |          | ns       |         |

| 49-14     | DIR245 Delay from -IOR ↓, -IOW ↓           |         | 17  |         | 15       | ns       |         |

| 49-14     | DIR245 Delay from - MEMR, - MEMW           |         | 17  |         | 15       | ns       |         |

|           | DIR245 Delay from - AEN1, - AEN2           |         | 40  |         | 35       | ns       |         |

| 55-16     | DT/R Delay High from PROCCLK ↓             |         | 45  |         | 40       | ns       |         |

| 56-16     | DT/R Delay Low from PROCCLK ↓              |         | 45  |         | 40       | ns       |         |

| 60-16     | F16 Setup Time to PROCCLK ↓                | 30      |     | 30      |          | ns       |         |

| 61-16     | F16 Hold Time from PROCCLK ↓               | 0       |     | 0       | <u> </u> | ns       | <u></u> |

|           | + FSYS16 Setup Time to PROCCLK ↓           | 100     |     | 83      |          | ns       |         |

|           | +FSYS16 Hold Time from PROCCLK \           | 50      |     | 40      |          | ns       |         |

| 50-14     | -GATE245 Delay from -IOR ↓, -IOW ↓         |         | 22  |         | 20       | ns       |         |

| 50-14     | -GATE245 Delay from -MEMR, -MEMW           |         | 22  |         | 20       | ns       |         |

|           | -GATE245 Delay from -AEN1, -AEN2           |         | 45  |         | 40       | ns       |         |

# 82230 AC CHARACTERISTICS ( $V_{DD} = 5V \pm 5\%$ , $T_A = 0$ °C to 70°C) (Continued)

| Symbol                       | Parameter                                                                                                                                                                                 | 101           | 10 MHz               | lz 12 MHz     |                      | MHz Units            |              |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------|---------------|----------------------|----------------------|--------------|

| -Figure                      | Farameter                                                                                                                                                                                 | Min           | Max                  | Min           | Max                  | 0.111.0              | Notes        |

| 37-9                         | Interrupt Request Pulse Width                                                                                                                                                             | 100           |                      | 100           |                      | ns                   | 8            |

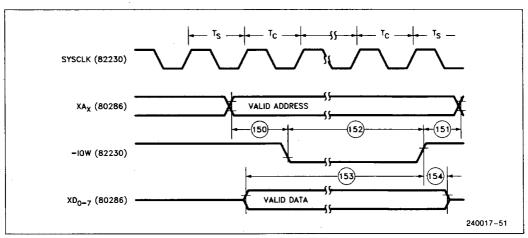

| 29-7, 8<br>30-7, 8           | - IOR, - IOW Active Delay from PROCCLK ↓ - IOR, - IOW Inactive Delay from PROCCLK ↓ - IOR, - IOW Enable/Disable Delay from CPUHLDA                                                        | 3             | 15<br>15<br>40       | 3             | 15<br>15<br>40       | ns<br>ns<br>ns       |              |

|                              | <ul> <li>INTA Active Delay from PROCCLK ↓</li> <li>INTA Inactive Delay from PROCCLK ↓</li> <li>INTA Enable/Disable Delay from CPUHLDA</li> </ul>                                          | 3             | 45<br>45<br>40       | 3             | 35<br>35<br>40       | ns<br>ns<br>ns       |              |

| 38-9                         | INTR Delay from Interrupt                                                                                                                                                                 |               | 175                  | ļ             | 150                  | ns                   |              |

| 33-7, 8<br>34-7, 8           | - INTR1CS, $-$ INTR2CS Setup Time to $-$ IOR, $-$ IOW ↓ $-$ INTR1CS, $-$ INTR2CS Hold Time from $-$ IOR, $-$ IOW ↑                                                                        | 0             |                      | 0             |                      | ns<br>ns             |              |

| 72-24<br>73-24               | −IO CS 16 Setup Time to SYSCLK ↓     −IO CS 16 Hold Time from SYSCLK ↓                                                                                                                    | 85<br>0       |                      | 75<br>0       |                      | ns<br>ns             |              |

| 57-16<br>58-16<br>66-19      | - LSDEN, -MSDEN Active Delay from PROCCLK ↓ - LSDEN, -MSDEN Inactive Delay from PROCCLK ↓ - LSDEN, -MSDEN Delay from -NPCS - LSDEN, -MSDEN Active Delay from SM/IO after - CS287 Inactive |               | 45<br>35<br>15<br>30 |               | 40<br>30<br>15<br>30 | ns<br>ns<br>ns       |              |

| 79–16<br>80–16               | - MEMR, - MEMW Active Delay from PROCCLK ↓ - MEMR, - MEMW Inactive Delay from PROCCLK ↓ - MEMR, - MEMW Enable/Disable Delay from CPUHLDA                                                  | 3             | 15<br>15<br>40       | 3             | 15<br>15<br>40       | ns<br>ns<br>ns       |              |

| 64-17                        | -MSDEN Delay from -XHBE                                                                                                                                                                   | <u> </u>      | 27                   | ļ             | 25                   | ns                   |              |

| 62-16<br>63-16               | M/ĪŌ Setup Time to PROCCLK ↓ M/ĪŌ Hold Time from PROCCLK ↓                                                                                                                                | 28<br>0       |                      | 25<br>0       |                      | ns<br>ns             |              |

| 65-18                        | -NPCS Delay from SM/IO-CS287, XA3, -INTA                                                                                                                                                  |               | 40                   | <u> </u>      | 35                   | ns                   | 1            |

| 11-2<br>12-2<br>13-2<br>14-2 | PCLK, - PCLK High Time PCLK, - PCLK Low Time PCLK, - PCLK Delay from PROCCLK PCLK, - PCLK Rise/Fall Times                                                                                 | 45<br>45      | 45<br>7.5            | 35<br>35      | 40<br>5              | ns<br>ns<br>ns       | 12           |

| 19-4<br>8-4                  | POWER GOOD Setup Time to PROCCLK ↓ POWER GOOD Hold Time from PROCCLK ↓ POWER GOOD Rise/Fall Times POWER GOOD Inactive Pulse Width                                                         | 26<br>50<br>1 | 20                   | 26<br>41<br>1 | 20                   | ns<br>ns<br>ns<br>µs | 3<br>3<br>12 |

| 5-2<br>6-2<br>7-2<br>9-2     | PROCCLK Delay from X3 PROCCLK High Time PROCCLK Low Time PROCCLK Rise/Fall Time                                                                                                           | 5<br>16<br>12 | 25<br>8              | 5<br>13<br>11 | 20                   | ns<br>ns<br>ns<br>ns | 12           |

| 22-5<br>23-5                 | <ul><li>RC Setup Time to SYSCLK ↑</li><li>RC Pulse Width</li></ul>                                                                                                                        | 30<br>100     | 1                    | 30<br>83      | 1                    | ns<br>ns             | 3            |

| 51-15<br>52-15               | READY Active Delay from PROCCLK ↓ READY Inactive Delay from PROCCLK ↓                                                                                                                     |               | 22<br>70             |               | 18<br>60             | ns<br>ns             |              |

# 82230 AC CHARACTERISTICS ( $V_{DD}=5V~\pm5\%,\,T_A=0^{\circ}C$ to 70°C) (Continued)

| Symbol<br>- Figure | Parameter                                 | 10 [ | MHz 12 MHz |            | 12 MHz |       | Notes   |

|--------------------|-------------------------------------------|------|------------|------------|--------|-------|---------|

|                    | T arameter                                | Min  | Max        | Min        | Max    | Units | Hotes   |

|                    | REFRDY Pulse Width                        | 50   |            | 40         |        | ns    |         |

|                    | REFRDY Hold Time from PROCCLK \$\d\cdot\$ | 34   |            | 34         |        | ns    |         |

|                    | REFRDY Setup Time to PROCCLK ↓            | -14  | L          | <b>-14</b> |        | ns    | <u></u> |

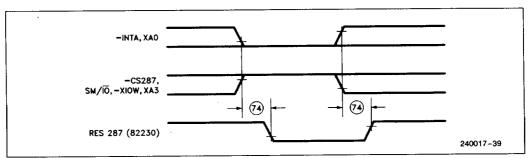

| 74-25              | RES 287 Delay from -IOW                   |      | 60         |            | 50     | ns    |         |

| 21-4               | RES CPU Delay from PROCCLK ↓              |      | 27         |            | 22     | ns    |         |

| 20-4               | + RESET Delay from PROCCLK ↓              |      | 50         |            | 50     | ns    |         |

| 41-12              | SA0 Enable Time from CPU HLDA             |      | 60         |            | 50     | ns    |         |

| 42-12              | SA0 Disable Time from CPU HLDA            | j    | 60         |            | 50     | ns    | 4       |

| 15-3               | S1, S0 Setup Time to PROCCLK ↓            | 28   |            | 15         |        | ns    |         |

| 16-3               | S1, S0 Hold Time from PROCCLK \$\(\psi\)  | 0    |            | 0          |        | ns    |         |

| 10-2               | SYSCLK Delay from PROCCLK ↓               | 5    | 20         | 5          | 20     | ns    |         |

| 1-2                | X3 Period                                 | 50   |            | 41.7       |        | ns    |         |

| 2-2                | X3 Low Time                               | 17   |            | 15         |        | ns    |         |

| 3–2                | X3 High Time                              | 23   |            | 20         |        | ns    |         |

| 4-2                | X3 Rise/Fall Times                        |      | 5          |            | 3      | ns    | 12      |

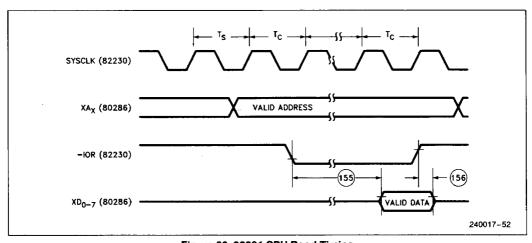

| 35-8, 11           | XD0-XD7 Delay Time from −IOR ↓            |      | 45         |            | 40     | ns    |         |

| 36-8, 11           | XD0-XD7 Hold Time from −IOR ↑             |      | 17         |            | 15     | ns    |         |

| 31-7               | XD0-XD7 Setup Time to −IOW ↑              | 100  |            | 83         | !      | ns    |         |

| 32-7               | XD0-XD7 Hold Time from −IOW ↑             | 0    |            | 0          |        | ns    |         |

# 82231 AC CHARACTERISTICS ( $V_{DD}=5V\pm5\%$ , $T_A=0^{\circ}C$ to $70^{\circ}C$ )

| Symbol<br>- Figure | Parameter                                                  | 10  | MHz 1 | Hz 12 |     | Units  | Notes |

|--------------------|------------------------------------------------------------|-----|-------|-------|-----|--------|-------|

|                    | raiametei                                                  | Min | Max   | Min   | Max | Oilles | Hotes |

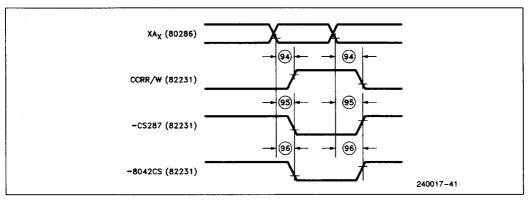

| 96-27              | -8042CS Delay from XA <sub>X</sub>                         |     | 60    |       | 48  | ns     |       |

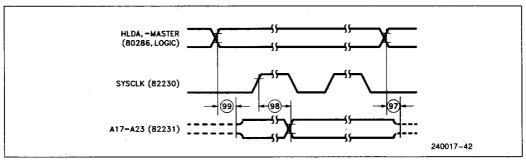

| 98-28<br>99-28     | A17-A23 Delay from SYSCLK ↑ A17-A23 Enable Delay from HLDA |     | 150   |       | 125 | ns     |       |

|                    | or -MASTER                                                 |     | 100   |       | 83  | ns     |       |

| 97-28              | A17-A23 Disable Delay from HLDA or -MASTER                 | •   | 100   |       | 83  | ns     | 4     |

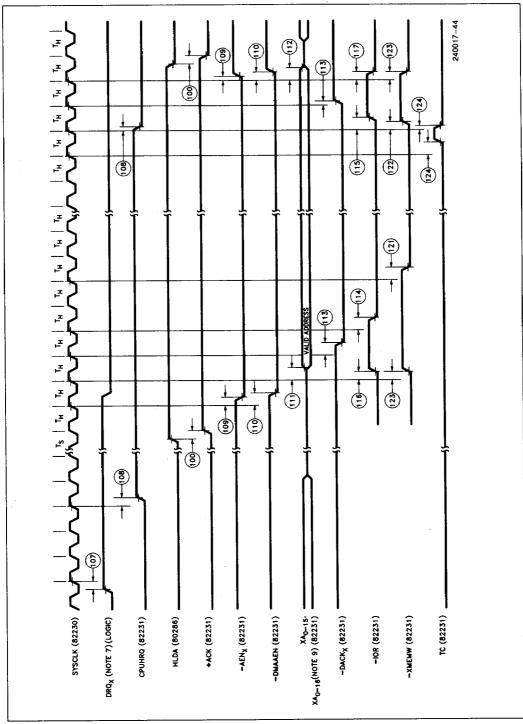

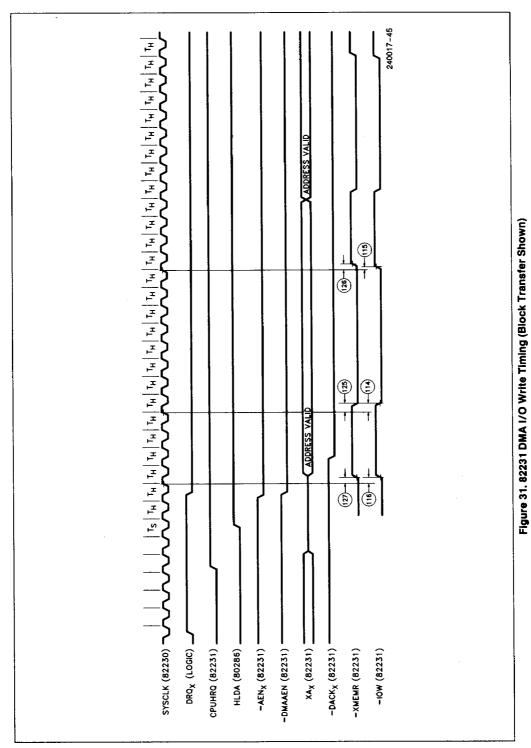

| 100-29             | + ACK Delay from HLDA                                      |     | 45    |       | 40  | ns     |       |

| 101-29             | + ACK Delay from - MASTER                                  |     | 45    |       | 40  | ns     |       |

| 109-30             | - AEN1, - AEN2 Delay from SYSCLK↑                          |     | 130   |       | 115 | ns     |       |

| 94-27              | CCRR/W Delay from XA <sub>X</sub>                          |     | 60    |       | 48  | ns     |       |

| 102-29             | CCRR/W Delay from HLDA or -MASTER                          |     | 50    |       | 41  | ns     |       |

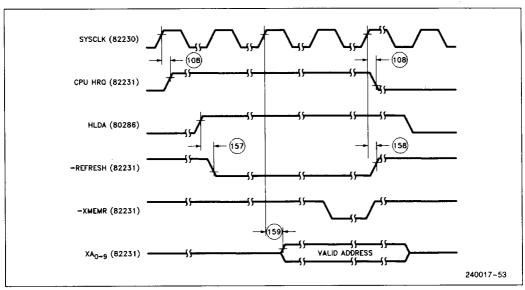

| 108-30, 39         | CPU HRQ Delay from SYSCLK↑                                 |     | 80    |       | 70  | ns     |       |

| 95-26              | - CS287 Delay from XA <sub>X</sub>                         |     | 60    |       | 48  | ns     |       |

| 103-29             | CS287 Delay from HLDA or MASTER                            |     | 50    |       | 41  | ns     |       |

| 113-30             | - DACK0-3, - DACK5-7 Delay from SYSCLK↑                    |     | 110   |       | 100 | ns     |       |

| 110-30             | - DMAAEN Delay from SYSCLK↑                                |     | 140   |       | 120 | ns     |       |

# 82231 AC CHARACTERISTICS ( $V_{DD} = 5V \pm 5\%$ , $T_A = 0$ °C to 70°C) (Continued)

| Symbol           | Downwooder                                                                                                              | 10 MHz   | 12 l       | MHz      | Units    | Notes    |       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|----------|------------|----------|----------|----------|-------|