### Intel486™ DX CPU-CACHE CHIP SET

50 MHz Intel486™ DX Microprocessor, 82495DX Cache Controller, and 82490DX Dual Ported Intelligent Cache SRAM

- 50 MHz Intel486™ DX CPU

- RISC Integer Core with Frequent Instructions Executing in One Clock

- 160 Mbyte/Sec Burst Bus

- 41 Dhrystone MIPs

- 11.5M Double Precision Whetstones/Sec.

- --- On-Chip Cache and FPU

- **■** Highly Flexible

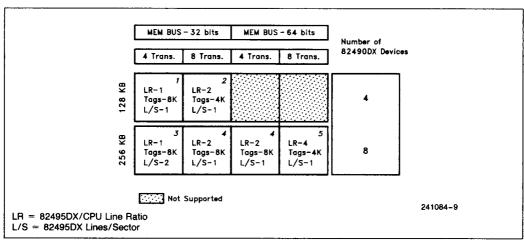

- Supports 128 Kbyte and 256 Kbyte Configurations

- Complete MESI Protocol Support

- 32- or 64-Bit Memory Bus Width

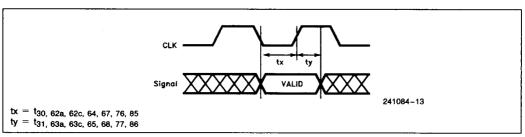

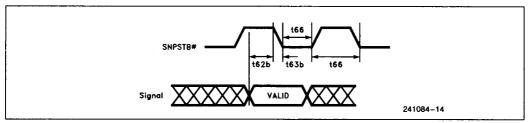

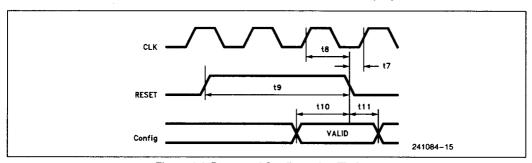

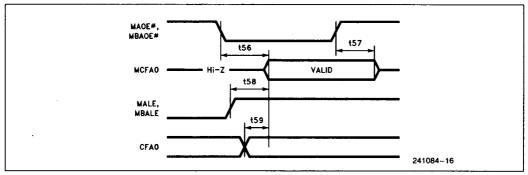

- Synchronous, Asynchronous, and Strobed Memory Bus Protocols

- Variable Cache Line Sizes and Sectoring

- Cache Data Parity Option

- High Performance Second Level Cache

- Two-Way Set Associative

- Write-Back or Write Through Cache

- Zero Wait State Cache Access

- Concurrent CPU Bus, Memory Bus, and Internal Array Operation

- **Full Multiprocessing Support**

- -- Implements MESI Write-Back Cache Protocol

- Low Bus Utilization

- Automatically Maintains 1st Level Cache Consistency

- Supports Read-for-Ownership, Write-Allocation, and Cache-to-Cache Transfers

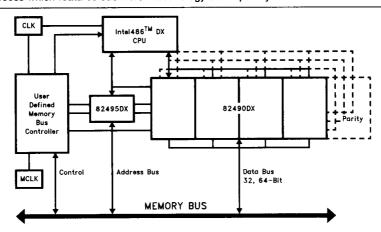

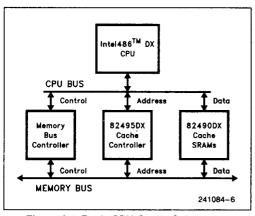

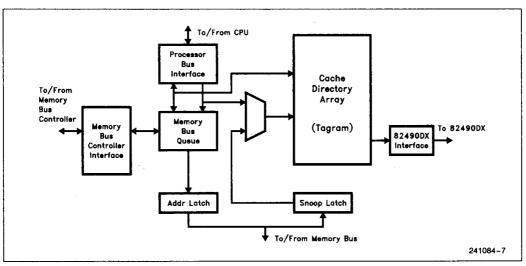

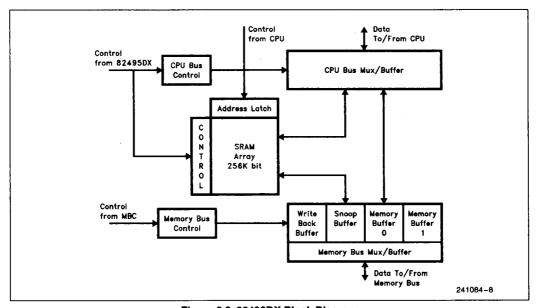

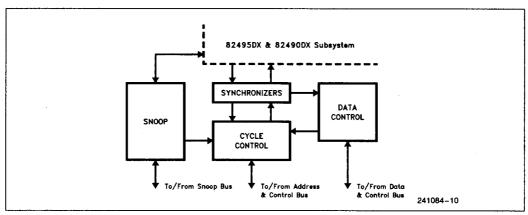

The 50 MHz Intel486 DX CPU-Cache Chip Set provides a high performance solution for servers and high-end desktop systems. This binary compatible solution has been optimized to provide 50 MHz, zero wait state performance. The CPU-Cache chip set combines the 50 MHz Intel486 Microprocessor with the 82495DX/82490DX cache subsystem. It delivers integer performance of 41 V1.1 Dhrystone MIPs and a SPEC integer rating of 27.9. The cache subsystem features the 82495DX Cache Controller and the 82490DX Dual Ported Data RAM. Dual ported buffers and registers of the 82490DX allow the 82495DX Cache Controller to concurrently handle CPU bus, memory bus, and internal cache operations for maximum performance.

The CPU-Cache Chip Set offers many features that are ideal for multiprocessor based systems. The Write-Back feature provides efficient memory bus utilization by reducing bus traffic through eliminating unnecessary writes to main memory. The CPU-Cache chip set also supports MESI protocol and monitors the memory bus to quarantee cache coherency.

The 50 MHz Intel486 DX CPU and 82495DX/82490DX Cache subsystem are produced on Intel's latest CHMOS V process which features submicron technology and triple layer metal.

241084-1

### 2

# Intel486™ DX CPU-Cache Chip Set

| CONTENTS                                                   | PAGE    |

|------------------------------------------------------------|---------|

| 1.0 PINOUTS                                                | . 2-856 |

| 1.1 i486™DX CPU Pinouts                                    | . 2-856 |

| 1.2 82495DX Pinouts                                        | . 2-858 |

| 1.3 82490DX Pinouts                                        | . 2-860 |

| 1.4 Pin Cross Reference Tables                             | . 2-862 |

| 1.4.1 i486™DX Microprocessor<br>Chip Set Version Pin Table | . 2-862 |

| 1.4.2 82495DX Quick Pin Referen by Name                    |         |

| 1.4.3 82490DX Quick Pin Referen by Name                    | ce      |

| 2.0 QUICK PIN REFERENCE                                    | . 2-865 |

| 2.1 Quick Pin Reference<br>(Optimized Interface)           | . 2-873 |

| 3.0 ARCHITECTURAL OVERVIEW                                 | . 2-877 |

| 3.1 Introduction                                           | . 2-877 |

| 3.2 CPU-Cache Chip Set Description                         | . 2-877 |

| 3.2.1 CPU                                                  |         |

| 3.2.2 Cache Controller                                     |         |

| 2.2.2 Cacho SBAM                                           | 0.077   |

| CONTENTS                                            |         |

|-----------------------------------------------------|---------|

| CONTENTS                                            | PAGE    |

| 3.3 Secondary Cache Features                        | . 2-879 |

| 3.4 Chip Set Design and Operation .                 | . 2-879 |

| 3.5 CPU Bus Interface                               | . 2-879 |

| 3.6 Secondary Cache Interface                       | . 2-879 |

| 3.7 Memory Bus Interface                            | . 2-880 |

| 3.8 Test                                            | . 2-881 |

| 4.0 ELECTRICAL DATA                                 | . 2-881 |

| 4.1 Background                                      | . 2-881 |

| 4.2 Maximum Ratings                                 | . 2-881 |

| 4.3 DC Specifications                               | . 2-882 |

| 4.4 AC Specifications                               | . 2-883 |

| 4.5 Optimized and External Interface Specifications | . 2-891 |

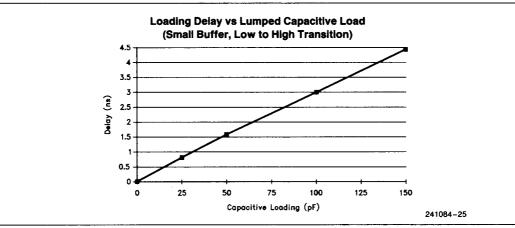

| 4.6 Capacitive Derating                             | . 2-906 |

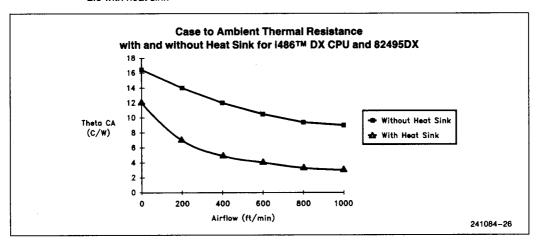

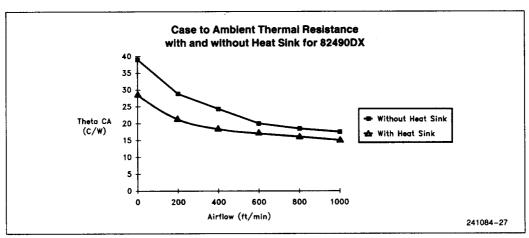

| 5.0 THERMAL DATA                                    | . 2-907 |

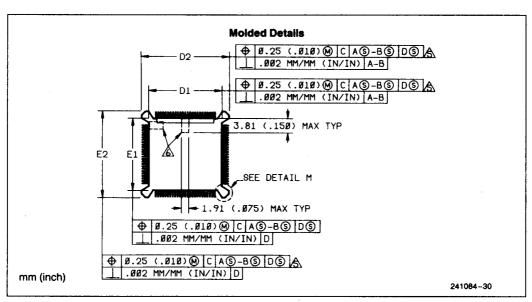

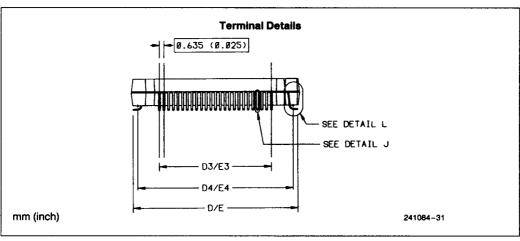

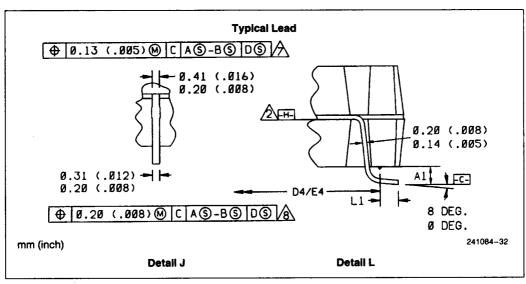

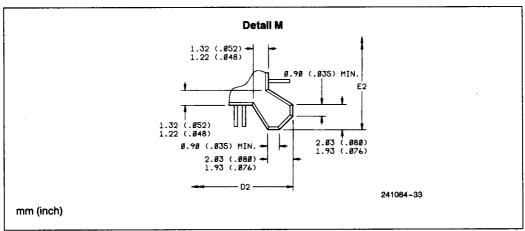

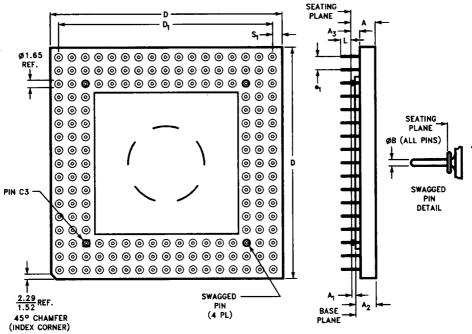

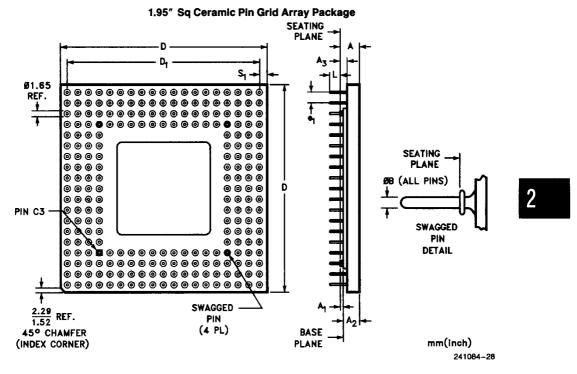

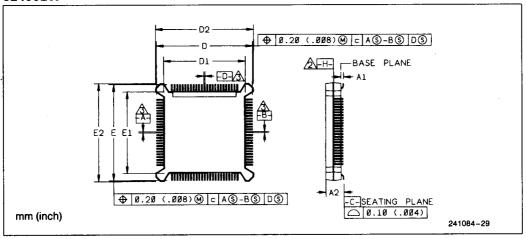

| 6.0 MECHANICAL SPECIFICATIONS .                     | . 2-909 |

#### 1.0 PINOUTS

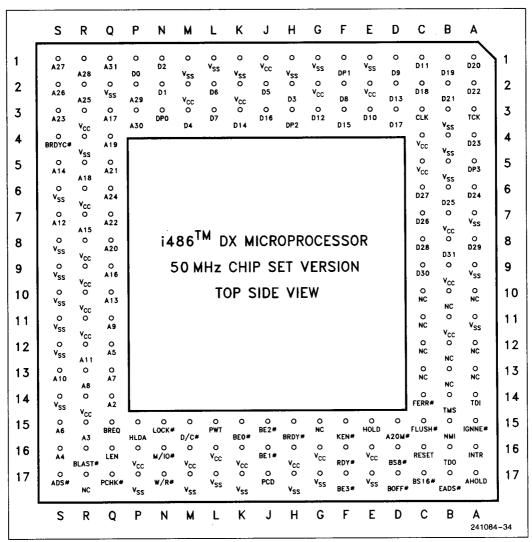

### 1.1 i486TM DX CPU Pinouts

Intel486™ DX CPU Pinout (Top View)

Intel486™ DX CPU Pinout (Bottom View)

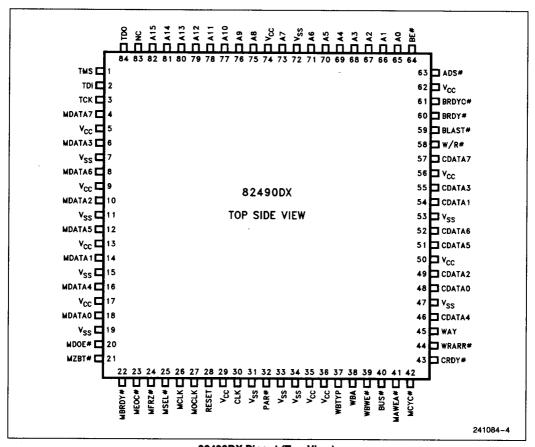

### 1.2 82495DX Pinouts

|    | S                    | R                    | Q           | Р           | N                    | М                    | L                    | K                             | j                    | Н                               | G                    | F                     | E                    | D                    | С                    | В                            | A                    |                |

|----|----------------------|----------------------|-------------|-------------|----------------------|----------------------|----------------------|-------------------------------|----------------------|---------------------------------|----------------------|-----------------------|----------------------|----------------------|----------------------|------------------------------|----------------------|----------------|

| 1  | o<br>V <sub>CC</sub> | O<br>MKEN#           | O<br>SWEND# | O<br>BRDY#  | v <sub>cc</sub>      | O<br>DRCTM#          | , v <sub>cc</sub>    | 0                             | O<br>MRO#            | 0                               | o<br>v <sub>cc</sub> | O<br>SNPBSY#          | o<br>V <sub>cc</sub> | 0                    | O<br>RDYSRC          | 0                            | O<br>TAG9            | ۱ (            |

| 2  | O<br>NC              | o<br>V <sub>SS</sub> | O<br>MALE   | O<br>TMS    | o<br>v <sub>ss</sub> | O<br>CRDY#           | o<br>V <sub>SS</sub> | V <sub>CC</sub>               | o<br>v <sub>ss</sub> | v <sub>cc</sub><br>0            | o<br>v <sub>ss</sub> | 0                     | o<br>V <sub>SS</sub> | FSIOUT               | O<br>MCACHE#         | TAG10                        | O<br>TAG7            | 2              |

| 3  | O<br>SNPCL           | 0                    | O<br>SNPNCA | O           | O<br>TDI             | O<br>BGT#            | o<br>V <sub>SS</sub> | V <sub>SS</sub><br>O<br>MWBWT | O<br>CWAY            | V <sub>SS</sub><br>O<br>SNPCYC4 | O<br>MTHIT#          |                       | O<br>CADS#           |                      | KLOCK#               | CFA3                         | O<br>TAG3            | 3              |

| 4  | O<br>MAOE#           | O<br>MCFA2           | O<br>SYNC#  | O<br>MBALE  | O<br>FLUSH#          | O<br>KWEND#          | O<br>CNA#            | 0                             | CPLOCK               | 0                               | O<br>CAHOLE          | SNPADS#<br>O<br>CDTS# | O<br>CWR#            | CDC#                 | O<br>TD0             | TAG5                         | O<br>TAG1            | 4              |

| 5  | o<br>Vcc             | o<br>V <sub>SS</sub> | O<br>RESET  | O           |                      |                      | _                    | V <sub>SS</sub>               |                      | MD((M*                          | _                    | CDIS#                 |                      | CMIO#                | O<br>TAG11           | TAG4                         | o<br>v <sub>cc</sub> | 5              |

| 6  | o<br>v <sub>cc</sub> | o<br>V <sub>SS</sub> | O<br>MCFA3  | O<br>MBAOE# |                      |                      |                      |                               |                      |                                 |                      |                       |                      | NENE#                | O<br>SMLN#           | v <sub>ss</sub><br>0         | o<br>v <sub>cc</sub> | 6              |

| 7  | v <sub>cc</sub>      | o<br>V <sub>SS</sub> | O<br>MTAG10 | O<br>MTAG11 |                      |                      |                      |                               |                      |                                 |                      |                       |                      | CFA2                 | O<br>TAG6            | v <sub>ss</sub>              | o<br>v <sub>cc</sub> | 7              |

| 8  | v <sub>cc</sub>      | o<br>V <sub>SS</sub> | O<br>MTAG4  | O<br>MTAG8  |                      |                      |                      | 82                            | 495                  | ĐΧ                              |                      |                       | -                    | TAG8<br>O<br>TAG2    | O<br>TAGO            | v <sub>ss</sub><br>0         | o<br>v <sub>cc</sub> | 8              |

| 9  | v <sub>cc</sub>      | o<br>V <sub>SS</sub> | O<br>MTAG2  | O<br>MTAG1  |                      |                      | 7                    |                               | SIDE                 |                                 | W                    |                       |                      | O<br>SET7            | o<br>v <sub>cc</sub> | V <sub>SS</sub>              | O<br>SET 10          | 9              |

| 10 | o<br>V <sub>CC</sub> | 0<br>V <sub>SS</sub> | O<br>MTAGO  | O<br>MSET8  |                      |                      |                      | IUF .                         | SIUL                 | VIEV                            | 7                    |                       |                      | O<br>SET8            | o<br>v <sub>ss</sub> | SET9<br>O                    | o<br>v <sub>cc</sub> | 10             |

| 11 | o<br>v <sub>cc</sub> | o<br>v <sub>ss</sub> | O<br>MSET10 | O<br>MSET2  |                      |                      |                      |                               |                      |                                 |                      |                       | j                    | O<br>CLK             | O<br>SET5            | v <sub>ss</sub><br>o         | o<br>v <sub>cc</sub> | 11             |

| 12 | o<br>V <sub>CC</sub> | o<br>V <sub>SS</sub> | O<br>MSET9  | O<br>MSET1  |                      |                      |                      |                               |                      |                                 |                      |                       |                      | O<br>SET6            | O<br>SET4            | V <sub>SS</sub><br>O<br>SET3 | o<br>v <sub>cc</sub> | 12             |

| 13 | o<br>v <sub>cc</sub> | o<br>v <sub>ss</sub> | O<br>MSET5  | O<br>MCFA6  |                      |                      |                      |                               |                      |                                 | "                    |                       |                      | O<br>SETO            | O<br>SET 1           | 0<br>V <sub>SS</sub>         | o<br>v <sub>cc</sub> | 13             |

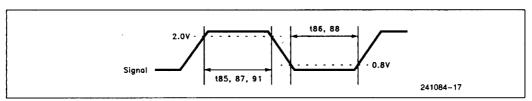

| 14 | O<br>MTAG6           | O<br>MTAG3           | O<br>MSET3  | O<br>MCFA5  | O<br>MCFA1           | O<br>WBA             | O<br>WRARR#          | o<br>(wrmrst                  | O<br>(CFG3)          | O<br>DC#                        | o<br>V <sub>SS</sub> | O<br>BRDYC2#          | O<br>CFA5            | O<br>CFA6            | O<br>SET2            | O CFA1                       | O<br>NC              | 14             |

| 15 | O<br>MTAG7           | O<br>MTAG5           | O<br>MSETO  | O<br>MCFA4  | O<br>WBTYP           | O<br>WBWE#           | O<br>WAY             | O<br>CLEN1                    | O<br>EADS#           | O<br>PCD                        | O<br>CLENO           | O<br>LEN              | O<br>CFA0            | 0                    | O<br>BLAST#          | O<br>ADS#                    | O<br>NC              | 15             |

| 16 | O<br>MTAG9           | O<br>MSET4           | O<br>MCFA0  | O<br>BUS#   | $v_{ss}^{\circ}$     | o<br>v <sub>ss</sub> | v <sub>ss</sub>      | o<br>v <sub>ss</sub>          | v <sub>ss</sub>      | o<br>V <sub>SS</sub>            | o<br>v <sub>ss</sub> | O<br>MIO#             | o<br>v <sub>ss</sub> | O<br>KEN#            | O<br>BLE#            | O<br>LOCK#                   | O<br>CFA4            | 16             |

| 17 | O<br>MSET7           | O<br>MSET6           | O<br>MAWEA# | O<br>MCYC#  | v <sub>cc</sub>      | o<br>V <sub>CC</sub> | v <sub>cc</sub>      | o<br>v <sub>cc</sub>          | o<br>V <sub>SS</sub> | o<br>V <sub>CC</sub>            | o<br>v <sub>cc</sub> | o<br>v <sub>cc</sub>  | v <sub>cc</sub>      | o<br>V <sub>SS</sub> | O<br>PWT             | 0<br>WR#                     | O<br>AHOLD           | 17             |

| •  | S                    | R                    | Q           | Р           | N                    | М                    | L                    | К                             | J                    | Н                               | G                    | F                     | Ε                    | D                    | С                    | В                            | A<br>241084          | <b>J</b><br>-2 |

82495DX Pinout (Top View)

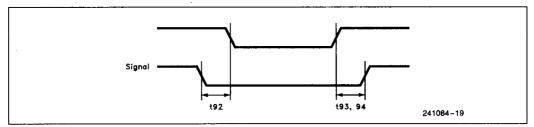

82495DX Pinout (Bottom View)

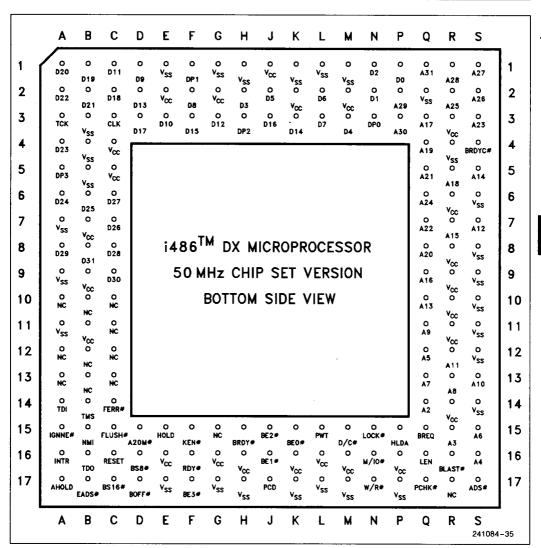

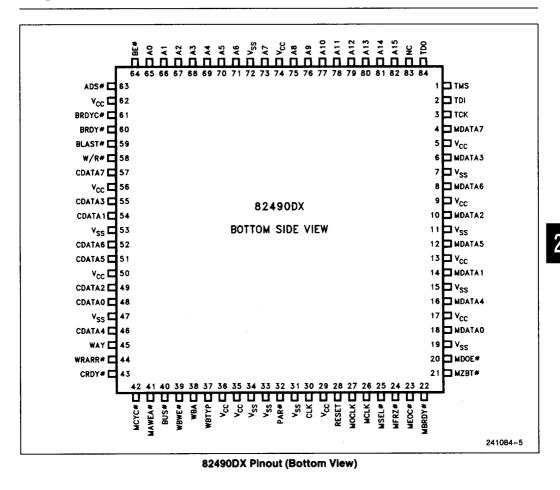

#### 1.3 82490DX Pinouts

82490DX Pinout (Top View)

### 1.4 Pin Cross Reference Tables

### 1.4.1 Intel486TM DX MICROPROCESSOR CHIP SET VERSION PIN TABLE

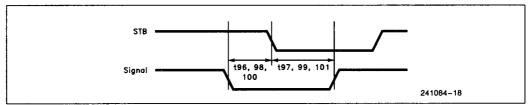

| Pin   | Location                                                                  |

|-------|---------------------------------------------------------------------------|

| A2    | Q14                                                                       |

| A3    | R15                                                                       |

| A4    | S16                                                                       |

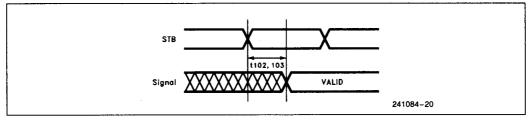

| A5    | Q12                                                                       |

| A6    | S15                                                                       |

| A7    | Q13                                                                       |

| A8    | R13                                                                       |

| A9    | Q11                                                                       |

| A10   | S13                                                                       |

| A11   | R12                                                                       |

| A12   | S7                                                                        |

| A13   | Q10                                                                       |

| A14   | S5                                                                        |

| A15   | R7                                                                        |

| A16   | Q9                                                                        |

| A17   | Q3                                                                        |

| A18   | R5                                                                        |

| A19   | Q4                                                                        |

| A20   | Q8                                                                        |

| A21   | Q5                                                                        |

| A22   | Q7                                                                        |

| A23   | S3                                                                        |

| A24   | Q6                                                                        |

| A25   | R2                                                                        |

| A26   | S2                                                                        |

| A27   | S1                                                                        |

| A28   | R1                                                                        |

| A29   | P2                                                                        |

| A30   | P3                                                                        |

| A31   | Q1                                                                        |

| A20M# | D15                                                                       |

| ADS#  | S17                                                                       |

| AHOLD | A17                                                                       |

| BE0#  | K15                                                                       |

| NC    | A10, A12,<br>A13, B10,<br>B12, B13,<br>C10, C11,<br>C12, C13,<br>G15, R17 |

| SOUN CHIP | SET VERSION PIN                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|

| Pin       | Location                                                                                                                    |

| BE1#      | J16                                                                                                                         |

| BE2#      | J15                                                                                                                         |

| BE3#      | F17                                                                                                                         |

| BLAST#    | R16                                                                                                                         |

| BOFF#     | D17                                                                                                                         |

| BRDY#     | H15                                                                                                                         |

| BRDYC#    | S4                                                                                                                          |

| BREQ      | Q15                                                                                                                         |

| BS16#     | C17                                                                                                                         |

| BS8#      | D16                                                                                                                         |

| CLK       | C3                                                                                                                          |

| D/C#      | M15                                                                                                                         |

| D0        | P1                                                                                                                          |

| D1        | N2                                                                                                                          |

| D2        | N1                                                                                                                          |

| D3        | H2                                                                                                                          |

| D4        | M3                                                                                                                          |

| D5        | J2                                                                                                                          |

| D6        | L2                                                                                                                          |

| D7        | L3                                                                                                                          |

| D8        | F2                                                                                                                          |

| D9        | D1                                                                                                                          |

| D10       | E3                                                                                                                          |

| D11       | C1                                                                                                                          |

| D12       | G3                                                                                                                          |

| D13       | D2                                                                                                                          |

| D14       | K3                                                                                                                          |

| D15       | F3                                                                                                                          |

| D16       | J3                                                                                                                          |

| D17       | D3                                                                                                                          |

| D18       | C2                                                                                                                          |

| D19       | B1                                                                                                                          |

| D20       | A1                                                                                                                          |

| D21       | B2                                                                                                                          |

| D22       | A2                                                                                                                          |

| VCC       | B11, B7, B9, C4,<br>C5, E16, E2, G16,<br>G2, H16, J1, K16,<br>K2, L16, M16,<br>M2, P16, R10,<br>R11, R14, R3,<br>R6, R8, R9 |

|           | ווט, ווט, חש                                                                                                                |

| D23         A4           D24         A6           D25         B6           D26         C7           D27         C6           D28         C8           D29         A8           D30         C9           D31         B8           DP0         N3           DP1         F1           DP2         H3           DP3         A5           EADS#         B17           FERR#         C14           FLUSH#         C15           HLDA         P15           HOLD         E15           IGGNE#         A15           INTR         A16           KEN#         F15           LEN         Q16           LOCK#         N15           M/IO#         N16           NMI         B15           PCD         J17           PCHK#         Q17           PWT         L15           RDY#         F16           RESET         C16           TCK         A3           TDI         A14           TDO         B16           T                                                             |         |                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------|

| D24         A6           D25         B6           D26         C7           D27         C6           D28         C8           D29         A8           D30         C9           D31         B8           DP0         N3           DP1         F1           DP2         H3           DP3         A5           EADS#         B17           FERR#         C14           FLUSH#         C15           HLDA         P15           HOLD         E15           IGGNE#         A15           INTR         A16           KEN#         F15           LEN         Q16           LOCK#         N15           M/IO#         N16           NMI         B15           PCD         J17           PCHK#         Q17           PWT         L15           RDY#         F16           RESET         C16           TCK         A3           TDI         A14           TDO         B16           TMS         B14                                                                        | Pin     | Location                              |

| D25         B6           D26         C7           D27         C6           D28         C8           D29         A8           D30         C9           D31         B8           DP0         N3           DP1         F1           DP2         H3           DP3         A5           EADS#         B17           FERR#         C14           FLUSH#         C15           HCDA         P15           HOLD         E15           IGGNE#         A15           INTR         A16           KEN#         F15           LEN         Q16           LOCK#         N15           M/IO#         N16           NMI         B15           PCD         J17           PCHK#         Q17           PWT         L15           RDY#         F16           RESET         C16           TCK         A3           TDI         A14           TDO         B16           TMS         B14           W/R#         N17 <t< td=""><td><u></u></td><td></td></t<>                             | <u></u> |                                       |

| D26         C7           D27         C6           D28         C8           D29         A8           D30         C9           D31         B8           DP0         N3           DP1         F1           DP2         H3           DP3         A5           EADS#         B17           FERR#         C14           FLUSH#         C15           HLDA         P15           HOLD         E15           IGGNE#         A15           INTR         A16           KEN#         F15           LEN         Q16           LOCK#         N15           M/IO#         N16           NMI         B15           PCD         J17           PCHK#         Q17           PWT         L15           RDY#         F16           RESET         C16           TCK         A3           TDI         A14           TDO         B16           TMS         B14           W/R#         N17           VSS         A11, A7, A9, B3, B4, B5, E1, E17, G1,                                   |         | A6                                    |

| D27         C6           D28         C8           D29         A8           D30         C9           D31         B8           DP0         N3           DP1         F1           DP2         H3           DP3         A5           EADS#         B17           FERR#         C14           FLUSH#         C15           HCDA         P15           HOLD         E15           IGGNE#         A15           INTR         A16           KEN#         F15           LEN         Q16           LOCK#         N15           M/IO#         N16           NMI         B15           PCD         J17           PCHK#         Q17           PWT         L15           RDY#         F16           RESET         C16           TCK         A3           TDI         A14           TDO         B16           TMS         B14           W/R#         N17           VSS         A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, |         |                                       |

| D28         C8           D29         A8           D30         C9           D31         B8           DP0         N3           DP1         F1           DP2         H3           DP3         A5           EADS#         B17           FERR#         C14           FLUSH#         C15           HLDA         P15           HOLD         E15           IGGNE#         A15           INTR         A16           KEN#         F15           LEN         Q16           LOCK#         N15           M/IO#         N16           NMI         B15           PCD         J17           PCHK#         Q17           PWT         L15           RDY#         F16           RESET         C16           TCK         A3           TDI         A14           TDO         B16           TMS         B14           W/R#         N17           VSS         A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12.                | D26     | C7                                    |

| D29         A8           D30         C9           D31         B8           DP0         N3           DP1         F1           DP2         H3           DP3         A5           EADS#         B17           FERR#         C14           FLUSH#         C15           HLDA         P15           HOLD         E15           IGGNE#         A15           INTR         A16           KEN#         F15           LEN         Q16           LOCK#         N15           M/IO#         N16           NMI         B15           PCD         J17           PCHK#         Q17           PWT         L15           RDY#         F16           RESET         C16           TCK         A3           TDI         A14           TDO         B16           TMS         B14           W/R#         N17           VSS         A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12, S12, S12, S12, S12, S12, S12            | D27     | C6                                    |

| D30 C9 D31 B8 DP0 N3 DP1 F1 DP2 H3 DP3 A5 EADS# B17 FERR# C14 FLUSH# C15 HLDA P15 HOLD E15 IGGNE# A15 INTR A16 KEN# F15 LEN Q16 LOCK# N15 M/IO# N16 NMI B15 PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, R4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | D28     | C8                                    |

| D31 B8 DP0 N3 DP1 F1 DP2 H3 DP3 A5 EADS# B17 FERR# C14 FLUSH# C15 HLDA P15 HOLD E15 IGGNE# A15 INTR A16 KEN# F15 LEN Q16 LOCK# N15 M/IO# N16 NMI B15 PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | D29     | A8                                    |

| DP0 N3 DP1 F1 DP2 H3 DP3 A5 EADS# B17 FERR# C14 FLUSH# C15 HLDA P15 HOLD E15 IGGNE# A15 INTR A16 KEN# F15 LEN Q16 LOCK# N15 M/IO# N16 NMI B15 PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D30     | C9                                    |

| DP1 F1 DP2 H3 DP3 A5 EADS# B17 FERR# C14 FLUSH# C15 HLDA P15 HOLD E15 IGGNE# A15 INTR A16 KEN# F15 LEN Q16 LOCK# N15 M/IO# N16 NMI B15 PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D31     | B8                                    |

| DP2 H3 DP3 A5 EADS# B17 FERR# C14 FLUSH# C15 HLDA P15 HOLD E15 IGGNE# A15 INTR A16 KEN# F15 LEN Q16 LOCK# N15 M/IO# N16 NMI B15 PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DP0     | N3                                    |

| DP3 A5  EADS# B17  FERR# C14  FLUSH# C15  HLDA P15  HOLD E15  IGGNE# A15  INTR A16  KEN# F15  LEN Q16  LOCK# N15  M/IO# N16  NMI B15  PCD J17  PCHK# Q17  PWT L15  RDY# F16  RESET C16  TCK A3  TDI A14  TDO B16  TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DP1     | F1                                    |

| EADS# B17 FERR# C14 FLUSH# C15 HLDA P15 HOLD E15 IGGNE# A15 INTR A16 KEN# F15 LEN Q16 LOCK# N15 M/IO# N16 NMI B15 PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DP2     | H3                                    |

| FERR# C14  FLUSH# C15  HLDA P15  HOLD E15  IGGNE# A15  INTR A16  KEN# F15  LEN Q16  LOCK# N15  M/IO# N16  NMI B15  PCD J17  PCHK# Q17  PWT L15  RDY# F16  RESET C16  TCK A3  TDI A14  TDO B16  TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12, S12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DP3     | A5                                    |

| FLUSH# C15 HLDA P15 HOLD E15 IGGNE# A15 INTR A16 KEN# F15 LEN Q16 LOCK# N15 M/IO# N16 NMI B15 PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EADS#   | B17                                   |

| HLDA P15 HOLD E15 IGGNE# A15 INTR A16 KEN# F15 LEN Q16 LOCK# N15 M/IO# N16 NMI B15 PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FERR#   | C14                                   |

| HOLD E15 IGGNE# A15 INTR A16 KEN# F15 LEN Q16 LOCK# N15 M/IO# N16 NMI B15 PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FLUSH#  | C15                                   |

| IGGNE# A15 INTR A16 KEN# F15 LEN Q16 LOCK# N15 M/IO# N16 NMI B15 PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | HLDA    | P15                                   |

| INTR A16  KEN# F15  LEN Q16  LOCK# N15  M/IO# N16  NMI B15  PCD J17  PCHK# Q17  PWT L15  RDY# F16  RESET C16  TCK A3  TDI A14  TDO B16  TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | HOLD    | E15                                   |

| KEN# F15  LEN Q16  LOCK# N15  M/IO# N16  NMI B15  PCD J17  PCHK# Q17  PWT L15  RDY# F16  RESET C16  TCK A3  TDI A14  TDO B16  TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12, S12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IGGNE#  | A15                                   |

| LEN Q16  LOCK# N15  M/IO# N16  NMI B15  PCD J17  PCHK# Q17  PWT L15  RDY# F16  RESET C16  TCK A3  TDI A14  TDO B16  TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INTR    | A16                                   |

| LOCK# N15  M/IO# N16  NMI B15  PCD J17  PCHK# Q17  PWT L15  RDY# F16  RESET C16  TCK A3  TDI A14  TDO B16  TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | KEN#    | F15                                   |

| M/IO# N16  NMI B15  PCD J17  PCHK# Q17  PWT L15  RDY# F16  RESET C16  TCK A3  TDI A14  TDO B16  TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LEN     | Q16                                   |

| NMI B15 PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LOCK#   | N15                                   |

| PCD J17 PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, R4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | M/IO#   | N16                                   |

| PCHK# Q17 PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NMI     | B15                                   |

| PWT L15 RDY# F16 RESET C16 TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, O2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PCD     | J17                                   |

| RDY# F16  RESET C16  TCK A3  TDI A14  TDO B16  TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, O2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PCHK#   | Q17                                   |

| RESET C16  TCK A3  TDI A14  TDO B16  TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, O2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PWT     | L15                                   |

| TCK A3 TDI A14 TDO B16 TMS B14 W/R# N17 VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, O2, B4, S10, S11, S12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RDY#    | F16                                   |

| TDI A14  TDO B16  TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RESET   | C16                                   |

| TDO B16  TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, B4, S10, S11, S12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TCK     | A3                                    |

| TMS B14  W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, P4, S10, S11, S12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TDI     | A14                                   |

| W/R# N17  VSS A11, A7, A9, B3, B4, B5, E1, E17, G1, G17, H1, H17, K1, K17, L1, L17, M1, M17, P17, Q2, P4, S10, S11, S12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TDO     | B16                                   |

| VSS A11, A7, A9, B3,<br>B4, B5, E1, E17,<br>G1, G17, H1, H17,<br>K1, K17, L1, L17,<br>M1, M17, P17, Q2,<br>B4, S10, S11, S12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TMS     | B14                                   |

| B4, B5, E1, E17,<br>G1, G17, H1, H17,<br>K1, K17, L1, L17,<br>M1, M17, P17, O2,<br>R4, S10, S11, S12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | W/R#    | N17                                   |

| S14, S6, S8, S9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VSS     | B4, B5, E1, E17,<br>G1, G17, H1, H17, |

### 1.4 Pin Cross Reference Tables (Continued)

### 1.4.2 82495DX QUICK REFERENCE BY NAME

| (CFG3) J14  ADS# B15  AHOLD A17  BGT#(CLDRV) M03  BLAST# C15  BLE# C16  BRDY# P01  BRDYC1# D15  BRDYC2# F14  BUS# P16  CADS# E03  CAHOLD G04  CD/C# D03  CDTS# F04  CFA0 E15  CFA1 B14  CFA2 D06  CFA3 B02  CFA4 A16  CFA5 E14  CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  CPLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16  KLOCK# C03                                                                                                                                                                                                                                                               | Signal         | Location |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|

| AHOLD A17 BGT # (CLDRV) M03 BLAST # C15 BLE # C16 BRDY # P01 BRDYC1 # D15 BRDYC2 # F14 BUS # P16 CADS # E03 CAHOLD G04 CD/C # D03 CDTS # F04 CFA0 E15 CFA1 B14 CFA2 D06 CFA3 B02 CFA4 A16 CFA5 E14 CFA6 D14 CLEN0 G15 CLEN1 K15 CLK D11 CM/IO # D04 CNA # (CFG0) L04 CPLOCK # J04 CPLOCK # J04 CPLOCK B15 CWAY J03 CW/R # E04 D/C # H14 DRCTM # M01 EADS # J15 FLUSH # N04 FSIOUT # D01 KEN # D16                                                                                                                                                                                                                                                                                                                  | (CFG3)         | J14      |

| BGT # (CLDRV) M03 BLAST # C15 BLE # C16 BRDY # P01 BRDYC1 # D15 BRDYC2 # F14 BUS # P16 CADS # E03 CAHOLD G04 CD/C # D03 CDTS # F04 CFA0 E15 CFA1 B14 CFA2 D06 CFA3 B02 CFA4 A16 CFA5 E14 CFA6 D14 CLEN0 G15 CLEN1 K15 CLK D11 CM/IO # D04 CNA # (CFG0) L04 CPLOCK # J04 CPLOCK # J04 CPLOCK # J04 CPLOCK # J04 CPLOCK # H14 DRCTM # E04 D/C # H14 DRCTM # M01 EADS # J15 FLUSH # N04 FSIOUT # D01 KEN # D16                                                                                                                                                                                                                                                                                                        | ADS#           | B15      |

| BLAST # C15 BLE # C16 BRDY # P01 BRDYC1 # D15 BRDYC2 # F14 BUS # P16 CADS # E03 CAHOLD G04 CD/C # D03 CDTS # F04 CFA0 E15 CFA1 B14 CFA2 D06 CFA3 B02 CFA4 A16 CFA5 E14 CFA6 D14 CLEN0 G15 CLEN1 K15 CLK D11 CM/IO # D04 CNA # (CFG0) L04 CPLOCK # J04 (PLOCKEN) CRDY # (SLFTST #) M02 CWAY J03 CW/R # E04 D/C # H14 DRCTM # M01 EADS # J15 FLUSH # N04 FSIOUT # D01 KEN # D16                                                                                                                                                                                                                                                                                                                                      | AHOLD          | A17      |

| BLAST # C15 BLE # C16 BRDY # P01 BRDYC1 # D15 BRDYC2 # F14 BUS # P16 CADS # E03 CAHOLD G04 CD/C # D03 CDTS # F04 CFA0 E15 CFA1 B14 CFA2 D06 CFA3 B02 CFA4 A16 CFA5 E14 CFA6 D14 CLEN0 G15 CLEN1 K15 CLK D11 CM/IO # D04 CNA # (CFG0) L04 CPLOCK # J04 (PLOCKEN) CRDY # (SLFTST #) M02 CWAY J03 CW/R # E04 D/C # H14 DRCTM # M01 EADS # J15 FLUSH # N04 FSIOUT # D01 KEN # D16                                                                                                                                                                                                                                                                                                                                      | BGT#(CLDRV)    | M03      |

| BLE# C16 BRDY# P01 BRDYC1# D15 BRDYC2# F14 BUS# P16 CADS# E03 CAHOLD G04 CD/C# D03 CDTS# F04 CFA0 E15 CFA1 B14 CFA2 D06 CFA3 B02 CFA4 A16 CFA5 E14 CFA6 D14 CLEN0 G15 CLEN1 K15 CLK D11 CM/IO# D04 CNA#(CFG0) L04 CPLOCK# J04 CPLOCK# J04 CPLOCKEN) CRDY#(SLFTST#) M02 CWAY J03 CW/R# E04 D/C# H14 DRCTM# M01 EADS# J15 FLUSH# N04 FSIOUT# D01 KEN# D16                                                                                                                                                                                                                                                                                                                                                            |                | C15      |

| BRDYC1# D15 BRDYC2# F14 BUS# P16 CADS# E03 CAHOLD G04 CD/C# D03 CDTS# F04 CFA0 E15 CFA1 B14 CFA2 D06 CFA3 B02 CFA4 A16 CFA5 E14 CFA6 D14 CLEN0 G15 CLEN1 K15 CLK D11 CM/IO# D04 CNA#(CFG0) L04 CPLOCKEN) CRDY#(SLFTST#) M02 CWAY J03 CW/R# E04 D/C# H14 DRCTM# M01 EADS# J15 FLUSH# N04 FSIOUT# D01 KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                       |                | C16      |

| BRDYC2# F14 BUS# P16 CADS# E03 CAHOLD G04 CD/C# D03 CDTS# F04 CFA0 E15 CFA1 B14 CFA2 D06 CFA3 B02 CFA4 A16 CFA5 E14 CFA6 D14 CLEN0 G15 CLEN1 K15 CLK D11 CM/IO# D04 CNA#(CFG0) L04 CPLOCK# J04 (PLOCKEN) CRDY#(SLFTST#) M02 CWAY J03 CW/R# E04 D/C# H14 DRCTM# M01 EADS# J15 FLUSH# N04 FSIOUT# D01 KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                       | BRDY#          | P01      |

| BUS# P16  CADS# E03  CAHOLD G04  CD/C# D03  CDTS# F04  CFA0 E15  CFA1 B14  CFA2 D06  CFA3 B02  CFA4 A16  CFA5 E14  CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                        | BRDYC1#        | D15      |

| CADS# E03  CAHOLD G04  CD/C# D03  CDTS# F04  CFA0 E15  CFA1 B14  CFA2 D06  CFA3 B02  CFA4 A16  CFA5 E14  CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                  | BRDYC2#        | F14      |

| CAHOLD         G04           CD/C#         D03           CDTS#         F04           CFA0         E15           CFA1         B14           CFA2         D06           CFA3         B02           CFA4         A16           CFA5         E14           CLEN0         G15           CLEN1         K15           CLK         D11           CM/IO#         D04           CNA#(CFG0)         L04           CPLOCK#         J04           (PLOCKEN)         CRDY#(SLFTST#)         M02           CWAY         J03           CW/R#         E04           D/C#         H14           DRCTM#         M01           EADS#         J15           FLUSH#         N04           FSIOUT#         D01           KEN#         D16 | BUS#           | P16      |

| CD/C# D03  CDTS# F04  CFA0 E15  CFA1 B14  CFA2 D06  CFA3 B02  CFA4 A16  CFA5 E14  CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                         | CADS#          | E03      |

| CD/C# D03  CDTS# F04  CFA0 E15  CFA1 B14  CFA2 D06  CFA3 B02  CFA4 A16  CFA5 E14  CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                         | CAHOLD         | G04      |

| CFA0 E15  CFA1 B14  CFA2 D06  CFA3 B02  CFA4 A16  CFA5 E14  CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                                               |                | D03      |

| CFA1 B14  CFA2 D06  CFA3 B02  CFA4 A16  CFA5 E14  CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CDTS#          | F04      |

| CFA2 D06  CFA3 B02  CFA4 A16  CFA5 E14  CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CFA0           | E15      |

| CFA3 B02  CFA4 A16  CFA5 E14  CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CFA1           | B14      |

| CFA4 A16  CFA5 E14  CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CFA2           | D06      |

| CFA5 E14  CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CFA3           | B02      |

| CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CFA4           | A16      |

| CFA6 D14  CLEN0 G15  CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CFA5           | E14      |

| CLEN1 K15  CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CFA6           |          |

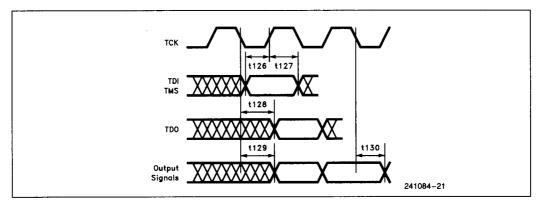

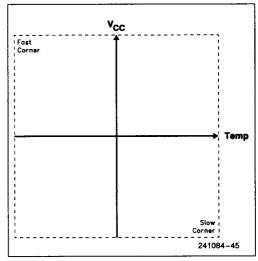

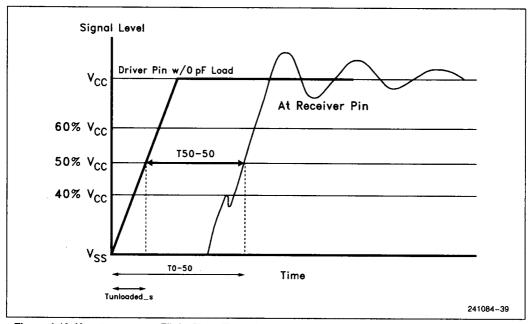

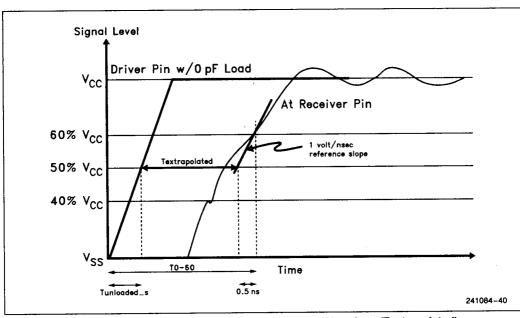

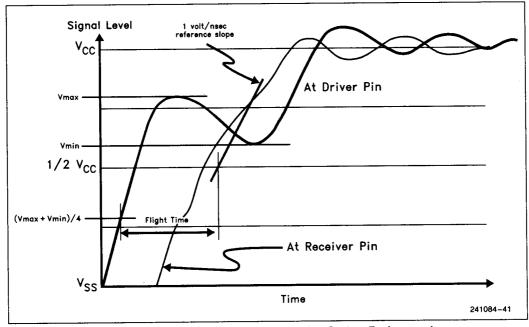

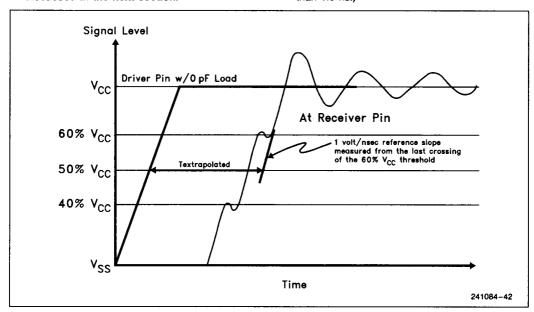

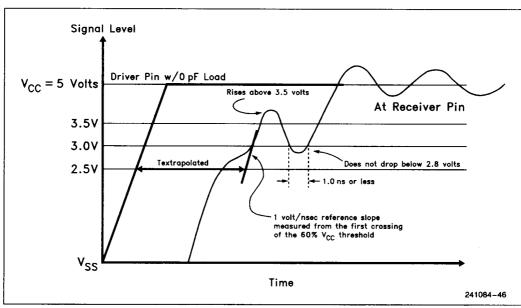

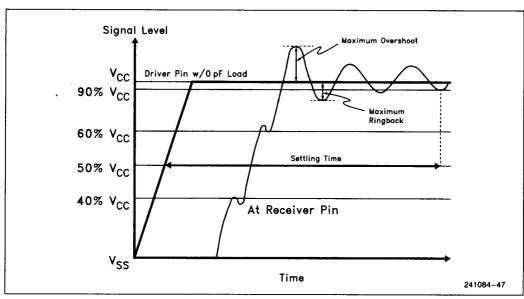

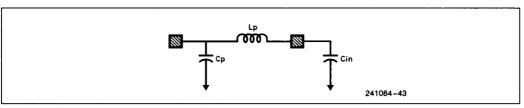

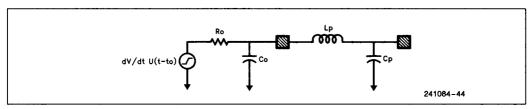

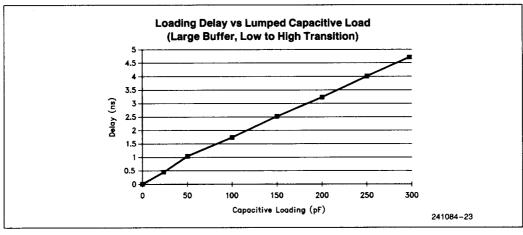

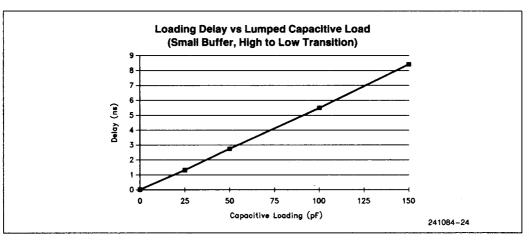

| CLK D11  CM/IO# D04  CNA#(CFG0) L04  CPLOCK# J04  (PLOCKEN)  CRDY#(SLFTST#) M02  CWAY J03  CW/R# E04  D/C# H14  DRCTM# M01  EADS# J15  FLUSH# N04  FSIOUT# D01  KEN# D16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CLEN0          | G15      |