# 82489DX ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER

# 82489DX FEATURES OVERVIEW

- Advanced Interrupt Controller for 32-Bit Operating Systems

- Solution for Multiprocessor Interrupt Management

- Dynamic Interrupt Distribution for Load Balancing in MP Systems

- Separate Nibble Bus (Interrupt Controller Communications (ICC) Bus) for Interrupt Messages

- **■** Inter-Processor Interrupts

- Various Addressing Schemes— Broadcast, Fixed, Lowest Priority, etc.

- Compatibility Mode with 8259A

- 32-Bit Internal Registers

- **■** Integrated Timer Support

- 33 MHz Operation

- 132-Lead PQFP Package, Package Type KU (See Packaging Specification. Order Number: 240800)

Refer to Application Note AP-388: 82489DX User's Manual (Order Number 292116) when evaluating your design needs.

# 82489DX Advanced Programmable Interrupt Controller

| CONTENTS                                   | PAGE | CONTENTS                                                    | PAGE |

|--------------------------------------------|------|-------------------------------------------------------------|------|

| 1.0 INTRODUCTION                           | 4-29 | Interrupt Command Register [63:32]                          | 4-43 |

| 2.0 FUNCTIONAL OVERVIEW                    | 4-30 | 6.5 IRR, ISR, TMR Registers                                 | 4-43 |

| ICC Bus                                    | 4-30 | Interrupt Acceptance                                        | 4-43 |

| Local Unit                                 | 4-30 | Acceptance Mechanism                                        | 4-45 |

| I/O Unit                                   | 4-30 | 6.6 Tracking Processor Priority                             | 4-47 |

| Timer                                      | 4-30 | Task Priority Register                                      | 4-47 |

| 3.0 PIN DESCRIPTION                        | 4-30 | 6.7 Dispensing Interrupts  Dispensing Interrupts to the Loc |      |

| 4.0 FUNCTIONAL DESCRIPTION                 | 4-34 | Processor                                                   | 4-48 |

| I/O Unit                                   |      | 6.8 Spurious Interrupt Vector Register                      |      |

| 5.0 INTERRUPT CONTROL                      |      | Spurious Interrupt                                          |      |

| MECHANISM                                  | 4-37 | Unit Enable                                                 |      |

| 5.1 Interrupts                             | 4-37 | 6.10 Remote Read Register                                   |      |

| Total Allowed Interrupt Vectors            |      | 6.11 82489DX Local Configuration                            |      |

| Interrupt Sources                          | 4-38 | Local Version Register                                      |      |

| Interrupt Destinations                     | 4-38 | 6.12 82489DX Timer Registers                                |      |

| Interrupt Delivery                         | 4-38 | Overview                                                    |      |

| 5.2 Interrupt Redirection                  | 4-39 | Time Base                                                   |      |

| Inter-82489DX Communication                | 4-39 | Timer                                                       |      |

| 6.0 82489DX LOCAL UNIT REGISTE DESCRIPTION |      | Timer Vector Table                                          | 4-50 |

| 6.1 Local Unit ID Register                 | 4-39 | 7.0 82489DX I/O UNIT REGISTERS                              | 4-51 |

| 82489DX Local Unit ID Register             | 4-39 | Registers Addressing Scheme                                 |      |

| 6.2 Destination Format Register            | 4-39 | 82489DX I/O Unit Configuration .                            |      |

| 6.3 Local Interrrupt Vector Table          |      | I/O Unit ID Register                                        |      |

| Registers                                  | 4-40 | I/O Unit Version Register                                   |      |

| Local Interrupts 0,1 Interrupt Vectors     | 4-40 | I/O Unit Interrupt Source Registers Redirection Tables      |      |

| 6.4 Inter-Processor Interrrupt Registers   | 4-41 | Descriptions                                                | 4-53 |

| Interrupt Command Register                 | 4.44 | Destination                                                 | 4-54 |

| CONTENTS                          | PAGE    | CONTENTS                             | PAGE |

|-----------------------------------|---------|--------------------------------------|------|

| 8.0 ICC BUS DEFINITION            | 4-55    | Pause-IR                             | 4-78 |

| Physical Characteristics          |         | Exit 2-IR                            | 4-78 |

| Bus Arbitration                   |         | Update-IR                            | 4-78 |

| Lowest-Priority Arbitration       |         | Instruction Register                 | 4-79 |

| ICC Bus Message Formats           |         | Bypass Instruction                   | 4-79 |

| Long Message Format               |         | Extest Instruction                   | 4-79 |

|                                   |         | Sample/Preload Instruction           | 4-79 |

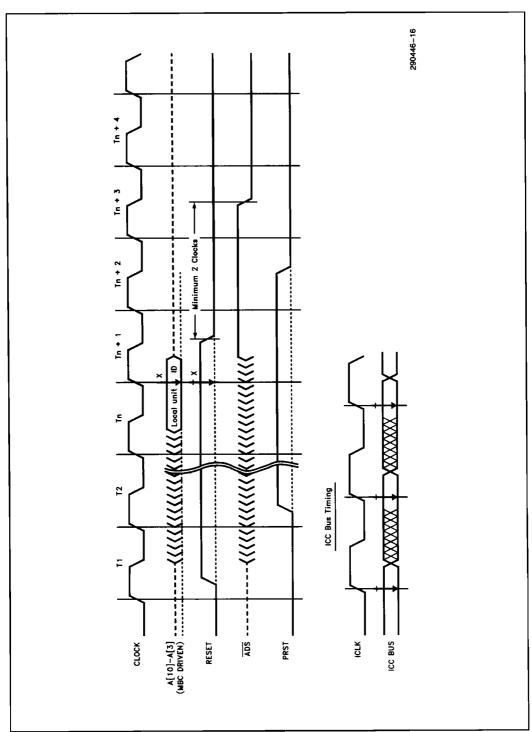

| 9.0 HARDWARE TIMINGS              |         | dcode Instruction                    | 4-79 |

| Interfacing to the ICC Bus        |         | Device Identification Register (DID) | 4-79 |

| First Order Buffer Models         |         | Boundary Scan Register               | 4-79 |

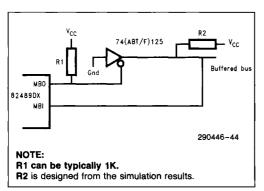

| MBO Pull-Up Register              | 4-60    | Boundary Scan Cell Names in Order    | ,    |

| Driving Lumped Capacitance        | 4-60    | from tđi to tdo                      |      |

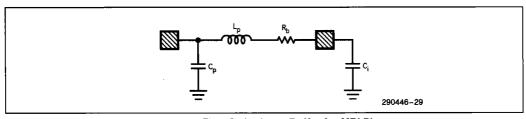

| Driving Transmission Lines        | 4-61    | Bypass Register                      |      |

| External Drivers/Buffered ICC Bus | s 4-63  | JTAG TAP Controller Initialization   | 4-83 |

| Transmission Line Termination     | 4-65    | 11.0 ELECTRICAL                      |      |

| ICC Bus Operating Frequency       | 4-65    | CHARACTERISTICS                      | 4-84 |

| 9.182489DX Register Access        |         | 11.1 D.C. Specifications             | 4-84 |

| Timing                            |         | 11.2 A.C. Specifications             | 4-85 |

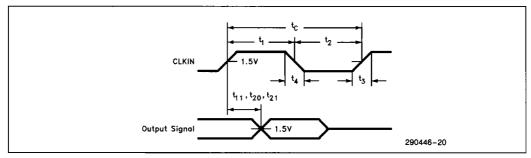

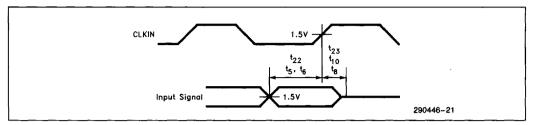

| Timing Diagram Notation           |         | 12.0 REGISTER SUMMARY                | 4-87 |

| Register WRITE Timing             |         | I/O Unit Registers                   |      |

| Register READ Timing              |         | Local Unit Registers                 |      |

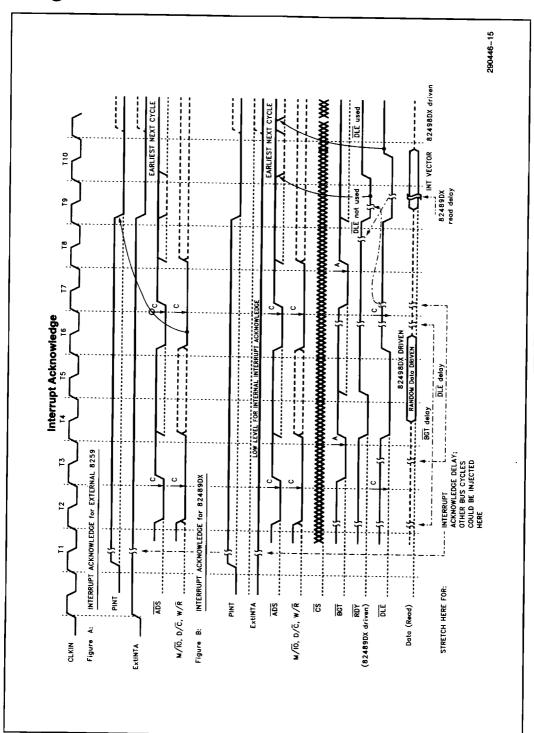

| Interrupt Acknowledge Timing      |         | -                                    |      |

| Reset and Miscellaneous Timir     | ng 4-74 | 13.0 TIMING DIAGRAMS                 | 4-90 |

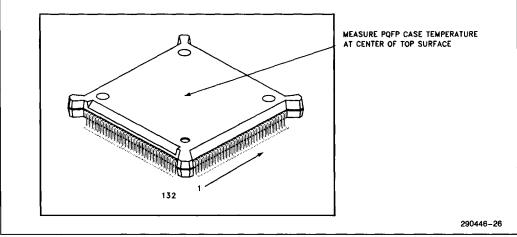

| 10.0 BOUNDARY SCAN DESCRIPTION    | 4-74    | 14.0 PACKAGE PIN-OUT                 | 4-94 |

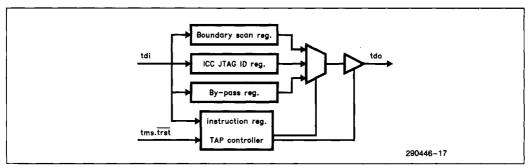

| 10.1 Boundary Scan Architecture   |         | 15.0 PACKAGE THERMAL                 |      |

| Test Access Ports                 |         | SPECIFICATION                        | 4-95 |

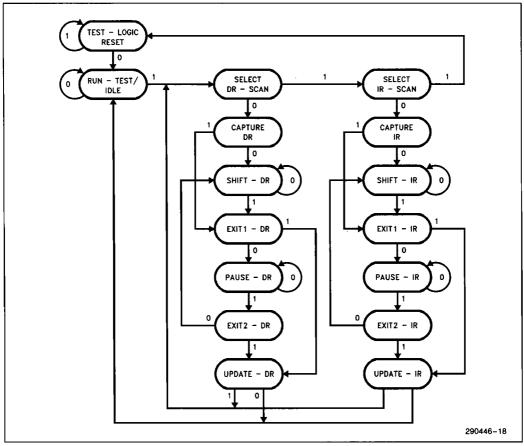

| TAP Controller                    |         | 16.0 GUIDELINES FOR 82489DX          |      |

| Test-Logic-Reset                  |         | USERS                                |      |

| Run-Test/Idle                     |         | 16.1 Initialization                  | 4-96 |

| Select-DR-Scan                    |         | 16.2 Compatibility                   | 4-96 |

| Select-IR-Scan                    |         | Compatibility Levels                 | 4-96 |

|                                   |         | 82489DX/8259A Interaction            | 4-96 |

| Capture-DR                        |         | 82489DX/8259A Dual Mode              |      |

|                                   |         | Connection                           | 4-97 |

| Exit 1-DR                         |         | 16.3 Hardware Guidelines             | 4-98 |

| Pause-DR                          |         | 82489DX Hardware State on            | 4.00 |

| Exit 2-DR                         |         | Reset                                |      |

| Update-DR                         |         | Pull Up and Pull Down Resistors      |      |

| Capture-IR                        |         | Pint and ExINTA Timings              |      |

| Shift-IR                          |         | ExtINTA Timings                      | 4-98 |

| Exit 1-IR                         | 4-78    |                                      |      |

| CONTENTS                                        | PAGE  | CONTENTS                                           | PAGE      |

|-------------------------------------------------|-------|----------------------------------------------------|-----------|

| 82489DX and Memory Mapping                      | 4-98  | Disabling Local Unit                               | 4-100     |

| JTAG Circuit Considerations                     | 4-98  | Issuing EOI                                        | 4-101     |

| 16.4 Programming Guidelines                     | 4-99  | External Interrupts and EO                         | l 4-101   |

| Unique ID Requirement                           | 4-99  | Spurious Interrupts and EC                         | )l 4-101  |

| Atomic Write Read to Task Prior                 |       | NMI and EOI                                        | 4-101     |

| Register                                        | 4-99  | Task Priority Register                             | 4-101     |

| Critical Regions and Mutual Exclusion           | 4-99  | ExtINT Interrupt and Task Priority                 | 4-101     |

| Interrupt Command Register Programming Sequence | 4.00  | Removing Masks                                     |           |

| Interrupt Vector                                | 4-99  | Delivery Mode and Trigger Mode                     | 4-101     |

| Local and I/O Unit                              | 4-99  | Assigning Interrupt Vectors                        | s 4-102   |

| ICR (Interrupt Command Register)                | 4-99  | Sending Inter-Processor<br>Interrupts              |           |

| ISR/IRR/TMR                                     |       | Delay with Level Triggered Interrupts              |           |

| ExtINT Interrupt Posting                        | 4-100 | Reset Deassert                                     |           |

| Synchronizing Arb IDs                           |       | Interrupt Masking                                  | 4-102     |

| Lowest Priority                                 |       | Changing Redirection Tab                           | les 4-102 |

| •                                               |       | Device Drivers with 82489                          | DX 4-102  |

|                                                 |       | SYSTEM HARDWARE AND SOFTWARE DESIGN CONSIDERATIONS | 4-103     |

|                                                 |       | DIRECTIONS FOR EASY MIGH                           |           |

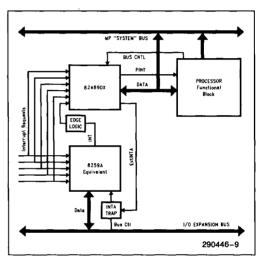

#### 1.0 INTRODUCTION

The 82489DX Advanced Programmable Interrupt Controller provides multiprocessor interrupt management, providing both static and dynamic symmetrical Interrupt distribution across all processors.

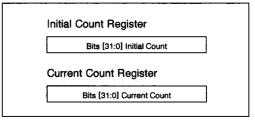

The main function of the 82489DX is to provide interrupt management across all processors. This dynamic interrupt distribution includes routing of the interrupt to the lowest-priority processor. The 82489DX works in systems with multiple I/O subsystems, where each subsystem can have its own set of interrupts. This chip also provides inter-processor interrupts, allowing any processor to interrupt any processor or set of processors. Each 82489DX I/O unit Interrupt Input pin is individually programmable by software as either edge or level triggered. The interrupt vector and interrupt steering information

can be specified per pin. A 32-bit wide timer is provided that can be programmed to interrupt the local processor. The timer can be used as a counter to provide a time base to software running on the processor, or to generate time slice interrupts locally to that processor. The 82489DX provides 32-bit software access to its internal registers. Since no 82489DX register reads have any side effects, the 82489DX registers can be aliased to a user readonly page for fast user access (e.g., performance monitoring timers).

The 82489DX supports a generalized naming/addressing scheme that can be tailored by software to fit a variety of system architectures and usage models. It also supports 8259A compatibility by becoming virtually transparent with regard to an externally connected 8259A style controller, making the 8259A visible to software.

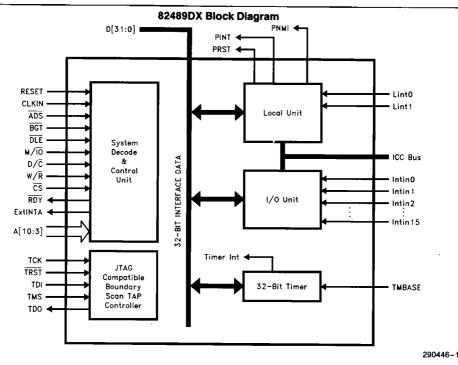

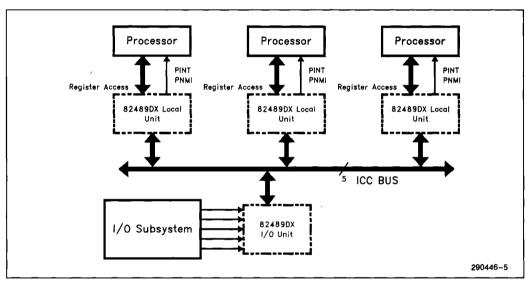

Figure 1. 82489DX Architecture

# 2.0 FUNCTIONAL OVERVIEW

## 82489DX Functional Blocks

82489DX contains one Local Unit, one I/O unit and a timer. The ICC bus is used to pass interrupt messages.

#### ICC BUS

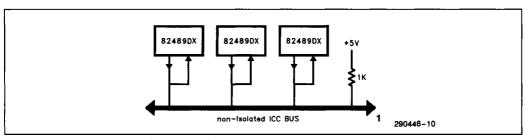

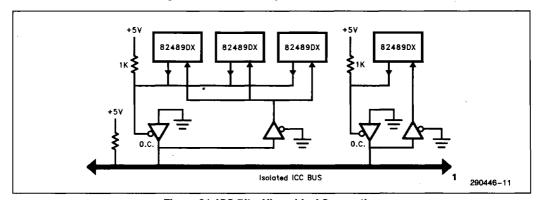

The ICC bus is a 5-wire synchronous bus connecting all 82489DXs (all I/O Units and all Local Units). The Local Units and I/O Units communicate over this ICC bus. Four of these five wires are used for data transmissions and arbitration, and one wire is a clock.

## LOCAL UNIT

The Local Unit contains the necessary intelligence to determine whether or not its processor should accept interrupt messages sent on the ICC bus by other Local Units and I/O Units. The Local Unit also provides local pending of interrupts, nesting and masking of interrupts, and handles all interactions with its local processor such as the INT/INTA/EOI protocol. The Local Unit further provides inter-processor interrupt functionality and a timer to its local processor. The interface of a processor to its 82489DX Local Unit is identical for every processor.

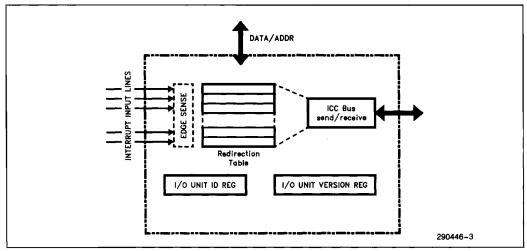

#### I/O UNIT

The I/O Unit provides the interrupt input pins on which I/O devices inject interrupts into the system in

the form of an edge or a level. The I/O unit also contains a Redirection Table for the interrupt input pins. Each entry in the Redirection Table can be individually programmed to indicate whether an interrupt on the pin is recognized as either an edge or a level; what vector and also what priority the interrupt has; and which of all possible processors should service the interrupt and how to select that processor (statically or dynamically). The information in the table is used to send interrupt messages to all 82489DX Units via the ICC bus.

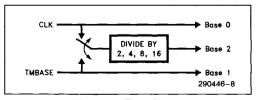

### TIMER

The 82489DX provides a 32-bit wide timer that can be programmed to interrupt the local processor. The timer can be used as a counter to provide a time-base to software running on the processor, or to generate time-slice interrupts local to that processor.

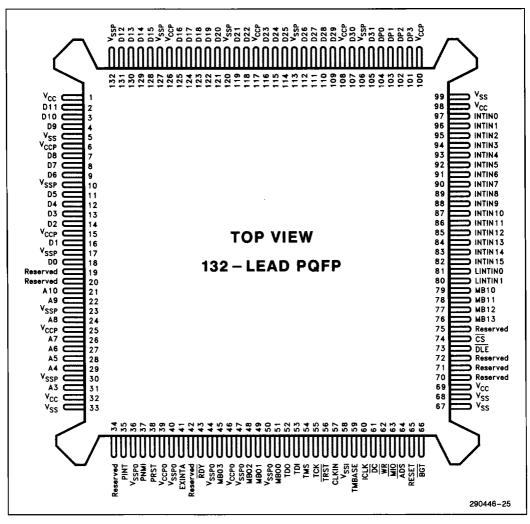

## 3.0 PIN DESCRIPTION

The 82489DX pin description is organized in a small number of functional groups. Pin definitions and protocols have been designed to minimize interface issues. In particular, they support the notion of independently controlled address and data phases. The primary host interface is synchronous in nature.

In the following pin definition table if the signal name has (\_\_) over it, the signal is in its active state when it has a low level. The signal direction column identifies output only signals as a continuous drive (O), tristate (T/S), or open drain (O/D). All bi-directional (BI-D) signals have tri-stating outputs.

# Pin Definition Table

| Symbol                 | Pin No.  | Туре | Function                                                                                                                                                                                                                                                                                                     |

|------------------------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSTEM PIN             | IS       |      |                                                                                                                                                                                                                                                                                                              |

| RESET                  | 65       | I    | The <b>RESET INPUT</b> forces 82489DX to enter its initial state. The 82489DX Local Unit in turn asserts it PRST (Processor Reset) output. All tri-state outputs remain in high impedance until explicitly enabled.                                                                                          |

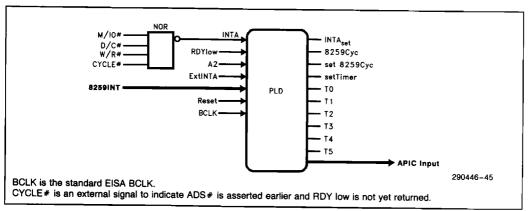

| ExtINTA                | 41       | 0    | The EXTERNAL INTERRUPT ACKNOWLEDGE output is asserted (high) when an external interrupt controller (e.g., 8259) is expected to respond to the current INTA cycle. If deasserted (low), 82489DX will respond, and the INTA cycle must not be delivered to the external controller.                            |

| CLKIN                  | 57       | 1    | CLOCK INPUT provides reference timing for most of the bus signals.                                                                                                                                                                                                                                           |

| TRST                   | 56       | 1    | <b>TEST RESET</b> is the JTAG compatible boundary scan TAP controller reset pin. A weak pull-up keeps the pin high if not driven.                                                                                                                                                                            |

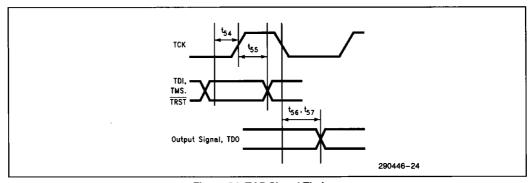

| TCK                    | 55       | ı    | <b>TEST CLOCK</b> is the clock input for the JTAG compatible boundary scan controller and latches.                                                                                                                                                                                                           |

| TDI                    | 53       | ı    | <b>TEST DATA INPUT</b> is the test data input pin for the JTAG compatible boundary scan chain and TAP controller. A weak pull-up keeps this pin high if not driven.                                                                                                                                          |

| TDO                    | 52       | 0    | TEST DATA OUTPUT is the test data output for the JTAG compatible boundary scan chain.                                                                                                                                                                                                                        |

| TMS                    | 54       | I    | TEST MODE SELECT is the test mode select pin for the JTAG boundary scan TAP controller. A weak pull-up keeps this pin high if not driven.                                                                                                                                                                    |

| TIMER PIN              |          |      |                                                                                                                                                                                                                                                                                                              |

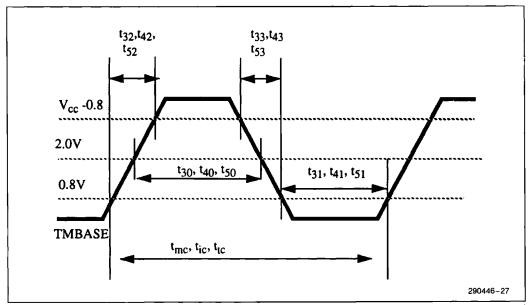

| TMBASE                 | 59       |      | The <b>TIME BASE</b> input provides a standard frequency that is only used by the 82489DX timer and that is independent of the system clock.                                                                                                                                                                 |

| INTERRUPT              | PINS     |      |                                                                                                                                                                                                                                                                                                              |

| INTIN[15:0]            | 82-97    | ļ    | These 16 INTERRUPT INPUT pins accept edge or level sensitive interrupt requests from I/O or other devices. The pin numbers are specified respectively. INTIN15 corresponds to pin number 82, INTIN14 corresponds to pin number 83 etc., and INTIN0 corresponds to pin number 97. These pins are active high. |

| LINTIN[1]<br>LINTIN[0] | 80<br>81 | l    | Two LOCAL INTERRUPT INPUT pins accept edge or level sensitive interrupt requests that can only be delivered to the connected processor. These pins are active high.                                                                                                                                          |

| REGISTER A             | ACCESS P | INS  |                                                                                                                                                                                                                                                                                                              |

| ADS                    | 64       | 1    | ADDRESS STROBE signal indicating the start of a bus cycle. 82489DX does not commit to start the cycle internally until BUS GRANT is detected active.                                                                                                                                                         |

# Pin Definition Table (Continued)

| Symbol                                                                              | Pin No.                                                                                                                                       | Туре                                                         | Function                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REGISTE                                                                             | R ACCES                                                                                                                                       | S PINS                                                       | (Continued)                                                                                                                                                                                                                                                                                                                                                                                   |

| M/IŌ,<br>D/Ō,<br>W/R                                                                | 63<br>61<br>62                                                                                                                                |                                                              | Bus cycle definition signals. Note that since the 82489DX registers can be mapped in either memory or I/O space, the M/IO pin is not used for register access cycles; it is only used to decode interrupt acknowledge cycles.  82489DX does not respond to code read cycles.                                                                                                                  |

| BGT                                                                                 | 66                                                                                                                                            | i                                                            | The <b>BUS GRANT</b> input is optional and is used to indicate the address phase of a bus cycle in configurations where address timing cannot be inferred from ADS. This signal is really used as an address latch enable, but is named as it is to indicate that it can normally be connected to the Intel Cache Controller generated signal of the same name. Must be tied low if not used. |

| CS                                                                                  | 74                                                                                                                                            | ı                                                            | The <b>CHIP SELECT</b> input indicates that the 82489DX registers are being addressed.                                                                                                                                                                                                                                                                                                        |

| A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10                                       | 31<br>29<br>28<br>27<br>26<br>24<br>22<br>21                                                                                                  | BI-D<br>BI-D<br>BI-D<br>BI-D<br>BI-D<br>BI-D<br>BI-D         | The address pins are used as inputs in addressing internal register space. Output function is reserved. They are also used to latch local unit ID on reset.                                                                                                                                                                                                                                   |

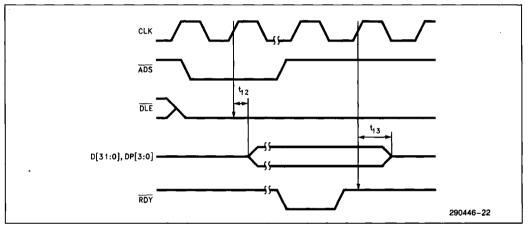

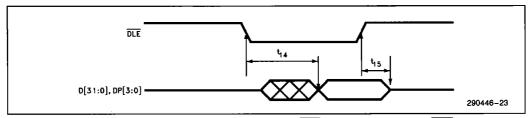

| DLE                                                                                 | 73                                                                                                                                            | į                                                            | DATA LATCH/ENABLE is optional and is used to indicate committing the data phase of a bus cycle in configurations where data timing cannot be inferred from other cycle timings. Must be tied low if not used.                                                                                                                                                                                 |

| D31 D30 D29 D28 D27 D26 D25 D24 D23 D22 D21 D20 D19 D18 D17 D16 D15 D14 D13 D12 D11 | 105<br>107<br>109<br>110<br>111<br>112<br>114<br>115<br>116<br>118<br>119<br>121<br>122<br>123<br>124<br>125<br>128<br>129<br>130<br>131<br>2 | BI-D<br>BI-D<br>BI-D<br>BI-D<br>BI-D<br>BI-D<br>BI-D<br>BI-D | The DATA BUS is for all register accesses and interrupt vectoring.                                                                                                                                                                                                                                                                                                                            |

# Pin Definition Table (Continued)

| Symbol   | Pin No.  | Туре    | Function                                                                          |

|----------|----------|---------|-----------------------------------------------------------------------------------|

|          |          |         | (Continued)                                                                       |

| D10      | 3        | BI-D    | <u> </u>                                                                          |

| D9       | 4        | BI-D    |                                                                                   |

| D8       | 7        | BI-D    |                                                                                   |

| D7       | 8        | Bi-D    |                                                                                   |

| D6       | 9        | BI-D    |                                                                                   |

| D5       | 11       | BI-D    |                                                                                   |

| D4       | 12       | BI-D    |                                                                                   |

| D3       | 13       | BI-D    |                                                                                   |

| D2       | 14       | BI-D    |                                                                                   |

| D1       | 16       | BI-D    |                                                                                   |

| D0       | 18       | BI-D    |                                                                                   |

| DP3      | 101      | BI-D    | One Data Parity pin for each byte on the data bus. EVEN parity is generated       |

| DP2      | 102      | BI-D    | any time the data bus is driven by the 82489DX.                                   |

| DP1      | 103      | BI-D    |                                                                                   |

| DP0      | 104      | BI-D    |                                                                                   |

| RDY      | 43       | 0       | READY output indicates that the current bus cycle is complete. In the case of     |

|          |          |         | a read cycle, valid data and the return to inactive state after going active low  |

|          |          |         | may be delayed till DLE goes active.                                              |

| PROCES   | SOR PINS |         |                                                                                   |

| PINT     | 35       | T/S     | The PROCESSOR INTERRUPT OUTPUT indicates to the processor that one                |

|          |          |         | or more maskable interrupts are pending. This pin is tri-stated at reset, and has |

|          |          | 1       | an internal pull-down resistor to prevent false signaling to the processor until  |

|          | L        |         | the 82489DX Local Unit is enabled and this pin is actively driven.                |

| PRST     | 38       | 0       | The PROCESSOR RESET OUTPUT is asserted/de-asserted upon 82489DX                   |

|          | 1        | 1       | reset, and also in response to ICC bus messages with "RESET" delivery             |

|          |          |         | mode. This pin should be used with care.                                          |

| PNMI     | 37       | T/S     | The NON-MASKABLE INTERRUPT output is signaled in respone to ICC bus               |

|          |          |         | messages with "NMI" delivery mode. This pin is tri-stated at reset, and has an    |

|          |          |         | internal pull-down resistor to prevent false signaling to the processor until the |

|          | <u> </u> | <u></u> | Local Unit is enabled and this pin is actively driven.                            |

| ICC BUS  | PINS     |         |                                                                                   |

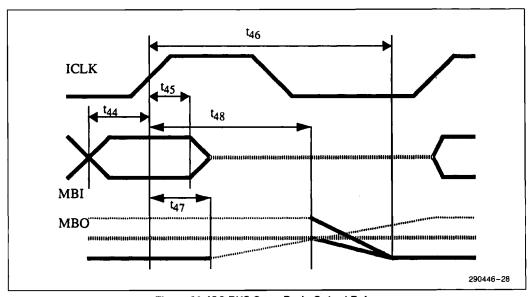

| ICLK     | 60       |         | The ICC BUS CLOCK input provides synchronous operation of the ICC bus.            |

| MBI[3:0] | 76-79    | l i     | The four ICC BUS IN inputs are used for incoming ICC bus messages. In             |

|          |          |         | smaller configurations the ICC bus input and outputs may be tied directly         |

|          |          |         | together at the pins. Pin number for MBI3 is 76, MBI2 is 77, MBI1 is 78 and       |

|          |          |         | MBI0 is 79.                                                                       |

| мвоз     | 45       | O/D     | The four ICC BUS OUT outputs are used for outgoing ICC bus messages. The          |

| MBO2     | 48       |         | current capacity is only 4 mA. So external bufferes will be needed.               |

| MBO1     | 49       |         |                                                                                   |

| MBO0     | 51       |         |                                                                                   |

# Pin Definition Table (Continued)

| Symbol            | Pin No.                                        | Туре  | Function                                                                                                  |

|-------------------|------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------|

| RESERVE           | D PINS                                         |       |                                                                                                           |

| Reserved          | 34, 42                                         | NC    | These pins MUST BE LEFT OPEN.                                                                             |

| Reserved          | 70, 72, 75                                     |       | Reserved by Intel. These pins should be strapped to V <sub>CC</sub> .                                     |

| Reserved          | 71, 19, 20                                     |       | Reserved by Intel. These pins should be strapped to GND.                                                  |

| POWER A           | ND GROUND PI                                   | NS    |                                                                                                           |

| Vcc               | 1, 32, 69, 98                                  | POWER | Nominally + 5V. These pins along with V <sub>SS</sub> and V <sub>SSI</sub> should be separately bypassed. |

| V <sub>CCP</sub>  | 6, 15, 25,100,<br>108, 117, 126                | POWER | Nominally $\pm$ 5V. These pins along with $V_{SSP}$ should be separately bypassed.                        |

| V <sub>CCPO</sub> | 39, 46                                         | POWER | Nominally + 5V. These pins along with V <sub>SSPO</sub> should be separately bypassed.                    |

| V <sub>SS</sub>   | 5, 33, 67,<br>68, 99                           | GND   | Nominally 0V. These pins along with V <sub>CC</sub> should be separately bypassed.                        |

| V <sub>SSP</sub>  | 10, 17, 23, 30,<br>106, 113, 120,<br>127, 132, | GND   | Nominally 0V. These pins along with V <sub>CCP</sub> should be separately bypassed.                       |

| V <sub>SSPO</sub> | 36, 40, 44,<br>47, 50                          | GND   | Nominally 0V. These pins along with V <sub>CCPO</sub> should be separately bypassed.                      |

| V <sub>SSI</sub>  | 58                                             | GND   | Nominally 0V. These pins along with V <sub>CC</sub> should be separately bypassed.                        |

#### NOTE:

VCC, VCCP and VCCPO should be of same voltage. VSS, VSSP, VSSPO and VSSI should be 0V.

# 4.0 FUNCTIONAL DESCRIPTION

As far as interrupt management is concerned, the 82489DX's interrupt control function spans over two functional units, the I/O Unit of which there is one per I/O subsystem, and the Local Unit of which there is one per processor. 82489DX has one I/O unit and one Local Unit in a single package. This section takes a detailed look at both local and I/O Units.

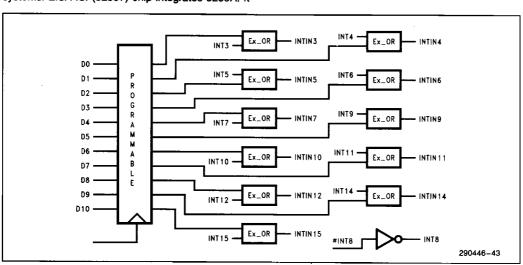

# I/O Unit

The I/O Unit consists of a set of Interrupt Input pins, an Interrupt Redirection Table, and a message unit for sending and receiving messages from the ICC bus. The I/O Unit is where I/O devices inject their interrupts, the I/O Unit selects the corresponding entry in the Redirection Table and uses the information in that entry to format an interrupt request message. The message unit then broadcasts this message over the ICC bus. The content of the Redirection Table is under software control and is assigned benign defaults upon reset. The masks in the Redirectional Table entries are set to 1 at hardware reset to disable the interrupts.

Figure 2. 82489DX I/O Unit Block Diagram

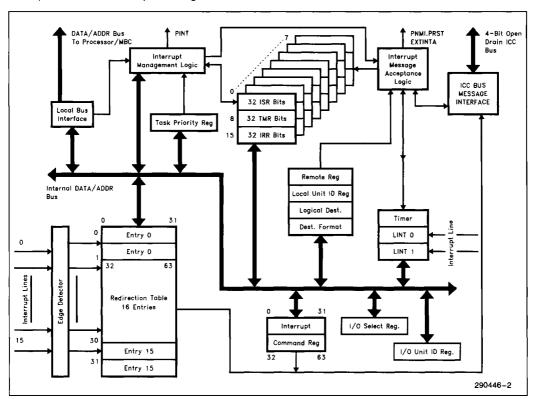

# **Local Unit**

Interrupt Management of the Local Unit is responsible for local interrupt sources, interrupt acceptance, dispensing interrupts to the processor, and sending inter-processor interrupts. Depending on the delivery

mode of the interrupt, zero, one or more units can accept an interrupt. A Local Unit accepts an interrupt only if it will deliver the interrupt to its processor. Accepting an interrupt is purely an inter-82489DX matter; dispensing an interrupt to the local processor only involves a 82489DX and its local processor.

Figure 3. 82489DX Local Unit Block Diagram

# 5.0 INTERRUPT CONTROL MECHANISM

This section describes briefly the interrupt control mechanism in the 82489DX.

# 5.1 Interrupts

The interrupt control function of all 82489DXs are collectively responsible for delivering interrupts from interrupt sources to interrupt destinations in the multiprocossor system. When a processor accepts an interrupt, it uses the vector to locate the entry point of the handler in its interrupt table. The 82489DX architecture allows for 16 possible interrupt priorities; zero being the lowest priority and 15 being the

highest. Priority of interrupt A "is higher than" the priority of interrupt B if servicing A is more urgent than servicing B. An interrupt's priority is implied by its vector; namely priority = vector/16.

With 256 vectors and 16 different priorities, this implies that 16 different interrupt vectors can share a single interrupt priority.

#### TOTAL ALLOWED INTERRUPT VECTORS

Out of 256 vectors, interrupt vectors 0 to 15 should not be used in the 82489DX. Only 240 interrupt vectors (vectors from 16 to 255) are supported in the 82489DX.

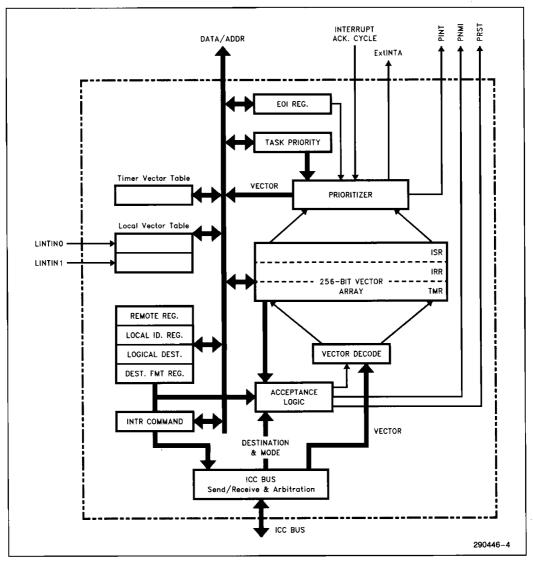

Figure 4. I/O Units and Local Units

#### INTERRUPT SOURCES

Interrupts are generated by a number of different interrupt sources in the system.

Possible interrupt sources are:

- Externally connected (I/O) devices. Interrupts from these external sources manifest themselves as edges or levels on interrupt input pins and can be redirected to any processor.

- Locally connected devices. These originate as edges or levels on interrupt pins, but they are al ways directed to the local processor only.

- 82489DX timer generated interrupts. Like locally connected devices, 82489DX timer can only interrupt its local processor.

- Processors. A processor can interrupt any individual processor or sets of processors. This supports software self-interrupts, preemptive scheduling, TLB flushing, and interrupt forwarding. A processor generates interrupts by writing to the interrupt command register in its Local Unit.

#### INTERRUPT DESTINATIONS

I/O Units can only source interrupts whereas Local Units can both source and accept interrupts, so whenever "interrupt destination" is discussed, it is implied that the Local Unit is the destination of the interrupt. In physical mode the destination processor is specified by a unique 8-bit 82489DX local ID. Only a single destination or a broadcast to all (LOCAL ID of all ones) can be specified in physical destination mode.

In logical mode destinations are specified using a 32-bit destination field. All Local Units contain a 32-bit Logical Destination register against which the destination field of the interrupt is matched to determine if the receiver is being targeted by the interrupt. An additional 32-bit Destination Format register in each Local Unit enables the logical mode addressing.

## INTERRUPT DELIVERY

The description of interrupt delivery makes frequent use of the following terms:

Each processor has a processor priority that reflects the relative importance of the code the processor is currently executing. This code can be part of a process or thread, or can be an interrupt handler. A processor's priority fluctuates as a processor switches threads, a thread or handler raises and lowers its priority level to mask out interrupt, and the processor enters an interrupt handler and returns from an interrupt handler to previously interrupted activity.

- A processor is lowest priority within a given group of processors if its processor priority is the lowest of all processors in the group. Note that more than one processor can be the lowest priority in a given group.

- A processor is the focus of an interrupt if it is currently servicing that interrupt, or if it currently has a request pending for the interrupt.

Interrupt delivery begins with an interrupt source injecting its interrupt into the interrupt system at one of the 82489DX. Delivery is complete only when the servicing processor tells its 82489DX Local Unit it is complete by issuing an end-of-interrupt (EOI) command to its 82489DX Local Unit. Only then has all (relevant) internal state regarding that occurrence of the interrupt been erased. The interrupt system guarantees exactly-once delivery semantics of interrupts to the specified destinations. Exactly-once guaranteed delivery implies a number of things:

The interrupt system never rejects interrupts; it never NAKs interrupt injection, interrupts are never lost, and the same interrupt (occurrence) is never delivered more than once.

Clearly a single edge interrupt or level interrupt counts as a single occurrence of an interrupt. In uniprocessor systems, an occurrence of an interrupt that is already pending (IRR) cannot be distinguished from the previous occurrence. All occurrences are recorded in the same IRR bit. They are therefore treated as "the same" interrupt occurrence.

For lowest-priority delivery mode, by delivering an interrupt first to its focus processor (if it currently has one), the identical behavior can be achieved in a MP (Multiprocessor) system. If an interrupt has a focus processor then the interrupt will be delivered to the interrupt's focus processor independent of priority information. This means that even if there is a lower priority processor compared to the focus processor, the interrupt still gets delivered to the focus processor.

Each edge occurring on an edge triggered interrupt input pin is clearly a one-shot event; each occurrence of an edge is delivered. An active level on a level triggered interrupt input pin represents more of a "continuous event". Repeatedly broadcasting an interrupt message while the level is active would cause flooding of the ICC bus, and in effect transmits very little useful information since the same processor (the focus) would have to be the target.

Instead, for level triggered interrupts the 82489DX merely recreate the state of the interrupt input pin at the destination . The source 82489DX accomplishes this by tracking the state of the appropriate destina-

tion 82489DX's Interrupt Request Register (or pending bit) and only sending inter-82489DX messages when the state of the interrupt input pin and the destination's interrupt request enter a disagreement. Unlike edge triggered interrupts, when a level interrupt goes into service, the interrupt request at the servicing 82489DX is not automatically removed. If the handler of a level sensitive interrupt executes an EOI then that interrupt will immediately be raised to the processor again, unless the processor has explicitly raised its task priority, or the source of that interrupt has been removed.

# 5.2 Interrupt Redirection

This section specifically talks about how a processor is picked during interrupt delivery. The 82489DX supports two modes for selecting the destination processor: Fixed and Lowest Priority.

## • Fixed Delivery Mode

In fixed delivery mode, the interrupt is unconditionally delivered to all local 82489DXs that match in the destination information supplied with the interrupt. Note that for I/O device interrupts typically only a single 82489DX would be listed in the destination. Priority and focus information are ignored. If the priority of a destination processor equal to or higher than the priority of the interrupt, then the interrupt is held pending locally in the destination processor's Local Unit, until the processor priority becomes low enough at which time the interrupt is dispensed to the processor. More than one processor can be the destination in fixed-delivery mode.

#### Lowest Priority Delivery Mode

Under the lowest priority delivery mode, the processor to handle the interrupt is the one in the specified destination with the lowest processor priority value. If more than one processor is at the lowest priority, then a unique arbitration ID is used to break ties. For lowest priority dynamic delivery, the interrupt will always be taken by its focus processor if it has one. The lowest priority delivery method assures minimum interruption of high priority tasks. Since each Local Unit only knows its own processor priority, determining the lowest priority processor is done by arbitration on the ICC bus. Only one processor can be the destination in lowest-priority delivery mode.

#### **INTER-82489DX COMMUNICATION**

All I/O and Local Units communicate during interrupt delivery. Interrupt information is exchanged between different units on a dedicated five wire ICC bus in the form of broadcast messages. A 82489DX Unit's 8-bit ID is used as its name for the purpose of using the ICC bus, and all 82489DX units using one ICC bus should be assigned a different ID. The Arbitration

ID of the Local Units used to resolve tles during lowest priority arbitration is also derived from the Local Unit's ID.

# 6.0 82489DX LOCAL UNIT REGISTERS DESCRIPTION

# 6.1 Local Unit ID Register

Each 82489DX Local Unit has a register that contains the Local Unit's 8-bit ID. The Local Unit ID serves as a physical name of the 82489DX Local Unit. It can be used in specifying destination information and is also used for accessing the ICC bus. Eight address lines A[10]-A[3] are sampled on every clock edge while RESET is asserted. The last sample remains in the Local Unit ID register after reset. Alternatively, the ID can be loaded with a register write as part of software initialization. The Local Unit ID is read-write by software.

|             | <br> |      |       | <br> |

|-------------|------|------|-------|------|

| Bits [3124] | 1    | Bits | [230] |      |

## 82489DX Local Unit ID Register

Bits [31..24] Local Unit ID: The Local Unit ID serves as the physical "name" of the Local Unit used for addressing the 82489DX in physical destination mode and for the ICC bus usage. In a system with say four 82489DX, there are 4 Local Units and 4 I/O Units. All the 8 units should be assigned different IDs. For future compatibility use only IDs from 0 to 14.

Bits [23..0] Bits [23..0] are Reserved. They should be written with 0.

# 6.2 Destination Format Register

Interrupt Destination can be either addressed physically or logically. When the interrupt message addresses the destination physically, each 82489DX in the ICC bus compares the address with its own unit ID. If the message is a broadcast type then every Local Unit accepts the interrupt.

When the message addresses the destination using logical addressing scheme each Local Unit in the ICC bus compares the logical address in the interrupt message with its own Logical Destination Register. If there is a bit match (i.e., if at least one of the corresponding pair of bits match) this local unit is selected for delivery.

All the 32 bits of Destination Format Register of all 82489DX connected in the ICC bus should be written with "1" to enable the addressing scheme.

**Destination Format Register**

Bits [31:0]

Logical Destination Register

Bits [31:0]

For future compatibility, use only bits 31-24 of Logical Destination Register. For binary compatibility, it is strongly recommended that 82489DX software use only 8 MSB of Logical Destination Register.

# 6.3 Local Interrupt Vector Table Registers

The Redirection Table serves to steer interrupts that originate in the I/O subsystems to the processors. The Local Vector Table is its equivalent for interrupts that are restricted to only the local processor. The Local Vector Table contains three 32-bit registers. Register 0 corresponds to the timer, registers 1 and 2 correspond to local interrupt input pins, LINTINO and LINTIN1.

The format of both the Local 0 and Local 1 interrupt vector tables are identical. The following register description talks about both Local Interrupts 0,1 vectors.

## Local Interrupts 0, 1 Interrupt Vectors

Vector: [Bits 7-0]

This is the vector to use when generating an interrupt for this entry.

Delivery Mode: [Bits 10-8]

000: Fixed

001: <reserved>

010: <reserved>

011: <reserved>

100: NMI

101: <reserved>

110: <reserved>

111: ExtINT

000: (fixed) means deliver the signal on the INT pin of the local processor. Trigger mode for "fixed" Delivery Mode can be edge or level

100: (NMI) means deliver the signal on the NMI pin of the local processor. Vector information is ignored. A Delivery Mode equal to "NMI" requires a "level" triggered mode.

111: (ExtINTA) means deliver the signal to the INT pin of the local processor as an interrupt that originated in an externally connected (8259A compatible) interrupt controller. ExtINTA pin is as-serted also. The INTA cycle that corresponds to this ExtINTA delivery, should be routed to the external controller that is expected to supply the vector. A delivery mode of ExtINT requires an edge trigger mode. (See the section on compatiblity for more details.)

Bit 11:

Bit 11 is Reserved. It should be written 0.

Delivery Status: [Bit 12]

This field is software-read only. Software writes to this field (as part of a 32-bit word) have no effect on this bit. Delivery status is a 1-bit field that contains the current status of the delivery of this interrupt. Two states are defined.

- **0:** (idle) means that there is currently no activity for this interrupt.

- (send pending) indicates that the interrupt has been injected, but its delivery is temporarily held up by the recently injected interrupts that are in the process of being delivered.

|              | _      |        |        |        |        |        |             |            |

|--------------|--------|--------|--------|--------|--------|--------|-------------|------------|

| Bits [31:17] | Bit 16 | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bits [10:8] | Bits [7:0] |

Figure 5. Local Vector Table

Bit 13:

Bit 13 is Reserved. It should be written

0.

Remote IRR: [Bit 14]

This bit is used for level triggered local interrupts; its meaning is undefined for edge triggered interrupts. Remote IRR mirrors the interrupt's IRR bit of this local unit. Remote IRR is software read-only; software writes to this bit do not affect it.

Trigger Mode: [Bit 15]

The Trigger Mode field indicates the type of signal on the local interrupt pin that triggers an interrupt.

0: indicates edge sensitive,

1: indicates level sensitive.

Only the local interrupt pins can be programmed as edge or level triggered. Timer interrupts are always treated as edges.

MASK: [Bit 16]

0: enables injection of the interrupt,1: masks injection of the interrupt.

Bits [31:17] Bits [31:17] are Reserved. Should be written 0.

# 6.4 Inter-Processor Interrupt Registers

A processor generates inter-processor interrupts by writing to the Interrupt Command Register in its 82489DX Local Unit. Conceptually, this can be thought of as the processor providing the interrupt's Redirection Table Entry on the fly. Not surprisingly, the layout of the Interrupt Command Register resembles that of an entry in the Redirection Table. Note that the format of this register allows a processor to generate any interrupt. A processor may use this to forward device interrupts originally accepted by it to other processors.

All fields of the Interrupt Command Register are read-write by software with the exception of the Delivery Status field which is read-only. Writing to the 32-bit word that contains the interrupt vector causes the interrupt message to be sent.

Vector: [Bits 7-0]

The vector identifies the interrupt being sent. If the Delivery Mode is "Remote Read", then the Vector field contains the address of the register to be read in the remote 82489DX's Local Unit. The addresses are listed in the section discussing 82489DX Local Unit register summary. For example, for ID register, remote read address of 02 should be specified in vector field.

Delivery Mode: [Bits 10-8]

The Delivery Mode is a 3-bit field that specifies how the 82489DX listed in the destination field (bits 63:32) should act upon reception of this signal. Note that certain Delivery Modes will only operate as intended when used in conjunction with a specific Trigger Mode. These restrictions are indicated for each Delivery Mode.

000: (Fixed) means deliver the signal on the INT pin of all processors listed in the destination. Trigger Mode for "fixed" Delivery Mode can be edge or level.

001: (Lowest Priority) means deliver the signal on the INT pin of the processor that is executing at the lower priority among all the processors listed in the specified destination; Trigger Mode for "lowest priority" Delivery Mode can be edge or level.

010: Intel Reserved. Should not be used.

011: (Remote Read) is a request to a remote 82489DX Local Unit to send the value of one of its registers over the ICC bus. The register is selected by providing its address in the Vector field. The register value is latched by the requesting 82489DX and stored in the Remote Register where it can be read by the local processor. A Delivery Mode of "Remote Read" requires an "edge" Trigger Mode.

## Interrupt Command Register [31:0]

- 100: (NMI) means deliver the signal on the NMI pin of all processors listed in the destination, vector information is ignored. A Delivery Mode equal to "NMI" requires a "level" Trigger Mode.

- 101: (Reset) means deliver the signal to all local units listed in the destination. The destination local unit will assert/deassert its PRST output pin. All addressed 82489DX Local Units will assume their reset state but preserve their ID. One side effect of an ICC bus message with Delivery Mode equal to "Reset" that results in a deassert of reset is that all Local Units (whether listed in the destination or not) will reset their lowest-priority tie breaker arbitration ID to their Local Unit ID (see the section on the ICC bus for details). A Delivery Mode of "Reset" requires a "level" Trigger Mode. "RESET" should not be used with "self" or "all incl self" Shorthand mode since it will leave the system in non-recoverable reset state. If "RESET" is used with "all excl self" mode software should make sure that only one CPU executes this instruction in a MP system.

- 110: Intel Reserved. Should not be used.

- 111: Intel Reserved. Should not be used

Destination Mode: [Bit 11]

This field determines the interpretation of the Destination field.

- 0: (Physical Mode): in Physical Mode, a destination 82489DX is identified by its Local Unit ID. Bits 56 through 63 (8 MSB of the destination field) specify the 8-bit 82489DX Local Unit ID.

- 1: (Logical Mode): in Logical Mode, destinations are identified by matching on Logical Destination under the control of the Destination Format Register in each Local 82489DX. The 32-bit Destination field is the logical destination.

Delivery Status: [Bit 12]

Delivery Status is a 1-bit field that contains the current status of the delivery of this interrupt. Two states are defined:

- 0: (Idle) means that there is currently no activity for this interrupt;

- 1: (Send Pending) indicates that the interrupt has been injected, but its delivery is temporarily held up by other recently injected interrupts that are in the process of being delivered;

Delivery Status is software read-only; software writes to this field (as part of a 32-bit word) do not affect this bit. Software can read to find out if the current interrupt has been sent, and the Interrupt Command Register is available to send the next interrupt. If the Interrupt Command Register is overwritten before the Delivery Status is "idle", then the destiny of that interrupt is undefined; i.e., the interrupt may have been lost.

Bit 13: Bit 13 is Reserved . Should be written 0.

Level: [Bit 14]

Software can use this bit in conjunction with the Trigger Mode bit when issuing an inter-processor interrupt to simulate assertion/deassertion of level sensitive interrupts.

To assert: Trigger mode = 1 and Level = 1.

To deassert: Trigger mode = 1 and Level = 0.

For example, a message with Delivery Mode of "Reset", a Trigger Mode of "Level", and Level bit of 0 deasserts Reset to the processor of the addressed 82489 DX Local Unit(s). As a side effect, this will also cause all 82489DX to reset their Arbitration ID to their unit ID. (The Arb ID is used for tie breaking in lowest priority arbitration.)

Trigger Mode: [Bit 15]

Software can use this in conjunction with Level Assert/Deassert to generate interrupts that behave as edges or levels.

0: Edge

Remote Read Status: [Bits 17,16]

This field indicates the status of the data contained in the Remote Read register. This field is read-only to software. Whenever software writes to the Interrupt Command Register using Delivery Mode "Remote Read" the Remote Read status becomes "in-progress" (waiting for the remote data to arrive). The remote 82489DX Local Unit is expected to respond in a fixed amount of ICC bus cycles. If the remote 82489DX Local Unit is unable to do so, then the Remote Read status becomes "Invalid". If successful, the Remote Read status resolves to "Valid". Software should poll this field to determine completion and success of the Remote Read command.

- 00: (invalid): the content of the Remote Read Register is invalid. This is the case after a Remote Read command issued and the remote 82489DX Local Unit was unable to deliver the Register content in time.

- 01: (in progress): a Remote Read command has been issued and this 82489DX is waiting for the data to arrive from the remote 82489DX Local Unit.

- 10: (valid): the most recent Remote Read command has completed and the remote register content in the Remote Read Register is valid.

11: reserved.

Destination Shorthand: [Bits 19,18]

This field indicates whether a shorthand notation is used to specify the destination of the interrupt and if so, which shorthand is used. Destination Shorthands do no use the 32-bit Destination field, and can be sent by software with a single 32-bit write to the 82489DX's Interrupt Command Register. Shorthands are defined for the following common cases: software self interrupt, interrupt to all processors in the system including the sender, interrupts to all processors in the system excluding the sender.

00: (dest field): means that no shorthand is used. The destination is specified in the 32-bit Destination field in the second word (bits 32 to 63) of the Interrupt Command Register.

- 01: (self): means that the current 82489DX Local Unit is the single destination of the interrupt. This is useful for software interrupts. The Destination field in the Interrupt Command Register is ignored. RE-SET Delivery mode should not be used with self destination. Only FIXED delivery mode should be used with SELF.

- 10: (all incl self): means that the interrupt is to be sent to "all" processors in the system including the processor sending the interrupt. The 82489DX will broadcast a message with destination unit ID field set to all ones. RESET assert Delivery mode should not be used with "all incl self" destination.

- 11: (all excl self): means that the interrupt is to be sent to "all" processors in the system with the exception of the processor sending the interrupt. The 82489DX will broadcast a message with destination unit ID field set to all ones. All-exclself is useful during selection of a boot processor (init) and also for TLB flush where "self" is flushed using the processor flush instruction. Only one CPU in a MP system should execute "all excl self" destination if used with RESET Delivery mode.

Bits [31:20] Bits [31:20] are Reserved. They should be written 0.

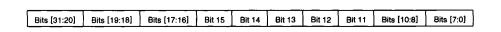

#### Interrupt Command Register [63:32]

Bits [63:32]

Destination: [Bits 63-32]

This field is only used when the Destination Shorthand is set to "Dest Field". If Destination Mode is Physical Mode, then the 8 MSB contain a Destination unit ID. If Logical Mode, the full 32-bit Destination field contains the logical address. The enabling is done by Destination Format Register.

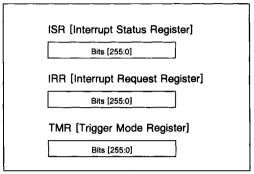

# 6.5 IRR, ISR, TMR Registers

## INTERRUPT ACCEPTANCE

All 82489DX Local Units listen to all messages sent over the ICC bus. For each message, the local unit first checks if it belongs to the destination in the

message. It does this by matching the 32-bit Destination field in the message against its logical Destination Register, if the message addresses in logical mode, and against its physical ID, if the message addresses in physical mode. All 82489DX Local Units that match are said to "belong to the group".

Each 82489DX Local Unit contains three 256-bit registers that play a role in the acceptance of interrupts and in dispensing accepted interrupts to the local processor. Each of these registers is a bit array where bit position i tracks information about the interrupt with vector i. These bits track information about the (PINT) maskable interrupts only. They are not relevant for NMI, RESET or ExtINT type of interrupts. The Interrupt Request Register (IRR) contains the interrupts accepted by this 82489DX Local Unit but not yet dispensed to the processor. The In Service Register (ISR) contains the interrupts that are currently in service by the processor, i.e., the interrupts that have been dispensed to the processor but for which the processor has not yet signaled the End-Of-Interrupt.

Note that the 82489DX's IRR and ISR registers have the same meaning and operation as in the 8259A in fully nested/non-specific EOI mode. Note also that these registers play no role in providing 8259A compatibility. Compatibility is handled by making an external 8259A-style controller directly visible to the processor and having the 82489DX become transparent.

Each interrupt has a vector associated with it, which determines the bit position, and hence the priority for the interrupt. When an interrupt is being serviced, all equal or lower priority interrupts are automatically masked by the 82489DX Local Unit.

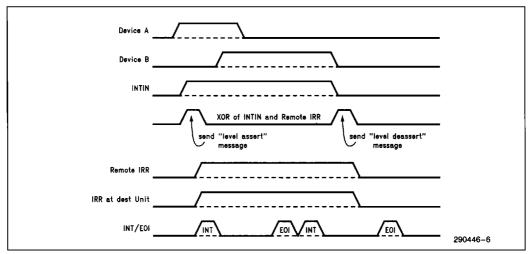

The Trigger Mode Register (TMR) indicates for each interrupt whether the interrupt is edge or level. This information is transmitted with each 82489DX interrupt request message and reflects the Trigger Mode bit in the interrupt's Redirection Table entry. If an interrupt goes in service and the TMR bit is 0 (edge), then the interrupt's IRR bit is cleared at the same time the ISR bit is set. If the TMR bit is 1 (level), then the IRR bit is not cleared when the interrupt goes in service. In the latter case, the IRR bit mirrors the state of the interrupt's input pin.

The following diagram shows 82489DX operation with devices A and B sharing a level triggered interrupt input. The diagram illustrates how Remote IRR, and the IRR bit at the destination 82489DX track the state of INTIN. It also illustrates how an EOI is followed immediately be re-raising the interrupt as long as the INTIN is still asserted by some device.

Figure 6. Interrupt Sharing

ISR, IRR, and TMR are read-only by software. Each of these 256-bit registers is accessed as four separate 32-bit registers. Note that there is no general Interrupt Mask Register (IMR) as in the 8259A. The processor masks interrupts temporarily by writing to the Icoal unit's Task Priority Register (described shortly).

Figure 7. ISR, IRR, and TMR

## TMR (Trigger Mode Register):

If 0 [edge triggered] the corresponding IRR bit is automatically cleared when interrupt service starts. If 1[level triggered] this is not the case; instead, the source 82489DX must explicitly request the IRR bit be cleared (upon deassert of the interrupt input pin or upon sending an appropriate interprocessor interrupt). Upon acceptance of an interrupt, the TMR bit is cleared for edge triggered interrupts and set for level triggered interrupts. This information is carried in the accepted interrupt message. The source 82489DX I/O unit also tracks the state of the destination unit's IRR bit (Remote IRR bit in the Redirection Table). When a level triggered interrupt input is deasserted, the source 82489DX I/O unit detects the discrepancy between the input pin state and the Remote IRR, and automatically sends a message telling the destination 82489DX to clear IRR for the interrupt.

## IRR (Interrupt Request Register):

It contains the active interrupt requests that have been accepted, but not yet dispensed by this 82489DX Local Unit. A bit in IRR is set when the 82489DX Local Unit accepts the interrupt. When TMR is 0, it is cleared when the interrupt is serviced; when TMR is 1, it is cleared when the 82489DX Local Unit receives a message to clear it.

## ISR (In Service Register):

It marks the interrupts that have been delivered to the processor, but that have not been fully serviced in that an End-Of-Interrupt has not yet been received. The ISR register reflects the current state of the processor's interrupt stack.

#### **ACCEPTANCE MECHANISM**

Interrupt acceptance proceeds as follows. If the delivery mode is Fixed, then each unit in the destination group unconditionally accepts the interrupt message and sets the interrupt's IRR bit. If the delivery mode is Lowest Priority, then each processor in the group first checks if it is currently the focus of the interrupt by checking its ISR and IRR. If an 82489DX finds one of these bits set for the incoming interrupt, then that 82489DX Local Unit accepts the interrupt independent of priority, and "signals" the other 82489DX Local Units to abort the priority arbitration. This avoids multiple delivery of a same interrupt occurrence to different processors, consistent with interrupt delivery semantics in uniprocessor systems as described above. If a message is to be delivered for NMI or Reset, then all 82489DX Local Units listed in the destination unconditionally assert/deassert the corresponding output pin. ISR, IRR, etc. are bypassed for NMI or reset and vector information is undefined.

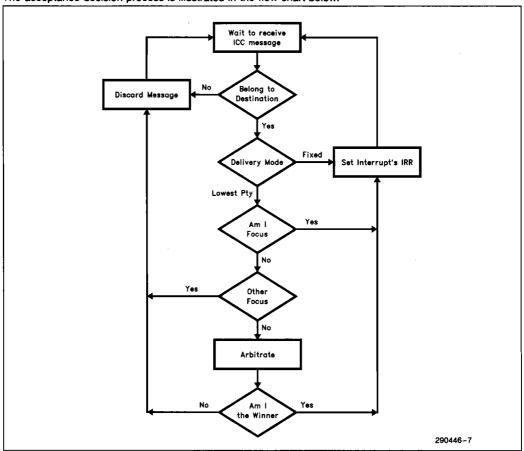

The acceptance decision process is illustrated in the flow chart below.

Figure 8. Interrupt Acceptance Flow Chart

# 6.6 Tracking Processor Priority

Each 82489DX Local Unit should be programmed with task priority so that it can mask interrupts that are less priority than that of the processor temporarily.

Task switching and task priority changes are the result of explicit software action. The operating system may define a number of task scheduling classes. Examples are an idle class, a background class, a foreground class, and a time critical class. Alternatively, different classes can be assigned to user code versus system code. If tasks in different classes are executing when an interrupt comes in, then it may be advantageous to interrupt the processor currently running the task in the least important class. Clearly, if one processor is idle while others are doing work, the idle processor would be the obvious target for servicing the interrupt. This implies that there is use in defining priority levels below all interrupt levels that can participate in lowest priority delivery selection.

At times, the operating system may need to block out interrupts from being serviced. For example, to synchronize access to a shared data structure between a device driver and its interrupt handler the driver raises it priority to equal or higher than the interrupt's priority.

The local 82489DX supports this via its Task Priority Register (the 8259A supports this via the interrupt mask register (IMR).) Software that wants to make use of this is required to inform its 82489DX Local Unit of the prioity change by updating the Task Priority Register. The Task Priority field is 8 bits providing up to 256 distinct priorities. The 4 MSB of this register correspond to the 16 interrupt priorities while the 4 LSB provide more precision. Priorities are best noted as x:y, where x is the value of the 4 MSB and y is the value of the 4 LSB. For example, Task Priority Register values 0:y with 0 < y < 15 (and 0 in the 4 MSB) can be used to represent the priorities of the task scheduling classes described above (y = 0 for idle; y = 1 for background; etc.). Except for interrupts with vectors 0 through 15 (which are often predefined by the processor) which all have priority 0:0, the priorities of all other interrupts and their handlers is x:0 with 1 < x < 15 and is above the base task priorities 0:y.

For example, interrupt vector 123 has priority 7:0 (123/16 = 7) and can be masked by any task that raises its priority to a value equal or higher than 7:0.

82489DX uses Task priority register for the purpose of masking the interrupts. The task priority register should be programmed with a priority value to specifiy the priority of task the processor is executing. 82489DX masks any interrupts of lower or equal priority when compared with task priority.

When task priority register is programmed with the priority 15, all the interrupts are masked. When task priority register is programmed with priority level X, by definition, all the interrupts of priority X and below X will be masked. When task priority register is programmed with the priority 0 then all the interrupts above priority 0 are allowed to interrupt the processor. This means that when task priority register is programmed even with the lowest value, i.e., 0, interrupts of priority 0 will be masked. So only 240 interrupt vectors should be used in 82489DX. Interrupt vectors from 0 to 15 should not be used.

The first priority value computed is the maximum of:

- Task Priority (4msb : 4lsb) and

- the priority of the highest order ISR bit set ((vector/16):0).

The value is used to determine whether or not a pending interrupt can be dispensed to the processor.

The second priority value computed is the maximum of:

- · Task Priority (4msb : 4lsb), and

- the priority of the highest order ISR bit set ((vector/16) :0), and

- the priority of the highest order IRR bit set ((vector/16):0).

This value is used during arbitration as part of lowest-priority delivery.

# **Task Priority Register**

| Bits [31:8] | Bits [7:0] |

|-------------|------------|

|             |            |

From the information in the Task Priority Register and the priority information derived from the ISR and IRR register, the 82489DX Local Unit computes two additional priority values:

Bits [31:8] Bits [31:8] are Reserved. They should be written 0.

Bits [7:0] Task Priority

Bits [7:0] are used to specify the task priority.

# 6.7 Dispensing Interrupts

# DISPENSING INTERRUPTS TO THE LOCAL PROCESSOR

Once a 82489DX Local Unit accepts an interrupt, it guarantees delivery of the interrupt to its local processor. (This part of the 82489DX functions similarly to an 8259A.) Dispensing a maskable interrupt to the local processor begins when the Local Unit asserts the INT pin of its processor. If the processor has interrupts enabled, it will respond by issuing an INTA cycle. This causes the Local Unit to freeze its internal priority state and release the 8-bit vector of the highest priority interrupt on the data bus where it is read by the processor and used to find the handler's entry point. The INT/INTA protocol also causes the interrupt's ISR bit to be set. The corresponding bit in the IRR register is only cleared if the TMR register indicates it should do so (edge triggered interrupts), otherwise (level triggered interrupts). IRR is only cleared when the Interrupt Input Pin is deasserted.

# 6.8 Spurious Interrupt Vector Register

#### SPURIOUS INTERRUPT

Note that it can happen that a level-triggered interrupt is deasserted right before its INTA cycle. In that case, all IRR bits may be clear and the prioritizer may not find a vector to give to the processor. To satisfy the processor's demand for a vector, instead, the 82489DX will return a spurious interrupt vector instead.

A similar situation may occur when the processor raises its Task Priority at or above the level of the interrupt for which the Processor INT pin is currently being asserted. When the INTA cycle is issued, the interrupt that was to be dispensed has become masked (masked but remembered).

Dispensing the spurious interrupt vector does not affect the ISR register, so the handler for this vector should just return without EOI. If the vector is shared with a valid interrupt, then the handler can read the vector's bit in the ISR register to check if it is invoked for the valid interrupt (ISR bit set) or not (ISR bit clear). Given the range of 240 vectors, overloading the spurious interrupt with a valid interrupt is not expected to be common practice. The spurious interrupt vector to be used by a Local Unit is programmable via the Spurious Interrupt Vector Register.

#### **UNIT ENABLE**

It is possible that Local Units exist in the system that do not have a processor to which to dispense interrupts. The only danger this represents in the system is that if any interrupt is broadcast to all processors using lowest priority delivery mode when all processors are at the lowest priority, there is a chance that a Local Unit without the processor may accept the interrupt if this Local Unit happens to have the lowest Arb ID at the time. To prevent this from happening, all Local Units initialize in the disabled state and must be explicitly enabled before they can either start accepting or transmitting messages from the ICC bus. A disabled 82489DX Local Unit only responds to messages with Delivery Modes set to "Reset". Reset deassert messages should be sent in Physical Destination mode using the target's Local Unit ID since the logical destination information in the Icoal units is undefined (all zeroes) when the 82489DX comes out of Reset.

| Bits [31:9]      | Bit 8          | Bits [7:0]     |   |

|------------------|----------------|----------------|---|

| Figure 9. Spurio | us Interrupt V | ector Register | _ |

Bits [31 .. 9] Reserved Bits. Should be written 0.

Unit Enable: [Bit 8]

- 0: When a 0 is written to this bit, this Local Unit gets disabled with regard to responding to messages sent as well as transmitting on the ICC bus. It only responds to messages with Delivery Mode set to "Reset". Reading a 0 at this bit indicates that the unit is disabled.

- 1: When a 1 is written to this bit, the current Local Unit is enabled for both transmitting and receiving unit messages. Reading a 1 at this bit indicates that the unit is enabled.

Spurious Vector: [Bits 7-0]

For future compatibility, bits [3-0] should be 1111.

# 6.9 End-of-Interrupt (EOI) Register

Before returning from the interrupt handler, software must issue an End-Of-Interrupt (EOI) command to the 82489DX Local Unit. The data written to EOI register is don't care. This tells the 82489DX to clear the highest priority bit in the ISR register since the interrupt is no longer in service. Upon EOI, 82489DX goes through prioritization returning to the next highest priority activity. This can be a previously interrupted handler (from ISR), a pending interrupt request (from IRR), or an interrupted task (from Task Priority).

Bits [31:0]

Figure 10. EOI Register

Bits [31:0]: are don't care.

# 6.10 Remote Read Register

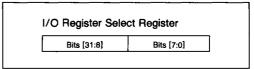

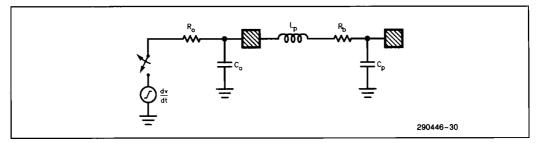

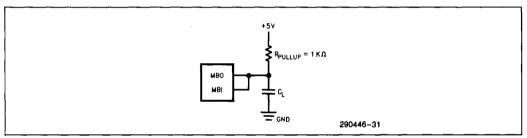

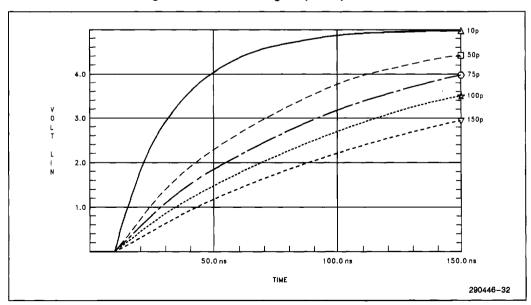

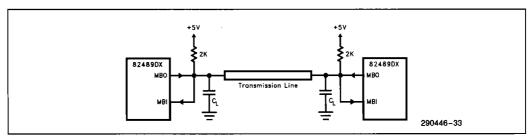

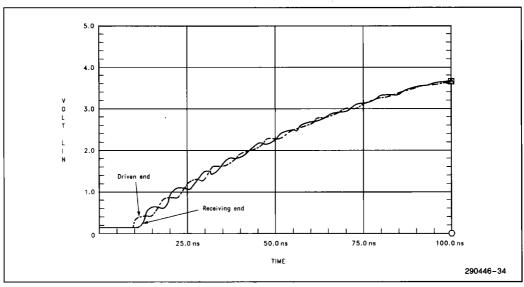

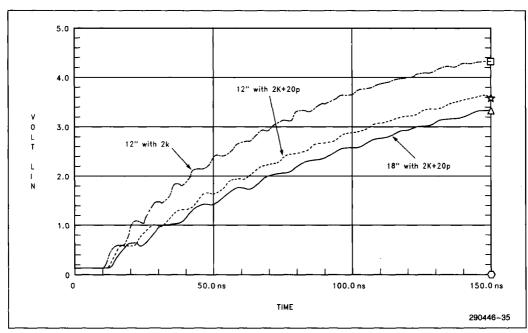

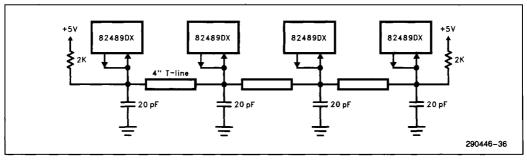

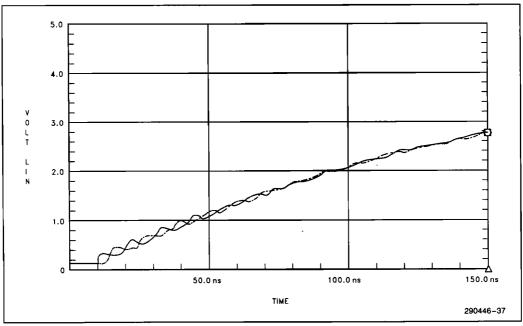

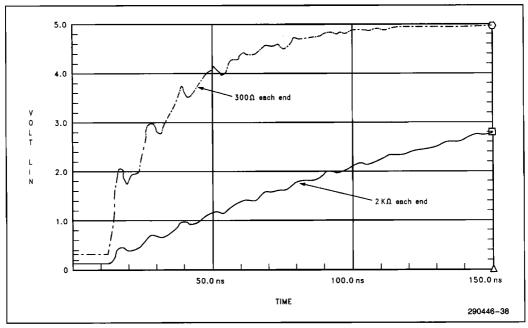

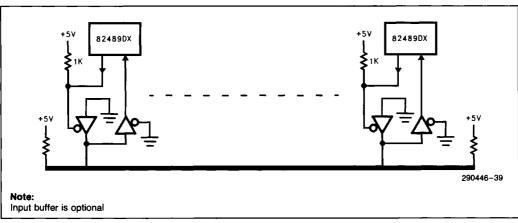

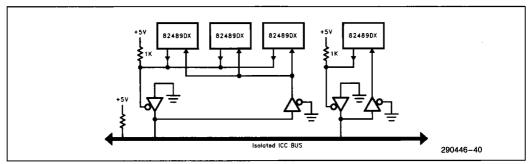

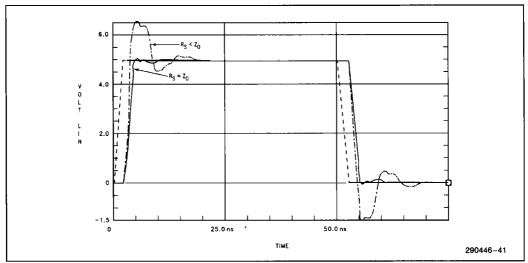

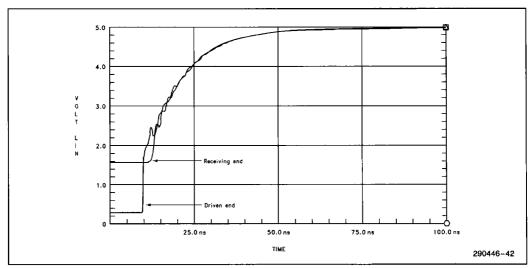

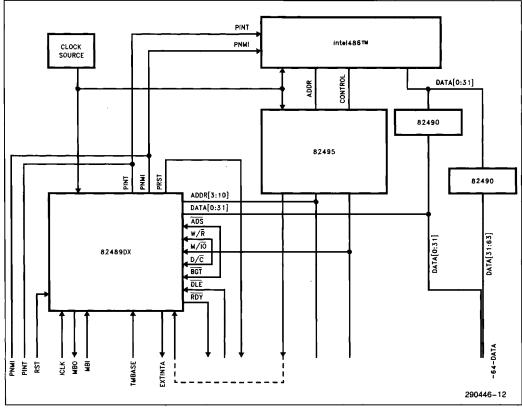

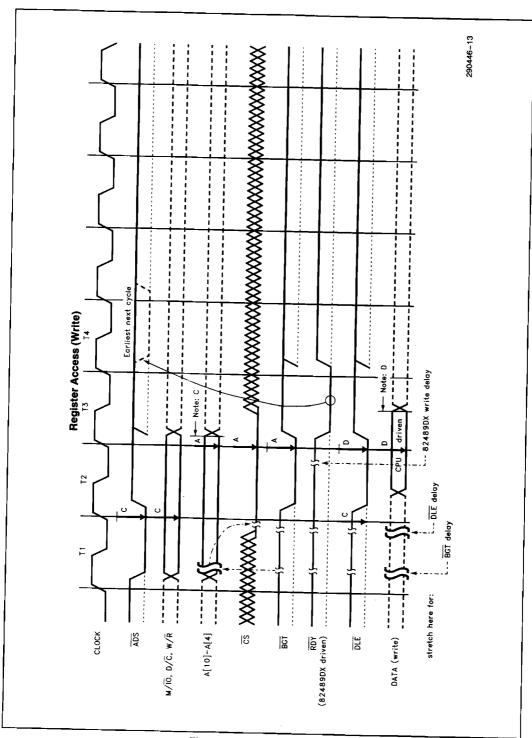

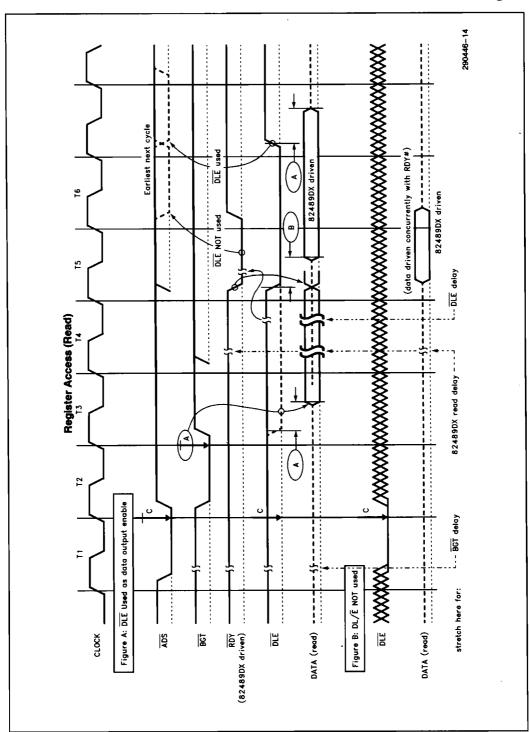

Since all 82489DX Local Units would typically occupy the same address range, an 82489DX local unit's registers can only be accessed by the local processor. From a system debugging point of view, this would mean that a large amount of state would become inaccessible if its corresponding processor hangs for whatever reason. To assist in the debugging of MP systems, the 82489DX support a mechanism that provides read-only access to any register in any other 82489DX local unit in the system.