# Intel 450KX/GX PCIset Specification Update 82454KX/GX (PB) 82453KX/GX (MC) 82452KX/GX (DP) 82451KX/GX (MIC)

Release Date: April 1998

Order Number: 243109-014

The Intel 450KX/GX PCIset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel 450KX/GX PCIset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

The Specification Update should be publicly available following the last shipment date for a period of time equal to the specific product's warranty period. Hardcopy Specification Updates will be available for one (1) year following End of Life (EOL). Web access will be available for three (3) years following EOL.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com

Copyright © Intel Corporation 1998.

\* Third-party brands and names are the property of their respective owners.

| F  | REVISION HISTORY                                       | v  |

|----|--------------------------------------------------------|----|

| F  | PREFACE                                                | vi |

| Ра | rt I: Specification Update for the Intel 450KX PCIset  |    |

| (  | GENERAL INFORMATION                                    | 3  |

| ŝ  | SPECIFICATION CHANGES                                  | 8  |

| E  | ERRATA                                                 | 11 |

| ŝ  | SPECIFICATION CLARIFICATIONS                           | 29 |

| [  | DOCUMENTATION CHANGES                                  | 30 |

| Ра | rt II: Specification Update for the Intel 450GX PCIset |    |

| (  | GENERAL INFORMATION                                    | 35 |

| Ş  | SPECIFICATION CHANGES                                  | 40 |

| E  | ERRATA                                                 | 46 |

| Ş  | SPECIFICATION CLARIFICATIONS                           | 61 |

| [  | DOCUMENTATION CHANGES                                  | 62 |

|    |                                                        |    |

### CONTENTS

## **REVISION HISTORY**

| Date of Revision | Version | Description                                                                                                                                                                                                                                                                                                                                     |

|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 1996         | -001    | This document is the first Specification Update for the Intel 450KX/GX PCIset.                                                                                                                                                                                                                                                                  |

| June 1996        | -002    | Updated 450KX PCIset Errata 6, 20, and 21, and 450GX PCIset<br>Erratum 4. Added 450KX PCIset Errata 30 through 33 and 450GX<br>PCIset Errata 12 through 15. Added 450KX and 450GX PCIset<br>Specification Change 1.                                                                                                                             |

| July 1996        | -003    | Added 450KX and 450GX Specification Change 2. Added 450KX<br>Errata 34 through 36 and 45GX Errata 16 through 19.                                                                                                                                                                                                                                |

| August 1996      | -004    | Updated 450KX and 450GX Specification Change 2, 450KX Erratum<br>35, 450GX Errata 13, 17, and 19, and 450KX and 450GX<br>Documentation Change 1. Added 450KX and 450GX Specification<br>Change 3, 450KX Errata 37 and 38, and 450GX Errata 20 through<br>22. Updated plans for 450KX Errata 4, 20, 21, 23 through 25, 27,<br>and 30 through 34. |

| September 1996   | -005    | Updated 450KX and 450GX Documentation Change 1.                                                                                                                                                                                                                                                                                                 |

| October 1996     | -006    | Added Documentation Change 2.                                                                                                                                                                                                                                                                                                                   |

| November 1996    | -007    | Updated 450KX and 450GX Specification Change 2, and 450GX Erratum 20.                                                                                                                                                                                                                                                                           |

| December 1996    | -008    | Added 450GX Specification Changes 4 through 7 and 450GX Errata 23 and 24.                                                                                                                                                                                                                                                                       |

| January 1997     | -009    | Added 450KX Erratum 39 and Specification Clarification 2. Added 450GX Erratum 25 and Specification Clarification 2.                                                                                                                                                                                                                             |

| March 1997       | -010    | Added 450GX Erratum 26. Updated 450GX PCIset Identification Information table.                                                                                                                                                                                                                                                                  |

| May 1997         | -011    | Updated 450GX Erratum 26. Added engineering sample marking and identification information.                                                                                                                                                                                                                                                      |

| October 1997     | -012    | Added 450KX Documentation Change 3, and 450GX Erratum 27 and Documentation Change 3.                                                                                                                                                                                                                                                            |

| March 1998       | -013    | Updated 450GX Specification Change 4. Added 450GX Erratum 28.                                                                                                                                                                                                                                                                                   |

| April 1998       | -014    | Updated 450GX Basic Information Table.                                                                                                                                                                                                                                                                                                          |

### PREFACE

This document is an update to the specifications contained in the *Intel 450KX/GX PCIset* datasheet (Order Number 290523). It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools. It contains Specification Changes, S-Specs, Errata, Specification Clarifications, and Documentation Changes.

#### Nomenclature

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in the next release of the specifications.

S-Specs are exceptions to the published specifications, and apply only to the units assembled under that sspec.

**Errata** are design defects or errors. Errata may cause the Intel 450KX/GX PCIset's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in the next release of the specifications.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These changes will be incorporated in the next release of the specifications.

#### Identification Information

The 82453 Memory Controller can be identified by the following values:

| Vendor ID <sup>1</sup> | Device ID <sup>1</sup> |

|------------------------|------------------------|

| 8086h                  | 84C5h                  |

The 82454 PCI Bridge can be identified by the following values:

| Vendor ID <sup>1</sup> | Device ID <sup>2</sup> |

|------------------------|------------------------|

| 8086h                  | 84C4h                  |

NOTES:

The Vendor ID corresponds to the value in the Vendor ID register of the device's PCI configuration space, at address

offset 00-01h (the A2 stepping of the 82453KX MC located the Vendor ID register at address offset 04-05h).

The Device ID corresponds to the value in the Device ID register of the device's PCI configuration space, at address

offset 02-03h (the A2 stepping of the 82453KX MC located the Device ID register at address offset 06-07h).

# Part I: Specification Update for the Intel 450KX PCIset

### **GENERAL INFORMATION**

#### **Top Markings**

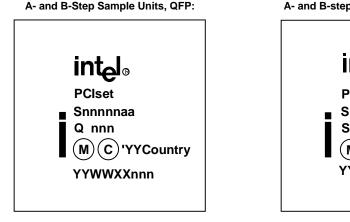

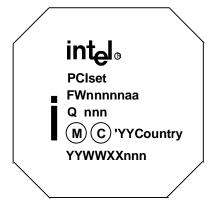

A- and B-step Sample Units, BGA:

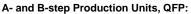

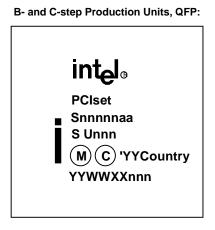

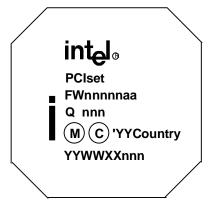

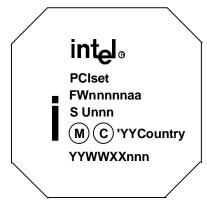

#### NOTES:

- nnnnnaa = Product Number

- Q nnn = Sample Specification Number

- S Unnn = S-spec Number

- 'YY Country = Copyright Dates and Country of Origin

- YYWWXXnnn = Alternative Identification Number

#### A- and B-step Production Units, BGA:

#### INTEL 450KX/GX PCISET SPECIFICATION UPDATE

|                   | Basic Intel 450KX PCIset Identification Information |              |                |                     |                  |        |                 |                   |       |  |  |  |  |

|-------------------|-----------------------------------------------------|--------------|----------------|---------------------|------------------|--------|-----------------|-------------------|-------|--|--|--|--|

| Product<br>Number | Vendor<br>ID                                        | Device<br>ID | Revision<br>ID | Product<br>Stepping | Kit<br>Steppings | S-Spec | v <sub>cc</sub> | T <sub>CASE</sub> | Notes |  |  |  |  |

| S82451KX          | n/a1                                                | n/a1         | n/a1           | A1                  | A2, B0           | Q 312  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| S82451KX          | n/a1                                                | n/a1         | n/a1           | A1                  | A2, B0           | Q 380  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| S82451KX          | n/a1                                                | n/a1         | n/a1           | A1                  | A2, B0           | S U025 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |  |

| S82451KX          | n/a1                                                | n/a1         | n/a1           | A1                  | A2, B0           | S U039 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |  |

| S82452KX          | n/a1                                                | n/a1         | n/a1           | A1                  | A2               | Q 313  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| FW82452KX         | n/a1                                                | n/a1         | n/a1           | A1                  | A2               | Q 316  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2,4   |  |  |  |  |

| S82452KX          | n/a1                                                | n/a1         | n/a1           | A1                  | A2               | Q 381  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| FW82452KX         | n/a1                                                | n/a1         | n/a1           | A1                  | A2               | Q 384  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2,4   |  |  |  |  |

| S82452KX          | n/a1                                                | n/a1         | n/a1           | A1                  | A2               | S U026 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |  |

| FW82452KX         | n/a1                                                | n/a1         | n/a1           | A1                  | A2               | S U029 | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2     |  |  |  |  |

| S82452KX          | n/a1                                                | n/a1         | n/a1           | A1                  | A2               | S U040 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |  |

| FW82452KX         | n/a1                                                | n/a1         | n/a1           | A1                  | A2               | S U043 | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2     |  |  |  |  |

| S82452KX          | n/a1                                                | n/a1         | n/a1           | A3                  | B0               | Q 400  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| FW82452KX         | n/a1                                                | n/a1         | n/a1           | A3                  | B0               | Q 403  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2,4   |  |  |  |  |

| S82452KX          | n/a1                                                | n/a1         | n/a1           | A3                  | B0               | Q 411  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| FW82452KX         | n/a1                                                | n/a1         | n/a1           | A3                  | B0               | Q 414  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2,4   |  |  |  |  |

| S82452KX          | n/a1                                                | n/a1         | n/a1           | A3                  | B0               | S U061 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |  |

| S82453KX          | 8086h <sup>3</sup>                                  | 84C5h3       | 2              | A2                  | A2               | Q 336  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| S82453KX          | 8086h3                                              | 84C5h3       | 2              | A2                  | A2               | Q 382  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| S82453KX          | 8086h <sup>3</sup>                                  | 84C5h3       | 2              | A2                  | A2               | S U027 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |  |

| S82453KX          | 8086h3                                              | 84C5h3       | 2              | A2                  | A2               | S U041 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |  |

| S82453KX          | 8086h                                               | 84C5h        | 4              | A4                  | B0               | Q 401  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| S82453KX          | 8086h                                               | 84C5h        | 4              | A4                  | B0               | Q 412  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| S82453KX          | 8086h                                               | 84C5h        | 4              | A4                  | B0               | S U062 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |  |

| S82454KX          | 8086h                                               | 84C4h        | 2              | A2                  | A2               | Q 337  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| FW82454KX         | 8086h                                               | 84C4h        | 2              | A2                  | A2               | Q 338  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2,4   |  |  |  |  |

| S82454KX          | 8086h                                               | 84C4h        | 2              | A2                  | A2               | Q 383  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |  |

| FW82454KX         | 8086h                                               | 84C4h        | 2              | A2                  | A2               | Q 385  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2,4   |  |  |  |  |

| S82454KX          | 8086h                                               | 84C4h        | 2              | A2                  | A2               | S U022 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |  |

| FW82454KX         | 8086h                                               | 84C4h        | 2              | A2                  | A2               | S U024 | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2     |  |  |  |  |

| S82454KX          | 8086h                                               | 84C4h        | 2              | A2                  | A2               | S U028 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |  |

| FW82454KX         | 8086h                                               | 84C4h        | 2              | A2                  | A2               | S U030 | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2     |  |  |  |  |

int<sub>el</sub>,

| Product<br>Number | Vendor<br>ID | Device<br>ID | Revision<br>ID | Product<br>Stepping | Kit<br>Steppings | S-Spec | v <sub>cc</sub> | T <sub>CASE</sub> | Notes |  |  |  |

|-------------------|--------------|--------------|----------------|---------------------|------------------|--------|-----------------|-------------------|-------|--|--|--|

| S82454KX          | 8086h        | 84C4h        | 2              | A2                  | A2               | S U042 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |

| FW82454KX         | 8086h        | 84C4h        | 2              | A2                  | A2               | S U044 | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2     |  |  |  |

| S82454KX          | 8086h        | 84C4h        | 4              | A4                  | B0               | Q 402  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |

| FW82454KX         | 8086h        | 84C4h        | 4              | A4                  | B0               | Q 404  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2,4   |  |  |  |

| S82454KX          | 8086h        | 84C4h        | 4              | A4                  | B0               | Q 413  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 4     |  |  |  |

| FW82454KX         | 8086h        | 84C4h        | 4              | A4                  | B0               | Q 415  | $3.3~V\pm5\%$   | 0 °C - 85 °C      | 2,4   |  |  |  |

| S82454KX          | 8086h        | 84C4h        | 4              | A4                  | B0               | S U064 | $3.3~V\pm5\%$   | 0 °C - 85 °C      |       |  |  |  |

#### Basic Intel 450KX PCIset Identification Information (Contd.)

#### NOTES:

1. These components are not visible from the PCI bus, and so do not have Vendor, Device, or Revision ID registers at the PCI specification-defined locations.

2. These components have BGA (Ball Grid Array) packaging.

The A2 82453KX MC's Vendor and Device ID registers are not at the PCI specification-defined locations; the Vendor ID register is located at register offset 04-05h, and the Device ID is located at 06-07h.

4. These are engineering samples only, provided under an Intel 450KX PCIset loan agreement.

#### Summary Table of Changes

The following table indicates the Specification Changes, Errata, Specification Clarifications, or Documentation Changes which apply to the Intel 450KX PCIset. Intel intends to fix some of the errata in future steppings of the component(s), and to account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

#### CODES USED IN SUMMARY TABLE

| X:                        | Specification Change, Erratum, Specification Clarification, or Documentation Change applies to the given stepping. |

|---------------------------|--------------------------------------------------------------------------------------------------------------------|

| Doc:                      | Intel intends to update the appropriate documentation in a future revision.                                        |

| Fix:                      | This erratum is intended to be fixed in a future stepping of the component.                                        |

| Fixed:                    | This erratum has been previously fixed.                                                                            |

| NoFix:                    | There are no plans to fix this erratum.                                                                            |

| (No mark) or (blank box): | This item is fixed in or does not apply to the given kit stepping.                                                 |

| Shaded:                   | This erratum is either new or modified from the previous version of the document.                                  |

| NO. | A2 | <b>B0</b> | Plans | SPECIFICATION CHANGES                                          |

|-----|----|-----------|-------|----------------------------------------------------------------|

| 1   | Х  | Х         | Doc   | PLLRST pin added                                               |

| 2   | Х  | Х         | Doc   | Valid memory timing parameters                                 |

| 3   | Х  | Х         | Doc   | CMOS overshoot/undershoot specification                        |

| NO. | A2 | B0        | Plans | ERRATA                                                         |

| 1   | Х  |           | Fixed | Stop Clock Acknowledge cycles may confuse buffers              |

| 2   | Х  |           | Fixed | 0-byte length write may cause subsequent write failure         |

| 3   | Х  |           | Fixed | Inbound read may be accepted despite posted outbound write     |

| 4   | Х  | Х         | NoFix | SMRAM addresses may not be decoded correctly                   |

| 5   | Х  |           | Fixed | Mixed read lines and partials may corrupt data                 |

| 6   | Х  |           | Fixed | Inbound write posting may cause write failure                  |

| 7   | Х  |           | Fixed | RMW with line write may cause data corruption                  |

| 8   | Х  |           | Fixed | Inbound write may collide with some special cycles             |

| 9   | Х  |           | Fixed | Extended read-around-write may corrupt write data              |

| 10  | Х  |           | Fixed | Outbound posted write after inbound read prefetch may hang     |

| 11  | Х  |           | Fixed | Inbound posted write with 1:1 interleaving may corrupt data    |

| 12  | Х  |           | Fixed | RAW may cause data corruption                                  |

| 13  | Х  |           | Fixed | Data transfer order 3 may cause data to be issued out of order |

| 14  | Х  |           | Fixed | PCI address parity error may cause dropped transaction         |

| 15  | Х  |           | Fixed | System hang with inbound write posting enabled                 |

| 16  | Х  |           | Fixed | RAW may cause data corruption during refresh                   |

| NO. | A2 | B0 | Plans | ERRATA                                                               |

|-----|----|----|-------|----------------------------------------------------------------------|

| 17  | Х  |    | Fixed | GAT devices may time out during inbound read prefetch                |

| 18  | Х  |    | Fixed | Data may be corrupted if RCD = 4 and LWC = 3                         |

| 19  | Х  |    | Fixed | T <sub>CO_MAX</sub> specification not met for GTL+ signals           |

| 20  | Х  | Х  | NoFix | RAW may hang 1:1 or 2:1 interleaved MP systems                       |

| 21  | Х  | Х  | NoFix | Mixed interleave increments may cause data corruption                |

| 22  | Х  | Х  | NoFix | Parity error may occur for ADS# during BINIT#                        |

| 23  | Х  | Х  | NoFix | Hang with PCI-to-PCI bridges in MP systems                           |

| 24  | Х  | Х  | NoFix | PCI_RST# not asserted asynchronously                                 |

| 25  | Х  | Х  | NoFix | BERR# to BINIT# conversion may prevent recovery from BINIT#          |

| 26  | Х  |    | Fixed | Error reporting registers may not record error information correctly |

| 27  | Х  | Х  | NoFix | Combination of ECC errors may cause one error to be undetected       |

| 28  | Х  |    | Fixed | 16-Byte write may hang system                                        |

| 29  | Х  | Х  | NoFix | 16-Byte read with two ECC errors may not be reported correctly       |

| 30  | Х  | Х  | NoFix | Inbound locked PCI transactions may hang system                      |

| 31  | Х  | Х  | NoFix | Retry on inbound read may corrupt outbound data                      |

| 32  | Х  | Х  | NoFix | ADS# in last clock of BINIT# prevents recovery                       |

| 33  | Х  | Х  | NoFix | Some signals indeterminate after RESET# deassertion                  |

| 34  | Х  | Х  | NoFix | Delayed read from PCI-to-PCI bridge may corrupt data                 |

| 35  | Х  | Х  | NoFix | Page Open Policy of "hold page open" may corrupt write data          |

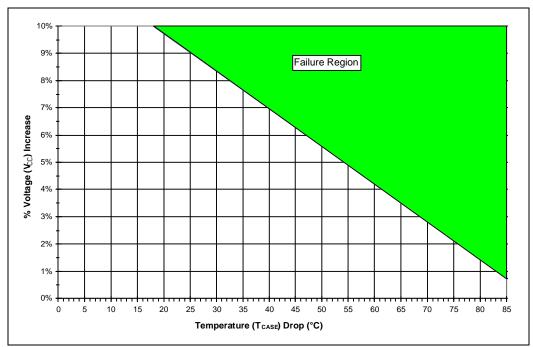

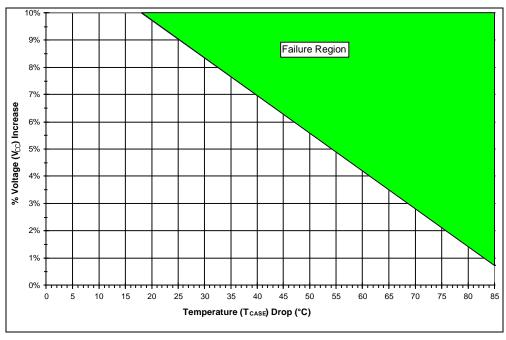

| 36  | Х  | Х  | NoFix | T <sub>CASE</sub> drop plus voltage swing may cause DPLL failure     |

| 37  | Х  | Х  | NoFix | Memory gap reclaiming may corrupt data                               |

| 38  | Х  | Х  | NoFix | RAW may corrupt write data in 1:1 interleaving                       |

| 39  | Х  | Х  | NoFix | BINIT# assertion may cause active RAS# negation                      |

| NO. | A2 | B0 | Plans | SPECIFICATION CLARIFICATIONS                                         |

| 1   | Х  | Х  | Doc   | Explicit writebacks claimed by 82454KX PB                            |

| NO. | A2 | B0 | Plans | DOCUMENTATION CHANGES                                                |

| 1   | Х  | Х  | Doc   | Register offset and default value correction                         |

| 2   | Х  | Х  | Doc   | CMOS definition should be 3.3 V or 5 V                               |

| 3   | Х  | Х  | Doc   | Pull-up resistor required on PCLK                                    |

### **SPECIFICATION CHANGES**

#### 1. PLLRST Pin Added

A PLLRST pin will be added to the definition of each device in the Intel 450KX PCIset. The pin numbers will be assigned as follows:

| Device          | Pin Number |

|-----------------|------------|

| 82454KX PB QFP  | 301        |

| 82454KX PB BGA  | A5         |

| 82453KX DC QFP  | 81         |

| 82452KX DP QFP  | 202        |

| 82452KX DP BGA  | B12        |

| 82451KX MIC QFP | 42         |

This signal will be added to the block diagram in Figure 1 of both Chapter 2 and Chapter 3.

Each of the specified PLLRST pins are 5 V tolerant signals.

The signal will be added to Chapter 2, Section 1.4. and to Chapter 3, Sections 1.1., 1.2. and 1.3. as signal "PLLRST", type "I, CMOS", and described as "This pin must be driven high for at least 2 clocks to reset the internal DPLL (Digital Phase Lock Loop). The DPLL should be reset after (or until) the clock input pins are stable at their final operating frequency. This pin does not have an edge rate requirement."

The following sentences will be added to Chapter 2, Section 3.7.2. and Chapter 3, Section 3.4.: "The PLLRST pin must be driven high for at least 2 clocks to reset the internal DPLL. The DPLL should be reset after (or until) the clock input pins are stable at their final operating frequency."

Chapter 4 will be updated to include this pin information throughout.

#### 2. Valid Memory Timing Parameters

The following is a list of timing values which have been validated by Intel. The list is the result of applying the rules set forth in the *Intel 450KX/GX PCIset* datasheet plus a set of filters to eliminate settings that Intel believes would not or could not be used in practice. Note that OEMs must still ensure that the timing parameters used meet the timing constraints for their system design, applicable clock rates, and supported DRAM speeds. See below for a list of acronyms used in the table.

RCD = 3, RCAD = 2, and CSR = 1 for all setting options listed below.

| int <sub>el</sub> . |

|---------------------|

|---------------------|

|     |       |     |      |      |    | 1:1          |   |      |    | 2:1 |      | 4:1 |     |      |  |

|-----|-------|-----|------|------|----|--------------|---|------|----|-----|------|-----|-----|------|--|

| LWC | RASPW | CAH | RCAS | WCAS | RP | CP RBD ACh C |   |      | СР | RBD | ACh  | СР  | RBD | ACh  |  |

| 2   | 5     | 1   | 2    | 2    | 3  | 1            | 2 | 2814 | 2  | 1   | 2834 | 1   | 0   | 2814 |  |

| 2   | 5     | 1   | 3    | 2    | 3  | 1            | 3 | 2914 | 1  | 1   | 2914 | 1   | 0   | 2914 |  |

| 2   | 5     | 1   | 3    | 3    | 3  | 1            | 3 | 2954 | 1  | 1   | 2954 | 1   | 0   | 2954 |  |

| 2   | 6     | 1   | 2    | 2    | 3  | 1            | 2 | 3014 | 2  | 1   | 3034 | 1   | 0   | 3014 |  |

| 2   | 6     | 1   | 3    | 2    | 3  | 1            | 3 | 3114 | 1  | 1   | 3114 | 1   | 0   | 3114 |  |

| 2   | 6     | 1   | 3    | 2    | 4  | 1            | 3 | 3115 | 1  | 1   | 3115 | 1   | 0   | 3115 |  |

| 2   | 6     | 1   | 3    | 3    | 3  | 1            | 3 | 3154 | 1  | 1   | 3154 | 1   | 0   | 3154 |  |

| 2   | 6     | 1   | 3    | 3    | 4  | 1            | 3 | 3155 | 1  | 1   | 3155 | 1   | 0   | 3155 |  |

| 2   | 6     | 2   | 3    | 2    | 3  | 1            | 3 | 3514 | 1  | 1   | 3514 | 1   | 0   | 3514 |  |

| 2   | 6     | 2   | 3    | 2    | 4  | 1            | 3 | 3515 | 1  | 1   | 3515 | 1   | 0   | 3515 |  |

| 2   | 6     | 2   | 3    | 3    | 3  | 1            | 3 | 3554 | 1  | 1   | 3554 | 1   | 0   | 3554 |  |

| 2   | 6     | 2   | 3    | 3    | 4  | 1            | 3 | 3555 | 1  | 1   | 3555 | 1   | 0   | 3555 |  |

| 2   | 6     | 2   | 4    | 3    | 3  | 1            | 4 | 3654 | 2  | 2   | 3674 | 1   | 0   | 3654 |  |

| 2   | 6     | 2   | 4    | 3    | 4  | 1            | 4 | 3655 | 2  | 2   | 3675 | 1   | 0   | 3655 |  |

| 3   | 5     | 1   | 2    | 2    | 3  | 2            | 3 | 4834 | 2  | 1   | 4834 | 1   | 0   | 4814 |  |

| 3   | 5     | 1   | 3    | 2    | 3  | 2            | 4 | 4934 |    |     |      | 1   | 0   | 4914 |  |

| 3   | 5     | 1   | 3    | 3    | 3  | 2            | 4 | 4974 |    |     |      | 1   | 0   | 4954 |  |

| 3   | 6     | 2   | 3    | 2    | 3  | 2            | 4 | 5534 |    |     |      | 1   | 0   | 5514 |  |

| 3   | 6     | 2   | 3    | 2    | 4  | 2            | 4 | 5535 |    |     |      | 1   | 0   | 5515 |  |

| 3   | 6     | 2   | 3    | 3    | 3  | 2            | 4 | 5574 |    |     |      | 1   | 0   | 5554 |  |

| 3   | 6     | 2   | 3    | 3    | 4  | 2            | 4 | 5575 |    |     |      | 1   | 0   | 5555 |  |

| 3   | 6     | 2   | 4    | 3    | 3  | 2            | 5 | 5674 | 2  | 2   | 5674 | 1   | 0   | 5654 |  |

| 3   | 6     | 2   | 4    | 3    | 4  | 2            | 5 | 5675 | 2  | 2   | 5675 | 1   | 0   | 5655 |  |

| 3   | 6     | 2   | 4    | 4    | 4  | 1            | 4 | 5695 | 2  | 2   | 56B5 | 1   | 0   | 5695 |  |

RCD = 3, RCAD = 2, and CSR = 2 for all setting options listed below.

|     |       |     |      |      |    | 1:1 |     |      | 2:1 |     |      | 4:1 |     |      |

|-----|-------|-----|------|------|----|-----|-----|------|-----|-----|------|-----|-----|------|

| LWC | RASPW | CAH | RCAS | WCAS | RP | СР  | RBD | ACh  | СР  | RBD | ACh  | СР  | RBD | ACh  |

| 3   | 6     | 2   | 3    | 4    | 3  | 1   | 3   | D594 | 1   | 1   | D594 | 1   | 0   | D594 |

| 3   | 6     | 2   | 4    | 3    | 4  | 2   | 5   | D675 | 2   | 2   | D675 | 1   | 0   | D655 |

| 2   | 6     | 2   | 3    | 3    | 3  | 1   | 3   | B554 | 1   | 1   | B554 | 1   | 0   | B554 |

#### INTEL 450KX/GX PCISET SPECIFICATION UPDATE

#### NOTE:

| All above | All above values are in number of cycles, not actual bit settings, except ACh (which is the actual bit setting, in hexadecimal). |  |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| RCD:      | RAS# to CAS# Delay: bits 3:2 of the Memory Timing Register (AC-AFh).                                                             |  |  |  |  |  |  |

| RCAD:     | RAS# to Column Address Delay: bit 4 of the Memory Timing Register (AC-AFh).                                                      |  |  |  |  |  |  |

| CSR:      | CAS# Setup to RAS# for CAS# before RAS# refresh: bit 15 of the Memory Timing Register (AC-AFh).                                  |  |  |  |  |  |  |

| LWC:      | Last Write to CAS#: bits 14:13 of the Memory Timing Register (AC-AFh).                                                           |  |  |  |  |  |  |

| RASPW:    | RAS# Pulse Width: bits 12:11 of the Memory Timing Register (AC-AFh).                                                             |  |  |  |  |  |  |

| CAH:      | Column Address Hold Time: bit 10 of the Memory Timing Register (AC-AFh).                                                         |  |  |  |  |  |  |

| RCAS:     | Read CAS# Pulse Width: bits 9:8 of the Memory Timing Register (AC-AFh).                                                          |  |  |  |  |  |  |

| WCAS:     | Write CAS# Pulse Width: bits 7:6 of the Memory Timing Register (AC-AFh).                                                         |  |  |  |  |  |  |

| RP:       | RAS# Precharge Time: bits 1:0 of the Memory Timing Register (AC-AFh).                                                            |  |  |  |  |  |  |

| CP:       | CAS# Precharge Time: bit 5 of the Memory Timing Register (AC-AFh).                                                               |  |  |  |  |  |  |

| RBD:      | Read Burst Delay: bits 2:0 of the Command Register (4C-4Fh).                                                                     |  |  |  |  |  |  |

| ACh:      | Actual hexadecimal value programmed into bits 15:0 of the Memory Timing Register (AC-AFh).                                       |  |  |  |  |  |  |

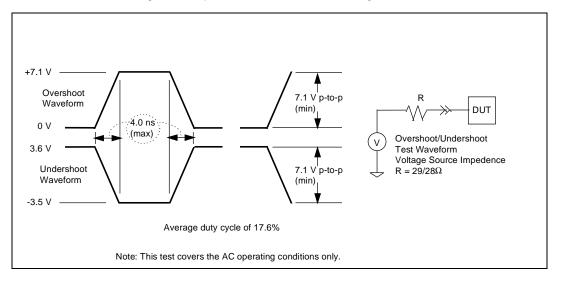

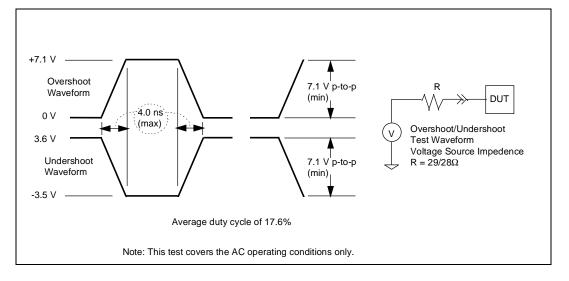

#### 3. CMOS Overshoot/Undershoot Specification

The following will be added to Chapter 4, Section 2.4., "Intel 450KX/GX Undershoot Specification," in the Intel 450KX/GX PCIset datasheet, and the section will be retitled "Intel 450KX/GX Overshoot/Undershoot Specifications."

The 3.3 V tolerant CMOS signals of the processor bus allow for the following maximum AC waveforms:

# ERRATA

#### 1. Stop Clock Acknowledge Cycles May Confuse Buffers

**PROBLEM:** If a Stop Clock Acknowledge special cycle is issued from a processor bus agent, the 82454 PB may pipeline an outbound (host-to-PCI bus) read behind it if the IOQ (In Order Queue) depth is set to 8. The read and write buffer pointers which track these transactions may become confused, and the data buffer which contains the data for the outbound read may be deallocated incorrectly. A similar situation arises if the special cycle is issued concurrent with an inbound read. Even if the IOQ depth is 1, this may occur, if inbound (PCI-to-host bus) write-posting is enabled in the 82454 PB.

**IMPLICATION:** A Stop Clock Acknowledge special cycle may cause premature deallocation of a buffer holding outbound read (or inbound write) data, resulting in a system hang with DBSY# asserted.

WORKAROUND: BIOS code can contain a workaround for this erratum.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 2. 0-Byte Length Write May Cause Subsequent Write Failure

**PROBLEM:** If a 0-byte write occurs, a subsequent write to memory may fail, corrupting memory, or a resulting implicit writeback or line read may not complete, causing a system hang. This can happen if:

- Back-to-back 8-byte writes occur after the 0-byte write.

- The 0-byte write receives an implicit writeback response with RAW enabled in the 82453KX MC.

- The 0-byte write is followed by a line read and preceded by a 0-byte read.

**IMPLICATION:** The Pentium<sup>®</sup> Pro processor will not perform 0-byte writes. The only configurations identified by Intel where the failing sequence is issued are with 824731FB (PIIX) or 824731SB (PIIX3) controllers used as IDE bus masters behind the 82454 PB, with inbound write-posting enabled and an IOQ depth of 8. In this case, the 82454KX PB may issue 0-byte writes as well as pipelined back-to-back 8-byte writes (which may be issued by the 82454KX PB normally).

**WORKAROUND:** Ensure that no system bus agent issues 0-byte writes. If the 824731FB (PIIX) or 824731SB (PIIX3) controllers are used, they must not be used as IDE bus masters.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 3. Inbound Read May Be Accepted Despite Posted Outbound Write

**PROBLEM:** The 82454 PB may accept an inbound read even if a posted write is queued. This is an ordering violation.

**IMPLICATION:** An outbound access which follows the outbound posted write may be snoop stalled indefinitely. If a new, nonposted, inbound request is issued, BPRI# will be asserted even though the outbound posted write has not been issued to the PCI bus, causing a deadlock, and the system will hang.

WORKAROUND: Do not enable outbound write posting in the 82454 PB.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 4. SMRAM Addresses May Not Be Decoded Correctly

**PROBLEM:** While executing in SMM (System Management Mode), certain sequences of transactions may allow the CAS# signal to be asserted without a corresponding RAS# signal during a memory access to SMRAM. In the A2 stepping of the Intel 450KX PCIset, there are many such sequences. For the B0 stepping of the Intel 450KX PCIset, the sequences must be pipelined SMRAM requests (with the IOQ depth set to 8) as follows:

- An SMRAM request which opens a page (i.e., the transaction address accesses a block of DRAM with a new row address).

- An SMRAM request which is a page hit.

- Another SMRAM request which is a page hit.

The address phase of the third request must occur during the first clock of CAS# assertion for the second request to encounter this erratum. A second sequence is:

- An SMRAM request which is a page hit.

- Another SMRAM request whose ADS# assertion comes 5 or 6 clocks later than the ADS# assertion for the

previous transaction, and which is also a page hit.

**IMPLICATION:** If these sequences occur while in SMM, data corruption may result.

**WORKAROUND:** For the A2 stepping of the Intel 450KX PCIset, SMM cannot be used. For the B0 stepping of the Intel 450KX PCIset, this erratum can be avoided by setting the IOQ depth to 1, thus preventing transactions from being pipelined together.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 5. Mixed Read Lines and Partials May Corrupt Data

**PROBLEM:** The 82453KX MC may not deallocate a data buffer correctly after the following sequence of transactions occurs:

- 1. A read line.

- 2. A read partial.

- 3. A read line which receives an implicit writeback response.

**IMPLICATION:** Stale data may be retrieved for a subsequent read line or read partial, resulting in corrupted data, or a protocol violation may be observed during a read line, causing a system shutdown.

**WORKAROUND:** If the following conditions are met, this erratum will not occur:

- In an MP system, all processors must have identical memory models, with all MTRRs for a particular region

of memory mapped the same way.

- Mixed mode paging must not be used.

- All memory behind the 82453KX MC must be mapped to the same memory type.

- The IOQ depth must be set to 1.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 6. Inbound Write Posting May Cause Write Failure

**PROBLEM:** During an inbound posted write burst, the 82454 PB may use the same data buffer for two adjacent transactions. This causes the first write to use and deallocate the data from the second write, corrupting data

and incorrectly deallocating a data buffer. When the data phase for the second write arrives, DBSY# may be asserted for some time, with no data phase or DRDY# assertion. When the PCI master completes the write burst, the deallocated buffer is never rewritten, resulting in a system hang with DBSY# asserted.

**IMPLICATION:** Enabling inbound write posting may cause data corruption followed by a system hang. Disabling inbound write posting may result in significant I/O performance loss.

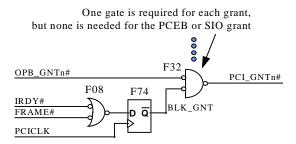

**WORKAROUND:** An external arbiter should be implemented which allows inbound posting to be enabled, and guarantees at least two idle cycles between inbound PCI requests.

This arbiter must not perform overlapped arbitration. One way to ensure this is to implement the circuit described below, external to the arbiter. The actual workaround involves waiting for a bus idle before allowing a new grant to be issued. The IOQ depth must still be set to 1, and 2:1 interleaving must be used, to work around other errata which may surface when inbound write posting is enabled (even with this workaround). Note that this latter restriction requires at least 4 SIMM DRAM modules to be loaded at all times.

This following circuit is an implementation of the described workaround:

This workaround will allow inbound write posting to be enabled on A2 450KX PCIset silicon, and will not affect the functionality of B0 450KX/GX PCIset silicon, though a slight performance loss may result if this workaround is used with the B0 stepping. Enabling inbound posting by using this workaround is a significant performance enhancement for systems with A2 450KX PCIset silicon; refer to Intel's World Wide Web site for more details on the performance loss incurred by disabling inbound write posting (at URL http://www.intel.com/procs/support/ppro/82450.htm).

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 7. RMW with Line Write May Cause Data Corruption

**PROBLEM:** If the 82453KX MC is performing a Read-Modify-Write (RMW) transaction due to a partial write to memory, and this is followed by a line write before the RMW completes, the byte enable signals for the RMW will be held too long, and only part of the line write will actually be written to memory.

**IMPLICATION:** A write may fail, corrupting data, if partial writes and line writes are pipelined together.

WORKAROUND: If the following conditions are met, this erratum will not occur:

- All processors in an MP system must have identical memory models, with all MTRRs for a particular region

of memory mapped the same way.

- Mixed mode paging must not be used.

- All memory behind the 82453KX MC must be mapped to the same memory type.

- The IOQ depth must be set to 1.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 8. Inbound Write May Collide with Some Special Cycles

**PROBLEM:** A special cycle from a processor bus agent which occurs during a write from the PCI bus to the processor bus may corrupt the byte enable signals for the write, causing incorrect data to be written into memory. Special cycles include Shutdown, Flush, Halt, Sync, Flush Acknowledge, Stop Clock Acknowledge, and SMI Acknowledge. This can only occur with outbound write posting enabled.

**IMPLICATION:** Special cycles coincident with inbound traffic from the PCI bus may corrupt data. However, only Flush, Sync, and Flush Acknowledge special cycles will normally be issued from Pentium Pro processors using the A2 stepping of the Intel 450KX PCIset.

- Flush special cycles are issued upon execution of an INVD instruction. Note that this instruction intentionally

removes modified lines from the cache without writing them back to memory; this results in the contents of

memory being unusable. Therefore, the possibility of data corruption due to a Flush special cycle can be

ignored.

- Flush Acknowledge special cycles are issued upon completion of flushing the caches after observation of a

FLUSH# signal assertion. This signal is only asserted by the 82454KX PB when the system is in Deturbo

mode. Therefore, these special cycles can be avoided by not enabling Deturbo mode in the affected

systems.

- Sync special cycles are issued upon execution of a WBINVD instruction. This instruction is a privileged

instruction which should only be executed by operating system level code. Intel has not identified any such

code which uses this instruction during inbound traffic.

Since each of these special cycles are only issued when the contents of the cache are being invalidated, inbound traffic which hits a cached memory location is not valid. If all inbound traffic during these special cycles targets cached memory, no effect will be seen due to this erratum. However, inbound traffic targeting uncached main memory would be corrupted if Deturbo mode, INVD instructions, or WBINVD instructions were used simultaneously. Note that INVD and WBINVD instructions are very rare system events; execution of an INVD instruction removes modified lines from the cache without writing them back to memory, so incorrect data in memory will not cause further system problems.

WORKAROUND: Do not enable outbound write posting in the 82454KX PB.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 9. Extended Read-Around-Write May Corrupt Write Data

**PROBLEM:** In a sequence of transactions to two different pages in memory (page X and page Y), the row address strobe (RAS#) and memory address (MA#) signals may be asserted on the same clock, resulting in a protocol violation which corrupts the data as it is written into memory. The sequence of transactions is as follows:

- 1. A line read to page X.

- 2. A line read to page X.

- 3. A line read to page X.

- 4. A line write to page Y.

- 5. A line read to page X.

- 6. A line write to page Y.

- 7. A line read to page X.

#### 8. A line read to page X.

This sequence will appear at the DRAM in the following order, with Read-Around-Write (RAW) and Extended Read-Around-Write (ERAW) enabled:

#### 1 - 2 - 3 - 5 - 4 - 7 - 8 - 6

In this sequence, transaction 5 is issued to memory before transaction 4 due to RAW/ERAW. Transaction 6 is then detected, and transaction 4 is issued since no reordering may occur around multiple writes. At this point, transaction 6 is at the front of the queue, and is a row-hit/page-hit relative to transaction 4, so the RAS# signal is left asserted in preparation for transaction 6. ERAW then causes transactions 7 and 8 to be reordered in front of transaction 6; these transactions are not row-hit/page-hit transactions, and the MA# lines are updated on the same clock as RAS# is reasserted, causing the protocol violation. The data returned for transactions 7 and 8 will then be corrupted.

**IMPLICATION:** ERAW will corrupt data returned for this sequence of memory transactions.

WORKAROUND: Do not enable ERAW in the 82453KX MC.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 10. Outbound Posted Write After Inbound Read Prefetch May Hang

**PROBLEM:** If an outbound write closely follows an inbound read prefetch, the data buffer containing the outbound write's data may be rewritten by the data for the prefetch. This occurs when the outbound write is issued after the PCI master has disconnected, but before the last prefetch has been issued on the processor bus; in this situation, the outbound write will incorrectly be allowed to post.

**IMPLICATION:** This condition will result in improper deallocation of the data buffer before the outbound write completes, hanging the system.

WORKAROUND: Outbound write posting must be disabled in the 82454KX PB.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 11. Inbound Posted Write with 1:1 Interleaving May Corrupt Data

**PROBLEM:** In systems configured with 1:1 interleaved memory (with only 2 SIMMs, for example) and inbound write posting enabled, if a string of line write transactions receive implicit writeback responses, data may be corrupted for subsequent writes if a refresh cycle occurs during the line writes. This occurs when the refresh backs up the transactions to memory such that the first partial write following the line write sequence is issued to the 82451 MIC with line-size encoding. The SYSCMD# and MEMCMD# signals will be correct, however.

**IMPLICATION:** Corrupted data will be written to memory in this case, with the data which was supposed to be written shifted by 8 bytes (data chunks 0-1-2-3 will be written as X-0-1-2, where X is most likely all 0's).

**WORKAROUND:** Do not enable inbound write posting in the 82454KX PB if memory is 1:1 interleaved, and use an IOQ depth of 1.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 12. RAW May Cause Data Corruption

**PROBLEM:** If Read-Around-Write (RAW) is enabled in the 82453KX MC, some sequences of memory transactions may cause the 82453KX MC to issue the memory address (MA#) and row address strobe (RAS#)

signals on the same clock edge for a DRAM read cycle, causing data corruption. The sequence which encounters this behavior is as follows:

- 1. A read to the 82454KX PB is snoop stalled.

- 2. During the snoop stall, a read-for-ownership (i.e., read and invalidate line) occurs.

- 3. Also during the snoop stall, a line write which is a row-hit/page-hit occurs.

- 4. A code line read which is a row-miss/page-miss occurs at the end of the snoop stall, but before snoop status is available for transactions 2 and 3.

**IMPLICATION:** When this occurs, the 82453KX MC will not start the write cycle until the snoop status is available for the preceding read. By then, the second read is in the internal queues behind the write, MA# will be driven with RAS# still asserted, and incorrect data will be returned for transaction 3.

WORKAROUND: Do not enable RAW in the 82453KX MC.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 13. Data Transfer Order 3 May Cause Data to Be Issued Out of Order

**PROBLEM:** If a line write is issued which uses a data transfer order of 3 (with A[4:3] = 11, so that the chunks are issued in order 3-2-1-0) and receives an implicit writeback response, a line write immediately following this transaction may be issued with a reversed data transfer order, corrupting memory.

**IMPLICATION:** A line write whose address has A[4:3] = 11 (binary) will have a "critical chunk" of 3. According to the protocol established by the Intel486<sup>™</sup> processor, this chunk must be written to memory first. A line write transaction which follows this one may have a different critical chunk (chunk 2, for example, issued in the order 2-3-0-1), but may be written to DRAM with a reversed order (1-0-3-2, in this case, or a data transfer order of 1). This causes the memory location to contain incorrect data. Note that neither the Pentium Pro processor nor the 450KX PCIset will issue line write transactions with this data transfer order (they will always have a data transfer order of 0). Third party agents which issue such transactions with a data transfer order of 3 will encounter this erratum.

**WORKAROUND:** Do not use third party agents which issue line writes with a data transfer order of 3 to the 82453KX MC.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 14. PCI Address Parity Error May Cause Dropped Transaction

**PROBLEM:** If PCI address parity checking is enabled in the 82454KX PB, an inbound (PCI to processor bus) transaction with bad address parity will cause the 82454KX PB to assert SERR#. The DEVSEL# signal may then remain deasserted incorrectly. If a second inbound transaction occurs after the error, it will not be forwarded to the processor bus.

**IMPLICATION:** Though a PCI address parity error may be detected and flagged, a second transaction after the one with the error may be dropped, possibly corrupting data.

**WORKAROUND:** The system can be configured to promote the SERR# resulting from the parity error to an NMI, allowing software to handle the failing I/O system normally.

**STATUS:** For the steppings affected see the Summary Table of Changes at the beginning of this section.

### 15. System Hang with Inbound Write Posting Enabled

**PROBLEM:** After a long write burst from the PCI to the processor bus, an outbound request will dynamically disable inbound write posting. The transaction immediately following the inbound burst may get a very fast retry. If this occurs, the 82454KX PB state machine may encounter a race condition which causes a bus hang on the next inbound request. The conditions for this to occur include:

- An inbound posted line write completes.

- The queue and data buffer for inbound transactions are full, or inbound write posting is dynamically disabled.

- The transaction after the inbound posted write is a nondual address transaction with A[4:2] = 5 or 6, with only

one idle cycle between it and the inbound posted line write.

This has only been observed in sequences containing a WRINV command on the PCI bus.

**IMPLICATION:** If inbound write posting is enabled in the 82454KX PB and the WRINV command is being used by a PCI device, the PCI bus may hang. The next outbound transaction will then hang the processor bus with BNR# toggling or with an infinite snoop stall.

**WORKAROUND:** Ensure nonoverlapped PCI arbitration via the workaround documented under Erratum 6, *Inbound Write Posting May Cause Write Failure*. If this workaround is not used, inbound write posting must be disabled in the 82454KX PB to avoid this erratum.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### 16. RAW May Cause Data Corruption During Refresh

**PROBLEM:** If Read-Around-Write (RAW) is enabled in the 82453KX MC and there are no transactions in its queues, a refresh which should occur next may cause improper transaction ordering. This boundary condition is as follows:

- 1. A line read transaction is issued.

- 2. From 2 to 6 clocks after the ADS# assertion for the read, a refresh is requested.

- 3. A line write transaction is issued.

- 4. A line read transaction is issued which is a row-miss.

In this case, the refresh will be recognized before the write appears at the head of the queue, and will block the write from being handled. This allows the second line read to be reordered by RAW to occur before the write.

**IMPLICATION:** This boundary condition may cause data to be corrupted, if the data for the line read is dependent on the line write. Intel has observed this erratum in 1:1 interleaved configurations, and to a lesser extent in 2:1 interleaved configurations.

WORKAROUND: Do not enable RAW in the 82453KX MC.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### 17. GAT Devices May Time Out During Inbound Read Prefetch

**PROBLEM:** While in GAT (Guaranteed Access Time) mode, the 82454KX PB does not dynamically disable inbound read prefetching. Thus, a transaction which is issued immediately after MEMACK# is asserted may cause a prefetch to occur, tying up the bus and possibly allowing ISA or EISA devices configured for GAT to time out.

#### INTEL 450KX/GX PCISET SPECIFICATION UPDATE

intel

**IMPLICATION:** The 2.4  $\mu$ s guaranteed access time may not be met for devices behind the 82454KX PB and an ISA or EISA bridge, resulting in spurious time-outs for such devices if inbound read prefetching is enabled, though most such devices will accept a longer access time.

**WORKAROUND:** If time-out problems occur while in GAT mode, disable inbound read prefetching in the 82454KX PB.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 18. Data May Be Corrupted If RCD = 4 and LWC = 3

**PROBLEM:** The memory timings RCD (RAS# to CAS# Delay) and LWC (Last Write to CAS#) interact in such a way that if RCD is set to 4 and LWC is set to 3, the following transaction sequence will cause a data read to be corrupted:

- 1. A line read which triggers an implicit writeback and results in a page miss.

- 2. A line read which triggers an implicit writeback.

- 3. A line read to the same line as transaction 2.

IMPLICATION: These timing values may cause read data to be corrupted if the writeback memory type is used.

WORKAROUND: Do not use an RCD value of 4.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 19. TCO\_MAX Specification Not Met for GTL+ Signals

**PROBLEM:** The  $T_{CO\_MAX}$  specification for the GTL+ signals of the Intel 450KX PCIset is 6.0 ns. The actual value is 7.5 ns.

**IMPLICATION:** This value should be used when designing systems using the affected chipsets.

WORKAROUND: None identified.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 20. RAW May Hang 1:1 or 2:1 Interleaved MP Systems

**PROBLEM:** If Read-Around-Write (RAW) is enabled in the 82453KX MC, there is a potential for two reads being assigned to the same internal data buffer, causing the system to hang. The following transactions must be issued during a snoop stall for a previous read for this erratum to occur:

- 1. A line read transaction.

- 2. A 0-byte length read transaction.

- 3. An explicit writeback transaction.

- 4. A line read transaction.

Transactions 1 and 4 may target the same buffer (causing the system to hang) in this situation. In A2 450KX PCIset silicon, it is also possible for a read transaction to incorrectly pass a write transaction with the same line address, but different chunk address. Both of these conditions require multiple symmetric bus agents (such as processors).

**IMPLICATION:** Uniprocessor systems will not be affected by this erratum. Other Intel 450KX PCIset-based systems will hang if this sequence occurs during a snoop stall.

WORKAROUND: Do not enable RAW in the 82453KX MC.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 21. Mixed Interleave Increments May Cause Data Corruption

**PROBLEM:** If some DRAM module sizes are mixed together, some Intel 450KX PCIset-based systems may corrupt user or system data, resulting in incorrect calculations and/or system failure. This can only occur if:

- Interleave increments containing 8-Mbytes or 32-Mbytes of memory exist in conjunction with interleave increments which contain other amounts of memory, or

- One or more interleave increments have 8- or 32-Mbytes of memory, and there are no DRAM modules in the first row (row 0) of the memory subsystem.

Note that in systems with only one row of memory in use (i.e., 2 SIMMs in 1:1 interleave or 4 SIMMs in 2:1 interleave), or with all SIMMs or DIMMs the same size and configuration, only one interleave increment size is possible (since all memory in the same row must be the same size), so this erratum will not affect the system.

Also note that the BIOS of some (usually server) platforms may automatically downsize or eliminate a row of memory if a bad DRAM module is detected in that row. It is possible for this alteration of memory sizes to result in the system entering a vulnerable configuration (if memory is downsized to interleave increments of 8 or 32 Mbytes, or if row 0 is removed from the configuration). This can occur even with logically double-sided DRAM modules, which otherwise always have the same size interleave increments across their two rows.

**IMPLICATION:** Some systems only support one row of memory (i.e., 1:1 interleaving with 2 SIMMs or 2:1 interleaving with 4 SIMMs). In these systems, only one interleave increment size is possible (since all memory in the same row must be the same size), so they are not affected by this erratum. In systems which support two or more rows of memory (other than systems which support two rows of double-sided SIMM DRAM only), one must be careful not to mix DRAM of certain sizes. If there are 8 or 32 Mbytes of DRAM in any interleave increment, all other interleave increments must have the same amount of DRAM, and row 0 must be populated with DRAM modules to avoid data corruption due to this erratum.

| SIMMs                       | DRAM        | Technology | Interleave Increment |  |  |

|-----------------------------|-------------|------------|----------------------|--|--|

| Two 4-Mbyte, single-sided   | 1-Mbit x 4  | 4-Mbit     | 8 Mbytes*            |  |  |

| Two 8-Mbyte, double-sided   | 1-Mbit x 4  | 4-Mbit     | 8 Mbytes*            |  |  |

| Two 8-Mbyte, single-sided   | 2-Mbit x 8  | 16-Mbit    | 16 Mbytes            |  |  |

| Two 16-Mbyte, double-sided  | 2-Mbit x 8  | 16-Mbit    | 16 Mbytes            |  |  |

| Two 16-Mbyte, single-sided  | 4-Mbit x 4  | 16-Mbit    | 32 Mbytes*           |  |  |

| Two 32-Mbyte, double-sided  | 4-Mbit x 4  | 16-Mbit    | 32 Mbytes*           |  |  |

| Two 32-Mbyte, single-sided  | 8-Mbit x 8  | 64-Mbit    | 64 Mbytes            |  |  |

| Two 64-Mbyte, double-sided  | 8-Mbit x 8  | 64-Mbit    | 64 Mbytes            |  |  |

| Two 64-Mbyte, single-sided  | 16-Mbit x 4 | 64-Mbit    | 128 Mbytes           |  |  |

| Two 128-Mbyte, double-sided | 16-Mbit x 4 | 64-Mbit    | 128 Mbytes           |  |  |

The chart below gives the interleave increments for some common memory technologies:

#### INTEL 450KX/GX PCISET SPECIFICATION UPDATE

# intel

| DIMMs                       | DRAM        | Technology | Interleave Increment |  |  |

|-----------------------------|-------------|------------|----------------------|--|--|

| One 8-Mbyte, single-sided   | 1-Mbit x 4  | 4-Mbit     | 8 Mbytes*            |  |  |

| One 16-Mbyte, double-sided  | 1-Mbit x 16 | 16-Mbit    | 8 Mbytes*            |  |  |

| One 16-Mbyte, single-sided  | 2-Mbit x 8  | 16-Mbit    | 16 Mbytes            |  |  |

| One 32-Mbyte, double-sided  | 2-Mbit x 8  | 16-Mbit    | 16 Mbytes            |  |  |

| One 32-Mbyte, single-sided  | 4-Mbit x 4  | 16-Mbit    | 32 Mbytes*           |  |  |

| One 64-Mbyte, double-sided  | 4-Mbit x16  | 64-Mbit    | 32 Mbytes*           |  |  |

| One 64-Mbyte, single-sided  | 8-Mbit x 8  | 64-Mbit    | 64 Mbytes            |  |  |

| One 128-Mbyte, double-sided | 8-Mbit x 8  | 64-Mbit    | 64 Mbytes            |  |  |

| One 128-Mbyte, single-sided | 16-Mbit x 4 | 64-Mbit    | 128 Mbytes           |  |  |

#### NOTE:

\*To avoid corruption of data, do not mix 8-Mbyte or 32-Mbyte interleave increments with other increment sizes (including each other). If 8-Mbyte or 32-Mbyte interleave increments are used (exclusively), ensure that row 0 is populated with DRAM modules.

WORKAROUND: When upgrading memory:

- In systems which support multiple rows of memory, always populate row 0 with DRAM modules.

- Exercise caution when using 4-Mbyte or 16-Mbyte SIMMs (single- or double- sided), or when using 8-Mbyte

or 32-Mbyte DIMMs. Note that exclusively using DRAM modules which are all the same size will always

avoid this erratum.

- When writing a BIOS for an Intel 450KX-based system, the memory configurations susceptible to this

erratum should be detected and flagged to alert the user of the problem. Ensure that such detection

mechanisms are placed after any bad DRAM detection mechanisms so that vulnerable configurations are

detected after memory downsizing has occurred.

- Refer to your system documentation, or contact your system vendor, for details on your system's support for the various interleaving modes and DRAM styles.

See the white paper *Mixing DRAM Sizes with the 82450KX/GX PCIset* on Intel's World Wide Web site at URL http://www.intel.com/procs/support/ppro/450kxgx.htm for more information.

**STATUS:** For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 22. Parity Error May Occur for ADS# During BINIT#

**PROBLEM:** If BINIT# is asserted due to some catastrophic system event, the system will reset the bus and attempt to recover. If, however, ADS# is asserted for a request during the BINIT#, some of the signals associated with the request may not be driven when they should be. This results in an incorrect request parity and an assertion of AERR# 2 clocks after the BINIT# is complete, which is not a valid error phase.

**IMPLICATION:** A second (spurious) AERR# will be observed, resulting in a spurious SERR#. No data loss or hang is associated with this erratum, just an extra assertion of AERR# after detection of a catastrophic bus condition.

WORKAROUND: None identified.

**STATUS:** For the steppings affected see the Summary Table of Changes at the beginning of this section.

### 23. Hang with PCI-to-PCI Bridges in MP Systems

**PROBLEM:** If a PCI-to-PCI bridge is present in a system, either on a card or native on the motherboard, a "livelock" hang condition may be possible if pipelined transactions are allowed (i.e., the IOQ depth is set to 8). This may happen if the following events occur:

- An ordering event (such as I/O reads, and I/O writes for some components) from one processor is followed by a second such event from another processor. These outbound events are directed through the 82454KX PB, and dynamically disable inbound write posting.

- 2. The PCI-to-PCI bridge is attempting to perform an inbound write through the 82454KX PB.

If this situation arises, the PCI-to-PCI bridge will retry the outbound transactions, but must follow ordering constraints on the I/O operations. The outbound transactions are then reissued on the processor bus faster than the 82454KX PB can prepare to service the inbound write request from the PCI-to-PCI bridge. Consequently, the inbound write cannot complete, and the I/O transactions are continuously retried and reissued on the processor bus, resulting in a "livelock" hang with neither side making forward progress.

**IMPLICATION:** PCI-to-PCI bridges present in an MP system may cause the system to hang.

**WORKAROUND:** Set the IOQ depth to 1. If this is not acceptable (multiprocessor systems may see significant performance degradation with this setting), a hardware workaround may be implemented using a programmable logic component. This workaround allows the outbound transactions to complete after they are retried by the PCI-to-PCI bridge, by putting the 82454KX PB in non-GAT (as opposed to GAT, or Guaranteed Access Time, mode) for 64 processor clocks after an outbound request is retried once, or after an inbound request is retried 8 times.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 24. PCI\_RST# Not Asserted Asynchronously

**PROBLEM:** The 82454KX PB requires a valid BCLK to assert the PCI\_RST# signal, due to clocked logic in the assertion paths of these signals.

**IMPLICATION:** This signal is not asynchronous, as was intended.

WORKAROUND: Ensure a valid BCLK is provided before attempting to reset the PCI bus.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### 25. BERR# to BINIT# Conversion May Prevent Recovery From BINIT#

**PROBLEM:** If an error on a bus split operation occurs which causes an assertion of both BERR# and BINIT#, and BERR# to BINIT# conversion is enabled in the 82454KX PB, BINIT# will be driven a second time, 2 bus clocks after the first completes. At this time, another 450KX agent may still be driving BNR# for the first BINIT#, and other devices may then try to drive BNR# for the second BINIT#. This results in the system being unable to recover successfully from the BINIT#, hanging the system.

**IMPLICATION:** After a double assertion of BINIT# due to detection of a catastrophic error, the bus may not be reset properly, resulting in a system hang.

**WORKAROUND:** Do not enable BERR#-to-BINIT# conversion in the 82454KX PB. BERR#-to-SERR# conversion can be used instead.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 26. Error Reporting Registers May Not Record Error Information Correctly

PROBLEM: The error reporting functionality of the 82453KX MC is limited in the following ways:

- If a transaction occurs which contains an SBC (single-bit correctable) error, the error is detected, corrected, and logged (if ECC error detection, correction, and logging are enabled in the 82453KX MC). If a subsequent transaction contains an SBC error on one chunk (an 8-byte block of data) and an UNC (uncorrectable, double-bit) error on another, both will be detected, and the SBCERR# and BERR# signals will be asserted normally, but only the SBC error will actually be logged in the error reporting registers of the 82453KX MC.

- 2. If a transaction occurs with an UNC error, the error is tracked via an internal error buffer, and BERR# is asserted (if this feature is enabled). If the system does not shut down due to this error, and an SBC error occurs such that the UNC error is being popped from the error buffer at the same time that the SBC error is pushed into the buffer, the UNC error will not be logged into the error reporting registers of the 82453KX MC.

**IMPLICATION:** Under some circumstances, some errors will not be reported properly when detected in combination with other errors. This will result in an error not being logged into the error reporting registers of the 82453KX MC. However, this erratum does not affect the detection and correction of SBC errors or the detection of UNC errors.

#### WORKAROUND: None identified.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 27. Combination of ECC Errors May Cause One Error to Be Undetected

**PROBLEM:** The 82452KX DP may not detect a memory ECC error during pipelined line reads, when there are multiple SBC and/or UNC errors across cache line boundaries. The error combinations which are affected are as follows:

- 1. An SBC error will detected and corrected, but not reported to the 82453KX MC, if it occurs on chunk 3 of the first line read when there is an UNC error on chunk 2 of the first line read and an SBC on chunk 0 of the second line read. In this case, no error record will exist for the first SBC, but data will not be corrupted.

- An UNC error will be detected by the 82452KX DP but not reported to the 82453KX MC, if it occurs on chunk 3 of the first line read when there is an SBC error on chunk 2 of the first line read and either type of error on chunk 0 of the second line read. In this case, no error record will exist for the first UNC, and BERR# will not be driven if the third error is an SBC.

Note that these are the only combinations of errors affected by this erratum; other combinations of errors (including cache lines with **more** errors than specified) will all be detected, and any subsequent UNC errors which occur will cause BERR# to be driven by the 82453KX MC (assuming this feature is enabled).

**IMPLICATION:** An error will not be detected if it occurs with these very specific combinations, possibly resulting in corrupted data. The other errors in these combinations, as well as all other errors which occur on other transactions which do not fall within this pattern, will be detected correctly.

WORKAROUND: None identified.

**STATUS:** For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 28. 16-Byte Write May Hang System

**PROBLEM:** If a 16-byte partial write is issued in the middle of a sequence of line writes, the line write immediately after the 16-byte write may fail. A subsequent read transaction will hang the processor bus. Note that neither the

# int<sub>el</sub>,

Pentium Pro processor nor any Intel 450KX PCIset agent will generate 16-byte writes. Only systems containing third-party bus agents may be affected by this erratum.

**IMPLICATION:** If third-party agents which issue 16-byte writes are present in a system, the system may hang after a sequence of write transactions.

WORKAROUND: Do not use third-party agents which issue 16-byte writes.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

### 29. 16-Byte Read with Two ECC Errors May Not Be Reported Correctly

**PROBLEM:** If a line read contains either type of error in chunk 3, and the line read is followed by a 16-byte read which has either an SBC error in chunk 0 and an UNC error in chunk 1 or an UNC error in chunk 1 and an SBC in chunk 0, a stale error record will be left in the error reporting registers which does not correspond to the last errors detected. All errors in this combination will be detected, however, and BERR# will be driven for UNC errors (assuming this feature is enabled). Note that neither the Pentium Pro processor nor any Intel 450KX PCIset agent will generate 16-byte reads; only systems containing third-party bus agents may be affected by this case.

**IMPLICATION:** Under some circumstances, some errors will not be reported properly when detected in combination with other errors. This may result in an error not being logged into the error reporting registers of the 82453KX MC at all, or it may result in incorrect error information being logged. This erratum does not affect the detection and correction of SBC errors or the detection of UNC errors.

**WORKAROUND:** Do not use third-party agents which issue 16-byte reads.

STATUS: For the steppings affected see the Summary Table of Changes at the beginning of this section.

#### 30. Inbound Locked PCI Transactions May Hang System

**PROBLEM:** This erratum manifests itself in the following sequence:

- 1. A locked read request is issued on the PCI bus, and targets the processor bus. The 82454KX PB asserts DEVSEL#.

- 2. The transaction is entered into the 82454KX PB's request queue, which then asserts BPRI#.