### 82420 PCIset

Intel's 82420 PCIset enables workstation level of performance for Intel486TM CPU desktop systems. The Peripheral Component Interconnect Bus (PCI) is driving a new architecture for PC's—eliminating the I/O bottleneck of standard expansion busses. PCI provides a glueless interface for high performance peripherals such as graphics, SCSI, LAN and video to be placed onto a fast local bus. By utilizing this technology and incorporating read/write bursts along with write buffers into the 82420 PCIset, a new level of performance is now possible for today's Intel486 CPU desktop systems.

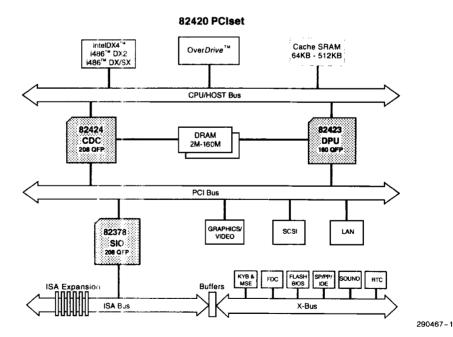

The Intel 82420 PCIset is comprised of three components: the 82424ZX Cache DRAM Controller (CDC), the 82423TX Data Path Unit (DPU), and the 82378ZB System I/O (SIO). The CDC and DPU provide the core system architecture while the SIO is a PCI master/slave agent which bridges the core architecture to the ISA standard expansion bus. Intel also offers two components, the 82374EB (ESC) and 82375EB (PCEB), that work in conjunction to bridge the PCI bus to the EISA expansion bus. Refer to the ESC and PCEB data sheets for information regarding the EISA bridge components.

The chip set supports the Intel486 CPU family as well as Intel's future OverDrive<sup>TM</sup> processor for the Intel486 DX2 CPU. The high performance memory subsystem supports concurrent operation between PCI bus masters while the CPU accesses memory. An integrated second level cache can be programmed for write-through or write-back operation.

## **Product Highlights**

## 82424ZX—Cache DRAM Controller (CDC)

- Concurrent Linefill during Copyback Cycles

- Supports Intel486 CPU Family and OverDrive Processors

- Supports OverDrive Upgrade

- 64K-512K Level 2 Cache Support

- Level 2 Cache Configurable as Write-Back or Write-Through

- 208-Pin QFP Package

#### 82423TX—Data Path Unit (DPU)

- m Highly Integrated

- **Four Dword Write Buffers**

- **Zero Wait-States for CPU Write Cycles**

- PCI Burst Write Capability

- 160-Pin QFP Package

# 82378ZB—System I/O Component (SIO)

- Supports Fast DMA Type A, B, or F Cycles

- Supports DMA Scatter/Gather

- Arbitration Logic for Four PCI Masters

- Reusable across Multiple Platforms

- Directly Drives Six External ISA Slots

- Integrates Many of Today's Common I/O Functions

- 208-Pin QFP Package

### **Product Description**

The 82424ZX Cache DRAM Controller (CDC) is a single-chip bridge from the CPU to the PCI bus. It provides the integrated functionality of a second level cache controller, a DRAM controller, and a PCI bus controller. It also features an optimized memory subsystem. The CDC is a dual ported device with one port as the host port and the other as the PCI port.

The 82423TX Data Path Unit (DPU) integrates the host data, memory data, and PCI data interface, DPU control/parity and four deep posted write buffers. With glue and buffers integrated directly into the DPU, the Intel 82420 PCIset reduces board space requirements. The DPU's posted write buffers allow CPU write cycles to be executed as 0 wait-states.

The 82378ZB System I/O (SIO) is a dual ported device which acts as a bridge between the PCI and standard ISA I/O bus. The SIO integrates the functionality of an ISA controller, PCI controller, fast 32-bit DMA controller, and standard system I/O functions.