### 82396SX SMART CACHE

- Optimized Intel386™ SX Microprocessor Companion

- 4 Way SET Associative with Pseudo LRU Algorithm

- **■** Write Buffer Architecture

- Integrated 4 Word Write Buffer

- Integrated Intel387™ SX Math Coprocessor Decode Logic

- 132 Lead PQFP Package

- Intel486™ SX Microprocessor like Burst

- Integrated 16 KB Data RAM

- 16-Byte Line Size

- Dual Bus Architecture

Snooping Maintains Cache

Coherency

- 20 MHz Clock

- Concurrent Line Buffer Cacheing

- # 1K of TAG RAM

- Non-Sectored Architecture

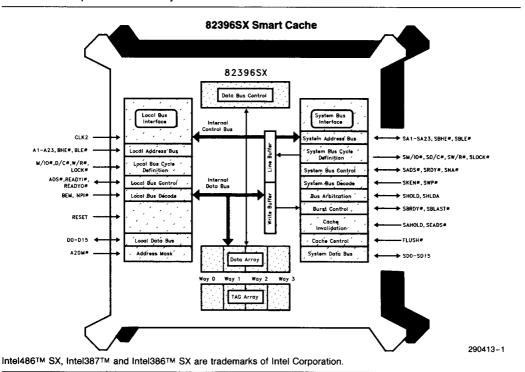

The 82396SX Smart Cache (part number 82396SX) is a low cost, single chip, 16-bit peripheral for Intel's i386TM SX Microprocessor. By storing frequently accessed code or data from main memory the 82396SX Smart Cache enables the i386TM SX Microprocessor to run at near zero wait states. The dual bus architecture allows another bus master to access the System Bus while the i386TM SX Microprocessor operates out of the 82396SX Smart Cache on the Local Bus. The 82396SX Smart Cache has a snooping mechanism which maintains cache coherency with main memory during these cycles.

The 82396SX Smart Cache is completely software transparent, protecting the integrity of system software. The advanced architectural features of the 82596SX Smart Cache offer high performance with a cache data RAM size that can be integrated on a single chip, offering the board space and cost savings needed in an i386TM SX Microprocessor based system.

### 82396SX Smart Cache

| <b>CONTENTS</b>                                             | AGE    | CONTENTS                                                       | PAGE    |

|-------------------------------------------------------------|--------|----------------------------------------------------------------|---------|

| 0.0 DESIGNER SUMMARY 0.1 Pin Out                            |        | 3.1.3.1 Local Bus Cycle Definition Signals (W/R#, M/IO#, D/C#) | . 5-645 |

| 0.2 Quick Pin Reference                                     | 5-628  | 3.1.3.2 Local Bus Lock<br>(LOCK#)                              |         |

| 1.0 82396SX SMART CACHE FUNCTIONAL OVERVIEW                 | 5-632  | 3.1.4 Local Bus Control                                        |         |

| 1.1 Introduction                                            |        | 3.1.4.1 Address Status                                         |         |

| 1.2 Features                                                |        | (ADS#)                                                         | . 5-645 |

| 1.2.1 82385SX-Like Features                                 |        | 3.1.4.2 Local Bus Ready<br>(READYI#)                           | 5-645   |

| 1.2.2 New Features                                          |        | 3.1.4.3 Local Bus Ready Outpu<br>(READYO#)                     | it      |

| 2.0 82396SX SMART CACHE SYSTEM                              | F 00.4 | 3.1.5 Reset (RESET)                                            |         |

| <b>DESCRIPTION</b> 2.1 82396SX Smart Cache                  | 5-634  | 3.1.6 Local Data Bus                                           |         |

| Organization                                                | 5-634  | 3.1.6.1 Local Bus Data Lines                                   |         |

| 2.1.1 82396SX Smart Cache                                   |        | (D[15:0])                                                      |         |

| Structure and Terminology                                   |        | 3.1.7 Local Bus Decode Pins                                    |         |

| 2.2 Pseudo LRU Algorithm                                    | 5-638  | 3.1.7.1 No Post Input (NPI#) .                                 | . 5-646 |

| 2.3 4-Way Set Associative Cache Organization                | 5-639  | 3.1.7.2 Byte Enable Mask<br>(BEM)                              | . 5-646 |

| 2.3.1 Cache Read Hits                                       |        | 3.1.8 Address Mask                                             |         |

| 2.3.2 Cache Read Misses                                     |        | 3.1.8.1 Address Bit 20 Mask                                    |         |

| 2.3.3 Other Operations That Affect                          |        | (A20M#)                                                        |         |

| the Cache and Cache Directory                               | E 620  | 3.2 System Bus Interface Pins                                  |         |

| 2.4 Concurrent Line Buffer                                  | J-039  | 3.2.1 System Address Bus                                       | . 5-647 |

| Cacheing                                                    | 5-639  | 3.2.1.1 System Bus Address Lines (SA[23:1])                    | 5-647   |

| 2.5 Cache Control                                           | 5-641  | 3.2.1.2 System Bus Byte                                        |         |

| 2.6 Cache Invalidation                                      | 5-641  | Enables (SBHE#, SBLE#) .                                       | . 5-647 |

| 2.7 Cache Flushing                                          | 5-642  | 3.2.2 System Bus Cycle                                         |         |

| 2.8 Cache Directory Accesses and                            | - 040  | Definition                                                     | . 5-64/ |

| Arbitration                                                 |        | 3.2.2.1 System Bus Cycle<br>Definition Signals (SW/R#,         |         |

| 2.9 Cache Memory Description                                | 5-644  | SM/IO#, SD/C#)                                                 | . 5-647 |

| 3.0 PIN DESCRIPTION                                         |        | 3.2.2.2 System Bus Lock<br>(SLOCK#)                            | E 647   |

| 3.1 Local Bus Interface Pins                                | 5-644  | 3.2.3 System Bus Control                                       |         |

| 3.1.1 i386™ SX Microprocessor/<br>82396SX Smart Cache Clock |        | 3.2.3.1 System Bus Address                                     | . 5-047 |

| (CLK2)                                                      | 5-644  | Status (SADS#)                                                 | . 5-647 |

| 3.1.2 Local Address Bus                                     |        | 3.2.3.2 System Bus Ready                                       |         |

| 3.1.2.1 Local Bus Address Lines                             |        | (SRDY#)                                                        | . 5-647 |

| (A[23:1])                                                   | 5-644  | 3.2.3.3 System Bus Next<br>Address (SNA#)                      | 5-648   |

| 3.1.2.2 Local Bus Byte Enables<br>(BHE#, BLE#)              | 5-645  | 3.2.4 Bus Arbitration                                          |         |

| 3.1.3 Local Bus Cycle Definition                            |        |                                                                |         |

| CONTENTS                                                      | PAGE  | CONTENTS                                           | PAGE            |

|---------------------------------------------------------------|-------|----------------------------------------------------|-----------------|

| 3.2.4.1 System Bus Hold Request (SHOLD)                       | 5-648 | 5.0 PROCESSOR INTERFACE                            |                 |

| 3.2.4.2 System Bus Hold                                       |       | 5.1 Hardware Interface                             |                 |

| Acknowledge (SHLDA)                                           |       | 5.2 Nonpipelined Local Bus                         | 5-658           |

| 3.2.5 Burst Control                                           |       | 5.3 Local Bus Response To Hit Cycles               | 5-658           |

| (SBRDY#)                                                      | 5-648 | 5.4 Local Bus Response to Miss                     | ;               |

| 3.2.5.2 System Bus Burst Las<br>Cycle Indication<br>(SBLAST#) |       | Cycles                                             | ADS#.           |

| 3.2.6 Cache Invalidation                                      |       | 5.6 82396SX Smart Cache's Re                       | sponse          |

| 3.2.6.1 System Bus Address<br>Hold (SAHOLD)                   |       | to the i386 <sup>TM</sup> SX Microproces<br>Cycles | sor             |

| 3.2.6.2 System Bus External                                   | 5-046 | 5.6.1 Locked Cycles                                |                 |

| Address Strobe (SEADS#)                                       | 5-649 | 5.6.2 I/O, HALT/SHUTDOW                            |                 |

| 3.2.7 Cache Control                                           | 5-649 | 5.6.3 NPI# Cycles                                  |                 |

| 3.2.7.1 Flush (FLUSH#)                                        |       | 5.6.4 NPI#/BEM Timing                              |                 |

| 3.2.8 System Data Bus                                         | 5-649 | 5.7 82396SX Smart Cache REA<br>Generation          | DYO#            |

| 3.2.8.1 System Bus Data Line<br>(SD[15:0])                    |       | 5.8 A20 Mask Signal                                |                 |

| 3.2.9 System Bus Decode Pins .                                | 5-649 | 5.9 82396SX Smart Cache Cycle                      | Э               |

| 3.2.9.1 System Cacheability Indication (SKEN#)                | 5-649 | Overview                                           | 5-661           |

| 3.2.9.2 System Write Protect                                  | 0 040 | 6.0 SYSTEM BUS INTERFACE                           |                 |

| Indication (SWP#)                                             | 5-649 | 6.1 System Bus Cycle Types                         |                 |

| 3.3 Pinout Summary Tables                                     | 5-650 | 6.1.1 Buffered Write Cycle                         |                 |

| .0 BASIC FUNCTIONAL                                           |       | 6.1.2 Non Buffered Write Cyc                       |                 |

| DESCRIPTION                                                   | 5-651 | 6.1.3 Write Protected Cycles                       | 5-667           |

| 4.1 Cacheable Accesses                                        |       | 6.1.4 Non Cacheable Read Cycle                     | 5-667           |

| 4.1.1 Cacheable Read Hit Accesses                             | 5-652 | 6.1.5 Cacheable Read Miss<br>Cycles                |                 |

| 4.1.2 Cacheable Read Miss<br>Accesses                         | 5-652 | 6.1.5.1 Aborted Line Fill                          |                 |

| 4.1.2.1 Burst Bus                                             |       | Cycles                                             |                 |

| 4.1.3 Cache Write Accesses                                    |       | 6.1.5.2 Line Fill Cycles                           |                 |

| 4.2 Noncacheable System Bus                                   |       | 6.2 82396SX Smart Cache Later<br>SB Accesses       | ncy in<br>5-676 |

| Accesses                                                      | 5-653 | 6.3 SHLDA Latency                                  | 5-676           |

| 4.3 Local and System Bus Concurrency                          | 5-656 | 6.4 Cache Consistency Support                      |                 |

| 4.4 Disabling the 82396SX Smart                               | 5-657 | 6.5 Write Buffer                                   | 5-678           |

| CONTENTS                           | PAGE           | CONTENTS                               | PAGE        |

|------------------------------------|----------------|----------------------------------------|-------------|

| 7.0 TESTABILITY FEATURES           | 5-678          | 9.0 ELECTRICAL DATA                    | 5-686       |

| 7.1 SRAM Test Mode                 | 5-678          | 9.1 Power and Grounding                | 5-686       |

| 7.2 Tristate Output Test Mode      | 5-681          | 9.1.1 Power Decoupling Recommendations | 5-686       |

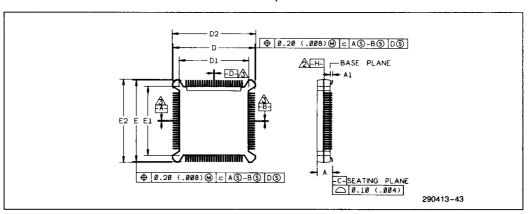

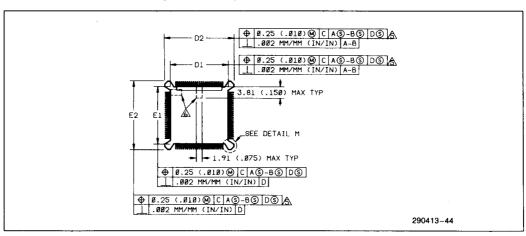

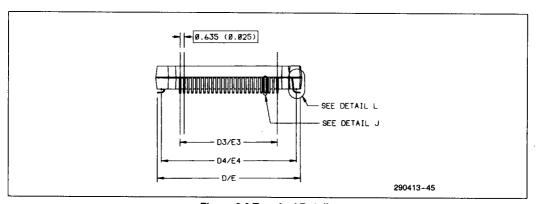

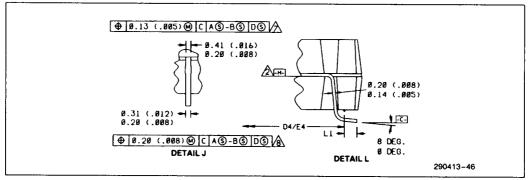

| 8.0 MECHANICAL DATA                | 5-683          | 9.1.2 Resistor                         | ,           |

| 8.1 Introduction                   | 5-683          | Recommendations                        | 5-686       |

| 8.2 Pin Assignment                 | 5-683          | 9.2 Absolute Maximum Rating            | s 5-686     |

| 8.3 Package Dimensions and         |                | 9.3 D.C. Specifications                | 5-687       |

| Mounting                           | 5- <b>68</b> 3 | 9.4 A.C. Characteristics               | 5-688       |

| 8.4 Package Thermal Specifications | 5-683          | 9.4.1 A.C. Characteristic Ta           | ıbles 5-689 |

|                                    |                | APPENDIX A—Terms                       | 5-696       |

|                                    |                | APPENDIX B                             | 5-697       |

**82396SX REVISION SUMMARY** ..... 5-700

| CONTE      | NTS                                          | PAGE    | CONTEN      | <b>ITS</b> PAGE                                                                                |

|------------|----------------------------------------------|---------|-------------|------------------------------------------------------------------------------------------------|

| FIGURES    |                                              |         | Figure 6.3  | Multiple Buffered Write                                                                        |

| Cover      | 82396SX Smart Cache                          | . 5-620 |             | Cycles during System Bus HOLD5-665                                                             |

| Figure 0.1 | 82396SX Smart Cache 132                      |         | Figure 6.4  | I/O Write Cycle 5-666                                                                          |

|            | Lead PQFP Package Pin Orientation            |         | Figure 6.5  | LOCK#ed Read Modify Write Cycle5-666                                                           |

| Figure 1.1 | System Block Diagram                         | . 5-632 | Figure 6.6  | I/O Read Cycle 5-667                                                                           |

| Figure 2.1 | 82396SX Smart Cache Organization             | 5-635   | Figure 6.7  | LOCK#ed INTA Cycle 5-667                                                                       |

| Figure 2.2 | 82396SX Smart Cache                          |         | Figure 6.8  | Aborted Line Fill Cycle 5-668                                                                  |

| <u>.</u>   | Directory Organization                       | . 5-636 | Figure 6.9  | Line Fill Without Burst or Pipeline5-670                                                       |

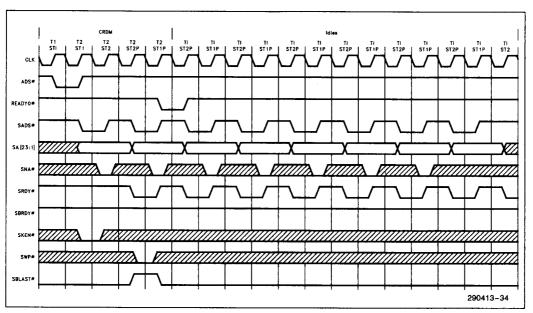

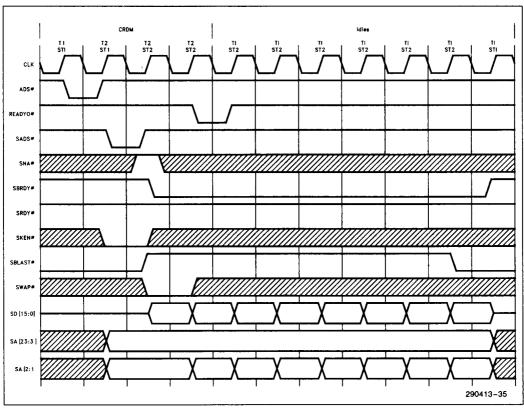

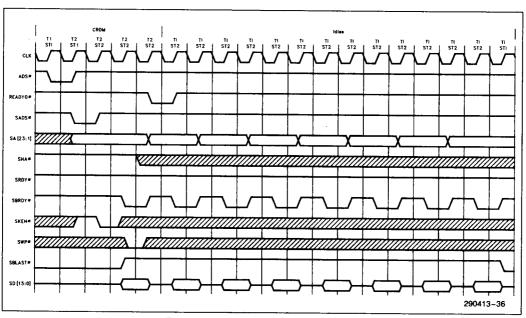

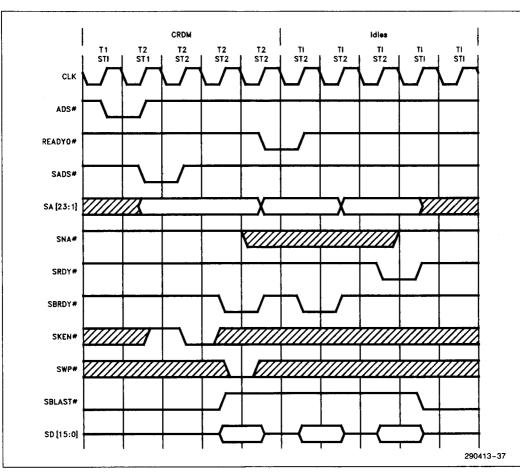

| Figure 2.3 | 82396SX Smart Cache Hit Logic                | . 5-637 | Figure 6.9A | Burst Mode Line Fill                                                                           |

| Figure 2.4 | Pseudo LRU Decision Tree                     | . 5-638 |             | Followed by Line Buffer Hit Cycles 5-671                                                       |

| Figure 2.5 | Four Way SET Associative                     |         | -           | Pipelined Line Fill 5-672                                                                      |

| Ū          | Cache Organization                           | . 5-640 |             | Fastest Burst Cycle 5-673                                                                      |

| Figure 2.6 | Interposing in the Cache                     | E 044   | Figure 6.12 |                                                                                                |

| Eiguro 2.7 | Directory                                    |         | Figure 6.13 | •                                                                                              |

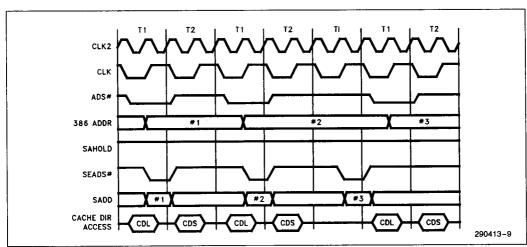

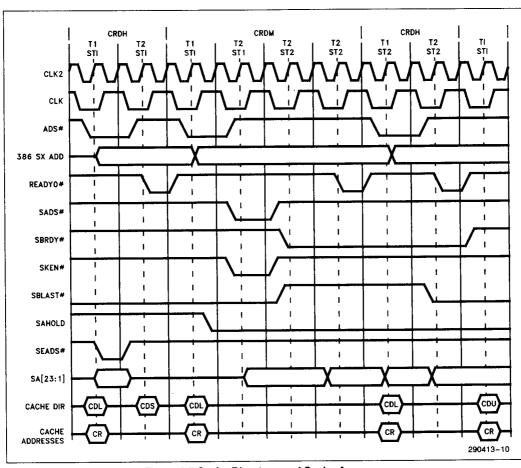

| Figure 2.7 | Cache Directory and Cache Accesses           | . 5-643 | Figure 6.14 | SAHOLD Behavior in<br>Pipelined Cycles 5-677                                                   |

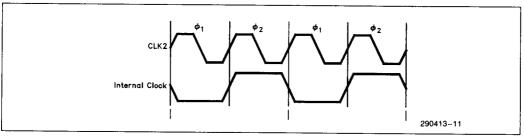

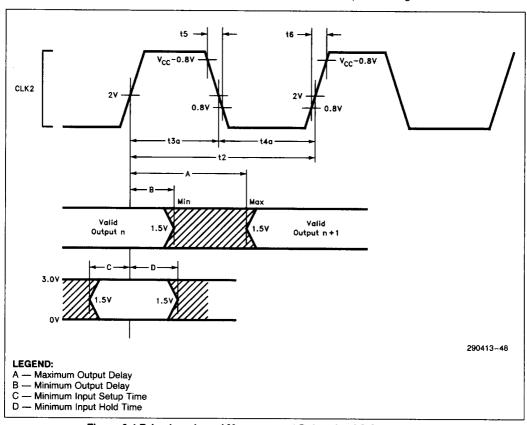

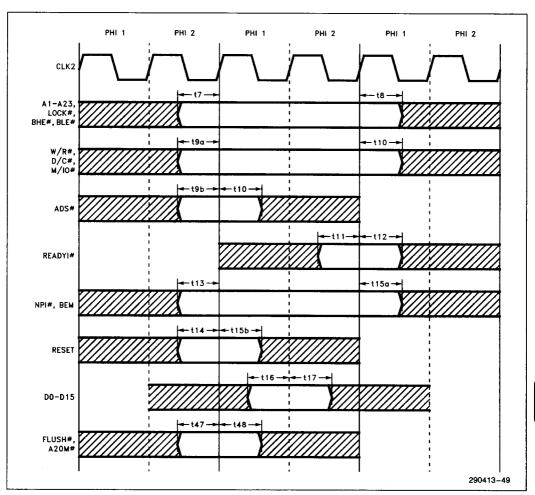

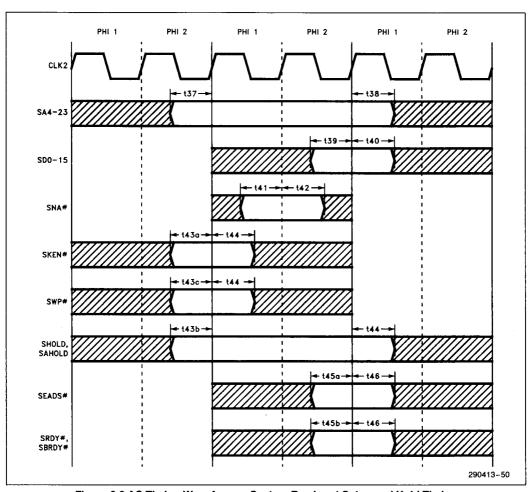

| Figure 3.1 | CLK2 and Internal Clock                      | . 5-646 | Figure 7.1  | SRAM Mode Read Cycle 5-681                                                                     |

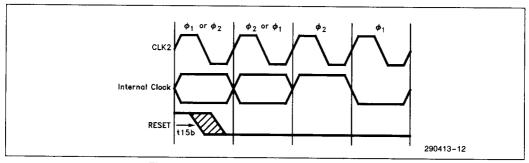

| Figure 3.2 | RESET/Internal Phase<br>Relationship         | 5-646   | Figure 7.2  | SRAM Mode Write Cycle 5-682                                                                    |

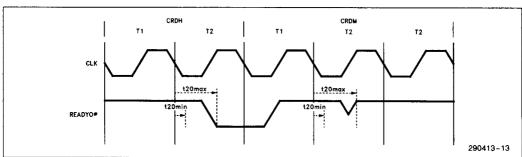

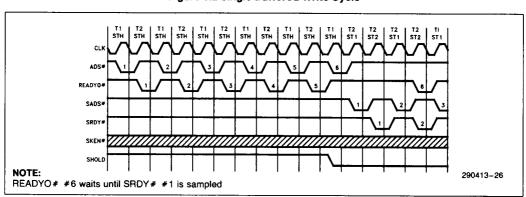

| Figure 4.0 | READYO# Behavior                             |         | Figure 7.3  | Entering the Tristate Test Mode5-682                                                           |

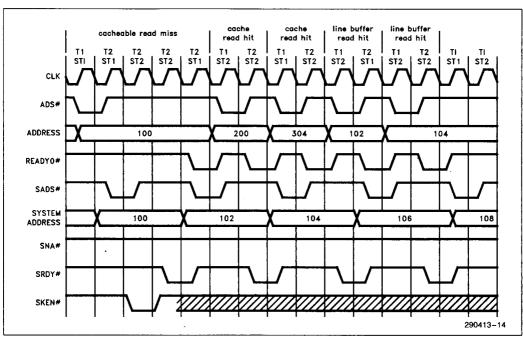

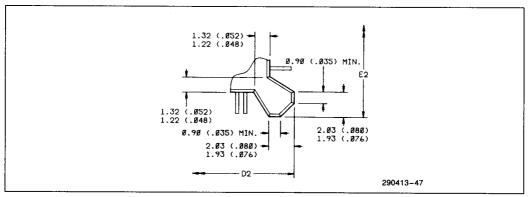

| Figure 4.1 | Read Hit Cycles During a Line Fill           | . 5-654 | Figure 8.1  | Principal Datums and Dimensions 5-683                                                          |

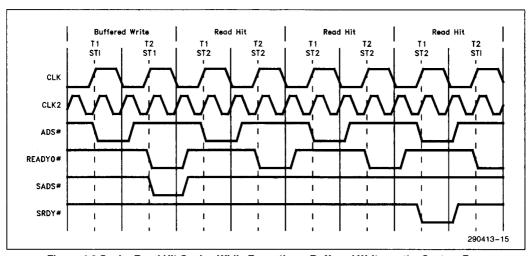

| Figure 4.2 | Cache Read Hit Cycles while                  | е       | Figure 8.2  | Molded Details 5-683                                                                           |

|            | Executing a Buffered Write on the System Bus | . 5-654 | Figure 8.3  | Terminal Details 5-684                                                                         |

| Figure 4.3 | Buffered Write Cycles during                 |         | Figure 8.4  | Typical Lead 5-684                                                                             |

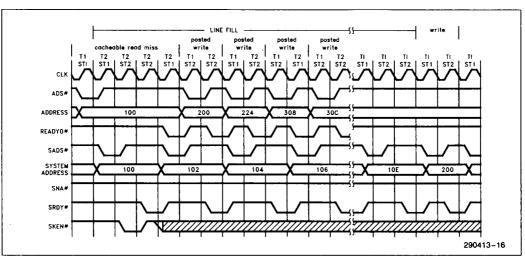

|            | a Line Fill                                  | . 5-655 | Figure 8.5  | Detail M 5-684                                                                                 |

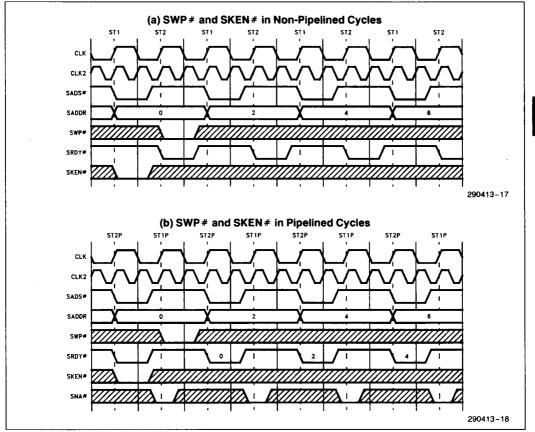

| Figure 4.4 | SWP# and SKEN#<br>Timing                     |         | Figure 9.1  | Drive Levels and<br>Measurement Points for AC                                                  |

| Figure 4.5 | System Description                           | . 5-657 | =           | Specifications 5-688                                                                           |

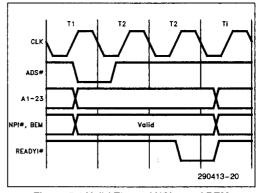

| Figure 5.1 | Valid Time of NPI# and BEM                   | . 5-659 | Figure 9.2  | AC Timing Waveforms -<br>Local Bus Input Setup and<br>Hold Timing                              |

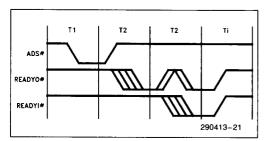

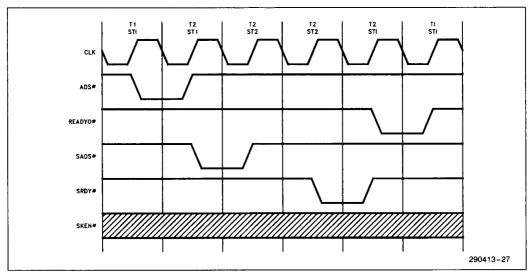

| Figure 5.2 | Externally delayed READY                     | . 5-660 | Figure 9.3  | AC Timing Waveforms -                                                                          |

| Figure 5.3 | A20 Mask Logic                               | . 5-660 |             | System Bus Input Setup and Hold Timing5-692                                                    |

| Figure 5.4 | Valid Time of A20M#                          | . 5-660 | Figure 9.4  | AC Timing Waveforms -                                                                          |

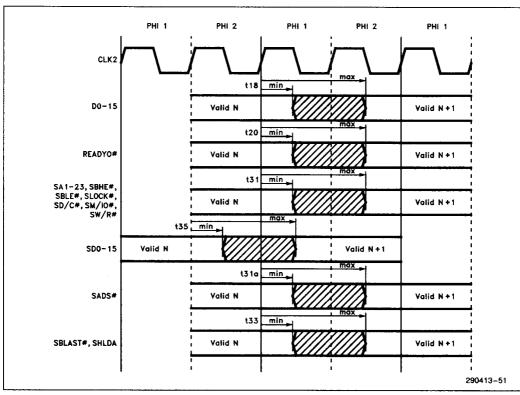

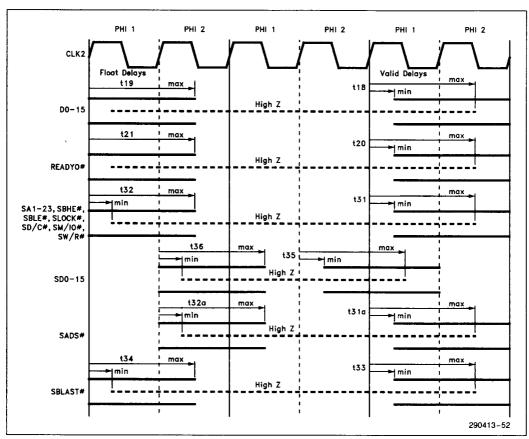

| Figure 6.1 | System Bus State Machine                     | 5 664   |             | Output Valid Delays 5-693                                                                      |

| Figure 6.2 | Single Buffered Write                        |         | Figure 9.5  | AC Timing Waveforms - Output Float Delays 5-694                                                |

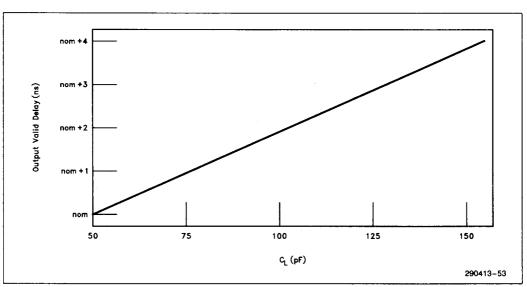

|            | Cycle                                        | . 5-665 | Figure 9.6  | Typical Output Valid Delay vs<br>Load Capacitance at<br>Maximum Operating<br>Temperature 5-695 |

| CONTEN                 | NTS                                                   | PAGE    | CONTEN    | <b>ITS</b> P/                                                          | AGE   |

|------------------------|-------------------------------------------------------|---------|-----------|------------------------------------------------------------------------|-------|

| TABLES Table 0.1       | 82396SX Smart Cache 196                               |         | Table 7.1 | Entering/Exiting the Various 82396SX Smart Cache Test Modes            | 5-678 |

|                        | Lead PQFP Package Pin Description                     | . 5-627 | Table 7.2 | SRAM Memory Map 5                                                      |       |

| Table 2.1              | 82396SX Smart Cache<br>Organization                   |         | Table 7.3 | Cache Address Allocation5                                              | -679  |

| Table 3.1              | Input Pins                                            | . 5-650 | Table 7.4 | TAGRAM Address Allocation                                              | -680  |

| Table 3.2<br>Table 3.3 | Output Pins                                           |         | Table 7.5 | SRAM Test Mode Cache<br>Directory Bit Map 5                            |       |

| Table 4.1              | i386TM SX Microprocessor<br>Bus Cycle Definition with | 5 050   | Table 8.1 | Symbol List for PQFP Package 5                                         |       |

| Table 5.1              | Cacheability                                          |         | Table 8.2 | 82396SX Smart Cache PQFP<br>Package Typical Thermal<br>Characteristics |       |

| Table 5.2              | Activity by Functional Grouping                       | . 5-661 | Table 8.3 | Ambient Temperature vs<br>Airflow5                                     | -686  |

| Table 5.3              | Activity in Line Buffer Hit Cycles                    | . 5-662 | Table 9.1 | Pullup Resistor<br>Recommendations 5                                   | -686  |

| Table 5.4              | Activity in the Line Buffer During ALF Cycles         | . 5-662 | Table 9.2 | DC Specifications 5                                                    | -687  |

| Table 5.5              | Activity in Test Cycles                               |         | Table 9.3 | Local Bus Signal AC Parameters 5                                       | -689  |

| Table 6.1              | Line Fill Address Order                               | . 5-675 | Table 9.4 | System Bus Signal AC Parameters 5                                      | -690  |

#### 0.0 DESIGNER SUMMARY

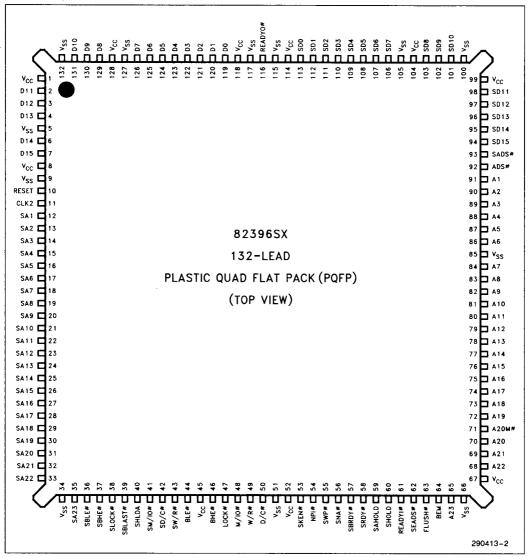

#### 0.1 Pin Out

Figure 0.1 82396SX Smart Cache 132 Lead PQFP Package Pin Orientation

Table 0.1 82396SX Smart Cache 132 Pin PQFP Pin Description

| 1  |                 | Pin | Signal          | <b>!</b> | Pin | Signal          |   | Pin | Signal          |

|----|-----------------|-----|-----------------|----------|-----|-----------------|---|-----|-----------------|

|    | V <sub>CC</sub> | 34  | V <sub>SS</sub> |          | 67  | V <sub>CC</sub> |   | 100 | V <sub>SS</sub> |

| 2  | D11             | 35  | SA23            |          | 68  | A22             |   | 101 | SD10            |

| 3  | D12             | 36  | SBLE#           |          | 69  | A21             | П | 102 | SD9             |

| 4  | D13             | 37  | SBHE#           |          | 70  | A20             | П | 103 | SD8             |

| 5  | V <sub>SS</sub> | 38  | SLOCK#          |          | 71  | A20M#           |   | 104 | V <sub>CC</sub> |

| 6  | D14             | 39  | SBLAST#         |          | 72  | A19             |   | 105 | V <sub>SS</sub> |

| 7  | D15             | 40  | SHLDA           |          | 73  | A18             | П | 106 | SD7             |

| 8  | V <sub>CC</sub> | 41  | SM/IO#          |          | 74  | A17             |   | 107 | SD6             |

| 9  | V <sub>SS</sub> | 42  | SD/C#           |          | 75  | A16             |   | 108 | SD5             |

| 10 | RESET           | 43  | SW/R#           |          | 76  | A15             |   | 109 | SD4             |

| 11 | CLK2            | 44  | BLE#            |          | 77  | A14             |   | 110 | SD3             |

| 12 | SA1             | 45  | V <sub>CC</sub> |          | 78  | A13             |   | 111 | SD2             |

| 13 | SA2             | 46  | BHE#            |          | 79  | A12             |   | 112 | SD1             |

| 14 | SA3             | 47  | LOCK#           |          | 80  | A11             |   | 113 | SD0             |

| 15 | SA4             | 48  | M/10#           |          | 81  | A10             |   | 114 | V <sub>CC</sub> |

| 16 | SA5             | 49  | W/R#            |          | 82  | A9              |   | 115 | V <sub>SS</sub> |

| 17 | SA6             | 50  | D/C#            |          | 83  | A8              |   | 116 | READYO#         |

| 18 | SA7             | 51  | V <sub>SS</sub> |          | 84  | A7              |   | 117 | V <sub>SS</sub> |

| 19 | SA8             | 52  | Vcc             |          | 85  | V <sub>SS</sub> |   | 118 | V <sub>CC</sub> |

| 20 | SA9             | 53  | SKEN#           |          | 86  | A6              |   | 119 | D0              |

| 21 | SA10            | 54  | NPI#            |          | 87  | A5              | l | 120 | D1              |

| 22 | SA11            | 55  | SWP#            |          | 88  | A4              |   | 121 | D2              |

| 23 | SA12            | 56  | SNA#            |          | 89  | A3              |   | 122 | D3              |

| 24 | SA13            | 57  | SBRDY#          |          | 90  | A2              |   | 123 | D4              |

| 25 | SA14            | 58  | SRDY#           |          | 91  | A1              |   | 124 | D5              |

| 26 | SA15            | 59  | SAHOLD          |          | 92  | ADS#            |   | 125 | D6              |

| 27 | SA16            | 60  | SHOLD           |          | 93  | SADS#           |   | 126 | D7              |

| 28 | SA17            | 61  | READYI#         |          | 94  | SD15            |   | 127 | V <sub>SS</sub> |

| 29 | SA18            | 62  | SEADS#          |          | 95  | SD14            |   | 128 | V <sub>CC</sub> |

| 30 | SA19            | 63  | FLUSH#          |          | 96  | SD13            |   | 129 | D8              |

| 31 | SA20            | 64  | ВЕМ             |          | 97  | SD12            |   | 130 | D9              |

| 32 | SA21            | 65  | A23             |          | 98  | SD11            |   | 131 | D10             |

| 33 | SA22            | 66  | V <sub>SS</sub> |          | 99  | V <sub>CC</sub> |   | 132 | V <sub>SS</sub> |

### 0.2 Quick Pin Reference

What follows is a brief pin description. For more details refer to Chapter 3.

| Symbol                | Туре    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK2                  | ı       | This signal provides the fundamental timing for the 82396SX Smart Cache. All external timing parameters are specified with respect to the rising edge of CLK2.                                                                                                                                                                                                                                                                                                                                   |

| Local Addre           | ess Bus | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A[23:1]               | I       | A[23:1] are the Local Bus address lines. These signals along with the byte enable signals, define the physical area of memory or input/output space accessed.                                                                                                                                                                                                                                                                                                                                    |

| BHE#,<br>BLE#         | I       | The byte enable signals are used to determine which bytes are accessed in partial cache write cycles. These signals are ignored for Cache Read Hit cycles. For all System Bus memory read cycles (except the last seven cycles of a Line Fill), these signals are mirrored by the SBHE#, SBLE# signals. (See also SBHE#, SBLE# and BEM.)                                                                                                                                                         |

| Local Bus C           | ycle D  | efinition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| W/R#<br>D/C#<br>M/IO# | 1 1     | The write/read, data/code and memory/input-output signals are the primary bus definition signals directly connected to the i386 <sup>TM</sup> SX Microprocessor. They become valid as the ADS# signal is sampled active. The bus definition signals are not driven by the i386 <sup>TM</sup> SX Microprocessor during bus hold and follow the timing of the address bus.                                                                                                                         |

| LOCK#                 | I       | The Local Bus LOCK# signal indicates that the current bus cycle is LOCK#ed. LOCK#ed cycles are treated as non-cacheable cycles, except that LOCK#ed write hit cycles update the cache.                                                                                                                                                                                                                                                                                                           |

| Local Bus C           | ontrol  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ADS#                  | ı       | The address status pin, an output of the i386™ SX Microprocessor, indicates that new and valid information is currently available on the Local Bus. The signals that are valid when ADS# is activated are: A[23:1], BHE#, BLE#, W/R#, D/C#, M/IO#, LOCK#, NPI#, BEM                                                                                                                                                                                                                              |

| READYI#               | ı       | This is the READY input signal seen by the Local Bus master. Typically it is a logical OR between the READYO# generated by the 82396SX Smart Cache and the READY# signal generated by the i387™ SX Math Coprocessor. It is used by the 82396SX Smart Cache, along with the ADS# signal, to keep track of the i386™ SX Microprocessor bus state.                                                                                                                                                  |

| READYO#               | 0       | This is the Local Bus READY output that is used to terminate all types of i386TM SX Microprocessor bus cycles, except for i387TM SX Math Coprocessor cycles. Assertion of READYO# indicates the completion of the cycle on the Local Bus. The cycle can be concurrently running on the System Bus allowing the dual bus nature of the 82396SX Smart Cache to be utilized.  The READYO# pin may serve as READY# for the i387TM SX Math Coprocessor.                                               |

| Reset                 |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

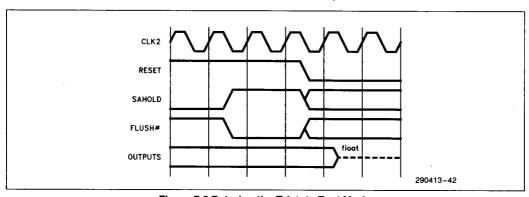

| RESET                 | 1       | The RESET signal forces the 82396SX Smart Cache to begin execution at a known state. The RESET falling edge is used by the 82396SX Smart Cache to set the phase of its internal clock identical to the i386TM SX Microprocessors internal clock. RESET falling edge must satisfy the appropriate setup and hold times (T14, T15b) for proper chip operation. RESET must remain active for at least 1ms after the power supply and CLK2 input have reached their proper DC and AC specifications. |

| Local Data            | Bus     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| D[15:0]               | 1/0     | These are the Local Bus data lines of the 82396SX Smart Cache. They must be connected to the D[15:0] pins of the i386™ SX Microprocessor.                                                                                                                                                                                                                                                                                                                                                        |

| Local Bus D           | ecode   | Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NPI#                  | ı       | The No Post Input signal instructs the 82396SX Smart Cache that the write cycle currently in progress must not be posted in the write buffer. NPI # is sampled at the falling edge of CLK at the end of T1 (see Figure 5.1).                                                                                                                                                                                                                                                                     |

### 0.2 Quick Pin Reference (Continued)

| Symbol                   | Type     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Local Bus                | Decod    | e Pins (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ВЕМ                      | ı        | The Byte Enable Mask signal, when asserted, causes the local bus byte enable signals to be masked so that both system bus byte enables are asserted on memory read cycles. If BEM is asserted during cacheble read cycles and that cycle requires a Line Fill (cache read miss), then both bytes will be accessed during the first cycle of the Line Fill. If BEM is not used (tied low), the system must return valid data for both bytes on the first access of a Line Fill, because SBHE# and SBLE# will be the same as BHE# and BLE# during the first access of a Line Fill and are not always active. |

| Address N                | lask     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

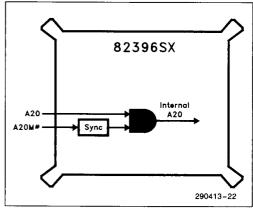

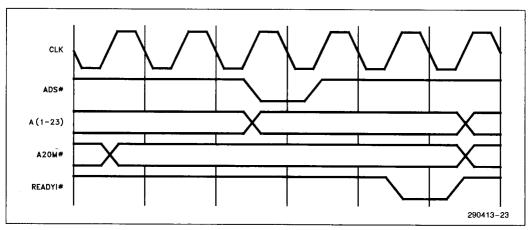

| A20M#                    | ı        | Address bit 20 Mask when active, forces the A20 input as seen by the 82396SX Smart Cache to logic '0', regardless of the actual value on the A20 input pin. A20M# emulates the address wraparound at 1 MByte which occurs on the 8086. This pin is asynchronous but must meet setup and hold times (t47 and t48) to guarantee recognition in a specific clock. It must be asserted two clock cycles before ADS# is sampled active (see figure 5.3). It must be stable throughout Local Bus memory cycles.                                                                                                  |

| System A                 | ddress   | Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

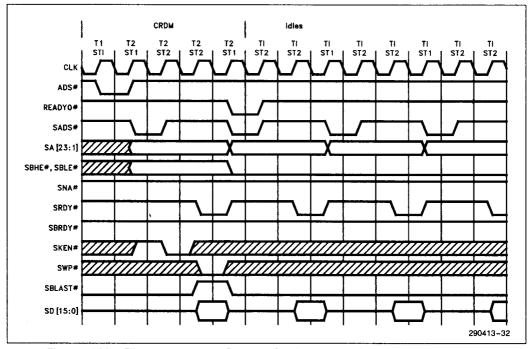

| SA[3:1]<br>SA[23:4]      | 0 9      | These are the System Bus address lines of the 82396SX Smart Cache. When driven by the 82396SX Smart Cache, these signals, along with the System Bus byte enables define the physical area of memory or input/output space being accessed.  During bus HOLD or address HOLD, the 20 MSB serve as inputs for the cache invalidation cycle.                                                                                                                                                                                                                                                                   |

| SBHE#,<br>SBLE#          | 0        | These are the Byte Enable signals for the System Bus. When BEM is inactive, the 82396SX Smart Cache drives these pins identically to BHE# and BLE# in all System Bus cycles except Line Fills. In Line Fills these signals are driven identically to BHE# and BLE# for the first read cycle of the Line Fill. They are both driven active in the remaining cycles of the Line Fill. When BEM is active, the 82396SX Smart Cache will assert SBHE# and SBLE# for all non-locked memory read cycles.                                                                                                         |

| System B                 | us Cycle | e Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SW/R#<br>SD/C#<br>SM/IO# | 000      | The System Bus write/read, data/code and memory/input- output signals are the System Bus cycle definition pins. When the 82396SX Smart Cache is the System Bus master, it drives these signals identically to the i386™ SX Microprocessor cycle definition encoding.                                                                                                                                                                                                                                                                                                                                       |

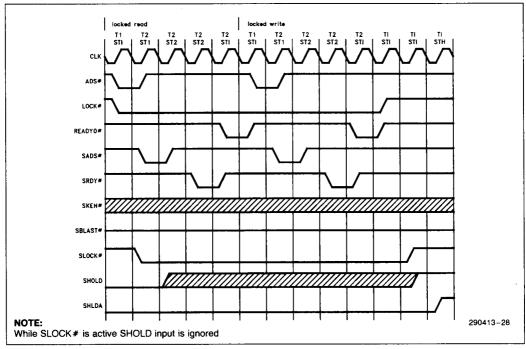

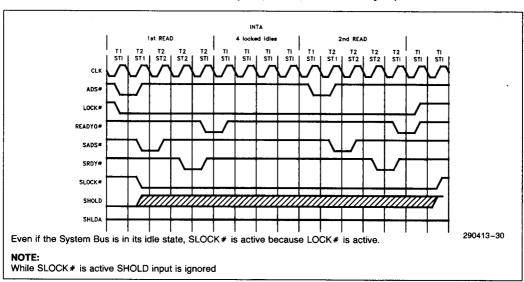

| SLOCK#                   | 0        | The System Bus LOCK signal indicates that the current cycle is LOCK # ed. The 82396SX Smart Cache has exclusive access to the System Bus across bus cycle boundries until this signal is negated. The 82396SX Smart Cache does not acknowledge a bus HOLD request while this signal is asserted. The 82396SX Smart Cache asserts SLOCK# when the System Bus is available and a LOCK#ed cycle was started on the Local Bus that requires System Bus service. SLOCK# is negated only after completion of all LOCK#ed System Bus cycles and negation of the LOCK# signal.                                     |

| System B                 | us Cont  | rol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

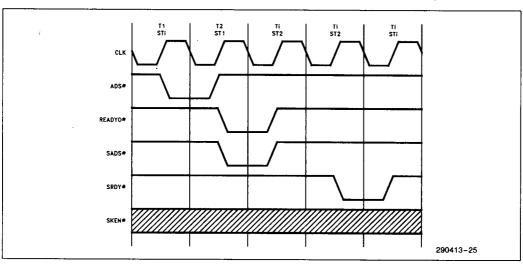

| SADS#                    | 0        | The System Bus Address Status signal is used to indicate that new and valid information is currently being driven onto the System Bus. The signals that are valid when SADS# is driven low are:  SA[23:1], SBHE#, SBLE#, SW/R#, SD/C#, SM/IO# and SLOCK#                                                                                                                                                                                                                                                                                                                                                   |

### 0.2 Quick Pin Reference (Continued)

| Symbol     | Туре      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Bu  | ıs Contro | of (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

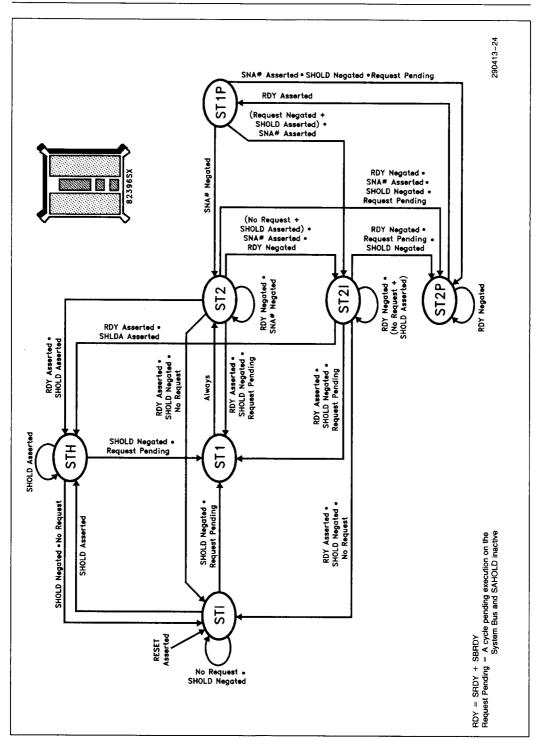

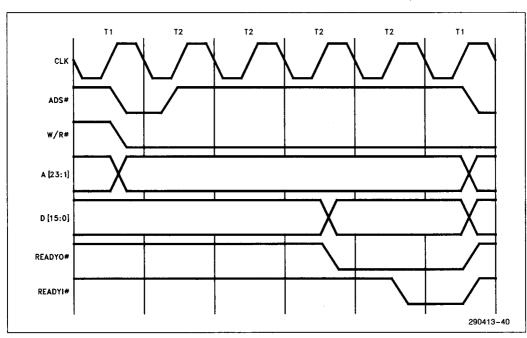

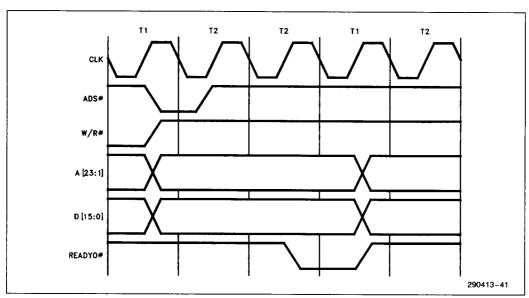

| SRDY#      | I         | The System Bus ReaDY # signal indicates that the current System Bus cycle is complete. When SRDY # is sampled asserted it indicates one of two things. In response to a read request it indicates that the external system has presented valid data on the system data bus. In response to a write request it indicates that the external system has accepted the 82396SX Smart Cache's data. This signal is ignored when the System Bus is in STi, STH, ST1 or ST1P states.  At the first read cycle of a Line Fill SRDY #, SBRDY # and SNA # determine if the Line Fill will proceed as a burst/non-burst, pipelined/non-pipelined Line Fill.  Once a burst Line Fill has started, if SRDY # is returned in the 2nd through the 7th word, the burst Line Fill will be interrupted and the cache will not be updated. The 1st word will already have been transferred to the CPU. In the 8th word of a Line Fill both SRDY # and SBRDY # have the same effect. They indicate the end of the Line Fill. |

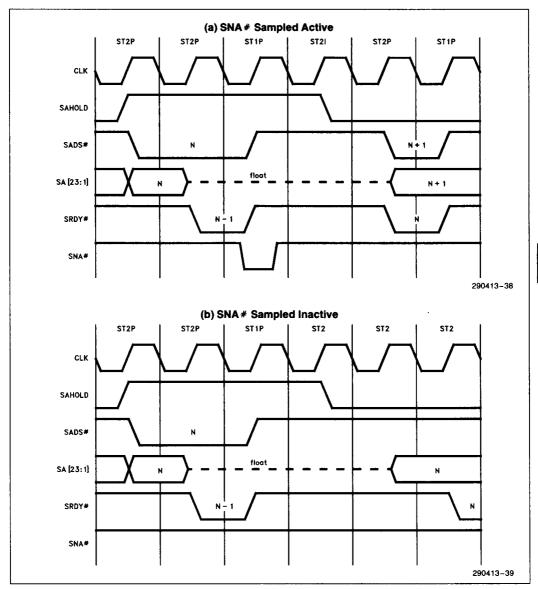

| SNA#       | I         | The System Bus Next Address signal, when active, indicates that a pipelined address cycle will be executed. It is sampled by the 82396SX Smart Cache at the rising edge of CLK in ST2 and ST1P cycles. SNA# is ignored during the eighth word of the Line Fill. If this signal is sampled active for the first word of the Line Fill then burst Line Fills are disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bus Arbitr | ation     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SHOLD      |           | The System Bus HOLD request indicates that another master must have complete control of the entire System Bus. When SHOLD is sampled asserted the 82396SX Smart Cache completes the current System Bus cycle or sequence of LOCK # ed cycles, before driving SHLDA active. In the same clock that SHLDA went active all the System Bus outputs and I/O pins are floated (with the exception of SHLDA). The 82396SX Smart Cache stays in this state until SHOLD is negated. SHOLD is recognized during RESET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SHLDA      | 0         | The System Bus HOLD Acknowledge signal is driven active by the 82396SX Smart Cache in response to a hold request. It indicates that the 82396SX Smart Cache has given the bus to another System Bus master. It is driven active in the same clock that the 82396SX Smart Cache floats it's System Bus. When leaving a bus HOLD, SHLDA is driven inactive and the 82396SX Smart Cache resumes driving the bus in the same clock. The 82396SX Smart Cache is able to support CPU Local Bus activities during System Bus HOLD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Burst Con  | trol      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SBRDY#     | 1         | The System Bus Burst ReaDY signal performs the same function during a burst cycle that SRDY # does in a non-burst cycle. SBRDY # asserted indicates that the external system has presented valid data on the data pins in response to a burst Line Fill cycle. This signal is ignored when the System Bus is at STi, STH, ST1 or ST1P states.  Note that in the eighth bus cycle of a Line Fill, SBRDY # and SRDY # have the same effect on the 82396SX Smart Cache. They indicate the end of the Line Fill. For all cycles other than burst Line Fills, SBRDY # and SRDY # have the same effect on the 82396SX Smart Cache.                                                                                                                                                                                                                                                                                                                                                                            |

### 0.2 Quick Pin Reference (Continued)

| Symbol            | Туре     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Burst Cont</b> | rol (Cor | tinued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

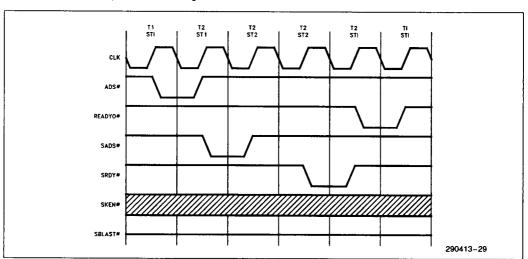

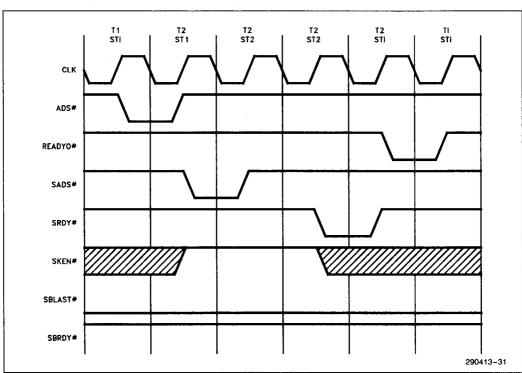

| SBLAST#           | 0        | The System Bus Burst LAST cycle indicator signal indicates that the next time SBRDY# is returned the burst cycle is complete. It indicates to the external system that the next SBRDY# returned is treated as a normal SRDY# by the 82396SX Smart Cache. Another set of addresses will be driven with SADS# or the System Bus will go idle. SBLAST# is normally active. In a cache read miss cycle, which may proceed as a Line Fill, SBLAST# starts active. After determining whether or not the cycle is cacheable via SKEN#, SBLAST# is driven inactive. If it is a cacheable cycle, and SBRDY# terminates the first word of the Line Fill, a burst Line Fill, SBLAST# will be driven active when the data is valid for the eighth word of the Line Fill. If SRDY# terminates the first word of the Line Fill, a non-burst Line Fill, SBLAST# is driven active in the cycle where SRDY# was sampled active. |

| Cache Inva        | lidation |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SAHOLD            | ı        | The System Bus Address HOLD request allows another bus master access to the address bus of the 82396SX Smart Cache. This is to indicate the address of an external cycle for performing an internal cache directory lookup and invalidation cycle. In response to this signal the 82396SX Smart Cache stops driving the System Bus address pins in the next cycle. No HOLD Acknowledge is required. Other System Bus signals can remain active during address hold. The 82396SX Smart Cache does not initiate another bus cycle during address hold. This pin is recognized during RESET.                                                                                                                                                                                                                                                                                                                      |

| SEADS#            |          | The System Bus External Address Strobe signal indicates that a valid external address has been driven onto the 82396SX Smart Cache System Bus address pins. This address will be used to perform an internal cache invalidation cycle. The maximum invalidation cycle rate is one every two clock cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Cache Con         | trol     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FLUSH#            | 1        | The FLUSH # pin, when sampled active for four clock cycles or more, causes the 82396SX Smart Cache to invalidate its entire TAG array. In addition, it is used to configure the 82396SX Smart Cache to enter various test modes. For details refer to chapter 7. This signal is asynchronous but must meet setup and hold times to guarantee recognition in any specific clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| System Da         | ta Bus   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SD[15:0]          | 1/0      | The System Bus Data lines of the 82396SX Smart Cache must be driven with appropriate setup and hold times for proper operation. These signals are driven by the 82396SX Smart Cache only during write cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| System Bu         | s Deco   | de Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SKEN#             | I        | The System Cacheability Enable signal is used to determine if the current cycle running on the System Bus is cacheable or not. When the 82396SX Smart Cache generates a read cycle, SKEN# is sampled one clock before the first SBRDY# or SRDY# or one cycle before the first SNA# is sampled active (see chapter 6). If SKEN# is sampled active the cycle will be transformed into a Line Fill. Otherwise, the cache and cache directory will be unaffected. Note that SKEN# is ignored after the first cycle in a Line Fill. SKEN# is ignored for all System Bus cycles except for cache read miss cycles.                                                                                                                                                                                                                                                                                                   |

| SWP#              | l        | The System Write Protect indicator signal is used to determine whether the current System Bus Line Fill cycle is write protected or not. In non-pipelined cycles, SWP # is sampled with the first SRDY # or SBRDY # of the Line Fill. In pipelined cycles, SWP # is sampled one clock phase after the first SNA # is sampled active (see figures 6.9-10). The Write Protect bit is sampled together with the TAG of each line in the 82396SX Smart Cache Cache Directory. In every cacheable write cycle the Write Protect bit is read. If active, the cycle will be a write protected cycle which is treated like a cacheable write miss cycle. It is buffered and it does not update the cache even if the addressed location is present in the cache.                                                                                                                                                       |

# 1.0 82396SX SMART CACHE FUNCTIONAL OVERVIEW

#### 1.1 Introduction

The primary function of a cache is to provide local storage for frequently accessed memory locations. The cache intercepts memory references and handles them directly without transferring the request to the System Bus. This results in lower traffic on the System Bus and decreases latency on the Local Bus. This leads to improved performance for a processor on the Local Bus. It also increases potential system performance by reducing each processor's demand for System Bus bandwidth, thus allowing more processors or system masters in the system. By providing fast access to frequently used code and data the cache is able to reduce the average memory access time of the i386TM SX Microprocessor based system.

The 82396SX Smart Cache is a single chip cache subsystem specifically designed for use with the i386TM SX Microprocessor. The 82396SX Smart Cache integrates 16KB cache, the Cache Directory and the cache control logic onto one chip. The cache is unified for code and data and is transparent to application software. The 82396SX Smart Cache provides a cache consistency mechanism which guarantees that the cache has the most recently updated version of the main memory. Consistency support has no performance impact on the i386TM SX Microprocessor. Section 1.2 covers all the 82396SX Smart Cache features.

The 82396SX Smart Cache architecture is similar to the i486™ SX Microprocessor's on-chip cache. The cache is four Way SET associative with Pseudo LRU (Least Recently Used) replacement algorithm. The

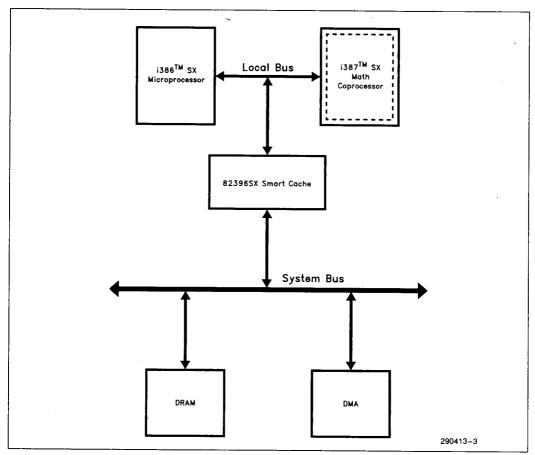

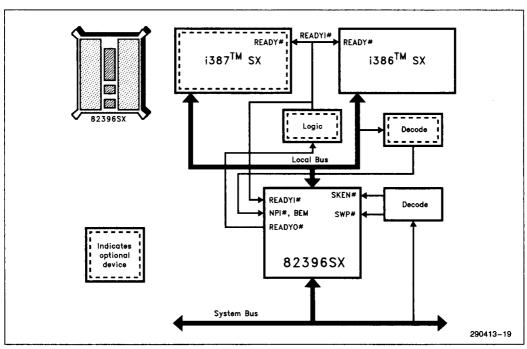

Figure 1.1 System Block Diagram

line size is 16B and a full line is retrieved from the memory for every cache miss. A TAG is associated with every 16B line. The 82396SX Smart Cache architecture allows for cache read hit cycles to run on the Local Bus even when the System Bus is not available. 82396SX Smart Cache incorporates a new write buffer cache architecture, which allows the i386TM SX Microprocessor to continue operation without waiting for write cycles to actually update the main memory.

A detailed description of the cache operation and parameters is included in Chapter 2.

The 82396SX Smart Cache has an interface to two electrically isolated busses. The interface to the i386TM SX Microprocessor bus is referred to as the Local Bus (LB) interface. The interface to the main memory and other system devices is referred to as the 82396SX Smart Cache System Bus (SB) interface. The SB interface emulates the i386TM SX Microprocessor. The SB interface, as does the i386TM SX Microprocessor, operates in pipeline mode.

In addition, it is enhanced by an optional burst mode for Line Fills. The burst mode provides faster line fills by allowing consecutive read cycles to be executed at a rate of up to one word per clock cycle. Several bus masters (or several 82396SX Smart Caches) can share the same System Bus and the arbitration is done via the SHOLD/SHLDA mechanism (similar to the i486TM SX Microprocessor).

Cache consistency is maintained by the SAHOLD/ SEADS# snooping mechanism, similar to the i486TM SX Microprocessor. The 82396SX Smart Cache is able to run a zero wait state i386TM SX Microprocessor non-pipelined read cycle if the data exists in the cache. Memory write cycles can run with zero wait states if the write buffer is not full.

The 82396SX Smart Cache organization provides a higher hit rate than other standard configurations. The 82396SX Smart Cache, featuring the new high performance write buffer cache architecture, provides full concurrency between the electrically isolated Local Bus and System Bus. This allows the 82396SX Smart Cache to service read hit cycles on the Local Bus while running line fills or buffered write cycles on the System Bus.

#### 1.2 Features

#### 1.2.1 82385SX-LIKE FEATURES

The 82396SX Smart Cache maps the entire physical address range of the i386<sup>TM</sup> SX Microprocessor (16MB) into an 16KB cache.

- Unified code and data cache.

- Cache attributes are handled by hardware. Thus the 82396SX Smart Cache is transparent to application software. This preserves the integrity of system software and protects the users software investment.

- Word and Byte writes, Word reads.

- Zero wait states in read hits and in buffered write cycles. All i386<sup>TM</sup> SX Microprocessor cycles are non-pipelined (Note: The i386<sup>TM</sup> SX Microprocessor must never be pipelined when used with the 82396SX Smart Cache - NA # must be tied to Vcc).

- A hardware cache FLUSH# option. The 82396SX Smart Cache will invalidate all the Tag Valid bits in the Cache Directory and clear the System Bus line buffer when FLUSH# is activated for a minimum of four CLK's.

- The 82396SX Smart Cache supports non-cacheable accesses.

- The 82396SX Smart Cache internally decodes the i387<sup>TM</sup> SX Math Coprocessor accesses as Local Bus cycles.

- The System Bus interface emulates a i386<sup>TM</sup> SX Microprocessor interface.

- The 82396SX Smart Cache supports pipelined and non-pipelined system interface.

- Provides cache consistency (snooping): The 82396SX Smart Cache monitors the System Bus address via SEADS# and invalidates the cache address if the System Bus address matches a cached location.

#### 1.2.2 NEW FEATURES

- 16KB on chip cache arranged in four banks, one bank for each way. In Read hit cycles, one word is read. In a write hit cycle, any byte within the word can be written. In a cache fill cycle, the whole line (16B) is written. This large line size increases the hit rate over smaller line size caches.

- Cache architecture similar to the i486TM SX Microprocessor cache: 4 Way set associative with Pseudo LRU replacement algorithm. Line size is 16B and a full line is retrieved from memory for every cache miss. A Tag Valid Bit and a Write Protect Bit are associated with every Line.

- New write buffer architecture with four word deep write buffer provides zero wait state memory write cycles. I/O, Halt/Shutdown and LOCK#ed writes are not buffered.

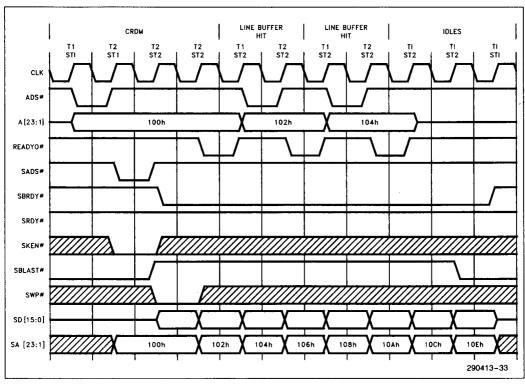

- Concurrent Line Buffer Cacheing: The 82396SX Smart Cache has a line buffer that is used as additional memory. Before data gets written to

the cache memory at the completion of a Line Fill it is stored in this buffer. Cache hit cycles to the line buffer can occur before the line is written to the cache

- In i387<sup>TM</sup> SX Math Coprocessor accesses, the 82396SX Smart Cache drives the READYO# in one wait state if the READYI# was not driven in the previous clock.

- Note that the timing of the 82396SX Smart Cache's READYO# generation for i387TM SX Math Coprocessor cycles is incompatible with 80287 timing.

- An enhanced System Bus interface:

- a) Burst option is supported in line-fills similar to the i486<sup>TM</sup> SX Microprocessor. SBRDY# (System Burst READY) is provided in addition to SRDY#. A burst is always a 16 byte line fill (cache update) which is equivalent to eight word cycles.

- b) System cacheability attribute is provided (SKEN#). SKEN# is used to determine whether the current cycle is cacheable. It is used to qualify Line Fill requests.

- c) SHOLD/SHLDA system bus arbitration mechanism is supported. A Multi i386<sup>TM</sup> SX / 82396SX Smart Cache cluster can share the same System Bus via this mechanism.

- f) Cache invalidation cycles supported via SEAD\$#. This is used to provide cache coherency.

- Full Local Bus/System Bus concurrency is attained by:

- a) Servicing cache read hit cycles on the Local Bus while completing a Line Fill on the System Bus. The data requested by the i386<sup>TM</sup> SX Microprocessor is provided over the local bus as the first word of the Line Fill.

- Servicing cache read hit cycles on the Local Bus while executing buffered write cycles on the system bus.

- c) Servicing cache read hit cycles on the Local Bus while another bus master is running (DMA, other i386™ SX Microprocessor, 82396SX Smart Cache, i486™ SX Microprocessor, etc...) on the System Bus.

- d) Buffering write cycles on the Local Bus while the system bus is executing other cycles.

- Write protected areas are supported by the SWP# input. This enables caching of ROM space or shadowed ROM space.

- No Post Input (NPI#) provided for disabling of write buffers per cycle. This option supports memory mapped I/O designs.

- Byte Enable Mask (BEM) is provided to mask the processor byte enables during a memory read cycle.

- A20M# input provided for emulation of 8086 address wrap-around.

- SRAM test mode, in which the TAGRAM and the cache RAM are treated as standard SRAM, is provided. A Tristate Output test mode is also provided for system debugging. In this mode the 82396SX Smart Cache is isolated from the other devices in the board by floating all its outputs.

- Single chip, 132 lead PQFP package, 1 micron CHMOS-IV technology.

# 2.0 82396SX SMART CACHE SYSTEM DESCRIPTION

#### 2.1 82396SX Smart Cache Organization

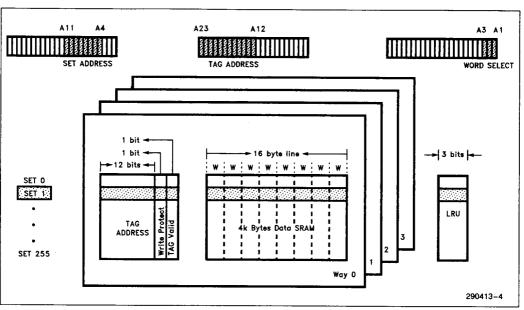

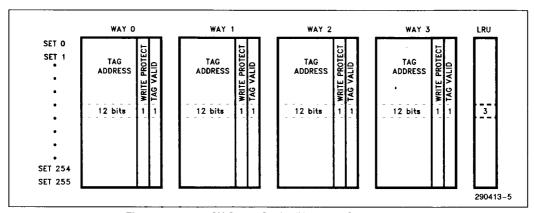

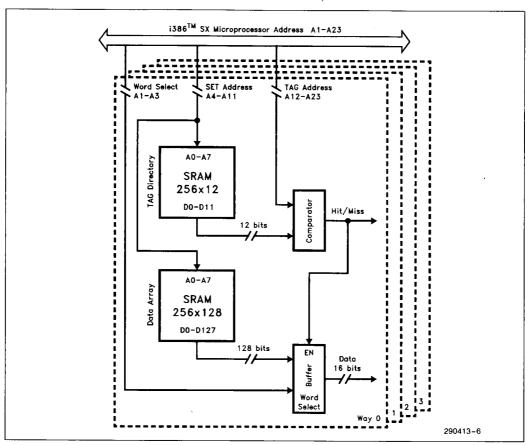

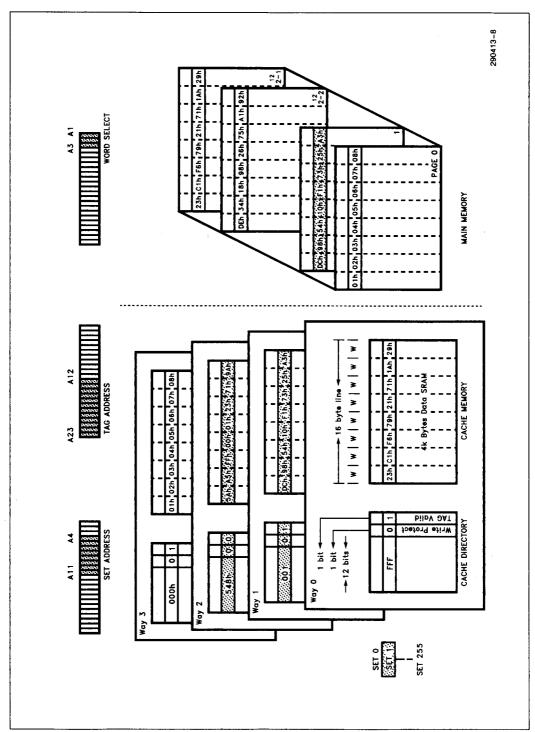

The on chip cache memory is a unified code and data cache. The cache organization is 4 Way SET Associative and each Line is 16 bytes wide (see Figure 2.1). The 16K bytes of cache memory are logically organized as 4 4KB banks (4: 1 bank for each Way). Each bank contains 256 16B lines (256: 1 line for each SET).

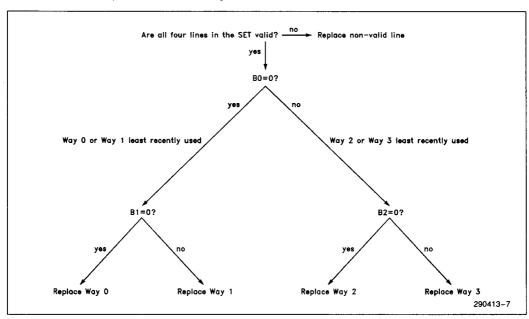

The Cache Directory is used to determine whether the data in the cache memory is valid for the address being accessed. The Cache Directory contains 256 TAG's (each TAG is 14-bits wide) for each Way, for a total of 1K TAG's (See Figure 2.2). With each 12 bit TAG Address there is a TAG Valid bit and a Write Protect bit. The Cache Directory also contains the LRU bits. The LRU bits are used to determine which Way to replace whenever the cache needs to be updated with a new line and all four ways contain valid data.

Table 2.1 lists the 82396SX Smart Cache organization.

Figure 2.1. 82396SX Smart Cache Organization

Table 2.1 82396SX Smart Cache Organization

| Cache Element     | 82396SX<br>Size/Qty | Comments                                                                                                                |

|-------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------|

| TAG               | 1K                  | Total number of TAGs                                                                                                    |

| SET               | 256                 | Cache Directory Offset                                                                                                  |