# ELITE 80386 PC/AT EAGLE CHIPSET e88C311 & e88C312

#### An Overview

The Eagle 386 AT chip set is designed for high performance PC-ATs with 80386DX running at 20/25/33 MHz. Major features of the Eagle chip set include:

- 100% IBM PC-AT compatible 386DX chip set

- Supports 20, 25 and 33 MHz 386DX based PC-ATs

- Fully integrated cache controller along with DRAM controller improves overall system performance

- Supports direct mapped and two way set-associative cache organizations

- Provides buffered write-through DRAM updating scheme to minimize write cycle penalty

- Supports 32KB, 64 KB and 128 KB of data cache

- Provides four blocks of non-cacheable regions ranging from 4KB to 4MB to offer software compatibility

- Provides cache freeze facility for frequently used program codes

- ZERO wait state for both pipelined/non-pipelined cache read hit access

- Highly optimized DRAM controller

- Supports up to 64MB of system memory

- Supports 256Kb, 1Mb and 4 Mb of DRAM configurations

- Provides both Page and Page-interleaved operations

- Supports 256KB of shadow RAM with 16KB granularity

- Provides hidden, burst and PC-AT style refresh modes

- Provides sophisticated memory remapping scheme to maximize the usage of physical memory installed

- ZERO wait state for both pipelined/non-pipelined cache miss/page hit operation

- Supports both 80387 and Weitek WTL3167 math coprocessors

- Provides both the Fast GATEA20 and Fast Reset for OS/2 optimization

- Provides programmable PC-AT bus clock to allow both synchronous and asynchronous operations

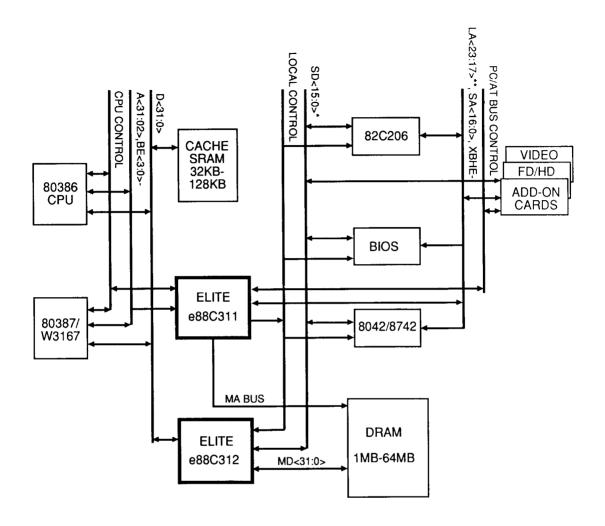

<sup>\*</sup>XD<7:0> Share the same BUS as SD<7:0>

Figure 0-1. System Block Diagram

<sup>\*\*</sup>XA<23:00> Share the same BUS as LA<23:17> and SA<16:00>

- Provides on-board chip selection logic for one parallel and two serial ports

- Provides on-board chip select logic for two software programmable I/O ports

- Requires less than 24 devices (including CPU, ROM, KBC) plus DRAMs/SRAMs for a complete cache based 386DX PC-ATs

- Supports both Cache/Cacheless PC-ATs with same design

- Provides 60 configuration registers to offer product differentiation and optimization

The Eagle 386DX AT chip set consists of the e88C311 and e88C312. Along with the commonly available Integrated Peripheral Controller, e.g., the 82C206, a high-performance, compact and cost-effective cache based 386DX PC-ATs can be implemented efficiently. This is achieved through a very high level of function integration and system partition. The Eagle chip set is designed to provide 100% IBM PC-AT compatibility while offering flexibility in addressing both the requirements of cache and non-cache based 386 PC-ATs. The Eagle chip set also provides system designers with sixty software programmable configuration registers in controlling the operation features of their designs.

#### e88C311 CPU/CACHE/DRAM Controller, an Introduction

The e88C311 generates and synchronizes all the control signals for buses and manages the interfaces of all functional blocks inside the chip, e.g., reset/shutdown logic, CPU/local memory/AT/Cache state machines, arbitration and refresh logic, DRAM controller, and the cache controller. The highly integrated cache controller with built-in TAG RAM supports both direct mapped or two way set-associative cache organization with data cache size ranging from 32KB, 64KB to 128KB. It implements a buffered write-through DRAM updating scheme and a Least Recently Used (LRU) replacement algorithm to improve the system performance.

By integrating the cache controller along with the DRAM controller, the e88C311 can further enhance system performance by time-sharing cache and DRAM cycles. For example, when a read cycle starts, cache access and DRAM access are performed in parallel and DRAM cycle can continue and/or be terminated depending on the outcome of the cache hit/miss detection. In such case, the time penalty associated with non-integrated cache/DRAM architecture is reduced because the e88C311 does not have to wait for the hit/miss signal from the TAG RAM directory to start the DRAM operation. The e88C311 thus can achieve ZERO wait state operation, for both pipelined and non-pipelined modes, during a cache hit access.

To further enhance system performance, the e88C311 provides an optimized page-interleaved DRAM operation. A ZERO wait state DRAM access can still be obtained during a page hit cycle following a cache read miss in a pipelined operation. In addition, the refresh scheme of the e88C311 is designed in such a way that when the Hidden/Burst mode option is enabled, the CPU can keep operating out of cache while the DRAM refresh logic is servicing the refresh requests. This would result in further improvement of the system performance.

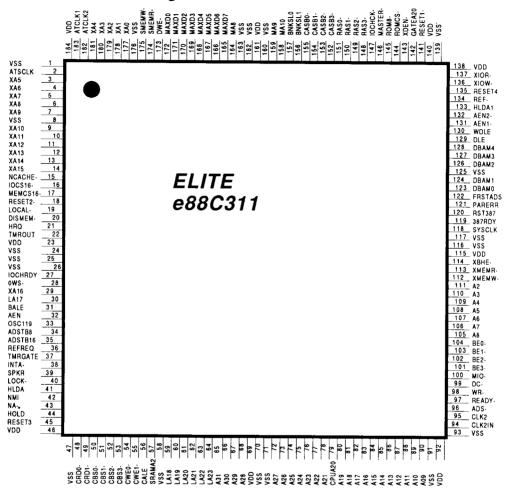

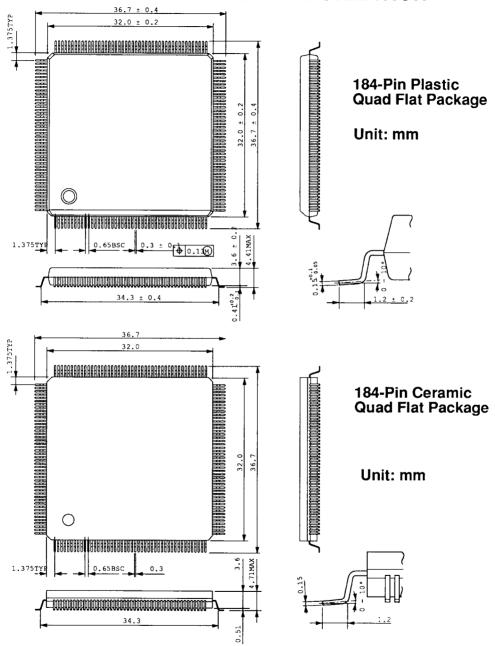

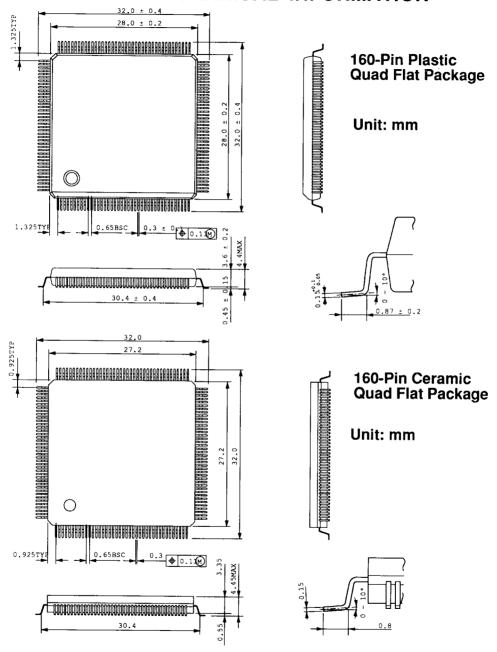

The e88C311 is available in 184 Pin PQFP (Plastic Quad Flat Package) with the more preferable 25 mil lead pitch to allow higher reliability during surface mount manufacturing process.

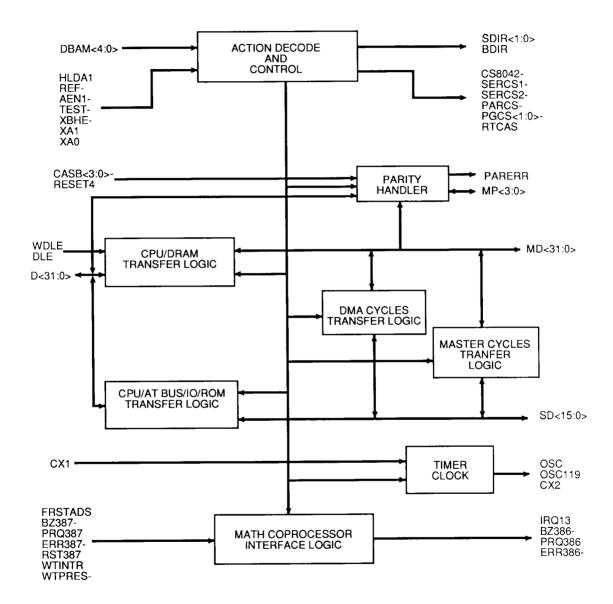

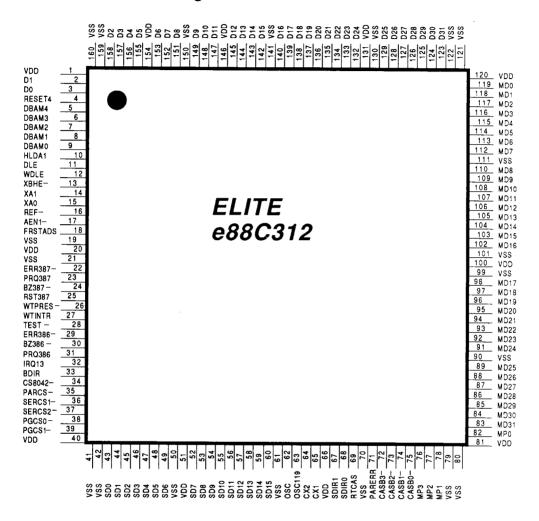

## e88C312 DATA Controller, an Introduction

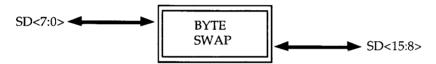

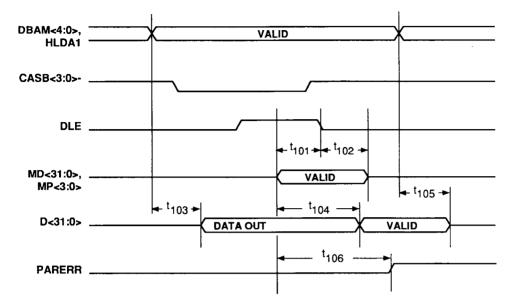

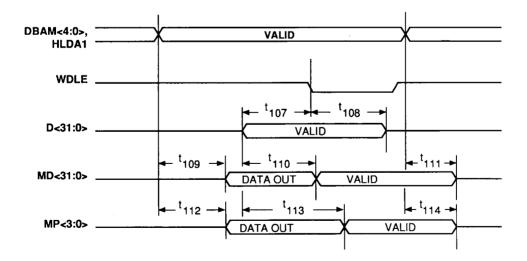

The e88C312 contains the control logic to manage the interface between the CPU data bus, local/main memory data bus, local system bus, PC-AT bus, ROM, and on-board peripherals. It also implements the byte alignment and byte swapping logics for data transfer where source and target are of different bus widths. The parity logic embedded in the e88C312 generates and writes the parity bits into the DRAM array during main memory write cycles. It also latches the data parity for each byte during memory read cycle. The parity handler and associated NMI logic is designed to assure data integrity throughout the system operation. The built-in coprocessor detection/interface circuitry supports both Intel 80387 and Weitek WTL3167 math coprocessors without additional discrete logic. The e88C312 also provides on-board chip selects for one parallel port, two serial ports and two software programmable I/O ports.

The e88C312 is available in 160 Pin PQFP (Plastic Quad Flat Package) with 25 mil lead pitch to allow higher reliability during surface mount manufacturing process.

# e88C311 CPU/CACHE/DRAM CONTROLLER

#### An Overview

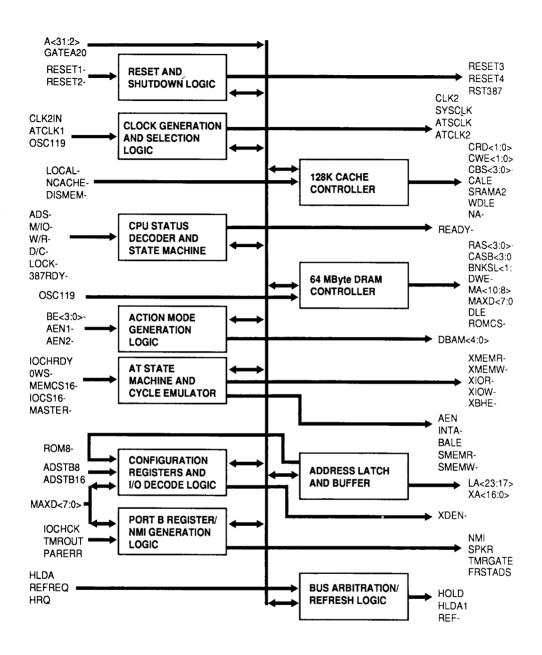

The e88C311 incorporates following function blocks:

- 1) Reset and shutdown logic

- 2) Clock generation and selection logic

- 3) Port B register and NMI generation logic

- 4) Action mode codes generation

- 5) CPU state machine, local memory state machines, cache state machines, and AT bus state machine

- 6) Bus arbitration

- 7) Coprocessor support

- 8) Cache controller

- 9) Page interleaved DRAM controller

- 10) Configuration registers

By utilizing the e88C311 together with the e88C312, the system designer can incorporate the most powerful cache based system while maintaining 100% compatibility with the IBM PC-AT architecture. In addition, the sixty (60) configuration registers provide OEMs with vast opportunities to offer product differentiation by fine tuning the system parameters.

# 1. e88C311 FUNCTIONAL DESCRIPTION

# 1.1 Reset and Shutdown Logic

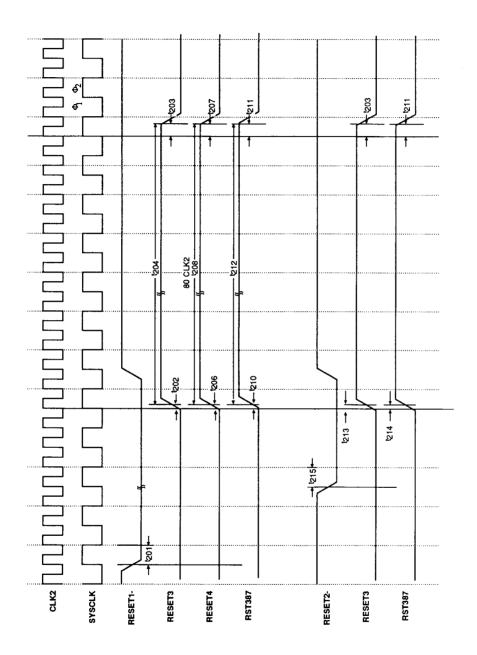

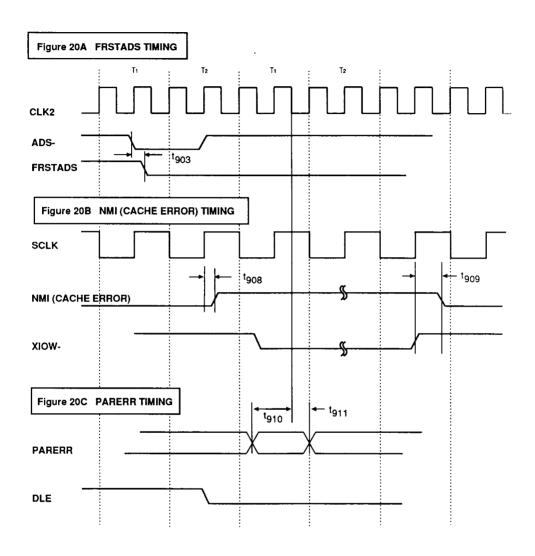

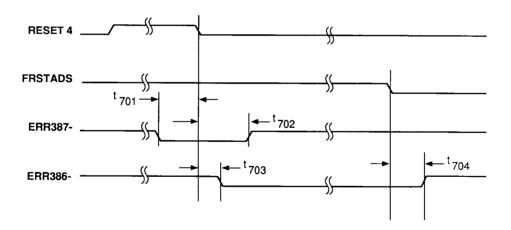

The e88C311 takes RESET1- and RESET2- inputs and generates the signals RESET3, RESET4 and RST387 that trigger both warm and cold reset. RESET1- is the Power Good signal and originates at the power supply. When RESET1- is active, the e88C311 will assert RESET3, RESET4 and RST387 initiating a cold reset of the complete system. If RESET2- is asserted by the keyboard controller (8042 or 8742) a system warm reset is generated, the e88C311 asserts RESET3 to reset the CPU. RESET3 is also asserted by the e88C311 when a shutdown bus cycle is detected. Additionally, a fast reset option is provided in the e88C311 to generate a warm reset without the long delay normally associated with the keyboard controller. This is done by writing bit 5 of configuration register 12h.

Both RESET3 and RESET4 should last for at least 80CLK2 cycles. The HIGH to LOW transition of RESET3 and RESET4 signal must be synchronous with CLK2 input signal to the 80386. This guarantees that the phase of the internal clock of the e88C311 state machine is the same as the phase of the internal clock of the 80386.

RST387 is the coprocessor reset signal. RST387 is activated by RESET3 or an I/O write operation to port F1. The High to Low transition of RST387 must meet the set-up and hold time requirement of the 80387. RST387 is held active for at least 80 CLK2 cycles and the 80386 will not receive a READY-signal from the coprocessor until at least 50 CLK2 periods after RST387 goes inactive.

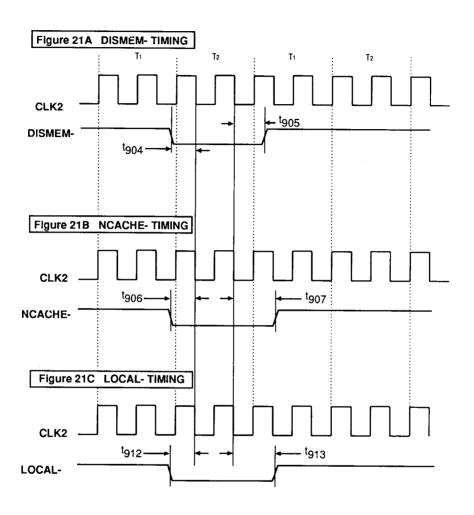

Figure 1-1. e88C311 Block Diagram

## 1.2 Clock Generation and Selection Logic

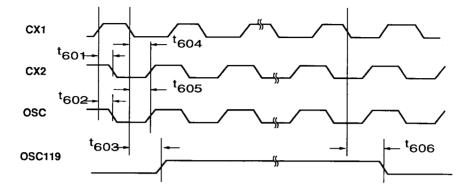

The e88C311 receives three clock inputs: CLK2IN, ATCLK1 and OSC119. It generates various clock signals to drive the 80386, the coprocessor, DRAM/Cache/AT state machines and the AT bus system. CLK2IN is derived from a crystal oscillator running at twice the rated frequency of the 80386, e.g., 66 MHZ for a 33 MHZ 80386 system. ATCLK1 is derived from another TTL crystal oscillator running at twice the frequency of the AT bus clock. OSC119 is a 1.19 MHZ clock generated by the 88C312 to control page mode RAS- time out in the DRAM controller.

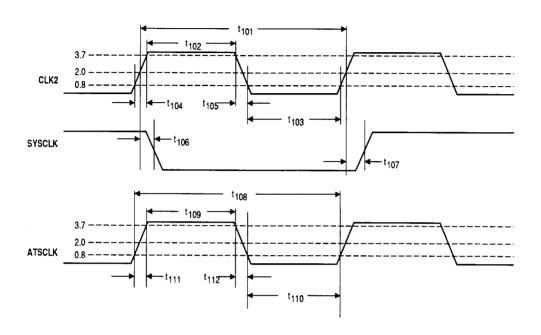

The e88C311 generates four clock output signals: CLK2, SYSCLK, ATCLK2 and ATSCLK. The processor clock CLK2 drives the CLK2 inputs of the 80386 and the coprocessor. It is also used to drive e88C311 internal DRAM/Cache state machines. The SYSCLK signal is derived by dividing the CLK2 signal in half and is in phase with the internal state of the 80386. ATCLK2 is the AT bus state machine clock. ATSCLK is always ATCLK2/2 and is used to drive the AT bus clock.

Under normal condition, CLK2 is derived from CLKIN2 to allow the 80386 to operate at the maximum speed. ATCLK2 can be either a sub-division of CLK2IN or can be derived from ATCLK1 input. ATCLK1 may be selected as CLK2 source to slow down code execution.

By setting bits <7:6> of configuration register 11h and bit 7 of configuration register 12h, the ATCLK2 frequency can be programmed to be ATCLK1, CLK2IN/3, CLK2IN/4 or CLK2IN/5. The CLK2 signal can be programmed to run at the same frequency as CLK2IN or ATCLK1.

# 1.3 Port B Register and NMI generation logic

The e88C311 provides access to the Port B defined for PC/AT system level function control. The port can be accessed through any odd I/O port address between 61h and 6Fh. Table 1 shows the register definition:

Table 1-1 Port B Register Definition

| BITs | READ/WRITE | DEFINITION   |                         |  |

|------|------------|--------------|-------------------------|--|

| 7    | READ ONLY  | PCK          | Memory Parity Check     |  |

| 6    | READ ONLY  | IO CH CK     | IO Channel Check        |  |

| 5    | READ ONLY  | OUT 2        | Timer 2 (8254) Out      |  |

| 4    | READ ONLY  | REF DET      | Refresh Detect          |  |

| 3    | READ/WRITE | ENA IO CK-   | Enable IO Channel Check |  |

| 2    | READ/WRITE | ENA RAM PCK- | Enable RAM Parity Check |  |

| 1    | READ/WRITE | SPKR DATA    | Speaker Data            |  |

| 0    | READ/WRITE | T2GATE SPK   | Timer 2 Gate Speaker    |  |

The master enable for NMI (non-maskable interrupt) is programmed through bit 7 of system I/O port 70h inside the e88C311. If this bit is set to 1, NMI generation is disabled and if set to 0, it is enabled.

After bit 7 of system I/O port 70h is set to 0 and the corresponding NMIs are enabled in Port B, a non-maskable interrupt is generated to the CPU and the source of the NMI is latched in Port B. Bits <7:6> indicate a memory parity error (PCK) or an IO Channel Check error (IOCHCK). The e88C311 also generates NMI due to a cache access error if the tag field and valid field of the two tag directories both match the incoming addresses.

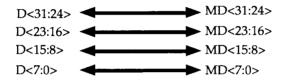

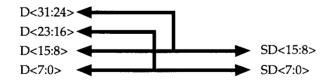

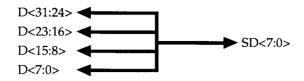

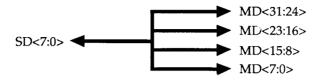

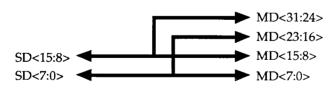

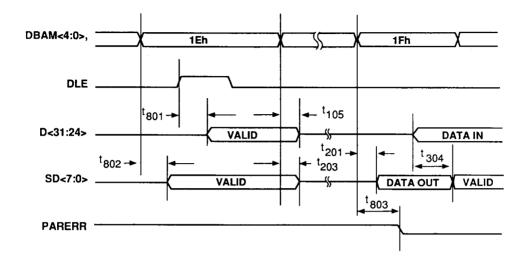

#### 1.4 Action Mode Codes Generation

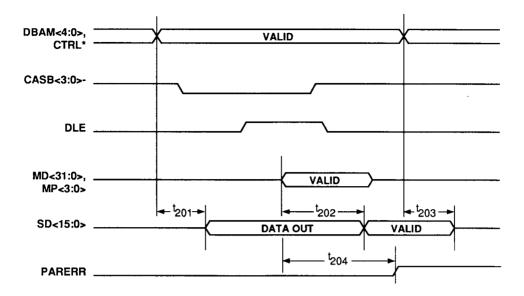

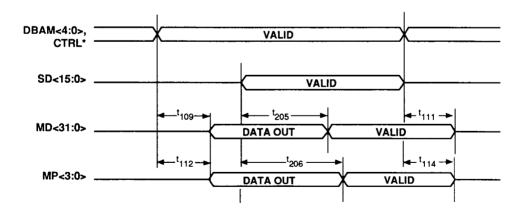

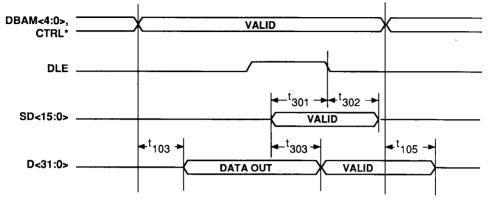

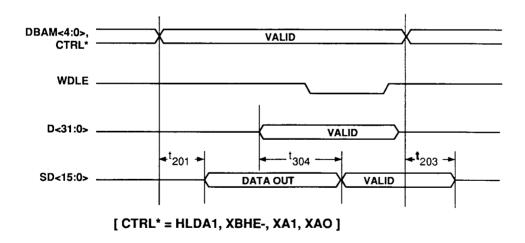

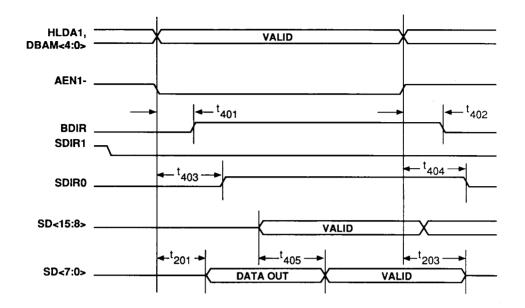

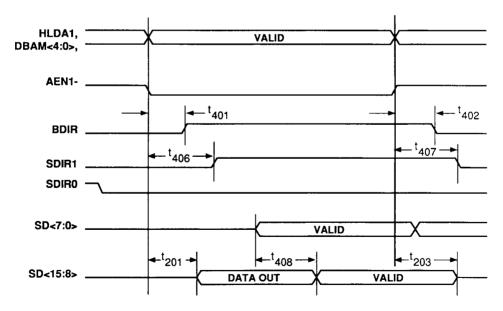

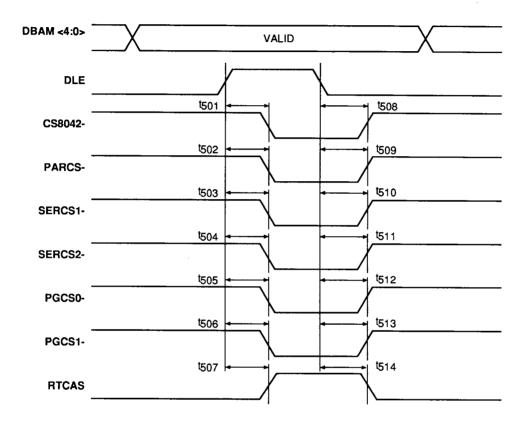

This logic performs Data Buffer Action Mode (DBAM) codes generation for CPU accesses to devices on the CPU(D) bus, system (SD) bus, or memory(MD) bus. The AT bus conversions are performed for 16-, and 8-bit read or write operations. 32-bit transfers to and from the CPU are broken into several 16- or 8- bit AT bus cycles. The e88C311 generates five bits of Data Buffer Action Mode codes (DBAM<4:0>) to the e88C312. These bits control the buffers in the e88C312 for byte alignment, direction control and data conversion between the D, MD and SD data buses. Refer to the e88C312 technical specification for detailed definitions regarding Action Mode codes. DBAM codes are also used by e88C312 to decode Chip Select (CS-) signals for on-board I/O ports.

# 1.5 CPU State Machine, Local Memory State Machines, Cache State Machine, AT Bus State Machine

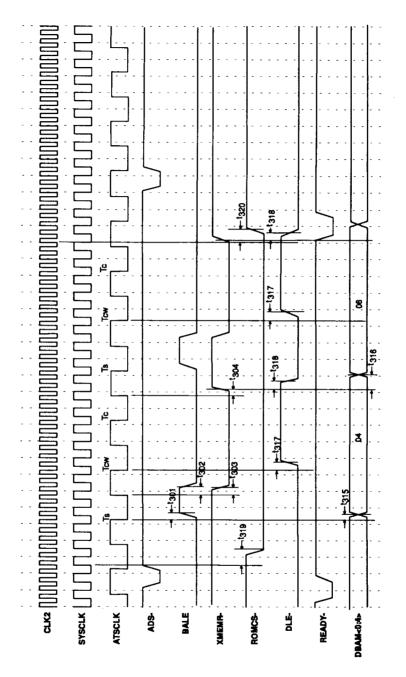

In the original IBM AT architecture, the CPU and AT bus run at the same speed. In order to maintain AT compatibility and to achieve the highest system performance; the CPU, the local DRAM and cache memory are driven by CLK2 while the AT bus is driven by ATCLK2. This allows the CPU and memories to operate at much higher frequencies, whereas the AT bus runs at an AT compatible 8 MHz speed. For synchronization, the e88C311 contains several state machines to control all the accesses initiated by the CPU, DMA/AT Bus Master or Refresh Request Timer.

The CPU state machine, DRAM and Cache state machines control all the accesses to the local bus (DRAM, Cache SRAM or coprocessor cycles). These state machines support only 32-bit data transfers between the CPU and the system memory; therefore no bus conversions are required.

The AT bus state machine is responsible for all non-local bus accesses and controls the AT bus for proper bus conversions.

#### 1.5.1 CPU State Machine

In e88C311, the CPU state machine provides the interface to the 80386 processor. The CPU state machine monitors and decodes the bus status lines, ADS-, W/R-, M/IO-, D/C- and establishes the type of bus cycle to be performed. The CPU state machine begins its cycle upon assertion of ADS-and terminates the cycle upon generation of READY- at completion of the access

For each new CPU cycle, the CPU state machine generates an internal signal CYCSTART (cycle start). It is sent to other state machines to indicate the beginning of a CPU cycle. For a non-pipelined cycle, CYCSTART is generated after ADS- is asserted. In contrast, for a pipelined cycle, CYCSTART is generated when both ADS- and READY- of the previous CPU cycle are detected.

Another internal signal LMEM32- is generated by the memory controller module to distinguish a local memory access (DRAM or SRAM) from a non-local memory access. After generation of CYCSTART, the CPU state machine samples the LMEM32- signal. If LMEM32- is active, it is a local memory cycle and control passes to the local DRAM and Cache state machines. DRAM or cache state machine generates the READY- to terminate the CPU cycle. However, if LMEM32- is inactive, the control is passed to the AT state machine. The CPU state machine then waits for the generation of the READY- signal from the AT state machine to terminate the cycle.

## 1.5.2 Local Memory State Machines

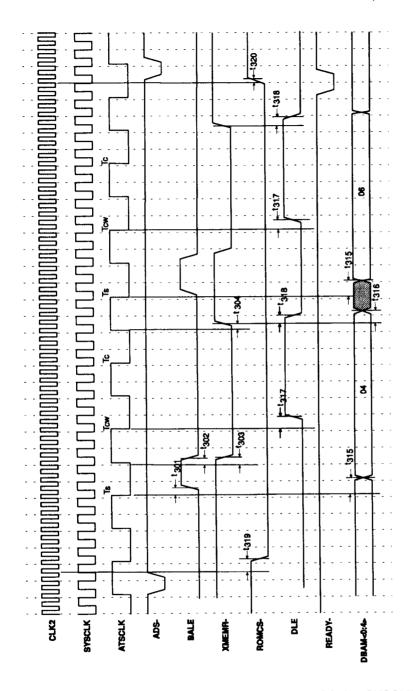

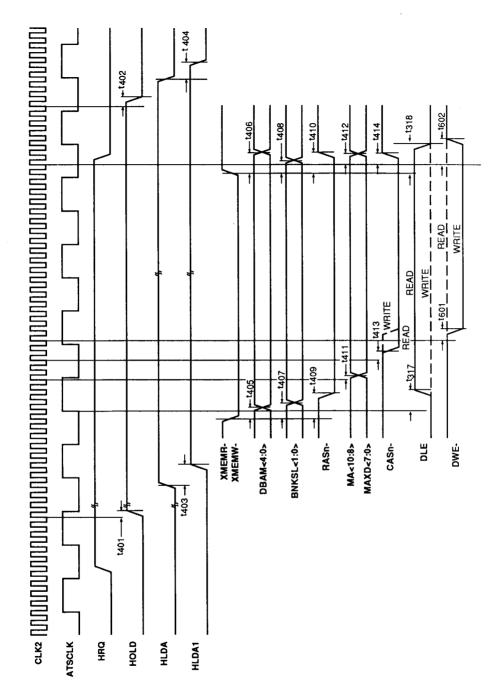

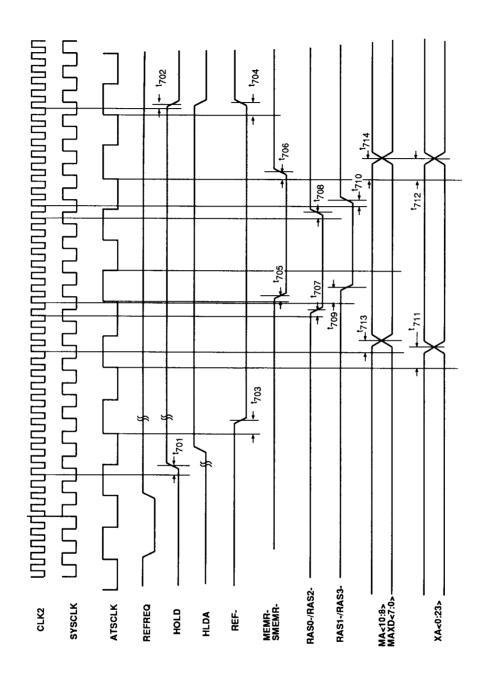

The DRAM array can be accessed by three different sources: CPU memory cycles, DMA/MASTER to local DRAMs, and refresh requests from the 82C206 timer output. These different accesses are controlled by three different state machines in the e88C311 DRAM module.

The e88C311 DRAM controller can support one, two, three, or four banks of local DRAMs. Each RAS- line drives one DRAM bank, and each CASB- line drives one byte of memory data. External demultiplexers (74F139s) combine CASB<3:0>- and BNKSL<1:0> lines to generate byte select signals for each memory bank. The DRAM row and column addresses are output on the MA<10:8>, MAXD<7:0> address pins.

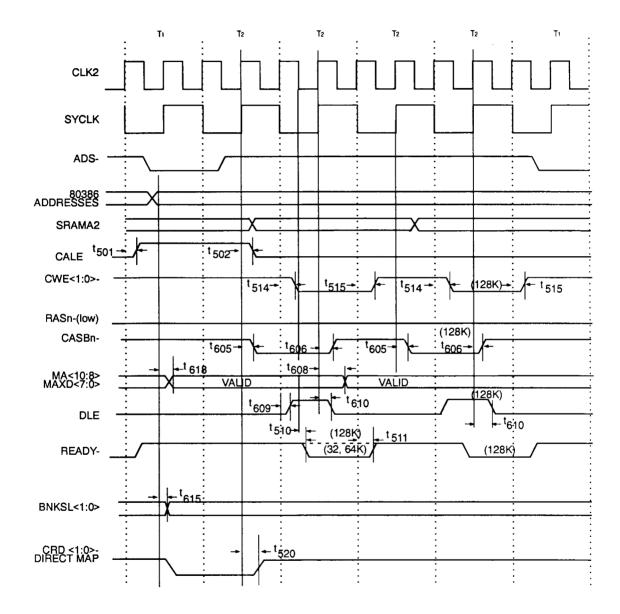

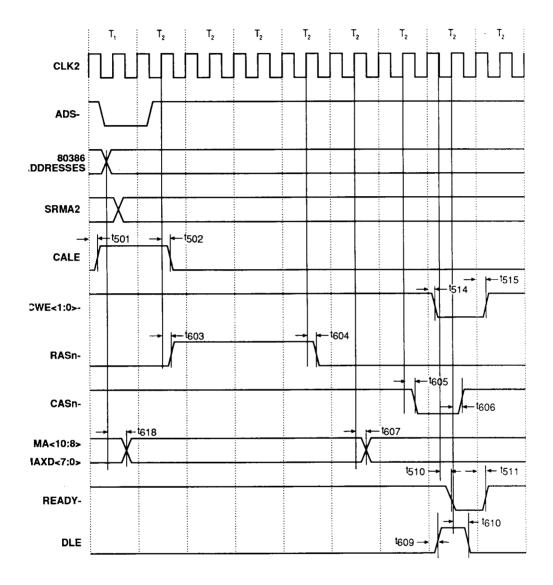

When a memory location is decoded to be within the local DRAM range (LMEM32- active) and a cache miss/or a write hit cycle is detected, the CPU and Cache state machines pass control to the local DRAM state machine. The local DRAM state machine generates RAS<3:0>-, CASB<3:0>-, BNKSL<1:0>, DWE-, and row/column address signals. The DRAM state machine also generates CWE<1:0>- to update the data cache during the cache read miss cycle. During a read miss, in the 128KB cache option, the local DRAM state machine initiates two DRAM accesses with inverted and non-inverted A2 address for each cycle respectively.

The e88C311 provides configuration registers to store memory system information for page/page interleave mode, DRAM wait states RAS- time-out period option, and shadow DRAM. For a "page hit" cycle, RAS- stays asserted after the previous accesses. For a "page miss" or RAS- time-out cycles, DRAM cycle starts by first de-asserting the RAS- corresponding to the accessed bank. The local DRAM state machine also inserts programmed wait states into the DRAM cycle.

Local DRAMs can also be accessed by a DMA controller or an AT bus master. DMA/MASTER local DRAM access is initiated by asserting HLDA1. The XMEMR- and XMEMW- determine if it is a read or write memory access per DMA/Master bus cycle.

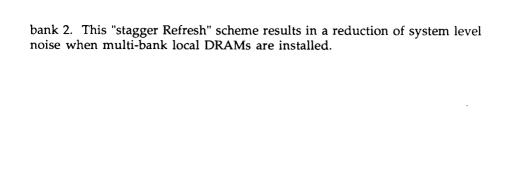

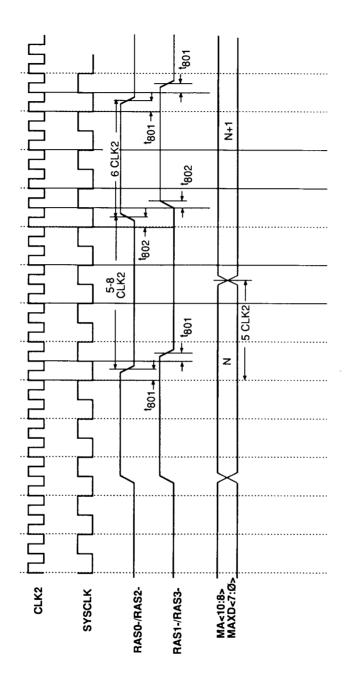

Local memory refreshes are controlled by a separate refresh state machine. During a refresh cycle, all four RAS- lines are asserted low for the DRAMs to be refreshed. RAS0- and RAS2- are activated first; followed by RAS1- and RAS3- with a CLK2 cycle delay. This staggering of RAS- signals reduces the system noise.

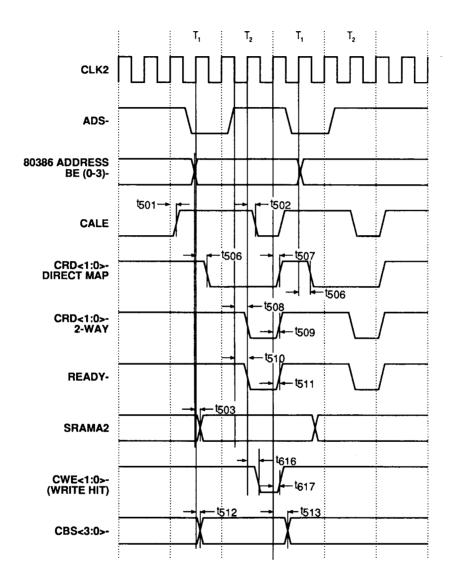

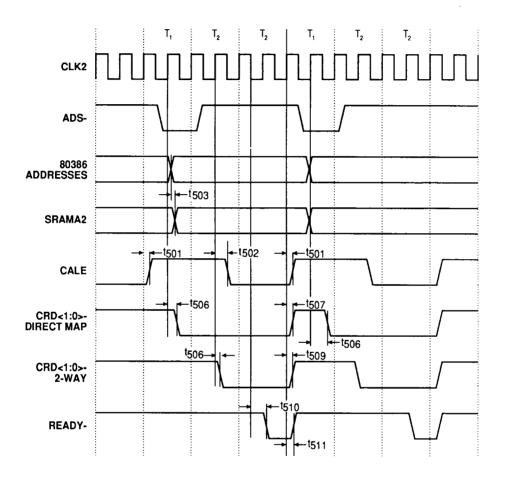

#### 1.5.3 Cache State Machine

The main function of the cache state machine in the e88C311 is to manage the internal tag directories and external cache memory through various CPU and DMA/Bus Master cycles. Apart from the difference between I/O, Halt, Shutdown, Interrupt Acknowledge cycles and memory read/write cycles, the e88C311 can be programmed to run in pipelined or non-pipelined mode. With the non-pipelined mode, it is also possible to run with zero or one wait state. For data coherency between the data SRAM and main memory, the cache state machine has to monitor the system bus used by the DMA controller or AT Bus Master. During a DMA/MASTER write hit cycle, when the other master overwrites DRAM contents of which the SRAM also has a copy, the cache state machine has to invalidate the data in the cache memory.

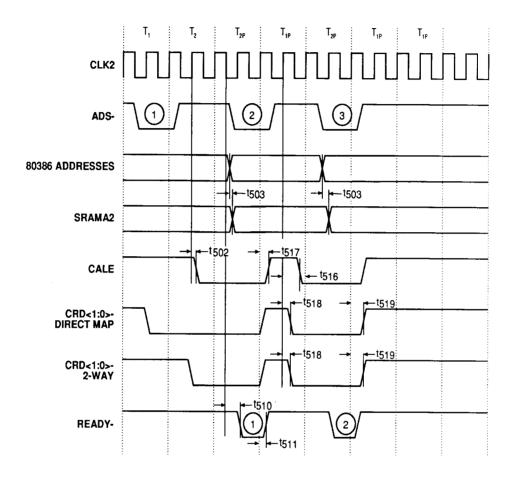

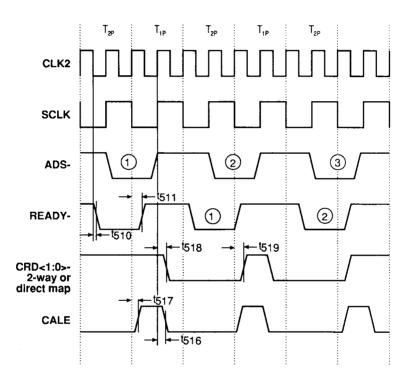

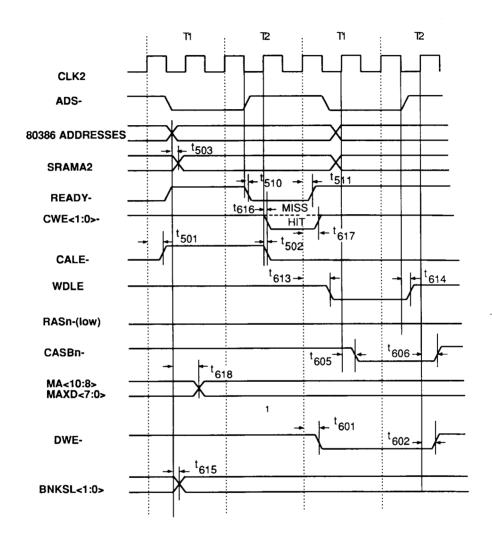

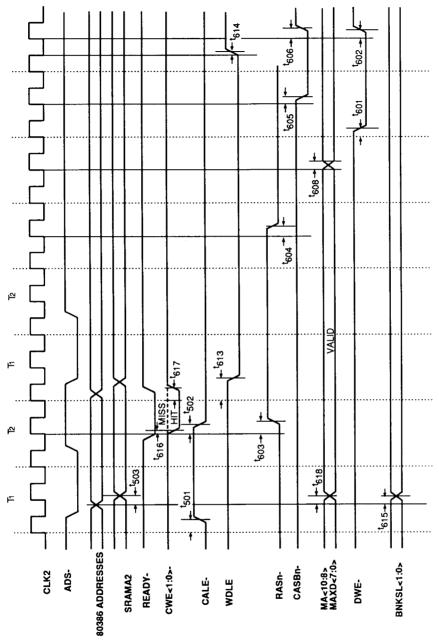

In the non-pipeline, zero wait states mode, and without any DMA/MASTER cycles running concurrently, a CPU cacne read hit cycle completes the access in two T states. The cache state machine generates the READY- signal back to CPU a quarter way into the second T state to terminate the cycle. For direct mapped cache, one of the CRD- signals is activated from the middle of T1 until the end of T2. In the two way set associate mode, the CRD- is not generated until a quarter way into T2.

For non-pipeline mode and one wait state, or pipeline mode, a CPU cache read hit cycle takes three T states to complete the access. The cache state machine generates a READY- signal to the CPU at the beginning of the third T state. In the pipeline mode, the ADS- for the next cycle overlaps with the READY- of the current cycle.

For CPU memory cycles that are not cache read hits, the cache state machine passes control over to the DRAM or the AT state machine. This occurs at the middle of the second T state after ADS- is active. One of the state machines generates the READY- signal to the CPU and terminate the cycle. For the DRAM state machine, the number of T states between ADS- and READY-depends on whether RAS- is active or inactive, page hit or miss, and the number of DRAM wait states programmed. Writing to cache SRAM is controlled by the cache state machine for cache write hit cycles. For read misses or cache line fill, the DRAM state machine controls the write operation to cache SRAM. In addition, during read miss cycles in the 128 KB cache mode, the DRAM state machine activates two sub-cycles to read in the DRAM contents and write back into the data cache.

DMA/MASTER write cycles, with or without Bus Snooping, require three T states to search through the cache directories and invalidate the tag entry if needed. The cache state machine will read the tag directories in the first T state, compare the contents with the DMA/MASTER address inputs in the second T state, and invalidate the tag entry for DMA/MASTER write hit access in the third T state. In the Bus Snooping mode, the access to the internal cache directories has to be shared between the CPU and DMA/MASTER. The cache state machine manages the tag accesses from the CPU cycle and DMA/MASTER write cycle simultaneously with negligible interference to CPU cache read hit cycles.

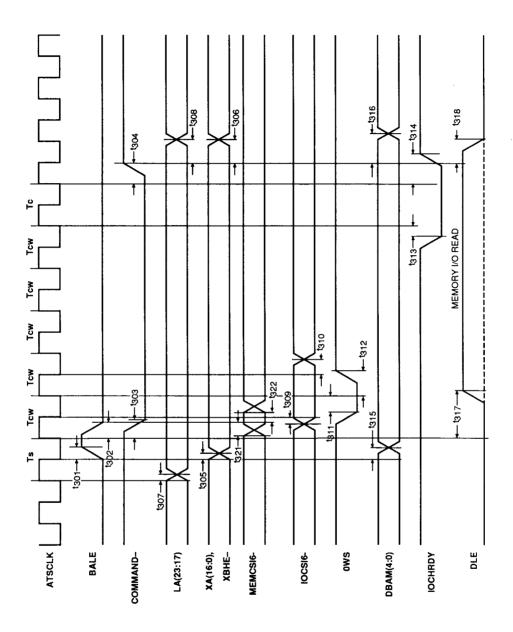

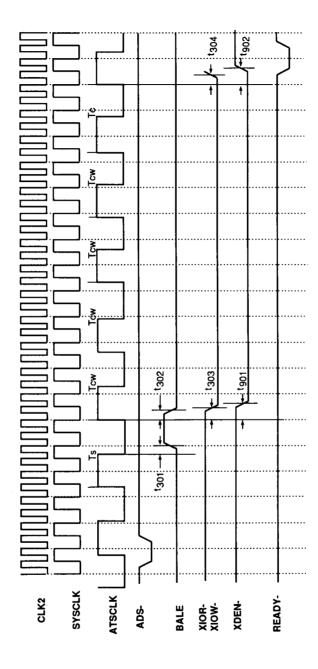

#### 1.5.4 AT Bus State Machine

The AT bus state machine is invoked when CYCSTART is generated and LMEM32- is inactive. The AT state machine is driven by ATCLK2, which runs twice the frequency of the AT bus clock (ATSCLK). The AT bus cycle is initiated by asserting the BALE signal decoded from the CPU status signals and is terminated by asserting READY-. The e88C311 supports 8-, 16-, or 32-bit transfers between the processor and 8- or 16- memory or I/O devices located on the AT bus. MCS16- and IOCS16- are sampled during the AT cycle to determine the bus size conversion and necessary byte alignment. For the AT memory cycle, MCS16- is sampled at the falling edge of BALE. For the AT I/O cycle, IOCS16- is sampled one-half of the ATSCLK after the falling edge of BALE to accommodate some slower I/O cards. If none of these 16-bit status signals are asserted, 8-bit transfers are assumed and the request is converted into 1, 2, 3, or 4 I/O channel cycles based on BE<3:0>-.

After BALE goes inactive, the AT state machine enters the command cycle. The command signals for the memory or I/O access remain active until the programmed number of wait states are executed. Bits <3:0> of register 11 control the I/O channel wait state generation for 8- and 16-bit accesses. Bits <5:4> provide the option to ensure enough recovery time for back to back I/O commands. The second I/O command is activated only after the programmed recovery time is satisfied.

After the programmed number of wait states are executed, IOCHRDY is sampled. If IOCHRDY is active (ready), the command becomes inactive after the next ATSCLK cycle. If IOCHRDY is not active (not ready), the commands are extended for an additional cycle (i.e., one ATSCLK) and IOCHRDY is sampled again. This process continues until IOCHRDY becomes active.

The AT bus cycle can also be terminated earlier by detecting an active 0WS-signal. This signal is sampled one ATSCLK after BALE becomes inactive.

#### 1.6 Bus Arbitration

The e88C311 provides bus arbitration between CPU, DMA, AT bus Master and AT style refresh logic (Burst and Hidden refresh cycles do not initiate a HOLD signal to the CPU). HRQ, a level triggered signal from the 82C206, is active when a DMA or a Master is requesting a bus cycle. REFREQ, an edge triggered signal from the 82C206, initiates a DRAM refresh request from refresh interval timer. The e88C311 arbitrates between HRQ and REFREQ by sending a hold request (HOLD) to the CPU in a non-preemptive manner. The CPU responds to hold request (HOLD) by issuing HLDA to e88C311 and relinquishes the CPU bus. The e88C311 then issues HLDA1 or REF- depending on which device prevailed during arbitration. With the Bus Snoop feature enabled, the e88C311 issues HLDA1 without sending a hold request (HOLD) to the CPU.

During a normal DMA cycle (with the Bus Snooping feature disabled), the DMA controller has control of the bus until HRQ becomes inactive. With the Bus Snoop feature enabled, the e88C311 issues HLDA1 without sending a hold request (HOLD) to the CPU. The CPU access can then run concurrently with DMA/MASTER cycles. During AT style refresh cycle, the refresh logic has control of the bus until REF- goes inactive and will generate separate control signals for local DRAM as well as AT bus memory. For local DRAM refresh, the internal refresh counters provide DRAM refresh addresses onto MA<10:8>, MAXD<7:0> bus and all RAS- lines are activated. For AT bus memory refresh, refresh addresses are latched into the SA<10:0> bus and XMEMR- is asserted. Refer to section 1.9.2 for other types of refresh operations.

PRELIMINARY

# 1.7 Coprocessor Support

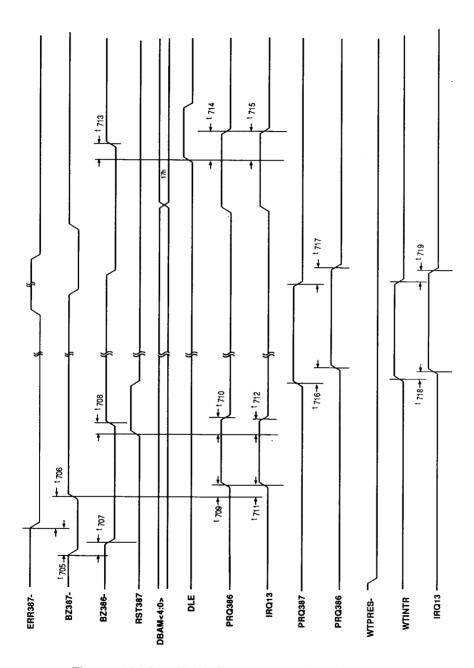

Both 80387 and Weitek processors are supported by the e88C311. After power up, bits 3,2 of configuration register 4D indicate the presence of the 80387 or Weitek WTL 3167 coprocessor respectively.

During 80387 operations, the CPU generates one or more I/O cycles to addresses 800000F8h through 800000FCh. The e88C311 executes a local (non-AT) cycle and no DRAM or AT commands will be activated. When present, the 80387 generates 387RDY- at the end of the coprocessor cycle. e88C311 samples 387RDY- signal and returns a ready signal READY- to the CPU. In the absence of 80387, the e88C311 will generate a ready signal READY- to terminate the cycle.

The Weitek coprocessor will respond to memory access of address C00000000h through C1FFFFFh. When the Weitek coprocessor is present, the coprocessor generates ready signal READY- to the CPU without any involvement from the e88C311. When the Weitek coprocessor is not present, the e88C311 generates READY- to the CPU and terminate the cycle.

#### 1.8 Cache Controller

The memory system in a PC/AT design is usually implemented with inexpensive, slow dynamic DRAMs. A cache memory is a small, high speed unit that resides between the CPU and the main memory. It increases the effective speed of the main memory by providing access to a copy of the most frequently used code or data from the main memory. When the CPU tries to read data from main memory, the high speed cache memory will respond first if the data resides in the cache memory (hit cycle). Otherwise (miss cycle), a normal main memory cycle will take place.

A cache system can further enhance system performance by time-sharing cache and DRAM cycles. During write cycles, the data is held in a temporary buffer inside the e88C312. Before the write cycle to main memory is completed, the CPU can access cache memory during a read hit cycle. However, if another read miss cycle or write cycle is performed, it has to wait until the previous write cycle is completed. While DRAMs are being refreshed in hidden refresh mode, the CPU can also access cache memory at the same time if it is a read hit cycle.

The e88C311 integrates the cache controller and the DRAM controller into a single chip. When a read cycle starts, cache access and DRAM access are performed in parallel. In the case of a cache hit, DRAM commands to main memory are terminated and cache memory provides the data to the CPU. In the case of a miss, a DRAM cycle will be completed. The integrated cache controller reduces the time penalty during a miss cycle because it does not have to wait for a HIT/MISS signal from the external cache tag RAM to start a DRAM operation.

To further enhance system performance, the e88C311 provides the user with a page-interleaved DRAM access option. A zero wait state (pipelined mode) or a one wait state (non-pipelined mode) DRAM access can be achieved during a page hit cycle, even if it is a cache read miss.

#### 1.8.1 Cache Performance

A cache reduces the average memory access time if it holds the most frequently requested code and data. The effectiveness of the cache is determined by the data cache size, line size, cache mapping scheme, cache replacement algorithm, and type of program execution.

The cache miss rate decreases with increasing data cache size. The gain is marginal, however, if the cache is 64KB or larger. The cache controller moves data from main memory to the cache during a miss cycle. A *block* is the basic unit of memory in that process. A typical block size (line size) is 4, 8, or 16 bytes. A large line size increases the hit rate if the CPU is accessing consecutive addresses or repeating a short loop. On the other hand, a large line size takes longer to transfer and increases the likelihood of unneeded data being placed in the cache.

In a direct mapped cache, each block can hold only one set of memory locations. The index field addresses are used to select one entry in the tag directory. The tag field addresses are compared with the contents of the tag directory to determine whether the access is a hit or a miss. Unlike the set associate cache, the direct mapped cache restricts the possible contents of the cache. More than one location with the same index cannot reside in the cache simultaneously. The result is a lower hit rate and increased data transfers from main memory to cache memory. However, it is easier to implement in hardware because only one comparator is required to determine whether the access is a hit or a miss.

In a set associative cache (2-way or 4-way), the index field addresses select multiple entries. In the case of a 2-way associative cache, there are two locations for each index field. This increases the likelihood of caching two accessed locations at the same time. Since two comparators are required to determine if the requested data resides in that cache, the process requires more hardware and extra time delay.

The Least Recently Used (LRU) algorithm is the most popular among setassociative cache designs. Upon miss access, the LRU algorithm selects for replacement, the item that has been least recently used by the CPU.

# 1.8.2 e88C311 Cache Organization

The e88C311 supports 32KB/64KB/128KB data cache options. It can also be programmed as a two way set associative or as a direct mapped cache. For a given cache size, the two way set associative scheme will result in a higher hit rate as compared to a direct mapped cache. The gain becomes marginal, however, as cache size increases. Since less time delay is needed to detect a hit/miss access with direct mapped cache, it is the most viable organization for 33MHz systems.

Table 1-2 illustrates two way associative set as well as direct mapped cache organization for the 32KB, 64KB and 128KB cache. It lists the physical address assignments of line select, set select, and tag field for all cache options supported by the e88C311.

Table 1-2 Direct Mapped & Two Way Set-Associative Cache

Organization

for 32KB, 64KB, and 128 KB Data Cache

|        | CACHE DATA SIZE                                                     | 32KB                       | 64KB                       | 128KB                      |

|--------|---------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|

| 2 WAY  | Line Size (Byte per Line) Set Size (Line per Set) Set # Line Select | 4<br>8<br>512              | 4<br>16<br>512             | 8<br>16<br>512             |

|        | Set Select Tag Field                                                | A2-A4<br>A5-A13<br>A14-A25 | A2–A5<br>A6–A14<br>A15–A25 | A3–A6<br>A7–A15<br>A16–A25 |

| DIRECT | Line Size (Byte per Line)<br>Size (Line per Set)<br>Set #           | 4<br>8<br>1024             | 4<br>16<br>1024            | 8<br>16<br>1024            |

| MAPPED | Line Select<br>Set Select<br>Tag Field                              | A2-A4<br>A5-A14<br>A15-A25 | A2–A5<br>A6–A15<br>A16–A25 | A3-A6<br>A7-A16<br>A17-A25 |

## 1.8.3 General Operations

In this section the following operations are illustrated in detail:

Read hit cycle Read miss cycle Write cycle DMA/Master cycle Bus snooping 128KB cache cycle

## 1.8.3.1 Read Hit Cycle

When the CPU starts a read cycle, the block (index) field of physical addresses selects a line from the cache directory. The tag bits and the valid bit stored in that location are compared with the CPU address inputs. A hit cycle is indicated when the tag field matches and the corresponding valid bit for the decoded sub-line is set. The e88C311 generates CRD<1:0>- to transfer data from cache memory to the CPU. A *ready* signal (READY-) is sent to the CPU to terminate the cycle.

After power up, the tag directory is automatically flushed within 2048 CLK2 cycles. (During this time, the e88C311 forces all local memory accesses to be DRAM cycles.) All valid bits in the cache directory should be invalidated. The hit rate starts with zero and the cache data RAM is empty. As the program is executed, the cache directory is filled and the hit rate increased. This mechanism avoids a cache error condition that occurs when the current address matches the tag field of both sets and both sets are valid. The tag directory can also be flushed via the software program by writing to index register 12 with bit 1 set to 1. If, due to an erroneous write operation to the tag RAM, a cache error occurs, the e88C311 allows the user to set up an interrupt through index register 64h. The tag RAM address that causes the cache error can be accessed through index register 64h and 65h.

## 1.8.3.2 Read Miss Cycle

In a read miss cycle, the DRAM memory provides the data to the CPU and write the same data to cache memory. The next time the same address is accessed, it will result in a hit cycle. In direct mapped cache, the cache controller will update the tag entry and corresponding cache memory data. In a two-way set associative cache, the set that has not been used recently (and therefore the least likely to be accessed) will be replaced.

## 1.8.3.3 Write Cycle

In a cache miss access during a write cycle, no cache write and tag updates are performed. The CPU writes the data to the DRAM array without any interaction with cache memory.

In the case of a hit access during a write cycle, CPU data should be written to cache memory as well as to the DRAM array. This will ensure that cache memory maintains the same copy of data or code as the main memory so that no "stale data" problem occurs. Since a SRAM write is much faster than a DRAM write, additional wait states will be needed before the CPU data is copied into DRAM. In order to enhance system performance, the e88C311 incorporates a "post write" scheme. During the write operation (hit or miss), the e88C311 will return a ready signal (READY-) to the CPU and a write data latch enable (WDLE) signal to e88C312. The data is latched into a write buffer inside the e88C312 during the write operation, while the CPU is released to begin another cycle before the current write cycle is completed.

If the next cycle does not require DRAM accesses (cache hit, AT, I/O cycles), the write cycle is running an equivalent of a zero wait state to the CPU. However, if the following cycle requires another DRAM access while the DRAM is busy with the first write cycle, additional wait states will be asserted until the DRAM has completed its previous cycle.

#### 1.8.3.4 DMA/MASTER Cycle

In an AT system, bus masters other than the CPU can access the main memory and alter its contents. When a cache hit access occurs within a master write cycle, data coherence between DRAM and cache memory must be maintained. The e88C311 will invalidate the cache for that tag location. Subsequent CPU memory access to the same memory location will be a cache miss until the cache is re-filled with new data. For local memory read cycles initiated by another master or DMA controller, only local DRAM accesses will be activated. For this reason, only local DRAM accesses are needed for DMA/MASTER write miss cycles.

#### 1.8.3.5 Bus Snooping

During DMA Master write cycles, the e88C311 monitors the system address bus (XA). If another master writes into the main memory, the cache controller latches the system addresses and compares them with the current tag directory contents. If they match up (snoop hit), the cache entry is invalidated in the cache directory. The snoop address look-up and invalidation of the tag directory is time multiplexed with 80386 CPU access. The result is that all snoops are monitored and serviced without slowing down the CPU. Even local address and data buses are running zero wait states.

If bit 4 of index register 12 is set to zero, the snoop feature is disabled. Every DMA Master cycle will put the CPU on hold when the tag directory is searched to determine whether a cache write hit access has occurred. Cache invalidation will take place if it is a cache hit.

## 1.8.3.6 128KB Cache Cycle

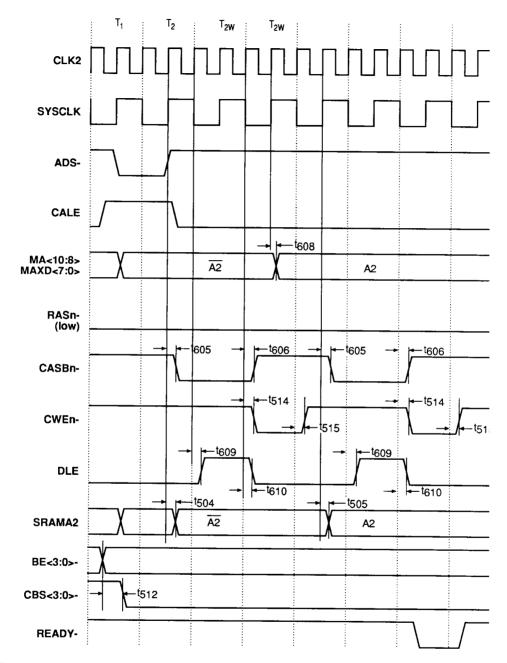

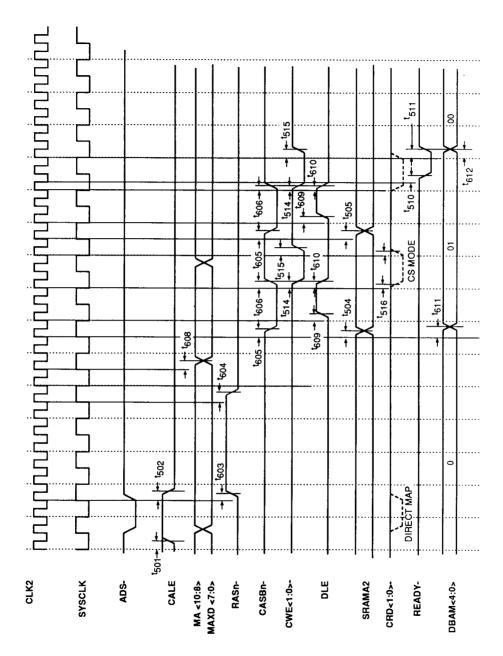

In the case of a 128KB cache option, there are 8 bytes for each subline and one valid bit is allocated to two double words. For read miss cycle, two double words must be moved into the cache memory before the corresponding valid bit is set. Two DRAM accesses have to be completed before the current cycle can be terminated. With a two double word move-in scheme, the e88C311 can support a 128KB data cache with the same block size that supports a 64KB data caches RAM (Table 1).

During the first data move-in and DRAM access, SRAMA2 drives inverted A2 address to data caches RAM and A2 is inverted to drive the DRAM address output. During the second data move-in and DRAM access, SRAMA2 returns to non-inverted A2 state and that same A2 drives the DRAM address output. At the end of the second DRAM access (non-inverted A2 access), the requested data is available on the CPU data bus and the ready signal, READY- is generated to terminate the cycle.

#### 1.8.4 Other Issues in Cache System Design

#### 1.8.4.1 Non-Cacheable Regions

The e88C311 provides four non-cacheable regions to allow the user to set aside four blocks (size ranges from 4KB to 4MB) of address space as non-cacheable. The starting address of any non-cacheable region has to be on a boundary of that region's size. These regions can then be used as ROM area, memory-mapped I/O space, shared memory accessed by multiple masters, or any other memory areas that should not be cacheable. Once the region is defined as non-cacheable, the memory operation can be re-directed to either local DRAM access or AT memory access via the DSDRAM<3:0> bits in index register 50h to 59h. Non-cacheable features are defined through index registers 50h to 5Bh.

Non-cacheable regions can also be hardware programmed by decoding the corresponding address to control the NCACHE- input to the e88C311. All memory accesses within the address range will be local DRAM cycles. However, there is a minimum set-up time requirement so that the e88C311 will recognize this input for the current cycle to be non-cacheable.

## 1.8.4.2 Direct SRAM and Tag RAM access

For diagnostic purposes, the contents of data cache and TAG RAM can be directly accessed by the CPU. Direct SRAM access is defined in index register 60h. If this feature is enabled, then the cache data RAM will be treated as an extension of main memory with 32KB / 64 KB / 128Kb block size at starting address 040000h. The on-chip tag RAM directory can also be accessed through the 8-bit I/O peripheral data bus (XD). The I/O write cycle loads the desired values into the directory. These features make system debugging and initialization easier, i.e., line invalidation, tag RAM, or data caches RAM purge.

#### 1.8.4.3 Cache Freeze

The e88C311 provides a feature to allow the user to freeze data cache contents. If a cache freeze is enabled through index register 60h, a read miss cycle cannot change the contents of data cache RAM nor can it update the tag directory. However, a cache write hit will write data into cache RAM. A DMA/Master cache write hit access will invalidate the corresponding tag RAM entry.

# 1.9 Page/Interleaved DRAM Controller

## 1.9.1 Page/Interleaved DRAM Operation

The e88C311 supports page mode (default) or page interleaved mode DRAM access providing higher performance over conventional DRAM access schemes. The access mode is programmed through bit-3 of index register 40h.

For normal DRAM access, both RAS- and CAS- have to be activated. The memory access time is determined by the Row Address Access time (Trac) rather than the much faster Column Address Access time (Tcac). Page mode DRAMs allow a number of locations within an area of memory (page) to be accessed without repeating the entire address. After providing the row address and asserting RAS-, the column address can be changed a number of times to access a series of locations. Each time a new column address is strobed by CAS-, RAS- must be kept asserted throughout the process. The number of cycles that can be performed is limited by the maximum length of the RAS- active pulse width. The effectiveness of the page-mode DRAM subsystem is determined by the page size and the locality of the program being executed. The page size can be increased by using higher density DRAMs.

The e88C311 also supports both 2-way and 4-way interleaved modes for DRAM access. For interleaved operation, the RAS- lines for each interleaved bank can be held active until the RAS- timeout period for that bank is reached. Therefore, it is possible to make access between the two (or four) banks by interleaving the CAS- precharge time of one bank with the CAS- active time of the other bank(s). As shown in the table below, the effective page size is increased when RAS- lines for memory banks are active.

Table 1-3 Effective Page Size for Page/Interleaved Mode DRAM

| DRAM type            | One bank             | Two banks            | Four banks            |

|----------------------|----------------------|----------------------|-----------------------|

| 256Kb x N<br>1Mb x N | 2 KBytes<br>4 KBytes | 4 KBytes<br>8 KBytes | 8 KBytes<br>16 KBytes |

| 4Mb x N              | 8 KBytes             | 16 KBytes            | 32 KBytes             |

The address assignment for page, 2 Way, or 4-way interleaved modes for different memory types are shown in the following tables.

Table 1-4. Address Assignment for Page, 2-Way, 4-Way Interleaved Mode

| Page (non-interle | eaved) Mode Operation | l       |

|-------------------|-----------------------|---------|

|                   | Row                   | Column  |

| 256Kb DRAMs       | A<19:11>              | A<10:2> |

| 1Mb DRAMs         | A<21:12>              | A<11:2> |

| 4Mb DRAMs         | A<23:13>              | A<12:2> |

|             | 2-Way Interleave | d Mode Operation |                  |

|-------------|------------------|------------------|------------------|

|             | Row              | Column           | Even/Odd<br>Bank |

| 256Kb DRAMs | A<20:12>         | A<10:2>          | A11              |

| 1Mb DRAMs   | A<22:13>         | A<11:2>          | A12              |

| 4Mb DRAMs   | A<24:14>         | A<12:2>          | A13              |

| 4-Wa        | y Interleaved | d Mode Oper | ation     |          |

|-------------|---------------|-------------|-----------|----------|

|             | Row           | Column      | Hi/Lo     | Even/Odd |

|             |               |             | Bank Pair | Bank     |

| 256Kb DRAMs | A<21:13>      | A<10:2>     | A12       | A11      |

| 1Mb DRAMs   | A<23:14>      | A<11:2>     | A13       | A12      |

| 4Mb DRAMs   | A<25:15>      | A<12:2>     | A14       | A13      |

# 1.9.2 Refresh Logic

The e88C311 provides the following refresh schemes:

- AT style refresh

- Hidden Refresh

- Burst mode refresh

- Slow refresh option

## 1.9.2.1 AT Refresh

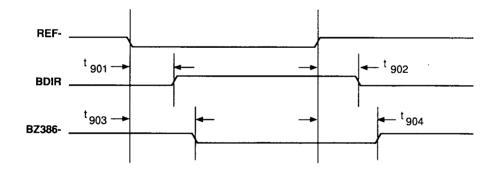

This is the default refresh mode. In an AT style refresh scheme, the e88C311 arbitrates the bus after receiving the REFREQ from the refresh interval timer and generates HOLD request to the CPU. The CPU relinquishes the bus by issuing the HLDA. The e88C311 in turn will respond with the REF and starts the AT refresh cycle. The local DRAM will be refreshed with RAS- active for all banks at the same time the AT bus is refreshed.

#### 1.9.2.2 Hidden Refresh

When the hidden refresh option is enabled, No HOLD signal will be generated to keep the CPU on hold and the refresh operation is transparent to the CPU access. The e88C311 monitors the AT bus as well as the local DRAM activities. If the AT bus is free while local DRAMs are busy, the AT bus refresh will be performed and the refresh of local DRAMs will be postponed. If cache option is enabled, the CPU will be able to operate cache memory independently. Assuming a cache read hit scenario, the refresh cycle can still proceed concurrently. The CPU will have to wait for its access to DRAM in other situations (e.g., cache read miss or write cycles). In the same way, DMA, and other AT bus accesses will be postponed until the current DRAM refresh cycle is completed.

#### 1.9.2.3 Burst Refresh

The burst refresh allows multiple local DRAM refresh cycles to run once the burst mode is activated. The e88C311 refresh logic allows up to 8 refresh requests to accumulate. It will begin to service these requests when the local DRAM is not being accessed. Depending on the option set in the burst mode configuration register 48h, the e88C311 is able to run multiple refresh cycles until the number of remaining refresh requests in the burst mode counter equals to 0. However, if the DRAM controller becomes active while the burst mode refresh is running, the refresh logic will relinquish control upon completion of the current burst refresh cycle. It will then wait to perform another burst mode refresh whenever the local DRAM becomes available. The burst mode refresh must be hidden as the CPU can not access the DRAM while the current refresh cycle is running. In addition, all AT memory refresh requests must be serviced every time a refresh is requested as it cannot run in a burst fashion.

#### 1.9.2.4 Slow Refresh

Slow refresh is an option provided for local DRAM refresh, not for an AT style refresh. Instead of generating refresh request at a rate of 256 per 4 ms, the Refresh control register (index 48H, bit 1 & 0) of the e88C311 can be set to allow slower refresh rate, e.g., 128 per 4 ms, 64 per 4 ms or 32 per 4 ms. The ability to run slow refresh option depends on the local DRAM used. This option is usually applicable when Low Power DRAMs are used for local memory.

The e88C311 refresh logic also provides a special mechanism to reduce system noise during simultaneous refreshing of each DRAM bank. RAS1- and RAS3- are delayed, after RAS0- and RAS2- are generated, to allow the refresh cycle for bank 1 and bank 3 to be performed immediately after refresh of bank 0 and

#### 1.9.3 Shadow RAM

It is preferable to execute codes through the faster local memory (DRAM or Cache RAM) than through the slower EPROMs. System performance can be enhanced by having the executable BIOS codes reside in local memory, rather than in EPROMs. This is especially true for applications with extensive BIOS calls. The e88C311 provides a SHADOW RAM feature that, when enabled, allows the BIOS codes stored in the EPROMs to be executed (shadowed) from the local RAM area. However, these BIOS codes need to be transferred from EPROMs into local RAMs prior to use the SHADOW RAM feature. In the e88C311 implementation, this transfer is accomplished at system initialization by means of the following procedure:

- Set register bits in configuration register 42h~45h for different memory access method

- 2) Copy ROM block to Shadow DRAM block

- 3) Set Corresponding bits in configuration 42~45 for blocks that are write protected.

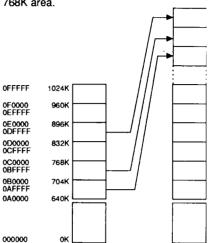

The e88C311 can shadow any DRAM block with an address from 0C0000H to 0FFFFFH (i.e., the C, D, E and F block) in 16KByte granularity. In another word, 256KBytes of total DRAM at 16KByte per chunk can be selectively activated for shadowing. With the cache option turned on, the shadow RAM region is then cacheable after the BIOS or other codes are copied into local DRAM. Special attention needs to be made to prevent any write operation onto the shadowed area. This is accomplished by setting write protection bits in procedure 3.

#### 1.9.4 Memory Remapping

The e88C311 memory remapping logic is able to remap physical memory locations between 640KB to 1MB (address 0A0000 to 0FFFFFH) in 64KByte chunks to the top of total system memory, provided that no portion of the 64KByte is shadowed. This feature is designed not to be limited by the amount of populated system DRAM. A 64KByte block is not remappable even if only one 16KByte chunk is shadowed.

Special consideration has been given to the remapping logic so that the e88C311 not only provides up to 384KBytes of remapping capability, but also assures all remapped memory to be contiguous on top of the total system memory.

The 384KByte reserved area at memory locations between 0A0000 and 0FFFFFH can be subdivided into A, B, C, D, E and F blocks, each with 64 KByte. The e88C311 supports the following remapping schemes:

- 1) A.B

- 2) A,B,D

- 3) A,B,D,E

- 4) A,B,D,E,C

- 5) A,B,D,E,C,F

While block A, B are remapped on top of the system memory, block "X" is remappable if no shadowed area exists within the block. Block "X" will be remapped by the e88C311 if and only if:

- i) It is remappable and

- ii) corresponding remap control bit in index register 46h is set to 1;

- iii) Other block(s) to the left of block "X" is also remapped, based on the series of combination stated above.

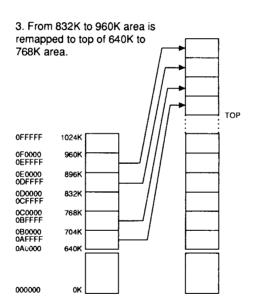

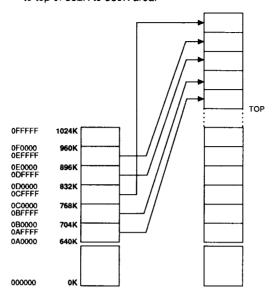

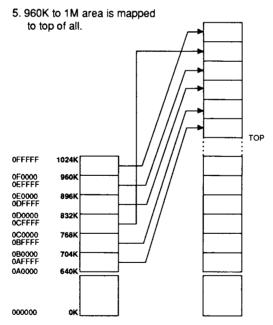

Refer to Remapping Scheme Figure on the next page for detailed remap implementation.

## 1.9.5 EPROM Control Logic

The e88C311 provides control logic to generate the ROMCS- signal for a EPROM access. The AT bus state machine generates the READY- for this cycle. ROMCS- is connected to the EPROM chip enable (CE-) input. Since the e88C311 supports both 8 and 16 bits of ROM, it needs to generate appropriate action codes DBAM<4:0> indicating 8 bits or 16 bits ROM access. DMAM<4:0> are passed on to its companion chip, the e88C312 to transfer ROM data to the CPU data bus.

- 1. The system always remaps 640K to 768K to top of physical memory.

- 0FFFFF 1024K 0F0000 960K 0EFFFF 0F0000 00FFFF 0D0000 832K 0CFFFF 0C0000 768K 0BF0FF 0B000 704K 0AFFFF 0A0000 640K

- 2. From 832K to 896K area is remapped to top of 640K to 768K area.

Figure 1-2. e88C311 Remapping Scheme

4. From 768K to 832K area is remapped to top of 832K to 960K area.

Figure 1-3. e88C311 Remapping Scheme (Continued)

## 1.9.6 OS/2 Optimization

The Eagle chip set provides two specific features that are further enhancements to the original IBM AT design:

.Fast Gate A20 (bit 6 of register 12h) .Fast Reset3 (bit 5 of register 12h)

The OS/2 operating system developed by IBM and Microsoft has two operating mode. The OS/2 mode operates on CPU protected address region while DOS mode operates on CPU real address region. In the OS/2 mode, the operating system can make many function calls in DOS mode. The CPU needs to switch from Protected Address Mode to Real Address mode before the DOS call could be executed. A CPU reset (RESET3) is one way to make the mode change without executing a cold reset (Power Down/On). The address A20 must be switched low before CPU changes to Real Address mode. This is necessary to assure downward compatibility with the 8086.

Both functions in the original PC/AT design were handled through the keyboard controller (8042). The interface between the CPU and the keyboard controller is very slow. To switch from Protected to Real mode, the CPU needs to set A20 low and reset the CPU. For each operation, the CPU checks the keyboard controller ready status and issues commands to the keyboard controller. The e88C311 provides both functions through much faster I/O operations.

In the e88C311 implementation, Fast Gate A20 is a read/write bit controlling internal address bit A20. This bit is set to 1 during system reset allowing CPUA20 from the 80386 to pass onto address A20. Writing a 0 into this bit will set Gate A20 to 0 (inactive) and forces the address A20 to be low.

The Fast Reset3 read/write bit (bit 5 of register 12h) is set to 0 during system reset (cold reset). To generate Fast Reset3 during normal operation, the CPU only needs to execute two I/O write cycles for this bit to make 0 to 1 transition. The RESET3 pin is pulled high after a 2µs delay or until a HALT state is detected, whichever is earlier.

# 1.9.7 Memory Subsystem Design Specification

The following table describes the SRAM, DRAM speed required for certain performance level as related to the 386DX clock frequency.

Eagle e88C311

| Table 1-5.  | 386DX/SRAM/D    | RAM Spee | d vs. W      | ait State | s*            |

|-------------|-----------------|----------|--------------|-----------|---------------|

| 386DX       | SRAM            | DR       | AM           |           | e Read<br>t** |

| Clock Freq. | Addr.<br>Access | trac     | <b>t</b> cac | NP        | P             |

| 20 MHz      | 45 ns           | 100ns    | ~25ns        | 0 w.s.    | 0 w.s.        |

| 25 MHz      | 35 ns           | 80 ns    | ~20 ns       | 0 w.s.    | 0 w.s.        |

| 33 MHz      | 25 ns           | 60 ns    | ~15 ns       | 0 w.s.    | 0 w.s.        |

<sup>\*</sup> Applicable to both direct map and Two Way set associative.

<sup>\*\*</sup> First write is always zero wait state.

# 2. CONFIGURATION REGISTERS

The Eagle chip set provides the most flexible and extensive features in the PC industry. All features can be set up by programming the corresponding registers provided inside the chip set. There are 60 registers provided in the Eagle chip set. They are classified into 6 groups: the local/AT bus operation control, the local DRAM access control, the local DRAM shadow/remap control, the non-cache/non-local memory blocks control, the cache memory control, and the EMS mapper support.

The local/AT bus operation control registers are indexed from 10H to 19H. The local DRAM access control registers are indexed from 30H to 37H. The local DRAM shadow/remap control registers are indexed from 40H to 4DH. The non-cache/non-local memory blocks control registers are indexed from 50H to 5BH. The cache memory control registers are indexed from 60H to 65H. The EMS mapper support registers are indexed from 70H to 75H and also include 4 non-indexed I/O ports. Only register 4DH is in e88C312. All other registers are in e88C311.

The following two sections describe the definitions of all the registers and include examples on how to program them.

# 2.1 How To Program the Configuration Registers

All registers except the 4 non-indexed I/O ports can be accessed by the CPU through the system I/O ports, 22H and 23H. To access a register, first write the index number of the register being programmed on the system I/O port 22H then write/read data through I/O port 23H to/from this register. The Eagle chip set also provides a special feature: lock or unlock the chip set registers. The registers need to be unlocked before any write operation and normally are locked after all write operations are completed. This, however, is not necessary for read operations. In order to avoid an I/O timing problem, a delay is needed between the consecutive I/O access unless bits 5 & 4 of register 11H are properly programmed. Here is an example of an assembler program which programs the register 11H with value 04H:

|     | MOV | AL,10H | ; LOCK/UNLOCK REGISTER INDEX         |

|-----|-----|--------|--------------------------------------|

|     | OUT | 22H,AL | ; LATCH REGISTER INDEX               |

|     | JMP | \$+2   | ; GIVE I/O DEVICE RECOVERY TIME      |

|     | JMP | \$+2   | ; GIVE MORE I/O DEVICE RECOVERY TIME |

|     | MOV | AL,0   | ; REGISTER BIT 0= 0                  |

|     | OUT | 23H,AL | ; UNLOCK REGISTERS                   |

|     | JMP | \$+2   | ; GIVE I/O DEVICE RECOVERY TIME      |

|     | JMP | \$+2   | ; GIVE MORE I/O DEVICE RECOVERY TIME |

| P0: | MOV | AL,11H | ; REGISTER INDEX 11H                 |

|     | OUT | 22H,AL | ; LATCH REGISTER INDEX               |

|     | JMP | \$+2   | ; GIVE I/O DEVICE RECOVERY TIME      |

|     | JMP | \$+2   | ; GIVE MORE I/O DEVICE RECOVERY TIME |

|     | MOV | AL,04H | ; VALUE TO BE WRITTEN TO REGISTER    |

|     | OUT | 23H,AL | ; WRITE TO REGISTERS                 |

|     | JMP | \$+2   | ; GIVE I/O DEVICE RECOVERY TIME      |

| P1: | JMP | \$+2   | ; GIVE MORE I/O DEVICE RECOVERY TIME |

|     | MOV | AL,10H | ; LOCK/UNLOCK REGISTER INDEX         |

|     | OUT | 22H,AL | ; LATCH REGISTER INDEX               |

|     | JMP | \$+2   | ; GIVE I/O DEVICE RECOVERY TIME      |

|     | JMP | \$+2   | ; GIVE MORE I/O DEVICE RECOVERY TIME |

|     | MOV | AL,1   | ; REGISTER BIT 0= 1                  |

|     | OUT | 23H,AL | ; LOCK REGISTERS                     |

|     |     |        |                                      |

An assembler program example which reads the value of register 11H back is provided as follows.

| P0: | MOV | AL,11H | ; REGISTER INDEX 11H                 |

|-----|-----|--------|--------------------------------------|

|     | OUT | 22H,AL | ; LATCH REGISTER INDEX               |

|     | JMP | \$+2   | ; GIVE I/O DEVICE RECOVERY TIME      |

|     | JMP | \$+2   | ; GIVE MORE I/O DEVICE RECOVERY TIME |

|     | IN  | AL,23H | ; READ DATA FROM PORT 23H            |

|     | JMP | \$+2   | ; GIVE I/O DEVICE RECOVERY TIME      |

| P1: | IMP | \$+2   | ; GIVE MORE I/O DEVICE RECOVERY TIME |

If more registers are to be read/written, the steps between P0 and P1 mentioned above should be repeated with an individual index number and value.

# 2.2 The Definition of Configuration Registers

There are some notation conventions in this section. A default value of a register is the value in the register after the system is powered on. An "X" in a default state means unknown value. An "\*" in front of a state value indicates the default value of the specific bits. The "R/W" item indicates "R" (read value), "W" (write value), or "R/W" (read/write value) for each individual bit.

This section includes a brief description of grouped registers and a detailed description of each register in that group.

# 2.2.1 Local/AT Bus Operation Control Registers

There are 10 registers in this group. The index registers 11H and 12H are used to select clocks and control the I/O operation while the registers from 13H through 19H are used to control the I/O ports. There are 2 programmable I/O, 2 serial I/O, and 1 parallel I/O chip selects in the Eagle chip set.

The following table briefly describes the function of the registers in this group:

| Index | Functions                                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10H   | To identify the chip set, and to lock or unlock registers.                                                                                                                                         |

| 11H   | To set the AT bus clock, the I/O recovery time, and the wait states.                                                                                                                               |

| 12H   | To set the CPU clock, the bus snooping, and the CPU pipelined request; to do the fast reset, the fast gate A20, and the cache controller Tag RAM flush; and to show the status of the coprocessor. |

| 13H          | To control the programmable I/O chip select #0.                |

|--------------|----------------------------------------------------------------|

| 14H          | To provide the programmable I/O #0 starting address high byte. |

| 15H          | To provide the programmable I/O #0 starting address low byte.  |

| 16H          | To control the programmable I/O chip select #1.                |

| 1 <b>7</b> H | To provide the programmable I/O #1 starting address high byte. |

| 18H          | To provide the programmable I/O #1 starting address low byte.  |

| 19H          | To enable or disable on board serial and parallel I/O ports.   |

| Index | Default     | Value  | Description                          |                                                                                                                                                                                                                                                                                         |  |

|-------|-------------|--------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10H   | [0011,0100] |        | num<br>regis<br>this<br>prog<br>prog | register provides the ID and revision ber of the Eagle chip set when read. This sters in the Eagle chip set. The bit 0 of register should be set to 0 before ramming the registers and set to 1 when ramming is done. This is to protect the sters from being overwritten accidentally. |  |

|       | Bits        | R/W    | State                                | Meaning                                                                                                                                                                                                                                                                                 |  |

|       | <7:0><br>0  | R<br>W | 0                                    | Chip set ID bits 7 - 0. All configuration registers are readable and writable (unlocked). All configuration registers except registers 10H, 41H and some specific bits of registers 12H, 49H, and 64H are read only (locked).                                                           |  |

| Index | Default     | Value  | Description                          |                                                                                                                                                                                                                                                                                         |  |

| 11H   | [1000,0110] |        |                                      | register is used to select the AT bus clock to set the I/O recovery time and wait s.                                                                                                                                                                                                    |  |

|       | Bits        | R/W    | State                                | Meaning                                                                                                                                                                                                                                                                                 |  |

|       | <7:6>       | R/W    | 00                                   | AT state machine clock frequency is the same as ATCLK1.                                                                                                                                                                                                                                 |  |

|       |             |        | 01                                   | AT state machine clock frequency is 1/3 of CPU clock frequency.                                                                                                                                                                                                                         |  |

|       |             |        | *10                                  | AT state machine clock frequency is 1/4 of CPU clock frequency.                                                                                                                                                                                                                         |  |

|       |             |        | 11                                   | AT state machine clock frequency is 1/5 of CPU clock frequency.                                                                                                                                                                                                                         |  |

The CPU clock frequency is 2 times the CPU speed while the AT state machine clock frequency is 2 times the AT bus speed. A 25 MHZ system with 8 MHZ AT bus means the system has a 50 MHZ CPU clock frequency and a 16 MHZ AT state machine clock frequency. To select the AT state machine clock frequency at 1/3 of the CPU clock frequency, the AT state machine clock frequency will be 16.6 MHZ for a 25 MHZ system while the AT state machine clock frequency is 22 MHZ for a 33 MHZ system.

|       | <5:4>    | R/W   | *00<br>01<br>10        | 1 AT bus clock for a back-to-back I/O cycle recovery time. The recovery time will be 125 ns if the AT bus cycle time is 125 ns (a 16 MHZ AT state machine clock frequency).  2 AT bus clocks for back-to-back I/O cycle recovery time.  3 AT bus clocks for back-to-back I/O cycle recovery time.  4 AT bus clocks for back-to-back I/O cycle recovery time.                                                                                   |

|-------|----------|-------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <3:2>    | R/W   | 00<br>*01<br>10        | 0 wait state for 16-bit AT bus operation.<br>1 wait state for 16-bit AT bus operation.<br>2 wait states for 16-bit AT bus                                                                                                                                                                                                                                                                                                                      |

|       |          |       | 11                     | operation.  3 wait states for 16-bit AT bus operation.                                                                                                                                                                                                                                                                                                                                                                                         |

|       | <1:0>    | R/W   | 00<br>01<br>,*10<br>11 | 2 wait states for 8-bit AT bus operation.<br>3 wait states for 8-bit AT bus operation.<br>4 wait states for 8-bit AT bus operation.<br>5 wait states for 8-bit AT bus operation.                                                                                                                                                                                                                                                               |

| Index | Default  | Value | Descr                  | ription                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12H   | [0110,XX |       |                        | register is used to select the CPU clock enable or disable the bus snooping and ined mode request. It also provides the rate A20, the fast reset, and the cache. The bits 6 & 5 of this register are ble even if this register is locked. The board controller (8042/8742) has the same ion as that of bits 5 and 6. However, CPU and activate gate A20 through 2 bits is faster than through using /8742. Bits 3 & 2 will be written once and |

can be read only afterwards. These 2 bits (3 & 2) should be obtained from bits 3 & 2 of register 4DH before any memory is accessed during system power-up.

|       | Bits        | R/W      | State | Meaning                                                                        |

|-------|-------------|----------|-------|--------------------------------------------------------------------------------|

|       | 7           | R/W      | *0    | CPU clock source is CLK2IN.                                                    |

|       |             |          | 1     | CPU clock source is ATCLK1.                                                    |

|       | 6           | R/W      | 0     | Address bit A20 is forced to 0 no                                              |

|       |             |          |       | matter what the value of the CPUA20.                                           |

|       |             |          | *1    | Address bit A20 is the same as CPU                                             |

|       |             |          |       | address bit CPUA20.                                                            |

|       | 5           | R/W      |       | A transition from 0 to 1 will activate                                         |

|       |             |          |       | RESET3 which resets the 80386 CPU.                                             |

|       | 4           | R/W      | *0    | The cache controller bus snooping is                                           |

|       |             |          |       | disabled. The CPU, DMA, and I/O                                                |

|       |             |          |       | channel bus master will share all of                                           |

|       |             |          |       | the bus through arbitration (hold                                              |

|       |             |          |       | request and hold acknowledge                                                   |

|       |             |          |       | protocol).                                                                     |

|       |             |          | 1     | The cache controller's bus snooping                                            |

|       |             |          |       | function is enabled. The CPU can use                                           |

|       |             |          |       | local bus while the DMA or bus master                                          |

|       | •           | 75       |       | is using the DRAM and AT buses.                                                |

|       | 3           | R        | 0     | INTEL 80387 is not installed.                                                  |

|       | •           | <b>D</b> | 1     | INTEL 80387 is installed.                                                      |

|       | 2           | R        | 0     | Weitek 3167 is not installed.                                                  |

|       | 1           | D / TAT  | 1     | Weitek 3167 is installed.                                                      |

|       | 1           | R/W      | *0    | Cache controller's Tag RAM is kept                                             |

|       |             |          |       | the same or a flush operation has been                                         |

|       |             |          | 1     | done.                                                                          |

|       |             |          | 1     | All cache controller's Tag RAM is                                              |

|       |             |          |       | invalidated. It takes 2048 CLK2 cycles                                         |

|       |             |          |       | to flush the Tag RAM to zero. During the flush process, cache access is always |

|       |             |          |       | a miss.                                                                        |

|       | 0           | R/W      | 0     | 80386 runs pipelined mode if possible.                                         |

|       | U           | 10, 11   | *1    | 80386 always runs non-pipeline mode.                                           |

|       |             |          | •     | obood arways rans non pipeline mode.                                           |

| Index | Default     | Value    | Desc  | ription                                                                        |

| 13H   | [0XXX,X     | XXX]     | This  | register controls the attribute and mask                                       |

|       | •           |          |       | of PIO chip select #0.                                                         |

| 16H   | [0XXX,XXXX] |          |       | register controls the attribute and mask                                       |

|       | ,           |          |       | of PIO chip select #1.                                                         |

|       |             |          |       | _                                                                              |

|       | Bits    | R/W    | State | Meaning                                                                       |

|-------|---------|--------|-------|-------------------------------------------------------------------------------|

|       | 7       | R/W    | *0    | Programmable I/O (PIO) ports are not used.                                    |

|       |         |        | 1     | PIO ports are used.                                                           |

|       | <6:5>   | R/W    | 00    | Reserved.                                                                     |

|       |         | ·      | 01    | Use these PIO ports only if I/O                                               |

|       |         |        |       | operation is to write to the location                                         |

|       |         |        |       | specified as in the bits 3-0 of this                                          |

|       |         |        |       | register and PIO ports starting address.                                      |

|       |         |        | 10    | Use these PIO ports only if I/O                                               |

|       |         |        |       | operation is read from the location                                           |

|       |         |        |       | specified as in the bits 3-0 of this register and PIO ports starting address. |

|       |         |        | 11    | Use these PIO ports if I/O operation is                                       |

|       |         |        | **    | write/read to/from the location                                               |

|       |         |        |       | specified as in the bits 3-0 of this                                          |

|       |         |        |       | register and PIO starting address.                                            |

|       | 4       |        |       | Reserved.                                                                     |

|       | 3       | R/W    | 0     | The bit 3 of PIO ports address low byte                                       |

|       |         |        | 1     | is part of I/O ports address.                                                 |

|       |         |        | 1     | The bit 3 of PIO ports address low byte is not part of I/O ports address.     |

|       | 2       | R/W    | 0     | The bit 2 of PIO ports address low byte                                       |

|       | _       | ,      | · ·   | is part of I/O ports address.                                                 |

|       |         |        | 1     | The bit 2 of PIO ports address low byte                                       |

|       |         |        |       | is not part of I/O ports address.                                             |

|       | 1       | R/W    | 0     | The bit 1 of PIO ports address low byte                                       |

|       |         |        | -1    | is part of I/O ports address.                                                 |

|       |         |        | 1     | The bit 1 of PIO ports address low byte                                       |

|       | 0       | R/W    | 0     | is not part of I/O ports address. The bit 0 of PIO ports address low byte     |

|       | Ü       | 10, 11 | v     | is part of I/O ports address.                                                 |

|       |         |        | 1     | The bit 0 of PIO ports address low byte                                       |

|       |         |        |       | is part of I/O ports address.                                                 |

| Index | Default | Value  | Desc  | ription                                                                       |

| 14H   | [XXXX,  | XXXX]  | This  | register provides the I/O ports address                                       |

|       | ·       |        |       | byte for PIO chip select #0 if the bit 7 of                                   |

|       |         |        |       | ter 13H is 1.                                                                 |

| 17H   | [XXXX,  | XXXX]  |       | register provides the I/O ports address                                       |

|       |         |        |       | byte for PIO chip select #1 if the bit 7 of                                   |

|       |         |        | regis | ter 16H is 1.                                                                 |

| Bits  | R/W | State | Meaning                                    |

|-------|-----|-------|--------------------------------------------|

| <7:0> | R/W |       | PIO chip select ports address bits 15 - 8. |

Note:

If PIO chip select ports address is above 3FFH, the lower 10 address bits 9 - 0 must not be the same as any IBM standard I/O ports address below 400H. This applies to both PIO chip selects.