## P R E L I M I N A R Y

May 1991

Data Sheet

#### **Copyright Notice**

Copyright © 1990, 1991, Chips and Technologies, Inc. ALL RIGHTS RESERVED.

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of Chips and Technologies, Inc.

#### **Restricted Rights Legend**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

#### **Trademark Acknowledgement**

CHIPS and NEAT are registered trademarks of Chips and Technologies, Inc.

CHIPS, CHIPSet, MICROCHIPS, SCAT, NEATsx, LeAPSet, LeAPSetsx, PEAK, CHIPS/230, CHIPS/250, CHIPS/280, CHIPS/450, CHIPSPak, CHIPSPort, CHIPSlink, and SMARTMAP are trademarks of Chips and Technologies, Incorporated.

IBM AT, XT, PS/2, Micro Channel, Personal System/2, Enhanced Graphics Adapter, Color Graphics Adapter, Video Graphics Adapter, IBM Color Display, and IBM Monochrome Display are trademarks of International Business Machines.

Hercules is a trademark of Hercules Computer Technology.

MS-DOS is a trademark of Microsoft, Incorporated.

MultiSync is a trademark of Nippon Electric Company (NEC).

Brooktree and RAMDAC are trademarks of Brooktree Corporation.

Inmos is a trademark of Inmos Corporation.

#### Disclaimer

This document is provided for the general information of the customer. Chips and Technologies, Inc., reserves the right to modify the information contained herein as necessary and the customer should ensure that it has the most recent revision of the data sheet. CHIPS makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that the field of personal computers is the subject of many patents held by different parties. Customers should ensure that they take appropriate action so that their use of the products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

Chips and Technologies, Inc. 3050 Zanker Road San Jose, California 95134 Phone: 408-434-0600 Telex: 272929 CHIPS UR FAX: 408-434-6452

Publication No.: DS108 Stock No.: 010411-001 Revision No.: 0.8

## 82C411 Flat Panel Color Palette/DAC

- Full IBM VGA-compatibility

- Supports digital and analog CRT monitors and LCD, plasma, and electroluminescent flat panels

- Three RGB color to grayscale reduction techniques

- Direct connection to analog RGB color monitors

- Direct connection to Chips and Technologies Enhanced Flat Panel / CRT VGA Controllers

- Proven DOS and OS/2<sup>TM</sup> compatibility

- All CRT and Flat Panel palette functions are integrated into a single package

- 256 color support for color panels

- 64 gray levels for monochrome panels

- IBM VGA monochrome CRT compatibility on monochrome panels

- Power Down modes minimize power consumption

- No Sparkle during palette write operations

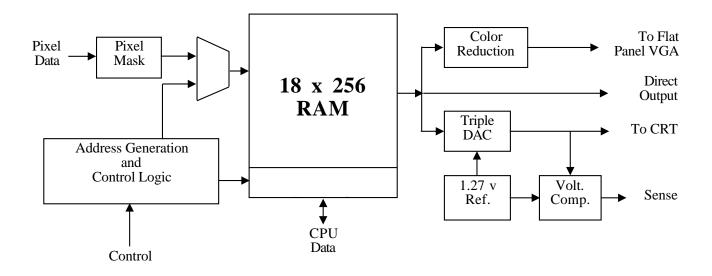

#### 82C411 BLOCK DIAGRAM

## **Revision History**

| <b>Revision</b> | Date     | By | Comment                                                  |

|-----------------|----------|----|----------------------------------------------------------|

| 0.0             | 3/151/90 | MR | Created document.                                        |

| 0.1             | 3/90     | MR | Minor update.                                            |

| 0.2             | 3/31/90  | MR | Update functionality.                                    |

| 0.3             | 3/31/90  | MR | Added electrical specs.                                  |

| 0.4             | 631/90   | MR | Update pinout, package spec, electrical specs.           |

| 0.5             | 7/14/90  | MR | Final update prior to Initial Release.                   |

| 0.6             | 7/25/90  | ST | Initial Release.                                         |

| 0.7             | 3/26/91  | SV | Included pin list and updated timing diagrams.           |

| 0.8             | 4/26/91  | SV | Update AC & DC specs and corrected various inaccuracies. |

## **Table of Contents**

| Section                                     | <u>Page</u> |

|---------------------------------------------|-------------|

| Introduction                                | 5           |

| Pinouts                                     | 7           |

| Pin Diagram<br>Pin List<br>Pin Descriptions | 8           |

| Register Description                        | 13          |

| Color Palette Control                       | 13          |

| Section                                                                                                                                                                                                                  | Page                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Electrical Specifications                                                                                                                                                                                                | 17                               |

| Absolute Maximum Conditions<br>Normal Operating Conditions<br>DC Characteristics<br>Thermal Characteristics<br>DAC Characteristics<br>AC Timing Characteristics - CPU Interface<br>AC Timing Characteristics - Pixel I/O | 17<br>17<br>18<br>18<br>19<br>20 |

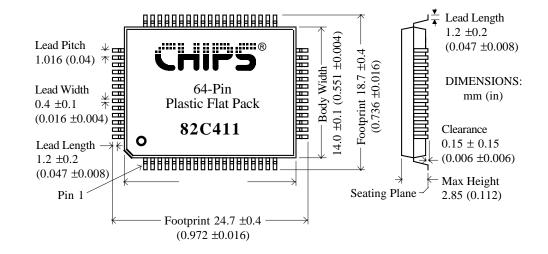

| Mechanical Specifications                                                                                                                                                                                                | 21                               |

| Plastic 64-PFP Package Dimensions                                                                                                                                                                                        | 21                               |

## List of Figures and Tables

| Figure                               | <u>Page</u> |

|--------------------------------------|-------------|

| Block Diagram                        | 1           |

| 82C411 Pinouts                       | 7           |

| CPU Interface Timing                 | 19          |

| Pixel I/O Timing                     | 20          |

| PFP-64 Package Mechanical Dimensions | 21          |

| Table                                                                                                                                                                                                        | <u>Page</u>                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Color Palette Control Register                                                                                                                                                                               | 13                         |

| Absolute Maximum Conditions.<br>Normal Operating Conditions.<br>DC Characteristics<br>Thermal Characteristics<br>DAC Characteristics<br>AC Characteristics - CPU Interface<br>AC Characteristics - Pixel I/O | 17<br>17<br>18<br>18<br>19 |

The 82C411 Flat Panel Palette supplies all of the functions of a VGA compatible RAMDAC, the 82C460 Flat Panel Color Palette, an LM339 voltage comparator and a current or voltage reference in a single CMOS package. In addition, features are provided to support power reduction as required in battery operated systems.

.....®

The 82C411 is designed to connect directly to Chips and Technologies Enhanced Flat Panel/CRT VGA Controllers and an analog CRT display. The 82C411 provides the analog output to drive a CRT as well as the color or grayscale data to the flat panel VGA controller. NTSC, equal weighting, and greengun-only are three reduction techniques supported on chip. In addition, the 82C411 can output all 18 bits of palette data directly. This may be used to drive digital CRTs or color panels. The flat panel controller uses the data to provide correct color or grayscale mapping on flat panel displays. The 82C411 and a flat panel VGA controller provide a two chip solution for a complete VGA Flat panel/CRT system.

The 82C411 provides two power saving features. Since the DAC outputs voltage reference and their support logic are required only when driving an analog CRT, they may be powered down when using the flat panel display. This portion of the chip is powered up only when the DACEN input is high.The second power down condition is the standby mode. When the PWRDN input is pulled high, all internal logic, references and outputs are turned off. Power is maintained only to the RAM core in order to retain the RAM data. No CPU accesses are allowed and the pixel clock may be stopped.

The 82C411 CPU and pixel interface are identical to that of an Inmos IMSG176 style RAMDAC. Since the DAC reference and LM339 voltage comparator are built into the 82C411, the system component count and complexity is greatly reduced.

As well as providing color or grayscale data for the flat panel controller, the 82C411 is designed to directly drive an analog CRT display. A single resistor is used to set the current level in the DACs. The 82C411 will directly drive a single or doubly terminated 75 ohm system. Only the termination resistor is required. No output series resistor is needed.

## CHICS\_

## 82C411 Pin List

| Pin Name | Pin # | Pin Name | Pin #  | Pin Name | Pin #    |

|----------|-------|----------|--------|----------|----------|

| AGND     | 47    | DGND     | 10     | P4       | 17       |

| AVCC     | 41    | DGND     | 2      | P5       | 18       |

| В        | 43    | DGND     | 58     | P6       | 19       |

| B0       | 59    | DGND     | 57     | P7       | 20       |

| B1       | 60    | DVCC     | 36     | PALRD/   | 22       |

| B2       | 61    | DVCC     | 27     | PALWR/   | 22<br>34 |

| B3       | 63    | DVCC     | 6      | PCLK     | 21       |

| B4       | 64    | DVCC     | 62     | PWRDN    | 44       |

| B5       | 1     | DVCC     | 53     | R        | 40       |

| BLANK/   | 23    | G        | 42     | R0       | 50       |

| D0       | 24    | G0       | 3      | R1       | 51       |

| D1       | 25    | G1       | 4<br>5 | R2       | 52       |

| D2       | 28    | G2       | 5      | R3       | 54       |

| D3       | 29    | G3       | 7      | R4       | 55       |

| D4       | 30    | G4       | 8      | R5       | 56       |

| D5       | 31    | G5       | 9      | RS0      | 37       |

| D6       | 32    | IREF     | 49     | RS1      | 38       |

| D7       | 33    | PO       | 13     | SEL0     | 11       |

| DACEN    | 46    | P1       | 14     | SEL1     | 12       |

| DGND     | 48    | P2       | 15     | SENSE    | 39       |

| DGND     | 35    | P3       | 16     | VREF     | 45       |

| DGND     | 26    |          |        |          |          |

### 82C411 PIN DESCRIPTIONS

| Pin #                                        | Pin Name                                     | Туре                                   | Active                                               | Description                                                                                                                                                                                                          |

|----------------------------------------------|----------------------------------------------|----------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21                                           | PCLK                                         | In                                     | Both                                                 | PIXEL CLOCK. The rising edge controls the sampling<br>of the values on the Pixel Address and Blank/ inputs. It<br>controls progress of these values through the Color<br>Palette pipeline to the outputs.            |

| 20<br>19<br>18<br>17<br>16<br>15<br>14<br>13 | P7<br>P6<br>P5<br>P4<br>P3<br>P2<br>P1<br>P0 | In<br>In<br>In<br>In<br>In<br>In<br>In | Both<br>Both<br>Both<br>Both<br>Both<br>Both<br>Both | PIXEL ADDRESS. The byte wide value on these<br>inputs is sampled and then masked by the Pixel Mask<br>register and then used as the address into the Color<br>Palette RAM.                                           |

| 9<br>8<br>7<br>5<br>4<br>3                   | G5<br>G4<br>G3<br>G2<br>G1<br>G0             | Out<br>Out<br>Out<br>Out<br>Out<br>Out | Both<br>Both<br>Both<br>Both<br>Both                 | GREEN DIGITAL OUTPUT. These pins provide the green data from the Color Palette RAM as addressed by the Pixel Address or the reduced data from the reduction logic. The output on these pins is selected by SEL[1:0]. |

| 1<br>64<br>63<br>61<br>60<br>59              | B5<br>B4<br>B3<br>B2<br>B1<br>B0             | Out<br>Out<br>Out<br>Out<br>Out<br>Out | Both<br>Both<br>Both<br>Both<br>Both                 | BLUE DIGITAL OUTPUT. These pins provide the blue data from the Color Palette RAM as addressed by the Pixel Address. The state of these outputs is controlled by SEL[1:0].                                            |

| 56<br>55<br>54<br>52<br>51<br>50             | R5<br>R4<br>R3<br>R2<br>R1<br>R0             | Out<br>Out<br>Out<br>Out<br>Out        | Both<br>Both<br>Both<br>Both<br>Both                 | RED DIGITAL OUTPUT. These pins provide the red data from the Color Palette RAM as addressed by the Pixel Address. The state of these outputs is controlled by SEL[1:0].                                              |

| 40<br>42<br>43                               | R<br>G<br>B                                  | Out<br>Out<br>Out                      | Analog<br>Analog<br>Analog                           | RED, GREEN, BLUE ANALOG OUTPUTS. These signals are the outputs of the 6-bit DACs. Each of these outputs is capable of driving a doubly terminated 75 ohm coaxial cable.                                              |

| 23                                           | BLANK/                                       | In                                     | Low                                                  | BLANKING CONTROL. A low on this input forces the analog outputs to the inactive state. (RGB=0 volts)                                                                                                                 |

### 82C411 PIN DESCRIPTIONS

| Pin #                                        | Pin Name                                     | Туре                                          | Active                                               | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------|----------------------------------------------|-----------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

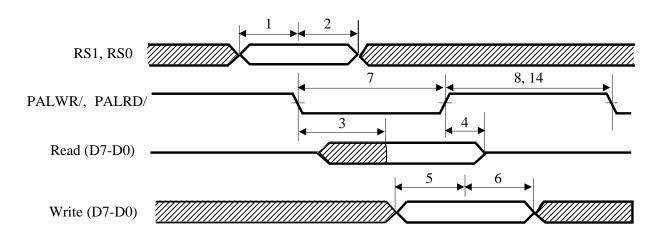

| 38<br>37                                     | RS1<br>RS0                                   | In<br>In                                      | Both<br>Both                                         | REGISTER SELECT 1 & 0. These two lines are<br>sampled during the falling edges of the enable signals<br>(PALWR/ or PALRD/) and select one of the three<br>internal registers or the palette RAM.                                                                                                                                                                                            |

|                                              |                                              |                                               |                                                      | RS1RS0Register00Address Register (RAM Write Mode)11Address Register (RAM Read Mode)01Palette RAM10Pixel Mask Register                                                                                                                                                                                                                                                                       |

| 33<br>32<br>31<br>30<br>29<br>28<br>25<br>24 | D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Both<br>Both<br>Both<br>Both<br>Both<br>Both<br>Both | PALETTE DATA. These pins provide the read/write data to the internal registers. During the write cycle, the rising edge of PALWR/ latches the data into the selected register. During the read cycle, the register data is output on these pins when PALRD/ is active (low). When PALRD/ is inactive (high) the data lines are 3-stated.                                                    |

| 34<br>22                                     | PALWR/<br>PALRD/                             | In<br>In                                      | Low<br>Low                                           | PALETTE WRITE ENABLE and PALETTE READ<br>ENABLE. These signals control the timing of read and<br>write operations on the CPU interface. RS1:0 are<br>latched on the falling edge of either of these signals<br>during a CPU read or write. D7:0 are sampled on the<br>rising edge of PALWR/ during an CPU write operation.<br>PALWR/ and PALRD/ should not be asserted at the<br>same time. |

| 12<br>11                                     | SEL1<br>SEL0                                 | In<br>In                                      | Both<br>Both                                         | SELECT 1 & 0. These signals select the data output on the digital outputs ( $R[5:0]$ , $G[5:0]$ B[5:0]), the reduction algorithm and the input to output delay. The functions are:                                                                                                                                                                                                          |

|                                              |                                              |                                               |                                                      | DelaySEL1 SEL0R[5:0]B[5:0]G[5:0](clocks)00OffOffNTSC Reduction601OffOffEqual Reduction610OffOffGreen Data611Red Data Blue DataGreen Data4                                                                                                                                                                                                                                                   |

| 39                                           | SENSE                                        | Out                                           | Both                                                 | COMPARATOR SENSE OUTPUT. A low indicates that one or more of the RGB outputs is above the sense reference level (335 mV).                                                                                                                                                                                                                                                                   |

### 82C411 PIN DESCRIPTIONS

| Pin #                                 | Pin Name | Туре | Active | Description                                                                                                                                                                                                                                  |  |

|---------------------------------------|----------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 44                                    | PWRDN    | In   | High   | POWER DOWN. A high on this signal places the entire device in a low power mode. No input or output takes place and the input clock may be stopped. All internal registers are preserved.                                                     |  |

| 45                                    | VREF     | In   | Analog | VOLTAGE REFERENCE INPUT. This pin may be used to override the internal 1.27 v reference.                                                                                                                                                     |  |

| 46                                    | DACEN    | In   | High   | DAC ENABLE. A high on this signal enables the voltage reference and the current outputs used in the DACs. When this input is low, the analog outputs and support logic are off.                                                              |  |

| 49                                    | IREF     | Out  | Analog | CURRENT REFERENCE SET. This pin is used to set<br>the current level in the analog outputs. It is usually<br>connected through a 220 ohm 1% resistor to ground.                                                                               |  |

| 6<br>27<br>36<br>53<br>62             | DVCC     | PWR  |        | DIGITAL POWER SUPPLY. The digital and analog<br>supplies are brought out separately to provide the<br>highest noise immunity. A high frequency decoupling<br>capacitor should be used between digital power and<br>ground.                   |  |

| 2<br>10<br>26<br>35<br>48<br>57<br>58 | DGND     | PWR  |        | DIGITAL GROUND.                                                                                                                                                                                                                              |  |

| 41                                    | AVCC     | PWR  |        | ANALOG POWER SUPPLY. The analog power<br>supply should be separated from the digital supply with<br>a high frequency noise suppressing inductor. A high<br>frequency decoupling capacitor should be used between<br>analog power and ground. |  |

| 47                                    | AGND     | PWR  |        | ANALOG GROUND.                                                                                                                                                                                                                               |  |

## 82C411 Color Palette Control Registers

| Register<br>Mnemonic | Register Name            | RS 1:0 | VGA<br>Access | VGA I/O<br>Address | Page |

|----------------------|--------------------------|--------|---------------|--------------------|------|

| DACMASK              | Pixel Mask Register      | 10     | RW            | 3C6h               | 13   |

| DACRX                | Palette Read-Mode Index  | 11     | W             | 3C7h               | 13   |

| DACX                 | Palette Write-Mode Index | 00     | RW            | 3C8h               | 14   |

| DACDATA              | Palette Data Port        | 01     | RW            | 3C9h               | 14   |

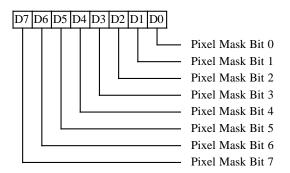

#### PIXEL MASK REGISTER (DACMASK)

*Read/Write at RS 1:0 = 10 Read/Write at VGA I/O Address 3C6h*

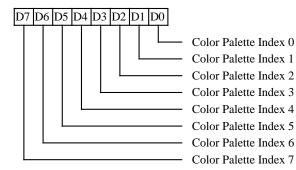

The contents of this register are logically ANDed with the 8 bits of video data. Zero bits in this register cause the corresponding input to the color palette RAM address to be zero. For example, if this register is programmed with 7, only addresses 0-7 would be accessible; video data input bits 3-7 would be ignored and all color values would map into the lower 8 locations in the color palette RAM.

#### **READ-MODE INDEX REGISTER (DACRX)**

*Read/Write RS 1:0 = 11 Write only at VGA I/O Address 3C7h*

This register is used to set the address of the next read access. When this register is written, the RGB color values are read from the palette RAM and saved in an internal storage register. The palette address pointer is then incremented.

#### WRITE MODE INDEX REGISTER (DACX)

Read/Write at RS 1:0 = 00 Read/Write at VGA I/O Address 3C8h

This register is used to set the address of the next read access. When this register is written, the RGB sequencer is cleared and the address pointer is loaded with the value written to this register.

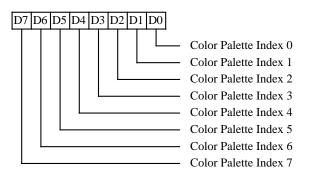

#### **PALETTE DATA PORT** (DACDATA 00-FF) Read/Write at RS 1: 0 = 01 Read/Write at VGA I/O Address 3C9h

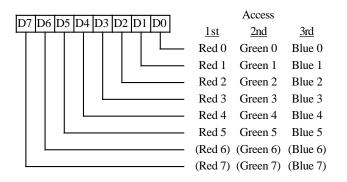

The index register is used to point to one of 256 data registers. Each data register is 18 bits in length (6 each for red, green, and blue), so the data values must be read as a sequence of 3 bytes. After writing the appropriate index register, data values may be read from or written to the palette data port in sequence: first red, then green, then blue, then repeated for the next location if desired (the address pointer is incremented automatically).

#### PROGRAMMING THE COLOR PALETTE

The index may be read or written at either RS [1:0] = 10 or 01. When the index value is written to either port, it is written to both the index register and a 'save' register internal to the color palette chip. The save register (not the index register) is used internally by the palette chip to point at the current data register. When the index value is written to the read mode index, it is written to both the index register is <u>automatically incremented</u>. When the index value is written to the write mode index, the automatic incrementing of the index register does not occur.

After the third of the three sequential data reads from (or writes to) the data port is completed, the save and index registers are both automatically incremented. This allows the entire palette (or any subset) to be read (written) by writing the index of the first color in the set, then sequentially reading (writing) the values for each color, without having to reload the index every three bytes.

The state of the RGB sequence is not saved; the user must access each three bytes in an uninterruptable sequence (or be assured that interrupt service routines will not access the palette index or data registers). When the index register is written (at either port), the RGB sequence is restarted. Data value reads and writes may be intermixed; either reads or writes increment internal RGB sequence counter.

#### **REDUCTION TECHNIQUES**

Three reduction algorithms are provided to reduce the 18 bit RGB data to 6 bits. Reduced data is output on G[5:0] when SEL1=0. The output data is delayed six clocks from the input pixel address to reduced data output when reduction is selected. The reduction algorithms are as follows:

NTSC: This is the industry standard technique for reducing RGB color information to gray levels. The weighting is 5/16R + 9/16G + 1/8B. The data is reduced with 9 bits of precision and the 6 most significant bits are output. This technique is selected when SEL0=0.

EQUAL: In this technique the RGB values are equally weighted. The reduction is 5/16R + 3/8G + 5/16B. This technique is selected when SEL0 = 1.

GREEN ONLY: When SEL1=1, the green output pins, G[5:0] contain the green palette data. On monochrome flat panels, this provides a display identical to the IBM monochrome monitor. When SEL[1:0] = 10, the data is delayed six clocks from the pixel input to the data output.

When SEL[1:0] = 11, the data is delayed four clocks from the input pixel address and all 18 digital outputs are enabled.

# This page was intentionally left blank

## 82C411 Electrical Specifications

#### 82C411 ABSOLUTE MAXIMUM CONDITIONS

| Symbol           | Parameter                       | Min  | Max                  | Units |

|------------------|---------------------------------|------|----------------------|-------|

| P <sub>D</sub>   | Power Dissipation               | _    | 1                    | W     |

| V <sub>CC</sub>  | Supply Voltage                  | -0.5 | 7                    | V     |

| V <sub>I</sub>   | Input Voltage                   | -0.5 | V <sub>CC</sub> +0.5 | V     |

| Vo               | Output Voltage                  | -0.5 | V <sub>CC</sub> +0.5 | V     |

| T <sub>A</sub>   | Operating Temperature (Ambient) | 0    | 70                   | ° C   |

| T <sub>STG</sub> | Storage Temperature             | -55  | 150                  | ° C   |

| I <sub>OD</sub>  | Digital Output Current          | -20  | 20                   | mA    |

| I <sub>OA</sub>  | Analog Output Current           | _    | 45                   | mA    |

**Note:** Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions described under Normal Operating Conditions.

#### 82C411 NORMAL OPERATING CONDITIONS

| Symbol          | Parameter           | Min | Max | Units |

|-----------------|---------------------|-----|-----|-------|

| V <sub>CC</sub> | Supply Voltage      | 4.5 | 5.5 | V     |

| T <sub>A</sub>  | Ambient Temperature | 0   | 70  | ° C   |

| T <sub>C</sub>  | Case Temperature    | 0   | 85  | ° C   |

#### 82C411 DC CHARACTERISTICS (Under Normal Operating Conditions Unless Noted Otherwise)

| Symbol           | Parameter                               | Notes                   | Min  | Тур  | Max                  | Units |

|------------------|-----------------------------------------|-------------------------|------|------|----------------------|-------|

| V <sub>IH</sub>  | Input High Voltage                      |                         | 2.0  | _    | V <sub>CC</sub> +0.5 | V     |

| V <sub>IL</sub>  | Input Low Voltage                       |                         | -0.5 | _    | 0.8                  | V     |

| V <sub>REF</sub> | Reference Voltage                       |                         | _    | 1.27 | _                    | V     |

| I <sub>IN</sub>  | Digital Input Current                   |                         | -10  | +10  | +10                  | uA    |

| I <sub>OZ</sub>  | Digital Output Current (High Impedance) |                         | -20  | -    | +20                  | uA    |

| V <sub>OH</sub>  | Output High Voltage                     | $I_{OH} = 4 \text{ mA}$ | 2.4  | _    | _                    | V     |

| V <sub>OL</sub>  | Output Low Voltage                      | $I_{OL} = 4 \text{ mA}$ | _    | _    | 0.4                  | V     |

| I <sub>CC0</sub> | Standby Supply Current                  | PWRDN=1                 | _    | _    | 2                    | mA    |

| I <sub>CC1</sub> | Power Supply Current                    | DACEN=1                 | _    | _    | 175                  | mA    |

| I <sub>CC2</sub> | Power Supply Current                    | DACEN=0                 | _    | 42   | 130                  | mA    |

| C                | Capacitance, Input or Output            |                         | _    | 10   | 20                   | pF    |

Note: Electrical specifications contained herein are preliminary and subject to change without notice.

.

#### 82C411 THERMAL CHARACTERISTICS (Under Normal Operating Conditions Unless Noted Otherwise)

| Symbol | Parameter          | Min | Тур | Max | Units |

|--------|--------------------|-----|-----|-----|-------|

| JA     | Thermal Resistance | —   | 63  | —   | ° C/W |

#### 82C411 DAC CHARACTERISTICS (Under Normal Operating Conditions Unless Noted Otherwise)

| Symbol         | Parameter               | Notes                   | Min  | Тур  | Max | Units |

|----------------|-------------------------|-------------------------|------|------|-----|-------|

| V <sub>O</sub> | Output Voltage          | Io $\leq 10 \text{ mA}$ | 1.5  | _    | _   | V     |

| Ι <sub>Ο</sub> | Output Current          | $Vo \le 1 V$            | 21   | _    | _   | mA    |

|                | Full Scale Error        |                         | _    | _    | ±5  | %     |

|                | DAC to DAC Correlation  |                         | ±2.0 | 1.27 | _   | %     |

|                | DAC Linearity           |                         | .5   | _    | _   | LSB   |

|                | Full Scale Setting Time |                         | _    | _    | 28  | nS    |

|                | Rise Time               | 10% to 90%              | _    | _    | 6   | nS    |

|                | Glitch Energy           |                         | _    | _    | 200 | pVsec |

|                | Comparator Sensitivity  |                         | _    | 50   | _   | mV    |

Note: Electrical specifications contained herein are preliminary and subject to change without notice.

•

......

\_\_\_\_\_®

| Symbol | Parameter                           | Min(ns) | Max(ns) |

|--------|-------------------------------------|---------|---------|

| 1      | RS0, RS1 Setup Time                 | 10      | _       |

| 2      | RS0, RS1, Hold Time                 | 10      | _       |

| 3      | PALRD/ to Data Valid                | _       | 45      |

| 4      | PALRD/ Negated to Data Bus 3-Stated | 5       | _       |

| 5      | Write Data Setup Time               | 10      | _       |

| 6      | Write Data Hold Time                | 10      | _       |

| 7      | PALWR/ or PALRD/ Low Pulse Width    | 50      | _       |

| 8      | PALRD/ High to PALRD/ or PALWR/ Low | 8*PCLK  | _       |

| 14     | PALWR/ High to PALRD/ or PALWR/ Low | 4*PCLK  | _       |

CPU Interface Timing

-

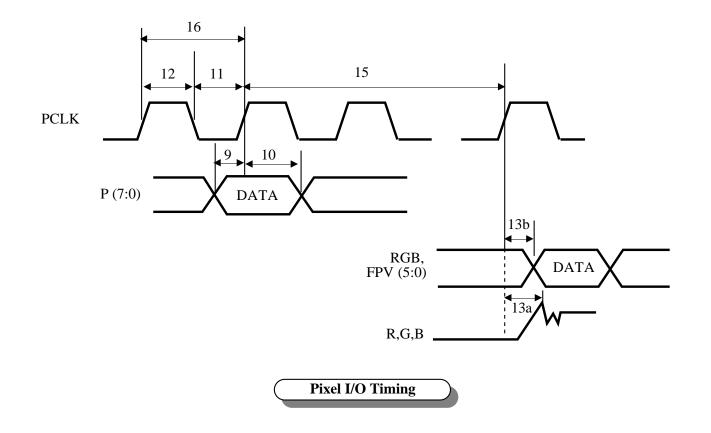

#### 82C411 AC TIMING CHARACTERISTICS - Pixel I/O

| Symbol | Parameter                                         | Notes          | Min(ns) | Max(ns) |

|--------|---------------------------------------------------|----------------|---------|---------|

| 9      | Pixel Setup Time                                  |                | 4       | _       |

| 10     | Pixel Hold Time                                   |                | 4       | _       |

| 16     | Clock Cycle Time                                  | 40MHz          | 25      | _       |

| 11     | Clock Pulse Width Low Time                        |                | 10      | _       |

| 12     | Clock Pulse Width High Time                       |                | 10      | _       |

| 13a    | PCLK to Valid Analog Output                       |                | _       | 30      |

| 13b    | PCLK to Valid Digital Output (load) = 10pf        |                | 5       | 21      |

| _      | Skew between any analog output on the same device |                | _       | 2       |

| 15a    | Pixel in to analog output                         |                |         | 3*PCLK  |

| 15b    | Pixel in to digital output                        | SEL1:=0x or 10 | 6*PCLK  | 6*PCLK  |

| 15c    | Pixel in to digital output                        | SEL1:0=11      | 4*PCLK  | 4*PCLK  |

|        | Analog output to Sense output delay               |                | _       | 1000    |