#### Copyright Notice

#### Copyright © 1993, Chips and Technologies, Inc. ALL RIGHTS RESERVED.

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without express written permission of Chips and Technologies, Inc.

#### **Restricted Rights and Limitations**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

#### Trademark Acknowledgment

CHIPS, CHIPS logotype, NEAT, and SCAT are registered trademarks of Chips and Technologies, Inc.

CHIPSet, ChipsLAN, CHIPSlink, CHIPSPak, CHIPSPort, CHIPS/230, CHIPS/250, CHIPS/280, CHIPS/450, Ether-Net, ETHERCHIP, LeAPSet, LeAPSetsx, MICROCHIPS, NEATsx, PC/Chip, PC Video, PEAK, SMARTMAP, and Wingine are trademarks of Chips and Technologies, Inc.

IBM, IBM PC/AT, IBM PC/XT are registered trademarks of International Business Machines Corporation.

VESA VL-Bus is a trademark of Video Electronics Standards Associations.

Weitek is a registered trademark of Weitek Inc.

387, 486, and i486 are trademarks of Intel Corporation.

#### Disclaimer

This document is provided as general information for our customers. Chips and Technologies, Inc. reserves the right to modify the information contained herein as necessary and the customer should ensure that they have the most recent revision of the data sheet. CHIPS makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that the field of personal computers is the subject of many patents held by different parties. Customers should ensure that they take appropriate action so that their use of the products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

## CS4031 CHIPSet

- Very low-cost and high-integration chip set

- Supports 486SX, 487SX, 486DX, and 486DX2 CPUs

- Operating speeds of up to 33MHz

- Two-chip chip set, no external IPC needed

- Integrated industry-standard CHIPS IPC core; no external RTC needed

- Integrated on-chip oscillators for 14.318MHz and 32.768KHz clocks

- Only 8 TTL devices required for a complete system with one VL-Bus slot

- Full VESA VL-Bus supports up to 3 slots for superior system performance, e.g. graphics

- Patented high-performance "Page-interleave" DRAM controller

- 3-2-2-2 or 4-3-3-3 for reads, and 0 or 1WS for writes

- Up to 64MB memory with 4 banks of DRAM or 32MB with 2 banks

- Supports 256KB, 1MB, 4MB, and 16MB DRAM with a depth of 256K, 1M, or 4M

- Hidden refresh supported for higher performance

- Integrated Flash Rom support

- External ISA-Bus drivers for design flexibility and optimum drive

- 100% PC/AT<sup>®</sup> compatible

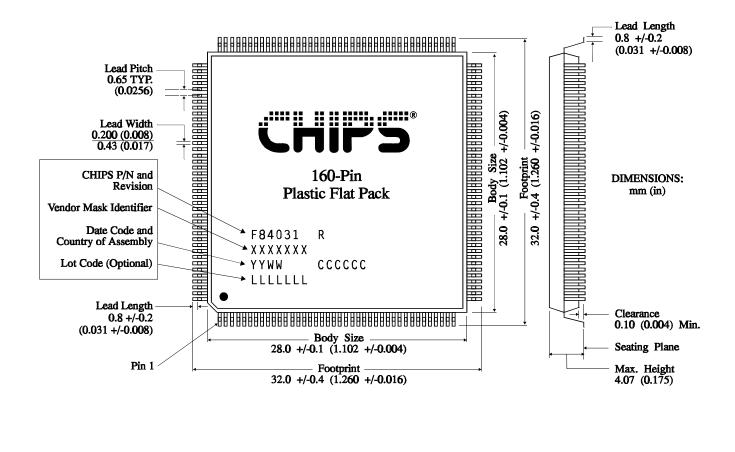

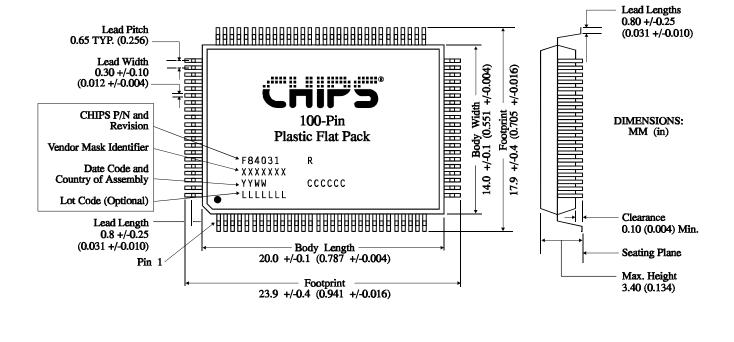

- 160-pin PQFP for the F84031 and 100-pin PQFP for the F84035

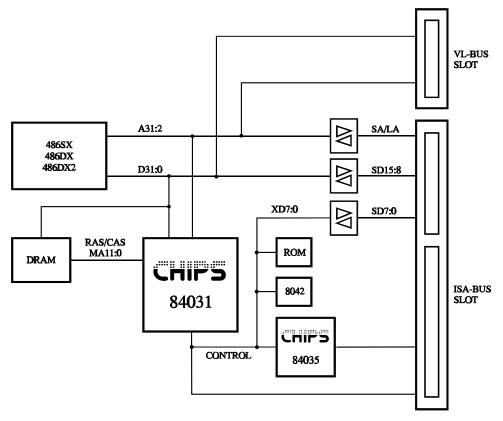

System Diagram

# Revision History

| Revision | Date    | By | Comment                                                             |

|----------|---------|----|---------------------------------------------------------------------|

| 0.1      | 3/2/93  | PD | Internal review —Rough draft.                                       |

| 0.2      | 3/26/93 | PD | Internal review — Added Product Overview and Introduction sections. |

| 0.3      | 4/30/93 | PD | Internal review.                                                    |

| 1.0      | 5/10/93 | PD | Final release.                                                      |

# Table of Contents

| Introduction 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CS4031 Pinouts       9         84031 Pinouts       9         84035 Pinouts       10                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CS4031 Pin Descriptions       11         84031 Pin Overview       11         84035 Pin Overview       15         84031 Pin Descriptions       17         84035 Pin Descriptions       23         CS4031 Registers       27                                                                                                                                                                                                                                                                                          |

| CS4031 Registers2784031 and 84035 I/O Port Summary2784031 and 84035 Configuration Register2784031 I/O Port Addresses2884031 Configuration Registers3184035 I/O Port Addresses3884035 Configuration Registers34                                                                                                                                                                                                                                                                                                      |

| CS4031 System Level Functions47Clocks47Reset and GATEA2047Arbitration47Refresh48Coprocessor Logic48Address Mapping48ISA-Bus48Local Bus Support48DRAM Controller48Data Buffers48                                                                                                                                                                                                                                                                                                                                     |

| 84031 Functional Descriptions       51         Clocks       51         Clock Divider       51         Clock Inputs       51         BUSCLK Generation       53         14.31818MHz Clock       53         SCLK       54         32.768KHz Clock       54         System Reset Logic       55         Reset From PWRGOOD       56         SYSRESET       56         CPU Shutdown       56         GATEA20 Function       57         Address Mapping       58         I/O Addressing       58         RoMCS#       58 |

| Section                                            | Page |

|----------------------------------------------------|------|

| DRAM Controller                                    | 59   |

| DRAM Configuration                                 |      |

| DRAM Controller Page Interleaving                  |      |

| DRAM Memory Map                                    | 62   |

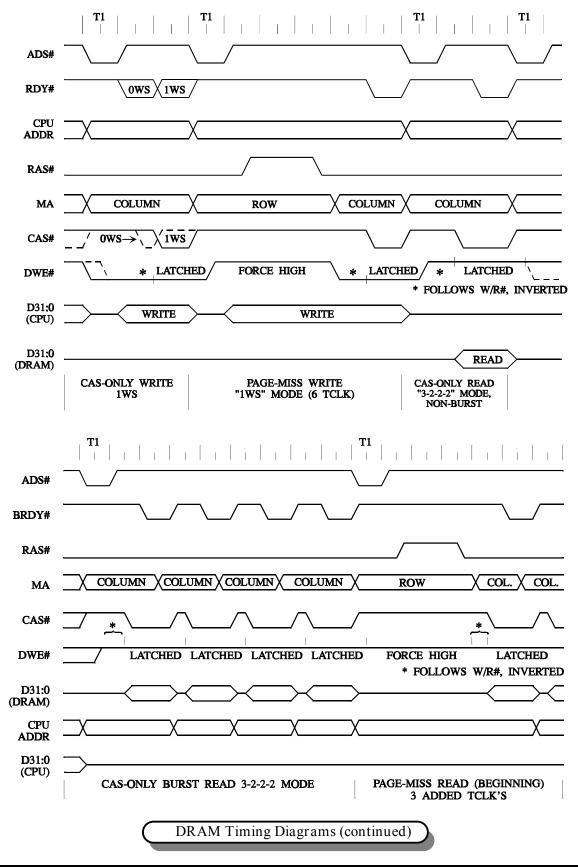

| DRAM Timing Modes                                  | 62   |

| DRAM Timing Mode Recommendations                   |      |

| DRAM Address Multiplexing                          | 65   |

| Local Bus Support                                  | 65   |

| ISA-Bus                                            | 68   |

| CPU and Local Master Accesses                      | 00   |

| to the ISA-bus                                     | 68   |

| DMA and ISA Master Accesses                        | 00   |

| to Local Slaves and DRAM                           | 68   |

| Bus Cycle Descriptions                             | 69   |

| CPU/LBM Read and Write                             | 0)   |

| to Local Bus Target                                | 69   |

| CPU/LBM Access to the ISA-Bus                      |      |

| IOCHRDY Operation                                  |      |

| DMA and ISA Master Memory Access                   | /1   |

| to a Local Bus Target                              | 71   |

| ISA Master I/O Access                              | /1   |

| to a Local Bus Target                              | 73   |

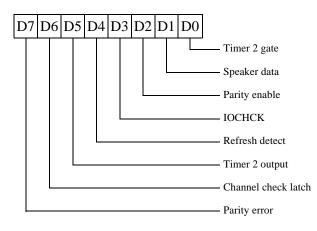

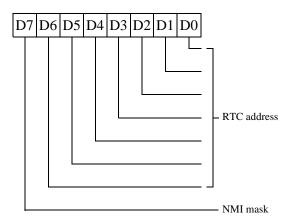

| PORT B AND NMI LOGIC                               | 74   |

| DATA BUS BUFFERS                                   | 74   |

| CONTROL LINK                                       | 74   |

| Control Link From the 84035                        | 15   |

|                                                    | 75   |

| to the 84031<br>Control Link From the 84031        | 15   |

|                                                    | 75   |

| to the 84035<br>Test Modes for the 84031 and 84035 | . 75 |

|                                                    |      |

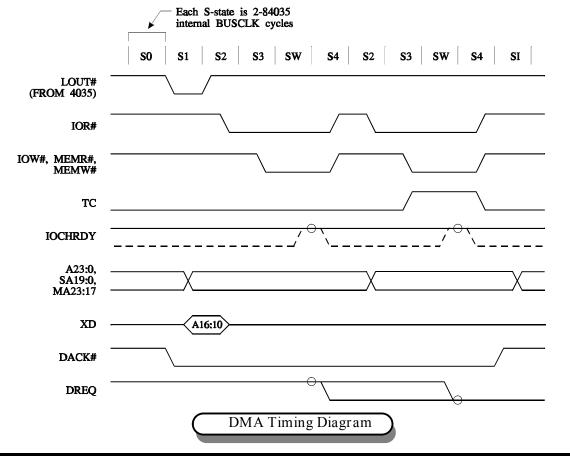

| 84035 Functional Descriptions                      | 77   |

| Clocks                                             | 77   |

| 14.31818MHz Clock                                  | 77   |

| SCLK                                               | 77   |

| 32.768KHz CLOCK                                    | 77   |

| Reset                                              | 78   |

| GATEA20                                            | 78   |

| Arbitration                                        | 78   |

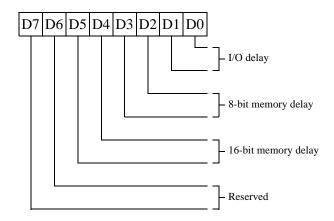

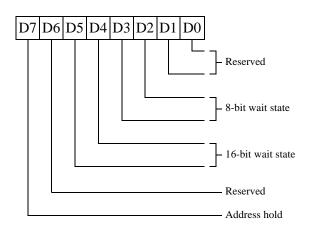

| Performance Control                                | 79   |

| Refresh                                            | 80   |

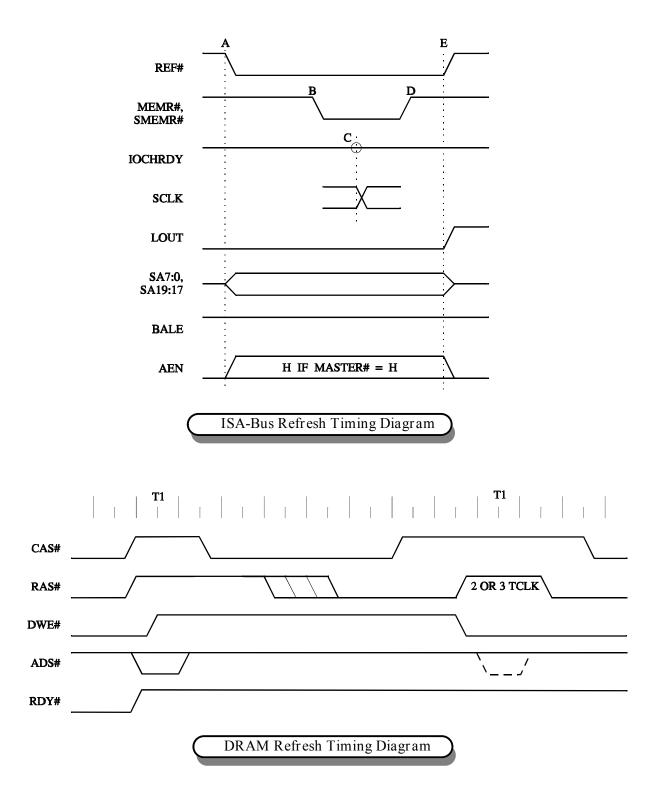

| ISA-Bus Refresh Cycles                             | 80   |

| DRAM Refresh Cycles                                | 80   |

| ISA-Bus                                            | 82   |

| 486 Floating-Point Logic                           |      |

| Port B and Speaker Logic                           | 83   |

|                                                    |      |

| <u>Section</u>                          | Page |

|-----------------------------------------|------|

| CS4031 Electrical Specifications        | 85   |

| 84031/84035 Absolute Maximum Conditions | 85   |

| 84031/84035 Recommended Operating       |      |

| Conditions                              | 85   |

| 84031/84035 DC Characteristics          | 85   |

| 84031 AC Characteristics                | 86   |

| 84035 AC Characteristics                | 90   |

| CS4031 Mechanical Specifications        | 93   |

## Fi

| <u>Figure</u>                                                                                                                                                                                                                      | Page                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| CS4031 CHIPSet<br>System Diagram                                                                                                                                                                                                   | 1<br>1                                       |

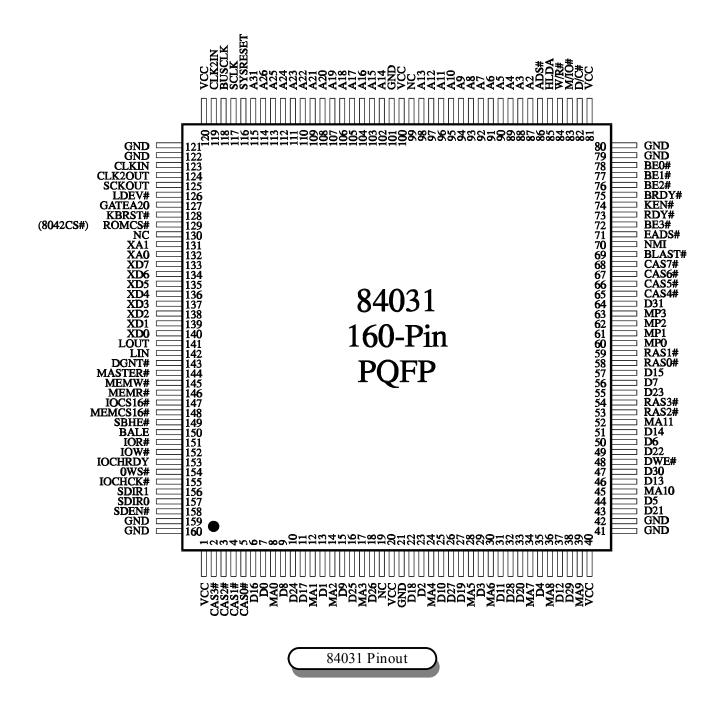

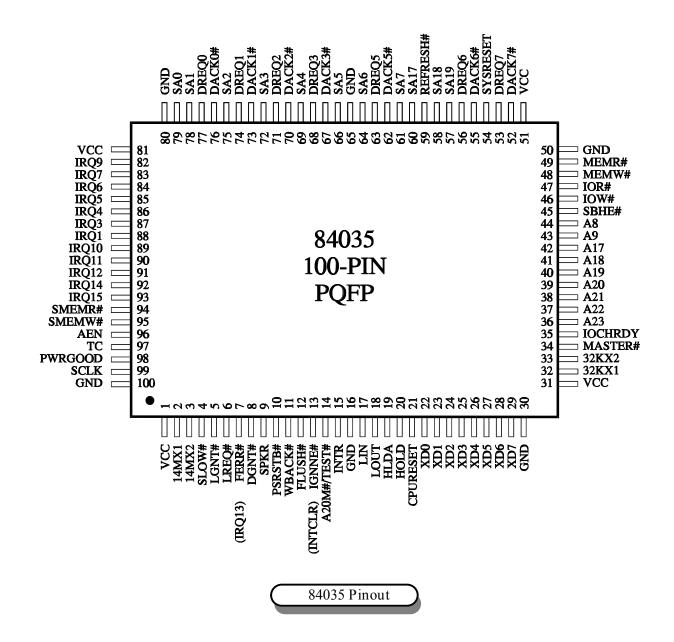

| CS4031 Pinouts<br>84031 Pinout<br>84035 Pinout                                                                                                                                                                                     | 9<br>9<br>10                                 |

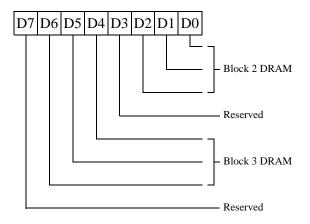

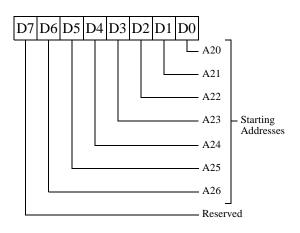

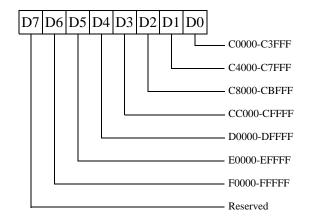

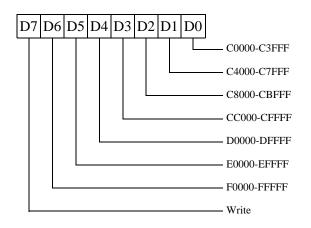

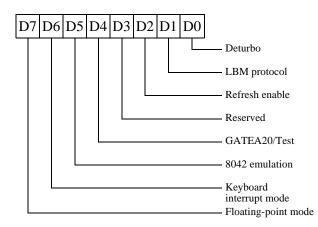

| CS4031 Registers                                                                                                                                                                                                                   | 28<br>28<br>28<br>28<br>29<br>30             |

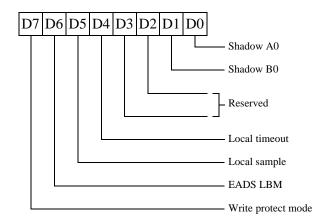

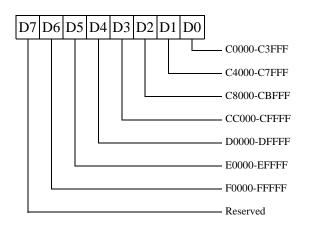

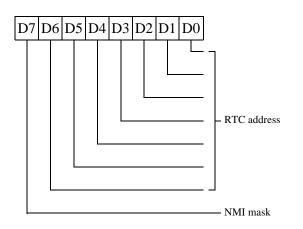

| and NMI Mask                                                                                                                                                                                                                       | 31<br>31<br>32<br>32<br>33<br>33<br>34<br>34 |

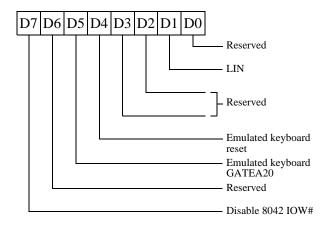

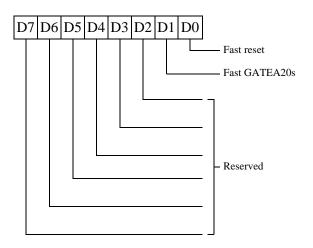

| Video Area Shadow<br>and Local Bus Control<br>DRAM Shadow Read Enable<br>DRAM Shadow Write Enable<br>ROMCS Enable<br>Soft Reset and GATEA20<br>Reserved (Do Not Write)<br>84035 I/O Port Addresses<br>DMA Controller 1 (8-Bit DMA) | 36<br>36<br>37<br>37<br>37<br>38             |

| Interrupt Controller 1 (IRQ7:0)<br>Configuration Register Address Port<br>Configuration Register Data<br>Timer (8254)<br>Port B<br>Real Time Clock Address Port<br>and NMI Mask                                                    | 38<br>38<br>38<br>38<br>39<br>40             |

| Real Time Clock Data Port<br>DMA Page Registers<br>Fast CPU Reset and GATEA20<br>Interrupt Controller 2 (IRQ15:8)<br>DMA Controller 2 (16-Bit DMA)                                                                                 | 40<br>41<br>41                               |

| <u>Figure</u>                                                                                                                        | Page     |

|--------------------------------------------------------------------------------------------------------------------------------------|----------|

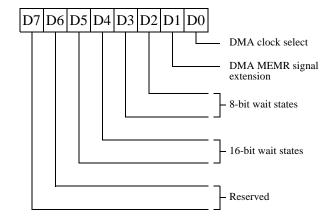

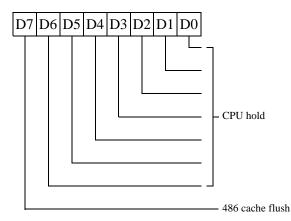

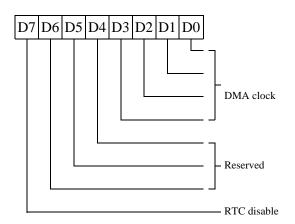

| 84035 Configuration Registers<br>DMA Wait State Control<br>Performance Control<br>84035 Miscellaneous Control<br>DMA Clock Selection | 42<br>43 |

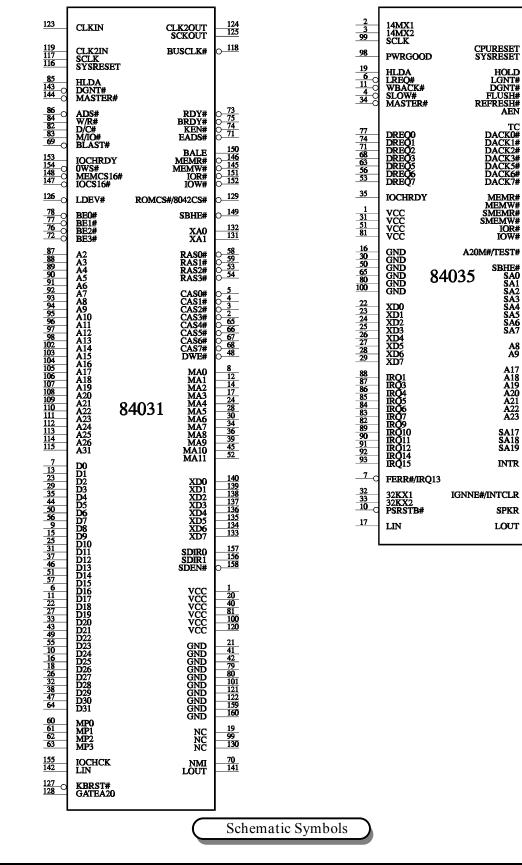

| CS4031 System Level Functions<br>Schematic Symbols                                                                                   | 47<br>49 |

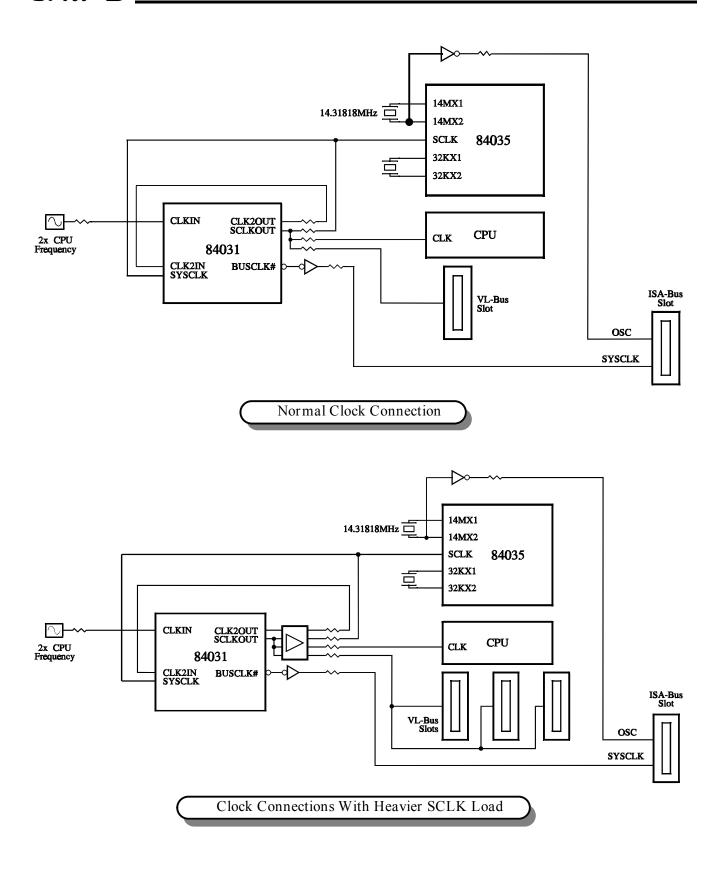

| 84031 Functional Descriptions<br>Clock Connections With Heavier                                                                      | 51       |

| SCLK Load                                                                                                                            | 52       |

| Normal Clock Connection                                                                                                              | 52       |

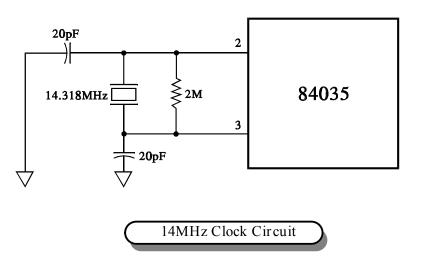

| 14MHz Clock Circuit                                                                                                                  | 53       |

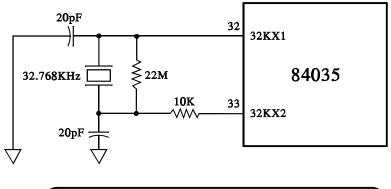

| Recommended 32KHz Clock Circuit<br>Diagram                                                                                           | 54       |

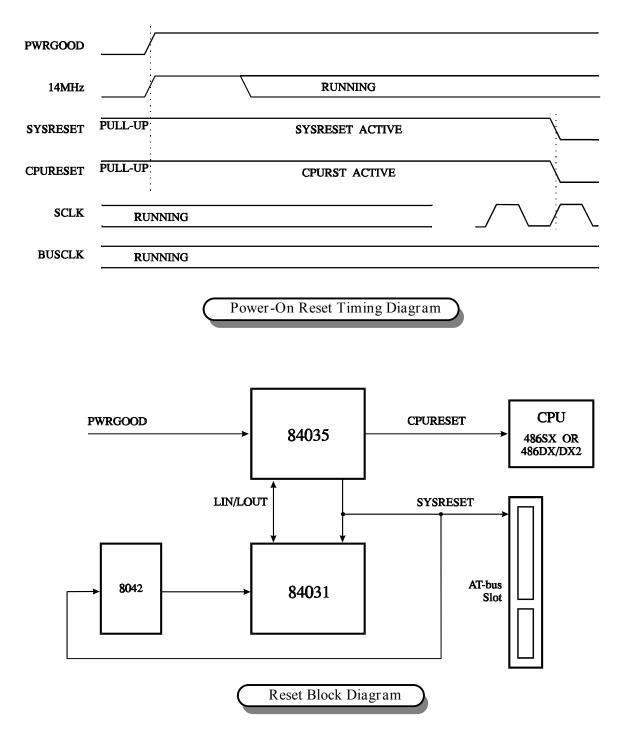

| Power-On Reset Timing Diagram                                                                                                        |          |

| Reset Block Diagram                                                                                                                  | 55       |

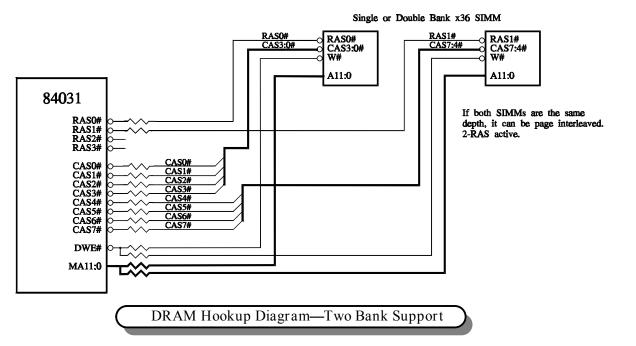

| DRAM Hookup Diagram — Two Bank                                                                                                       | 60       |

| Support                                                                                                                              |          |

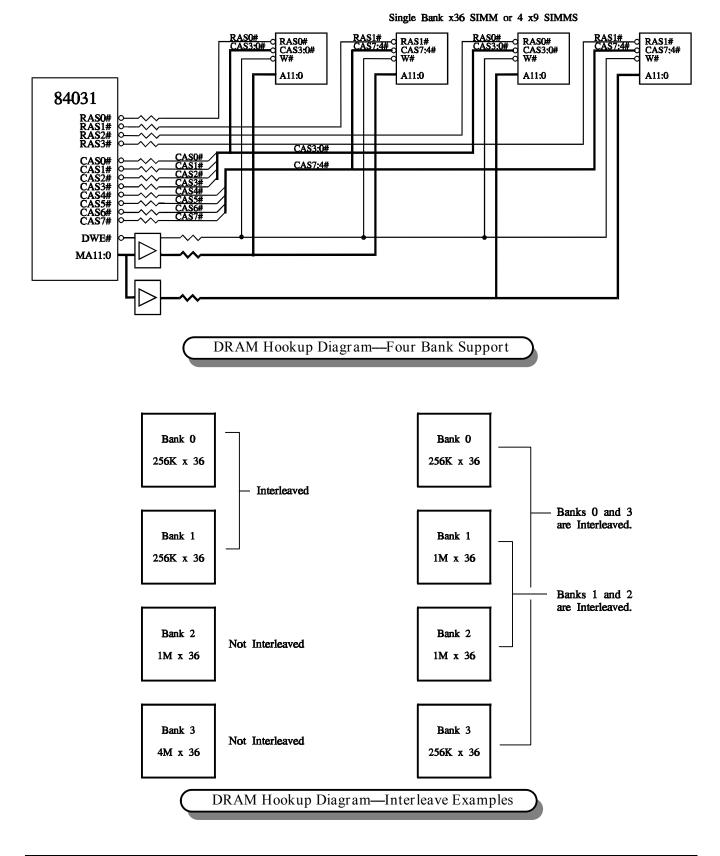

| Page Interleaving Example<br>DRAM Hookup Diagram —Four Bank                                                                          | 60       |

| Support                                                                                                                              | 61       |

| DRÂM Hookup Diagram —Interleave                                                                                                      |          |

| Examples                                                                                                                             | 61       |

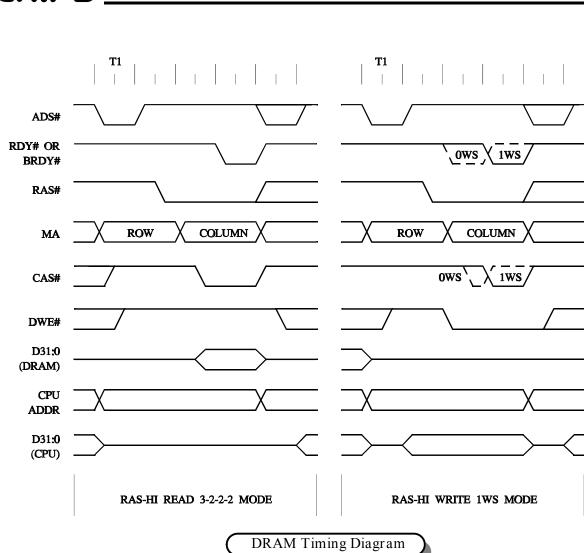

| DRAM Timing Diagram                                                                                                                  | 63       |

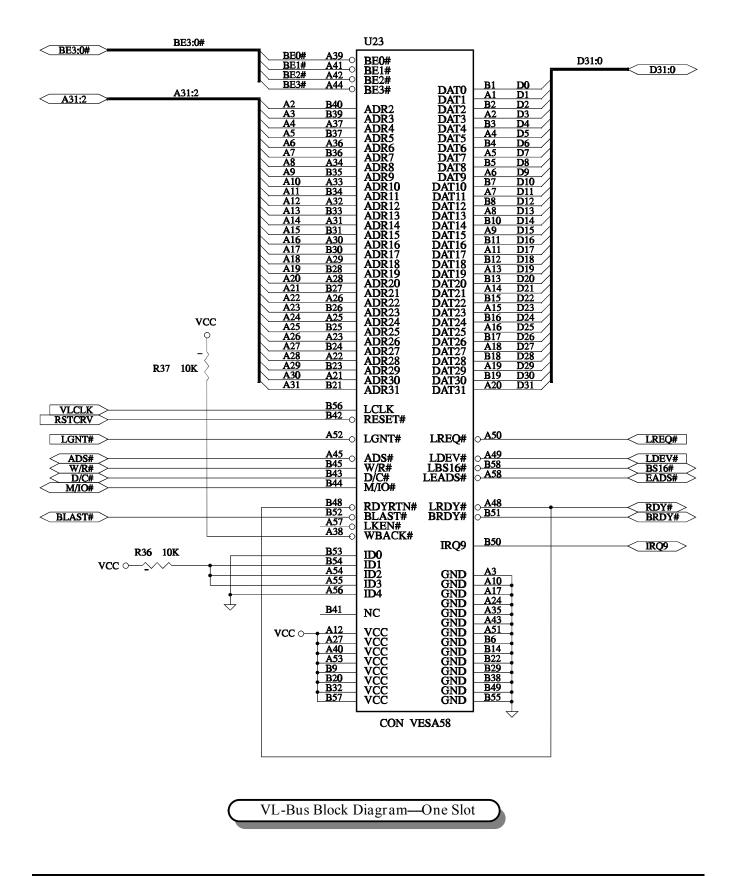

| VL-Bus Block Diagram —One Slot                                                                                                       | 66       |

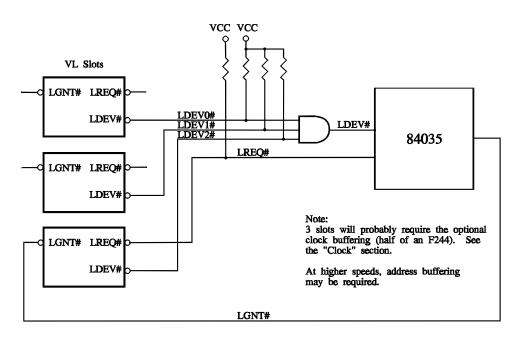

| VL-Bus Block Diagram —One Slot<br>VL-Bus Block Diagram —Multiple Slots<br>With Multiple Masters                                      | 67       |

| VL-Bus Block Diagram —Multiple Slots                                                                                                 |          |

| With Single Master<br>CPU/LBM Read and Write to LBT                                                                                  | 67       |

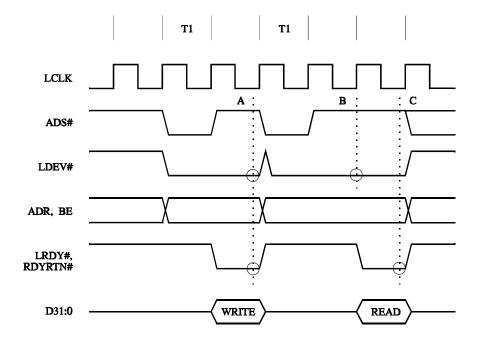

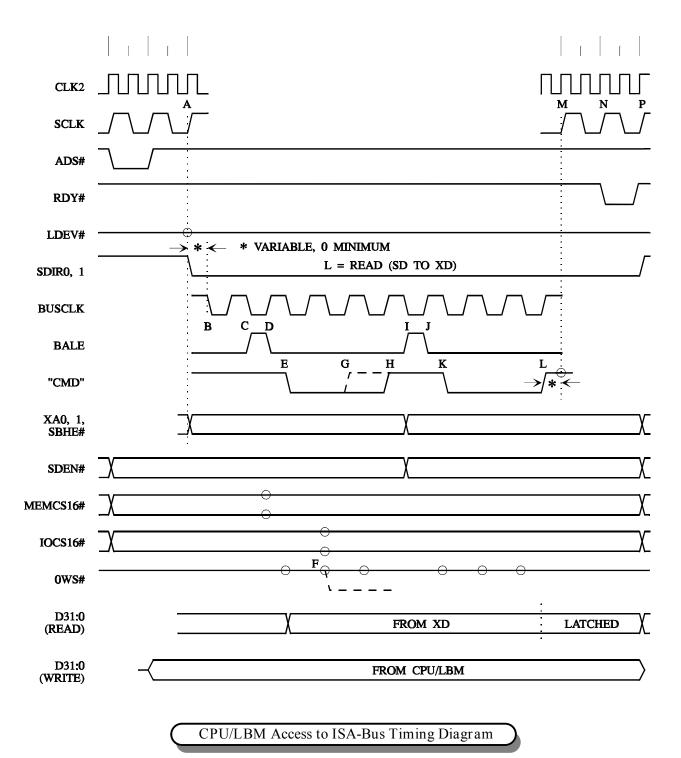

| Timing Diagram<br>CPU/LBM Access to ISA-Bus                                                                                          | 69       |

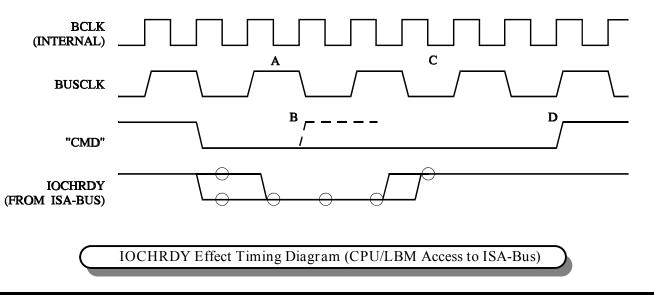

| Timing Diagram<br>IOCHRDY Effect Timing Diagram                                                                                      | 70       |

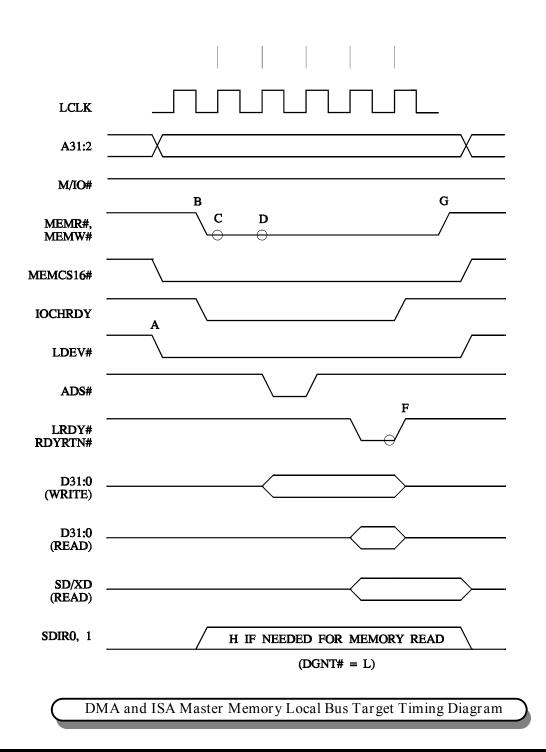

| (CPU/LBM Access to ISA-Bus)<br>DMA and ISA Master Memory Local Bus                                                                   | 71       |

| Torget Timing Diagram                                                                                                                | 72       |

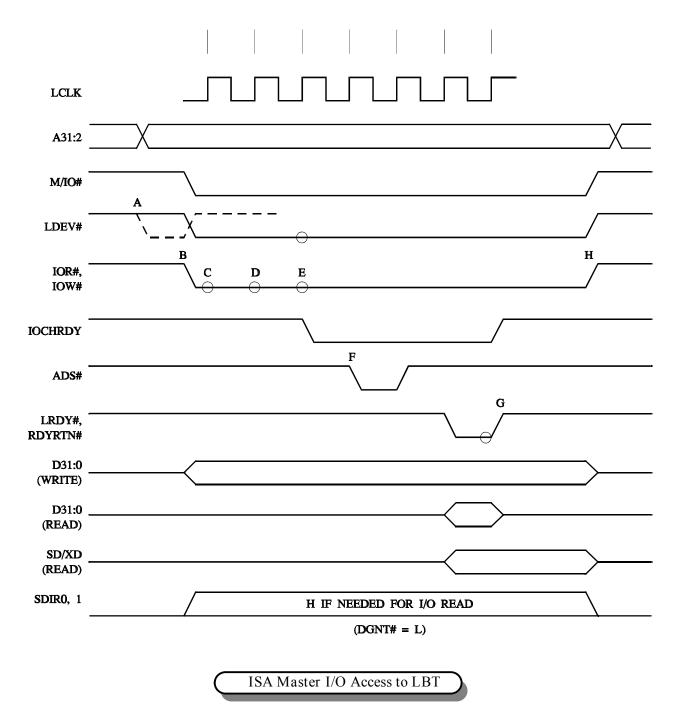

| Target Timing Diagram<br>ISA Master I/O Access to LBT                                                                                | 72       |

| ISA Master I/O Access to LB1                                                                                                         | 13       |

| 84035 Functional Descriptions                                                                                                        | 77       |

| DRAM Refresh Timing Diagram                                                                                                          | 81       |

| ISA-Bus Refresh Timing Diagram                                                                                                       | 81       |

| DMA Timing Diagram                                                                                                                   | 82       |

| CS4031 Electrical Specifications                                                                                                     | 85       |

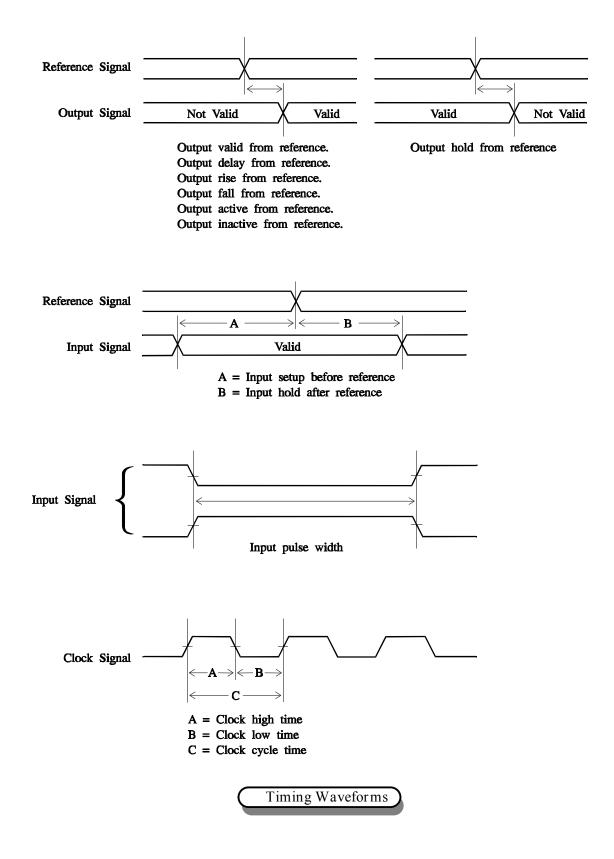

| Timing Waveforms                                                                                                                     | 91       |

# List of Tables

### Table

### Page

## Page

| CS4031 Pin Descriptions                | 11 |

|----------------------------------------|----|

| 84031 Pin Overview                     | 11 |

| 84035 Pin Overview                     | 15 |

| 84031 Pin Descriptions                 | 17 |

| Clocks And Reset                       | 17 |

| Arbitration                            | 17 |

| CPU and Local Bus Control Signals      | 18 |

| ISA-Bus                                | 18 |

| Address Bus                            | 19 |

| DRAM Controller                        | 20 |

| Data Bus                               | 21 |

| Interrupts                             | 22 |

| Control Link And Keyboard              | 22 |

| 84035 Pin Descriptions                 | 23 |

| Clocks                                 | 23 |

| Resets                                 | 23 |

| Arbitration                            | 23 |

| ISA-Bus                                | 24 |

| Address Bus                            | 25 |

| Data Bus                               | 25 |

| Interrupts                             | 26 |

| Interval Timer and Date-Time Clock     | 26 |

| Control Link                           | 26 |

|                                        | 27 |

| CS4031 Registers                       | 27 |

| 84031 and 84035 Configuration Register | 21 |

|                                        | 27 |

| Summary                                | 21 |

| 84031 Functional Descriptions          | 51 |

| Suggested BUSCLK Dividers for Each     |    |

| CPU Frequency                          | 53 |

| Possible ISA-Bus Clock Frequencies     |    |

| at Each Cpu Frequency                  | 53 |

| 84035 Clock Divider                    | 54 |

| Special Cycle Encoding                 |    |

| DRAM Bank Starting Address             | 59 |

| Suggested Ras-to-CAs Delay             |    |

| for Read Cycles                        | 62 |

| DRAM Timing Mode                       | 62 |

| Address Multiplexing                   | 65 |

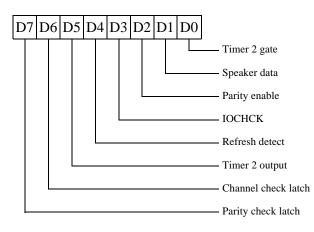

| Port B Bits                            | 74 |

|                                        |    |

| Table                                                                        | Page           |

|------------------------------------------------------------------------------|----------------|

| 84035 Functional Descriptions<br>84035 Clock Divider<br>Bus Owner Indication | 77<br>77<br>79 |

| 84035 Port B Bits                                                            | 83             |

| CS4031 Electrical Specifications<br>84031/84035 Absolute Maximum             | 85             |

| Conditions                                                                   | 85             |

| Conditions                                                                   | 85             |

| 84031/84035 DC Characteristics                                               |                |

| 84031 AC Characteristics                                                     | 86             |

| Clock Signals<br>Dram Signals                                                | 86<br>87       |

| Dram Formula Specifications                                                  | 88             |

| CPU and Local Bus Signals                                                    | 89             |

| 84035 AC Characteristics                                                     | 90             |

## Introduction

CS4031 is a very high-integration and low-cost chip set for 486-based PC/AT compatible systems. It consists of two chips, the F84031 and F84035. These are optimally partitioned to minimize the external TTL count.

Only 8 TTL devices are required to implement a 100% PC/AT compatible complete system with a 2-bank DRAM (up to 32MB) and one VESA VL-Bus slot for either a master or a slave. Only one additional TTL is needed for the system supporting two VL-Bus slots with no more than one master.

The 84031 integrates DRAM controller, ISA-bus controller, and VESA VL-Bus controller in a 160-pin PQFP package.

The 84035 is a super set of the industry-standard CHIPS IPC (Integrated Peripheral Controller, 82C206) which integrates two 8237 DMA controllers, two 8259 interrupt controllers, one 8254 timer/counter, one MC146818 real time clock, and a 74LS612 memory mapper in a 100-pin PQFP package.

## CS4031 Pinouts

The CS4031 CHIPSet is comprised of two chips, the 84031 and the 84035. Following the 84031 and 84035 pinout diagrams are the pin assignments listed by signal names.

## CS4031 Pin Descriptions

#### 84031 PIN OVERVIEW

The 84031 Pin Overview table below lists the pins by signal names. The detailed pin functional descriptions for the 84031 follows the pin overview tables.

#### 84031 PIN OVERVIEW

| Signal Name              | Pin No.                                                | Input/<br>Output | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | Load<br>(pF) | Pull-up<br>(Ω) | Notes                                  |

|--------------------------|--------------------------------------------------------|------------------|-------------------------|-------------------------|--------------|----------------|----------------------------------------|

| V <sub>CC</sub> (6 Pins) | 1, 20, 40, 81, 100, and 120                            |                  | —                       |                         |              |                | System V <sub>CC</sub>                 |

| GND (10 Pins)            | 21, 41, 42, 79, 80, 81, 101,<br>121, 122, 160, and 159 |                  |                         |                         |              |                | System ground                          |

| 0WS#                     | 1                                                      | In               |                         |                         |              | 300            | ISA-bus                                |

| A02                      | 87                                                     | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A03                      | 88                                                     | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A04                      | 89                                                     | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A05                      | 90                                                     | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A06                      | 91                                                     | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A07                      | 92                                                     | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A08                      | 93                                                     | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A09                      | 94                                                     | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A10                      | 95                                                     | I/O              | 4                       | -2                      | 50           |                | CPU, local bus devices, and AT buffers |

| A11                      | 96                                                     | I/O              | 4                       | -2                      | 50           |                | CPU, local bus devices, and AT buffers |

| A12                      | 97                                                     | I/O              | 4                       | -2                      | 50           |                | CPU, local bus devices, and AT buffers |

| A13                      | 98                                                     | I/O              | 4                       | -2                      | 50           |                | CPU, local bus devices, and AT buffers |

| A14                      | 102                                                    | I/O              | 4                       | -2                      | 50           |                | CPU, local bus devices, and AT buffers |

| A15                      | 103                                                    | I/O              | 4                       | -2                      | 50           |                | CPU, local bus devices, and AT buffers |

| A16                      | 104                                                    | I/O              | 4                       | -2                      | 50           |                | CPU, local bus devices, and AT buffers |

| A17                      | 105                                                    | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A18                      | 106                                                    | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A19                      | 107                                                    | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A20                      | 108                                                    | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A21                      | 109                                                    | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A22                      | 110                                                    | In               |                         |                         |              |                | CPU, local bus devices, and AT buffers |

| A23                      | 111                                                    | In               | _                       |                         | _            |                | CPU, local bus devices, and AT buffers |

| A24                      | 112                                                    | I/O              | 4                       | -2                      | 50           |                | CPU, local bus devices, and AT buffers |

| A25                      | 113                                                    | I/O              | 4                       | -2                      | 50           |                | CPU, local bus devices, and AT buffers |

| A26                      | 114                                                    | I/O              | 4                       | -2                      | 50           |                | CPU, local bus devices, and AT buffers |

| A31                      | 115                                                    | I/O              | 4                       | -2                      | 50           |                | CPU, local bus devices, and AT buffers |

| ADS#                     | 86                                                     | I/O              | 4                       | -2                      | 40           | 10K            | CPU and local bus devices              |

| BALE                     | 150                                                    | Out              | 18                      | -10                     | 240          | _              | ISA-bus                                |

| BE0#                     | 78                                                     | I/O              | 4                       | -2                      | 50           | -              | CPU and local bus devices              |

| BE1#                     | 77                                                     | I/O              | 4                       | -2                      | 50           |                | CPU and local bus devices              |

| BE2#                     | 76                                                     | I/O              | 4                       | -2                      | 50           |                | CPU and local bus devices              |

| BE3#                     | 72                                                     | I/O              | 4                       | -2                      | 50           |                | CPU and local bus devices              |

| BLAST#                   | 69                                                     | I/O              | 4                       | -2                      | 40           |                | CPU and local bus devices              |

| BRDY#                    | 75                                                     | I/O              | 4                       | -2                      | 40           | 10K            | CPU and local bus devices              |

| BUSCLK                   | 118                                                    | Out              | 18                      | -10                     | 50           | _              | 8042 inverter                          |

| Signal Name | Pin No. | Input/<br>Output | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | Load<br>(pF) | Pull-up<br>(Ω) | Notes                             |

|-------------|---------|------------------|-------------------------|-------------------------|--------------|----------------|-----------------------------------|

| CAS0#       | 5       | Out              | 18                      | -10                     | 65           |                | 6 DRAMs @ 7pF plus wiring         |

| CAS1#       | 4       | Out              | 18                      | -10                     | 65           |                | 6 DRAMs @ 7pF plus wiring         |

| CAS2#       | 3       | Out              | 18                      | -10                     | 65           |                | 6 DRAMs @ 7pF plus wiring         |

| CAS3#       | 2       | Out              | 18                      | -10                     | 65           |                | 6 DRAMs @ 7pF plus wiring         |

| CAS4#       | 65      | Out              | 18                      | -10                     | 65           |                | 6 DRAMs @ 7pF plus wiring         |

| CAS5#       | 66      | Out              | 18                      | -10                     | 65           |                | 6 DRAMs @ 7pF plus wiring         |

| CAS6#       | 67      | Out              | 18                      | -10                     | 65           |                | 6 DRAMs @ 7pF plus wiring         |

| CAS7#       | 68      | Out              | 18                      | -10                     | 65           |                | 6 DRAMs @ 7pF plus wiring         |

| CLK2        | 119     | In               |                         |                         |              |                | CLK2OUT or oscillator circuit     |

| CLK2OUT     | 124     | Out              | 9                       | -5                      | 30           |                | 84031 CLK2                        |

| CLKIN       | 123     | In               |                         |                         |              |                | Oscillator                        |

| D/C#        | 82      | I/O              | 4                       | -2                      | 40           |                | CPU and local bus devices         |

| D0          | 7       | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D1          | 13      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D2          | 23      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D3          | 29      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D4          | 35      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D5          | 44      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D6          | 50      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D7          | 56      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D8          | 9       | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D9          | 15      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D10         | 25      | I/O<br>I/O       | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D10         | 31      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D12         | 37      | I/O<br>I/O       | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D12<br>D13  | 46      | I/O<br>I/O       | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D13         | 51      | I/O<br>I/O       | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D14<br>D15  | 57      | I/O<br>I/O       | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D15<br>D16  | 6       | I/O<br>I/O       | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D10<br>D17  | 11      | I/O<br>I/O       | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D17<br>D18  | 22      | I/O<br>I/O       | 4                       | -2                      | 65           |                |                                   |

|             |         | I/O<br>I/O       | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D19         | 27      |                  |                         | -2                      |              |                | CPU, DRAMs, and local bus devices |

| D20         |         | I/O              | 4                       |                         | 65           |                | CPU, DRAMs, and local bus devices |

| D21         | 43      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D22         | 49      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D23         | 55      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D24         | 10      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D25         | 16      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D26         | 18      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D27         | 26      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D28         | 32      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D29         | 38      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D30         | 47      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| D31         | 64      | I/O              | 4                       | -2                      | 65           |                | CPU, DRAMs, and local bus devices |

| DGNT#       | 143     | In               |                         |                         |              |                | IPC                               |

| DWE#        | 48      | Out              | 18                      | -10                     | 240          |                | 24 DRAMs @ 7pF plus wiring        |

| EADS#       | 71      | Out              | 9                       | -5                      | 40           | 10K            | CPU and local bus devices         |

| GATEA20     | 127     | In               |                         |                         |              | 4.7K           | Keyboard controller               |

| HLDA        | 85      | In               |                         |                         |              |                | CPU                               |

| Signal Name        | Pin No. | Input/<br>Output | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | Load<br>(pF) | Pull-up<br>(Ω) | Notes                              |

|--------------------|---------|------------------|-------------------------|-------------------------|--------------|----------------|------------------------------------|

| IOCHCK#            | 155     | In               |                         |                         |              | 4.7K           | ISA-bus                            |

| IOCHRDY            | 153     | I/O              | 18                      |                         | 240          | 1K             | ISA-bus                            |

| IOCS16#            | 147     | In               | _                       |                         |              | 300            | ISA-bus                            |

| IOR#               | 151     | I/O              | 18                      | -10                     | 240          | 10K            | ISA-bus                            |

| IOW#               | 152     | I/O              | 18                      | -10                     | 240          | 10K            | ISA-bus                            |

| KBRST#             | 127     | In               | _                       |                         |              | 4.7K           | Keyboard controller                |

| KEN#               | 74      | Out              | 4                       | -2                      | 40           | -              | CPU                                |

| LDEV#              | 125     | In               | _                       |                         |              | 10K            | From VL-Bus slots.                 |

| LIN                | 142     | In               | _                       |                         |              | 10K            | IPC                                |

| LOUT               | 141     | Out              | 4                       | -2                      | 30           |                | IPC                                |

| M/IO#              | 83      | I/O              | 4                       | -2                      | 200          |                | CPU and local bus developers       |

| MA0                | 8       | Out              | 18                      | -10                     | 200          |                | 24 DRAMS @ 6pF plus wiring         |

| MA1                | 12      | Out              | 18                      | -10                     | 200          |                | 24 DRAMS @ 6pF plus wiring         |

| MA2                | 14      | Out              | 18                      | -10                     | 200          |                | 24 DRAMS @ 6pF plus wiring         |

| MA3                | 17      | Out              | 18                      | -10                     | 200          |                | 24 DRAMS @ 6pF plus wiring         |

| MA4                | 24      | Out              | 18                      | -10                     | 200          |                | 24 DRAMS @ 6pF plus wiring         |

| MA5                | 28      | Out              | 18                      | -10                     | 200          |                | 24 DRAMS @ 6pF plus wiring         |

| MA6                | 30      | Out              | 18                      | -10                     | 200          |                | 24 DRAMS @ 6pF plus wiring         |

| MA7                | 34      | Out              | 18                      | -10                     | 200          |                | 24 DRAMS @ 6pF plus wiring         |

| MA8                | 36      | Out              | 18                      | -10                     | 200          |                | 24 DRAMS @ 6pF plus wiring         |

| MA9                | 39      | Out              | 18                      | -10                     | 200          | _              | 24 DRAMS @ 6pF plus wiring         |

| MA10               | 45      | Out              | 18                      | -10                     | 200          |                | 24 DRAMS @ 6pF plus wiring         |

| MA11               | 52      | Out              | 18                      | -10                     | 200          |                | 24 DRAMS @ 6pF plus wiring         |

| MASTER#            | 144     | In               | _                       |                         |              | 300            | ISA-bus                            |

| MEMCS16#           | 148     | I/O              | 18                      |                         | 240          | 300            | ISA-bus                            |

| MEMR#              | 146     | I/O              | 18                      | -10                     | 240          | 10K            | ISA-bus                            |

| MEMW#              | 145     | I/O              | 18                      | -10                     | 240          | 10K            | ISA-bus                            |

| MP0                | 60      | I/O              | 4                       | -2                      | 65           |                | CPU and DRAMs                      |

| MP1                | 61      | I/O              | 4                       | -2                      | 65           | _              | CPU and DRAMs                      |

| MP2                | 62      | I/O              | 4                       | -2                      | 65           |                | CPU and DRAMs                      |

| MP3                | 63      | I/O              | 4                       | -2                      | 65           |                | CPU and DRAMs                      |

| NC                 | 19      |                  |                         |                         |              |                | Reserved                           |

| NC                 | 99      |                  |                         |                         |              |                | Reserved                           |

| NC                 | 130     |                  |                         |                         |              | 10K            | Requires 10K pull-up               |

| NMI                | 70      | Out              | 4                       | -2                      | 30           |                | CPU                                |

| RAS0#              | 58      | Out              | 18                      | -10                     | 120          |                | 12 DRAMs @ 7pF plus wiring         |

| RAS1#              | 59      | Out              | 18                      | -10                     | 120          |                | 12 DRAMs @ 7pF plus wiring         |

| RAS2#              | 53      | Out              | 18                      | -10                     | 120          |                | 12 DRAMs @ 7pF plus wiring         |

| RAS3#              | 54      | Out              | 18                      | -10                     | 120          |                | 12 DRAMs @ 7pF plus wiring         |

| RDY#               | 73      | I/O              | 4                       | -2                      | 40           | 10k            | CPU and local bus devices          |

| ROMCS# (8042CS#)   | 129     | Out              | 4                       | -2                      | 50           |                | ROM and 8042 chip select           |

| SBHE#              | 149     | I/O              | 18                      | -10                     | 240          |                | ISA-bus                            |

| SCLK               | 117     | In               |                         |                         |              |                | Oscillator circuit                 |

| SCLKOUT (VBUFDIR#) | 125     | Out              | 9                       | -5                      | 85           |                | 84031, 84035, CPU, or VRAM buffers |

| SDEN#              | 158     | Out              | 4                       | -2                      | 30           |                | F245 and inverter                  |

| SDIR0              | 150     | Out              | 4                       | -2                      | 40           |                | F245                               |

| SDIR1              | 156     | Out              | 4                       | -2                      | 40           |                | F245                               |

| SYSRESET           | 116     | In               |                         |                         |              |                | IPC                                |

| Signal Name | Pin No. | Input/<br>Output | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | Load<br>(pF) | Pull-up<br>(Ω) | Notes                      |

|-------------|---------|------------------|-------------------------|-------------------------|--------------|----------------|----------------------------|

| W/R#        | 84      | I/O              | 4                       | -2                      | 40           |                | CPU and local bus devices  |

| XA0         | 132     | I/O              | 4                       | -2                      | 40           |                | F245                       |

| XA1         | 131     |                  |                         |                         |              |                |                            |

| XD0         | 140     | I/O              | 4                       | -2                      | 65           |                | 8042, ROM, LS245, or 84035 |

| XD1         | 139     |                  | 4                       | -2                      |              |                |                            |

| XD2         | 138     |                  | 4                       | -2                      |              |                | _                          |

| XD3         | 137     |                  | 4                       | -2                      |              |                |                            |

| XD4         | 136     |                  | 4                       | -2                      |              |                |                            |

| XD5         | 135     |                  | 4                       | -2                      |              |                |                            |

| XD6         | 134     |                  | 4                       | -2                      |              |                |                            |

| XD7         | 133     |                  | 4                       | -2                      |              |                |                            |

#### 84035 PIN OVERVIEW

The 84035 Pin Overview table below lists the pins by signal names. The detailed pin functional descriptions for the 84035 follows this overview table.

#### 84035 PIN OVERVIEW

| Signal Name              | Pin No.                           | Input/<br>Output | Driver | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | Load<br>(pF) | Pull-up<br>(Ω) | Notes                                                |

|--------------------------|-----------------------------------|------------------|--------|-------------------------|-------------------------|--------------|----------------|------------------------------------------------------|

| V <sub>CC</sub> (4 Pins) | 1, 31, 51,<br>and 81              |                  |        | —                       |                         |              |                | Battery backup circuit                               |

| GND (6 Pins)             | 16, 30, 50,<br>65, 80,<br>and 100 |                  |        |                         |                         |              | _              | System ground                                        |

| NC                       | 1                                 |                  |        |                         |                         |              |                | Reserved, do not connect                             |

| 14MX1                    | 2                                 | In               |        |                         |                         |              |                | 14.31818MHz crystal input                            |

| 14MX2                    | 3                                 | Out              | TP     | 2                       | -1                      | 50           |                | 14.31818MHz crystal output                           |

| 32KX1                    | 32                                | In               |        |                         |                         |              |                | Crystal circuit                                      |

| 32KX2                    | 33                                | Out              | TP     | 1                       | -1                      |              |                | Crystal circuit                                      |

| A8                       | 44                                | I/O              | TS     | 4                       | -1                      | 65           |                | CPU and 84031                                        |

| A9                       | 43                                | I/O              | TS     | 4                       | -1                      | 65           |                | CPU and 84031                                        |

| A17                      | 42                                | I/O              | TS     | 4                       | -1                      | 65           |                | CPU and 84031. Driven for DMA; inputs to generate SA |

| A18                      | 41                                | I/O              | TS     | 4                       | -1                      | 65           |                | CPU and 84031. Driven for DMA; inputs to generate SA |

| A19                      | 40                                | I/O              | TS     | 4                       | -1                      | 65           |                | CPU and 84031. Driven for DMA; inputs to generate SA |

| A20                      | 39                                | Out              | TS     | 4                       | -1                      | 65           |                | CPU and 84031. Driven for DMA.                       |

| A21                      | 38                                | Out              | TS     | 4                       | -1                      | 65           |                | CPU and 84031. Driven for DMA.                       |

| A22                      | 37                                | Out              | TS     | 4                       | -1                      | 65           |                | CPU and 84031. Driven for DMA.                       |

| A23                      | 36                                | Out              | TS     | 4                       | -1                      | 65           |                | CPU and 84031. Driven for DMA.                       |

| A20M#/TEST#              | 14                                | I/O              | TS     | 4                       | -1                      | 30           | 10K            | CPU                                                  |

| AEN                      | 96                                | Out              | TP     | 24                      | -3                      | 240          |                | ISA-bus                                              |

| CPURESET                 | 21                                | Out              | TP     | 4                       | -1                      | 50           |                | CPU(s)                                               |

| DACK0#                   | 76                                | Out              | TP     | 4                       | -1                      | 240          |                | ISA-bus                                              |

| DACK1#                   | 73                                | Out              | TP     | 4                       | -1                      | 240          |                | ISA-bus                                              |

| DACK2#                   | 70                                | Out              | TP     | 4                       | -1                      | 240          |                | ISA-bus                                              |

| DACK3#                   | 67                                | Out              | TP     | 4                       | -1                      | 240          |                | ISA-bus                                              |

| DACK5#                   | 62                                | Out              | TP     | 4                       | -1                      | 240          |                | ISA-bus                                              |

| DACK6#                   | 55                                | Out              | TP     | 4                       | -1                      | 240          |                | ISA-bus                                              |

| DACK7#                   | 52                                | Out              | TP     | 4                       | -1                      | 240          |                | ISA-bus                                              |

| DGNT#                    | 8                                 | Out              | TP     | 4                       | -1                      | 40           |                | 84031; one buffer direction                          |

| DREQ0                    | 77                                | In               |        |                         |                         |              | 10K            | ISA-bus                                              |

| DREQ1                    | 74                                | In               |        |                         |                         |              | 10K            | ISA-bus                                              |

| DREQ2                    | 71                                | In               |        |                         |                         |              | 10K            | ISA-bus                                              |

| DREQ3                    | 68                                | In               |        |                         |                         |              | 10K            | ISA-bus                                              |

| DREQ5                    | 63                                | In               |        |                         |                         |              | 10K            | ISA-bus                                              |

| DREQ6                    | 56                                | In               |        |                         |                         |              | 10K            | ISA-bus                                              |

| DREQ7                    | 53                                | In               |        |                         |                         |              | 10K            | ISA-bus                                              |

| FERR# (IRQ13)            | 7,83                              | In               |        |                         |                         |              |                | CPU or coprocessor logic                             |

| FLUSH#                   | 12                                | Out              | TS     | 4                       | -1                      | 30           |                | CPU                                                  |

| HLDA                     | 19                                | In               |        |                         |                         |              |                | CPU                                                  |

| HOLD                     | 20                                | Out              | TP     | 4                       | -1                      | 30           |                | CPU(s)                                               |

| IGNNE#/INTCLR            | 13                                | Out              | TP     | 4                       | -1                      | 30           |                | CPU or coprocessor logic                             |

| INTR                     | 15                                | Out              | TP     | 4                       | -1                      | 30           |                | CPU                                                  |

| IOCHRDY                  | 35                                | In               |        |                         |                         |              | 1K             | ISA-bus and 84031                                    |

| IOR#                     | 47                                | I/O              | TS     | 24                      | -3                      | 240          | 10K            | ISA-bus and 84031. Driven for DMA cycles only.       |

| Signal Name | Pin No.  | Input/<br>Output | Driver   | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | Load<br>(pF) | Pull-up<br>(Ω) | Notes                                         |

|-------------|----------|------------------|----------|-------------------------|-------------------------|--------------|----------------|-----------------------------------------------|

| IOW#        | 46       | I/O              | TS       | 24                      | -3                      | 240          | 10K            | ISA-bus and 84031. Driven for DMA cycles only |

| IRQ01       | 88       | In               |          |                         |                         |              |                | ISA-bus                                       |

| IRQ03       | 87       | In               |          |                         |                         |              |                | ISA-bus                                       |

| IRQ04       | 86       | In               |          |                         |                         |              |                | ISA-bus                                       |

| IRQ05       | 85       | In               |          |                         |                         |              |                | ISA-bus                                       |

| IRQ06       | 84       | In               | _        | _                       | _                       |              |                | ISA-bus                                       |

| IRQ07       | 83       | In               |          |                         |                         |              |                | ISA-bus                                       |

| IRQ09       | 82       | In               | _        | _                       | _                       |              |                | ISA-bus                                       |

| IRQ10       | 89       | In               | _        | _                       | _                       |              |                | ISA-bus                                       |

| IRQ11       | 90       | In               |          |                         |                         |              |                | ISA-bus                                       |

| IRQ12       | 91       | In               |          |                         |                         |              |                | ISA-bus                                       |

| IRQ14       | 92       | In               |          |                         |                         |              |                | ISA-bus                                       |

| IRQ15       | 93       | In               |          |                         |                         |              |                | ISA-bus                                       |

| LGNT#       | 5        | Out              | TP       | 4                       | -1                      | 50           |                | Local bus                                     |

| LIN         | 17       | In               |          | _                       |                         |              |                | 84031                                         |

| LOUT        | 18       | Out              | TP       | 4                       | -1                      | 30           |                | 84031                                         |

| LREQ#       | 6        | In               |          |                         |                         |              | 10K            | Local bus (pull-up if not used).              |

| MASTER#     | 34       | In               |          |                         |                         |              | 300            | ISA-bus                                       |

| MEMR#       | 49       | Out              | TS       | 24                      | -3                      | 240          | 10K            | ISA-bus and 84031. Driven for DMA cycles only |

| MEMW#       | 48       | Out              | TS       | 24                      | -3                      | 240          | 10K            | ISA-bus and 84031. Driven for DMA cycles only |

| PSRSTB#     | 10       | In               |          |                         |                         | 240          | RC             | RC circuit                                    |

| PWRGOOD     | 98       | In               |          |                         |                         |              |                | Power supply of PUC circuit                   |

| REFRESH#    | 59       | I/O              | OC       | 24                      |                         | 240          | 300            | ISA-bus                                       |

| SA0         | 79       | I/O<br>I/O       | TS       | 24                      | -3                      | 240          |                | ISA-bus and F245                              |

| SA1         | 79       | I/O<br>I/O       | TS       | 24                      | -3                      | 240          |                | ISA-bus and F245                              |

| SA2         | 78       | I/O<br>I/O       | TS       | 24                      | -3                      | 240          |                | ISA-bus and F245                              |

| SA3         | 73       | I/O<br>I/O       | TS       | 24                      | -3                      | 240          |                | ISA-bus and F245                              |

|             |          | I/O<br>I/O       |          | 24                      |                         |              |                |                                               |

| SA4<br>SA5  | 69<br>66 | I/O<br>I/O       | TS<br>TS | 24                      | -3<br>-3                | 240<br>240   |                | ISA-bus and F245<br>ISA-bus and F245          |

|             |          | I/O<br>I/O       |          | 24                      | -3                      | 240          |                |                                               |

| SA6<br>SA7  | 64       | I/O<br>I/O       | TS<br>TS | 24                      | -3                      | 240          |                | ISA-bus and F245                              |

|             | 61       |                  |          |                         |                         |              |                | ISA-bus and F245                              |

| SA17        | 60       | Out              | TS       | 24                      | -3                      | 240          |                | ISA-bus (driven from A19:17)                  |

| SA18        | 58       | Out              | TS       | 24                      | -3                      | 240          |                | ISA-bus (driven from A19:17)                  |

| SA19        | 57       | Out              | TS       | 24                      | -3                      | 240          |                | ISA-bus (driven from A19:17)                  |

| SBHE#       | 45       | Out              | TS       | 24                      | -3                      | 240          |                | ISA-bus and 84031                             |

| SCLK        | 99       | In               |          |                         |                         |              |                | Oscillator circuit                            |

| SLOW        | 4        | In               |          |                         |                         |              | 10K            | Turbo switch                                  |

| SMEMR#      | 94       | Out              | TP       | 24                      | -3                      | 240          |                | ISA-bus and 84031                             |

| SMEMR#      | 95       | Out              | TP       | 24                      | -3                      | 240          |                | ISA-bus and 84031                             |

| SPKR        | 9        | Out              | TP       | 4                       | -1                      | 30           |                | Speaker buffer                                |

| SYSRESET    | 54       | Out              | TP       | 8                       | -2                      | 50           |                | Coprocessor, 4025, and buffer to ISA-bus.     |

| TC          | 97       | Out              | TP       | 4                       | -1                      | 240          |                | ISA-bus                                       |

| XD0         | 22       | I/O              | TS       | 4                       | -1                      | 65           |                | 84031, LS244, 8042, and ROM                   |

| XD1         | 23       | I/O              | TS       | 4                       | -1                      | 65           |                | 84031, LS244, 8042, and ROM                   |

| XD2         | 24       | I/O              | TS       | 4                       | -1                      | 65           |                | 84031, LS244, 8042, and ROM                   |

| XD3         | 25       | I/O              | TS       | 4                       | -1                      | 65           |                | 84031, LS244, 8042, and ROM                   |

| XD4         | 26       | I/O              | TS       | 4                       | -1                      | 65           |                | 84031, LS244, 8042, and ROM                   |

| XD5         | 27       | I/O              | TS       | 4                       | -1                      | 65           |                | 84031, LS244, 8042, and ROM                   |

| XD6         | 28       | I/O              | TS       | 4                       | -1                      | 65           |                | 84031, LS244, 8042, and ROM                   |

| XD7         | 29       | I/O              | TS       | 4                       | -1                      | 65           |                | 84031, LS244, 8042, and ROM                   |

### 84031 PIN DESCRIPTIONS

The pin functional descriptions for the 84031 are listed below. For a pin overview by signal names, see the 84031 Pin Overview table or the pinout diagram.

#### CLOCKS AND RESET

|             |         | Input/ |                                                                                                                                                                      |

|-------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Pin No. | Output | Description                                                                                                                                                          |

| CLKIN       | 123     | In     | Clock Input (2x clock from oscillator). Used only to create CLK2OUT and SCLKOUT.                                                                                     |

| CLK2OUT     | 124     | Out    | Clock 2x Output. CLK2OUT is a buffered version of CLK2, with very low skew to SCLKOUT. It is fed back to CLK2 on the 84031 and any other logic requiring a 2x clock. |

| SCLKOUT     | 125     | Out    | 1x clock output. This is CLKIN divided by 2, and is used to drive SCLK on the 84031, 84035, as well as the CPU.                                                      |

| CLK2        | 119     | In     | 2x clock input. Used for the DRAM state machine. It is also used as a source for the ISA-bus clock divider.                                                          |

| SCLK        | 117     | In     | 1x clock input.                                                                                                                                                      |

| SYSRESET    | 116     | In     | System Reset from the 84035.                                                                                                                                         |

| BUSCLK      | 118     | Out    | ISA-Bus Clock.                                                                                                                                                       |

|             |         |        |                                                                                                                                                                      |

#### ARBITRATION

| Signal Name | Pin No. | Input/<br>Output | Description                                                                                                                                                                                                                                         |

|-------------|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HLDA        | 85      | In               | CPU Hold Acknowledge. When low, indicates that the CPU has control of the local bus. When high, either the local master, the DMA controller, or the ISA master has the bus. The 84031 generates parity for DRAM write cycles when this pin is high. |

| DGNT#       | 143     | In               | DMA controller Grant. When low, indicates that either the DMA controller or an ISA-bus master has control of the bus. The 84031 becomes the ISA slave and floats the ISA-bus commands when this signal is low.                                      |

| MASTER#     | 144     | In               | ISA-bus Master signal. Indicates that the ISA master has the bus. The 84031 uses this to determine the difference between DMA and ISA master cycles. It is also used in determining the timing for IOCHRDY generation.                              |

## CPU AND LOCAL BUS CONTROL SIGNALS

| Signal Name | Pin No. | Input/<br>Output | Description                                                                                                                                                                                |

|-------------|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|