51E D CHIPS & TECHNOLOGIES INC ■ 209877P 00055P3 488 ■ CHb ISA/486 T-49-17-01 The 4021 CHIPSet Databook Revision 1.0 ELIM l N R Y

#### **Copyright Notice**

Software Copyright © 1992, Chips and Technologies, Inc. Manual Copyright © 1992, Chips and Technologies, Inc. All Rights Reserved.

Printed in U.S.A.

51E D

#### Trademark Acknowledgement

CHIPS® and the CHIPS logotype are registered trademarks of Chips and Technologies, Inc. ISA/486™, 4021™, 4025™, SuperState V™, and Wingine™ are trademarks of Chips and Technologies, Inc.

IBM® and PC/AT® are registered trademarks and PS/2™ is a trademark of International Business Machines, Inc.

#### Disclaimer

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without express written permission of Chips and Technologies, Inc.

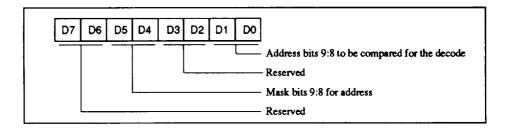

The information contained in this document is being issued in advance of the production cycle for the device(s). The parameters for the device(s) may change before final production.

Chips and Technologies, Inc. makes no representations or warranties regarding the contents of this manual. We reserve the right to revise the manual or make changes in the specifications of the product described within it at any time without notice and without obligation to notify any person of such revision or changes.

The information contained in this manual is provided for general use by our customers. Our customer should be aware that the personal computer field is the subject of many patents. Our customers should ensure that they take appropriate action so that heir use of our products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

#### Restricted Rights and Limitations

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013

Chips and Technologies, Inc. 3050 Zanker Road San Jose, California 95134 Phone: 408-434-0600

# The 4021 CHIPSet

T-49-17-01

### **Product Brief**

The 4021 two-chip CHIPSet™ with CPU is designed for use in PC/AT® systems. It is 100 percent compatible with 486DX, 486DX2, 486SX, or 386DX processors or Super386™ CPUs without any component changes. The performance to cost ratio is optimized for each CPU option. This design allows the system designer flexibility and produces an easily upgradable system.

The 4021 provides a low cost high-performance non-cache solution for 486SX systems. It offers maximum performance benefits through the use of a CHIPS® -patented page interleaving algorithm.

The 4021 CHIPSet architecture provides an alternate, faster, and efficient bus interface for speed-sensitive devices like video, disks, or networks. This is to overcome the bus speed bottlenecks such as those associated with EISA/ISA systems that can degrade system performance.

## Features

- Supports 486DX<sup>™</sup>, 486DX2<sup>™</sup>, 486SX<sup>™</sup>, and Super386<sup>™</sup> CPUs

- Supports 487 and 4167 in 486 CPU mode and 367, 3167 in 386 CPU mode.

- SuperState™ V support for the Super38605

- Burst Mode support in cache and DRAM modes •

- Zero wait state Weitek <sup>®</sup> support

- 64K, 128K, 256K, and 512K cache size

- Direct-mapped, write back operation, with pipeline allocate on read miss

- Internal tag comparator

- · Zero wait state writes

- 2-1-1-1 burst for cache reads to the 486 and 486SX

- Two-way interleaved data RAMs

- · Posted writes to DRAM

- 3-1-1-1 burst read with 486SX CPU at 20MHz with no cache

- 256K, 1M, and 4M deep DRAM support

- Support 4Mx4 DRAMs with 12/10 or 11/11 addressing

- Support for 9-bit DRAM SIMS or 36-bit DRAM SIMMs

- Page mode RAM access with option of using page interleaving

- Up to 8 banks of 36-bit DRAMs

- CAS before RAS refresh for low power consumption

- Option of using asynchronous or synchronous AT clock source

- · Classic, hidden, or disabled refresh

- Fast 12MHz AT bus support

- Dual-ported VRAM interface

- Local bus master and slave support

The 4021 CHIPSet has the following features:

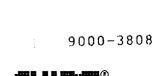

Figure 1 shows a block diagram of the 4021 CHIPSet.

CHIPS & TECHNOLOGIES INC 51E D = 2098116 0002266 198 = CHP

Figure 1. The ISA/486 4021 CHIPSet Block Diagram

T-49-17-01

# Contents

T-49-17-01

## Chapter 1 Introduction

| Introducing the 4021 CHIPSet                                                                                                                                      | 1-1                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| The Basic 486 Non-cache System (16 - 25 MHz)                                                                                                                      | 1-3                                                                                |

| 486 Cache System (25 - 33 MHz)                                                                                                                                    | 1-3                                                                                |

| Cache 386DX or Super386 System (20 - 40 MHz)                                                                                                                      | 1-3                                                                                |

| System with Advanced Device Interfaces  Local Bus Master  Local Bus Slave  System VRAM Interface  Fast AT Bus Interface                                           | 1-4<br>1-4<br>1-4                                                                  |

| Functional Description                                                                                                                                            |                                                                                    |

| Chapter 2<br>Pin Description                                                                                                                                      |                                                                                    |

| The 4021 CHIPSet Pinouts                                                                                                                                          | 2-1                                                                                |

| Signal Description Clocks Resets Arbitration CPU Control Coprocessor Control Address Cache DRAM Buffer Control Interrupts Real-Time Clock Test, Power, and Ground | 2-8<br>2-9<br>2-10<br>2-12<br>2-13<br>2-15<br>2-16<br>2-17<br>2-18<br>2-19<br>2-19 |

| 4025 Pin Description                                                                                                                                              | 2-20                                                                               |

|         | 51E     | D              |               | 5048776                                 | 00022           | 5 P B   | TLO         | ■ CHP                                   | ISA/486    |

|---------|---------|----------------|---------------|-----------------------------------------|-----------------|---------|-------------|-----------------------------------------|------------|

| Chapt   |         |                |               |                                         | CHIPZ           | &       | TECH        | NOLOGIE                                 | S INC      |

| The 4   |         |                |               | •                                       |                 |         |             |                                         |            |

|         |         |                |               | • • • • • • • • • • • • • • • • • • • • |                 |         |             |                                         |            |

| CPUI    | KESEI   | Gen            | eratio        | n                                       | • • • • • • • • | • • • • | • • • • • • | • • • • • • • • • • • • • • • • • • • • | 3-4        |

| Chapt   | er 4    |                |               |                                         |                 |         |             | T-49                                    | 9-17-01    |

| The G   |         | 120            | Fun           | ction                                   |                 |         |             | •                                       |            |

|         |         |                |               |                                         |                 |         |             |                                         |            |

|         |         |                |               | 38605 CPU                               |                 |         |             |                                         |            |

|         |         |                |               | 1 38600 CPU                             |                 |         |             |                                         |            |

| Simu    | lated K | Jenei<br>Jevho | anon<br>ard C | Sources ontroller (804)                 | <br>2)          | • • • • | • • • • • • | • • • • • • • • • • • • • • • • • • • • | 4-4<br>4-4 |

| GAT     | EA20 S  | Syste          | m Lev         | el Considerat                           | ions            |         |             |                                         | 4-5        |

|         |         | •              |               |                                         |                 |         |             |                                         |            |

| Chapt   | er 5    |                |               |                                         |                 |         |             |                                         |            |

| The S   |         | n C            | lock          | s                                       |                 |         |             |                                         |            |

| The 402 | 1 Syste | m Cl           | ocks          |                                         |                 |         |             |                                         | 5-1        |

| CPU Clo | ocks .  |                |               |                                         |                 |         |             |                                         | 5-4        |

| AT Bus  | Clocks  |                |               |                                         |                 |         |             |                                         | 5-5        |

| 14.3181 | 8 MHz   | Cloc           | ks            |                                         |                 |         |             |                                         | 5-9        |

| 32KHz ( | Clock   |                |               |                                         |                 |         |             |                                         | 5-10       |

| Clock   | c Speed | i Che          | ck            | • • • • • • • • • • • • •               | • • • • • • • • |         |             | • • • • • • • • • • • • • • • • • • • • | 5-10       |

| Chapt   | er 6    |                |               |                                         |                 |         |             |                                         |            |

| The D   |         | Col            | ntro          | iler                                    |                 |         |             |                                         |            |

| Page Mo | nde     |                |               | • • • • • • • • • • •                   |                 |         |             |                                         | 6-1        |

|         |         |                |               |                                         |                 |         |             |                                         |            |

|         |         |                |               |                                         |                 |         |             |                                         |            |

|         |         |                |               |                                         |                 |         |             |                                         |            |

|         |         |                |               | lodes                                   |                 |         |             |                                         |            |

|         |         |                |               |                                         |                 |         |             |                                         |            |

|         |         |                |               |                                         |                 |         |             |                                         |            |

|         |         |                |               | ons                                     |                 |         |             |                                         |            |

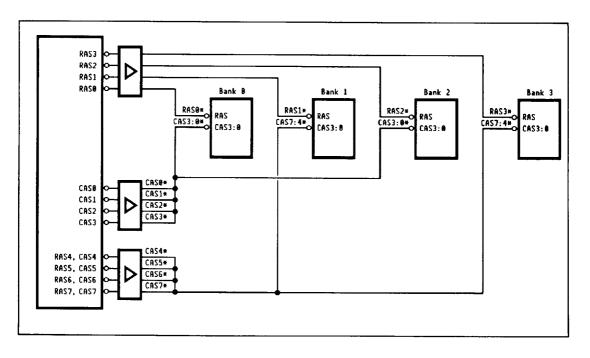

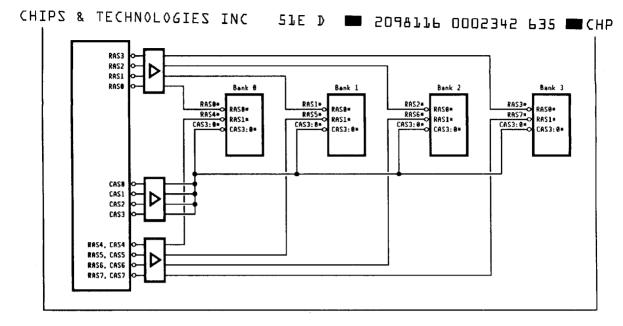

| 4 RA    | S Mod   | e              |               |                                         |                 |         |             |                                         | 6-11       |

| 8 RA    | S Mod   | е              |               |                                         |                 |         |             |                                         | 6-12       |

| DRAM    | Block I | Progr          | ammi          | ng                                      |                 |         |             |                                         | 6-15       |

| DRAM A  | Addres  | s Mu           | xing          | • • • • • • • • • • • • • • • • • • • • |                 |         |             |                                         | 6-16       |

| DRAM (  | Cycles  | for D          | MA/!          | MASTER Cyc                              | les             |         |             |                                         | 6-17       |

| Chapter 7                                                                                                                              | T-49-17-01                           |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 4021 Cache Operation                                                                                                                   | ,                                    |

| 4021 Cache Architecture and Terminology Cache Read Hit Cycle Cache Write Hit Cycle Cache Read Miss Cycle Conditions Cache Write Miss   | 7-2<br>7-4<br>7-5<br>7-6             |

| Cache Mode and Initialization                                                                                                          | 7-13                                 |

| Cacheability and Write Protection  KEN* Generation  DMA/AT Master Access                                                               | 7-16                                 |

| Cache Coherency                                                                                                                        |                                      |

| SRAM Requirements Cache Critical Paths 4021 Write Buffers Castout Write Buffer Tag and Data SRAM Testing Data SRAM Testing Tag Testing | 7-19<br>7-22<br>7-23<br>7-23<br>7-24 |

| Chapter 8 System Bus Arbitration                                                                                                       |                                      |

| Pin Multiplexing                                                                                                                       | 8-3                                  |

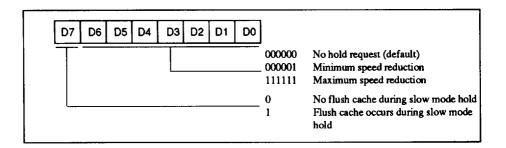

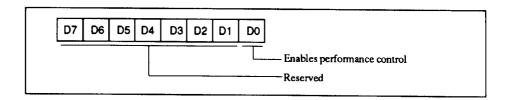

| Performance Control                                                                                                                    | 8-5                                  |

| Refresh Classic AT Refresh AT Hidden Refresh Disabled AT Refresh                                                                       | 8-6<br>8-6                           |

CHIPS & TECHNOLOGIES INC 51E D ■ 2098116 0002270 619 ■ CHP

| Chapter 9                                                                    | T-49-17-01 |

|------------------------------------------------------------------------------|------------|

| The ISA Bus                                                                  | •          |

| General ISA Bus Support  I/O Accesses to Internal 4021  XDIR Decoding        | 9-3        |

| Configuration Registers Affecting the ISA Bus                                | 9-6        |

| DMA/AT Master Access                                                         | 9-7        |

| Coprocessor Support                                                          | 9-14       |

| Weitek 3167 and 4167 Numeric Processors                                      | 9-15       |

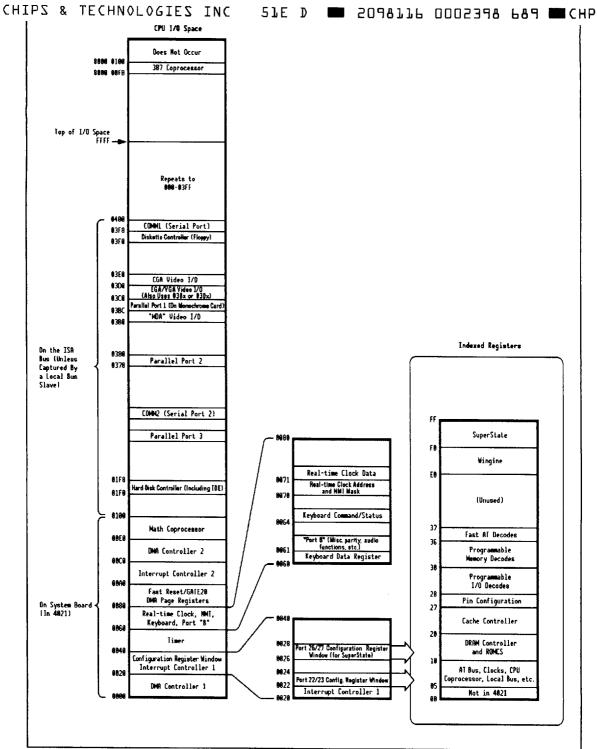

| Chapter 10 Address Mapping  I/O Address Mapping                              | 10-1       |

| 8042CS* Some Fixed Decodes Programmable I/O Ranges Programmable Chip Selects |            |

| Memory Address Mapping Shadow RAM ROMCS*                                     |            |

| Programmable Memory Ranges                                                   | 10-10      |

| Chapter 11<br>SuperState V <sup>TM</sup>                                     |            |

| SuperState V Memory Space                                                    | 11-1       |

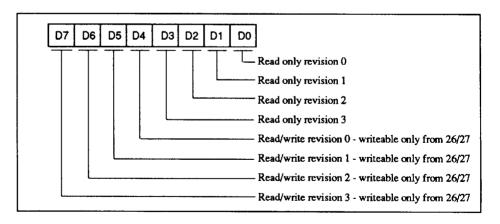

| SuperState V Configuration Register Access (Port 26/27)                      | 11-3       |

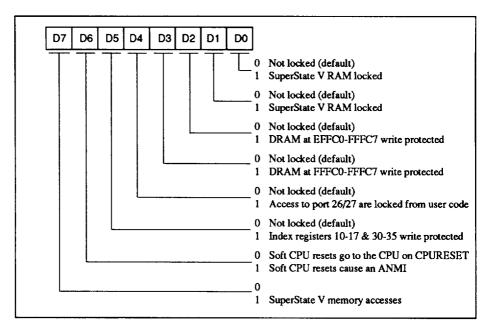

| SuperState V Locking                                                         | 11-4       |

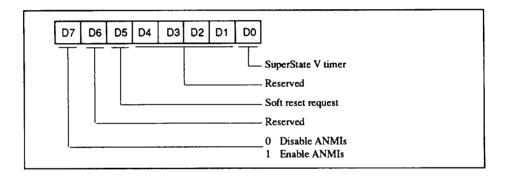

| SuperState V Timer                                                           | 11-5       |

| ANMI Register                                                                | 11-6       |

| SuperState V Soft Reset Redirection                                          | 11-6       |

T-49-17-01

# Chapter 12 Advanced Device Interface

| FASTAT Interface                         |

|------------------------------------------|

| Using FASTAT With Existing ISA Bus Cards |

| Fast ISA Bus Clock                       |

| BUSCLK 12-3                              |

| FBUSCLK 12-3                             |

| Zero Wait State Input/Output             |

| DMA and ISA Master Cycles                |

| FASTAT Programmable Registers            |

| Board Level Implementation               |

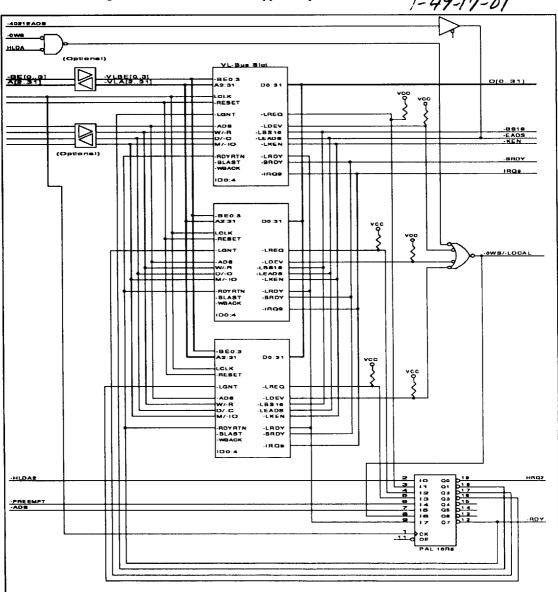

| Local Bus Support                        |

| Local Masters                            |

| Local Slaves                             |

| VRAM interface                           |

| Wingine™ Concept                         |

| 4021 Implementation                      |

## Chapter 13 Configuration Registers

**Index Register 11**

**Index Register 12**

Index Register 18

| Index Register 0 | 5  |    |   |  | <br> |  | <br> |  |  |  |  |      |  |  |  |  | <br> |  |     |  | 13-9  |

|------------------|----|----|---|--|------|--|------|--|--|--|--|------|--|--|--|--|------|--|-----|--|-------|

| Index Register 0 | 6  |    |   |  | <br> |  | <br> |  |  |  |  |      |  |  |  |  | <br> |  |     |  | 13-10 |

| Index Register 0 | 7  |    |   |  | <br> |  | <br> |  |  |  |  |      |  |  |  |  | <br> |  |     |  | 13-11 |

| Index Register 0 | 8  |    |   |  | <br> |  | <br> |  |  |  |  |      |  |  |  |  | <br> |  |     |  | 13-12 |

| Index Register 0 | 9  |    |   |  | <br> |  | <br> |  |  |  |  |      |  |  |  |  | <br> |  |     |  | 13-13 |

| Index Register 0 | Α  |    |   |  |      |  | <br> |  |  |  |  | <br> |  |  |  |  |      |  |     |  | 13-14 |

| Index Register 0 | В  |    |   |  |      |  | <br> |  |  |  |  |      |  |  |  |  |      |  | • • |  | 13-15 |

| Index Register 0 | C  |    |   |  |      |  |      |  |  |  |  | <br> |  |  |  |  |      |  |     |  | 13-16 |

| Index Register 0 | D  |    |   |  |      |  |      |  |  |  |  | <br> |  |  |  |  |      |  |     |  | 13-17 |

| Index Register 0 | E- | 0F | • |  |      |  | <br> |  |  |  |  |      |  |  |  |  |      |  |     |  | 13-17 |

Index Register 13

13-22

Index Registers 14 through 17

13-23

Index Register 19

13-25

Index Register 1A

13-26

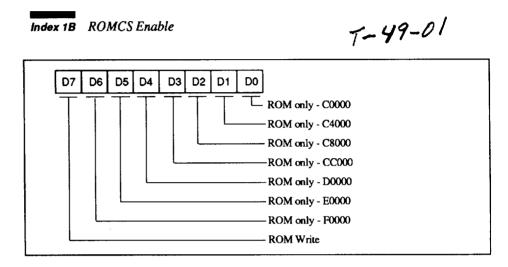

Index Register 1B

13-27

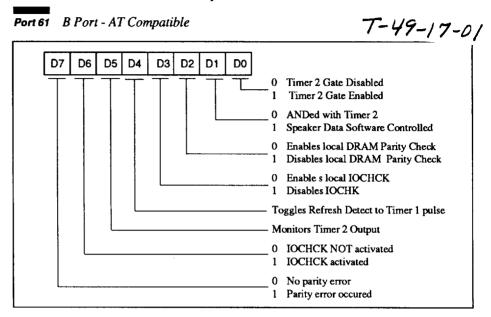

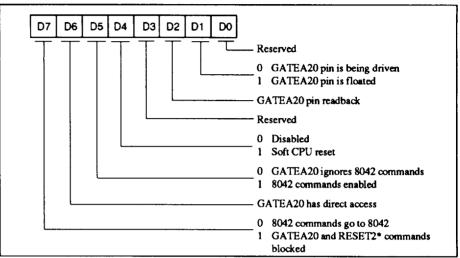

I/O Port Address 61

13-3

I/O Port Addresses 70-8F

13-4

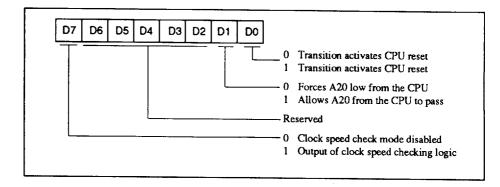

I/O Port Address 92

13-5

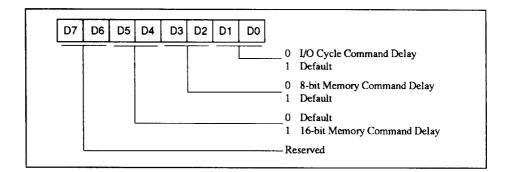

I/O Port Addresses A0-FF

13-6

| 51E D 🖿 2098116 0002272 491 🖿 CHP             | ISA/486 |

|-----------------------------------------------|---------|

| Index Register 1C-1F CHIPS & TECHNOLOGIES INC | . 13-27 |

| Index Register 20                             | 13-28   |

|                                               | 13-29   |

| index Register 22                             | 13-30   |

| Index Register 23                             | 13-31   |

| Index Register 24                             |         |

| Index Register 25 and 26                      |         |

| Index Register 27                             |         |

| Index Register 28                             |         |

| Index Register 29                             |         |

| Index Register 2A                             |         |

| Index Register 2B                             |         |

| Index Register 2C through 2F                  |         |

| Index Register 30                             |         |

|                                               |         |

| Index Register 32                             |         |

| Index Register 36                             |         |

| Index Register E0                             | 12 40   |

| Index Register E2                             | 13-40   |

| Index Register E3                             | 13_42   |

| Index Register E4                             |         |

| Index Register E5                             |         |

| Index Register F0                             |         |

| Index Register F1                             |         |

| Index Register F2                             |         |

| Index Register F3                             | . 13-47 |

| Index Register F4                             | . 13-47 |

| Index Registers F5 through F7                 | . 13-48 |

| Index Register F8                             | . 13-48 |

| Index Register F9 through FB                  | . 13-48 |

| Chapter 14                                    |         |

| AC/DC Characteristics                         |         |

|                                               |         |

| General Characteristics                       |         |

| DC Characteristics                            | -       |

| 4021 AC Characteristics                       | . 14-4  |

| 4025 AC Characteristics                       | . 14-9  |

|                                               | · = · • |

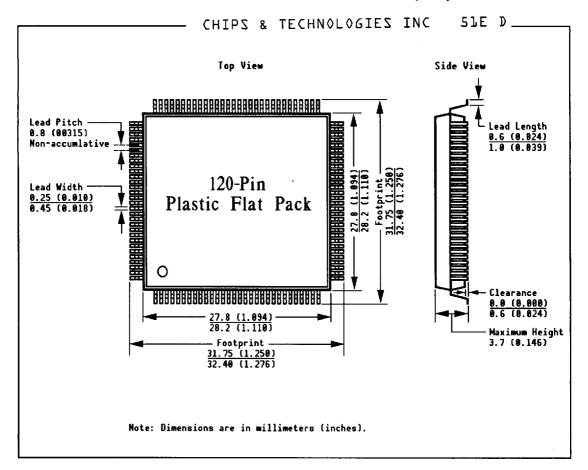

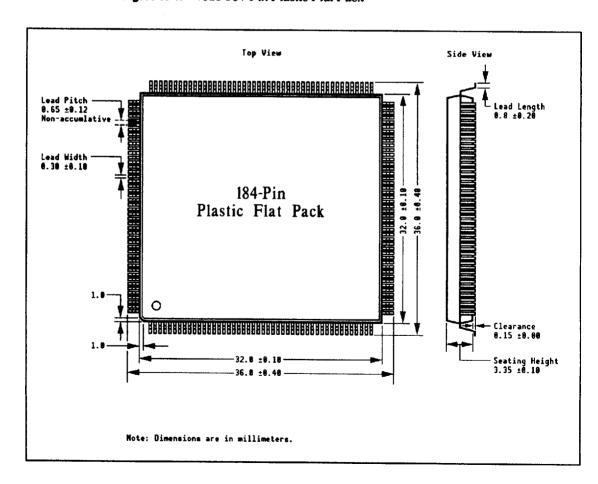

Chapter 15 Mechanical Specifications

Regional Sales Offices

**■** Contents

| List of Fig | ures CHIPS & TECHNOLOGIES INC            |

|-------------|------------------------------------------|

| Figure 1-1. | System Block Diagram                     |

| Figure 1-2. | System Block Diagram                     |

| Figure 1-3. | 4025 Block Diagram1-6                    |

|             |                                          |

| Figure 2-1. | 4021 Pinout (Top View)2-1                |

| Figure 2-2. | 4025 Pinout (Top View)2-2                |

| Figure 2-3. | The 4021 Schematic Symbols               |

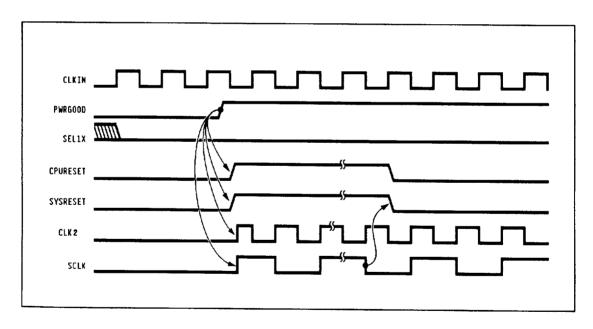

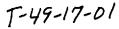

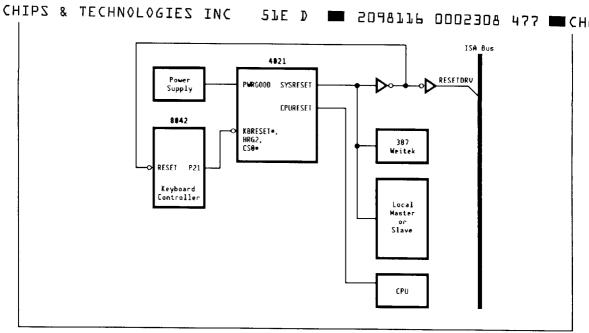

| Figure 3-1. | Generating CPURESET and SYSRESET         |

| Figure 3-2. | PWRGOOD Reset                            |

| Figure 3-3. | System Level RESET Connections           |

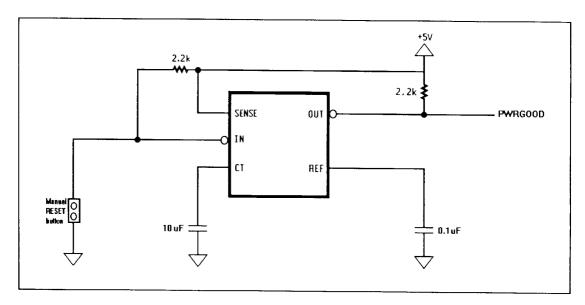

| Figure 3-4. | Example of PWRGOOD Reset Circuit         |

|             |                                          |

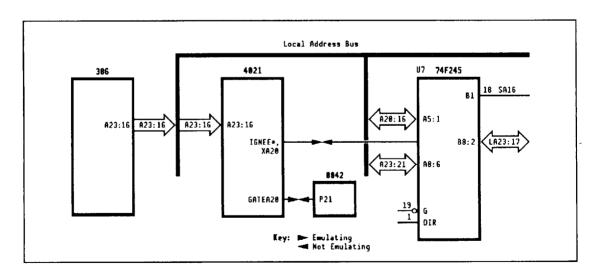

| Figure 4-1. | 486 CPU GATEA20 Connection4-2            |

| Figure 4-2. | Super386 CPU GATEA20 Connection          |

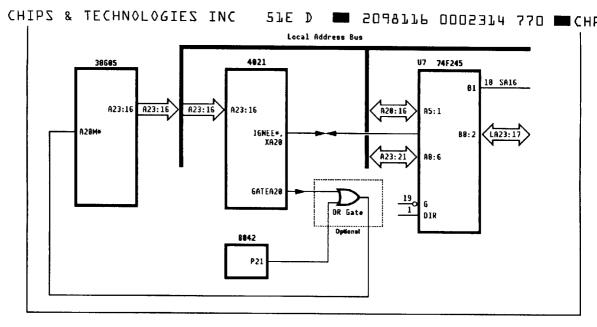

| Figure 4-3. | 38605 CPU GATEA20 Connection             |

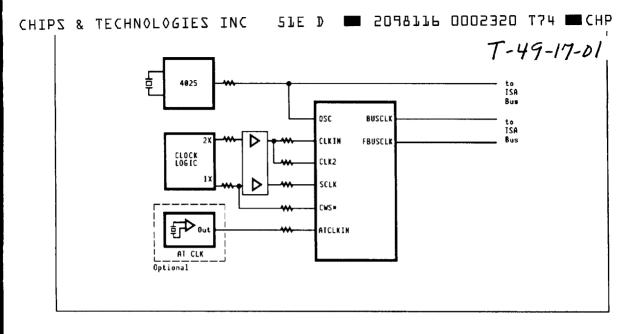

| Figure 5-1. | 2x Clock Connection                      |

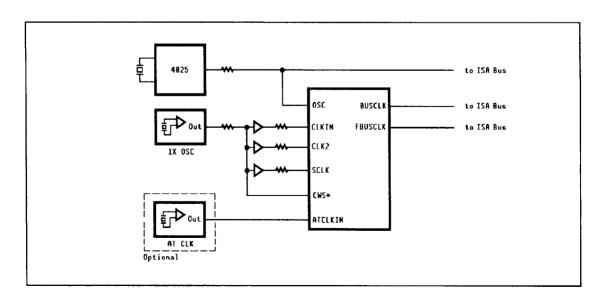

| Figure 5-2. | 1x Clock Connection                      |

| 1.6400 2.   | The clock connection                     |

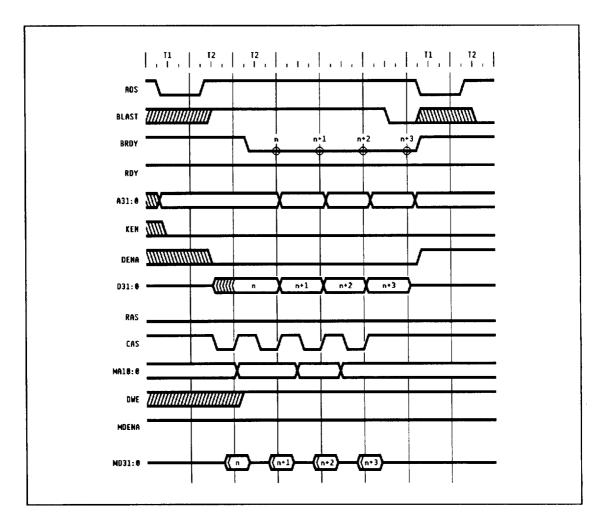

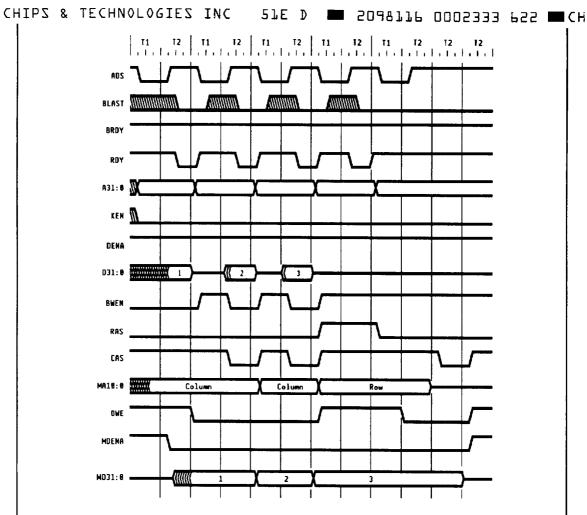

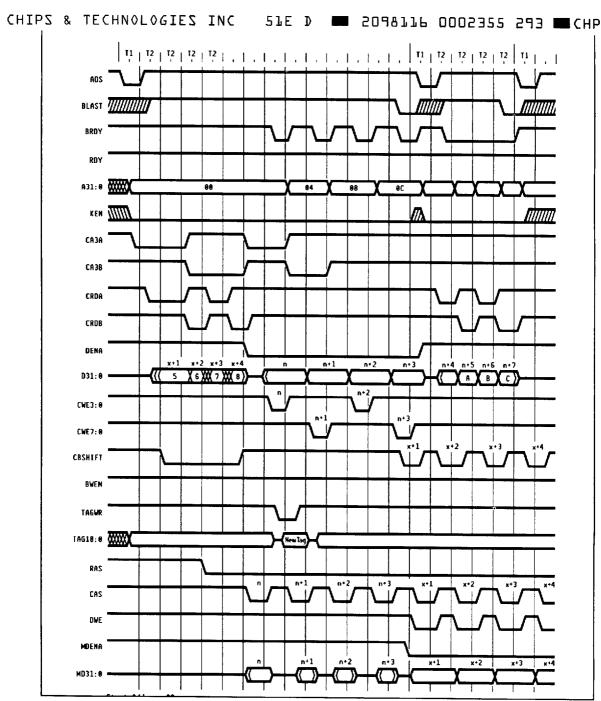

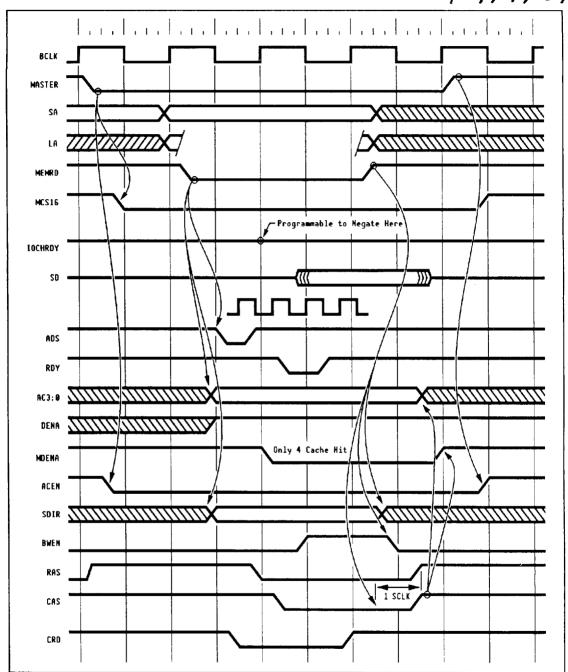

| Figure 6-1. | DRAM - Page Hit Read Burst               |

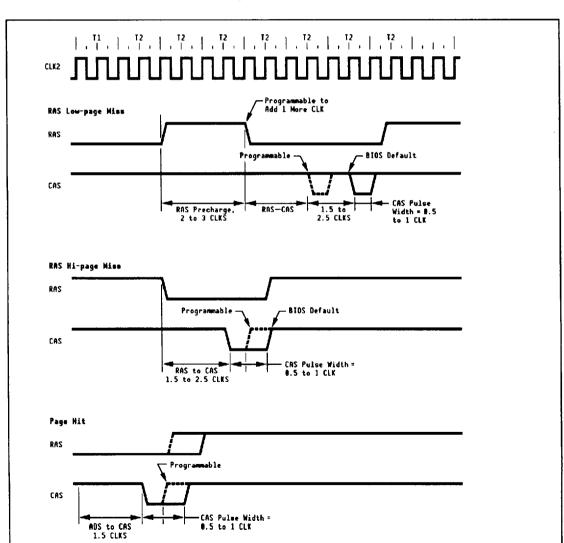

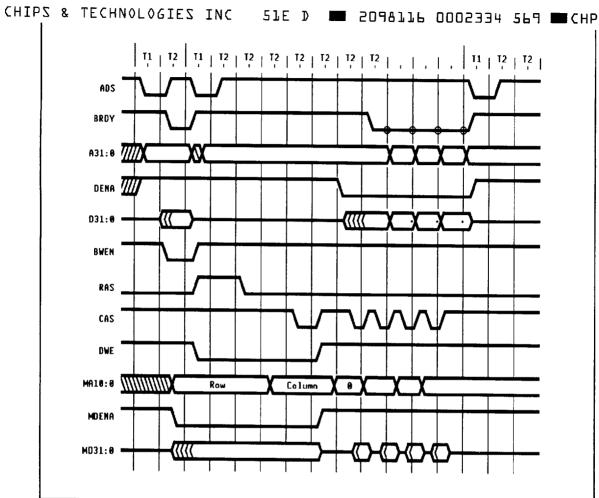

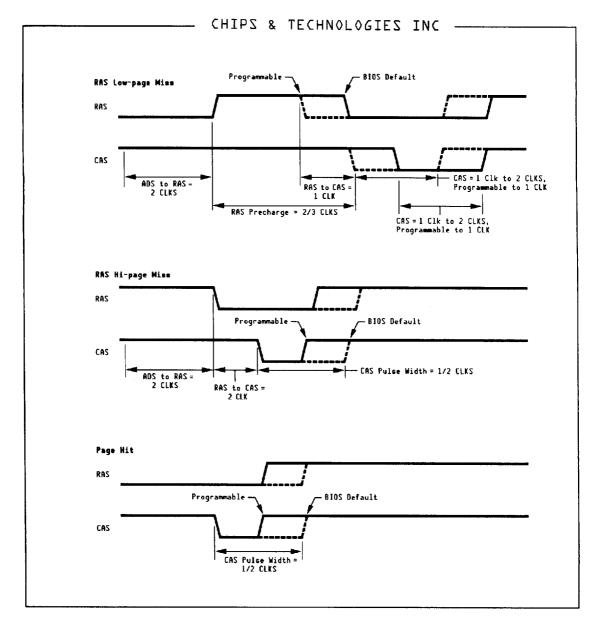

| Figure 6-2. | DRAM - Programmable Options6-4           |

| Figure 6-3. | Posted Writes                            |

| Figure 6-4. | DRAM Write Miss — Read Hit Burst6-7      |

| Figure 6-5. | DRAM Cache Modes — RAS/Cache Relation6-9 |

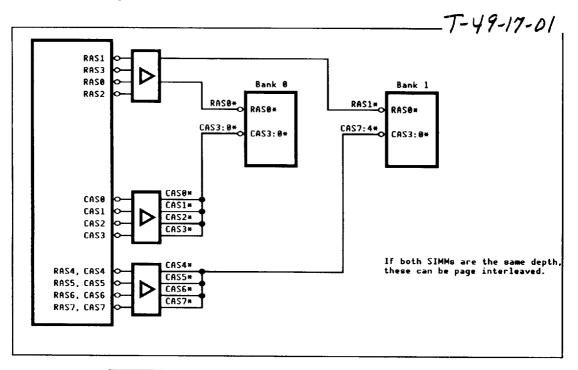

| Figure 6-6. | 4 RAS Mode with Two Banks6-14            |

| Figure 6-7. | 4 RAS Mode with Four Banks6-14           |

| Figure 6-8. | 8 RAS Mode with Eight Banks              |

| Figure 7-1. | Cache Architecture                       |

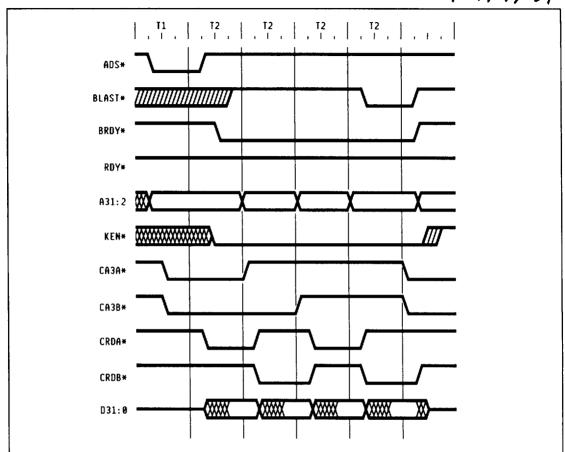

| Figure 7-2. | Cache Read Hit7-3                        |

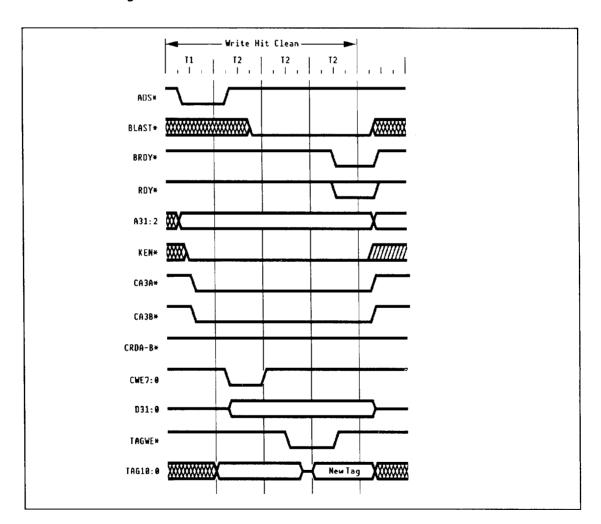

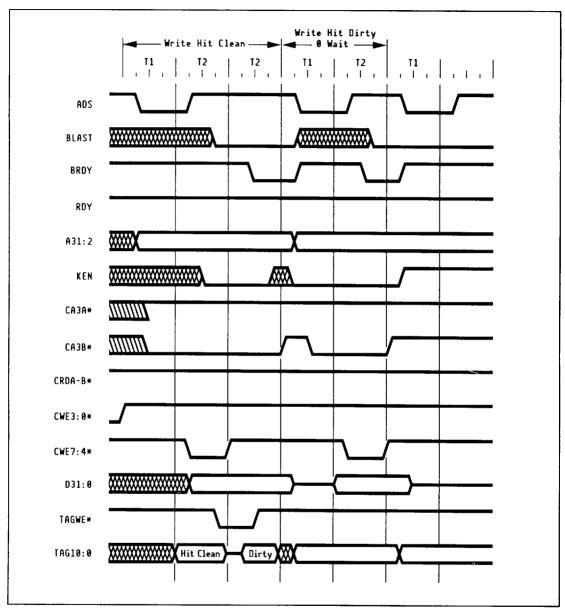

| Figure 7-3. | Write Hit Clean7-7                       |

| Figure 7-4. | Write Hit Dirty7-8                       |

| Figure 7-5. | Write Through Cache Write Hit,           |

| _           | Cache Write Miss and Read Hit7-9         |

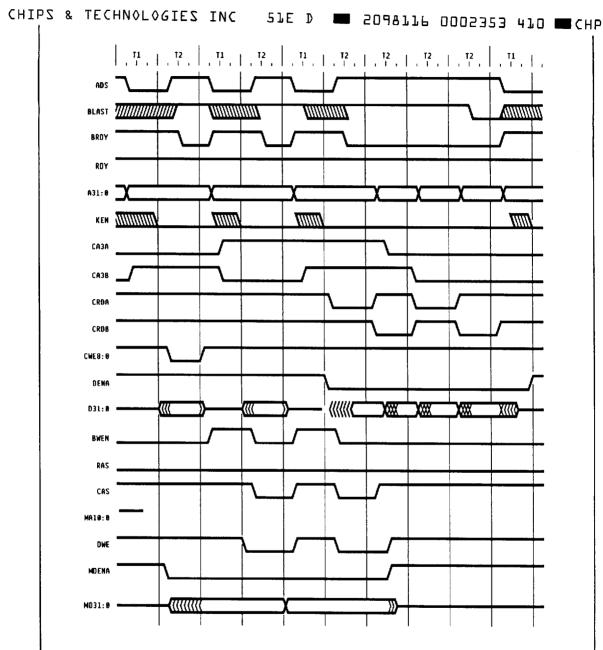

| Figure 7-6. | Read Burst Line File7-10                 |

| Figure 7-7. | Castout — Read Hit7-11                   |

| Figure 7-8. | Cache Write Miss — Cache Read Miss7-12   |

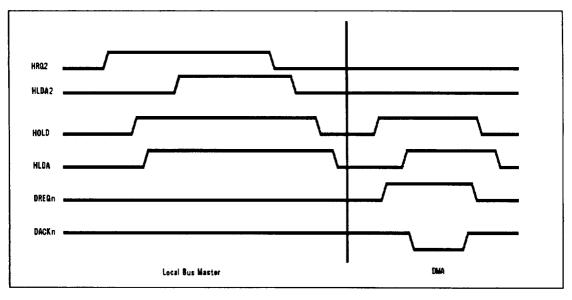

| Figure 8-1. | Bus Arbitration8-1                       |

| Figure 8-2. | DRQ and DACK System Interface8-1         |

| 3           |                                          |

| 2 PF D ■     | ■ 504877P 0005534 5P4 ■ CH5                            | ISA/486                   |

|--------------|--------------------------------------------------------|---------------------------|

| <b>-</b>     | DMA 8-bit CPU for 16-bit AT Cycle                      | 9-2                       |

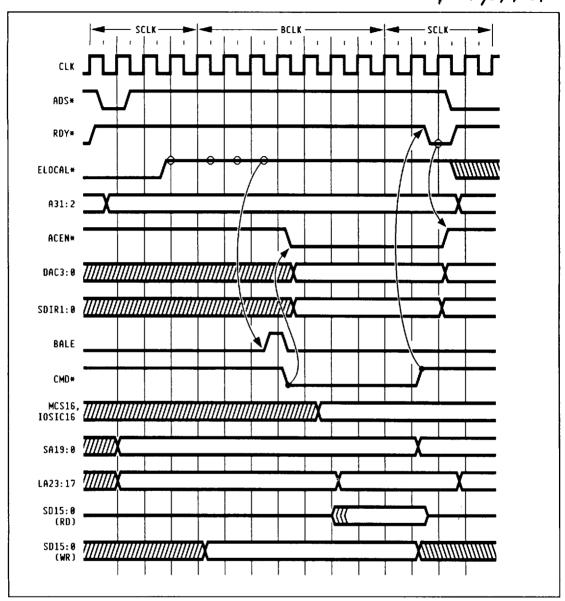

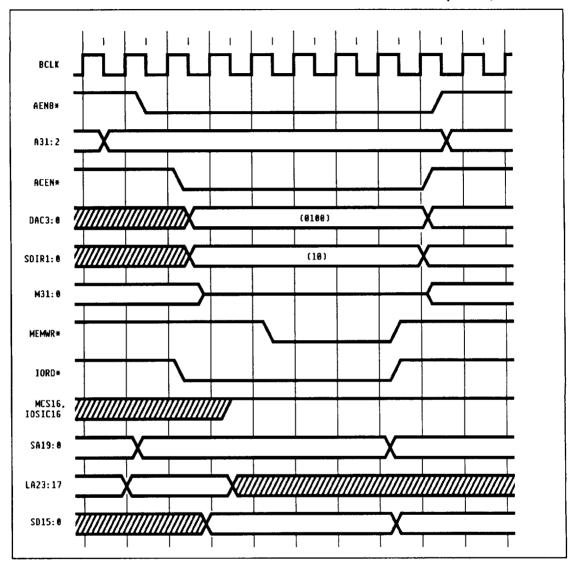

| Figure 9-1.  | DMA 8-bit CPU for 16-bit AT Cycle                      |                           |

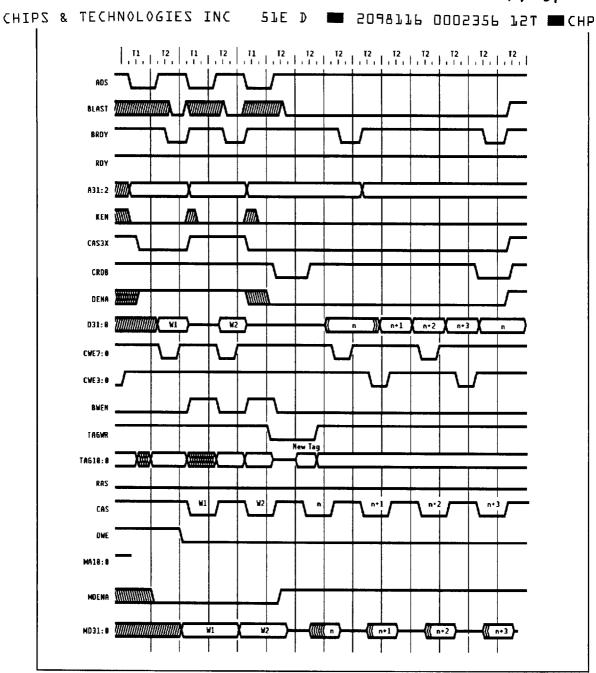

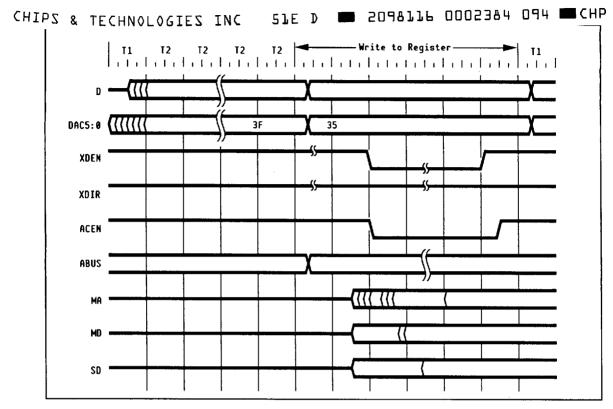

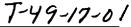

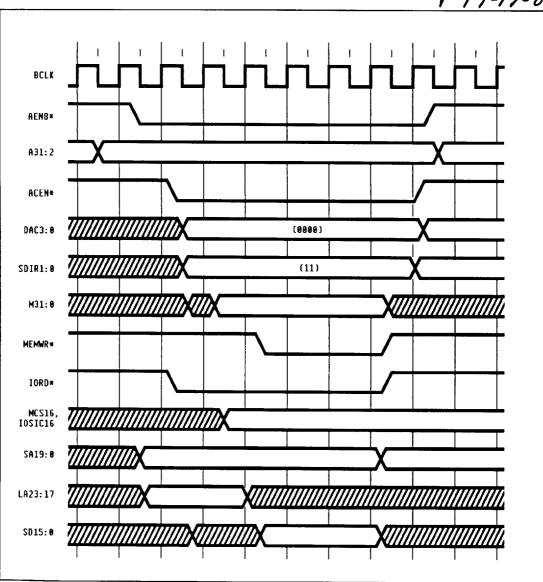

| Figure 9-2.  | CHIP Register Read to DRAM Read                        |                           |

| Figure 9-3.  | CHIP Register Write                                    |                           |

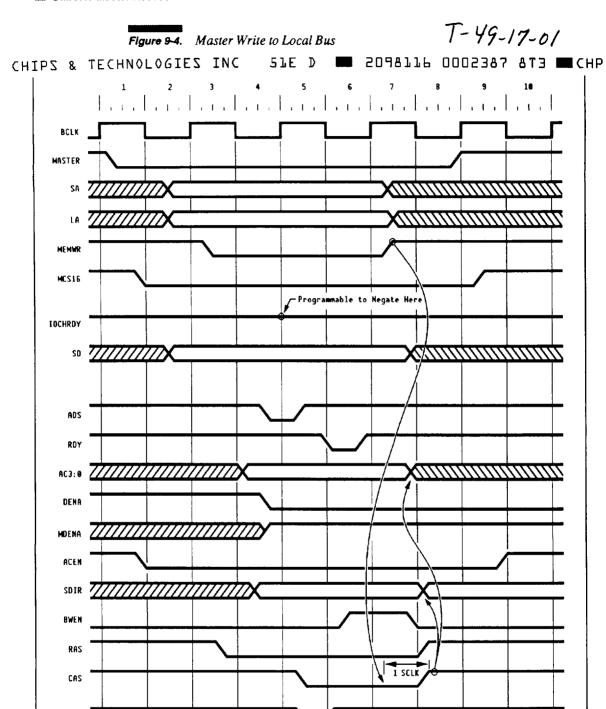

| Figure 9-4.  | Master Write to Local Bus                              |                           |

| Figure 9-5.  | Master Read from Local Bus                             |                           |

| Figure 9-6.  | 8-bit DMA Read from System Memory                      |                           |

| Figure 9-7.  | 8-bit DMA Write to System Memory                       |                           |

| Figure 9-8.  | 8-bit DMA for 16-bit AT Cycle                          |                           |

| Figure 9-9.  | 8-bit DMA Write to 8-bit AT Memory                     | 9-13                      |

| Figure 10-1. | I/O and Configuration Register Map                     | 10-3                      |

| Figure 10-1. |                                                        |                           |

| rigue 10-2.  | Memory Mapping Programming Options                     | 10 0                      |

| Figure 12-1. | ISA/486 VESA Support Implementation                    |                           |

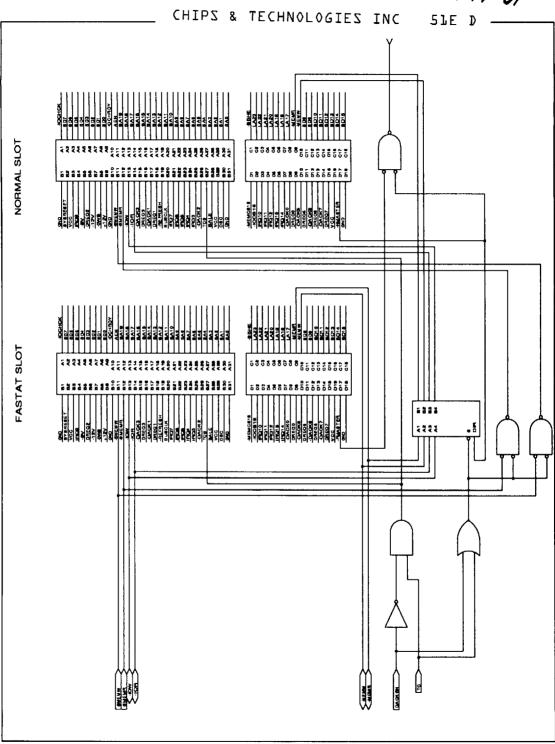

| Figure 12-2. | FASTAT Bus Board Level Implementation                  | 12-8                      |

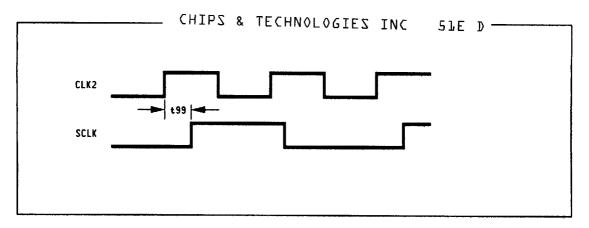

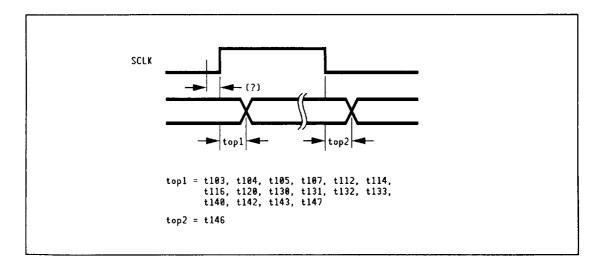

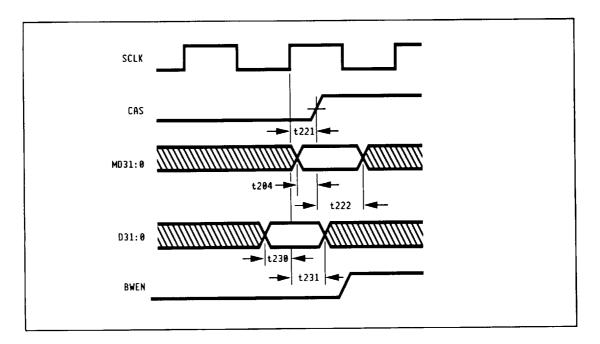

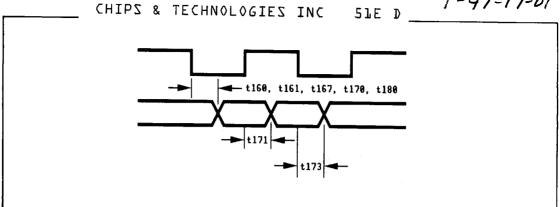

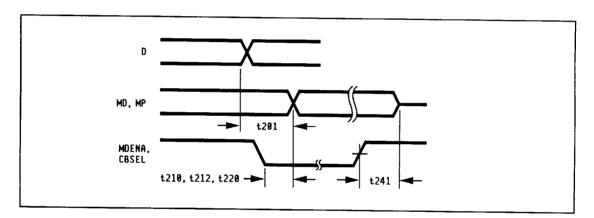

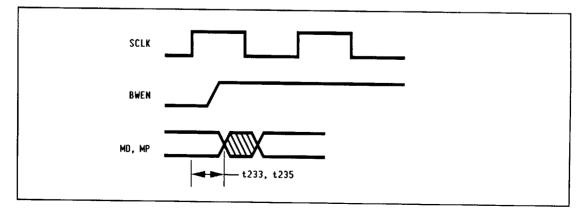

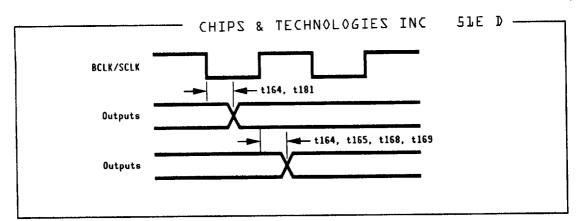

| Figure 14-1. | CLK2 to SCLK 4021 Timing                               | 14-5                      |

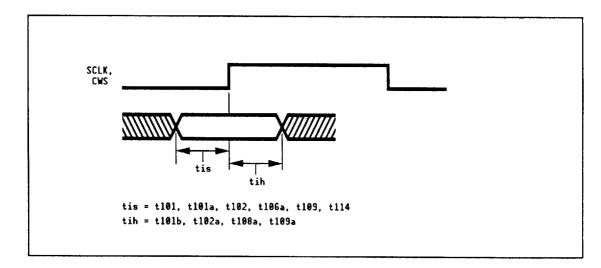

| Figure 14-2. | 4021 Input Timing                                      |                           |

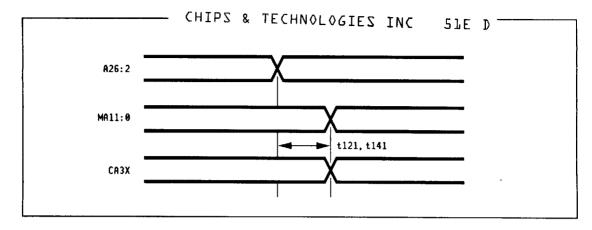

| Figure 14-4. | 4021 Timing for Local Bus Address to MA Bus Delay, CA3 | x .14-7                   |

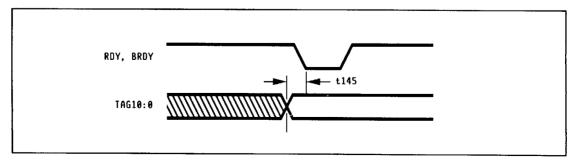

| Figure 14-5. | 4021 Timing for TAG Data to RDY/BRDY Setup             |                           |

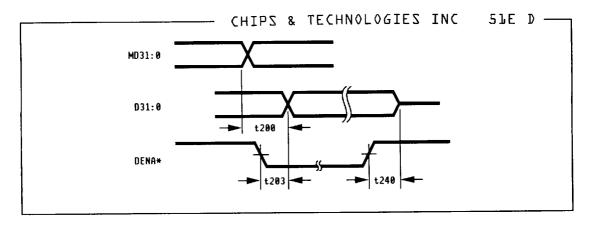

| Figure 14-6. | 4025 Output Timing                                     |                           |

| Figure 14-7. | 4025 Input Timing                                      |                           |

| Figure 14-8. | AT Bus Control Signal Setup and Hold                   |                           |

| Figure 14-9. | 4025 Output Timing                                     |                           |

|              | 4. 4025 Output Timing                                  |                           |

|              | . AT Bus Control Signal Delays                         |                           |

| 14-11        | . At bus control signal bolays                         | , , , 1- <del>7</del> -12 |

| Figure 15-1. | 4021 184-Pin Plastic Flat Pack                         | 15-1                      |

| Figure 15-2  | 4025 120-Pin Flat Pack                                 | 15-2                      |

CHIPS & TECHNOLOGIES INC

Contents

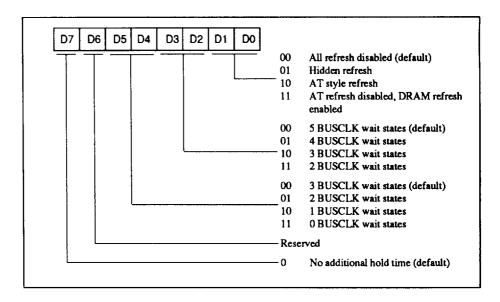

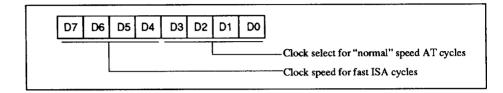

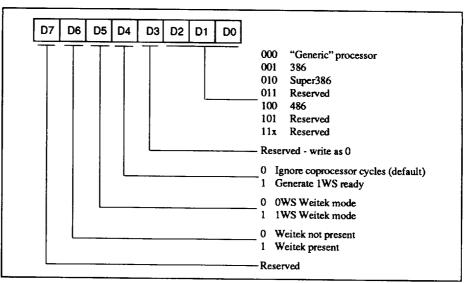

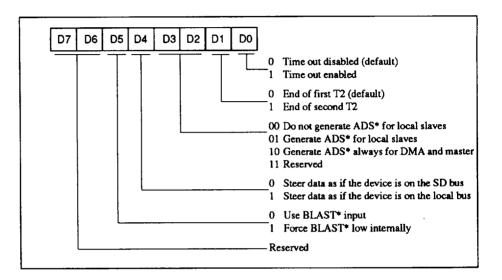

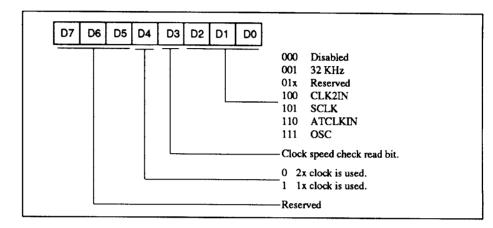

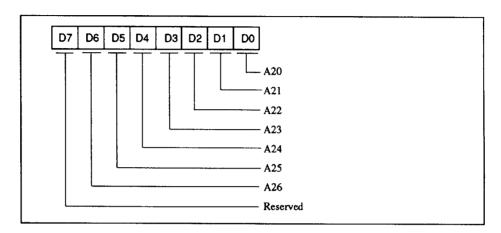

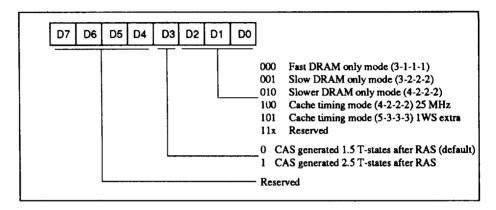

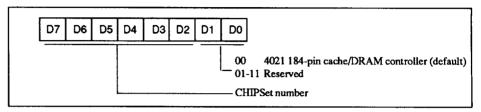

#### CHIPS & TECHNOLOGIES INC **List of Registers** Port 00-60 I/O Port Addresses 00-60 .... T-49-17-01 B Port - AT Compatible Port 61 Port 70-8F Fast CPU Reset and GATEA20 ......13-5 Port 92 AT Bus Command Delay ......13-9 Index 05 Index 06 AT Refresh, Wait State, and Address Hold ......13-10 Index 07 Index 08 Performance Control ......13-12 Performance Control Enable ......13-13 Index 09 Index 0A Index OB CPU and Coprocessor ......13-15 Index 0C Index 0D Index 10 DRAM Timing ......13-18 Index 11 DRAM Setup ......13-20 Index 12 DRAM Configuration Blocks 0 and 1 ......13-21 Index 13 Index 18 Index 19 Index 1A Index 1B Index 20 Index 21 Index 22 Data Port Tag Testing Bits 0-7 ......13-31 Index 23 Data Port Tag Testing Bits 8-10 ......13-31 Index 24 Index 27 Pin Configuration ......13-32 Index 28

Wingine VRAM Timing Mode Register ......13-44

Index 29

Index 2A Index 2B

Index 30 Index 31

Index 32

Index 36 Index E2

Index E3

Index E4

Index E5

Index F0

Index F1

Index F2

Index F8

| Ь | 000557P   | 037  | CHP   | ISA/486 |

|---|-----------|------|-------|---------|

| 9 | R TETHNOI | ٥٤٦٣ | S TNC |         |

| List of Tab | les CHIPS & TECHNOLOGIES INC                              |

|-------------|-----------------------------------------------------------|

| Table 2-1.  | 4021 Pin Assignments                                      |

| Table 2-2.  | 4021 Pin Assignments                                      |

| Table 3-1.  | SHUTDOWN Bus Cycle Encoding3-6                            |

| Table 4-1.  | A20 Generation Sources4-3                                 |

| Table 4-2.  | Keyboard Controller Commands4-5                           |

| Table 5-1.  | CPU Clocks                                                |

| Table 5-2.  | AT Bus Clocks5-2                                          |

| Table 5-3.  | 14MHz Clock5-2                                            |

| Table 5-4.  | 32KHz Clock5-2                                            |

| Table 5-5.  | ISA Clock Frequencies for CLKIN with a 2x Clock Source5-6 |

| Table 5-6.  | ISA Clock Frequencies for CLKIN with a 1x Clock Source5-6 |

| Table 5-7.  | ISA Clock Frequencies for CLKIN with                      |

|             | External ATCLK Source5-7                                  |

| Table 5-8.  | ISA Clock Programming Recommendations                     |

|             | (FASTAT Not Implemented)5-8                               |

| Table 5-9.  | ISA Clock Programming Recommendations                     |

|             | (FASTAT Implemented)                                      |

| Table 5-10. | Clock Speed Check Timing Period5-10                       |

| Table 6-1.  | DRAM Timing Modes6-2                                      |

| Table 6-2.  | Non-Cache Modes and DRAM Timing Parameters 6-8            |

| Table 6-3.  | Non-Cache Modes and DRAM Timing Parameters6-10            |

| Table 6-4.  | 4 RAS Mode RAS and CAS Usage6-12                          |

| Table 6-5.  | 8 RAS Mode RAS and CAS Usage6-13                          |

| Table 6-6.  | DRAM Block Starting Address                               |

| Table 6-7.  | Address Multiplexing6-17                                  |

| Table 7-1.  | Data SRAM Configurations7-19                              |

| Table 7-2.  | Tag SRAM Configurations7-20                               |

| Table 7-3.  | 486 CPU Data and Tag SRAM Speed Requirements              |

| Table 7-4.  | 386 CPU Data and Tag SRAM Speed Requirements              |

| Table 7-5.  | Tag Comparison Table7-22                                  |

| Table 7-6.  | Cache Test Window Location                                |

| Table 7-7.  | 512K Cache Test Mode Mapping When in the Lower MB7-24     |

| Table 8-1.  | Arbitration Signals for Each Master8-2                    |

| Table 8-2.  | Indication of Current Master8-2                           |

| Table 8-3.  | Address Source for Master Refresh8-6                      |

| Table 9-1.  | Configuration Registers Affecting the ISA Bus9-6          |

| Table 9-2.  | Coprocessors Supported for each CPU9-14                   |

| ISA/486 | 5le D 📟      | I 2098]]6 0002277 T73 ■ CHP                         | Contents I |

|---------|--------------|-----------------------------------------------------|------------|

|         | Table 10-1.  | I/O Fixed Decodes for Local Bus and FASTAT Function | ons10-4    |

|         | Table 10-2.  | Programmable I/O Decode Compare and Mask Bits       | 10-5       |

|         | Table 10-3.  | Fixed Memory Decodes                                | 10-9       |

|         | Table 10-4.  | Programmable Memory Range Options                   | 10-10      |

|         | Table 10-5.  | Programmable Memory Range Configuration Register    | s10-12     |

|         | Table 13-1.  | 4021 I/O Port Summary T-49-17-01                    | / 13-1     |

|         | Table 13-2.  | I/O Port Addresses A0-FF                            | 13-6       |

|         | Table 13-3.  | 4021 Index Register Summary                         |            |

|         | Table 14-1.  | Recommended Operating Conditions                    | 14-1       |

|         | Table 14-2.  | Maximum Tolerated Conditions                        |            |

|         | Table 14-3.  | Capacitance                                         |            |

|         | Table 14-4.  | DC Characteristics for TTL Signals                  | 14-3       |

|         | Table 14-5.  | DC Characteristics for CMOS Signals                 |            |

|         | Table 14-6.  | CPU Interface Timing                                | 14-4       |

|         | Table 14-7.  | DRAM Timing                                         | 14-6       |

|         | Table 14-8.  | Cache Timing                                        | 14-7       |

|         | Table 14-9.  | Tag Timing                                          | 14-7       |

|         | Table 14-10. | AT Bus Timing                                       | 14-8       |

|         |              | Miscellaneous Timing                                |            |

|         | Table 14-12. | Data Buffer Timing                                  | 14-9       |

CHIPS & TECHNOLOGIES INC

Contents

CHAPTER 1

Introduction T-49-17-b/

# **Introducing The 4021 CHIPSet**

The 4021 CHIPSet supports a diverse system architecture from a low cost 16MHz 486SX to the high-performance cache architecture of a 33 MHz 486DX or 40 MHz 386DX with the best performance and reliability. It provides the option of using the Fast AT bus or the Advanced Device Interface, which is independent of the system CPU.

The 4021 CHIPSet allows for a modular design for use with the 486SX CPU and the high-performance 386DX or 486DX CPU markets. Four basic systems are described in this section:

- Basic 486 non-cache system (16-25 MHz)

- 486 cache system (25-33 MHz)

- Cache 386DX or Super386 system (40 MHz)

- System with Advanced Device Interface

Figure 1-1 shows a system block diagram of the 4021 CHIPSet. Each of the dotted blocks in Figure 1-1 can be used as a building block within a unique product design.

Figure 1-1. System Block Diagram

T-49-17-01

CHIPS & TECHNOLOGIES INC 51E D ■ 2098116 0002279 846 ■ CH Fast AT Bus and SMHz AT Bus Local Bus Address Control Bus Bus Address Control Bus Bus Data MA Bus Bus Optional 386 DX Super386 486 DX 486 SX 486 DX2 2-banks Cache 387 487 3167 4167 4021 74F244 4025 74F245 DRAM Banks Local Master Video Interface BIOS ROM Controller Bus

### The Basic 486 Non-cache System (16 - 25 MHz)

T-49-17-01

CHIPS & TECHNOLOGIES INC 51E D = 2098116 0002280 568 CHP

The basic 486 non-cache system consists of the following components:

- 486SX, 486DX, and 486DX2 CPU

- 4021 CHIPSet

- System memory (DRAM)

- · Keyboard controller

- BIOS ROM

The 486 non-cache system is a simple, low cost system that can yield performance comparable to a cache-based system. It can be designed with a 4-layer baby AT form factor system board. The system chip count is minimum in this configuration but it can be upgraded to any of the advanced device interfaces and a cache system.

# 486 Cache System (25-33 MHz)

The 486 cache system consists of the following components:

- 486SX, 486DX, and 486DX2 CPU

- 4021 CHIPSet

- System memory (DRAM)

- · Data and tag RAM

- Keyboard controller

- BIOS ROM

This 486 cache system is the same as the basic 486 non-cache system but with the addition of cache (data and tag RAM). It can be designed with a 4-layer baby AT form factor system board. It can also be upgraded to any of the advanced device interfaces.

# Cache 386DX or Super386 System (25 - 40 MHz)

The cache 386DX or Super386 system consists of the following components:

- 386DX CPU

- 4021 CHIPSet

- System memory (DRAM)

- · Data and tag RAM

- · Keyboard controller

- BIOS ROM

This system can be designed with a 4-layer baby AT form factor system board, and can be upgraded to any of the advanced device interfaces. T-49-17-01

CHIPS & TECHNOLOGIES INC

5LE D

**■ 2098116 0002281 4T4 ■ CHP**

# **System with Advanced Device Interfaces**

The 4021 CHIPSet provides four system memory interfaces to connect to external devices. The devices would normally interface through the EISA\ISA bus, like video, disk, or network cards.

#### **Local Bus Master**

The 4021 CHIPSet supports a local bus master without requiring any external logic. The local bus master must meet the system CPU timing. The local bus master can access system memory at the system CPU speed and can achieve burst transfer rates of 200 Mbytes/sec. The CHIPSet handles all the arbitration between the local master and the various devices, and other buses.

#### **Local Bus Slave**

The 4021 CHIPSet allows a local slave to map multiple system memory or I/O areas to the local slave memory.

# System VRAM Interface

The 4021 CHIPSet provides a high-speed interface for up to two banks of VRAMs. This improves the performance of a VGA chip over a standard AT or local interface type VGA.

## **Fast AT Bus Interface**

The fast AT bus interface is designed for external devices that need a fast, sustained transfer rate of up to 24 Mbytes/sec without major changes in the interface logic from the standard AT interface. A performance gain is achieved by either increasing the AT clock speed, or by forcing zero wait states for I/O cycles. The fast AT bus interface can be programmed for video memory, video I/O, and disk I/O space.

## **Functional Description**

CHIPS & TECHNOLOGIES INC 51E D == 2098116 0002282 330 HTCHP

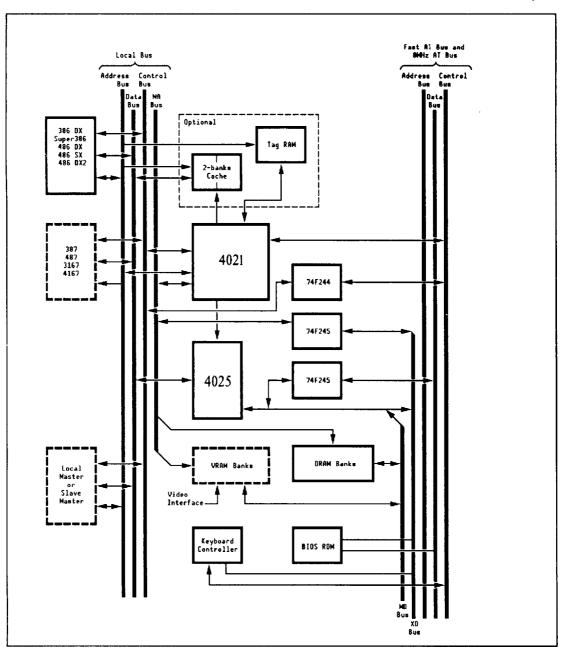

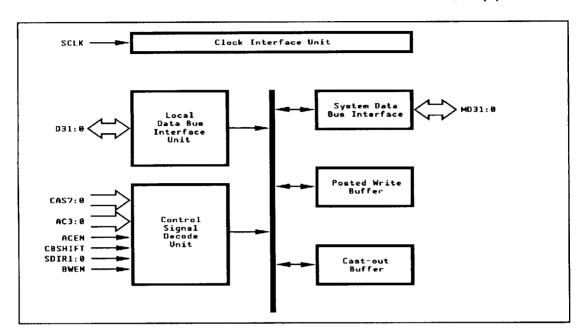

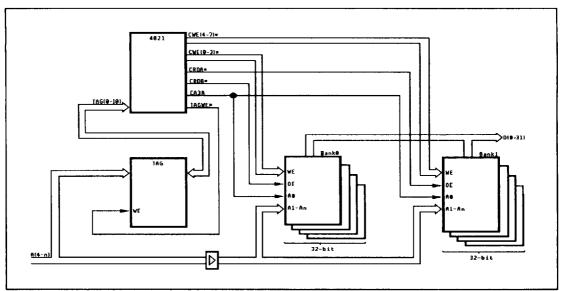

This section provides block diagrams of the 4021 and 4025 CHIPSets. Figure 1-1 shows the 4021 block diagram. Figure 1-2 shows the 4025 block diagram.

T-49-17-01

Figure 1-2. 4021 Block Diagram

CHIPS & TECHNOLOGIES INC 51E D ■ 2098116 0002283 277 ■ CHP

Figure 1-3. 4025 Block Diagram

T-49-17-01

**CHAPTER 2**

T-49-17-01

# Pin Description

### The 4021 CHIPSet Pinouts

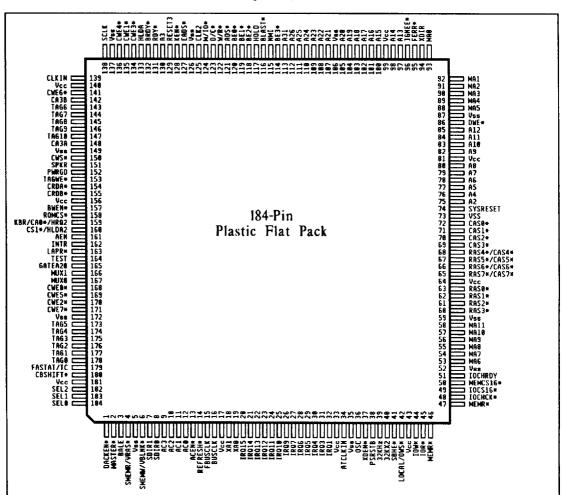

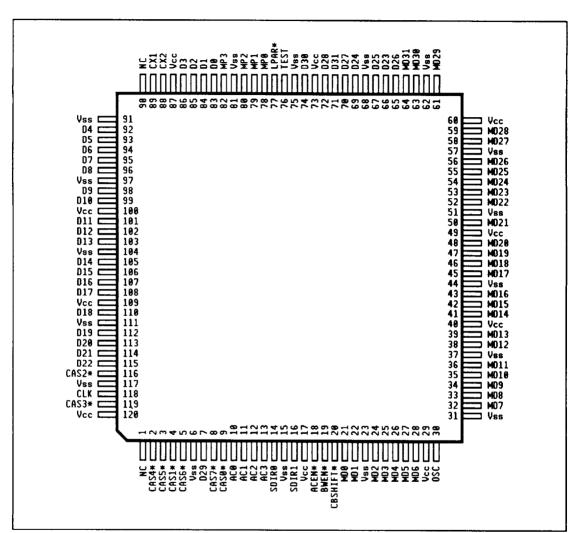

The 4021 CHIPSet is composed of a 4021 chip and a 4025 chip. Figure 2-1 shows the 4021 chip. Figure 2-2 shows the 4025 chip. Table 2-1 identifies the pin assignments for the 4021, and Table 2-2 identifies the pin assignments for the 4025.

Figure 2-1. 4021 Pinout (Top View)

CHIPS & TECHNOLOGIES INC 51E D == 209811: 0002285 04T == CH

Figure 2-2. 4025 Pinout (Top View)

T-49-17-01

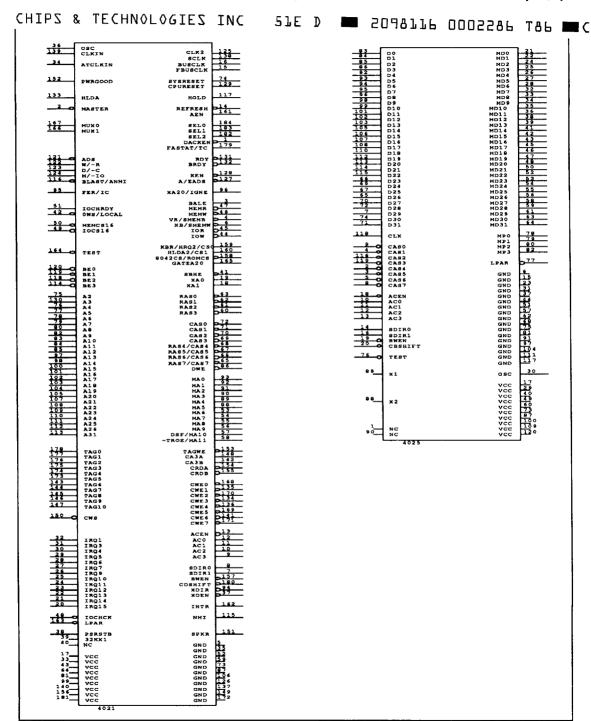

Figure 2-3. The 4021 Schematic Symbols

T-49-17-01

51E D = 2098116 0002287 912 = CHP

| Signal     | Pin No. | Signal     | Pin No. | T-49-         | Pin No |

|------------|---------|------------|---------|---------------|--------|

| 32KHZ      | 39      | BEO*       | 120     | HLDA          | 133    |

| NC         | 40      | BE1*       | 119     | HOLD          | 117    |

| A2         | 75      | BE2*       | 118     | IGNEE*        | 96     |

| <b>A</b> 3 | 130     | BE3*       | 114     | INTR          | 162    |

| <b>A</b> 4 | 76      | BLAST*     | 116     | IOCHCK*       | 48     |

| A5         | 77      | BRDY*      | 132     | IOCHRDY       | 51     |

| A6         | 78      | BUSCLK     | 16      | IOCS16*       | 49     |

| <b>A</b> 7 | 79      | BWEN*      | 157     | IOR*          | 45     |

| A8         | 80      | CA3A       | 148     | IOW*          | 44     |

| A9         | 82      | CA3B       | 142     | IRQ1          | 32     |

| A10        | 83      | CAS0*      | 72      | IRQ3          | 31     |

| A11        | 84      | CAS1*      | 71      | IRQ4          | 30     |

| A12        | 85      | CAS2*      | 70      | IRQ5          | 29     |

| A13        | 97      | CAS3*      | 69      | IRQ6          | 28     |

| A14        | 98      | CBSHIFT*   | 180     | IRQ7          | 27     |

| A15        | 100     | CLKIN      | 139     | IRQ9          | 26     |

| A16        | 101     | CLK2       | 125     | IRQ10         | 25     |

| A17        | 102     | CRDA*      | 154     | IRQ11         | 24     |

| A18        | 103     | CRDB*      | 155     | IRQ12         | 23     |

| A19        | 104     | CS1*/HLDA2 | 160     | IRQ13         | 22     |

| A20        | 105     | CWE0*      | 168     | IRQ14         | 21     |

| A21        | 107     | CWE1*      | 135     | IRQ15         | 20     |

| A22        | 108     | CWE2*      | 170     | KBR/CS0*/HRQ2 | 159    |

| A23        | 109     | CWE3*      | 134     | KEN*          | 128    |

| A24        | 110     | CWE4*      | 136     | LOCAL/0WS*    | 42     |

| A25        | 111     | CWE5*      | 169     | LPAR*         | 163    |

| A26        | 112     | CWE6*      | 141     | M/IO*         | 124    |

| A31        | 113     | CWE7*      | 171     | MA0           | 93     |

| AC0        | 12      | CWS*       | 150     | MA1           | 92     |

| AC1        | 11      | D/C*       | 123     | MA2           | 91     |

| AC2        | 10      | DACKEN*    | 1       | MA3           | 90     |

| AC3        | 9       | DWE*       | 86      | MA4           | 89     |

| ACEN*      | 13      | EADS*      | 127     | MA5           | 88     |

| ADS*       | 121     | FASTAT/TC  | 179     | MA6           | 53     |

| AEN        | 161     | FBUSCLK    | 15      | MA7           | 54     |

| ATCLKIN    | 34      | FERR*      | 95      |               |        |

| BALE       | 3       | GATEA20    | 165     |               | 1      |

Table 2-1. 4021 Pin Assignments (continued)

T-49-17-01

CHIPS & TECHNOLOGIES INC 51E D == 2098116 0002288 859 == CHP

| Signal      | Pin No. | Signal       | Pin No. | Signal          | Pin No. |  |

|-------------|---------|--------------|---------|-----------------|---------|--|

| MA8         | 55      | ROMCS*       | 158     | Vcc             | 17      |  |

| MA9         | 56      | SBHE*        | 41      | V <sub>cc</sub> | 33      |  |

| MA10/DSF    | 57      | SCLK         | 138     | V <sub>cc</sub> | 43      |  |

| MA11/TROE*  | 58      | SDIR0        | 8       | V <sub>cc</sub> | 64      |  |

| MASTER*     | 2       | SDIR1        | 7       | Vcc             | 81      |  |

| MEMCS16*    | 50      | SEL0         | 184     | V <sub>cc</sub> | 99      |  |

| MEMR*       | 47      | SEL1         | 183     | V <sub>cc</sub> | 140     |  |

| MEMW*       | 46      | SEL2         | 182     | V <sub>cc</sub> | 156     |  |

| MUX0        | 167     | SMEMR*/VRAS* | 4       | V <sub>cc</sub> | 181     |  |

| MUX1        | 166     | SMEMW*/XREQ* | 6       | V <sub>ss</sub> | 5       |  |

| NMI         | 115     | SPKR         | 151     | Vas             | 35      |  |

| OSC         | 36      | SYSRESET     | 74      | Vss             | 52      |  |

| PSRSTB      | 38      | TAG0         | 178     | Vss             | 59      |  |

| PWRGOOD     | 152     | TAG1         | 177     | Vss             | 73      |  |

| RAS0*       | 63      | TAG2         | 147     | Vss             | 87      |  |

| RAS1*       | 62      | TAG3         | 176     | Vss             | 106     |  |

| RAS2*       | 61      | TAG4         | 175     | V <sub>ss</sub> | 126     |  |

| RAS3*       | 60      | TAG5         | 174     | V <sub>ss</sub> | 137     |  |

| RAS4*/CAS4* | 68      | TAG6         | 173     | Vss             | 149     |  |

| RAS5*/CAS5* | 67      | TAG7         | 143     | V <sub>ss</sub> | 172     |  |

| RAS6*/CAS6* | 66      | TAG8         | 144     | W/R*            | 122     |  |

| RAS7*/CAS7* | 65      | TAG9         | 145     | XA0             | 19      |  |

| RDY*        | 131     | TAG10        | 146     | XA1             | 18      |  |

| REFRESH*    | 14      | TAGWE*       | 153     | XDEN*           | 37      |  |

| RESET3      | 129     | TEST         | 164     | XDIR            | 94      |  |

Table 2-2. 4025 Pin Assignments

T-49-17-01

CHIPS & TECHNOLOGIES INC 51E D ■ 2098116 0002289 795 ■ CHP

| Signal   | Pin No. | Signal | Pin No. | Signal          | Pin No. |

|----------|---------|--------|---------|-----------------|---------|

| AC0      | 10      | D18    | 110     | MD21            | 50      |

| AC1      | 11      | D19    | 112     | MD22            | 52      |

| AC2      | 12      | D20    | 113     | MD23            | 53      |

| AC3      | 13      | D21    | 114     | MD24            | 54      |

| ACEN*    | 18      | D22    | 115     | MD25            | 55      |

| BWEN*    | 19      | D23    | 66      | MD26            | 56      |

| CAS0*    | 9       | D24    | 69      | MD27            | 58      |

| CAS1*    | 4       | D25    | 67      | MD28            | 59      |

| CAS2*    | 116     | D26    | 65      | MD29            | 61      |

| CAS3*    | 119     | D27    | 70      | MD30            | 63      |

| CAS4*    | 2       | D28    | 72      | MD31            | 64      |

| CAS5*    | 3       | D29    | 7       | MP0             | 78      |

| CAS6*    | 5       | D30    | 74      | MP1             | 79      |

| CAS7*    | 8       | D31    | 71      | MP2             | 80      |

| CBSHIFT* | 20      | LPAR*  | 77      | MP3             | 82      |

| CLK      | 118     | MD0    | 21      | NC              | 1       |

| CX1      | 89      | MD1    | 22      | NC              | 90      |

| CX2      | 88      | MD2    | 24      | OSC             | 30      |

| D0       | 83      | MD3    | 23      | SDIR0           | 14      |

| D1       | 84      | MD4    | 26      | SDIR1           | 16      |

| D2       | 85      | MD5    | 27      | TEST            | 76      |

| D3       | 86      | MD6    | 28      | Vœ              | 17      |

| D4       | 92      | MD7    | 32      | Vcc             | 40      |

| D5       | 93      | MD8    | 33      | Vcc             | 49      |

| D6       | 94      | MD9    | 34      | Vcc             | 60      |

| D7       | 95      | MD10   | 35      | Vcc             | 73      |

| D8       | 96      | MD11   | 36      | V <sub>cc</sub> | 87      |

| D9       | 98      | MD12   | 38      | Vcc             | 100     |

| D10      | 99      | MD13   | 39      | Vcc             | 109     |

| D11      | 101     | MD14   | 41      | Vcc             | 120     |

| D12      | 102     | MD15   | 42      | V <sub>cc</sub> | 29      |

| D13      | 103     | MD16   | 43      | V <sub>ss</sub> | 6       |

| D14      | 105     | MD17   | 45      | Vss             | 13      |

| D15      | 106     | MD18   | 46      | V <sub>ss</sub> | 23      |

| D16      | 107     | MD19   | 47      | Vas             | 31      |

| D17      | 108     | MD20   | 48      | Vss             | 37      |

Table 2-2. 4025 Pin Assignments (continued)

T-49-17-01

CHIPS & TECHNOLOGIES INC

51E D

■ 2098116 0002290 407 ■CHP

| Signal          | Pin No. | Signal | Pin No. | Signal | Pin No. |

|-----------------|---------|--------|---------|--------|---------|

| V <sub>ss</sub> | 44      | Vss    | 68      | Vss    | 104     |

| V <sub>ss</sub> | 51      | Vss    | 75      | Vss    | 111     |

| Vss             | 57      | Vss    | 81      | Vss    | 117     |

| Vss             | 62      | Vss    | 97      | Vss    | 91      |

# **Signal Description**

The following sections describe all of the pin signals for the 4021 CHIPSet and the 4025 CHIPSet. An asterisk (\*) indicates that the signal is active when low. The signal direction input (I), output (O), or bidirectional (I/O) is also noted.

CHIPS & TECHNOLOGIES INC 51E D 2098116 0002291 343 CHP

| Clocks      |         |      | T-49-17-01                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Pin No. | Туре | Description                                                                                                                                                                                                                                                                                                                                                        |

| OSC         | 36      | I    | 14.31818MHz clock input for the timer<br>From an oscillator or the output of the crystal circuit<br>in the 4025.                                                                                                                                                                                                                                                   |

| CLKIN       | 139     | I    | CPU clock input from oscillator In 1x clock mode this is a 1x clock. In 2x clock mode this is a 2x clock.                                                                                                                                                                                                                                                          |

| CLK2        | 125     | I    | 2x clock pin Normally receives a 2x clock. This is required for 386 operation and when using the 486 in 2x DRAM modes. If only 1x DRAM modes are used with the 486, this pin can receive a 1x clock.                                                                                                                                                               |

| SCLK        | 138     | l    | 1x clock pin Input from the external clock drivers. This clock should be at the same phase and delay as the 486 clock.                                                                                                                                                                                                                                             |

| ATCLKIN     | 34      | I    | Oscillator input for an asynchronous AT clock May be divided by 1, 2, or 3 internally to form the 2x AT state machine clock. It will be generally connected to a 16MHz oscillator if FASTAT is not implemented, and 48MHz if FASTAT is implemented. If CLKIN is used as the source for the ISA bus clocks this pin need not be connected (it should be pulled up). |

| BUSCLK      | 16      | 0    | AT bus clock May be derived from CLKIN or ATCLKIN. It is normally close to 8 MHz. Between 6 and 8.33 MHz is recommended.                                                                                                                                                                                                                                           |

| FBUSCLK     | 15      | 0    | Fast AT bus clock Goes to the fast slots when FASTAT is implemented on the board. This pin will switch between the normal and fast AT clocks. The fast clock will normally be about 12 MHz.                                                                                                                                                                        |

CHIPS & TECHNOLOGIES INC 51E D ■ 2098116 0002292 28T ■ CH

| Resets      |         |      | T-49-17-01                                                                                                                                                                                                                                                        |

|-------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Pin No. | Туре | Description                                                                                                                                                                                                                                                       |

| PWRGOOD     | 152     | l    | Power up reset input Asynchronous. When low, all outputs are Hiz and all inputs are internally forced high (there are a few exceptions which are noted in the RESET section of this document). Generates CPURESET and SYSRESET.                                   |

| CPURESET    | 129     | 0    | Reset to the CPU only Active for hard resets (initiated by PWRGOOD) and soft resets (soft resets may be redirected to ANMI* for the Super386). CPURESET will go low during the second half of a T state to properly sync the 386 and Super386 to the clock phase. |

| SYSRESET    | 74      | 0    | Reset to everything except the CPU Activated only by PWRGOOD low. Has the same timing as CPURESET.                                                                                                                                                                |

CHIPS & TECHNOLOGIES INC 51E D 2098116 0002293 116 CHP

| Arbitration        |         |      | T-49-17-01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name        | Pin No. | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HOLD               | 117     | 0    | HOLD to the CPU<br>Synchronous to the clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| HLDA               | 133     | - 1  | HOLD acknowledge from the CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| KBR*/CS0*/<br>HRQ2 | 159     | VO   | Hold request from a local bus master This is a synchronous input. This pin is multiplexed for two more functions. These are not time multiplexed functions and hence only one of them may be used in a system. The other functions are a programmable chip select or the keyboard reset input from the keyboard controller. This pin function option is selected by a configuration register. At powerup it is an unused input, and need not be pulled low. It is configured as HRQ2 by software. If used as a chip select a 10K pullup should be connected to prevent the peripheral from being selected before the pin is configured by software. |

| CS1*/HLDA2*        | 160     | 0    | Hold acknowledge to a local bus master This signal is synchronous to the 1x clock. This pin may optionally be converted to a programmable chip select by a configuration register. At powerup this pin will be HLDA2*, and will be high, so no pullup is necessary when used as a chip select.                                                                                                                                                                                                                                                                                                                                                      |

| MASTER*            | 2       | 1    | ISA bus signal indicating that an ISA master has the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| REFRESH*           | 14      | I/O  | Refresh Active for refresh cycles. A bus master may pull this pin low to cause a refresh cycle. Must have an external pullup. Pseudo open collector (drives high for a short period of time before floating).                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AEN                | 161     | 0    | Address enable High during DMA cycles to indicate that I/O devices should disable their decode. Also high for refresh cycles. Low for AT master cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

CHIPS & TECHNOLOGIES INC 51E D = 2098116 0002294 052 = CHP

| INOLOGIEZ   | TNC              | اطا  |                                                                       |                                                                                                                                                          | 0002294                                                                                                      | 052 <b>C</b> HP                                                             |

|-------------|------------------|------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Signal Name |                  | Гуре | Descri                                                                |                                                                                                                                                          | T.                                                                                                           | -49-17-01                                                                   |

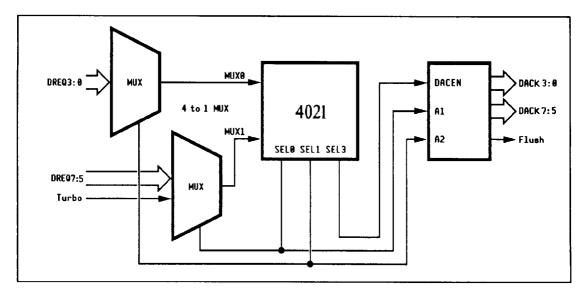

| SEL2:0      | 182,<br>183, 184 | 0    | The SE                                                                | exer enable signal<br>L1:0 are used as the<br>exer. SEL2:0 are a<br>de the DACKs* are                                                                    | e select lines<br>used along wit                                                                             | on the DREQ                                                                 |

|             |                  |      | SEL2:0                                                                | <b>Decoded Output</b>                                                                                                                                    | SEL2:0                                                                                                       | <b>Decoded Output</b>                                                       |

|             |                  |      | 0<br>1<br>2<br>3                                                      | DACK0*<br>DACK1*<br>DACK2*<br>DACK3*                                                                                                                     | 4<br>5<br>6<br>7                                                                                             | FLUSH*<br>DACK5*<br>DACK6*<br>DACK7*                                        |

| DACKEN*     | 1                | 0    | This is                                                               | * enable<br>the output enable<br>plexer for DACK:                                                                                                        |                                                                                                              |                                                                             |

| MUX1:0      | 166/167          | I    | An external and TU The enaby SEL slower,                              | and TURBO multicrnal 74F153 multicrnal 74F153 multicrnal as the able of the externation. When TURE as defined by the coded MUX1:0 out                    | iplexer encode<br>MUX1:0 for<br>I multiplexer is<br>O is low, the<br>Performance                             | es the DREQx<br>the CHIPSet.<br>is controlled<br>CPU runs<br>Control logic. |

|             |                  |      | SEL1:0                                                                | MUX0                                                                                                                                                     | MUX1                                                                                                         |                                                                             |

|             |                  |      | 0<br>1<br>2<br>3                                                      | DREQ0<br>DREQ1<br>DREQ2<br>DREQ3                                                                                                                         | TURBO<br>DREQO<br>DREQO<br>DREQO                                                                             | 5                                                                           |

| FASTAT/TC   | 179              | 0    | When F<br>FASTA<br>speed)<br>control<br>(includ<br>Two F(<br>the sep. | erminal count FASTAT mode is AT pin (low for nowhen the CPU or . When a DMA cling master cycles) 98 gates and an invarate signals. The FASTAT mode is in | rmal speed, hi<br>local bus mast<br>hannel has the<br>this pin is ter-<br>verter on the o<br>se gates are of | gh for high ter has bus minal count. tutside decode nly required            |

CHIPS & TECHNOLOGIES INC 51E D == 2098116 0002295 T99 == CHP

## **CPU Control**

| 01 0 00111101 |         |      |                                                                                                                                                                                                                                 |                                                                 |  |

|---------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|

| Signal Name   | Pin No. | Type | Description                                                                                                                                                                                                                     | T-49-17-01                                                      |  |

| ADS*          | 121     | I/O  | CPU address strobe Input during CPU or local masduring DMA and ISA master of internal cache invalidation, and                                                                                                                   | cycles for 38605                                                |  |

| W/R*          | 122     | VO   | CPU write/read signal Input during CPU or local maduring DMA and AT master c invalidation and for local bus                                                                                                                     | ycles for 38605 cache                                           |  |

| D/C*          | 123     | VO   | CPU data/code signal Input during CPU or local maduring DMA and AT master c invalidation and for local bus                                                                                                                      | ycles for 38605 cache                                           |  |

| M/IO*         | 124     | VO   | CPU memory and I/O signal<br>Input during CPU or local maduring DMA and AT master of<br>invalidation and for local bus                                                                                                          | ycles for 38605 cache                                           |  |

| RDY*          | 131     | VO   | Pseudo open collector READ'<br>Input during local slave cycle.<br>CPU, non-cachable 486 cycle:<br>cycles.                                                                                                                       | Output during 386                                               |  |

| BRDY*         | 132     | 1/0  | Burst ready. Input during loca<br>READY output during 486 ca                                                                                                                                                                    |                                                                 |  |

| KEN*          | 128     | 0    | Cache enable to the CPU<br>The 4021 drives this pin low a<br>It will be driven high only for                                                                                                                                    |                                                                 |  |

| BLAST*/ANMI*  | 116     |      | Burst last/Alternate nonmaska 486: Burst last from the CPU will be the last cycle of a burs 38605: ANMI* output pin. C ANMI* timer and soft reset re Super state functions. 38605 of pull-up on this signal. 386: unused input. | . When low, the cycle t. Controlled by the edirection for 38605 |  |

| EADS*/AADS*   | 127     | VO   | External ADS/Alternate addres 486: External ADS. Driven do master memory writes. Used CPU internal cache line. 38605: AADS* input indicate between user and SuperState 386: unused input.                                       | aring DMA and bus to invalidate the 486 ing the difference      |  |

CHIPS & TECHNOLOGIES INC 51E D == 2098116 0002296 925 == CHP

| Coproces    | sor Co  | ntrol | T-49-17-0                                                                                                                                                                                                    |  |  |

|-------------|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Signal Name | Pin No. | Туре  | Description                                                                                                                                                                                                  |  |  |

| IGNEE*/XA20 | 96      | VO    | Ignore numeric error/Gated A20 486: Ignore numeric error. Connects to the 486 or 487SX CPUs. 38605 and 386: XA20. Gated A20 for the ISA bus. Must be buffered by an external F245.                           |  |  |

| FERR*/INTR  | 95, 162 | VO    | Floating-point error/Clear interrupt 486: Floating-point error. Used to generate IRQ13. 38605 and 386: INTCLR to the coprocessor PAL. Active for I/O writes to F0 and F1 to clear the coprocessor interrupt. |  |  |

# **ISA Bus Signals**

| Signal Name      | Pin No. | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|------------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BALE             | 3       | 0    | ISA bus ALE.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| MEMR*            | 47      | I/O  | ISA bus memory read Output during CPU access to ISA bus. Input for ISA master cycles.                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| MEMW*            | 46      | VO   | ISA bus memory write<br>Output during CPU access to ISA bus. Input for ISA<br>master cycles.                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| SMEMR*/<br>VRAS* | 4       | 0    | Memory read strobe/VRAM RAS. Dual function, selected by a configuration register.  SMEMR* Memory read strobe for the bottom megabyte. Always driven.  VRAS* VRAM RAS for Windows video support.                                                                                                                                                                                                                                     |  |  |  |

| SMEMW*/<br>XREQ* | 6       | I/O  | Memory write strobe/blank video controller signal.  Dual function, selected by a configuration register.  SMEMW* Memory write strobe for the bottom megabyte. Always driven.  XREQ* Blank signal from the video controller (possibly modified to include the field information). Used for the windows video support to determine when to do a VRAM transfer cycle. Horizontal and vertical information is derived from this signal. |  |  |  |

| CHIPS & ' | TECHNOLOGIES IN<br>Signal Name Pin No | -  | Description T-49-17-01                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|---------------------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|