## 82C835

Integrated Cache Controller Chip

PRELIMINARY

## U.S. Sales Representatives

## **Regional Sales Offices**

## **United States**

California, Irvine Chips and Technologies, Inc. (714) 852-8721

California, San Jose Chips and Technologies, Inc. (408) 437-3300

Florida, Boca Raton Chips and Technologies, Inc. (407) 241-3162

Georgia, Norcross Chips and Technologies, Inc. (404) 662-5098

Illinois, Schaumburg Chips and Technologies, Inc. (708) 397-4300

Massachusetts, Andover Chips and Technologies, Inc. (508) 688-4600

**Texas, Dallas**Chips and Technologies, Inc. (214) 702-9855

## International

Germany, Munich Chips and Technologies, GmbH 49-89-463-074

Japan, Tokyo Chips and Technologies, Inc. 813-3-797-7242

Korea, Seoul Chips and Technologies, Inc. 82-2-558-5559

Switzerland, Marin Chips and Technologies, Inc. 41-38-33-6379

Taiwan, Taipei Chips and Technologies, Inc. 88-62-717-5595

## Sales Representatives

### **United States**

Arizona, Scottsdale

AzTECH Component Sales

(602) 991-6300

California, Santa Clara Magna Sales (408) 727-8753

California, San Diego S.C. Cubed (619) 458-5808

California, Thousand Oaks S.C. Cubed (805) 496-7307

California, Tustin S.C. Cubed (714) 731-9206

Colorado, Wheat Ridge Wescom Marketing, Inc. (303) 422-8957

Connecticut, Guilford DataMark Inc. (203) 453-0575

Florida, Casselberry Dyne-A-Mark Corp. (407) 831-2822

Florida, Clearwater Dyne-A-Mark Corp. (813) 441-4702

Florida, Fort Lauderdale Dyne-A-Mark Corp. (305) 771-6501

Idaho, Boise Wescom Marketing, Inc. (208) 336-6654

Illinois, Hoffman Estates Micro-Tex, Inc. (312) 382-3001

Indiana, Carmel Geisting & Associates (317) 844-5222 Kentucky, Versailles Geisting & Associates (606)873-2330

Maryland, Annapolis EES (301) 269-4234

Massachusetts, Woburn Mill-Bern Associates (617) 932-3311

Michigan, Coloma Giesting & Associates (616) 468-3308

Michigan, Comstock Park Giesting & Associates (616) 784-9437

Michigan, Livonia Giesting and Associates (313) 478-8106

Minnesota, Eden Prairie High Tech Sales Associates (612) 944-7274

Missouri, Bridgeton Centech (314) 291-4230

Missouri, Raytown Centech (816) 358-8100

New Jersey, Moorestown T.A.I. (609) 778-5353

New York, Commack ERA, Inc. (516) 543-0510

New York, Pleasant Valley Pitronics (914) 635-3233

New York, Syracuse Pitronics (315) 455-7346

New York, Williamsville Pitronics (716) 689-2378 Ohio, Cincinnati Giesting & Associates (513) 385-1105

Ohio, Cleveland Giesting & Associates (216) 261-9705

Oregon, Beaverton L-Squared Limited (503) 629-8555

Pennsylvania, Pittsburg Giesting & Associates (412) 828-3553

Texas, Austin OM Associates, Inc. (512) 794-9971

Texas, Houston OM Associates, Inc. (713) 789-4426

Texas, Richardson OM Associates, Inc. (214) 690-6746

Utah, Salt Lake City Wescom Marketing, Inc. (801) 269-0419

Washington, Kirkland L-Squared Limited (206) 827-8555

Wisconsin, Waukesha Micro-Tex, Inc. (414) 542-5352

## Canada

Ontario, Kanata Electro Source, Inc. (613) 592-3214

Ontario, Rexdale Electro Source, Inc. (416) 675-4490

Quebec, Pointe Claire Electro Source, Inc. (514) 630-7846

British Columbia, Vancouver Electro Source, Inc. (604) 435-8066

# **D**istributors

#### **United States**

Alabama, Huntsville Reptron Electronics, Inc. (205) 722-9500

Arizona, Tempe Anthem (602) 966-6600

California, Chatsworth Anthem (818) 755-1333

California, Fountain Valley Bell Microproducts (714) 963-0667

California, Irvine Anthem (714) 768-4444

California, Milpitas Bell Microproducts (408) 434-1150

California, Rocklin Anthem (916) 624-9744

California, San Diego Anthem (619) 453-9005

California, San Jose Anthem (408) 453-1200

Colorado, Englewood Anthem (303) 790-4500

Connecticut, Waterbury Anthem (203) 237-2282

Florida, Fort Lauderdale Reptron Electronics, Inc. (305) 735-1112

Florida, Tampa Reptron Electronics, Inc. (813) 854-2351 Georgia, Norcross

B.I.T.S., Inc. (404) 446-1155

Georgia, Norcross Reptron Electronics, Inc. (404) 446-1300

Georgia, Norcross JACO/QC (404) 449-1996

Illinois, Elk Grove Anthem (708) 884-0200

Illinois, Schaumburg Reptron Electronics, Inc. (312) 882-1700

Massachusetts, Wilmington Anthem (508) 657-5170

Massachusetts, Wilmington Bell Microproducts (508) 658-0222

Maryland, Columbia Anthem (301) 995-6640

Michigan, Livonia Reptron Electronics, Inc. (313) 525-2700

Minnesota, Eden Prairie Anthem (612) 944-5454

Minnesota, Minnetonka Reptron Electronics, Inc. (612) 938-0000

New Jersey, Fairfield Anthem (201) 227-7960

New York, Commack Anthem (516) 864-6600

North Carolina, Raleigh Reptron Electronics, Inc. (919) 870-5189

PRELIMINARY

North Carolina, Raleigh JACO/QC (919) 876-7767

Ohio, Columbus EMC (614) 299-4161

Ohio, Solon Reptron Electronics, Inc. (216) 349-1415

Ohio, Worthington Reptron Electronics, Inc. (614) 436-6675

Oklahoma, Tulsa JACO/QC (918) 664-8812

Oregon, Beaverton Anthem (503) 643-1114

Pennsylvania, Horsham Anthem (215) 443-5150

Texas, Addison JACO/QC (214) 733-4300

Texas, Austin JACO/QC (512) 835-0220

Texas, Richardson Anthem (214) 238-7100

Texas, Sugarland JACO/QC (713) 240-2255

Utah, Salt Lake City Anthem (801) 973-8555

Washington, Bothell Anthem (206) 483-1700

#### Distributors

#### Canada

Ontario, Woodbridge Valtrie Marketing (416) 798-2555

#### International

#### Asia/Pacific

Australia Victoria, Burwood R&D Electronics (613) 808-8911

Australia, Bayswater Zatek Components (613) 763-8899

Hong Kong, Kwung Tong Wong's KK Ltd. 85-2-345-0121

India, Bombay Silicon Electronics 91-22-243-460

India, New Dehli Ajay Jain 91-11-686-3044

Israel, Tel-Aviv CVS 97-23-544-7475

Japan, Tokyo ASCII Corporation 81-3-486-9188

Japan, Kawasaki CTC Components Systems Co. Ltd. 81-44-852-1825

Korea, Seoul Nae Wae Semiconductor 82-2-704-0103

Malaysia, Penang Dynamar 60-4-637-292

Malaysia, Penang Selangor 03-776-7140/199

Singapore, Singapore Technology Distribution PTE Ltd. 65-368-6065

**Taiwan,** Taipei Ally, Inc. 886-2-562-0828

Taiwan, Taipei World Peace Industrial Co. Ltd. 88-62-786-5311

Thailand, Bangkok Grawinner 66-2-215-8742

#### Europe

Belgium, Zaventem ACAL Auriema Belgium 32-2-720-5983

**Denmark,** Herlev Nordisk Elektronik A/S 454-284-2000

Finland, Helsinki OY Fintonic AB 35-806-926022

France, Le Chesnay A2M 33-1-395-49113

Germany, Neteltal Rein Elektronik GmbH 49-215-37330

Italy, Milano Moxel S.R.L. 39-2-612-90521

Netherlands, Eindhoven ACAL Auriema Nederland B.V. 31-40-816-565

Norway, Hvalstad Nordisk Elektronik A/S 47-284-6210

Spain, Madrid Compania Electronica de Tecnicas Aplicadas, S.A. 34-1-754-3001

Spain, Barcelona Compania Electronica de Tecnicas Aplicadas, S.A. 34-3-300-7712

Sweden, Kista Nordisk Elektronik A.B. 46-8-703-4630

Switzerland, Dietikon DataComp AG 41-1-740-5140 United Kingdom

Berkshire, Maidenhead

Katakana Limited

44-628-778622

United Kingdom Berkshire Magna Technology 44-734-880211

United Kingdon Oxfordshire, Thame Components Ltd. 44-844-261188

#### **Americas**

Brazil Florida Etek Electronics Corporation 305-593-1188

Sao Paulo Brastek 55-11-531-2632

Mexico Guadalajara Sonika 52-364-74250

## 82C835

Integrated Cache Controller Chip

Single CHIP 386sx AT Cache Controller

Data Sheet

April 1991

PRELIMINARY

#### **Copyright Notice**

Software Copyright © 1991, CHIPS and Technologies, Inc.

Manual Copyright @ 1991, CHIPS and Technologies, Inc.

All Rights Reserved.

Printed in U.S.A.

#### **Trademarks**

PEAK-sx<sup>TM</sup> is a trademark of CHIPS and Technologies, Incorporated.

IBM®, IBM PC®, and IBM PC/AT® are registered trademarks of International Business Machines Corporation.

$PS2^{TM}$ , Microchannel<sup>TM</sup>, and Personal System/ $2^{TM}$  are trademarks of International Business Machines Corporation.

Intel® is a registered trademark of Intel Corporation.

Lotus® is a registered trademark of Lotus Development Corporation.

MS-DOS® is a registered trademark of Microsoft Corporation.

Motorola® is a registered trademark of Motorola.

#### Disclaimer

This manual is copyrighted by CHIPS and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of CHIPS and Technologies, Inc.

Every possible effort was made to ensure the accuracy of this manual. However, CHIPS Systems Logic Division cannot accept responsibility for any errors in the manual or consequences resulting therefrom.

The information contained in this document is being issued in advance of the production cycle for the device(s). The parameters for the device(s) may change before final production.

CHIPS and Technologies, Inc. makes no representations or warranties regarding the contents of this manual. We reserve the right to revise the manual or make changes in the specifications of the product described within it at any time without notice and without obligation to notify any person of such revision or change.

The information contained in this manual is provided for general use by our customers. Our customers should be aware that the personal computer field is the subject of many patents. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. It is the policy of CHIPS and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

#### **Restricted Rights and Limitations**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

CHIPS and Technologies, Inc. 3050 Zanker Road San Jose, California 95134 Phone: 408-434-0600

# Preface

The 82C835 integrated cache controller chip operates in conjunction with the 82C836 (Scat-sx). In combination, they form the Peak-sx CHIPSet. This manual covers the 82C835 cache controller chip only. The following related documentation is also available:

- The 82C835 Integrated Cache Controller Data Sheet

- The 82C836 Single Chip AT-sx Data Sheet

- The 82C641 Power Management/Buffer Unit Data Sheet

The Development Kit Package for each chip which includes:

- Development Kit Users Guide

- Development Kit System Board

- Development Kit Schematics

If you would like to review any of the above noted documentation, contact the CHIPS and Technologies Sales Office near you.

Preface

# Contents

| Section | on 1: Introduction                                                                                                                                                                                                   | . 1                              |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1.1     | Features                                                                                                                                                                                                             |                                  |

| 1.2     | 82C835 Overview                                                                                                                                                                                                      | . 1                              |

| 1.3     | What You Need to Know                                                                                                                                                                                                | .3                               |

| 1.4     | About This Manual                                                                                                                                                                                                    | . 3                              |

| 1.5     | Manual Conventions                                                                                                                                                                                                   | . 3                              |

| Section | on 2: Functional Description                                                                                                                                                                                         | . 5                              |

| 2.1     | Functional Overview                                                                                                                                                                                                  |                                  |

| 2.2     | Bus Structure Overview                                                                                                                                                                                               | . 5                              |

| 2.3     | Address Latching and Command Buffering                                                                                                                                                                               | . 6                              |

| 2.4     | Basic Cache Operation READY Protocol Cache Flush and Enable Memory Read Cycles Memory Write Cycles Other CPU Cycles DMA and Master Cycles                                                                            | .6<br>.7<br>.7<br>.7             |

| 2.5     | Cache Structure  Direct Mapped Organization  Read Hits  Read Misses  Write Cycles  Other Cycles Affecting the Cache Two Way Set Organization  Read Hits  Read Misses  Write Cycles  Other Cycles Affecting the Cache | .8<br>.9<br>.9<br>10<br>10<br>11 |

| 2.6     | Hardware Interface                                               |

|---------|------------------------------------------------------------------|

|         | CPU Interface                                                    |

|         | Cache Address Bus                                                |

|         | Cache Data Bus                                                   |

|         | Channel Address Bus                                              |

|         | Channel Command Bus                                              |

|         | Cache Control Signals       14         Reset       15            |

|         |                                                                  |

| 2.7     | Programmable Features                                            |

|         | Cache Enable         15           Directory Freeze         15    |

|         | Write Pulse Width on Read Misses                                 |

|         | Directory Flush                                                  |

|         | Direct SRAM Access                                               |

|         | Directory Access                                                 |

|         | Cache Type (Direct Mapped or Two-Way Set-Associative) . 17       |

|         | Cacheable Areas                                                  |

|         | RAM Write Protect                                                |

|         | AT Channel Memory Caching                                        |

| 2.8     | Design Considerations                                            |

|         | Clocks                                                           |

|         | Cache Size and Type                                              |

|         | Cache Data SRAM Speed Requirements                               |

|         | DRAM Controller Impact on Performance                            |

|         | Cache Address Bus         20           Cache Data Bus         20 |

|         | External Non-cacheable Areas                                     |

|         | Future Revisions                                                 |

| 2.0     | Test Considerations                                              |

| 2.9     | Test Considerations20                                            |

| Section | on 3: Configuration Registers21                                  |

|         | CHIPS Configuration Registers                                    |

|         | OS/2 Optimization Control Register                               |

| 3.2     | OS/2 Optimization Condot Register                                |

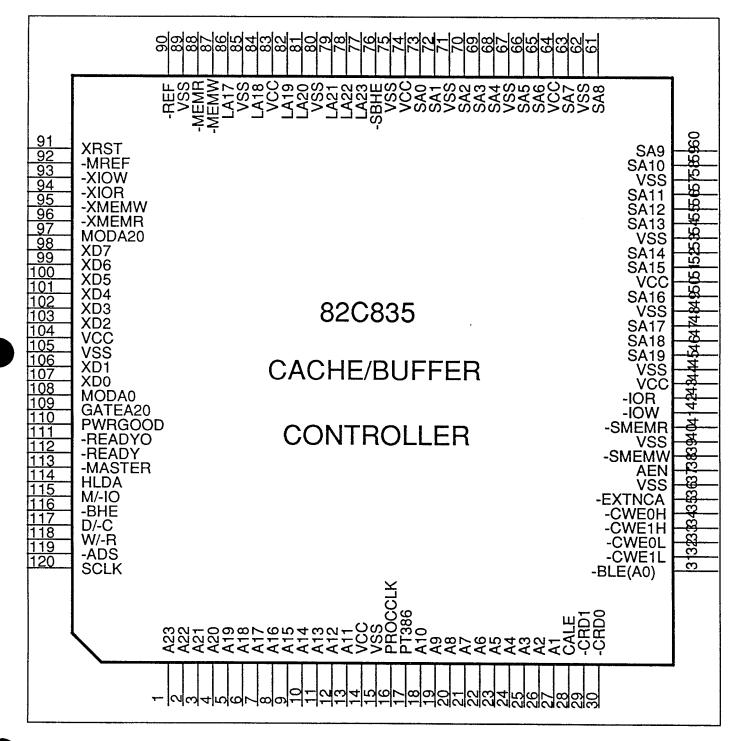

| Secti   | on 4: Pin Descriptions33                                         |

| 4.1     | Pin Assignments                                                  |

| 4.2     | Pin Totals and Summary34                                         |

| 4.3     | Numerical Listing of Pin Assignments35                           |

| 4.4     | Alphabetical Listing of Pin Assignments                          |

| 4.5     | Pin Diagram                                                      |

| Sect | tion 5: Physical Characteristics | 39 |

|------|----------------------------------|----|

| 5.1  | Absolute Maximum Ratings         | 39 |

| 5.2  | Operating Conditions             | 39 |

| 5.3  | Capacitive Characteristics       | 40 |

| Sect | tion 6: DC/AC Characteristics    |    |

| 6.1  | DC Characteristics               | 41 |

| 6.2  | AC Characteristics               | 41 |

| Sect | tion 7: Timing Diagrams          | 45 |

| Sect | tion 8: Physical Dimensions      | 55 |

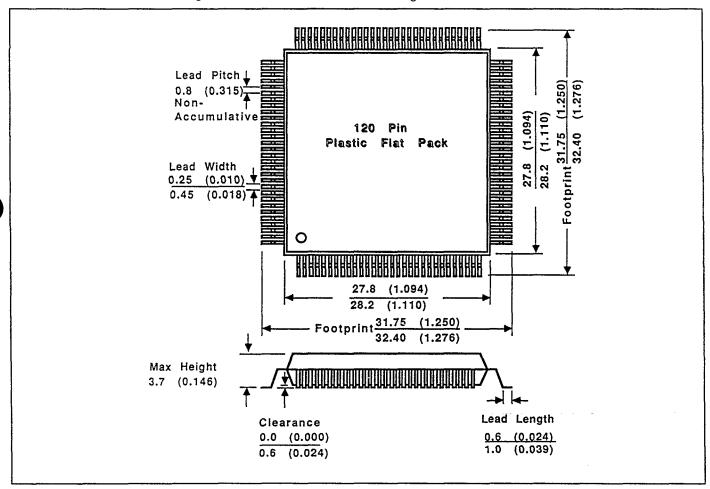

| 8.1  | 82C835 Cache Controller          | 55 |

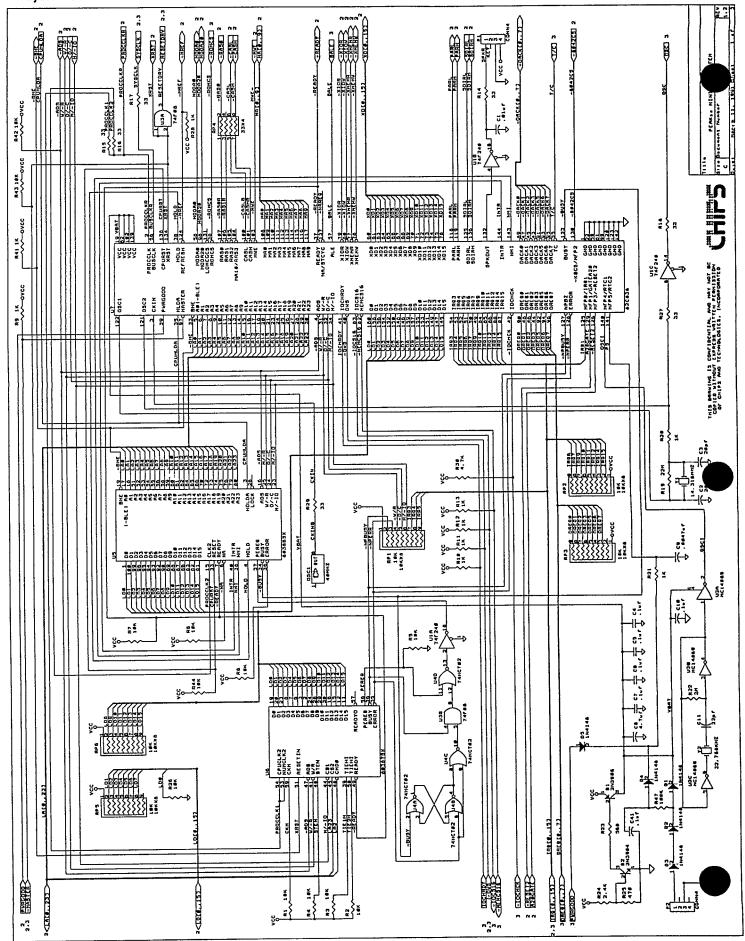

| App  | pendix A: System Schematics      | 57 |

| u.s. | . Sales Representatives          | 61 |

| Diet | tributors                        | 62 |

Contents

# List of Figures

| Section 1:  | Introduction                        | 1  |

|-------------|-------------------------------------|----|

| Figure 1-1  | System Block Diagram                | 2  |

| Section 4:  | Pin Descriptions                    | 3  |

| Figure 4-1: | 82C835 Cache Controller Pin Diagram | 7  |

| Section 7:  | Timing Diagrams 4                   | 5  |

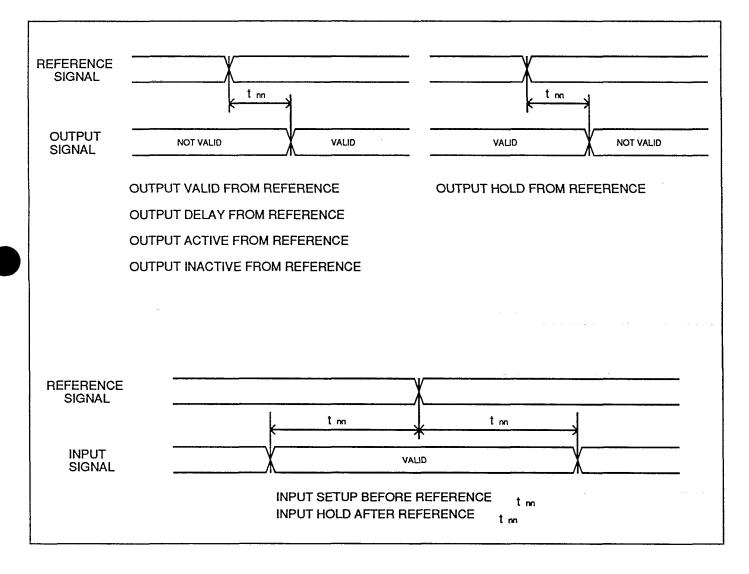

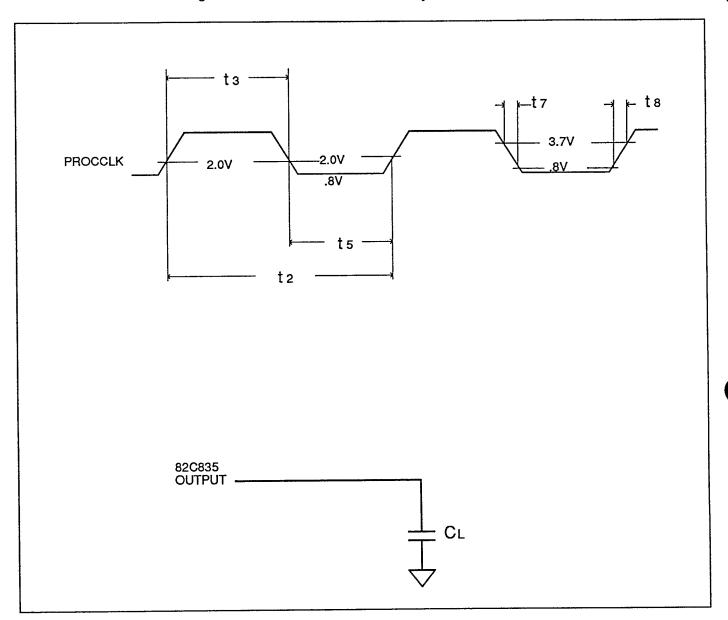

| Figure 7-1  | Supplemental AC Parameters4         |    |

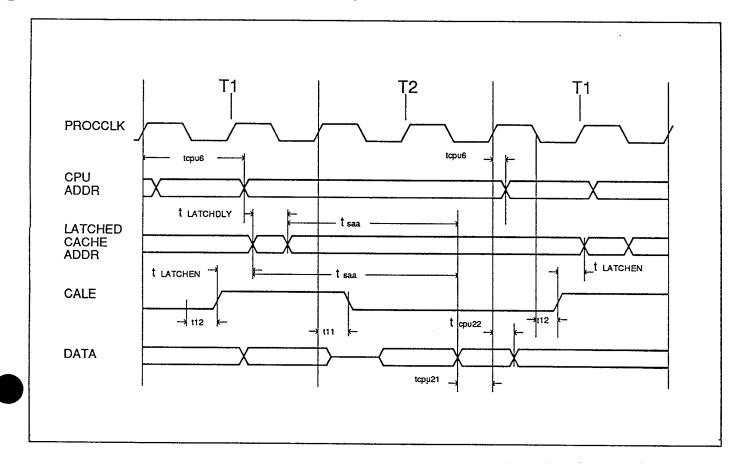

| Figure 7-2  | PROCCLK and AC Load Requirement     | 6  |

| Figure 7-3  | CPU/82C835 Interface                | 7  |

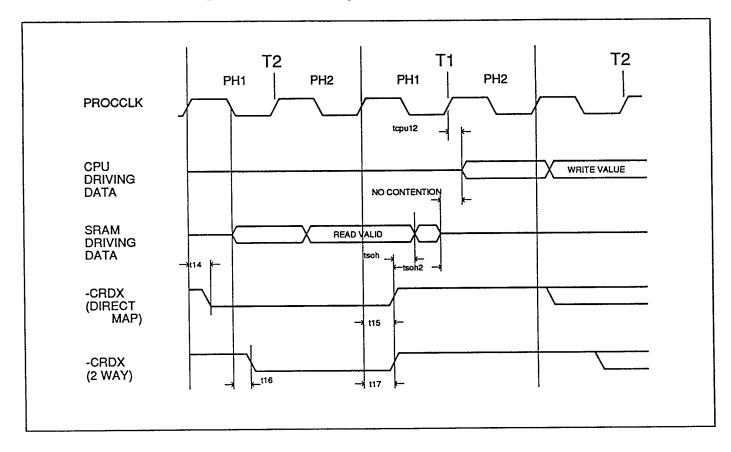

| Figure 7-4  | Cache Read Hit4                     | 8  |

| Figure 7-5  | Cache Write Hit4                    |    |

| Figure 7-6  | Cache Read Miss5                    | iO |

| Figure 7-7  | Cache Read Miss (Back-End Timing)   | 1  |

| Figure 7-8  | CPU Write (After Cache Read Hit)5   | 2  |

| Figure 7-9  | CALE Timing5                        |    |

| Figure 7-10 |                                     |    |

| Section 8:  | Physical Dimensions 5               | ;7 |

| Figure 8-1  | 120-Pin Plastic Flat Package5       | 57 |

List of Figures

## List of Tables

| Functional Description                                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82C835 Local and AT Address Bus Direction1                | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 82C835 Local and AT Bus Command Direction                 | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pin Descriptions                                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pin Definitions                                           | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Numerical Pin Definitions                                 | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Alphabetical Pin Definitions                              | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Physical Characteristics                                  | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Physical Characteristics - Maximum Ratings                | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Physical Characteristics - Operating Conditions           | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Physical Characteristics - Capacitive Characteristics . 4 | 4(                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DC/AC Characteristics                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DC Characteristics of the 82C835                          | 4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Clock Requirements                                        | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Cache Control                                             | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Address/Control Requirements                              | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Address/Control Delays                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Master Cycles                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                           | 82C835 Local and AT Bus Command Direction  Pin Descriptions Pin Definitions Numerical Pin Definitions Alphabetical Pin Definitions Physical Characteristics Physical Characteristics - Maximum Ratings Physical Characteristics - Operating Conditions Physical Characteristics - Capacitive Characteristics  Physical Characteristics - Capacitive Characteristics  DC/AC Characteristics DC Characteristics of the 82C835 Clock Requirements Cache Control Address/Control Requirements Address/Control Delays |

**■** List of Tables

# List of Registers

| Section 3: | Configuration Registers                           |

|------------|---------------------------------------------------|

| Index 20H  | Cache Control Register (READ/WRITE)22             |

| Index 21H  | Directory RAM Control Register (READ/WRITE) 23    |

| Index 22H  | Low Bits of Directory Address Register            |

|            | (READ/WRITE)                                      |

| Index 23H  | Reference Location Register (READ/WRITE) 24       |

| Index 24H  | SRAM Configuration and Direct Access              |

|            | Address Register (READ/WRITE)24                   |

| Index 25H  | Memory Boundary Register (READ/WRITE)24           |

| Index 26H  | Version Register (READ)24                         |

| Index 27H  | Special Control Register (READ/WRITE)25           |

| Index 28H  | Cacheable Block Enable Register 1 (READ/WRITE) 25 |

| Index 29H  | Cacheable Block Enable Register 2 (READ/WRITE) 20 |

| Index 2AH  | Cacheable Block Enable Register 3 (READ/WRITE) 2  |

| Index 2BH  | Cacheable Block Enable Register 4 (READ/WRITE) 28 |

| Index 2CH  | Cacheable Block Enable Register 5 (READ/WRITE) 2  |

| Index 2DH  | Cacheable Block Enable Register 6 (READ/WRITE) 2  |

| Index 2EH  | RAM Write Protect Register (READ/WRITE)3          |

| Index 2FH  | Cacheable Block Enable Register (READ/WRITE) 3    |

| Addr 092H  | OS/2 Optimization Control Register (WRITE) 3      |

List of Registers

## 1.1 Features

- Interfaces to the 80386sx

- Close-coupled design with the 82C836 (SCATsx) for a cache based system

- 32KB or 16KB cache

- Two-way Set-associative or Direct-mapped organization

- Supports CPU speeds up to 20MHz

- Caches AT I/O Channel memory as well as local DRAM

- Internal tag RAM and comparators

- Latches and buffers for all address lines to/from the AT expansion bus using integrated 24mA drivers

- Buffers commands to/from the expansion bus using integrated 24mA drivers

- 120-pin plastic quad flat pack

### 1.2 82C835 Overview

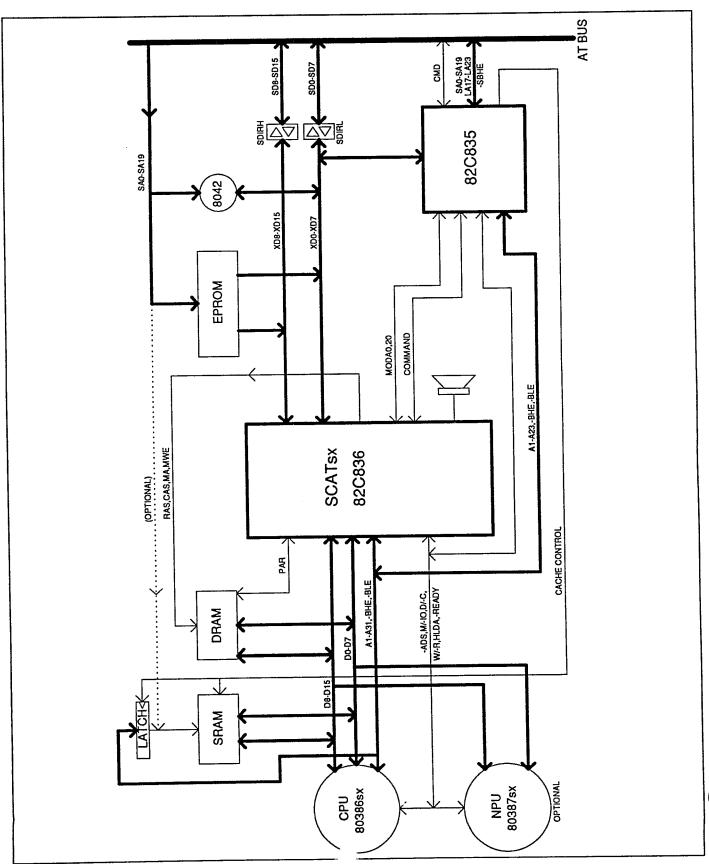

The 82C835 interfaces directly with the 386sx and has been designed to work closely with the 82C836 single chip AT (SCAT-sx). The 82C835 contains a 386sx cache controller incorporating the cache control logic and tag RAM. Also included are several programmable registers provided for configuration options. The ability to configure the cache organization (Two-Way Set-Associative or Direct Mapped) and size (16KB or 32KB) allows a flexible selection of external data SRAM.

In addition to the cache controller, the 82C835 integrates the AT I/O channel command and address buffers and the corresponding control logic. Many existing 80386sx system implementations require the use of external buffers, latches, and transceivers to drive and receive the commands and addresses. These systems also require external SSI logic to control the operation of these buffers. Systems will typically save six to seven external TTL buffers and five to six SSI gates when implementing the channel interface with the 82C835. By integrating the channel drivers and logic, the 82C835 reduces the system size and complexity.

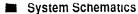

Figure 1-1. System Block Diagram

## 1.3 What You Need to Know

This manual is written with the assumption that you have a basic comprehension of computer concepts, operations, and terminology. Understanding of cache organizations and operations as well as DRAM memory controller operations is essential. Most of the cache related descriptions require that you also have a basic understanding of SRAM usage. Finally, familiarity with the Industry Standard Architecture (ISA) is highly recommended.

The scope of the information presented in this manual is limited to this CHIPSet and does not include the operation of external components. It is assumed you have a working knowledge of these components. With such knowledge, combined with the information presented here, you can utilize our CHIPSet to enhance the overall performance and excellence of your final product.

If you are unfamiliar with any of the mentioned subjects, please consult the appropriate reference documentation.

## 1.4 About This Manual

Here's what you'll find in the rest of this manual:

- Section 2: Functional Description explains the functionality of the 82C835.

- Section 3: Configuration Registers details the internal registers within the 82C835.

- Section 4: Pin Descriptions provides tables describing the details of each pin.

- Section 5: Physical Characteristics reports the range of absolute maximum ratings, operating conditions, and capacitive characteristics.

- Section 6: DC/AC Characteristics lists the DC and AC Characteristics of the 82C835.

- Section 7: Timing Diagrams details the timings of the 82C835 signals.

- Section 8: Physical Dimensions identifies the dimensions of the 82C835 PFP package.

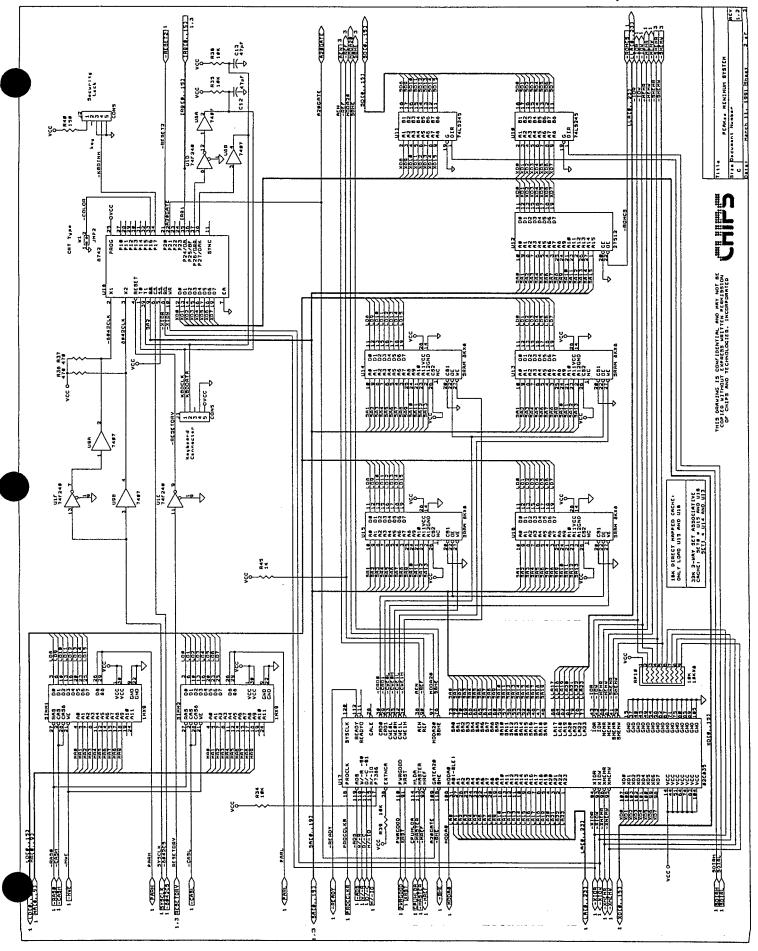

- Appendix A: System Schematics provides diagrams of the 82C835 minimum system.

## 1.5 Manual Conventions

The following conventions are used throughout this manual:

- REGnH identifies the internal register of index n, where n is in hexadecimal notation.

- REGnH <x:y> indicates the bit range from bit x to bit y of indexed register

n.

- (xxx) signifies the default value after power-on Reset (where xxx are register bit values).

#### Introduction

- Signal names are identified in UPPER CASE. For example, XRST.

- A dash at the beginning of the signal name indicates an active low signal.

For example, -READY.

- Section titles are shown in *italic* type. For example; Section 2.1 Functional Overview.

The following abbreviations are used throughout this document:

- Kb. = kilobit

- KB = kilobyte

- Mb = megabit

- MB = megabyte

- MHz = megahertz

- ns = nano seconds

- pF = pico Farad

## Functional Description

## 2.1 Functional Overview

The cache controller in the 82C835 operates in conjunction with the main memory (DRAM) controller. All CPU accesses to locations within main memory are completed by either the cache or memory controller. The cache controller services and completes all read hits in zero wait-states. All other memory cycles are completed by the memory controller.

The 82C835 operates in non-pipeline mode only. This eliminates the performance degradation attributed to switching into pipeline mode.

The cache controller monitors all 80386sx memory accesses to determine whether the desired location resides in the cache (a "hit"). Memory read hits are performed in zero wait-states, never incurring the performance penalty from additional wait-states associated with a normal system memory controller. If the location is not in the cache (a "miss"), the main memory or system controller completes the cycle. The data read during read misses may be cached regardless of the source (local memory or AT bus memory) depending upon the state of the internal configuration registers. The width of the data accessed during cacheable read misses must be 16-bits, the cache line size of the 82C835.

Frequently accessed data usually resides inside the cache. Consequently, most memory read cycles are performed by the cache controller as it responds to read hits. Maximum performance is obtained when the ratio of read hits to total cycles (read hit rate) is high. This is the predominant case with application programs because the majority of cycles are memory code fetches.

The 82C835 integrates the tag SRAM's and cache control logic required to provide either a 16KB or a 32KB cache size. Additionally, either direct mapped or two-way set organization can be chosen via software configuration registers. External SRAMs are required to store the cache data.

## 2.2 Bus Structure Overview

The 82C835 resides between the local bus (CPU), peripheral bus (82C836), and the AT bus. With this architecture, the 82C835 is responsible for maintaing the correct address, command and data flow or "bus direction" during CPU cycles, DMA cycles, Master cycles, and Refresh cycles. It directly monitors the CPU status and control lines as well as -MASTER, -REF and PWRGOOD signals in order to determine the type of cycle occurring and control the bus direction accordingly.

Bus command signals provided by the system controller (82C836) are buffered and driven onto the AT bus. Local addresses and byte enables are latched and driven onto the AT bus as SA<19:0>, -SBHE and LA<23:17>. The bus control logic is integrated into the 82C835 and maintains operation during DMA, Master, and Refresh cycles compatible with ISA specifications.

The data SRAM's for the cache are usually placed directly on the local data bus D<15:0>. This bus is shared by the CPU, the 82C836, the local DRAM's, and an optional coprocessor. Since data SRAM access time is critical, no buffer should be placed between the SRAM's and the local data bus for most implementations.

## 2.3 Address Latching and Command Buffering

The 82C835 provides high-drive slew-rate controlled buffers for the AT I/O channel. Bus command signals provided by the system controller (82C836) are buffered and driven onto the channel. Local addresses are also buffered and driven onto the channel during CPU cycles. These signals include -IOR, -IOW, -MEMR, -MEMW, -SMEMR, -SMEMW, and -REF. Signal AEN is also driven onto the channel, but derived from logic internal to the 82C835.

At the beginning of each CPU cycle, the 82C835 latches the local address bus and byte enables. The latched address lines are driven onto the AT bus as LA<23:17> and SA<19:1>. Low address bit SA<0> is also driven onto the bus, but is a buffered version of the unlatched MODA0 input. Although both byte enables are latched for use by the 82C835, only a gated version of -BHE is driven out (as signal -SBHE). The gate logic for -SBHE is enabled to provide partial support for constant AT bus memory caching (refer to the section titled AT Chsnnel Memory Caching). The 82C835 provides the control logic necessary to correctly generate SA<2 by examining the state of HLDA from the CPU, GATEA20 from the keyboard controller, and fast GATEA20 from I/O Port 092H.

As previously stated, bus direction during DMA, Master, and Refresh cycles is compatible with ISA specifications (refer to Tables 2-1 and 2-2). In addition, address latches are kept open during these cycles.

## 2.4 Basic Cache Operation

The following sections describe the cache operation.

#### **READY Protocol**

The 82C835 uses the -READY signal to communicate servicing of read hits. When a memory read cycle is determined to be a cache read hit, the 82C835 completes the cycle by asserting -READY in the first T2 period. The 82C835 holds -READY active until sampled by the CPU at the end of T2 in order to complete a zero wait-state cycle. The main memory controller must also monitor this line at the end of the first T2 to determine whether the cache controller is claiming the cycle. If -READY is active at this time, the memory controller must not participate in the cycle. If -READY is not active, the main memory controller is free to service the read miss at the beginning of the second T2.

The 82C835 does not assert -READY for write cycles. Therefore, to improve performance, the memory controller should begin servicing all write cycles immediately. The 82C835 and 82C836 is designed to follow this protocol when the 82C836 is programmed for "Early READY" mode (CHIPS REG41H<6>=1).

### Cache Flush and Enable

Before the cache is enabled, the internal cache directory must be cleared (often referred to as "flushing"). The cache is always disabled after a system reset. To guarantee that the cache does not incorrectly respond to a given location as a hit and present false data, the system software must flush the directory before the cache is enabled. Flushing is also necessary every time the cache is disabled and re-enabled in order to guarantee coherency. The software mechanics of the cache flush and cache enable functions are discussed later in this manual.

## **Memory Read Cycles**

The first read access of a local memory location produces a read miss since the location is not initially contained in the cache directory. In response to this case, the main memory controller provides 16-bits of data (equivalent to the cache line size) and completes the cycle. At the same time, the data from main memory is stored in the external data SRAM while the cache directory is updated with the current location. Subsequent reads to this memory location results in read hits and is completed in zero wait-states until a new memory location with the same index but different tag is accessed. During read hits, the data SRAM provides the data while the 82C835 asserts -READY to complete the cycle.

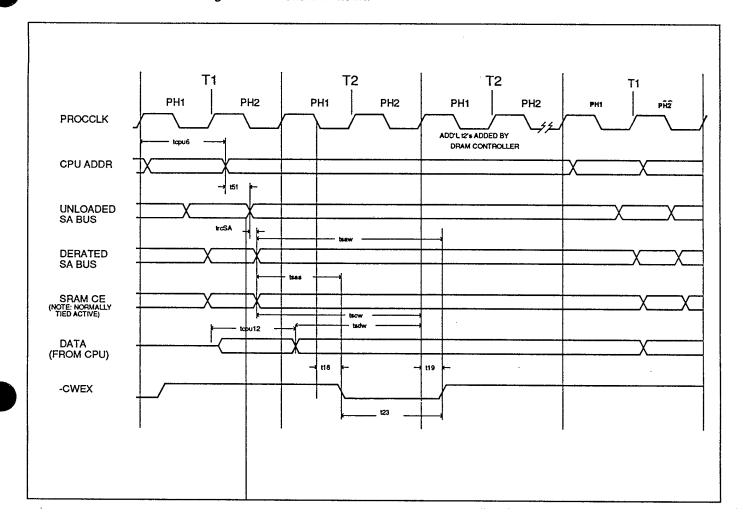

## **Memory Write Cycles**

When the system controller detects a memory write cycle, it may begin the write operation immediately; there is no need to wait for the 82C835. If the memory location of the memory write cycle is in the cache directory (a write hit), the corresponding cache data contents are updated. This update occurs in parallel with the write cycle to main memory, preventing cache data from becoming old or "stale." Write misses have no affect on the cache and are handled directly by the main memory controller.

The 82C836 system controller is optimized to produce fast DRAM write cycles in non-pipeline mode. When the 82C836 is configured for operation with the cache, local DRAM page-hit write cycles require zero wait-states, local DRAM RAS high write cycles require one wait-state, and local DRAM page-miss write cycles require three wait-states. As a result, the majority of write cycles are serviced in zero wait-states (page hits). This gives the performance of a multi-level posted write architecture without the need for expensive external FIFOs and control logic.

## Other CPU Cycles

Other CPU cycles such as I/O reads and writes, interrupt acknowledge, halts, and shutdowns are not cached. For these cases, the 82C835 allows the system controller (82C836) to complete the cycle.

## DMA and Master Cycles

In order to maintain AT compatability, the 82C835 does not respond to memory reads during Direct Memory Access (DMA) and Master operations. Although the read operation may produce a read hit, the cycle is serviced by the main memory controller or adapter card. In contrast to read misses originated by the CPU, read misses during DMA/Master mode do not update the cache directory. DMA/Master memory write misses have no affect on the cache. However, write hits update the contents of the data in the cache in order to maintain cache coherency. This update-on-write-hit scheme offers increased performance over cache schemes which invalidate on write hit for bus masters.

All 82C835 registers are inaccessible during DMA and Master operations.

## 2.5 Cache Structure

The following sections describe the two types of cache structures supported by the 82C835.

## **Direct Mapped Organization**

In the direct mapped cache, every memory location corresponds to only one possible location in the cache. The lower order address lines (A<13:5> for cache size = 16KB, A<14:5> for size = 32KB) comprise the cache directory "index" which selects one of the directory entries. There are 1024 directory entries for 32KB cache size, or 512 entries for 16KB cache size. Each entry contains two fields:

- 1. A tag field (10-bits for size = 16KB, 9-bits for size 32KB).

- 2. A 16-bit valid field.

Each tag is associated with a block of 16 words (32 bytes) of cache SRAM data. The valid bits signify which of the 16 words are valid. During a memory access, the most significant address bits are compared with the contents of the tag field. At the same time, address lines A<4:1> determine which bit in the valid field to evaluate. The memory access is considered a "hit" if the most significant address bits and tag match, and if the valid bit is set; else, the result is a "miss." Also, the least significant address bits (A<13:1> for 16KB, A<14:1> for 32KB) form the "cache address" to the external data SRAM's.

The use of slower cache data SRAM's is a primary advantage of a direct mapped cache. Because only one address comparison is required, the hit-miss decision logic is faster than the corresponding logic in an associative cache. As a result, the external SRAM is enabled earlier for a direct-mapped cache. However, the potential drawback is a lower hit rate. In a worse case scenario, program code may jump back and forth between two addresses containing the same cache directory indices. Because no two addresses with the same index can reside in the cache memory at the same time, a miss occurs after the jump,

forcing the cache controller to invalidate the entry if the cycle is a read access. Depending on the structure of the code, this drawback can be partially or completely offset by an increase of the cache size.

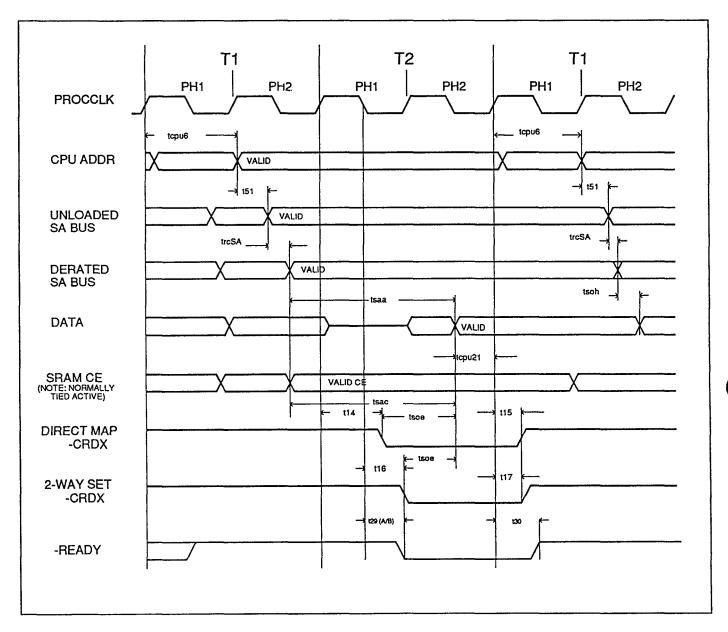

#### **Read Hits**

The external cache SRAMs provide data to the CPU for read hit cycles. For all memory read cycles, the cache controller asserts the -CRD0 signal at the beginning of T2. The -CRD0 signal should be connected to the output enable of the SRAMs. Since the chip-enable to these SRAMs is typically grounded, the output enable time of the SRAMs is a critical parameter when selecting SRAM vendors. Signal -CRD0 remains asserted throughout T2 and de-activates at the beginning of the next T-state (T1 or Ti) after assuring that CPU data hold time has been met. Therefore, no other device should drive the local data bus during the first T2 state of a memory read cycle with the 82C835 configured and enabled for direct-mapped cache.

#### **Read Misses**

When a cache read miss occurs, the requested data is not in the cache memory. The system or memory controller must provide the data. The cache controller writes a copy of the data into the cache data SRAM's. It also updates the directory depending upon the type of miss. If the tag mismatches, the upper address bits are loaded into the tag field. All valid bits are cleared except for the bit corresponding to the current word which is set. If the tag matches but the valid bit is not set, only that bit is set; no other bits of the tag or valid fields are modified. The cache controller asserts the SRAM write enable signals -CWE0H and -CWE0L in the middle of the second T2, allowing data from memory to be written into the cache as it becomes available on the local data bus. These signals remain asserted until the end of the last T2 (normal) or else until one-half of a processor clock before the end of the last T2 (early) depending on the state of REG20<3>. Refer to the section titled Write Pulse Width on Read Misses for details of the pulse width feature.

Subsequent reads to this memory location produce zero wait-state read hit until a read from another memory location with the same directory index. If this happens, a read miss occurs prompting the 82C835 to initiate an update cycle.

#### Write Cycles

When a memory write cycle is initiated by the CPU, the system or memory controller should begin the cycle immediately since the 82C835 never generates -READY for normal write cycles. If a cache hit occurs during the write cycle, the cache data SRAMs are updated. Else, the result is a cache miss, and no cache operation occurs.

On write hits, the 82C835 updates its data SRAMs during the first T2. The SRAM write enable signals -CWE0H and/or -CWE0L become asserted one-half PROCCLK after the start of T2 and terminate at the end of T2 regardless of the number of T-states required by the memory controller. This allows the 82C835 to work with memory controllers capable of zero wait-state writes.

If the system controller is the 82C836 and it is configured for operation with the 82C835, the write cycle durations are as follows:

- Zero wait-states for all DRAM page hits

- One wait-state for RAS high cycles

- Three wait-states for page misses

No additional wait-states are required for "back-to-back" write cycles. These write times have the cumulative effect of producing the appearance of a system similar to a posted write architecture with a full DRAM page of buffering during consecutive write cycles of DRAM page hits.

### Other Cycles Affecting the Cache

The external cache data SRAMs are not accessed for memory read cycles initiated by the DMA controller or other bus masters. Data for all memory reads during these types of cycles is provided by main memory or adapter card. For DMA and Master write cycles, the appropriate cache line is updated on write hits and unaffected by write misses. This assures coherency and eliminates the performance penalty of a cache line invalidation after every DMA or Master write cycle.

## Two Way Set Organization

In addition to the direct mapped option, the 82C835 also supports 16KB and 32KB two-way set-associative organization. In this cache configuration, two sets of external data SRAM's and two sets of cache directories exist. Every memory location corresponds to two possible locations in the cache, allowing two addresses with the same cache directory index to reside in the cache concurrently. The lower order address lines (A<12:5> for 16KB and A<13:5> for size = 32KB) comprise the cache directory index. Each index corresponds to two sets and an additional field for a total of five fields (two tag fields, two valid fields, and a "least-recently-used" (LRU) field). Each tag field width is 11-bits for size = 16KB and 10-bits for size = 32KB. Similar to direct mapped cache, each valid field is 16-bits wide. As with direct mapped cache, each tag applies to 16 words (32 bytes) of cache SRAM data. The valid bits signify which of the 16 words are valid. One additional field for set-associative configuration is the LRU bit which tracks the set that has been least used in order to implement a least-recently-used replacement algorithm. If a hit occurs, it is generated exclusively from one set.

For the 16KB size, each SRAM bank (or set) is 4K words (4K x 16 bits = 8KB per set) and the directory consists of 256 entries. For the 32KB size, each SRAM bank (or set) is 8K words (8K x 16 bits = 16KB per set) and the directory consists of 512 entries.

A two-way set-associative cache has the potential to yield higher performance than a direct mapped cache with applications that jump frequently between memory locations which share the same address index. However, the two-way set-associative cache also requires slightly faster SRAMs than a direct mapped cache. This requirement is because the hit-miss decision logic of a set-associative cache requires additional time to check both sets.

#### **Read Hits**

The external cache SRAMs provide data to the CPU for read hit cycles. When a read hit is detected, the cache controller asserts either -CRD0 or -CRD1 one half clock after the beginning of T2. The -CRD0 and -CRD1 signals are typically connected to the output enable of the SRAMs for set 0 and set 1, respectively. Since the chip enables of these SRAMs are typically grounded, the output enable time of the SRAMs is a critical parameter when selecting SRAM vendors. The appropriate -CRD0 signal remains asserted throughout T2 and de-activates at the beginning of the next T-state (T1 or Ti) after assuring that CPU data hold time has been met.

The cache directory is also modified during read hits. The LRU field is loaded with the number (1 or 0) of the set not producing the hit. For example, if the hit is derived from set 1, the LRU bit is loaded with a value of zero.

#### Read Misses

When a cache read miss occurs, the requested data is not in the cache memory. The system memory controller must provide the data. The cache controller writes a copy of the data of the cache data SRAM's of the set determined by the least-recently-used algorithm. It also updates the directory depending upon the type of miss and the state of the LRU bit. If both tags mismatch, the upper address bits are loaded into the tag field of the set least-recently-used. All valid bits of the same set are cleared except for the bit corresponding to the current word which is set. If a set's tag matches but valid bit not set, only that valid bit is set; no other bits of the tag or valid fields are modified. For either type of miss, the LRU field is loaded with the number (1 or 0) of the set not modified.

The cache controller asserts the SRAM write enable signals -CWE0H and -CWE0L, or -CWE1H and -CWE1L (depending on which set is chosen) in the middle of the second T2, allowing data from memory to be written into the cache as it becomes available on the local data bus. These signals remain asserted until the end of the last T2 (normal) or until one-half of a processor clock before the end of the last T2 (early) depending on the state of REG20<3>. Refer to the section titled Write Pulse Width on Read Misses for details for the pulse width feature.

Subsequent reads to the same memory location produce zero wait-state read hits until the tag is removed from the directory. The removal is a result of a read miss to a different location with the same index and different tag in combination with the LRU pointing the corresponding set.

#### Write Cycles

When a memory write cycle is initiated by the CPU, the system or memory controller should begin the cycle immediately since the 82C835 never generates -READY for normal cycles. If a cache hit occurs during the write cycle, then the data SRAMs are updated. Else, if the result is a cache miss, then no cache operation occurs.

On write hits, 82C835 updates its data SRAMs during the first T2. The SRAM write enable signals (-CWE0H and/or -CWE0L for set 0 and -CWE0H and/or -CWE0L for set 1) become asserted after the start of T2 and terminate at the end of T2 regardless of the number of T-states required by the memory controller. This allows the 82C835 to work with memory controllers capable of zero wait state writes.

The cache directory is also modified during write hits. The LRU field is loaded with the number (1 or 0) of the set not producing the hit.

### Other Cycles Affecting the Cache

The external cache data SRAMs are not accessed for memory read cycles initiated by the DMA controller or other bus masters. Data for all memory reads during these types of cycles is provided by main memory or adapter card. For DMA and Master write cycles, the appropriate cache line is updated on write hits and unaffected by write misses. This assures coherency and eliminates the performance penalty of a cache line invalidation after every DMA or Master write cycle.

## 2.6 Hardware Interface

This section gives a brief description of the 82C835 hardware interface.

## **CPU Interface**

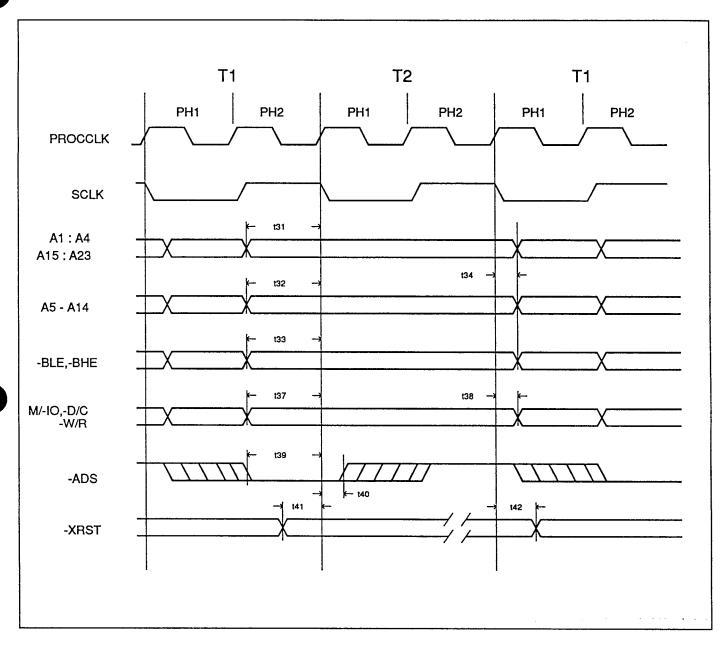

The processor clock signal (PROCCLK) provides the fundamental timing for the 82C835 state machines. This signal is synchronized on the trailing edge of the system reset signal XRST. SCLK is a diagnostic output signal that is in phase with the 82C835 clock. It can be used to monitor CPU-82C835 synchronization. SCLK is low during phase one of a T-state and high during phase two.

The CPU control, status, address lines, and byte enables M/-IO, D/-C, W/-R, A<23:0>, -BHE, -BLE connect directly from the CPU to the 82C835. Signal MODA0 is connected to the system controller (82C836) driven out as SA0.

In order to minimize the external interface, a portion of the "GATEA20" logic is duplicated inside the 82C835. The GATEA20 signal from the keyboard controller is brought into the chip and combined with the FAST GATEA20 signal from the write only register 92H<1> (duplicated in the 82C835) and HLDA and A20 from the CPU to create an internal version of the MODA20 signal. Since Port 092H is write-only, the current state of the duplicated bit is readable only through 82C835 configuration REG20H<1>. The state of the keyboard GATEA20 pin is readable in REG20H<0>.

Signals -ADS and -READY are connected directly to the CPU. Since -READY is an open collector signal that is shared by several devices, determining which device is driving it during troubleshooting is often difficult. To alleviate this problem, the -READYO diagnostic pin can be used to monitor the 82C835 contribution to -READY during the normal CPU cycles. During Hold Acknowledge State (DMA and Master), the state of -READYO diagnostic pin is indeterminate and may assert low.

### Cache Address Bus

There are two options for the source of the cache address bus. The most direct method is to connect the AT addresses bus directly to the cache data SRAMs as follows:

- 16KB direct mapped = SA<13:1>

- 32KB direct mapped = SA<14:1>

- 16KB two-way set-associative = SA<12:1>

- 32KB two-way set-associative SA<13:1>

This approach is the simplest and does not require any additional TTL parts. The SA bus is latched inside the 82C835 to guarantee address hold times at the end of cache updates. When this address interface is used, care must be taken that any add-on cards to the AT bus do not significantly degrade the signal quality of the SA bus.

The other method is to place latches between the CPU local address bus and the cache address bus (2 x 74F373 or equivalent). The 82C835 provides the cache address latch enable signal CALE so that no additional external logic is required to control these latches. Although this approach requires two additional parts, it has the advantage of making the cache address immune to the effects of loading on the AT bus.

### Cache Data Bus

The cache data bus should be connected directly to the CPU local data bus. This connection allows the SRAMs to read the same data the CPU receives from memory.

### **Channel Address Bus**

The 82C835 provides high drive buffers (24 mA) for the AT bus address lines LA<23:17>, SA<19:0> and -SBHE. These signals can directly drive the bus, and as previously stated, one architectural option is to connect the cache data SRAMs directly to the low order SA lines.

The following table summarizes the local and AT address bus direction provided by the 82C835:

Table 2-1.

82C835 Local and AT Address Bus Direction

|                         | PWRGOOD=0 -MASTER=x -MREF=x (Stand-by) | PWRGOOD=1<br>-MASTER=1<br>-MREF=1<br>(Normal) | PWRGOOD=1<br>-MASTER=1<br>-MREF=0<br>(Norm Ref) | PWRGOOD=1 -MASTER=0 -MREF=1 (Master) | PWRGOOD=1 -MASTER=0 -MREF=0 (Master Ref) |

|-------------------------|----------------------------------------|-----------------------------------------------|-------------------------------------------------|--------------------------------------|------------------------------------------|

| A<23:21>, A<19:1>, -BHE | Input                                  | Input                                         | Input                                           | Output                               | Input                                    |

| MODA0                   | Input                                  | Input                                         | Input                                           | Output                               | Input                                    |

| MODA20                  | Tri-state                              | Tri-state                                     | Tri-state                                       | Output                               | Tri-state                                |

| LA<23:17>               | Input                                  | Output                                        | Output                                          | Input                                | Output                                   |

| SA<19:17>               | Tri-state                              | Output                                        | Output                                          | Tri-state                            | Tri-state                                |

| SA<16:0>, -SBHE         | Input                                  | Output                                        | Output                                          | Input                                | Output                                   |

| A20, -BLE               | Input                                  | Input                                         | Input                                           | Input                                | Input                                    |

### **Channel Command Bus**

In addition to buffering the AT bus address lines, the 82C835 also buffers the AT bus command signals. The buffer control logic required to support DMA and Master cycles is integrated in the 82C835.

The following table summarizes the local and AT bus command direction provided by the 82C835:

Table 2-2.

82C835 Local and AT Bus Command Direction

|                         | PWRGOOD=0 -MASTER=x -MREF=x (Stand-by) | PWRGOOD=1 -MASTER=1 -MREF=1 (Normal) | PWRGOOD=1 -MASTER=1 -MREF=0 (Norm Ref) | PWRGOOD=1 -MASTER=0 -MREF=1 (Master) | PWRGOOD=1 -MASTER=0 -MREF=0 (Master Ref) |

|-------------------------|----------------------------------------|--------------------------------------|----------------------------------------|--------------------------------------|------------------------------------------|

| -XIOR, -XIOW,<br>-XMEMW | Input                                  | Input                                | Input                                  | Output                               | Input                                    |

| IOR, -IOW, -MEMW        | Input                                  | Output                               | Input                                  | Input                                | Input                                    |

| XMEMR                   | Input                                  | Input                                | Input                                  | Output                               | Input                                    |

| MEMR                    | Input                                  | Output                               | Output                                 | Input                                | Output                                   |

| SMEMR,-SMEMW            | Tri-state                              | †                                    | Output                                 | †                                    | Output                                   |

<sup>†</sup> Output if address is below 1MB; otherwise, tri-stated.

The 82C835 also generates and buffers the AEN signal to the AT bus. AEN is active during DMA cycles (i.e., -MASTER = 1 and HLDA = 1). In addition, the bi-directional refresh request signal is also buffered to/from the AT bus. -MREF from the system controller is an input during normal cycles and an output during master cycles. -REF is driven onto the AT bus except during Master cycles when it becomes an input. Note that all 82C835 registers are inaccessible during DMA and Master cycles.

## **Cache Control Signals**

The -CRD1 and -CRD0 signals are the SRAM output enables. For direct map operation, only -CRD0 is connected. For two-way set mode, -CRD1 corresponds to set 1 and -CRD0 corresponds to set 0. Signals -CWE1H, -CWE1L, -CWE0H, and -CWE0L are the SRAM write enable. These enables may be tied directly to the write enable inputs of the SRAMs. -CWE0H and -CWE0L are used for direct map as well as set 0 in the two-way set organization. -CWE1H and -CWE1L are only used for set 1 of a two-way set-associative configuration. For direct map, they should remain unconnected.

The -EXTNC (external non-cacheable area) input is provided to allow the option of selecting non-cacheable areas via external hardware decodes. An active low signal on this input indicates that the current memory location is not to be cached. This signal is monitored by the 82C835 only during read miss cycles which allows a relaxed timing requirement for this signal. Signal -EXTNC must be active before the middle of the second T2 and must remain active until the end of the read cycle. The external non-cacheable area definition cannot change without being preceded by a cache flush.

### Reset

The system reset signal XRST should be directly connected to the 82C835. This signal, in conjunction with the processor clock signal, synchronizes the internal phase clocks and resets state machines.

Signal PWRGOOD is an active high input from the power supply. When this signal is high, it indicates that all power supply voltages have reached their operating levels. The 82C835 tri-states its outputs while PWRGOOD is low. This signal is also used by the 82C836.

## 2.7 Programmable Features

The following sections list the features that are selectable via the configuration registers in the 82C835. A brief description of each programmable function is included. Refer to Section 3.1 CHIPS Configuration Registers for a complete listing of the 82C835 registers.

## Cache Enable

The cache is enabled (or disabled) by programming REG20H<7>. Writing a '1' to this bit enables the cache and writing a '0' disables it. The cache must be flushed before it is enabled or unreliable operation may result. The cache is disabled when the 82C835 is reset and remains disabled until explicitly enabled by software.

## **Directory Freeze**

This is a diagnostic mode that prevents the cache directory from being updated on read misses. When this mode is selected, only write hits update the cache data SRAMs. This feature is a useful diagnostic tool for isolating write hits and examining the contents of the cache directory. This mode is enabled by writing a '1' to REG20H<5>. The default value after a reset is '0,' which produces normal directory operation when the cache is enabled.

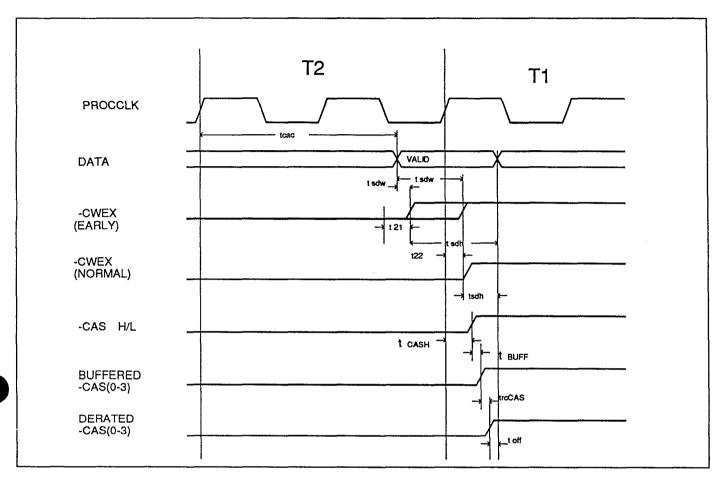

## Write Pulse Width on Read Misses

This option determines when the write enables to the SRAMs are deactivated during read misses. It has no effect and is not needed during write hit cycles since data will remain available until the middle of the T-state following a write cycle. Two modes are available: "Normal CWE mode" causes the -CWExx signals to be disabled at the end of the first T2 of a read miss; "Early CWE mode" de-asserts the signals one half of a processor clock earlier.

The early mode is intended for systems that would otherwise have difficulty satisfying the local data bus hold times of both the CPU and SRAMs. When this mode is selected, the memory controller must only meet the CPU required hold time for the local data bus. It need not satisfy the SRAM hold time because the SRAM update finishes before the CPU read is completed. The disadvantage of this mode is that the DRAM controller MUST provide data earlier to guarantee that the SRAM parameter tDW (tDW = minimum time required for data to be valid until the end of the SRAM write) is satisfied. Typically, with the early

mode selected, the memory controller inserts one wait-state during read misses to satisfy this parameter.

The normal mode requires the memory controller to hold data on the local bus long enough to satisfy both the CPU and the data SRAMs. The 82C836 has been designed to satisfy the 82C835 by guaranteeing that the memory CAS signals remain active long enough into the beginning of the following T-state to meet the cache SRAM's hold time requirement. This means that the 82C835 provides data on the local bus in time to meet the CPU data setup specification and holds it long enough to meet the cache data SRAM. As a result, the 82C836 can be programmed for zero CAS extended wait states and still meet the SRAM setup time. REG20<3> is used to select this option. A value of '1' enables the early -CWExx mode and a '0' sets the 82C835 to normal -CWExx mode (default).

## **Directory Flush**

The cache directory should always be flushed before the cache is enabled. The flush invalidates all entries, preventing erroneous hits and hits to locations containing stale data. Flushing can be accomplished by first writing a '1' to REG20<2> and then performing memory read cycles to all entries in the cache directory. For example, reading a 16KB block of contiguous memory with the flush bit set invalidates all entries for a 16KB direct mapped cache. A 16KB two-way set-associative cache requires a read to 8KB of contiguous memory.

Other cases requiring cache flushing include redefinition of cacheable areas and re-enabling the cache after disabling it. The following provides an example of flushing cache.

```

AX, 0420

MOV

;SETTING REG20<2>

22, AL

OUT

AH, AL

XCHG

; ENABLING DIRECTORY FLUSH

OUT

23,AL

BX,8000

;SETTING 32KB FLUSHING AREA

:FLUSHING

MOV

; READING ONE WORD FROM AREA

AX, [BX]

MOV

BX,02

; INCREMENT NEXT WORD AREA

ADD

; END OF FLUSHING AREA

JNZ

FLUSHING

AX,0020

;SETTING REG20<2>

MOV

OUT

22,AL

XCHG

AH, AL

23, AL

; DISABLING DIRECTORY FLUSH

OUT

AX,8020

;SETTING REG20<7>

MOV

22, AL

OUT

XCHG

AH, AL

TUO

23, AL

; ENABLING CACHE OPERATION

```

PRELIMINARY

## **Direct SRAM Access**

The 82C835 allows the contents of the external data SRAMs to be directly examined and modified when in this diagnostic mode. Normal memory read and write cycles access the SRAMs directly. The 82C835 provides the -READY for these cycles in zero wait states. During direct SRAM reads, the memory controller samples -READY and does not interfere with the cycle, similar to its response during a cache read hit. For direct SRAM writes, the memory controller must have a programmable mode to prevent it from initiating a write to memory until after it verifies that -READY did not occur in the first T2. The 82C836 contains such a mode. This diagnostic mode is disabled after a reset (default normal cache operation).

The starting memory address of the directly accessible SRAMs in this mode is user selectable. REG24H<4:0> contains a 5-bit value corresponding to the system address lines A<19:15> and determines the starting SRAM location in the memory map. For example, a value of '01000' in REG24H<4:0> corresponds to a starting SRAM address of 40000H.

When in direct mapped mode, a 16KB cache appears as main memory with a memory base address specified in register 24H. The address range begins at the base address and extends to the base + 3FFFH. Similarly, a 32KB cache range starts from the same base and extends to the base + 7FFFH.

For a 16KB two-way set-associative cache, accesses start at the base location specified in REG24H<4-0> with an offset range of 0-1FFFH for set 0, and an offset range of 2000H-3FFFH for set 1. A 32KB cache accesses the SRAM starting at the selected memory base plus an offset range of 0-3FFFH for set 0 and an offset range of 4000H-7FFFH for set 1. (All direct writes to SRAM must be 16-bits wide cycles.)

## **Directory Access**

The internal directory of the 82C835 may be accessed with the following I/O sequence:

- 1. Load REG21H<7> with a '1' to enable directory access. Also, select the desired directory field by writing the appropriate value to REG21<6-3>.

- 2. Load REG21H<1-0> and REG22H with the directory index pointing to the desired entry.

The selected field can now be accessed through REG23H. An I/O read from REG23H reads the corresponding contents of the directory field and an I/O write to REG23H loads the value into the directory field.

## Cache Type (Direct Mapped or Two-Way Set-Associative)

The cache type is software selectable. Direct map is the default mode, but since the cache is disabled after a reset, two-way set mode can be selected by software before the cache begins operation. Configuration REG24H<7> controls this option. Writing a '1' to this bit enables the 82C835 to operate as a two-way set-associative cache and writing a '0' selects a direct mapped organization.

The cache size is programmed by REG24H<5>. Writing a '1' to this bit indicates that a 32KB of external cache SRAM exists. Writing a '0' (default) specifies a 16KB cache.

## Cacheable Areas

The 82C835 recognizes two types of cacheable areas: those defined by configuration registers, and those defined by the external non-cacheable area input -EXTNC. Non-cacheable regions must be selected BEFORE enabling the cache. Once an area is defined as cacheable and the cache enabled, changing that area to a non-cacheable region will not prevent hits resulting from accesses to that area from continuing to occur. Therefore, the cache should be flushed anytime an area is re-defined from cacheable to non-cacheable. When an area is defined to be non-cacheable, read misses to that area will not update the internal directory or external SRAMs. Write hits will never occur since a write hit only occurs after a read miss update cycle to that particular address has previously occurred. Chips configuration registers 28H-2DH and 2FH define cacheable regions.

## **RAM Write Protect**

Configuration register 2EH allows the area between C0000H and FFFFFH to be designated as either read-only or readable and writeable. Each bit in the register corresponds to 32KB segment of memory with bit 0 referring to segment 0C0000H-0C7FFF.

## **AT Channel Memory Caching**

The 82C835 is capable of caching AT bus memory as well as motherboard DRAM memory. For 16-bit memory read cycles, the data will be cached regardless of the source if the location is configured as cacheable. However, to guarantee caching of extended memory on the AT bus, 16-bits of data must always be presented to the CPU for read cycles. The 82C835, in conjunction with 82C836, support a feature to force 16-bit read cycles to AT bus memory.

To achieve these 16-bit cycles, -SBHE can be forced low by enabling REG24<6> with a logic '1' and loading REG25 (AT memory boundary) with a value designating the starting address of AT Bus Memory. The 8-bit value corresponds to the upper 8 bits of the AT address. For all CPU read cycles, the upper 8 bits of CPU address (A<23:16>) are compared with the value in REG25H. If the CPU address is equivalent or greater, the 82C835 assumes the memory resides on the AT bus. As an example, if REG25H contains the value '0001 0000B, all access at and above 0100000H are considered AT memory access.

With the feature enabled, signal -SBHE from the 82C835 and MODA<0> from the system controller are always asserted low during memory read cycles to the defined AT address memory space, effectively generating a 16-bit access to the AT bus and allowing the 82C835 to cache the data.

Note

The Memory Boundary register (REG25H) should never be set below 1MB (less the 10H). Also, certain types of adapter cards must not be cached. These adapters include those which contain either memory-mapped I/O or multi-ported memory. Configuration registers are provided in the 82C835 to define "non-cacheable" memory address spaces.

## 2.8 Design Considerations

The following considerations should be observed when designing a system with the 82C835.

## Clocks