#### 82C110 IBM™ PS/2 MODEL 30 AND SUPER XT™ COMPATIBLE CHIP

- 100% PC/XT compatible

- Build IBM PS/2™ Model 30 with XT software compatibility

- Bus Interface compatible with 8086, 80C86, V30, 8088, 80C88, V20

- Includes all PC/XT functional units compatible with:

8284, 8288, 8237, 8259, 8254, 8255, DRAM control, Keyboard control, Parity Generation and Configuration registers

The 82C110 is a single chip implementation of most of the system logic necessary to implement a super XT compatible system with PS/2 Model 30 functionality using either an 8086 or 8088 microprocessor. The 82C110 can be used with either 8 or 16-bit microprocessors. The 82C110 includes features which will enable the PC manufacturer to design a super PS/2 Model 30/XT compatible system with the highest performance at 10 MHz zero wait state system with an 8086, the highest func-

- Key superset features: EMS control, dual clock, and 2.5 MB DRAM support

- Complete system requires 12 ICs plus memory

- 10 MHz Zero wait state operation

- Applicable for high performance Desktop PCs and CMOS industrial Control Applications

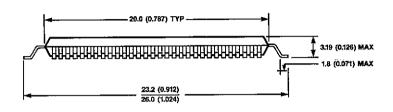

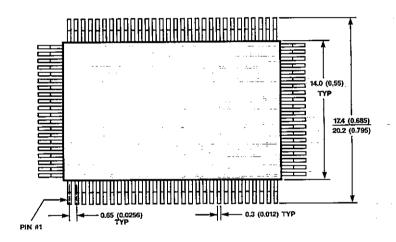

- Single chip implementation available in 100-pin flat pack

tionality with dual clock and 2.5 MB DRAM (with integrated Extended Memory System control logic), the highest integration with the lowest component count SMT design.

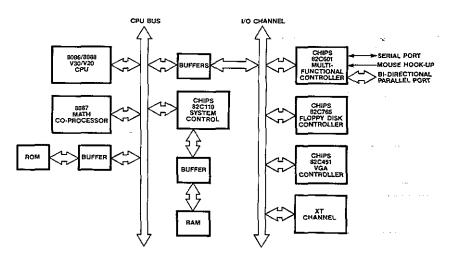

The 82C110 can be combined with CHIPS' 82C601 Multifunction Controller and 82C451 VGA Graphics Controller to provide a high performance, high integration PS/2 Model 30 type system.

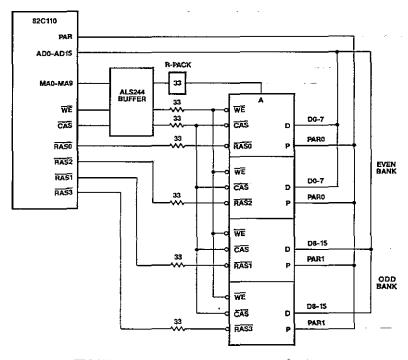

Figure 1. Super XT Model 30 Compatible System

The 82C110 supports most of the peripheral functions on the PS/2 Model 30 planar board: 8284 compatible clock generator with the option of 2 independent oscillators, 8288 compatible bus controller, 8237 compatible DMA controller, 8259 compatible interrupt controller, 8254 compatible timer/counter, 8255 compatible peripheral I/O port, XT Keyboard interface, Parity Generation and Checking for DRAM memory and memory controller for DRAM memory sub-system.

The 82C110 enables the user to add PS/2 Model 30 superset functionality on the planar board: dual clock with synchronized switching between the two clocks, built-in Lotus-Intel-Microsoft<sup>18</sup> (LIM) EMS support for up to 2.5 Megabytes of DRAM.

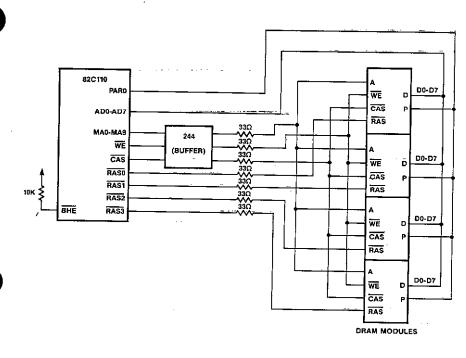

The 82C110 supports a very flexible memory architecture. The DRAM controller supports 64K, 256K and 1M DRAMs. These DRAMs can be organized in four banks of up to a maximum of 2.5 MB on the planar board. The 2.5 MB memory can be implemented with 2 banks of 1M X 1 DRAMs, partitioned locally as 640KB of real memory and 1.875 MB of EMS memory.

The 82C110 is packaged in a 100-pin plastic flatpack.

CHIPS and Technologies, Inc. 3050 Zanker Road, San Jose, CA 95134 408-434-0600 Telex 272929 CHIPS UR

#### COPYRIGHT NOTICE

Copyright ♥ 1990, Chips and Technologies, Inc. ALL RIGHTS RESERVED.

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of Chips and Technologies.

#### TRADEMARKS

CHIPS, NEAT, CHIPSport are registered trademarks of Chips and Technologies, Inc. CHIPSport, LeAPset-sx, PEAKset/386, NEATsx, CHIPS/250, CHIPS/280, SCAT, MicroCHIPS, M/PAX, CHIPS/Ink, CHIPSport, CHIPSport are registered trademarks of Chips and Technologies, Inc.

JBM, EGA, IBM PC, IBM PC AT, IBM XT, and IBM PC XT are registered trademarks of International Business Machines Corporation, P/S2, Micro Channel, and Personal System/2 are trademarks of International Business Machines Corporation.

MS-DOS is a registered trademark of Microsoft Corporation.

Intel, 386, 387, 386SX and 387SX are trademarks of Intel Corporation,

#### DISCLAIMER

Chips and Technologies, Inc. makes no representations or warranties regarding the contents of this manual. We reserve the right to revise the manual or make changes in the specifications of the product described within it at any time without notice and without obligation to notify any person of such revision or change.

The information contained in this manual is provided for general use by our customers. Our customers should be aware that the personal computer field is the subject of many patents. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents, it is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

#### RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

|             |                | 91     | <u>چ</u> ا | <b>∞</b> ( | اء <u>ا</u> | &   &      | 0 I 4 | ım     | 101   |       |             | ı m      | l an  | ١٠.              | Lia   |                   |            |             | ۱   |       |      |   |      |       |    |

|-------------|----------------|--------|------------|------------|-------------|------------|-------|--------|-------|-------|-------------|----------|-------|------------------|-------|-------------------|------------|-------------|-----|-------|------|---|------|-------|----|

|             |                | 8      | ్          | <u>~</u>   | <u></u>     | 9 0        | 8 8   | ឌ      | 66    | 91    | ន           | Ľ        | 2     | 8                | 85    | \$                | BA         | 83          | 器   | Į₹    | 1    |   |      |       |    |

|             |                | Ĕ      | RQ7        | ROG        | RQS         | ğ ;        | 200   | PARO   | PAR1  | 품     | ă           | 0        | MAO   | 41               | ĺZ    | 2                 | Z          | . ¥         | ပ္  | Ŀ     | :    |   |      |       | 7  |

|             | 1              | KBDATA | Ξ          | 竺          | ≝           | <u>e</u> 1 | Ξ Ξ   | å      | ď     | 0     | PWRGOOD     | RESERVED | 3     | MA               | OBEN  | 200               | OFN        | SYSCLK      | ž   | RESET |      |   |      |       | 1  |

|             |                |        |            |            |             |            |       |        |       |       | Ä           | SE       |       |                  |       |                   |            | σj          |     | ~     |      |   |      |       |    |

| _1_         | KBCLK/I        | IRQ    | 1          |            |             |            |       |        |       |       | Š           | ä        |       |                  |       |                   |            |             |     |       |      |   | RE   | ADY   | 80 |

| 2           | Vcc            |        |            |            |             |            |       |        |       |       |             | •        |       | ٠.               |       |                   | ٠          |             |     | -     |      |   |      | RST   | 79 |

| 3           | GND            |        |            |            |             |            |       |        |       |       |             |          |       |                  | -     |                   |            |             |     |       |      |   |      | νcc   | 78 |

| 5<br>6<br>7 | MREF           |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   |      | osc   | 77 |

| 5           | RESERV         | ED     |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   | (    | GND   | 76 |

| - 6         | A19            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   | P    | osc   | 75 |

| .7          | A18            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   |      | CX2   | 74 |

| 8           | A17            |        |            |            |             |            |       |        |       | R2    | ٠٠.         | 110      |       |                  |       |                   |            |             |     |       |      |   |      | CX1   | 73 |

|             | A16<br>AD15    |        |            |            |             |            |       | FL     | ATI   |       |             |          |       | )U               | г     |                   |            |             |     |       |      | Ī | OCH  | СНК   | 72 |

| 10          | AD15<br>AD14   |        |            |            |             |            |       |        | 7     | O     | Pγ          | ΊE       | W     |                  |       |                   |            |             |     |       |      | ŀ | OCH  | RDY   | 71 |

| 11_         | AD13           |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   | SPKC | ATA   | 70 |

| 12          | AD12           |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   |      | BIN   | 69 |

| 13          | AD11           |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   | P    | BEN   | 68 |

| 14          | AD10           |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   | 1    | MA2   | 67 |

| 15          | AD9            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   | - 1  | MA8   | 66 |

| 16          | AD8            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   | - 1  | PAM   | 65 |

| 17          | AD7            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   |      | NMI   | 64 |

| 18<br>19    | AD6            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   |      | IMM   | 63 |

|             | AD5            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   | RON  |       | 62 |

| 20<br>21    | AD4            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      | - | RQ/i |       | 61 |

| _           | AD3            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   |      | WE    | 60 |

| 22<br>23    | AD2            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   |      | CAS   | 59 |

|             | AD1            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   |      | AS3   | 58 |

| 24<br>25    | AD0            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   | _    | AS2   | 57 |

|             | Vcc            |        |            |            |             |            |       |        |       | -     |             |          |       |                  |       |                   |            |             |     |       | -    |   |      | 451   | 56 |

| 26<br>27    |                | _      |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   | _    | ASO   | 55 |

| 28          | RESERVE<br>N/C | U      |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   |      | AAG . | 54 |

| 29          | INTR           |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   |      | ND    | 53 |

| 30          | GND            |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   |      | EN    | 52 |

| 30          |                |        |            |            |             |            |       |        |       |       |             |          |       |                  |       |                   |            |             |     |       |      |   | 4    | LE    | 51 |

|             |                |        |            |            | 100         | ≥          | en .  | N -    | _     |       |             |          |       | 1                | ៗ រ   | <u>ا بع</u>       | Ξ          | ΙΞ          |     |       |      |   | -    | 1     |    |

| ľ           |                |        | ľ          | 3          | : 🚡         | 3          | DRO3  | e è    | 2 9   | 2     | 4           | MA7      | MA5   |                  | DACK3 | DACK2             | DACK       | RO/GT       |     | _     |      | - |      |       |    |

| Į           |                | ٨      | 12         | 15         | : 12        | 12         | ō١    | 2 0    | •     | Σ:    | Σ.          | 3        | 2     | ۲ı               | ا ō   | ۵ŀ                | ã          | ř           | ા જ | ĊΟ.   | ន    |   |      | - 1   |    |

|             |                | _      | ev.        | 33         | 34          | 35         | 98    | 3 8    |       | n 0   | ⊋ :         | £ :      | ş  ş  | 2 5              |       | : ا ءِ            | ٦          | ~ [         | o o |       | _    |   | •    |       |    |

|             |                |        | • 67       | 160        | 163         | 1 (9 1     | (C) ( | 73   E | 3 1 6 | 9 ( 4 | <b>~</b> !· | 4  -     | œ   • | <del>-</del>   - | -   - | <del>o-</del>   • | <b>4</b> ( | <b>→</b> 1÷ | ÷ ÷ | 1     | i en |   |      |       |    |

## 82C110 Pin Description

| Pin<br>No. | Pin<br>Type | Symbol  | Pin Description                                                                                                                                                                                                                                                                                                                                       |

|------------|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ciocks     | and Rese    | t Logic |                                                                                                                                                                                                                                                                                                                                                       |

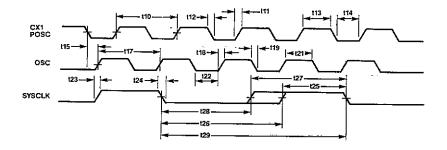

| 73         | l           | CX1     | Crystal/oscillator input. CX1 is an input for a passive crystal circuit or packaged oscillator to generate the initial system timings. This frequency is divided by three to generate the default system clock when the system is powered up. The type of crystal is 14,31818 MHz, parallel resonance, fundamental frequency.                         |

| 74         | 0           | CX2     | Crystal/oscillator output. CX2 is the inverted output of CX1. If a crystal is used, then CX2 should be connected to the crystal circuit. If an oscillator is used, then CX2 should be left unconnected.                                                                                                                                               |

| 75         | š           | POSC    | Optional Oscillator input. The POSC input is divided by three to generate alternate system timing (other than 4.77 MHz). Typically POSC is a 24 MHz or 30 MHz oscillator with a 50% duty cycle, for 8 MHz or 10 MHz sytems, respectively. The maximum POSC frequency is 30 MHz. System timing is software selectable from the configuration register. |

| 83         | 0           | SYSCLK  | System Clock. SYSCLK is a continuous running clock with selectable frequency and duty cycle. The duty cycle is either 33% for INTEL 808X CPUs, or 50% for NEC V20/30 CPUs. The SYSCLK frequency is selected from either 1/3 of the POSC or 1/3 of the CX1 frequencies. The default is 4.77 MHz, 33% duty cycle.                                       |

| 77         | 0           | osc     | Oscillator output. OSC is a continuous running square wave with a 50% duty cycle, derived from the frequency generated by CX1. Normally this is used for the 14.3818 MHz.                                                                                                                                                                             |

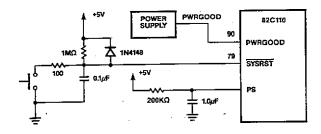

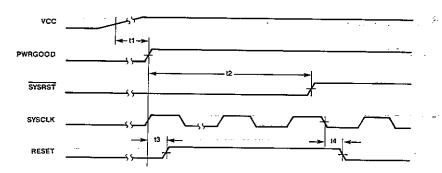

| 90         | Ī           | PWRGOOD | Power Good. An active high indicator that the power supply is stable, it also starts the clocks and the internal system functions. PWRGOOD is generated by the power supply, by monitoring V <sub>CC</sub> .                                                                                                                                          |

| Pin<br>No.     | Pin<br>Type | Symbol            | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|----------------|-------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 79             | 1           | SYSRST            | System Reset. SYSRST is an active low Schmitt trigger input for power-up reset. SYSRST initializes the 82C110 circutry. This signal also generates the RESET output used to reset the CPU, 8087 and other peripherals. It should be held active until PWRGOOD becomes active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| CPU I          | nterface    |                   | The second secon |  |  |  |  |  |  |

| 81             | 0           | RESET             | RESET. RESET is an active high output derived from the SYSRST input. RESET should be used to reset the CPU, the 8087, and the external peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 48<br>49<br>50 | 1<br>1<br>1 | \$2<br>\$1<br>\$0 | Processor Status Signals. These signals are status inputs from the CPU. \$0-\$2 should be pulled up with 4.7K-10K resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 91             | t           | BHE               | Byte High Enable. BHE is an input signal. BHE and A0 from the CPU indicate the type of bus transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|                |             |                   | BHE A0 Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                |             |                   | 0 0 16 bit transfer<br>0 1 odd byte transfer<br>1 0 even byte transfer<br>1 1 invalid (for 16 bit CPU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                |             |                   | If the 82C110 is used with an 8 bit processor, BHE should be tied high through a 4.7K to 10K resistor. The 82C110 uses the "invalid" state to perform the correct bus conversion for a 16-bit processor. BHE is floated to the high impedance state during "hold" cycles, so it should be pulled up with 4.7K-10K resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

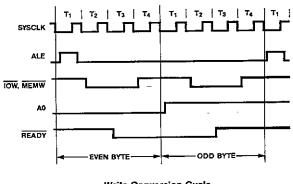

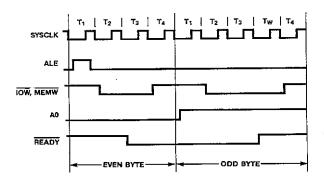

| 80             | 0           | READY             | READY. READY is an active high, asynchronous output indicates that a memory or I/O transfer can complete. READY is internally synchronized to meet the setup/hold times of the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Pin<br>No.                                                                                   | Pin<br>Type                             | Symbol                                                                                                             | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

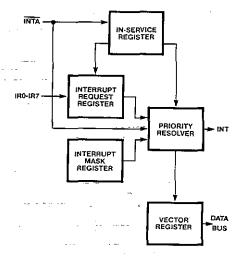

| 29                                                                                           | 0                                       | INTR                                                                                                               | interrupt Request. INTR is an active high output from the internal Interrupt Controller. It should be connected to the INTR pin of the CPU.                                                                                                                                                                                                                                                                                            |

| 64                                                                                           | 0                                       | NMI                                                                                                                | Non-Maskable Interrupt. A LOW to HIGH transition on NMI causes an interrupt at the end of the current instruction. It should be connected to the NMI input of the CPU.                                                                                                                                                                                                                                                                 |

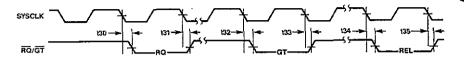

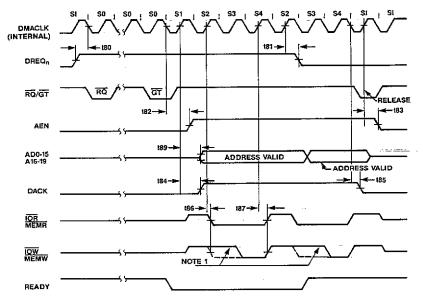

| 61<br>47                                                                                     | 8<br>8                                  | RO/GTI<br>RO/GTI                                                                                                   | Request/Grant. These signals are used by bus masters other than the CPU to gain control of the CPU local bus. In the Model 25/30 or XT application, the other bus masters are the 8087 numeric co-processor, and the 82C110 itself. RQ/GT0 has higher priority than RQ/GT1. 808X RQ/GT signals are internally pulled up, so external pullups are not necessary. See the Request/Grant section of this data sheet for more information. |

| Local                                                                                        | Bus Interf                              | ace                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6<br>7<br>8<br>9                                                                             | 8<br>8<br>8<br>8                        | A19<br>A18<br>A17<br>A16                                                                                           | Address Bits A19-16. During processor cycles, these are inputs for the high order address bits. During DMA cycles, the 82C110 sources the high order address on these lines. These should be connected directly to the processor address lines and to the system address latches.                                                                                                                                                      |

| 10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25 | 888888888888888888888888888888888888888 | AD15<br>AD14<br>AD13<br>AD12<br>AD11<br>AD10<br>AD9<br>AD8<br>AD7<br>AD6<br>AD5<br>AD4<br>AD3<br>AD2<br>AD1<br>AD0 | Local Address/Data Bus Bits 15:0. During the 71 phase of a CPU cycle the processor sources the address on these lines. The 82C110 sources the address during hold acknowledge and interrupt acknowledge cycles. AD0-AD7 should be isolated from the 82C110 using bidirectional buffers to prevent bus contention during bus conversion cycles. PBEN enables the buffers and PBIN controls the direction.                               |

| 31                                                                                           | 0 .                                     | Α0                                                                                                                 | Address Bit 0. This signal represents the state of address bit 0. It is latched and should be used throughout the system instead of AD0 that would normally be latched externally from the AD bus. The 82C110 toggles this bit during bus conversion cycles. It should be buffered (in a normal system) but not routed through transparent latched like the other address bits.                                                        |

| Pin<br>No. | Ріл<br>Type    | Symbol  | Pin Description                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

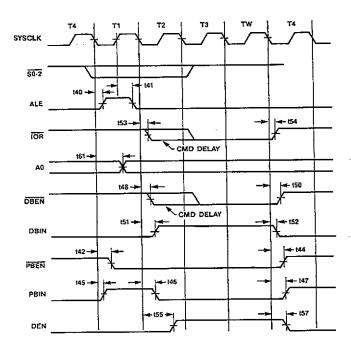

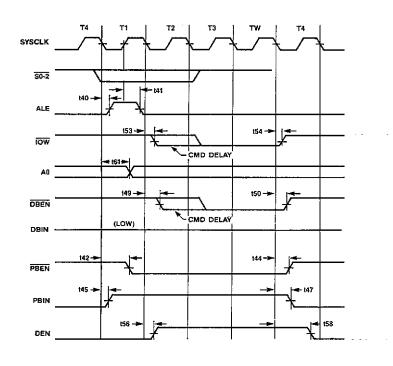

| 32         | ō              | IOR     | I/O Read. An active low strobe that informs the I/O devices to put their data on the bus. All the commands (MEMR MEMW, IOR, and IOW) can be delayed one cycle through software. The delay is necessary when running the CPU at high speed. Delaying the commands allow more data and address setup time. Default is no delay.                                                                          |

| 33         | o <sup>_</sup> | TOW     | I/O Write. An active low strobe that informs the I/O devices that data is available on the bus.                                                                                                                                                                                                                                                                                                        |

| 34         | 0              | MEMR    | Memory Read. An active low strobe that informs the memory devices to put their data on the bus.                                                                                                                                                                                                                                                                                                        |

| 35         | 0              | MEMW    | Memory Write. An active low strobe that informs the memory devices that data is available on the bus.                                                                                                                                                                                                                                                                                                  |

| 51         | 0              | ALE     | Address Latch Enable. ALE is used by the address buffer, latch to latch the address. During the second half of a bus conversion cycle, a second ALE will not be generated by the 82C110.                                                                                                                                                                                                               |

| 52         | Ō.             | AEN     | Address Enable. When high, this signal is an indication to the devices on the I/O channel that DMA is active, meaning the DMA channel has control of the address bus, data bus, and the appropriate command lines.                                                                                                                                                                                     |

| 84         | O              | DEN     | Data Enable. Provided to control the output enable of 245 type transceiver. DEN is active during memory and 1/O accesses and for INTA cycles. It floats to the high impedance state in "hold acknowledge" cycles. This signal is equivalent to the DEN signal generated by an 8288 bus controller. It is normally not used in XT/Model 30 type applications.                                           |

| 93         | В              | PAR0    | Parity Bit 0. The parity bit from the low order byte of the DRAMs. A HIGH means there are an odd number of 1's in memory, including the parity bit itself, thus odd parity.                                                                                                                                                                                                                            |

| 92         | В              | PAR1    | Parity Bit 1. The parity bit from the high order byte of the DRAMs. A HIGH means there are an odd number of 1's in memory, including the parity bit itself, thus odd parity. This signal is not used in 8 bit only systems.                                                                                                                                                                            |

| 71         | I              | IOCHRDY | I/O Channel Ready. An active high signal from the I/O channel. It is normally HIGH indicating that the addressed device on the channel is ready to complete the data transfer. Slow I/O or memory devices pull this signal LOW to lengthen bus cycles, IOCHRDY should be pulled up with a 4.7K resistor, because if there are no add-in boards present, this signal would float to an undefined state. |

| Pin<br>No.                                               | Pin<br>Type          | Symbol                                                             | Pin Description                                                                                                                                                                                                                                                      |

|----------------------------------------------------------|----------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 72                                                       | ı                    | ТОСНСНК                                                            | I/O Channel Check. This signal goes low when there is parity or other error on memory or devices on the I/O channel. IOCHCHK should be pulled up with a 4.7K resistor, because if there are no add-in boards present, this signal would float to an undefined state. |

| Buffer                                                   | r Controls           |                                                                    |                                                                                                                                                                                                                                                                      |

| 86                                                       | 0                    | DBEN                                                               | Data Buffer Enable. DBEN enables the data transceiver between the I/O channel data bus and 82C110.                                                                                                                                                                   |

| 85                                                       | 0                    | DBIN                                                               | Data Buffer Direction. A HIGH allows data to flow from the I/O channel to the internal bus. Normally low, this means the data direction is to the I/O channel, DBIN is used to control the direction of the buffer for the system data bus.                          |

| 68                                                       | 0                    | PBEN                                                               | Processor Buffer Enable. An active low signal, PBEN enables the data buffer between the processor and the 82C110. It is high during DMA cycles so that the data bus is tri-stated. PBEN is qualified with DEN to avoid bus contention during T2 cycles.              |

| 69                                                       | 0                    | PBIN                                                               | Processor Buffer Direction. A HIGH on PBIN allows data to flow from the processor to the 82C110. PBIN controls the direction of the data buffer on the local data bus.                                                                                               |

| Mem                                                      | ory Contro           | ls                                                                 |                                                                                                                                                                                                                                                                      |

| 62                                                       | 0                    | ROMOS                                                              | ROM Chip Select. This signal goes low for memory accesses in the address range F0000H-FFFFFH. It would normally be tied to the chip select inputs of the BIOS ROM(s).                                                                                                |

|                                                          | All DRAM<br>9 memory |                                                                    | RAS3-0, CAS and WE should be buffered if connected to more                                                                                                                                                                                                           |

| 65<br>66<br>41<br>54<br>42<br>40<br>39<br>67<br>87<br>88 | 0000000000           | MA9<br>MA8<br>MA7<br>MA6<br>MA5<br>MA4<br>MA3<br>MA2<br>MA1<br>MA1 | Multiplex Address Bits 9-0. Should be connected to DRAM address bits 9-0.                                                                                                                                                                                            |

| Pin<br>No.           | Pin<br>Type | Symbol                       | Pin Description                                                                                                                                                                                                                                                          |

|----------------------|-------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55<br>56<br>57<br>58 | 0 0 0       | RASO<br>RASI<br>RAS2<br>RAS3 | RA\$3-0. Active low row address strobes for DRAM banks 0-3. Each bank is 9 bits wide (1 bit for parity). Byte referencing is done using the RA\$ signal. For more information, see the DRAM Interface section of this data sheet.                                        |

| 59                   | 0_          | CAS                          | CAS. Active low column address strobe for all DRAMs.                                                                                                                                                                                                                     |

| 60                   | 0           | WE                           | WE. Active low write enable for all DRAMs.                                                                                                                                                                                                                               |

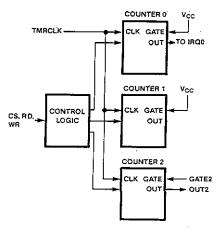

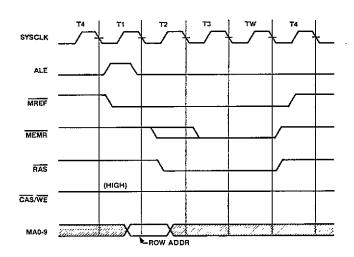

| 4                    | 0           | MREF                         | Memory Refresh. MREF is the output of the independent refresh timer signifying that a refresh cycle is occurring. The refresh rate is programmable from 838 ns to 214 µs.                                                                                                |

| DMA an               | d Interru   | pt Controller Inte           |                                                                                                                                                                                                                                                                          |

| 36<br>37<br>38       | 1           | DRQ3<br>DRQ2<br>DRQ1.        | DMA Request 3-1. These signals are asynchronous requests used by peripherals to request DMA services. They have a fixed priority: channel 1 is the highest and channel 3 is the lowest. DRQ must be held active HIGH until it is acknowledged by the corresponding DACK. |

| Pin<br>No.                       | Pin<br>Type | Symbol                               | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------|-------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44<br>45<br>46                   | 000         | DACK3<br>DACK2<br>DACK1              | DMA Acknowledge 3-1. An active low acknowledgement signal generated by the 82C110 as a result of a request for DMA service (via a DRQ line) and a successful arbitration. These lines must be pulled up with 10K0hm resistors.                                                                                                                                                                                                                                                                                                                                                                          |

| 43                               | 0           | TC                                   | Terminal Count. An active high output pulse from the DMA Controller, indicating the end of a DMA transfer (transfer count register = 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 94<br>95<br>96<br>97<br>98<br>99 | 1           | IRQ2<br>IRQ3<br>IRQ4<br>IRQ5<br>IRQ6 | Interrupt Request 2-7. Active high asynchronous inputs to<br>the interrupt controller generated by I/O devices. They are<br>edge-triggered, but should be held active HIGH until<br>acknowledged.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 63                               | 1           | NPNMI                                | Numeric Co-Processor NMI. An active high signal indicating that an error has occurred during numeric instruction execution. This is an active high, edge-sensitive input. If enabled, will cause an NMI to the CPU. The NMI service routine has to determine which NMI occurred by reading the NMI Status Register.                                                                                                                                                                                                                                                                                     |

| Keybo                            | pard and S  | peaker Interface                     | ## ### ### #### ######################                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1                                | В           | KBCLK/IRO1                           | Keyboard Clock/Interrupt Request 1. KBCLK is a bidirectional open drain signal. Defaults to KBCLK when using an XT style keyboard. The 82C110 synchronizes the internal keyboard logic with this signal. It sources the clock for the keyboard when sending serial data to the keyboard and receives the clock when the keyboard is sending data. If an external Model 25/30 style keyboard interface is used (and selected through the Internal Configuration Register), IRQ1 is the shared, active high Interrupt Request 1 input from the keyboard controller, pointing device, and real time clock. |

| 100                              | В           | KBDATA                               | Keyboard Data. KBDATA is an open drain bidirectional serial data to or from the keyboard. This line is unused if a Model 25/30 external keyboard interface is used.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin<br>No.     | Pin<br>Type | Symbol          | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70             | 0           | SPKDATA         | Speaker Data. SPKDATA should be buffered, and the output of the buffer should go through a low pass filter. The output of the filter connects to the speaker.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Power a        | and Grou    | nds             | The second secon |

| 2,26,78        |             | V <sub>CC</sub> | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3,30,<br>53,76 | _           | GND             | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

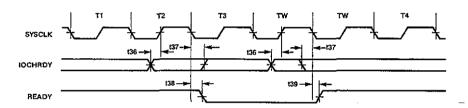

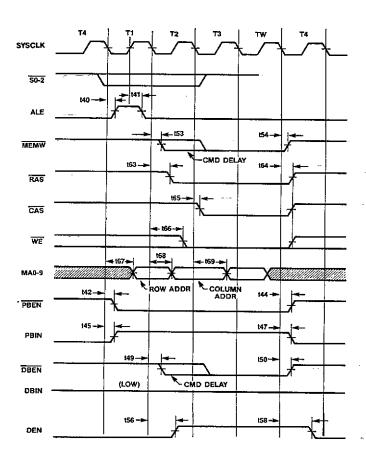

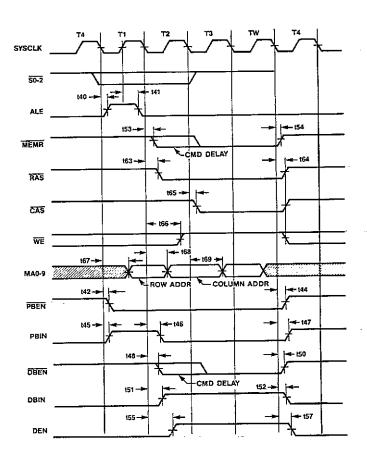

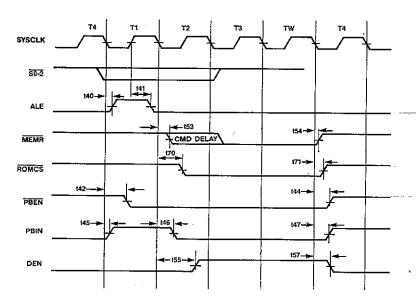

| 28,82          | N/C         |                 | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |