# 3221 Data Processor

ACC Micro's 3221 Data Processor is a single chip controller providing a total I/O solution for the PC/XT and PC/AT systems. This data processor supports a floppy disk controller, two serial ports, bidirectional parallel ports, and an IDE interface in either a 144-, 128- or 100-pin PQFP package. The 3221 has a unique power conservation feature that allows the whole chip and each individual data I/O device to be powered down. That is, all the inputs are disabled, and all the outputs are tri-stated.

#### Floppy Disk Controller

- Compatible with IBM PC/AT and PC/XT disk drive systems

- \* Supports 360K/720K/1.2M/1.44M formats

- Supports up to three 3.5" or 5.25" floppy disk drives

- Emulates the NEC765A in an IBM PC environment

- Supports variable write precompensation

- On-chip digital data separator eliminates critical analog adjustments

- \* Data rates of 250, 300 and 500 Kbits

- Programmable data record length 128, 256, 512, or 1024 bytes/sector

- 16-bit half cell divide algorithm reduces soft error rates

- Direct high current drive output for floppy drives

- Supports external bootable floppy drives<sup>2</sup>

#### IDE (Integrated Drive Electronics) Interface

Supports one IDE bus interface hard disk drive for AT/XT systems

#### Serial and Parallel Ports

- Supports two serial ports and bi-directional parallel ports

- Direct drive for parallel ports

- Controller signals for parallel port B<sup>1</sup>

- \* Parallel port extended mode supports bidirectional input and output

- Serial ports fully 16C450 compatible

#### General

- EISA support mode<sup>2</sup>

- RTC interface<sup>2</sup>

- General purpose chip selects<sup>2</sup>

- Power down individual port in the chip

- Programmable configuration registers to eliminate hardware jumpers

- Hardware or software disable of ports<sup>3</sup>

- Supports board level in-circuit testing<sup>3</sup>

- All configuration registers are readable

- 1.2 micron high performance CMOS

- 144-L/128-L/100-L PQFP package

#### **General Description**

ACC Micro's 3221 is a high performance CMOS single-chip data processor. This chip integrates Floppy disk controller, AT hard disk interface, two serial ports, and bi-directional parallel ports into a single chip with advanced features. The 3221-EP and 3221-DP chips integrate two bi-directional parallel ports. The 3221-SP integrates one bi-directional port.

#### Floppy Disk Controller

With the 3221, designers can build an IBM PC/XT or AT compatible Floppy Disk Drive with fast access time, high reliability and low cost per bit capability. The 3221 integrates the functions of a standard floppy disk drive controller.

Data separator

Write precompensation circuit

Decode logic

Data rate selection

Clock generation

Drive interface drivers and receivers.

This integration greatly reduces the number of components required to interface floppy disk drives to a microprocessor system.

The 3221 supports up to three floppy disk drives. It is compatible with IBM System 34 double density format (MFM), and Sony EMCA format.

The 3221 contains the decode logic for the internal registers, the write logic and the read logic. The system address decoder is compatible with the IBM PC drive system. Handshaking signals are provided to make DMA operation easy to incorporate with the aid of an external DMA control chip. The 3221 operates in either DMA or Non-DMA modes. In the Non-DMA mode, the 3221 generates interrupts to the processor each time a data byte is available. In DMA mode, the processor only needs to load the command into the 3221 which will control all data transfers.

The Data Separator in the 3221 minimizes read error rates for high performance floppy disk drives. The on-chip phase locked loop digital circuit adjusts the clock used during data read to keep it in phase with the data signal. Write precompensation is included in addition to the formatting, encoding/decoding, stepper motor control, and status sensing functions. All inputs are TTL compatible, and outputs are high current, open drain with direct drive interface.

Using a single 24 MHz crystal input, the 3221's internal Clock Generation circuit provides all timing signals for the sampling clock, write clock, and master clock. It generates 8 and 4 MHz to handle standard data rates of 500 and 250 Kb/s and 4.8 MHz to support a 300 Kb/s data rate. This chip can support 1Mb/s data transfer rate by using 48MHz oscillator.

The 3221 executes the following fifteen commands from the microprocessor.

Read Data

Read Deleted Data

Read a Track

Read ID

Write Data

Write Deleted Data

Format a Track

Scan Equal

Scan Low or Equal

Scan High or Equal

Recalibrate

Sense Interrupt Status

Specify

Sense Drive Status

Seek

#### AT Hard Disk Interface

The 3221 supports one AT hard disk drive interface through a 40-pin AT interface connector, and includes the address decoding and buffering of signals for this interface.

#### **Bi-directional Parallel Port**

The 3221-EP and 3221-DP provide two bi-directional parallel ports. The 3221-SP provides one bi-directional parallel port. Each parallel port supports PS/2 compatible extended mode for the parallel port to receive data from external devices.

In 3221-DP and 3221-SP, parallel ports have direct drives to interface to the line printer port.

The 3221-EP parallel port A has direct drives to interface to the line printer. Parallel port B needs to add data buffers to interface to the line printer port.

#### **Serial Ports**

The 3221 supports two serial ports. Each serial port interface converts data from peripheral devices or modems from serial-in-data to parallel-out-data. Data transmitted from the CPU is converted from parallel-in-data to serial-out-data. The status of the UART can be read during any CPU operation. Status includes type and condition of the transfer operations in progress, and error conditions.

#### Individual Port Hardware Disable

For add-in board applications, the 3221-DP and 3221-SP allow power-on status of each individual port to be set by adding a pull-up resistor, or a pull-down resistor, on the pins shown below. A pull-up resistor on the pin disables the associated port. A pull-down resistor enables the associated port. For instance, if 3221 senses there is a pull-up resistor on pin 116 (/HCS0), then the primary serial port will be disabled at power-on. Applies only to 3221-DP and 3221-SP.

| DP  | SP  | Symbol  | Port                    |

|-----|-----|---------|-------------------------|

| 116 | 93  | /HCS0   | Primary Serial Port     |

| 121 | 97  | /IENL   | Secondary Serial Port   |

| 117 | 94  | /HCSI   | Floppy Disk Controller  |

| 120 | 96  | /IENH   | Primary Parallel Port   |

| 13  | 13  | DBIR    | IDE                     |

| 77  | n/a | DISPAR2 | Secondary Parallel Port |

|     |     |         |                         |

After power-on, each individual port can then be programmed by the associated control registers to enable or disable individually as needed (refer to programmable confirmation registers).

#### **Multifunction Modes**

The 3221-EP and 3221-DP support three modes of operation. Configuration register DF, bits 0 and 1 select the operation modes.

In Mode 0, multifunction pins are used for second parallel port control and IDE interface. In Mode 1, multifunction pins are used for IDE, RTC interface\*, and general chip selects. In Mode 2, multifunction pins are used for supporting EISA registers and RTC interface. The default in 3221-EP is Mode 1. The default in 3221-DP is Mode 0. The 3221-SP has only one operation mode to keep the pin count to a minimum.

#### Notes:

- 1 Feature supported in 3221-EP only.

- 2 Feature supported in 3221-EP and

- 3221-DP.

- 3 Feature supported in 3221-EP and 3221-SP.

Din

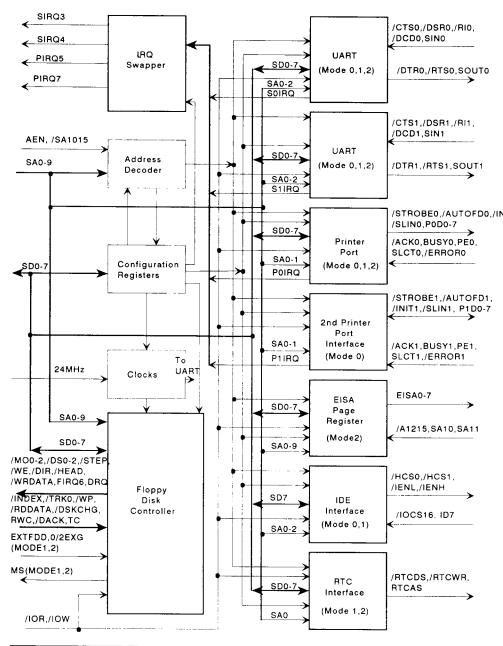

### Block Diagram (3221-EP/DP)

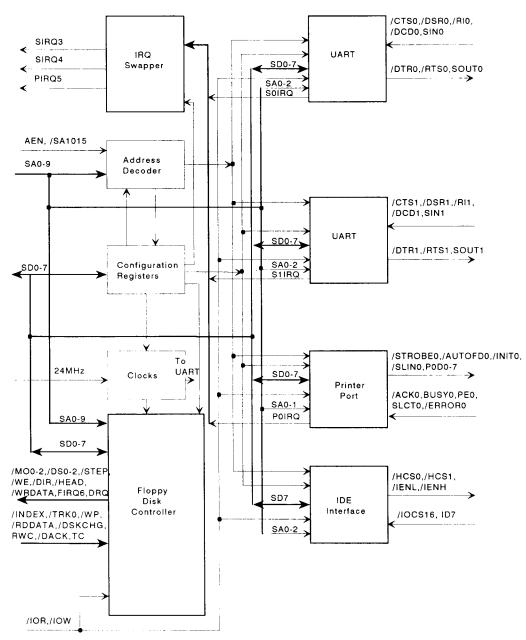

### Block Diagram (3221-SP)

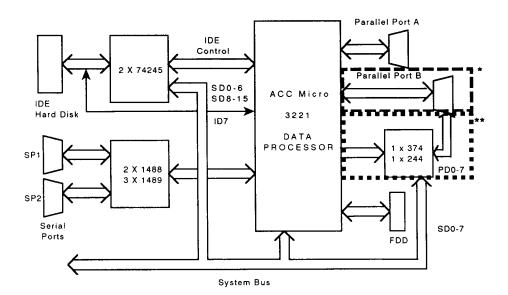

### **Typical Application**

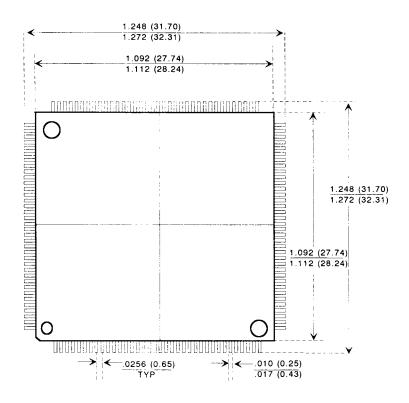

| Features         | 3221-SP  | 3221-DP  | 3221-EP  |

|------------------|----------|----------|----------|

| Package          | 100 Pins | 128 Pins | 144 Pins |

| Three FDDS       | Yes      | Yes      | Yes      |

| Two Serial Ports | Yes      | Yes      | Yes      |

| Parallel Port    | 1        | 2        | 2        |

| Two IDE Drives   | Yes      | Yes      | Yes      |

|                  | 1        |          |          |

- Applies to 3221-EP and 3221-DP.

- \*\* Applies to 3221-EP only.

6

Rev. 1.1

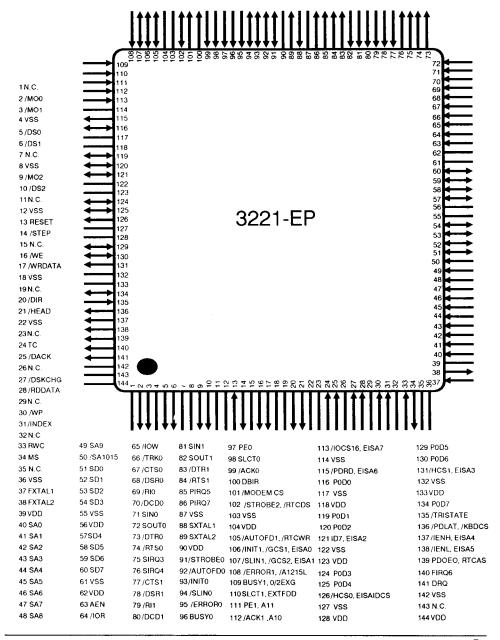

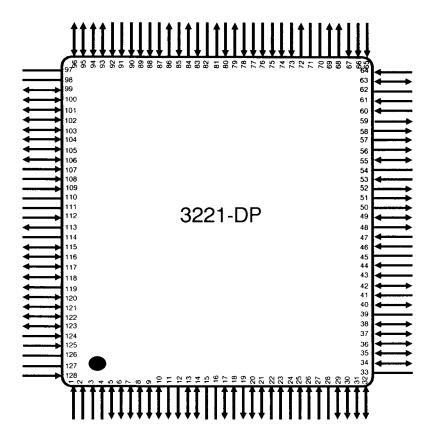

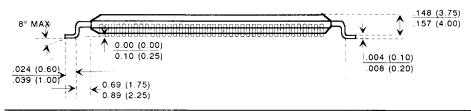

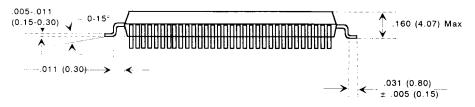

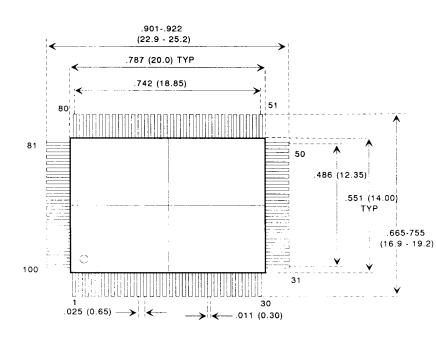

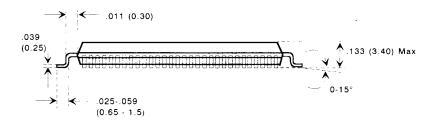

#### Pin Diagram (144-Pin Package)

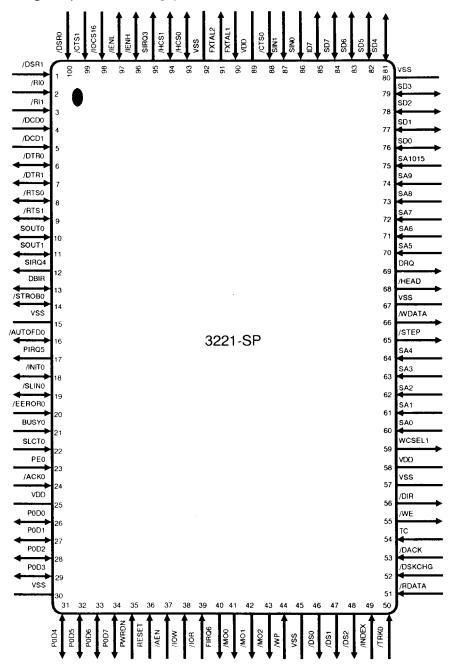

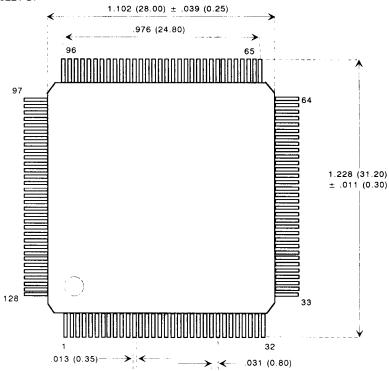

## Pin Diagram (128-Pin Package)

| 1 /RIO     | 17 /AUTOFD0 | 33 VS\$      | 49 /SLIN1* | 65 /DSKCHG | 81 /WDATA | 97 VSS     | 113 FXTAL2 |

|------------|-------------|--------------|------------|------------|-----------|------------|------------|

| 2 /RI1     | 18 /ERROR1* | 34 /STROBE1* | 50 /MO0    | 66 /DACK   | 82 VSS    | 98 VDD     | 114 VSS    |

| 3 /DCD0    | 19 PIRQ5    | 35 /AUTOFD1* | 51 /MO1    | 67 TC      | 83 PE1*   | 99 P1D2*   | 115 P1D5   |

| 4 /DCD1    | 20 /INIT0   | 36 P0D4      | 52 /MO2    | 68 /WE     | 84 /HEAD  | 100 SD4    | 116/HCS0*  |

| 5 /DTR0    | 21 /SLIN0   | 37 P0D5      | 53 /WP     | 69 /DIR    | 85 /ACK1* | 101 SD5    | 117/HCS1*  |

| 6 /DTR1    | 22 BUSY1*   | 38 P0D6      | 54 VSS     | 70 VSS     | 86 DRQ    | 102 SD6    | 118 P1D6   |

| 7 /RTS0    | 23 /EEROR0  | 39 VDD       | 35 P1D1*   | 71 VDD     | 87 SA5    | 103 P1D3   | 119 SIRQ3  |

| 8 /RTS1    | 24 BUSY0    | 40 POD7      | 56 /D\$0   | 72 RWCSEL1 | 88 SA6    | 104 SD7    | 120/IENH*  |

| 9 SOUTO    | 25 SLCT0    | 41 PWRDN     | 57 /DS1    | 73 SA0     | 89 SA7    | 105 ID7*   | 121/IENL*  |

| 10 SOUT1   | 26 PE0      | 42 /INIT1*   | 58 MS*     | 74 SA1     | 90 SA8    | 106 P1D4   | 122 P1D7   |

| 11 PIRQ7   | 27 /ACK0    | 43 RESET     | 59 /DS2    | 75 SA2     | 91 SA9    | 107 SIN0   | 123/IOC16* |

| 12 SIRQ4   | 28 VDD      | 44 /AEN      | 60 /INDEX  | 76 SA3     | 92 SA1015 | 108 SIN1   | 124 /CT\$1 |

| 13 DBIR    | 29 P0D0     | 45 VSS       | 61 /TRK0   | 77 DISPAR2 | 93 SD0    | 109 /CTS0  | 125 /DSR0  |

| 14 /STROB0 | 30 P0D1     | 46 /IOW      | 62 VSS     | 78 SA4     | 94 SD1    | 110 VSS    | 126 VSS    |

| 15 VDD     | 31 P0D2     | 47 /IOR      | 63 P1D0*   | 79 /STEP   | 95 SD2    | 111 VDD    | 127 VDD    |

| 16 VSS     | 32 P0D3     | 48 FIRQ6     | 64 /RDATA  | 80 SLCT1*  | 96 SD3    | 112 FXTAL1 | 128 /DSR1  |

### Pin Diagram (100-Pin Package)

| Symbol                                               |                                              | Pin                                              |                                              |     | Pin Description                                                                                                                            |

|------------------------------------------------------|----------------------------------------------|--------------------------------------------------|----------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| AT Bus                                               | EP                                           | DP                                               | SP                                           |     |                                                                                                                                            |

| SA0<br>SA1<br>SA2<br>SA3<br>SA4<br>SA5<br>SA6<br>SA7 | 40<br>41<br>42<br>43<br>44<br>45<br>46<br>47 | 73<br>74<br>75<br>76<br>78<br>87<br>88<br>89     | 60<br>61<br>62<br>63<br>64<br>70<br>71<br>72 | I   | Address bus.                                                                                                                               |

| SA8<br>SA9                                           | 48<br>49                                     | 90<br>91                                         | 73<br>74                                     |     |                                                                                                                                            |

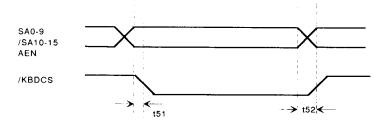

| /SA1015                                              | 50                                           | 92                                               | 75                                           | I   | This input pin is active low signal when all I/O address bits 10-15 are low to ensure that I/O bus is fully decoded.                       |

| SD0<br>SD1<br>SD2<br>SD3<br>SD4<br>SD5<br>SD6<br>SD7 | 51<br>52<br>53<br>54<br>57<br>58<br>59<br>60 | 93<br>94<br>95<br>96<br>100<br>101<br>102<br>104 | 76<br>77<br>78<br>79<br>81<br>82<br>83<br>84 | I/O | I/O Data bus. 16 ma.                                                                                                                       |

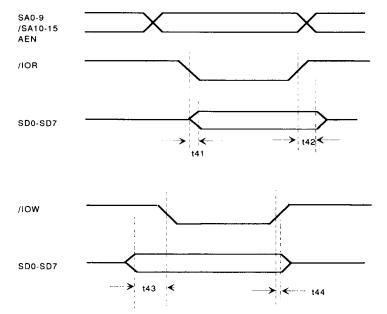

| AEN                                                  | 63                                           | 44                                               | 37                                           | ı   | Address enable. Input from DMA controller. When this line is active, the DMA controller has control of the address bus.                    |

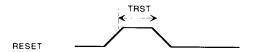

| RESET                                                | 13                                           | 43                                               | 36                                           | 1   | Active high input that resets the controller to the idle state. Resets all the output lines to their disabled states. TTL Schmitt trigger. |

| /IOW                                                 | 65                                           | 46                                               | 38                                           | 1   | Command from the processor to transfer data from the SD bus to the 3221 chip.                                                              |

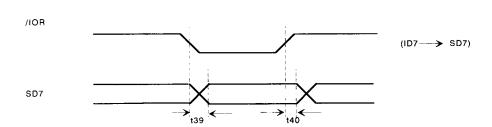

| /IOR                                                 | 64                                           | 47                                               | 39                                           | 1   | Command from the processor to transfer data from the chip to the SD bus.                                                                   |

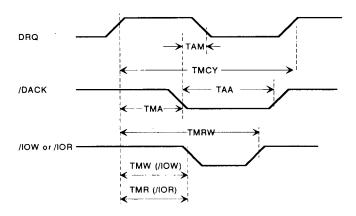

| DRQ                                                  | 141                                          | 86                                               | 69                                           | 0   | DMA request by FDC when DRQ=1. 16ma.                                                                                                       |

| Symbol               | ymbol Pin    |                | I/O            | Pin Description |                                                                                                                         |

|----------------------|--------------|----------------|----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------|

|                      | EΡ           | DP             | SP             |                 |                                                                                                                         |

| /DACK                | 25           | 66             | 53             | I               | When set to 0, a DMA cycle is active and the controller performs a DMA transfer.                                        |

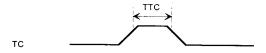

| TC                   | 24           | 67             | 54             | I               | When set to 1, terminates data transfer during Read/<br>Write/Scan commands in DMA or interrupt mode.                   |

| FIRQ6                | 140          | 48             | 40             | 0               | Floppy controller interrupt request. 16ma                                                                               |

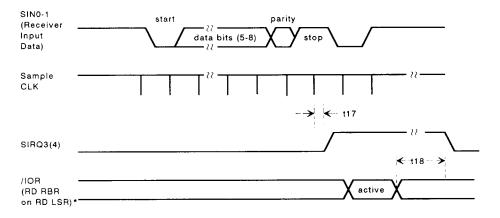

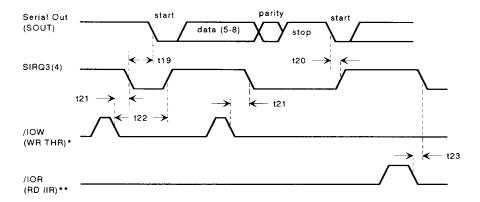

| SIRQ3                | 75           | 119            | 95             | 0               | Primary serial port interrupt request (programmable polarity). 16ma                                                     |

| SIRQ4                | 76           | 12             | 12             | 0               | Secondary serial port interrupt request (programmable polarity). 16ma                                                   |

| PIRQ5                | 85           | 19             | 17             | 0               | Primary parallel port interrupt request (programmable polarity). 16ma                                                   |

| PIRQ7                | 86           | 11             | n/a            | 0               | Secondary parallel port interrupt request (programmable polarity). 16ma                                                 |

| DBIR                 | 100          | 13             | 13             | 0               | Host data bus buffer direction. Low for internal access of serial ports, parallel ports, FDC and low byte of IDE. 4 ma. |

| Floppy Disk (        | Contro       | ller           |                |                 |                                                                                                                         |

| FXTAL1               | 37           | 112            | 90             | t               | FDC XTAL oscillator input. 24 MHz.                                                                                      |

| FXTAL2               | 38           | 113            | 91             | 0               | FDC XTAL oscillator output.                                                                                             |

| /MO0<br>/MO1<br>/MO2 | 2<br>3<br>9  | 50<br>51<br>52 | 41<br>42<br>43 | 0               | When set to 0, the MOTOR ON enables the disk drive.<br>This is an open drain output. 48ma                               |

| /DS0<br>/DS1<br>/DS2 | 5<br>6<br>10 | 56<br>57<br>59 | 46<br>47<br>48 | 0               | When set to 0, the drive select enables the disk drive. This signal is an open drain output. 48ma                       |

| /WE                  | 16           | 68             | 55             | 0               | Write Enable. When set to 0, causes a write operation to the floppy disk drive. An open drain output. 48ma              |

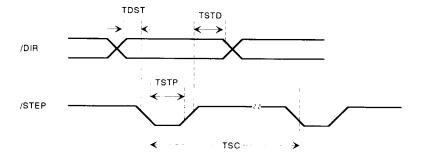

| /DIR                 | 20           | 69             | 56             | 0               | Direction of the head stepper motor. An open drain output. Logic 1 = outward motion. Logic 0 = inward motion. 48ma      |

3221

| Symbol  |    | Pi | n  | I/O | Pin Description                                                                                                                                                                             |  |

|---------|----|----|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | EP | DP | SP |     |                                                                                                                                                                                             |  |

| /HEAD   | 21 | 84 | 68 | 0   | Head select. Open drain output. Determines which disk drive head is active. Logic 1 = Side 0. Logic 0 = Side 1. 48ma                                                                        |  |

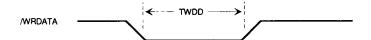

| /WRDATA | 17 | 81 | 66 | 0   | Write Data. Logic low open drain. Writes precompensated serial data to the selected FDD. An OD output. 48ma                                                                                 |  |

| /STEP   | 14 | 79 | 65 | 0   | STEP output pulses. Active low open drain output. Produces a pulse at a programmable rate to move the head to another cylinder. 48ma                                                        |  |

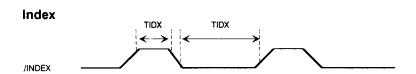

| /INDEX  | 31 | 60 | 49 | I   | Active low Schmitt input from the disk drive. Senses the head positioning over the beginning of a track marked by an index hole. TTL Schmitt trigger.                                       |  |

| /TRK0   | 66 | 61 | 50 | I   | Track 00. Active low schmitt input from the disk drive. Signals that the head is positioned over the outermost track. TTL Schmitt trigger.                                                  |  |

| /WP     | 30 | 53 | 44 | I   | Write Protected. Active low schmitt input from the disk drive indicates that the diskette is write protected. TTL Schmitt trigger.                                                          |  |

| /RDDATA | 28 | 64 | 51 | I   | Read data input. Signals a read from the FDD to the microprocessor. TTL Schmitt trigger.                                                                                                    |  |

| /DSKCHG | 27 | 65 | 52 | t   | Diskette change. This signal is active low at power-on and when the diskette is removed. It remains active until a /STEP pulse is received with the diskette in place. TTL Schmitt trigger. |  |

| /RWC    | 33 | 72 | 59 | 0   | Reduced write current. 48ma.                                                                                                                                                                |  |

|         |    |    |    |     | 1: 500KB                                                                                                                                                                                    |  |

<sup>0: 250, 300</sup>KB

3221

| Symbol                                         | Symbol Pin                |            | I/O      | Pin Description |                                                                                                                                                                                                                               |

|------------------------------------------------|---------------------------|------------|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDE HD Interfa                                 | EP<br>ace <sup>to,1</sup> | DP         | SP       |                 |                                                                                                                                                                                                                               |

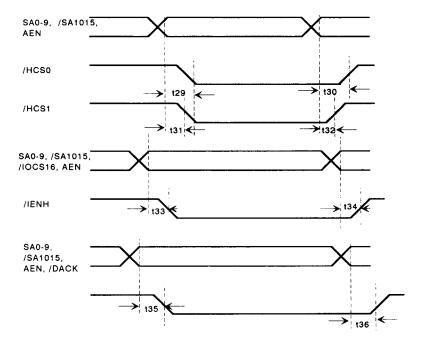

| /HCS0* <sup>0,1</sup><br>/HCS1* <sup>0,1</sup> | 126<br>131                | 116<br>117 | 93<br>94 | 0               | Chip selects for hard disk interface. In AT Mode /HCS0 is active for addresses 1F0h - 1F7h or 170h - 177h. /HCS1 is active for addresses 3F6h - 3F7h or 376h - 377h. 16ma. In XT Mode, /HCS0 is active for address 320h-323h. |

| /IENH*0,1                                      | 137                       | 120        | 96       | 0               | IDE Bus Transceiver High Byte Enable. 4ma                                                                                                                                                                                     |

| /IENL* <sup>0,1</sup>                          | 138                       | 121        | 97       | 0               | IDE Bus Transceiver Low Byte Enable. 4ma                                                                                                                                                                                      |

| /IOCS16*0,1                                    | 113                       | 123        | 98       | 1               | Indicating 16 Bit transfer in AT Mode. Using as DACK3 input in XT Mode.                                                                                                                                                       |

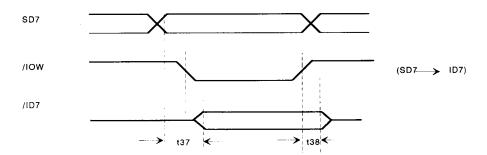

| ID7*0.1                                        | 121                       | 105        | 85       | 1/0             | IDE Data Bus Bit 7. 16ma                                                                                                                                                                                                      |

| Serial Port                                    |                           |            |          |                 |                                                                                                                                                                                                                               |

| SXTAL1                                         | 88                        | n/a        | n/a      | 1               | Serial port crystal/clock input, 1.84 MHz                                                                                                                                                                                     |

| SXTAL2                                         | 89                        | n/a        | n/a      | 0               | Serial port clock source output                                                                                                                                                                                               |

| /RTS0<br>/RTS1                                 | 74<br>84                  | 7<br>8     | 8<br>9   | 0               | Request to send. 4ma                                                                                                                                                                                                          |

| /CTS0<br>/CTS1                                 | 67<br>77                  | 109<br>124 | 88<br>99 | 1               | Clear to send                                                                                                                                                                                                                 |

| /DTR0<br>/DTR1                                 | 73<br>83                  | 5<br>6     | 6<br>7   | 0               | Data Terminal Ready. 4ma                                                                                                                                                                                                      |

| /DSR0<br>/DSR1                                 | 68<br>78                  | 125<br>128 | 100<br>1 | ł               | Data Set Ready                                                                                                                                                                                                                |

| /RI0<br>/RI1                                   | 69<br>79                  | 1<br>2     | 2        | 1               | Ring Indicator                                                                                                                                                                                                                |

| /DCD0<br>/DCD1                                 | 70<br>80                  | 3<br>4     | 4<br>5   | i               | Data Carrier Detected                                                                                                                                                                                                         |

| SINO<br>SIN1                                   | 71<br>81                  | 107<br>108 | 86<br>87 | 1               | Serial Data In                                                                                                                                                                                                                |

| SOUT0<br>SOUT1                                 | 72<br>82                  | 9<br>10    | 10<br>11 | 0               | Serial data out. 4ma                                                                                                                                                                                                          |

## **Pin Descriptions**

| Symbol          |     | Pin |     |     | Pin Description                                                       |  |

|-----------------|-----|-----|-----|-----|-----------------------------------------------------------------------|--|

| Daniel Daniel   | ΕP  | DP  | SP  |     |                                                                       |  |

| Parallel Port A | `   |     |     |     |                                                                       |  |

| PD0             | 116 | 29  | 26  | I/O | Parallel port A data bus. 16 ma                                       |  |

| PD1             | 119 | 30  | 27  |     |                                                                       |  |

| PD2             | 120 | 31  | 28  |     |                                                                       |  |

| PD3             | 124 | 32  | 29  |     |                                                                       |  |

| PD4             | 125 | 36  | 31  |     |                                                                       |  |

| PD5             | 129 | 37  | 32  |     |                                                                       |  |

| PD6             | 130 | 38  | 33  |     |                                                                       |  |

| PD7             | 134 | 40  | 34. |     |                                                                       |  |

| /STROBE0        | 91  | 14  | 14  | I/O | Parallel port A Strobe. 16ma                                          |  |

| /AUTOFD0        | 92  | 17  | 16  | I/O | Parallel port A Autofeed. 16ma                                        |  |

| /INITO          | 93  | 20  | 18  | I/O | Parallel port A Initialize. 16ma                                      |  |

| /SLIN0          | 94  | 21  | 19  | I/O | Parallel port A Select. 16ma                                          |  |

| /ERROR0         | 95  | 23  | 20  | 1   | Parallel port A Error, TTL Schmitt trigger.                           |  |

| BUSY0           | 96  | 24  | 21  | 1   | Parallel port A Busy, TTL Schmitt trigger.                            |  |

| SLCT0           | 98  | 25  | 22  | 1   | Parallel port A Selected, TTL Schmitt trigger.                        |  |

| PE0             | 97  | 26  | 23  | 1   | Parallel port A End of Paper, TTL Schmitt trigger.                    |  |

| /ACK0           | 99  | 27  | 24  | t   | Parallel port A Acknowledge signal from printer, TTL Schmitt trigger. |  |

| Parallel port E | 3*° |     |     |     |                                                                       |  |

| /STROBE1*0      | 102 | 34  | n/a | I/O | Parallel port B Strobe. 16ma                                          |  |

| /AUTOFD1*0      | 105 | 35  | n/a | I/O | Parallel port B Autofeed. 16ma                                        |  |

| /INIT1*°        | 106 | 42  | n/a | I/O | Parallel port B Initialize. 16ma                                      |  |

| /SLIN1*°        | 107 | 49  | n/a | I/O | Parallel port B Select. 16ma                                          |  |

| /ERROR1*°       | 108 | 18  | n/a | 1   | Parallel port B Error.                                                |  |

| BUSY1*0         | 109 | 22  | n/a | 1   | Parallel port B Busy.                                                 |  |

| SLCT1*0         | 110 | 80  | n/a | ŧ   | Parallel port B Selected.                                             |  |

|                 |     |     |     |     |                                                                       |  |

\_\_\_\_\_\_ 3221

### **Pin Descriptions**

| Symbol                                                                               | Symbol Pin                                           |                                                   | I/O                                           | Pin Description |                                                        |

|--------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------|-----------------------------------------------|-----------------|--------------------------------------------------------|

|                                                                                      | EP                                                   | DP                                                | SP                                            |                 |                                                        |

| PE1*0                                                                                | 111                                                  | 83                                                | n/a                                           | I               | Parallel port B End of Paper.                          |

| /ACK1*°                                                                              | 112                                                  | 85                                                | n/a                                           | 1               | Parallel port B Acknowledge Signal from printer.       |

| PDLAT*0                                                                              | 136                                                  | n/a                                               | n/a                                           | 0               | Parallel port B, data output latch.                    |

| /PDOEO*°                                                                             | 139                                                  | n/a                                               | n/a                                           | 0               | Parallel port B data output enable.                    |

| /PDRD*°                                                                              | 115                                                  | n/a                                               | n/a                                           | 0               | Parallel port B data input enable.                     |

| P1D0*°<br>P1D1*°<br>P1D2*°<br>P1D3<br>P1D4<br>P1D5<br>P1D6<br>P1D7                   | n/a<br>n/a<br>n/a<br>n/a<br>n/a<br>n/a<br>n/a        | 63<br>55<br>99<br>103<br>106<br>115<br>118<br>122 | n/a<br>n/a<br>n/a<br>n/a<br>n/a<br>n/a<br>n/a | I/O             | Parallel port B data bus. 16 ma                        |

| DISPAR2                                                                              | n/a                                                  | 77                                                | n/a                                           | Į.              | Disable secondary parallel port                        |

| EISA page reg                                                                        | gisters                                              | <b>*</b> 2                                        |                                               |                 |                                                        |

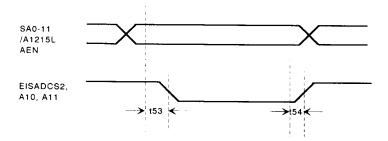

| /A1215L*2                                                                            | 108                                                  | 18                                                | n/a                                           | t               | When /A1215L is active, addresses A12-A15 are logic 0. |

| SA11*2                                                                               | 111                                                  | 83                                                | n/a                                           | ı               | Address input Bit 11.                                  |

| SA10*2                                                                               | 112                                                  | 85                                                | n/a                                           | I               | Address input Bit 10.                                  |

| /EISAIDCS*2                                                                          | 126                                                  | 116                                               | n/a                                           | 0               | Active low when address = 0C80H-0C83H                  |

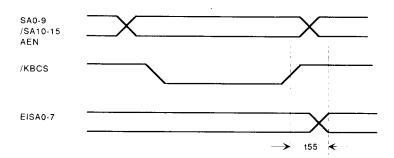

| EISA0*2<br>EISA1*2<br>EISA2*2<br>EISA3*2<br>EISA4*2<br>EISA5*2<br>EISA6*2<br>EISA7*2 | 106<br>107<br>121<br>131<br>137<br>138<br>115<br>113 | 42<br>49<br>105<br>117<br>120<br>121<br>99<br>123 | n/a<br>n/a<br>n/a<br>n/a<br>n/a<br>n/a<br>n/a | 0               | EISA page register, address = 0C00h                    |

| Symbol                                                                  | Symbol                                                                      |                | Pin                                             |                  | I/O                    | Pin Description                                                                                          |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------|-------------------------------------------------|------------------|------------------------|----------------------------------------------------------------------------------------------------------|

| Miscella                                                                | neous                                                                       | EP             |                                                 |                  |                        |                                                                                                          |

| /TRISTA                                                                 | /TRISTATE                                                                   |                | DP<br>n/a                                       | <b>SP</b><br>n/a | 1                      | When /TRISTATE is active low, all the outputs are tristated to support board level in-circuit testing.   |

| /PWRDO                                                                  | NN                                                                          | n/a            | 41                                              | 35               | l                      | When /PWRDOWN is active low, all the outputs are tristated to support board level in-circuit testing.    |

| MS*1,2                                                                  |                                                                             | 34             | 58                                              | n/a              | 0                      | Support for 3 1/2", 1.2MB drive.                                                                         |

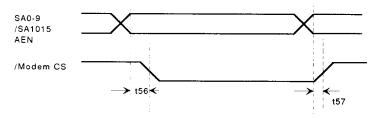

| /MODEM                                                                  | 1 CS*2                                                                      | 101            | 99                                              | n/a              | 0                      | Modem select. 4ma                                                                                        |

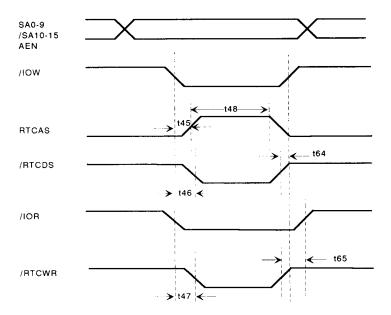

| RTCAS*                                                                  | 1                                                                           | 139            | 99                                              | n/a              | 0                      | Address strobe for 146818 Real Time Clock. Falling edge causes address to be latched in 146818.          |

| /RTCDS*1,2                                                              |                                                                             | 102            | 34                                              | n/a              | 0                      | Data strobe for Real Time Clock. Identifies the cycle when the RTC and RAM drive the bus with read data. |

| /RTCWR                                                                  | /RTCWR*1,2                                                                  |                | 35                                              | n/a              | 0                      | Read or write select for Real Time Clock.                                                                |

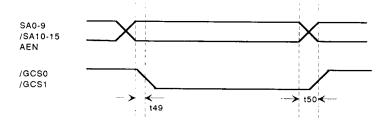

| /GCS1*1                                                                 |                                                                             | 106            | 42                                              | n/a              | 0                      | General purpose chip select.                                                                             |

| /GCS2*1                                                                 | /GCS2*1                                                                     |                | 49                                              | n/a              | 0                      | General purpose chip select.                                                                             |

| /KBDCS                                                                  | <b>*</b> 1,2                                                                | 136            | 55                                              | n/a              | 0                      | Keyboard chip select                                                                                     |

| EXTFDD                                                                  | <b>*</b> 1,2                                                                | 110            | 80                                              | n/a              | 1                      | External FDD is powered on and connected to the system                                                   |

| 0/2 EXG                                                                 | <b>*</b> 1,2                                                                | 109            | 22                                              | n/a              | 1                      | External FDD's switch is exchanged by the operator to use the external FDD as the "A" drive              |

|                                                                         | 144-                                                                        | Pin            | 128                                             | Pin              | 100-P                  | lin                                                                                                      |

| VSS                                                                     | VSS 4,8,12,<br>18,22,36,<br>55,61,87,<br>103,114,<br>117,122,<br>127,132,14 |                | 16,33,45,<br>54,62,70,<br>82,97,110,<br>114,126 |                  | 15,30,<br>57,67,<br>92 |                                                                                                          |

| VDD 39,56,62, 15,28,3<br>90,104, 71,98,1<br>118,123, 127<br>128,133,144 |                                                                             |                | 25,58,                                          | 89               |                        |                                                                                                          |

| N.C. 1,7,1<br>15,19<br>26,29<br>35,14                                   |                                                                             | 9,23,<br>9,32, | n/a                                             |                  | n/a                    |                                                                                                          |

#### Pin Numbers and Modes of Multifunction Pins

| Pin N      | lumber    | Mode 0<br>(Default) | Mode 1           | Mode 2              |

|------------|-----------|---------------------|------------------|---------------------|

| EP         | DP        |                     |                  |                     |

| 34<br>102  | 58<br>34  | /STROBE1            | MS<br>/RTCDS     | MS<br>/RTCDS        |

| 105        | 35        | /AUTOFD1            | /RTCWR           | /RTCWR              |

| 106<br>107 | 42<br>49  | /INIT1<br>/SLIN1    | /GCS1<br>/GCS2   | EISA0<br>EISA1      |

| 108        | 18        | /ERROR1             | 0/0570           | /A1215L<br>0/2EXG   |

| 109<br>110 | 22<br>80  | BUSY1<br>SLCT1      | 0/2EXG<br>EXTFDD | EXTFDD              |

| 111<br>112 | 83<br>85  | PE1<br>/ACK1        |                  | SA11<br>SA10        |

| 113        | 123       | /IOCS16             | /IOCS16          | EISA7               |

| 115<br>121 | 63<br>105 | P1D0<br>ID7         | ID7              | EISA6<br>EISA2      |

| 126        | 116       | /HCS0               | /HCS0            | EISAIDCS2           |

| 131<br>136 | 117<br>55 | /HCS1<br>P1D1       | /HCS1<br>KBDCS   | EISA3<br>KBDCS      |

| 137        | 120       | /IENH               | /IENH            | EISA4               |

| 138<br>139 | 121<br>99 | /IENL<br>P1D2       | /IENL<br>RTCAS   | EISA5<br>/MODEM, CS |

|            |           |                     |                  |                     |

### **Programmable Configuration Registers**

Configuration registers in the 3221 are programmed with an indirect addressing scheme using I/O addresses F2 and F3. I/O address F2 contains the write-only configuration index register. F2 selects the correponding configuration register accessed at I/O address F3.

#### Configuration Register Index, BE (R/W)

| Bit | Function                                |

|-----|-----------------------------------------|

| 7   | PIRQ 5 polarity.                        |

| ,   | •                                       |

|     | 1 = active high, default                |

| _   | 0 = active low                          |

| 6   | PIRQ 7 polarity.                        |

|     | 1 = active high, default                |

|     | 0 = active low                          |

| 5   | Primary Parallel Port Extended Mode     |

|     | 0 = Compatible mode, default            |

|     | 1 = Extended/Bidirectional mode,        |

| 4   | Primary Parallel Port Disable           |

|     | 1 = Disable, 0 = Enable                 |

|     | Power Up Default is set by pin 120      |

|     | (3221-DP)/pin 96 (3221-SP)              |

| 3   | Primary Parallel Port Power Down        |

|     | 1 = Power Down, default = 0             |

| 2** | Secondary Parallel Port Extended        |

|     | Mode                                    |

|     | 0 = Compatible mode, default            |

|     | 1 = Extended/Bidirectional mode         |

| 1** | Secondary Parallel Port Disable         |

| •   | 1 = Disable, 0 = Enable                 |

|     | Power Up Default is set by pin 77       |

|     | , , , , , , , , , , , , , , , , , , , , |

| 0++ | (3221-DP)                               |

| 0** | Secondary Parallel Port Power Down      |

#### Configuration Register Index, BF (R/W)

1 = Power Down 0 = Enable, default Note: Power Up not applicable to 3221-EP.

| Bit | Function                                                                                                    |

|-----|-------------------------------------------------------------------------------------------------------------|

| 7-0 | The 8 most significant address bits of<br>the primary parallel port (A9-2)<br>Default 9E (LPT2, at 278-27B) |

#### Configuration Register Index, DA (R/W)\*\*

| Bit | Function                                                                                                 |  |

|-----|----------------------------------------------------------------------------------------------------------|--|

| 7-0 | The 8 most significant address bits of the secondary parallel port (A9-2) Default DE (LPT1, at 378-37B). |  |

#### Configuration Register Index, DB (R/W)

| Bit   | Function                           |

|-------|------------------------------------|

| 7     | SIRQ4 polarity.                    |

|       | 1 = active high; default           |

|       | 0 = active low                     |

| 6     | SIRQ3 polarity.                    |

|       | 1 = active high; default           |

|       | 0 = active low                     |

| 5     | SXTAL clock off, 1 = SCLK off,     |

|       | 0 = SCLK on, default               |

| 4     | Primary serial port disable        |

|       | 1 = Disable, 0 = Enable            |

|       | Power Up default is set by pin 116 |

|       | (3221-DP)/pin 93 (3221-SP)         |

| 3     | Primary serial port power down     |

|       | 1 = Power down, 0 = Enable         |

|       | Power Up default is set by pin 116 |

|       | (3221-DP)/pin 93 (3221-SP)         |

| 2     | Reserved                           |

| 1     | Secondary serial port disable      |

|       | 1 = Disable, 0 = Enable            |

|       | Power Up default is set by pin 121 |

|       | (3221-DP)/pin 97 (3221-SP)         |

| 0     | Secondary serial port power down   |

|       | 1 = Power down, 0 = Enable         |

|       | Power Up default is set by pin 121 |

|       | (3221-DP)/pin 97 (3221-SP)         |

| Note: | Power Up not applicable to 3221-EF |

#### Configuration Register DC (R/W)

| Bit | Function                                                                                       |  |

|-----|------------------------------------------------------------------------------------------------|--|

| 7-1 | The MSB of the Primary Serial Port<br>Address (bits A9-3).<br>Default = 7F (COM1, at 3F8-3FF). |  |

| 0   | When this bit is set to 1, bit A2 of primary parallel port is decoded.  Default is 0.          |  |

#### Configuration Register DD (R/W)

| Bit   | Function                             |

|-------|--------------------------------------|

| 7-1   | The MSB of the Secondary Serial Port |

|       | Address (bits A9-3).                 |

|       | Default = 5F (COM2, at 2F8-2FF)      |

| 0**   | When this bit is set to 1, bit A2 of |

|       | secondary parallel port is decoded.  |

|       | Default is 0.                        |

| Note: | Bit 0 is reserved in 3221-SP         |

#### Configuration Register Index, DE (R/W)

| Interrupt Request Source |          |                |                                               |

|--------------------------|----------|----------------|-----------------------------------------------|

| Bit                      | Funct    | tion           |                                               |

| 7-6                      | b7       | 3 source<br>b6 |                                               |

|                          | 0        | 0              | Disabled, tri-stated                          |

|                          | 0        | 1<br>0         | Disabled, tri-stated**                        |

|                          | 1        | 1              | Primary serial port<br>Secondary serial port, |

|                          | ·        | ·              | default                                       |

| 5-4                      | SIRQ     | 4 source       |                                               |

|                          | b5       | b4             |                                               |

|                          | 0        | 0              | Disabled, tri-stated                          |

|                          | 0        | 1              | Disabled, tri-stated**                        |

|                          | 1        | 0              | Primary serial port, default                  |

|                          | 1        | 1              | Secondary serial port                         |

| 3-2**                    | PIRQ     | 7 source       |                                               |

|                          | b3       | b2             |                                               |

|                          | 0        | 0              | Disabled, tri-stated, default                 |

|                          | 0        | 1              | Primary serial port                           |

|                          | 1        | 0              | Primary parallel port                         |

|                          | 1        | 1              | Secondary parallel                            |

| Note:                    | Bits 3-2 | 2 are rese     | port<br>rved in 3221-SP.                      |

| 1-0                      | PIRQ     | 5 source       |                                               |

|                          | b1       | b0             |                                               |

|                          | 0        | 0              | Disabled, tri-stated                          |

|                          | 0        | 1              | Secondary serial port                         |

|                          | 1        | 0              | Primary parallel port, default                |

|                          | 1        | 1              | Secondary parallel                            |

port\*\*

### Configuration Register Index, DF (R/W)\*\*

| Bit | Func                                                                          | tion     |                                           |

|-----|-------------------------------------------------------------------------------|----------|-------------------------------------------|

| 7-6 | Reserved                                                                      |          |                                           |

| 5   | 1 = /                                                                         | RTCCS    | e disable<br>disabled                     |

| 4   | Disab                                                                         | ole Mode | enabled, default<br>em Select             |

|     | <ul><li>1 = Modem CS disabled, default</li><li>0 = Modem CS enabled</li></ul> |          |                                           |

| 3-2 |                                                                               |          |                                           |

|     | b3                                                                            | b2       |                                           |

|     | 1                                                                             | 1        | Reserved                                  |

|     | 1                                                                             | 0        | Modem port address<br>= 3E8-3EF (default) |

|     | 0                                                                             | 1        | Modem port address:                       |

|     | 0                                                                             | 0        | Modem port address:<br>3F8-3FF            |

| 1-0 |                                                                               |          |                                           |

|     | b1                                                                            | b0       |                                           |

|     | 1                                                                             | 1        | Reserved                                  |

|     | 1                                                                             | 0        | Mode 2, EISA Mode                         |

|     | 0                                                                             | 1        | Mode 1, AT BUS,                           |

|     | 0                                                                             | 0        | Mode 0, Two parallel ports, default       |

|     |                                                                               |          |                                           |

### Configuration Register Index, FA (R/W)\*\*

| Bit | Function                            |

|-----|-------------------------------------|

| 7   | General purpose I/O register, Bit 7 |

| 6   | General purpose I/O register, Bit 6 |

| 5   | General purpose I/O register, Bit 5 |

| 1   | General purpose I/O register, Bit 4 |

| 3   | General purpose I/O register, Bit 3 |

| 2   | General purpose I/O register, Bit 2 |

| 1   | General purpose I/O register, Bit 1 |

| )   | General purpose I/O register, Bit 0 |

### Configuration Register Index, FB (R/W)

| Bit   | Function                                 |

|-------|------------------------------------------|

| 7     | Reserved                                 |

| 6**   | 0/2 EXG (Read Only)                      |

|       | In mode 1 and mode 2                     |

|       | operation, when the third                |

|       | floppy drive is installed, pin           |

|       | EXTFDD should be pulled                  |

|       | high to enable the third floppy          |

|       | drive or be pulled low to                |

|       | disable the third floppy drive.          |

|       | 1 = Third floppy drive enabled           |

|       | 0 = Third floppy drive disabled          |

| 5**   | EXTFDD (Read Only)                       |

| 5     | • • • • • • • • • • • • • • • • • • • •  |

|       | In mode 1 and mode 2                     |

|       | operation, when the third                |

|       | floppy drive is installed and            |

|       | pin 0/2 EXG is pulled high,              |

|       | the third floppy drive becomes           |

|       | the bootable drive (drive 0).            |

|       | When pin 0/2 EXG is pulled low,          |

|       | the third floppy drive acts as           |

|       | drive 2.                                 |

|       | 1 = Third floppy as drive 0 (bootable)   |

|       | 0 = Third floppy as drive 2              |

| 4**   | MS                                       |

|       | In mode 1 and mode 2, this bit is to     |

|       | control the output pin MS to support a   |

|       | special 3 1/2", 1.2M drive. When this    |

|       | bit is set to high (1), the MS pin sends |

|       | a low signal. When this bit is set to    |

|       | low (0), the MS pin sends a high         |

|       | signal to support a 3 1/2", 1.2M drive.  |

| 3     | FDC, Clock disable                       |

|       | 0 = enable, default                      |

|       | 1 = disable                              |

| 2     | Reserved                                 |

| 1     | FDC disable                              |

|       | 0 = enable, 1 = disable                  |

|       | Power Up default set by pin 117 (3221-   |

|       | DP)/pin 94 (3221-SP)                     |

| ^     | , , , , , , , , , , , , , , , , , , , ,  |

| 0     | FDC address                              |

|       | 0 = Primary, default                     |

|       | 1 = Secondary                            |

| Note: | Bits 6-4 are reserved in 3221-SP.        |

### Configuration Register Index, FE (R/W)

| Bit                | Function                                              |

|--------------------|-------------------------------------------------------|

| 7**                | Disable general chip select 1                         |

|                    | 1 = disable, default                                  |

|                    | 0 = enable                                            |

| 6**                | Disable general chip select 2                         |

|                    | 1 = disable, default                                  |

|                    | 0 = enable                                            |

| 5**                | Enable SA2 decoding for general chip                  |

|                    | select 1                                              |

|                    | 1 = enable                                            |

|                    | 0 = disable, default                                  |

| 4**                | Enable SA2 decoding for general chip                  |

|                    | select 2                                              |

|                    | 1 = enable                                            |

|                    | 0 = disable, default                                  |

| 3                  | Reserved                                              |

| 2                  | IDE XT selected                                       |

|                    | 0 = IDE AT interface, default                         |

|                    | 1 = IDE XT interface                                  |

| 1                  | IDE disable, $1 = IDE$ disable                        |

|                    | 0 = IDE enable                                        |

|                    | Power Up default set by pin 13 (3221-                 |

|                    | DP)/pin 13 (3221-SP)                                  |

| 0                  | Secondary IDE                                         |

|                    | 1 = secondary                                         |

|                    | 0 = primary, default                                  |

| Note:              | Bits 6-4 are reserved in 3221-SP.                     |

|                    |                                                       |

|                    | guration Register Index, BC (R/W)                     |

|                    | guration Register Index, BC (R/W) ral chip select 1** |

|                    |                                                       |

| Gene               | ral chip select 1**                                   |

| Gene<br>Bit<br>7-0 | ral chip select 1** Function                          |

# Configuration Register Index, BD (R/W) General chip select 2\*\*

| Bit | Function           |  |

|-----|--------------------|--|

| 7-0 | Address bits A9-A2 |  |

This register defines address for general chip select 2, /GSC2, default 00

#### **FDC Register Descriptions**

There are six floppy disk controller registers in the 3221, three registers for the status of signals used in diskette operations, one for data register, and two controller registers. The I/O addresses of these registers are described in the tables below.

#### Input Register

(HEX 3F0) (R)

The Input Register is a general purpose input register.

| Bit | Function                           |

|-----|------------------------------------|

| 7   | 0                                  |

| 6   | 0                                  |

| 5   | General purpose programmable bit 5 |

| 4   | General purpose programmable bit 4 |

| 3   | General purpose programmable bit 3 |

| 2   | General purpose programmable bit 2 |

| 1   | General purpose programmable bit 1 |

| 0   | General purpose programmable bit 0 |

#### Digital Output Register (HEX 3F2) (8-bits) (W)

The Digital Output Register controls drive motors, drive selection, and feature enable. All bits are cleared by the I/O reset line.

| Bit | Function                      |

|-----|-------------------------------|

| 7   | Reserved                      |

| 6   | Motor Enable 2                |

| 5   | Motor Enable 1                |

| 4   | Motor Enable 0                |

| 3   | DMA and Interrupt Enable      |

| 2   | /Floppy Disk Controller reset |

| 1,0 | Drive Select 0 through 2      |

|     | 00 selects drive 0            |

|     | 01 selects drive 1            |

|     | 10 selects drive 2            |

|     | 11 Reserved                   |

| Address |           | Registers              |                           |  |  |

|---------|-----------|------------------------|---------------------------|--|--|

| Primary | Secondary | READ                   | WRITE                     |  |  |

| 3F0     | 370       | Input register         |                           |  |  |

| 3F2     | 372       | mpat register          | Digital output register   |  |  |

| 3F4     | 374       | Main status register   | 3 , 3                     |  |  |

| 3F5     | 375       | Data register          | Data register             |  |  |

| 3F7     | 377       | Digital input register | Diskette control register |  |  |

#### Main Status Register (HEX 3F4) (R)

The main status register controls data flow between the microprocessor and the controller.

### Bit Function

- 7 Request for Master

- 1 Data Register ready for transfer

- 6 Data Input/Output

- 1 Data transfer from Controller

- 0 Data transfer from the SD BUS

- 5 Execution Mode (Non-DMA mode)

- 1 Execution

- 4 Controller Busy

- 1 Controller busy

- 3 Drive 3 Busy

- Diskette 3 in seek mode Drive 3 busy

- 2 Drive 2 Busy

- Diskette 2 in seek mode Drive 2 Busy

- 1 Drive 1 Busy

- Diskette 1 in the seek mode Drive 1 Busy

- 0 Drive 0 Busy

- 1 Diskette 0 in the seek mode Drive 0 Busy

#### Data Register

(HEX 3F5) (R/W)

The Data Register consists of four status registers in a stack. Only one register is presented to the data bus at a time. It stores data, commands and parameters, and provides diskette/drive status information. Data bytes are passed through the data register to program or obtain results after a command.

#### Status Register 0 (ST0)

**Function**

Rit

| Dit | runction                                                                                                                                                                                                          |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6 | IC (Interrupt Code) 00 Normal termination of command 01 Abnormal termination of command 10 Invalid command issue 11 Abnormal termination because the ready signal from FDD changed state during command execution |

| 5   | SE (seek end)<br>1 seek end                                                                                                                                                                                       |

| 4   | <ul> <li>EC (Equipment Check)</li> <li>1 When a fault signal is received from the FDD, or the track 0 signal fails to occur after 77 step pulses</li> <li>0 No error</li> </ul>                                   |

| 3   | NR (Not Ready) 1 Drive is not ready 0 Drive is ready                                                                                                                                                              |

| 2   | HD (Head address) 1 Head 1 select 0 Head 0 select                                                                                                                                                                 |

| 1-0 | US1,US0. (Unit select)                                                                                                                                                                                            |

00 Drive 0 select01 Drive 1 select10 Drive 2 select11 Drive 3 select

#### Status Register 1 (ST1)

#### Bit **Function** 7 EN (End of Cylinder) When the FDC tries to access a sector beyond the final sector of a cylinder. 6 Not used. This bit is alv ays 0. 5 DE (Data Error) When the FDC detects a CRC error in either the ID field or data field. OR (Over Run) IF the FDC is not serviced by the host system during data transfer within a certain time interval Not used. This bit is always 0. 3 2 ND (No Data) During execution of Read, Write or Verify Data if the specified sector cannot be found. NW (Not Writable) Set if the "write Protect" signal is detected from the diskette drive during the execution of Write Data. 0 Missing Address Mark When the FDC cannot detect the data address mark or deleted data

address mark

#### Status Register 2 (ST2)

| Bit | Function                                                                                                                                                                           |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Not used. This bit is always 0                                                                                                                                                     |

| 6   | CM (Control Mark)  1 If deleted data is encountered during execution of the Read Data or Scan command.                                                                             |

| 5   | DD (Data Error in Data Field)  1 If the FDC detects a CRC error in the data field.                                                                                                 |

| 4   | WC (Wrong Cylinder)<br>1 Wrong Cylinder                                                                                                                                            |

| 3   | <ul><li>SH (Scan Equal Hit)</li><li>1 During execution of the Scan command, if the condition "equal" is satisfied.</li></ul>                                                       |

| 2   | <ul><li>SN (Scan Not Satisfied)</li><li>During execution of the Scan command if FDC cannot find a sector.</li></ul>                                                                |

| 1   | BC (Bad Cylinder) 1 Bad Cylinder                                                                                                                                                   |

| 0   | <ul> <li>MD (Missing Address Mark in Data Field)</li> <li>1 When data is read from the medium, if the FDC cannot find a data address mark or deleted data address mark.</li> </ul> |

### Status Register 3 (ST3)

| Bit | Function            |

|-----|---------------------|

| 7   | FT, Fault           |

| 6   | WP, Write Protected |

| 5   | RY, Ready           |

| 4   | T0, Track 0         |

| 3   | TS, Two-Side        |

| 2   | HD, Head Address    |

| 1   | US1, Unit Select 1  |

| 0   | US0, Unit Select 0  |

#### Diskette Control Register (HEX 3F7) (W)

The Diskette Control Register sets the precompensation.

| Bit        | Fun                                                                    | ction    |        |  |  |  |  |

|------------|------------------------------------------------------------------------|----------|--------|--|--|--|--|

| 7-2<br>1,0 | Reserved<br>Transfer Rates Select and<br>Reduced Write Current Control |          |        |  |  |  |  |

|            | 00                                                                     | 500 Kb/s | /RWC=1 |  |  |  |  |

|            | 01                                                                     | 300 Kb/s | /RWC=0 |  |  |  |  |

|            | 10                                                                     | 250 Kb/s | /RWC=0 |  |  |  |  |

|            | 11                                                                     | Reserved |        |  |  |  |  |

### Digital Input Register

(HEX 3F7) (R)

The Digital Input Register is for diagnostic purposes.

| Bit | Function                 |

|-----|--------------------------|

| 7   | Diskette Change (DSKCHG) |

| 6   | Tri-State                |

| 5   | Tri-State                |

| 4   | Tri-State                |

| 3   | Tri-State                |

| 2   | Tri-State                |

| 1   | Tri-State                |

| 0   | Tri-State                |

|     |                          |

#### Commands

The diskette controller in 3221 is capable of performing fifteen commands. Each command is initiated by a multi-byte transfer from the microprocessor. The result can also be a multi-byte transfer back to the microprocessor. Each command consists of three phases: Command, Execution, and Result.

#### Command

The microprocessor issues all required information to the controller to perform a specific operation.

#### Execution

The controller performs the specified operation.

#### Result

After completing the operation, status information and other housekeeping information are made available to the microprocessor.

#### **Command Symbol Descriptions**

- A0 Address Line 0

A0 controls the selection of main status register (A0=0) or data register (A0=1).

- C Cylinder Number Current or selected cylinder (tr**ac**k), numbers 0 through 76.

- D DataData pattern to be written into a sector.

- D<sub>7</sub> -D<sub>0</sub> Data Bus

8 bit data bus, where D7 stands for the most significant bit, and D0 stands for the least significant bit.

- DTL Data Length

The value of this byte is normally ignored by the controller. However, a byte must be written at this location.

- EOT End of Track

The final sector number on a cylinder.

- GPL Gap Length

The length of gap 3. During Read/

Write commands this value determines the number of bytes that VCO sync keeps low after two CRC bytes. During Format command it determines the size of gap 3.

- H Head Address

Head number 0 or 1, as specified in the ID field.

- HD Head

Selected head number 0 or 1.

(H=HD in all commands)

- HLT Head Load Time

The head load time in the selected

FDD (2 to 254 ms in 2 ms increments.)

- HUT Head Unload Time

Time after a Read or Write operation.

(16 to 240 ms in 16 ms increments).

MF FM or MFM Mode

Must be 1 to select MFM mode.

MT Multitrack

If MT is high, a multitrack operation is performed. If MT=1 after finishing a read/write operation on side 0, FDC automatically starts searching for sector 1 on side 1.

N Number

The number of data bytes written in a sector.

NCN New Cylinder Number

New cylinder number reached as a result of the seek operation; desired position of head.

ND Non-DMA Mode

PCN Present Cylinder Number

Cylinder number at the completion of the Sense Interrupt Status command, current position of the head.

R Record

The sector number to be read or written.

R/W Read/Write

Either a Read or Write signal.

SC Sector

Number of sectors per cylinder.

SK Skip

Skip deleted data address mark.

SRT Stepping Rate

These bits indicate the stepping rate for the FDD (1 to 16 ms in 1 ms increments). Stepping rate applies to all drives (FH=1ms, EH=2 ms, etc.).

#### STO-ST3

Status 0-Status 3

One of the four registers that store status information after a command has been executed. This information is available during the result phase after command execution. These registers must not be confused with the main status register (selected by A0=0). ST0-ST3 are read only after a command has been executed and only if they contains information relevant to the command.

STP Scan Test

If STP=1 during a scan operation, the data in contiguous sectors is compared byte by byte with data sent from the processor (or DMA). If STP=2, alternate sectors are read and compared.

US0-1 Unit Select

Selected drive number 0 or 1.

#### **COMMAND FORMAT**

The following commands cari De issued to the controller. An "x" indicates a "don't care" condition.

#### READ DATA

#### Command Phase

| Byte 0 | MT   | MF    | SK    | 0   | 0 | 1    | 1   | 0   |

|--------|------|-------|-------|-----|---|------|-----|-----|

| Byte 1 | X    | X     | X     | х   | X | HD ( | JS1 | US0 |

| Byte 2 | Cyli | nder  | Num   | ber |   |      |     |     |

| Byte 3 | Hea  | d Ad  | dress |     |   |      |     |     |

| Byte 4 | Sec  | tor N | umbe  | er  |   |      |     |     |

4 3 2 1

Byte 5 Number of Data Bytes in Sector Byte 6 End of Track Byte 7 Gap Length Byte 8 Data Length

#### Result Phase

| Byte 0 | Status Register 0 |

|--------|-------------------|

| Byte 1 | Status Register 1 |

| Byte 2 | Status Register 2 |

| Byte 3 | Cylinder Number   |

| Byte 4 | Head Address      |

| Byte 5 | Sector Number     |

Byte 6 Number of Data Bytes in Sector

#### READ DELETED DATA

#### **Command Phase**

|        | •    | U     | 3     | ~   | 3 | 2    | •   | U   |

|--------|------|-------|-------|-----|---|------|-----|-----|

| Byte 0 | МТ   | MF    | SK    | 0   | 1 | 1    | 0   | 0   |

| Byte 1 | Х    | Х     | X     | х   | Х | HD ( | JS1 | US0 |

| Byte 2 | Cyli | nder  | Num   | ber |   |      |     |     |