# ACC 85000A Model 50/60 Chip Set

The ACC 85000 is a four-device CMOS chip set designed to provide OEMs with 100% PS/2\* Model 50/60 compatibility and greater flexibility to build a distinctive high performance Model 50/60 compatible system. Only 29 external TTLs are required along with this highly integrated chip set to build a Model 50/60 compatible turbo system.

#### **Features**

- 100% hardware and software compatible with IBM\* PS/2 Model 50/60

- 100% compatible with IBM PS/2

Model 50/60 Micro Channel\*

implementation

- Supports 10, 12.5, and 16 MHz 80286 and 80386SX processors

- DMA and Micro Channel operate at the ultimate Micro Channel bus performance

- Software switching for turbo speed

- Compatible with commercially available VGA chips

- Supports up to 16 MB of on-board DRAM

- Supports 256K x 1, 256K x 4, 1M x 1, and 1M x 4 DRAMs

- Supports shadow RAM

- Supports EMS 4.0

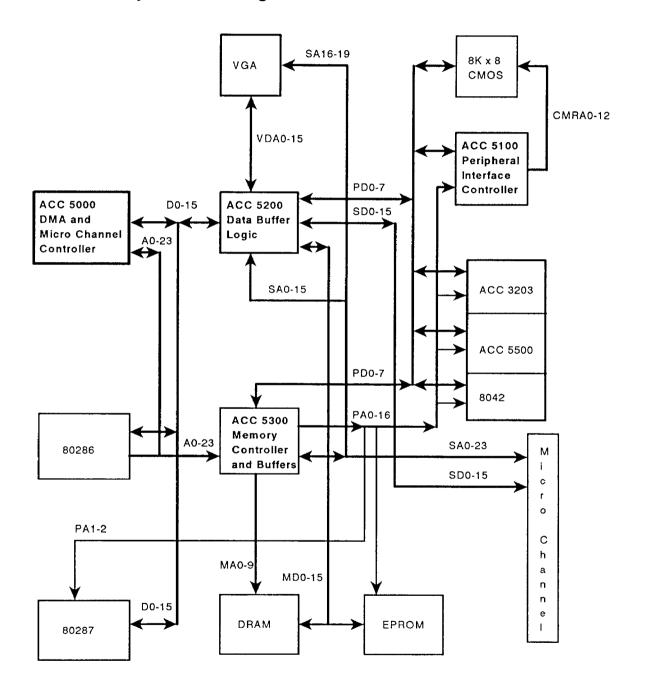

The ACC 85000 chip set includes the ACC 5000 DMA and Micro Channel Controller, the ACC 5100 Peripheral Interface Controller, the ACC 5200 Data Buffer Logic and the ACC 5300 Memory Controller and Buffers.

The ACC 5000 DMA and Micro Channel Controller integrates DMA control and Micro Channel control logic into a single chip.

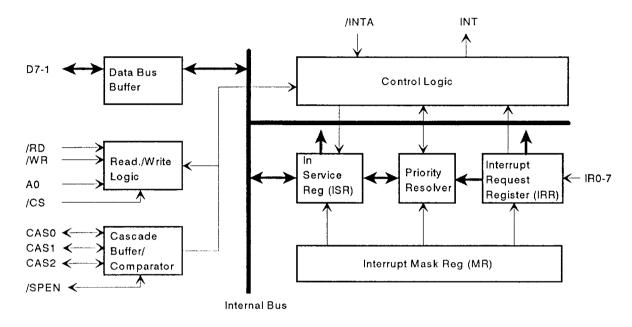

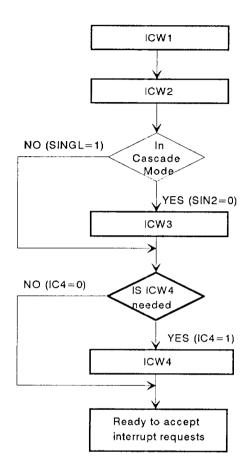

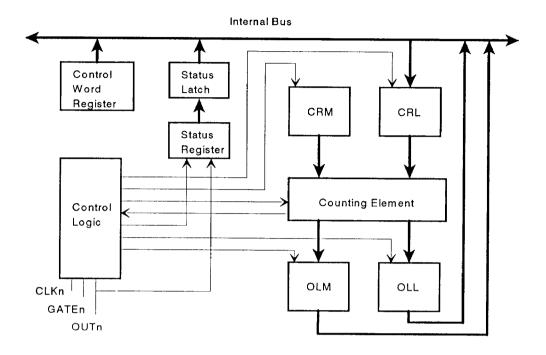

The ACC 5100 integrates a level-sensitive interrupt sharing controller, Programmable Option Select Logic, an 8254 compatible timer and glue logic.

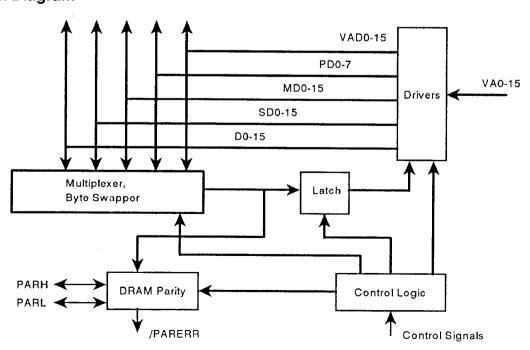

The ACC 5200 integrates data buffers and latches.

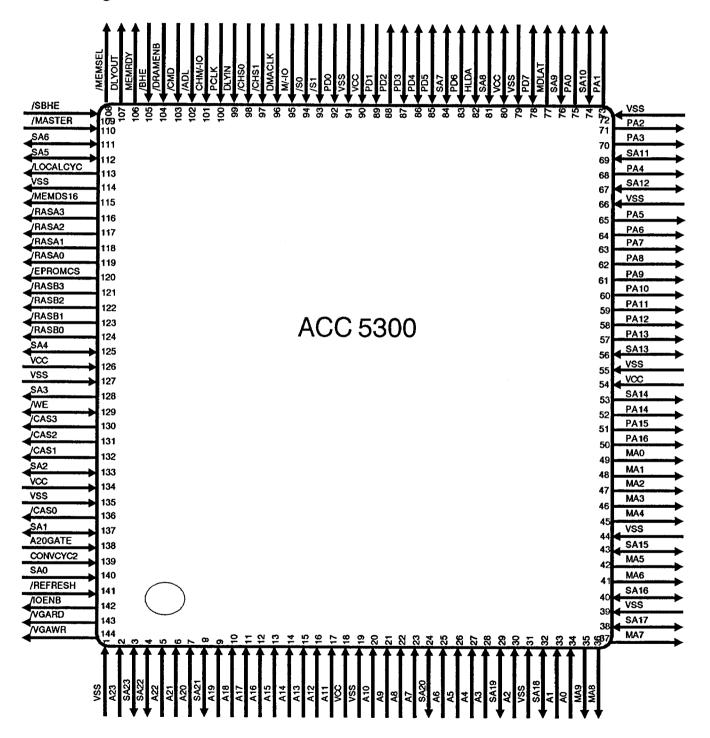

The ACC 5300 integrates the memory controller, and memory buffers and latches.

\* Trademarks of International Business Machines

## ACC 85000 System Block Diagram

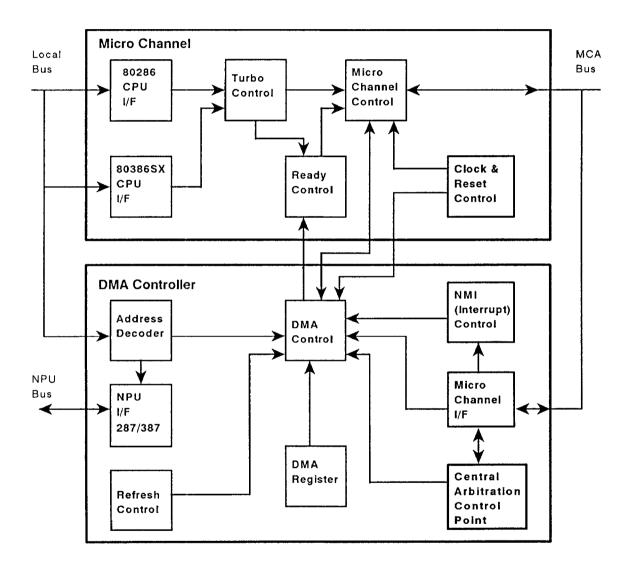

# ACC 5000 DMA & Micro Channel Controller

The ACC 5000 is a high performance CMOS device that integrates the DMA control and Micro Channel\* control logic of an IBM PS/2\* Model 50/60 into a single 144-pin flat pack. Both the DMA and Micro Channel operate at IBM standard clock rate to reach 100% IBM compatibility. The ACC 5000 supports turbo speed switch making the CPU speed switchable between turbo mode (12.5/16 MHz) and normal mode (10 MHz) on the fly.

#### **Features**

- 100% IBM PS/2 compatible Model 50/60 DMA controller implementation

- 100% IBM PS/2 compatible Model 50/60 Micro Channel implementation

- Supports 10, 12.5, and 16 MHz 80286 and 80386SX processors

- 200 ns cycle for DMA and Micro Channel provides the ultimate Micro Channel BUS performance

- Turbo speed change accomplished through software switching on the fly

- Equivalent performance of two 8237 DMA controllers with support for Extended mode

- 16 MB memory address capability and 64 KB I/O address capability

- Eight independent DMA channels for extended mode

- Executes central arbitration control point functions

- Regulates and controls the duration of arbitration cycles

- Monitors the Micro Channel for time-out conditions

- Clock and reset logic

- 1.5 micron high performance CMOS technology

- 144-pin PFP package

<sup>\*</sup> Trademarks of International Business Machines

## ACC 5000 System Block Diagram

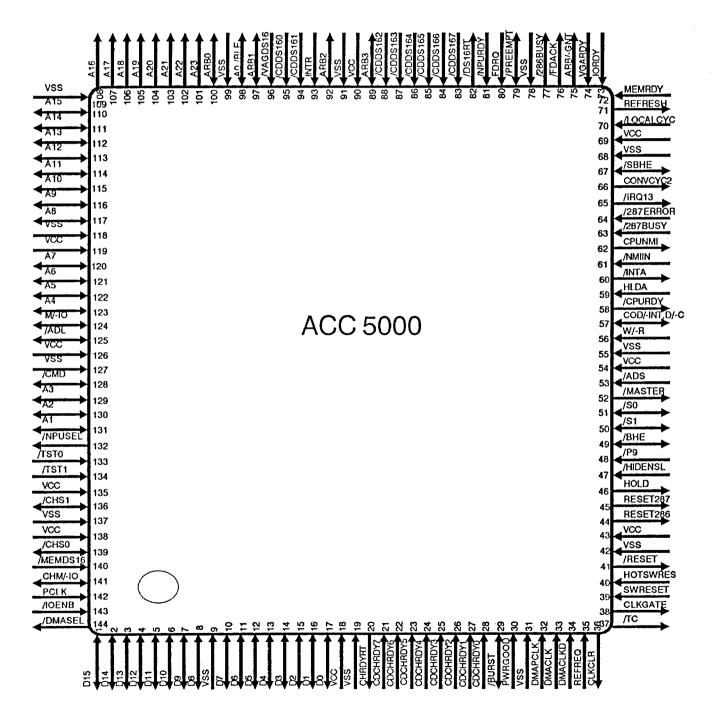

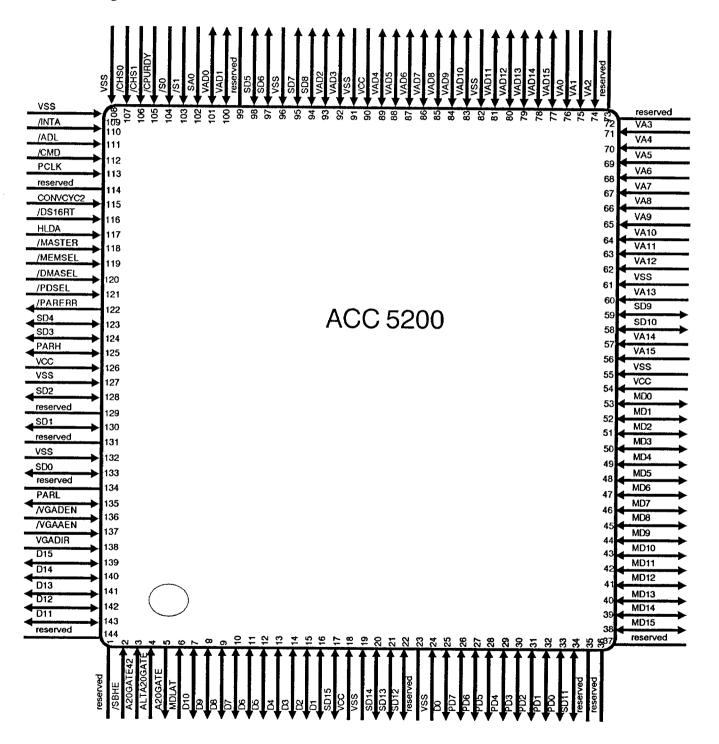

## Pin Diagram

| Symbol   | Pin | I/O | Pin Description                                                                                         |

|----------|-----|-----|---------------------------------------------------------------------------------------------------------|

| D15      | 1   | I/O | CPU/DMA data bus.                                                                                       |

| D14      | 2   |     |                                                                                                         |

| D13      | 3   |     |                                                                                                         |

| D12      | 4   |     |                                                                                                         |

| D11      | 5   |     |                                                                                                         |

| D10      | 6   |     |                                                                                                         |

| D9       | 7   |     |                                                                                                         |

| D8       | 8   |     |                                                                                                         |

| D7       | 10  |     |                                                                                                         |

| D6       | 11  |     |                                                                                                         |

| D5       | 12  |     |                                                                                                         |

| D4       | 13  |     |                                                                                                         |

| D3       | 14  |     |                                                                                                         |

| D2       | 15  |     |                                                                                                         |

| D1       | 16  |     |                                                                                                         |

| D0       | 17  |     |                                                                                                         |

| CHRDYRT  | 20  | 0   | Channel ready return signal to bus.                                                                     |

| CDCHRDY7 | 21  | *   | Channel ready signal from adapter slot.                                                                 |

| CDCHRDY6 | 22  |     | , ,                                                                                                     |

| CDCHRDY5 | 23  |     |                                                                                                         |

| CDCHRDY4 | 24  |     |                                                                                                         |

| CDCHRDY3 | 25  |     |                                                                                                         |

| CDCHRDY2 | 26  |     |                                                                                                         |

| CDCHRDY1 | 27  |     |                                                                                                         |

| CDCHRDY0 | 28  |     |                                                                                                         |

| /BURST   | 29  | I/O | Signal from Micro Channel, indicates that the present master will make multiple transfers. (24 ma sink) |

| PWRGOOD  | 30  | 1   | Power good indication from power supply. Generates power-up reset.                                      |

| DMAPCLK  | 32  | ł   | DMA version of PCLK, constant 10 MHz. (50% duty cycle)                                                  |

| DMACLK   | 33  | 1   | 20MHz clock input for DMA and Micro Channel. (40-50% duty cycle)                                        |

| DMACLKD  | 34  | I   | Delayed 20MHz clock input for DMA and Micro Channel, generates internal non-overlapping clocks.         |

| REFREQ   | 35  | 1   | Refresh request from ACC 5100.                                                                          |

| Symbol     | Pin      | I/O | Pin Description                                                                                                            |

|------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------|

| CLKCLR     | 36       | 0   | Signal clears external CPU clock divider.                                                                                  |

| /TC        | 37       | 0   | Signal indicating the last DMA transfer for the present DMA channel (terminal count). (24 ma sink)                         |

| CLKGATE    | 38       | 0   | Signal gates DMACLK into CPU clock when Micro Channel is accessed.                                                         |

| SWRESET    | 39       | 1   | CPU software reset signal from 8042 chip.                                                                                  |

| HOTSWRES   | 40       | ı   | Alternate "hot" CPU reset from ACC 5100 (faster than SWRESET).                                                             |

| /RESET     | 41       | 0   | Reset signal for all motherboard logic except 80286 and 80287.                                                             |

| RESET286   | 44       | 0   | Reset for 80286.                                                                                                           |

| HOLD       | 45       | 0   | Reset for 80287.                                                                                                           |

| RESET287   | 46       | 0   | CPU Hold request signal.                                                                                                   |

| /HIDENSL   | 47       | 1   | High density floppy disk select.                                                                                           |

| /P9        | 48       | 1   | Input selects 80386SX processor when pulled low, otherwise 286 is selected by default because of built-in pullup resistor. |

| /BHE       | 49       | I/O | Enable for high byte.                                                                                                      |

| /S1<br>/S0 | 50<br>51 | 1/0 | Cycle status signals for CPU/DMA. For the 80386SX processor, these signals are derived from other signals by the ACC 5000. |

| /MASTER    | 52       | 0   | Signal indicates that another master (besides CPU or DMA) has control of the Micro Channel.                                |

| /ADS       | 53       | 1   | Address strobe from 80386SX processor.                                                                                     |

| W/-R       | 56       | ŀ   | 80386SX processor write/read signal.                                                                                       |

| COD/-INTA  | 57       | I/O | For 286: Additional status signal.                                                                                         |

| D/-C       | 57       | I/O | For 80386SX processor: Additional status signal.                                                                           |

| /CPURDY    | 58       | 0   | CPU ready signal.                                                                                                          |

| Symbol    | Pin | I/O | Pin Description                                                                                               |

|-----------|-----|-----|---------------------------------------------------------------------------------------------------------------|

| HLDA      | 59  | 1   | Hold acknowledge signal from CPU.                                                                             |

| /INTA     | 60  | 0   | Interrupt Acknowledge signal for ACC 5100.                                                                    |

| /NMIIN    | 61  | ı   | Non-maskable interrupt from ACC 5100.                                                                         |

| CPUNMI    | 62  | 0   | Non-maskable interrupt to CPU.                                                                                |

| /287BUSY  | 63  | 1   | Busy signal from numeric processor.                                                                           |

| /287ERROR | 64  | 1   | Error signal from numeric processor.                                                                          |

| /IRQ13    | 65  | 0   | Numeric processor interrupt to ACC 5100.                                                                      |

| CONVCYC2  | 66  | 0   | Signal indicates to ACC 5200 and ACC 5300 that the second part of a byte/word conversion cycle is in progess. |

| /SBHE     | 67  | I/O | Micro Channel byte high enable. (24 ma sink)                                                                  |

| /LOCALCYC | 70  | I   | Signal from ACC 5300 indicates that the current cycle is local and does not involve the Micro Channel.        |

| REFRESH   | 71  | 0   | Signals the Micro Channel that this is a memory refresh cycle. (24 ma sink)                                   |

| MEMRDY    | 72  | ŧ   | Ready signal from ACC 5300 (for DRAM or EPROM).                                                               |

| IORDY     | 73  | 1   | Ready signal from ACC 5100 (for on-board I/O).                                                                |

| VGARDY    | 74  | 1   | Ready signal from VGA subsystem.                                                                              |

| ARB/-GNT  | 75  | 0   | Signal indicates Arbitrate vs Bus Grant state on the Micro Channel. (24 ma sink)                              |

| /FDACK    | 76  | 0   | DMA acknowledge to ACC 3203 FDC.                                                                              |

| /286BUSY  | 77  | 0   | Numeric processor busy to CPU.                                                                                |

| /PREEMPT  | 79  | 1/0 | Requests the Micro Channel. (24 ma sink)                                                                      |

| FDRQ      | 80  | 1   | DMA request from ACC 3203 FDC.                                                                                |

| /NPURDY   | 81  | ı   | Ready input from 80376SX NPU (P9 only). Pullup resister is built in.                                          |

| Symbol                                                                                                       | Pin                                    | I/O | Pin Description                                                                                   |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|---------------------------------------------------------------------------------------------------|

| /DS16RT                                                                                                      | 82                                     | 0   | Data size 16 return to bus. (24 ma sink)                                                          |

| /CDDS16(7)<br>/CDDS16(6)<br>/CDDS16(5)<br>/CDDS16(4)<br>/CDDS16(3)<br>/CDDS16(2)<br>/CDDS16(1)<br>/CDDS16(0) | 83<br>84<br>85<br>86<br>87<br>88<br>94 | I   | Input signal from each of 8 adapter slots. Indicates that the adapter allows 16-bit I/O.          |

| ARB3<br>ARB2<br>ARB1<br>ARB0                                                                                 | 89<br>92<br>97<br>100                  | I/O | Micro Channel arbitration priority level signal. (24 ma sink)                                     |

| INTR                                                                                                         | 93                                     | 1   | CPU interrupt signal from the ACC 5100.                                                           |

| /VGADS16                                                                                                     | 96                                     | I   | Signal from VGA subsystem for 16-bit I/O.                                                         |

| A0                                                                                                           | 98                                     | I/O | For 286: CPU/DMA address Bit 0.                                                                   |

| /BLE                                                                                                         | 98                                     | I/O | For 80386SXX processor: Enable for lower byte (pin works the same way, only the name is changed). |

| M/-IO                                                                                                        | 124                                    | I/O | Signal indicates Memory or I/O operation.                                                         |

| /ADL                                                                                                         | 125                                    | I/O | Micro Channel Address Latch signal. (24 ma sink)                                                  |

| /CMD                                                                                                         | 128                                    | I/O | Micro Channel Command Strobe. (24 ma sink)                                                        |

| /NPUSEL                                                                                                      | 132                                    | 0   | Chip select for 80287 NPU.                                                                        |

| /CHS1<br>/CHS0                                                                                               | 136<br>139                             | I/O | MicroChannel /S1 signal. (24 ma sink)                                                             |

| /MEMDS16                                                                                                     | 140                                    | ı   | Input from ACC 5300. Indicates that the on-board memory selected can handle 16-bit transfers.     |

| CHM/-IO                                                                                                      | 141                                    | I/O | Micro Channel version of M/-IO. (24 ma sink)                                                      |

| PCLK                                                                                                         | 142                                    | ł   | Peripheral clock, half speed of CPUCLK.                                                           |

| /IOENB                                                                                                       | 143                                    | 1   | Qualifies I/O decoding inside the ACC 5000.                                                       |

| Symbol                                                                                                                                               | Pin                                                                                                                                                           | I/O                     | Pin Des              | cription                      |                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------|-------------------------------|-------------------------------------------------|

| /DMASEL                                                                                                                                              | 144                                                                                                                                                           | 0                       | Selects I<br>the DMA | DMA or NPU r<br>is accessed I | egisters. When low, indicates that by the CPU.  |

| A23<br>A22<br>A21<br>A20<br>A19<br>A18<br>A17<br>A16<br>A15<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1 | 101<br>102<br>103<br>104<br>105<br>106<br>107<br>108<br>110<br>111<br>112<br>113<br>114<br>115<br>116<br>117<br>120<br>121<br>122<br>123<br>129<br>130<br>131 | 0                       | CPU/DM               | A address bu                  | S.                                              |

| /TST0<br>/TST1                                                                                                                                       | 133<br>134                                                                                                                                                    | 1                       | Reserved             | d. Tied to pull               | up register in system.                          |

| ,                                                                                                                                                    |                                                                                                                                                               |                         | Test Pin             | Input                         |                                                 |

|                                                                                                                                                      |                                                                                                                                                               |                         | TST0                 | TST1                          | Function                                        |

|                                                                                                                                                      |                                                                                                                                                               |                         | 0<br>0<br>1<br>1     | 0<br>1<br>0<br>1              | reserved<br>MCA Mode<br>DMA Mode<br>Normal Mode |

| vcc                                                                                                                                                  | 18, 43, 5<br>119, 126                                                                                                                                         | 4, 69, 90<br>, 135, 138 | +5 v                 | olt supply                    |                                                 |

| vss                                                                                                                                                  | 9, 19, 31,<br>68, 78, 9<br>109, 118                                                                                                                           |                         | Grou                 | nd                            |                                                 |

#### **Functional Description**

### CPU Interface (80286/80386SX)

The Micro Channel Controller subsystem converts control signals from either the 80286 or 80386SX CPU to signals compatible with the Micro Channel bus. In the case of the 80386SX CPU, an extra translation takes place. The 80386SX CPU is assumed to be pipelined (/NA connected to ground) and its control lines are decoded to create /S1 and /S0 signals which imitate those of the 80286. See Table 1 below.

#### **TURBO Control**

The ACC 5000 chip can switch dynamically between two operating speeds, 10Mhz (for IBM compatibility) and a selected higher (turbo) speed for faster CPU DRAM accesses. The ACC 85000 chip set is characterized for four turbo speeds: 10 Mhz, 12.5 Mhz, 16 Mhz and 20 Mhz. However, with a properly designed external clock generator, any speed between 10Mhz and 20Mhz can be used.

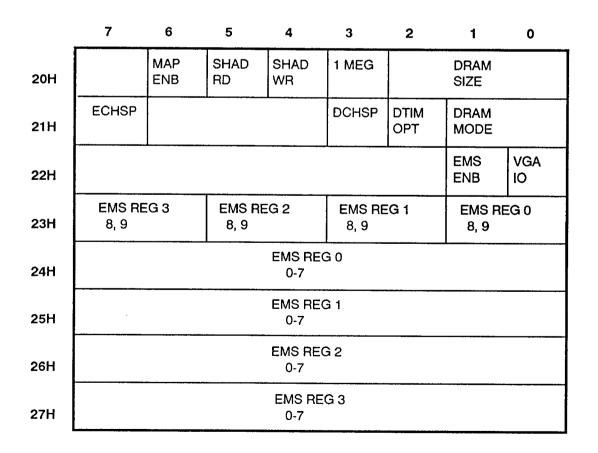

All programmable options of the ACC 85000 chip set are controlled by software accesses to configuration registers which are present inside individual chips. All chips in the ACC 85000 chip set have these configuration registers except for the ACC 5200.

Registers are accessed through I/O ports 22H and 23H. The procedure is to write a register number to 22H, then read or write the actual register data at port 23H. Address space for 64 configuration registers has been provided, with the addresses allocated between the chips as indicated below.

| Chip     | Register numbers allocated |

|----------|----------------------------|

| ACC 5000 | 00H - 0FH                  |

| ACC 5100 | 10H - 1FH                  |

| ACC 5300 | 20H - 3FH                  |

Not all of the allocated registers are actually used. Register 00H is the only one in the ACC 5000. It is used by the Turbo and Ready Control logic blocks.

Table 1 80386SX to 80286 Conversion

| (80386SX inputs) |       | SSX inputs) Cycle |                       | (80286 eq | uivalent status) |  |

|------------------|-------|-------------------|-----------------------|-----------|------------------|--|

| D/-C             | M/-10 | -                 | Туре                  | ` /S1     | /S0              |  |

| 0                | 0     | 0                 | Interrupt Acknowledge | 0         | 0                |  |

| 0                | 0     | 1                 | Reserved              |           |                  |  |

| 0                | 1     | 0                 | Code Read             | 0         | 1                |  |

| 0                | 1     | 1                 | Halt/shutdown         | 0         | 0                |  |

| 1                | 0     | 0                 | I/O Read              | 0         | 1                |  |

| 1                | 0     | 1                 | I/O Write             | 1         | 0                |  |

| 1                | 1     | 0                 | Data Read             | 0         | 1                |  |

| 1                | 1     | 1                 | Data Write            | 1         | 0                |  |

NOTE: The 80386SX D/-C pin is connected to pin COD/-INTA on the ACC 5000.

The format for Register 00H is shown below.

00H

| 7 6 5 4 3 | 2   | 1   | 0     |

|-----------|-----|-----|-------|

|           | 1   |     | TURBO |

| reserved  | MEG | DEF |       |

All these bits are cleared to zero by a CPU reset.

#### **TURBO**

When TURBO is 0, the CPU runs at a fixed 10 Mhz frequency. All DRAM accesses are directed through the Micro Channel. In this mode, the system timing is 100% compatible with the IBM PS/2 Model 50/50Z/60.

When TURBO is 1, the CPU switches between 10 Mhz for Micro Channel cycles and a higher turbo rate for all cycles not involving the Micro Channel. In this mode, the CPU accesses the DRAM directly, bypassing the Micro Channel.

#### **ENB DEF**

This bit, when set, enables the "default" Micro Channel cycle used in the PS/2 Model 50Z. When ENB DEF is zero, one wait state is inserted into all Micro Channel cycles for 100% compatibility with the IBM PS/2 Model 50/60.

#### TEN MEG

Turbo mode usually indicates switching to a higher CPU speed. However the turbo mode in the ACC 85000 chip set is advantageous even for a 10 Mhz turbo speed. At 10 MHz, although the CPU clock is the same speed, the paged and page/interleaved DRAM access modes can be used in the ACC 5300. With these

modes, the system can use slower DRAMS for near zero wait state performance. When turbo mode is selected for a CPU speed of 10Mhz, the TEN MEG bit must be set to one so the ACC 5000 can optimize its turbo control logic for that speed. TEN MEG has no effect when TURBO is zero.

When the ACC 5000 is in turbo mode, the signal /LOCALCYC is checked at the beginning of each CPU cycle (as indicated by /S1 and /S0) to determine if the Micro Channel is required. If /LOCALCYC is high, the clock is switched down to 10 Mhz, and a Micro Channel cycle is initiated. At the end of the cycle, the clock is switched back to turbo speed, as long as the TURBO bit is high.

This Turbo Control logic requires that both the normal and turbo clocks be synchronous to each other. Because of the stringent speed and accuracy requirements of this clock switching, the actual clock generator is implemented outside of the ACC 5000 in TTL circuitry. The ACC 5000 provides the control signals for the clock generator. ACC has designed TTL clock generators for 10Mhz, 12.5 Mhz, 16 Mhz and 20 Mhz CPUs. These clock generators require, in the worst case, two 16L8D PAL chips. If another CPU speed is required, contact ACC for design assistance with this clock generator.

# Micro Channel Control/Ready Control

The Micro Channel Control/Ready Control logic generates IBM Micro Channel compatible strobes using status signals from the CPU. All Micro Channel output signals can sink 24ma for direct connection to the bus. All I/O operations on the motherboard are initiated by the Micro Channel, except for the 80387SX NPU for 80386SX systems. This includes CPU accesses to the DMA slave registers inside the ACC 5000.

One Micro Channel cycle is usually generated for each CPU cycle. However, there is one case in which a CPU cycle can cause two Micro Channel cycles. This occurs when the CPU accesses 16 bits of data from an 8-bit peripheral, or 8-bit memory. The Micro Channel Control block detects this condition and handles it by making two separate Micro Channel cycles while the CPU waits. In this case, the signal /CONVCYC2 indicates to the ACC 5200 and ACC 5300 that the second of the two cycles is taking place.

CPU Ready control logic is built into the Micro Channel bus state machine. /CPURDY becomes active only after all incoming ready signals are high, including CDCHRDY(0) through CDCHRDY(7), VGARDY, DMARDY, MEMRDY and IORDY. DMARDY is generated inside the ACC 5000 by the DMA subsystem. During non-Micro Channel cycles, /CPURDY is generated from MEMRDY and /NPURDY and INTRDY. INTRDY is generated internally in response to Interrupt Acknowledge, Halt and Shutdown cycles.

## Interrupt and Reset Control

The ACC 5000 receives three reset inputs: PWRGOOD, SWRESET and HOTSWRES. PWRGOOD is the power good signal from the power supply. When PWRGOOD is low, both /RESET and RESET286 signals are activated for a system power-up reset.

RESET286 is valid for at least 16 CPUCLK cycles and is synchronized with respect to CPUCLK. Both edges of RESET286 are timed to set the 80286 or 80386SX CPU's internal PCLK to a known state.

/RESET performs system reset for all other chips on the motherboard, except the 80287 or 80387SX NPU. The NPU interface block controls this.

SWRESET and HOTSWRES are software reset signals for the CPU only. SWRESET is

generated by the 8042 keyboard controller. HOTSWRES is an alternate CPU reset from the ACC 5100 which is several microseconds faster than SWRESET.

Several special CPU conditions are monitored in this logic. In response to a "shutdown" cycle received from the CPU, a RESET286 pulse is generated. "Halt" cycles are ignored, except for generating /CPURDY, and an "interrupt acknowledge" cycle results in a 200ns /INTA pulse.

#### **DMA Control**

The DMA controller is software compatible with two Intel 8237 chips and includes the extended functions added by IBM for the P/S 2 Model 50/60. There are eight programmable DMA channels along with the Micro Channel central arbitration control point (CACP). Six of the DMA channels are assigned fixed priorities, and two have programmable priorities. An 11-bit memory refresh counter, numeric processor interface and other logic are also included.

The DMA controller is a serial transfer device requiring a minimum of two cycles with a cycle time of 200 ns to transfer a word or byte for either I/O or memory access. During a DMA cycle, data is first read from a source device and held in a temporary register for writing to a destination device in the second cycle. DMA cycles on the Micro Channel can be extended in the same manner as CPU-initiated Micro Channel cycles. All DMA data transfers are between an I/O and a memory device. Memory to memory transfer is not supported.

Two DMA operating modes are supported, Compatible and Extended. Each of these modes is discussed in detail below.

#### Compatible Mode

In the 8237 compatible mode, DMA I/O devices are addressed only by priority number on the

Micro Channel, no I/O address is available. DMA channels 1-3 and 5-7 are assigned to a fixed priority level, according to their channel numbers. Channels 0 and 4 have programmable priority, using any level from 00H through 0EH. The user must be sure that the priorities assigned to these channels do not conflict with any other active DMA channels.

A local arbiter (typically on a Micro Channel Adapter card) uses a DMA channel by assuming its priority level on the Micro Channel. When the arbiter requires DMA, it must participate in an arbitration cycle and be granted control by the Micro Channel. If the DMA channel is enabled, the ACC 5000 assumes control and performs the DMA transfer after HLDA is received from the CPU. Priority levels for DMA channels 0 and 4 are controlled by two Arbus registers, which are written to by the CPU.

#### **DMA Slave Cycles**

The DMA controller is ordinarily in slave mode. In this mode, its internal registers can be accessed by the CPU. All registers in the DMA controller are 8 bits wide, no word transfers are possible.

#### **DMA Master Cycles**

In master mode, the DMA controller emulates the timing of an Intel 80286 processor consisting of three states similar to the 80286 processor: idle state, status state, and command state.

#### Idle State

The DMA controller is in idle state after reset or if no DMA requests are received.

#### Status State

When the DMA controller receives a DMA request from an unmasked channel, it asserts a HOLD signal to the CPU. After receiving an HLDA signal from the CPU, it

starts a DMA cycle by asserting status lines to perform data transfer between memory and I/O devices. This can be a single data transfer, burst data transfer, or verify data transfer from memory depending on the setup of the mode register.

#### Command State

In the command state, the DMA controller either reads the data from the source device to the temporary holding register or transfers data to the target device.

In the compatible mode, channels 4-7 can perform either byte or word transfers. Channels 0-3 can only perform byte transfers. In the extended mode, all channels can be either byte or word data transfers depending on the mode register set-up. Each data transfer cycle is terminated by /CPURDY which is asserted by the Micro Channel controller.

The ACC 5000 also supports multiple-byte data transfers. To request this feature, the winning local arbiter must activate the /BURST signal. Once /BURST is activated, the data transfer continues until /BURST goes inactive, or until the transfer count goes to zero. The ACC 5000 indicates this condition to the local arbiter by activating the /TC (terminal count) signal.

#### Byte Pointer

An internal byte pointer allows 16 and 24-bit registers to be accessed through a byte wide port. After each byte has been accessed, the byte pointer is changed to allow the next byte to be accessed next time. The pointer always starts out pointing to the least significant byte, then to each more significant byte in order. Table 2 lists DMA registers.

#### Memory Address Register

The Memory Address Register consists of two parts, Base and Current. A CPU write to the

Memory Address Register updates both the base and current internal registers. The base register remains unchanged during the DMA operation, while the current register is updated to indicate the next Memory Address to be accessed. A CPU read always returns the contents of the current register.

If auto-initialize is enabled, the current register reloads at the end of process (EOP) with the value stored in the base register. EOP is generated when the DMA controller reaches a terminal count condition and the /TC signal is asserted.

#### Transfer Count Register

The Transfer Count Register also consists of Base and Current parts. A CPU write updates both base and current. The base register remains unchanged during the DMA operation, while the current register is decremented. This register determines the number of word or byte DMA transfers which take place. The number of transfers is one plus the register contents. Writing zero to the Transfer Count Register results in one DMA transfer. /TC is activated as the current Transfer Count Register goes from 0000H to FFFFH.

If auto-initialize is enabled, this register reloads at the end of process (EOP) with the value stored in the base register.

#### Current I/O Address Register

The Current I/O Address Register is initialized by the CPU in Extended mode only. The DMA I/O address is determined by this register while Bit 0 of the Extended Mode Register is 1. Otherwise, the DMA I/O address is always zero. Refer to Table 3 for an I/O map of DMA registers in compatible mode.

Table 2 DMA Registers

| Register Name     | Number of<br>Registers | Size<br>(bits) | Allocation            |  |

|-------------------|------------------------|----------------|-----------------------|--|

| Memory address    | 8                      | 24             | 1 per channel         |  |

| I/O address       | 8                      | 16             | 1 per channel         |  |

| Transfer count    | 8                      | 16             | 1 per channel         |  |

| Temporary holding | 1                      | 16             | All channels          |  |

| Mask              | 2                      | 4              | 1 per 4-channel group |  |

| Arbus             | 2                      | 4              | 1 per 4-channel group |  |

| Mode              | 8                      | 8              | 1 per channel         |  |

| Status            | 2                      | 8              | 1 per 4-channel group |  |

| Function          | 1                      | 8              | All channels          |  |

| Refresh           | 1                      | 11             | Independent of DMA    |  |

Table 3 DMA Registers - I/O Map for Compatible Mode

| I/O Address | Bits | Description                        | Byte Pointer |

|-------------|------|------------------------------------|--------------|

| 0000H       | 16   | Ch 0 Memory address register (R/W) | Yes          |

| 0001H       | 16   | Ch 0 Transfer count register (R/W) | Yes          |

| 0002H       | 16   | Ch 1 Memory address register (R/W) | Yes          |

| 0003H       | 16   | Ch 1 Transfer count register (R/W) | Yes          |

| 0004H       | 16   | Ch 2 Memory address register (R/W) | Yes          |

| 0005H       | 16   | Ch 2 Transfer count register (R/W) | Yes          |

| 0006H       | 16   | Ch 3 Memory address register (R/W) | Yes          |

| 0007H       | 16   | Ch 3 Transfer count register (R/W) | Yes          |

| 0008H       | 8    | Ch 0-3 Status register             |              |

| 000AH       | 3    | Ch 0-3 Mask register (Set/Rst)(W)  |              |

| 000BH       | 8    | Ch 0-3 Mode register (W)           |              |

| 000CH       | -    | Ch 0-3 Clear byte pointer (W)      |              |

| 000DH       | -    | Ch 0-3 Master clear (W)            |              |

| 000EH       | -    | Ch 0-3 Clear mask register (W)     |              |

| 000FH       | 4    | Ch 0-3 Write mask register (W)     |              |

| 0081H       | 8    | Ch 2 Page register (R/W)*          |              |

| 0082H       | 8    | Ch 3 Page register (R/W)*          |              |

| 0083H       | 8    | Ch 1 Page register (R/W)*          |              |

| 0087H       | 8    | Ch 0 Page register (R/W)*          |              |

| 0089H       | 8    | Ch 6 Page register (R/W)*          |              |

| 008AH       | 8    | Ch 7 Page register (R/W)*          |              |

| 008BH       | 8    | Ch 5 Page register (R/W)*          |              |

| 008FH       | 8    | Ch 4 Page register (R/W)*          |              |

| 00C0H       | 16   | Ch 4 Memory address register (R/W) | Yes          |

| 00C2H       | 16   | Ch 4 Transfer count register (R/W) | Yes          |

| 00C4H       | 16   | Ch 5 Memory address register (R/W) | Yes          |

| 00C6H       | 16   | Ch 5 Transfer count register (R/W) | Yes          |

| 00C8H       | 16   | Ch 6 Memory address register (R/W) | Yes          |

| 00CAH       | 16   | Ch 6 Transfer count register (R/W) | Yes          |

| 00CCH       | 16   | Ch 7 Memory address register (R/W) | Yes          |

| 00CEH       | 16   | Ch 7 Transfer count register (R/W) | Yes          |

| 00D0H       | 8    | Ch 4-7 Status register             |              |

| 00D4H       | 3    | Ch 4-7 Mask register (Set/Rst)(W)  |              |

| 00D6H       | 8    | Ch 4-7 Mode register (W)           |              |

| 00D8H       | -    | Ch 4-7 Clear byte pointer (W)      |              |

| 00DAH       | -    | Ch 4-7 Master clear (W)            |              |

| 00DCH       | -    | Ch 4-7 Clear mask register         |              |

| 00DEH       | 4    | Ch 4-7 Write mask register (W)     |              |

<sup>\*</sup> Upper bytes of Memory Address Register

#### Mode register

The operating mode of the DMA controller can be programmed when HLDA is inactive through the Mode register. Mode register format is described below. The 8237 originally supported four operating modes. The ACC 5000 (identical to PS/2 Model 50/60) only supports "demand" mode. In this mode, the length of each burst of data transfers is controlled by the /BURST signal.

If /BURST is not activated, each burst is limited to a single byte or word transfer. If /BURST is activated during one transfer, another transfer occurs, until /BURST is deactivated, or the transfer count is expired. Once this takes place (EOP condition), /TC goes active and the channel is masked until the CPU reinitializes it.

#### **End Conditions**

In compatible mode, only the lower 16 bits of the Memory Address Register are updated while a DMA operation is taking place. An increment or decrement past a 64K page boundary results in address wraparound. Despite the wraparound, the DMA operation continues until the transfer count goes to FFFFH. Be sure that this does not result in altering unintended memory locations.

The Transfer count register decrements to FFFFH and stops. If the register is set to FFFFH initially, the counter decrements until it encounters FFFFH again.

If Auto-initialize is selected, the channel's associated mask register bit is NOT set at EOP. (EOP masks the channel.)

Tables 4 and 5 are the mode register formats for the Compatible and Extended modes respectively.

Table 4 Mode Register Format for Compatible Mode

| 7 | 6 | 5   | 4    | 3   | 2 | 1   | 0  |  |

|---|---|-----|------|-----|---|-----|----|--|

| 0 | 0 | DIR | AUTO | TYF | E | CH. | AN |  |

DIR Address direction

1 = decrement.

0 = increment

AUTO Auto-initialize feature 1 = on

| TYPE | Tran | Transfer type |              |  |  |  |  |

|------|------|---------------|--------------|--|--|--|--|

|      | 0    | 0             | Verify       |  |  |  |  |

|      | 0    | 1             | Write Memory |  |  |  |  |

|      | 1    | 0             | Read Memory  |  |  |  |  |

|      | 1    | 1             | Reserved     |  |  |  |  |

| CHAN | Char | nnel Select |                |

|------|------|-------------|----------------|

|      | 0    | 0           | Channel 0 or 4 |

|      | 0    | 1           | Channel 1 or 5 |

|      | 1    | 0           | Channel 2 or 6 |

|      | 1    | 1           | Channel 3 or 7 |

Table 5 Mode Register Format for Extended Mode

| 7 | , | 6   | 5 | 4 | 3   | 2    | 1 | 0   |

|---|---|-----|---|---|-----|------|---|-----|

| 0 | ) | WID | 0 | 0 | W/R | DATA | 0 | 1/0 |

WID Data width

1 = 16-bit transfer,

0 = 8-bit transfer

W/R Write/Read

1 = Write.

0 = Read

DATA Data/Verify

1 = Data transfer,

0 = Verifv

I/O I/O Address

1 = programmable,

0 = I/O address 0000H

#### **Arbus Registers**

There are two Arbus registers, one for DMA channel 0 and one for DMA channel 4. These registers provide an arbitration level that is assigned by software. The lower 4 bits of each register contains the programmed arbitration level for its DMA channel. Level 0FH cannot be used. That level is dedicated to the system CPU.

#### Status Register

In Compatible mode, I/O address 0008H is reserved for channels 0-3 of the status register. I/O address 00D0H is reserved for channels 4-7 of the status register. In Extended mode, a status read provides the status of channels 0-3 and a second read provides the status of channels 4-7. The byte pointer is cleared when an access to the extended command register is made. Table 6 contains the format for the Status register. All the bits in the status register are set to zero during initialization.

Table 6 Status Register Format

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|

| CRQ |   |   |   |   | T | С |   |

| 3   | 2 | 1 | 0 | 3 | 2 | 1 | 0 |

| CRQ3 | ChanRQ 3 or 7 |

|------|---------------|

| CRQ2 | ChanRQ 2 or 6 |

| CRQ1 | ChanRQ 1 or 5 |

| CRQ0 | ChanRQ 0 or 4 |

| TC3  | TC 3 or TC 7  |

| TC2  | TC 2 or TC 6  |

| TC1  | TC 1 or TC 5  |

| TC0  | TC 0 or TC 4  |

#### Mask Register

Each DMA channel has an associated mask bit. These bits are used to prevent external DMA requests from generating transfer cycles. Each mask bit can be programmed to be set or cleared. After a reset, all mask bits are set. A clear mask register command clears all mask bits.

In compatible mode, the I/O address for channels 0-3 is 000AH. For channels 4-7, the I/O address is 00D4H. Table 7 contains mask register formats.

Table 7 Mask Register Format

| 7 | 6 | 5 | 4 | 3 | 2    | 1  | 0  |  |

|---|---|---|---|---|------|----|----|--|

| 0 | 0 | 0 | 0 | 0 | MASK | CH | AN |  |

MASK Mask bit

1 = set mask,

0 = clear mask

CHAN Channel Select

| 0 | 0 | 0 or 4 |

|---|---|--------|

| 0 | 1 | 1 or 5 |

| 1 | 0 | 2 or 6 |

| 1 | 1 | 3 or 7 |

In Extended mode, each channel mask bit can be set by setting Bits 7-4 of the extended function register (0018H) to a hexadecimal value 9(H). It can also be reset by setting bits 7-4 of the extended function register to a hexadecimal value, A(H). Refer to the description of extended functions below for details.

#### Write Mask Register

The DMA controller can be masked by setting or resetting all the mask bits in the write mask register. The I/O address for channels 0-3 is 000FH. The I/O address for channels 4-7 is 00DEH. Table 8 contains the format for the Write mask register.

#### **Table 8 Write Mask Register Format**

| 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|---|---|---|---|-----|-----|-----|-----|

| 0 | 0 | 0 | 0 | СМЗ | CM2 | CM1 | СМО |

CM3 Channel 3 or 7 Mask

CM2 Channel 2 or 6 Mask

CM1 Channel 1 or 5 Mask

CM0 Channel 0 or 4 Mask

#### Clear Mask Register

A write command issued to I/O address 000EH unmasks channels 0-3. A write command issued to I/O address 00DCH unmasks channels 4-7.

#### Clear Byte Pointer (Write only)

The Clear Byte Pointer command is usually executed before reading or writing to the address or word count registers. This command initializes the flip-flop to point to the low byte of the register.

In Compatible mode, I/O address 000CH is for channels 0-3, I/O address 00D8H is for channels 4-7. In Extended mode, the byte pointer is cleared each time the extended function register is accessed.

#### **Extended Mode**

The extended mode uses two byte locations, the Extended Function Register (EFR) (0018H) and the Extended Function Execute register (EFE) (001AH), to program all DMA and CACP registers.

Programming in extended mode requires first writing to the EFR, then possibly accessing one or more bytes in the EFE. Commands that do not require EFE access are called "Direct." Table 9 contains the format of the extended function register.

# Central Arbitration Control Point (CACP)

The central arbitration control point controls and monitors the Micro Channel and CPU local bus arbitration functions. The bit settings in the Arbitration register (0090H) configure the CACP. Table 10 shows the format of the Arbitration register. This format is different for read and write. Default condition at power up is zero.

An arbitration cycle is defined as the transition of an ARB/-GNT signal from low to high and back low again. During ARB, all competing local arbiters can drive their priority level on ARB0-3 to determine the new bus owner. Refresh cycles are executed during ARB high time and extend the arbitration cycle. Arbitration cycles can be initiated by the following six internal conditions:

- Refresh Request

- Bus Timeout

- Competing Bus Master

- Competing DMA Slave

- NMI

- Bus idle

A Bus Idle condition exists if a bus master or DMA slave is granted the bus, the transfer is complete, and none of the bus control signals (/S0, /S1, /CMD, /BURST) are active.

Bus cycles originating from a DMA slave, a channel bus master, or refresh requests, require that the CPU relinquish the local bus. The CACP accomplishes this task.

In a special case, if level 0 is detected on the ARB0-3 bus, arbitration can be truncated to a minimum of 100 ns.

Arbitration time can be extended by an NMI or Refresh cycle. NMI sets Bit 6 to one. To continue arbitration, the CPU must clear Bit 6 to zero. A Refresh cycle extends arbitration time by the length of the refresh cycle.

Table 9 Extended Address Register

| 7 | 6   | 5   | 4 | 3 | 2 | 1   | 0 |   |

|---|-----|-----|---|---|---|-----|---|---|

|   | FUN | IC. |   | 0 | C | IAH | V | _ |

| FU | NC |   |   | Extended function code                    |  |

|----|----|---|---|-------------------------------------------|--|

| 0  | 0  | 0 | 0 | Read/Write I/O Address Register (16 bits) |  |

| 0  | 0  | 0 | 1 | Reserved                                  |  |

| 0  | 0  | 1 | 0 | Write Memory Address Register (24 bits)   |  |

| 0  | 0  | 1 | 1 | Read Memory Address Register (24 bits)    |  |

| )  | 1  | 0 | 0 | Write Transfer Count Register (16 bits)   |  |

| 0  | 1  | 0 | 1 | Read Transfer Count Register (16 bits)    |  |

| )  | 1  | 1 | 0 | Read Status Register                      |  |

| )  | 1  | 1 | 1 | Read/Write Extended Mode Register         |  |

| 1  | 0  | 0 | 0 | Read/Write Arbus Register                 |  |

| l  | 0  | 0 | 1 | Set Mask Register bit (Direct)            |  |

| l  | 0  | 1 | 0 | Clear Mask Register bit (Direct)          |  |

| 1  | 0  | 1 | 1 | Reserved                                  |  |

| ı  | 1  | 0 | 0 | Reserved                                  |  |

| l  | 1  | 0 | 1 | Master Clear (Direct)                     |  |

| 1  | 1  | 1 | 0 | Reserved                                  |  |

| 1  | 1  | 1 | 1 | Reserved                                  |  |

CHAN Selected DMA Channel (0 - 7)

#### **Table 10 Arbitration Register Format**

#### Write format

| 7   | 6    | 5   | 4 | 3 | 2 | 1 | 0 |

|-----|------|-----|---|---|---|---|---|

| CPU | MASK | EXT | 0 | 0 | 0 | 0 | 0 |

#### Read format

| 7   | 6    | 5    | 4 | 3 2 1 0 |   |

|-----|------|------|---|---------|---|

| CPU | MASK | TIMO | 0 | LEVEL   | 1 |

CPU Enable System CPU cycles during arbitration.

MASK Arbitration Mask, forces ARB/-GNT pin high. NMI interrupts set this bit.

EXT Enable extended 600ns arbitration cycle.

TIMO Bus timeout has occurred. Clearing MASK also clears this bit.

LEVEL Arbitration level on Micro Channel during most recent grant state.

The built-in 15 microsecond refresh timer is used to detect a Micro Channel bus timeout condition. If a refresh request is pending, and is still not serviced by the time another refresh is requested, a bus timeout condition occurs. because memory refresh has the highest priority on the Micro Channel, the existence of this bus timeout implies that a burst DMA cycle was taking place, and did not respond to the /PREEMPT signal.

When a bus timeout occurs, the CACP identifies the arbitration level of the device. It generates an NMI, initializes the DMA controller, Micro Channel control logic, and ready logic so the CPU can begin error recovery. After a bus timeout, DMA registers must be reprogrammed to restart any DMA operation. The bus timeout error condition exists until the CPU sets the MASK bit to 0.

The CACP acts as a local arbiter for the onboard floppy disk controller, converting its DMA requests into appropriate Micro Channel signals. The interface returns /DACK to the floppy disk controller after bus control is obtained.

#### **Arbitration States**

Arbitration control has six major states and two primary outputs. The outputs are the ARB/-GNT and CPU HOLD signals.

#### 1. System/Dispatcher State

In the System/Dispatcher State, the system CPU can execute error recovery programs, diagnostics or other system level programs. Normal applications do not usually execute when the arbiter is in this state.

#### 2. CPU State

In the CPU State, normal application programs are executed. Error recovery or supervisory programs can also be executed when the arbiter is in this state.

#### 3. ARB State

The ARB State is a transition state between a request for the CPU to yield the bus to a higher priority and the release. When the CPU releases the bus, a refresh cycle or bus master can use the bus.

#### 4. Refresh State

The Refresh State is a transition state when a single refresh cycle is generated. This state is relinquished when the cycle is finished.

#### 5. Grant State

Arbitration control is in Grant State when a bus master or DMA slave has won the bus.

#### 6. Wait State

The Wait State is a transition state for the DMA controller to finish both bus cycles of a transfer before relinquishing the bus.

The ACC 5000 generates a /PREEMPT signal under the following conditions:

- When the floppy disk controller issues DRQ and the DMA controller channel 2 is not masked.

- 2. When a refresh request occurs.

- When the ARB/-GNT line is low and NMI occurs while ARB0-3 not equal to 0FH. In this case, the MASK bit is set.

## **Rating Specifications**

## Absolute Maximum Ratings\*

| Parameter                   | Symbol | Min  | Max Unit | s  |

|-----------------------------|--------|------|----------|----|

| Power supply voltage        | VCC    | -0.3 | 7.0      | V  |

| Power dissipation (@5.25 V) | Wd     |      | TBD      | W  |

| Current (@5.25 V)           | IDD    |      | TBD      | mA |

| DC Input voltage            | VI     | -0.3 | 7.0      | V  |

| Storage temperature         | Tstg   | -40  | 125      | °C |

<sup>\*</sup> Exposing the device to stress above these can cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods can affect device reliability.

## **Recommended Operating Conditions**

| Parameter           | Symbol | Min  | Max  | Units |

|---------------------|--------|------|------|-------|

| DC supply voltage   | VCC    | 4.75 | 5.25 | ٧     |

| Ambient temperature | Та     | 0    | 70   | °C.   |

#### **Capacitance Limits**

$$TA = +25^{\circ} C$$

,  $VCC = 5 V$

| Parameter         | Symbol | Min | Max | Unit | Test Condition                       |

|-------------------|--------|-----|-----|------|--------------------------------------|

| Input capacitance | CI     |     | 10  | pF   | fc = 1 MHz<br>unmeasured pins at GND |

| I/O capacitance   | CIO    |     | 15  | pF   |                                      |

## **DC Specifications**

$TA = 0^{\circ} C$  to  $+70^{\circ} C$ , VCC = +5 V + /-5% ambient termperature

Group 1 INPUT

Pins CDCHRDY0-7, DMAPCLK, DMACLKD, REFREQ, SWRESET, HLDA, HOTSWRES, /HIDENSL, /NMIIN, /287BUSY, /287ERROR, /LOCALCYC, MEMRDY, IORDY, VGARDY, FDRQ, /NPURDY, /CDDS160-7, INTR, /VGADS16, /TST0, /TST1

| Parameter             | Symbol | Min | Max | Unit | Test Condition     |

|-----------------------|--------|-----|-----|------|--------------------|

| Input low<br>voltage  | VIL    |     | 0.8 | ٧    | VCC = 5 +/- 0.25 V |

| Input high<br>voltage | VIH    | 2.0 |     | ٧    | VCC = 5 +/- 0.25 V |

| Input low current     | IIL    | -10 | 10  | uA   | VIN = 0.0V         |

| Input high current    | ШН     | -10 | 10  | uA   | VIN = VCC          |

## Group 2 INPUT WITH PULLUP RESISTORS

Pins /P9, /ADS, W/-R

| Parameter             | Symbol | Min  | Max | Unit | Test Condition     |

|-----------------------|--------|------|-----|------|--------------------|

| Input low voltage     | VIL    |      | 0.8 | V    | VCC = 5 +/- 0.25 V |

| Input high<br>voltage | VIH    | 2.0  |     | ٧    | VCC = 5 +/- 0.25 V |

| Input low<br>current  | IIL    | -200 | -10 | uA   | VIN = 0.0V         |

| Input high current    | IIH    | -10  | 10  | uA   | VIN = VCC          |

## Group 3 OUTPUT (3mA)

RESET287, /IRQ13, /286BUSY, A16-20 Pins

| Parameter           | Symbol | Min | Max | Unit | Test Condition |  |

|---------------------|--------|-----|-----|------|----------------|--|

| Output low voltage  | VOL    |     | 0.4 | V    | IOL = 3mA      |  |

| Output high voltage | VOH    | 2.4 |     | ٧    | IOH = -3mA     |  |

## Group 4 OUTPUT (6 mA)

CLKCLR, CLKGATE, RESET286 Pins

| Parameter           | Symbol | Min | Max | Unit | Test Condition |  |

|---------------------|--------|-----|-----|------|----------------|--|

| Output low voltage  | VOL    |     | 0.4 | ٧    | IOL = 6mA      |  |

| Output high voltage | VOH    | 2.4 |     | ٧    | IOH = -6mA     |  |

## Group 5 OUTPUT (9 mA)

Pins CONVCYC2, /FDACK

| Parameter           | Symbol | Min | Max | Unit | Test Condition |  |

|---------------------|--------|-----|-----|------|----------------|--|

| Output low voltage  | VOL    |     | 0.4 | ٧    | IOL = 9mA      |  |

| Output high voltage | VOH    | 2.4 |     | V    | IOH = -9mA     |  |

Group 6 OUTPUT (24 mA)

Pins /TC, HOLD, /SBHE, REFRESH, ARB/-GNT, /FDACK, /DS15RT, /ADL, CHM/-IO

| Parameter           | Symbol | Min | Max | Unit | Test Condition |  |

|---------------------|--------|-----|-----|------|----------------|--|

| Output low voltage  | VOL    |     | 0.4 | V    | IOL = 24mA     |  |

| Output high voltage | VOH    | 2.4 |     | V    | IOH = -24mA    |  |

Group 7 I/O (1.5 mA)

Pins PWRGOOD

| Parameter             | Symbol | Min | Max | Unit | Test Condition     |

|-----------------------|--------|-----|-----|------|--------------------|

| Input low voltage     | VIL    |     | 0.8 | ٧    | VCC = 5 +/- 0.25 V |

| Input high<br>voltage | VIH    | 2.0 |     | ٧    | VCC = 5 +/- 0.25 V |

| Input low current     | IIL    | -10 | 10  | uA   | VIN = 0.0V         |

| Input high current    | IIH    | -10 | 10  | uA   | VIN = VCC          |

| Output low voltage    | VOL    |     | 0.4 | ٧    | IOL = 1.5mA        |

| Output high voltage   | VOH    | 2.4 |     | ٧    | IOH = -1.5mA       |

Group 8 I/O WITH PULLUP RESISTORS (3 mA)

Pins D0-15, CPUNMI, /PREEMPT, /DMASEL, A1-15, A21-23

| Parameter             | Symbol | Min  | Max | Unit | Test Condition     |

|-----------------------|--------|------|-----|------|--------------------|

| Input low<br>voltage  | VIL    |      | 0.8 | V    | VCC = 5 +/- 0.25 V |

| Input high<br>voltage | VIH    | 2.0  |     | V    | VCC = 5 +/- 0.25 V |

| Input low<br>current  | IIL    | -200 | -10 | uA   | VIN = 0.0V         |

| Input high current    | ΙΙΗ    | -10  | 10  | uA   | VIN = VCC          |

| Output low voltage    | VOL    |      | 0.4 | V    | IOL = 3mA          |

| Output high voltage   | VOH    | 2.4  |     | V    | IOH = -3mA         |

Group 9 I/O WITH PULLUP RESISTORS (6 mA)

Pins /MASTER, M/-IO

| Parameter             | Symbol | Min  | Max | Unit | Test Condition     |

|-----------------------|--------|------|-----|------|--------------------|

| Input low voltage     | VIL    |      | 0.8 | ٧    | VCC = 5 +/- 0.25 V |

| Input high<br>voltage | VIH    | 2.0  |     | V    | VCC = 5 +/- 0.25 V |

| Input low current     | IIL    | -200 | -10 | uA   | VIN = 0.0V         |

| Input high<br>current | IIH    | -10  | 10  | uA   | VIN = VCC          |

| Output low voltage    | VOL    |      | 0.4 | ٧    | IOL = 6mA          |

| Output high voltage   | VOH    | 2.4  |     | V    | IOH = -6mA         |

Group 12 I/O WITH OPEN DRAIN OUTPUT (24 mA)

Pins /BURST, ARB0-3

| Parameter             | Symbol | Min  | Max | Unit | Test Condition     |

|-----------------------|--------|------|-----|------|--------------------|

| Input low<br>voltage  | VIL    |      | 0.8 | V    | VCC = 5 +/- 0.25 V |

| Input high<br>voltage | VIH    | 2.0  |     | V    | VCC = 5 +/- 0.25 V |

| Input low current     | IIL    | -200 | -10 | uA   | VIN = 0.0V         |

| Input high current    | IIH    | -10  | 10  | uA   | VIN = VCC          |

| Output low voltage    | VOL    |      | 0.4 | ٧    | IOL =24mA          |

| Output high voltage   | VOH    | n/a  | n/a | ٧    | n/a                |

## Group 13 I/O WITH PULLUP RESISTORS (24 mA)

Pins /CMD, /CHS0, /CHS1

| Parameter             | Symbol | Min  | Max | Unit | Test Condition     |

|-----------------------|--------|------|-----|------|--------------------|

| Input low<br>voltage  | VIL    |      | 0.8 | V    | VCC = 5 +/- 0.25 V |

| Input high<br>voltage | VIH    | 2.0  |     | ٧    | VCC = 5 +/- 0.25 V |

| Input low current     | IIL    | -200 | -10 | uA   | VIN = 0.0V         |

| Input high current    | IIH    | -10  | 10  | uA   | VIN = VCC          |

| Output low voltage    | VOL    |      | 0.4 | ٧    | IOL =24mA          |

| Output high voltage   | VOH    | 2.4  |     | ٧    | IOH = -24mA        |

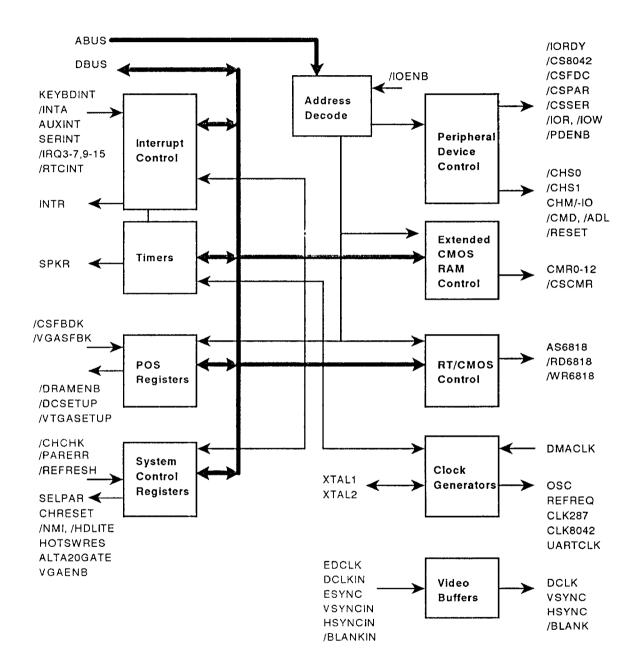

# ACC 5100 Peripheral Interface Controller

The ACC 5100 is a high performance CMOS device that integrates a level-sensitive interrupt sharing controller, Programmable Option Select Logic, an IBM compatible timer, and glue logic into a single 144-pin flat pack. The ACC 5100 is one of four devices in the ACC 85000 chip set designed to provide 100% PS/2\* Model 50/60 compatibility and greater flexibility in building a distinctive high performance Model 50/60 compatible system.

#### **Features**

- 100% hardware and software compatible with IBM PS/2 Model 50/60

- 100% implementation of Programmable Option Select (POS) logic

- 100% implementation of Model 50/60 compatible system control registers

- Two IBM compatible interrupt controllers

- IBM compatible system timer

- Watchdog timer logic

- System board I/O decode logic

- Peripheral device control logic

- NMI generator

- Clock generation logic for the 80287 and 8042 keyboard controller

- Supports external CMOS RAM for configuration registers

- Built-in 74LS245 compatible video buffers

- 1.5 micron high performance CMOS technology

- 144-pin PFP package

<sup>\*</sup> Trademarks of International Business Machines

## ACC 5100 Block Diagram

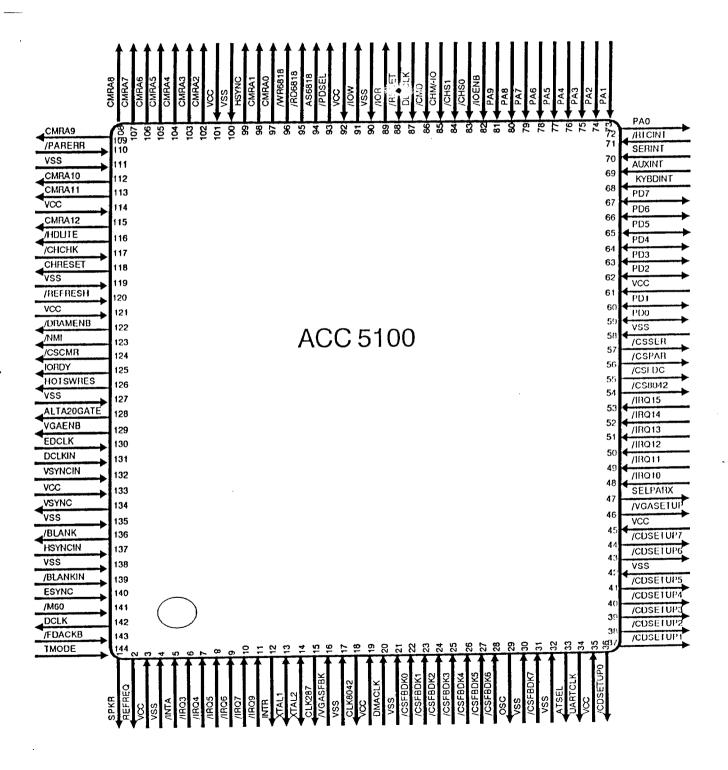

## Pin Diagram

| Symbol                                                                                                         | Pin                                                              | I/O | Pin Description                                                    |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----|--------------------------------------------------------------------|

| SPKR                                                                                                           | 1                                                                | 0   | Speaker output.                                                    |

| REFREQ                                                                                                         | 2                                                                | 0   | Refresh request output.                                            |

| /INTA                                                                                                          | 5                                                                | I   | Interrupt Acknowledge from ACC 5000.                               |

| /IRQ3<br>/IRQ4<br>/IRQ5<br>/IRQ6<br>/IRQ7<br>/IRQ9<br>/IRQ10<br>/IRQ11<br>/IRQ12<br>/IRQ13<br>/IRQ14<br>/IRQ15 | 6<br>7<br>8<br>9<br>10<br>11<br>48<br>49<br>50<br>51<br>52<br>53 | I   | Interrupt.                                                         |

| INTR                                                                                                           | 12                                                               | 0   | Interrupt output for 80286.                                        |

| XTAL1<br>XTAL2                                                                                                 | 13<br>14                                                         | 1/0 | 14MHz Crystal Oscillator.                                          |

| CLK287                                                                                                         | 15                                                               | 0   | 9.54 MHz clock output for 80287.                                   |

| /VGASFBK                                                                                                       | 16                                                               | 1   | Selected feedback for VGA subsystem.                               |

| CLK8042                                                                                                        | 18                                                               | 0   | 9.54 MHz clock output for 8042 (different duty cycle than CLK287). |

| DMACLK                                                                                                         | 20                                                               | 1   | 20MHz clock input, 50/50 duty cycle.                               |

| /CSFBDK0<br>/CSFBDK1<br>/CSFBDK2<br>/CSFBDK3<br>/CSFBDK4<br>/CSFBDK5<br>/CSFBDK6<br>/CSFBDK7                   | 22<br>23<br>24<br>25<br>26<br>27<br>28<br>31                     | I   | Card selected feedbacks for Micro Channel slot.                    |

| osc                                                                                                            | 29                                                               | 0   | 14MHz buffered output for I/O cards. (24ma sink)                   |

| ATSEL                                                                                                          | 33                                                               | 0   | AT bus select.                                                     |

| Symbol                 | Pin      | I/O | Pin Description                              |

|------------------------|----------|-----|----------------------------------------------|

| UARTCLK                | 34       | 0   | 1.8432MHz output derived from 14Mhz Crystal. |

| /CDSETUP0              | 36       | 0   | Card setup output for I/O card.              |

| /CDSETUP1              | 37       |     |                                              |

| /CDSETUP2              | 38       |     |                                              |

| /CDSETUP3              | 39       |     |                                              |

| /CDSETUP4<br>/CDSETUP5 | 40<br>41 |     |                                              |

| /CDSETUP6              | 41<br>43 |     |                                              |

| /CDSETUP7              | 44       |     |                                              |

| /VGASETUP              | 46       | 0   | Puts VGA chip in setup mode.                 |

| SELPARX                | 47       | 0   | Selects parallel port extended mode.         |

| /CS8042                | 54       | 0   | Selects 8042 chip.                           |

| /CSFDC                 | 55       | 0   | Selects 3203 FDC chip.                       |

| /CSPAR                 | 56       | 0   | Select Parallel I/O Port.                    |

| /CSSER                 | 57       | 0   | Selects Serial I/O Port.                     |

| PD0                    | 59       | I/O | Data bus.                                    |

| PD1                    | 60       |     |                                              |

| PD2                    | 62       |     |                                              |

| PD3                    | 63       |     |                                              |

| PD4                    | 64       |     |                                              |

| PD5<br>PD6             | 65<br>66 |     |                                              |

| PD7                    | 66<br>67 |     |                                              |

| KYBDINT                | 68       | 1   | Keyboard interrupt from 8042.                |

| AUXINT                 | 69       | 1   | Auxiliary interrupt from 8042.               |

| SERINT                 | 70       | I   | Serial Interrupt.                            |

| /RTCINT                | 71       | I   | Interrupt from Real Time Clock.              |

| /IOENB                 | 82       | 1   | Input enables I/O decode on ACC 5100.        |

| /CHS0<br>/CHS1         | 83<br>84 | ı   | Channel Status input.                        |

| Symbol I/O                                                                       |                                                                                | Pin [ | Pin Description                    |  |  |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|------------------------------------|--|--|

| PA0<br>PA1<br>PA2<br>PA3<br>PA4<br>PA5<br>PA6<br>PA7                             | 72<br>73<br>74<br>75<br>76<br>77<br>78<br>79                                   | I     | Address bus input.                 |  |  |

| PA9<br>CHM/-IO                                                                   | 81<br>85                                                                       | 1     | Channel Memory /IO input.          |  |  |

| /CMD                                                                             | 86                                                                             | I     | Command signal from Micro Channel. |  |  |

| DLYCLK                                                                           | 87                                                                             | 1     | 20 MHz clock delay, 15 ns.         |  |  |

| /RESET                                                                           | 88                                                                             | t     | Reset input.                       |  |  |

| /IOR                                                                             | 89                                                                             | 0     | I/O Read strobe output.            |  |  |

| /IOW                                                                             | 91                                                                             | 0     | I/O Write strobe output.           |  |  |

| /PDSEL                                                                           | 93                                                                             | 0     | Peripheral Bus selected output.    |  |  |

| AS6818                                                                           | 94                                                                             | 0     | Control line for 6818 RTC.         |  |  |

| /RD6818                                                                          | 95                                                                             | 0     | Control line for 6818 RTC.         |  |  |

| /WR6818                                                                          | 96                                                                             | 0     | Control line for 6818 RTC.         |  |  |

| CMRA0 CMRA1 CMRA2 CMRA3 CMRA4 CMRA5 CMRA6 CMRA7 CMRA8 CMRA9 CMRA10 CMRA11 CMRA12 | 97<br>98<br>102<br>103<br>104<br>105<br>106<br>107<br>108<br>109<br>112<br>113 | 0     | Address line for 8K x 8 CMOS RAM.  |  |  |

| HSYNC                                                                            | 99                                                                             | 0     | Horizontal sink to VGA.            |  |  |

| Symbol     | Pin | I/O | Pin Description                                                                                |

|------------|-----|-----|------------------------------------------------------------------------------------------------|

| /PARERR    | 110 |     | Parity error input.                                                                            |

| /HDLITE    | 116 | 0   | Hard Disk activity light output.                                                               |

| /CHCHK     | 117 | 1   | Micro Channel check input.                                                                     |

| CHRESET    | 118 | 0   | Micro Channel reset output. (24ma sink).                                                       |

| /REFRESH   | 120 | I   | Micro Channel refresh input.                                                                   |

| /DRAMENB   | 122 | 0   | DRAM enable output for ACC 5300.                                                               |

| /NMI       | 123 | 0   | Non-maskable interrupt.                                                                        |

| /CSCMR     | 124 | 0   | Chip select for 8K x 8 CMOS RAM.                                                               |

| IORDY      | 125 | 0   | I/O Ready output. Indicates that the perhipheral controlled by the ACC 5100 is ready.          |

| HOTSWRES   | 126 | 0   | Alternate "hot" CPU reset.                                                                     |

| ALTA20GATE | 128 | 0   | Alternate A20 gate signal.                                                                     |

| VGAENB     | 129 | 0   | Enables on-board VGA operation. Derived from port 3C3H.                                        |

| EDCŁK      | 130 | I   | Enables on-board VGA to drive DCLK. Pin has built-in pullup resistor.                          |

| DCLKIN     | 131 | 1   | DCLK from on-board VGA.                                                                        |

| VSYNCIN    | 132 | 1   | Sync signal from on-board VGA.                                                                 |

| VSYNC      | 134 | 0   | Vertical sync to VGA.                                                                          |

| /BLANK     | 136 | 0   | Blank signal to VGA.                                                                           |

| HSYNCIN    | 137 | 1   | Sync signal from on-board VGA.                                                                 |

| /BLANKIN   | 139 | 1   | Sync signal from on-board VGA.                                                                 |

| ESYNC      | 140 | I   | Enables on-board VGA to drive sync signals on Micro Channel. Pin has built-in pullup resistor. |

| Symbol | Pin                                                                 | I/O | Pin Description                                                                                               |

|--------|---------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------|

| /M60   | 141                                                                 | l   | Model 50/60 strap. Pin grounded for Model 60, or no connect for Model 50. Model 50 does not require CMOS RAM. |

| DCLK   | 142                                                                 | 0   | DCLK to Micro Channel.                                                                                        |

| /FDACK | 143                                                                 | 1   | DMA acknowledge for FDC.                                                                                      |