# ACC 82020 Turbo PC/AT Chip Set

- 100% hardware and software compatible with the IBM\* PC/AT\*

- Fully compatible with

Intel 8237 DMA controller Intel 8259 interrupt controller Intel 8254 timer/counter Intel 82284 clock generator Intel 82288 bus controller TI 74LS612 memory mapper

- Functions include

- 7 DMA channels

3 timer/counter channels

14 external interrupt channels

Data buffers

Address buffers

- Supports Intel 286 and 386SX microprocessors

- Supports Intel 287 and 387SX coprocessors

- Supports chip select for mouse, hard disk, serial/parallel ports

- Optional Direct Memory Access mode\*\*

- Supports 64K x 1, 256K x 1, 256K x 4, 1M x 1, 1M x 4, 4M x 1 memory and 16MB on motherboard

- Supports single module of 1M x 9 DRAM\*\*

- Supports remapping of 640K through 1M memory range

- 4-Way or 2-way page interleaved memory controller

- Supports EMS 4.0

- Built-in staggered memory refresh control

- Supports up to 25 MHz system clock

- I/O (8 MHz) AT BUS compatible

- Quick hardware and software switch from protected mode to real mode for OS/2 optimization

- Shadow RAM for BIOS

- \* Trademarks of International Business Machines \*\* Will be Available fourth quarter 1989

## The Turbo PC/AT chip set includes the following three chips:

ACC 2000 Multifunctional Peripheral Controller

ACC 2120 System Bus Controller and Memory Controller

ACC 2220 Data Buffers or Address Buffers

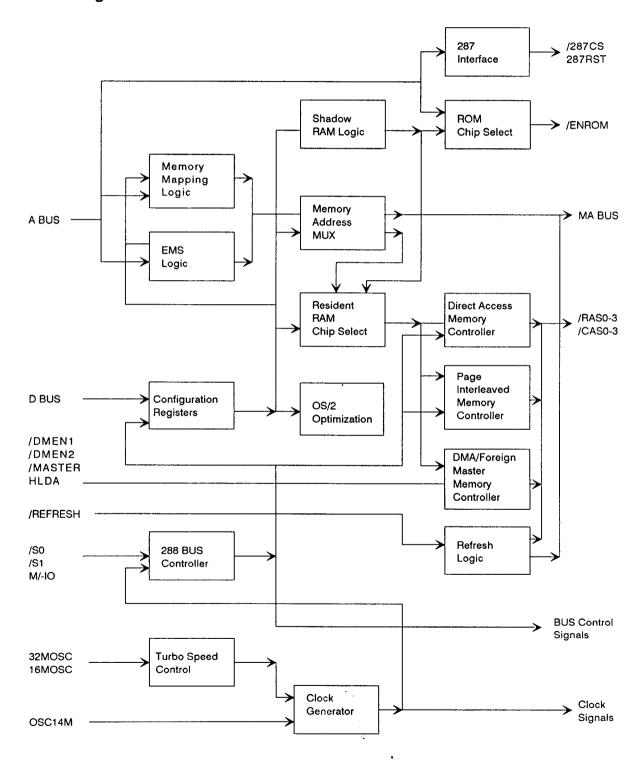

## **General Description**

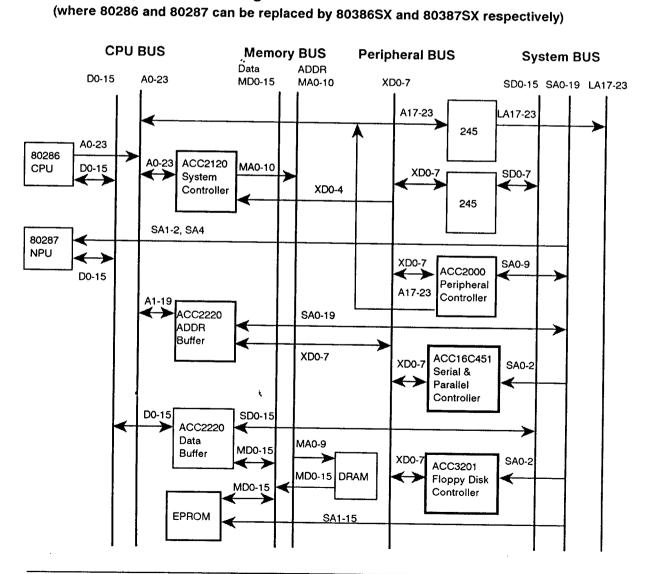

The ACC 82020 is an integrated high performance CMOS chip set that replaces most of the MSI/SSI logic used in building an IBM PC/AT compatible system.

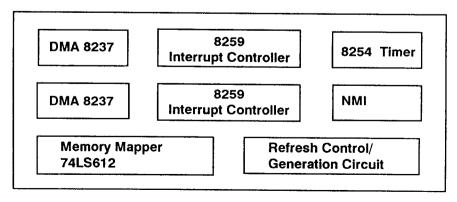

The first chip, the ACC 2000, is a peripheral controller that performs the functions of two 8237 DMA controllers, two 8259 interrupt controllers, one 8254 timer/counter, and one

74LS612 memory mapper as well as other standard control logic circuitry.

The second chip, the ACC 2120, is a system controller containing one 82284 clock generator, one 82288 bus controller, and a high performance memory controller providing up to 25 MHz operation as well as the standard AT mode with zero and one wait state schemes. To support a 16 MHz page interleaved operation with a 0.7 wait state, 100 ns memory can be used.

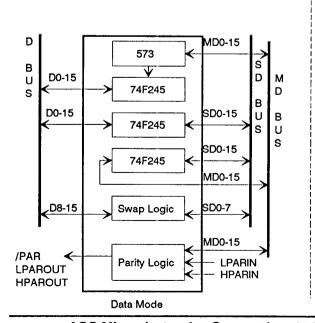

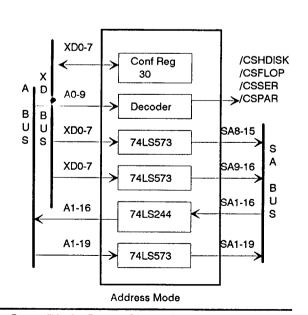

The ACC 2220 is a data and address buffer/ latch chip that runs in two modes. This chip is used twice, one chip is the data buffer, the other is the address buffer/latch.

The ACC 82020 chip set supports a system clock design up to 25 MHz while maintaining 8 MHz AT bus compatibility. All chips in the ACC 82020 chip set are implemented using advanced CMOS technology. The chip set's high integration reduces total system cost through lower power requirements, increased reliability, and reduced board size.

# ACC 82020 System Block Diagram

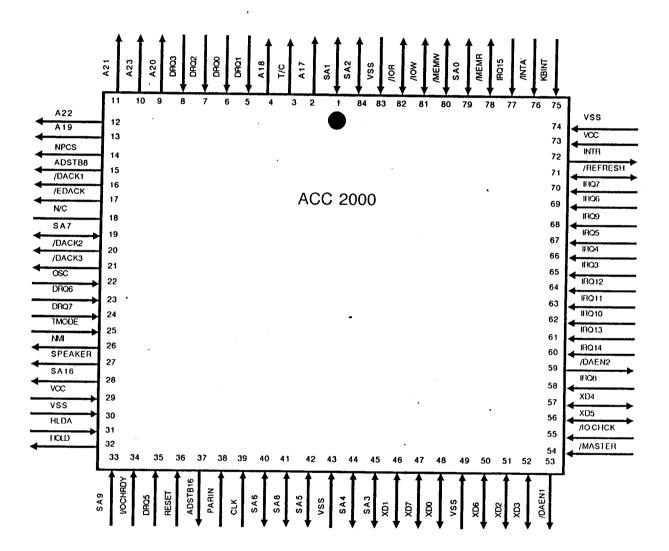

# ACC 2000 PC/AT Integrated Bus & Peripheral Controller

The ACC 2000 is an integrated high performance CMOS PC/AT\* peripheral controller that incorporates several TTL, SSI, and MSI including two 8237 DMA controllers, two 8259 interrupt controllers, one 8254 timer/counter, and one 74LS612 memory mapper. The ACC 2000 is a high performance VLSI that offers a single chip solution for all the peripherals attached to the X BUS (peripheral bus) in IBM PC/AT compatible systems.

#### **Features**

- 100% hardware and software compatible with the IBM\* PC/AT

- Fully compatible to Intel's

8237 DMA controller8254 Timer/Counter8259 Interrupt controller

- Fully compatible to Tl's 74LS612 memory mapper

- Supports 7 DMA channels, 3 timer/counter channels and 14 interrupt request channels

- 100% compatible with the IBM AT I/O BUS

- Supports up to 8 MHz DMA clock

- Supports 16 MB DMA address space

- Built-in refresh control circuit

- 1.5 micron high performance CMOS technology

- TTL compatible

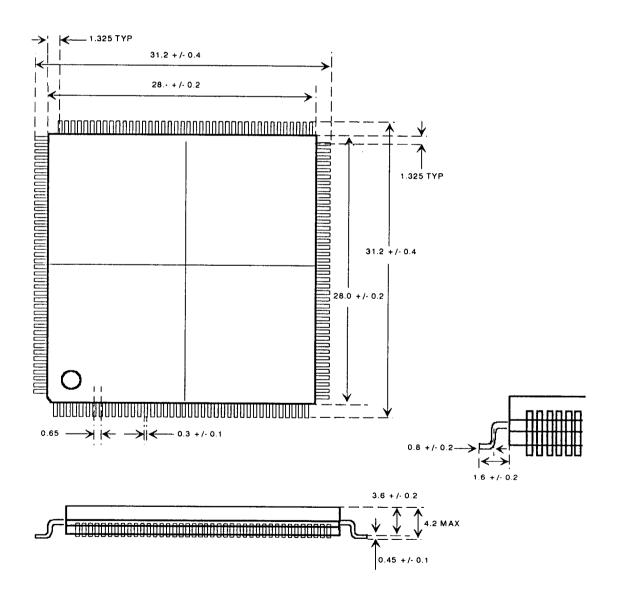

- 84-L PLCC package

## **Block Diagram**

\*Trademarks of International Business Machines

Microelectronics:

| Symbol | Pin | Туре | Description                                                                 |

|--------|-----|------|-----------------------------------------------------------------------------|

| SA0    | 79  | I/O  | System address bus bit.                                                     |

| SA1    | 1   | •    | ,                                                                           |

| SA2    | 84  |      |                                                                             |

| SA3    | 45  |      |                                                                             |

| SA4    | 44  |      |                                                                             |

| SA5    | 42  |      |                                                                             |

| SA6    | 40  |      |                                                                             |

| SA7    | 19  |      |                                                                             |

| SA8    | 41  |      |                                                                             |

| SA9    | 33  | I    | System address bus bit.                                                     |

| SA16   | 28  | 0    | System address bus Bit 16.                                                  |

| A17    | 2   | 0    | Address bus bit.                                                            |

| A18    | 4   |      |                                                                             |

| A19    | 13  |      |                                                                             |

| A20    | 9   |      |                                                                             |

| A21    | 11  |      |                                                                             |

| A22    | 12  |      |                                                                             |

| A23    | 10  |      |                                                                             |

| T/C    | 3   | 0    | Terminal count pulsing. When the terminal count for DMA channel is reached. |

| DRQ0   | 6   | 1    | DMA Request Line. Active high.                                              |

| DRQ1   | 5   |      | - marria quaes <u>- marria marria</u>                                       |

| DRQ2   | 7   |      |                                                                             |

| DRQ3   | 8   |      |                                                                             |

| DRQ5   | 35  |      |                                                                             |

| DRQ6   | 23  |      |                                                                             |

| DRQ7   | 24  |      |                                                                             |

| NPCS   | 14  | 0    | Chip select for numeric processor 80287.                                    |

| ADSTB8 | 15  | 0    | Address strobe for 8 bit DMA transfers.                                     |

| /DACK1 | 16  | 0    | Encoded DMA acknowledge bit.                                                |

| /DACK2 | 20  | •    |                                                                             |

| /DACK3 | 21  |      |                                                                             |

| /EDACK | 17  | 0    | Enable DMA acknowledge decoder. Active low.                                 |

| N.C.   | 18  | 0    | Do not connect.                                                             |

| Symbol                                               | Pin                                    | Туре | Description                                                                                                                            |

|------------------------------------------------------|----------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| osc                                                  | 22                                     | ı    | 14.31818 MHz clock input.                                                                                                              |

| TMODE                                                | 25                                     | I    | Test pin.                                                                                                                              |

| NMI                                                  | 26                                     | 0    | Non-maskable interrupt to 80286 CPU. Active high; NMI generated by the math processor, memory parity error, or error from bus /IOCHCK. |

| SPEAKER                                              | 27                                     | 0    | Data to speaker.                                                                                                                       |

| HLDA                                                 | 31                                     | 1    | Hold acknowledge from CPU.                                                                                                             |

| HOLD                                                 | 32                                     | 0    | Hold request to CPU. Active high.                                                                                                      |

| IOCHRDY                                              | 34                                     | 1    | I/O channel ready from expansion bus.                                                                                                  |

| RESET                                                | 36                                     | 1    | System reset.                                                                                                                          |

| ADSTB16                                              | 37                                     | 0    | Address strobe for 16 bit DMA transfers.                                                                                               |

| /PAR                                                 | 38                                     | 1    | Parity error output from Data buffer. Active low.                                                                                      |

| SYSCLK                                               | 39                                     | 1    | System clock.                                                                                                                          |

| XD0<br>XD1<br>XD2<br>XD3<br>XD4<br>XD5<br>XD6<br>XD7 | 48<br>46<br>51<br>52<br>57<br>56<br>50 | I/O  | Peripheral data bus Bit 0.                                                                                                             |

| /DAEN1                                               | 53                                     | 0    | DMA address enable for 8 bit data transfer. Active low.                                                                                |

| /MASTER                                              | 54                                     | ı    | CPU I/O control for address, data, and control lines.                                                                                  |

| /IOCHCK                                              | 55                                     | 1    | Error expansion bus. Active low.                                                                                                       |

| /DAEN2                                               | 59                                     | 0    | DMA address enable for 16 bit data transfer. Active low.                                                                               |

| Symbol   | Pin                      | Туре | Description                           |

|----------|--------------------------|------|---------------------------------------|

| IRQ3     | 65                       | 1    | Interrupt request input. Active high. |

| IRQ4     | 66                       | 1    | 5                                     |

| IRQ5     | 67                       | 1    |                                       |

| IRQ6     | 69                       | i    |                                       |

| IRQ7     | 70                       | 1    |                                       |

| IRQ8     | 58                       | 1    |                                       |

| IRQ9     | 68                       | 1    |                                       |

| IRQ10    | 62                       | İ    |                                       |

| IRQ11    | 63                       | 1    |                                       |

| IRQ12    | 64                       | 1    |                                       |

| IRQ13    | 61                       | 1    |                                       |

| IRQ14    | 60                       | 1 .  |                                       |

| IRQ15    | 77                       | 1    |                                       |

| /REFRESH | 71                       | I/O  | Refresh cycle. Active low.            |

| INTR     | 72                       | 0    | Interrupt to CPU. Active high.        |

| KBINT    | 75                       | i    | Keyboard interrupt to 8259.           |

| /INTA    | 76                       | 1    | Interrupt acknowledge. Active low.    |

| /MEMR    | 78                       | I/O  | Memory read. Active low.              |

| /MEMW    | 80                       | 1/0  | Memory write. Active low.             |

| /IOW     | 81                       | I/O  | I/O write. Active low.                |

| /IOR     | 82                       | 1/0  | I/O read. Active low.                 |

| VCC      | 29, 73                   |      | +5 volt supply                        |

| VSS      | 30, 43,<br>49, 74,<br>83 | •    | Ground                                |

## **Functional Description**

## **Interrupt Controller**

Two programmable interrupt controllers in the ACC 2000 function as a system wide interrupt manager for an IBM PC/AT system, compatible with the Intel 8259 interrupt controller. The interrupt controller efficiently determines when and which I/O device is serviced by the microcomputer.

The two cascaded interrupt controllers in the ACC 2000 provide a total of 15 possible interrupt sources. One of these interrupt request lines is used internally, providing a total of 14 possible external interrupt sources. The internal line connects to the 8254 Counter 0 output.

#### **DMA**

There are two 8237 equivalent DMA controllers cascaded together in the ACC 2000 chip. During a DMA cycle, one of the two external 8-bit latches hold the middle range address bits while the 74LS612 generates the upper range address bits. Once the hold request has been acknowledged, the DMA controller drives 24 address bits for a total addressing capability of 16 Megabytes. The middle address bits of the 24-bit address range are held in two sets of 8-bit registers, one register for each DMA controller. The DMA controller drives the value to be loaded onto the data bus, and then issues an address strobe signal to latch the data bus value into these registers.

The two 8237 compatible DMA controllers in the ACC 2000 provide a total of seven external DMA channels. Each channel has a 24-bit address output to access data throughout the entire 16 megabyte system address space. Channel 0 through channel 3 support 8-bit peripherals and an 8 or 16-bit memory. Each channel can transfer data in 64 Kbyte pages.

Channel 4 is used for cascading and is not available externally. Channel 5 through channel 7 support 16-bit I/O adapters to transfer data between 16-bit I/O adapters and 16-bit system memory. Each channel can transfer data in 128 Kbyte pages. The DMA function improves the computer system by allowing external devices to transfer information directly from and to the system memory.

#### Features include

- Address increment or decrement.

- Seven independent DMA channels with independent auto initialization for each channel.

- Each DMA request can be controlled individually to enable or disable.

- Software DMA request.

#### Timer/Counter

The Timer/Counter is the functional equivalent of an 8254 timer. It has three internal counters and clock inputs. The three clock inputs are tied to a clock of 1.19 MHz. The output of Counter 0 is connected to the IRQ input of interrupt controller one. Counter one output initiates a refresh cycle and Counter two output generates sound waveforms for speaker circuitry.

#### Features:

- Three independent 16-bit counters

- Count binary or BCD

Microelectronics \_\_

## **Memory Mapper**

The ACC 2000 has the equivalent of a 74LS612 to generate the upper address bits during a DMA cycle.

| Source M                 | emory Mapper              | 8237      |  |  |  |  |  |

|--------------------------|---------------------------|-----------|--|--|--|--|--|

| (for DMA Channels 0 - 3) |                           |           |  |  |  |  |  |

| Address                  | A23 <del>←→</del> A16     | A15 ←→ A0 |  |  |  |  |  |

| (fc                      | - 7)                      |           |  |  |  |  |  |

| Address                  | A23 <del>&lt;→→</del> A17 | A16 ←→ A1 |  |  |  |  |  |

#### PIO

The PIO is the system configuration to control the timer channel speaker ports. It also has circuitry to detect refresh. This condition can be read back as Bit 4.

## **Refresh Generation Logic**

Refresh circuitry contains an 8-bit counter for address SA0-7 during a refresh.

## Refresh/DMA Abitration Logic

ACC 2000 contains circuitry to control a refresh cycle. A 74LS590 equivalent 8-bit counter outputs the refresh addresses onto the memory bus when the refresh signal is pulled low.

There are two possible sources for a hold request to the CPU. Either the DMA controller issues a hold request or the output of Counter 1 in the 8254 makes a low to high transition. The HOLD line is active when either source is requesting a hold. The hold request from the

DMA controller is sampled on the rising edge of the DMA clock and the request from the timer is sampled on the falling edge of the DMA clock.

If the DMA controller's hold wins the arbitration, the HOLD is asserted, and it waits for a signal back from the CPU. When the DMA controller is finished, it negates its hold request signal to the arbiter. The arbitration then switches to a REFRESH cycle if there is a pending hold from the Counter/Timer, otherwise the arbiter inactivates the HOLD line and returns control to the CPU.

If a refresh cycle wins the arbitration, the HOLD is asserted and the ACC 2000 pulls the /REFRESH pin low. /REFRESH remains low for four SYSCLK rising edges. On the fourth rising edge of SYSCLK, the HOLD line is inactivated. However, if there is a pending hold request from the DMA controller on the fourth rising edge of SYSCLK, the REFRESH cycle is extended for one more SYSCLK cycle. The Hold request arbiter then acknowledges the hold request from the DMA controller.

## NMI and Port B Logic

The ACC 2000 contains non-maskable interrupt (NMI) signal generation logic. An NMI can be caused by an I/O error or by a parity error. Port B indentifies the source of the error. At power up, the NMI signal is masked off. NMI is enabled by writing to I/O address 070 hex with Bit 7 low; NMI is disabled by writing to I/O addresss 070 hex with Bit 7 high.

## **Rating Specifications**

## Absolute Maximum Ratings\*

$TA = 25^{\circ} C$

| Parameter                   | Symbol           | Min  | Max                  | Unit |

|-----------------------------|------------------|------|----------------------|------|

| Power supply voltage        | V <sub>cc</sub>  | -0.5 | 7.0                  | ٧    |

| Power dissipation (@5.25 V) | $W_d$            |      | 1                    | W    |

| Current (@5.25 V)           | I <sub>cc</sub>  |      | 50                   | mA   |

| Input voltage               | V <sub>i</sub>   | -0.5 | V <sub>CC</sub> +0.5 | ٧    |

| Output voltage              | $V_{o}$          | -0.5 | V <sub>cc</sub> +0.5 | V    |

| Operating temperature       | T <sub>op</sub>  | 0    | 70                   | °C   |

| Storage temperature         | T <sub>stg</sub> | -40  | 150                  | °C   |

<sup>\*</sup> Exposing the device to stress above these limits can cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods can affect device reliability.

## **Capacitance Limits**

$$TA = +25^{\circ} C$$

,  $VCC = 5 V$

| Parameter         | Symbol          | Min | Max | Unit | Test Condition                       |

|-------------------|-----------------|-----|-----|------|--------------------------------------|

| Input capacitance | C               |     | 10  | pF   | fc = 1 MHz<br>unmeasured pins at GND |

| I/O capacitance   | C <sub>io</sub> |     | 15  | pF   |                                      |

## **DC Characteristics**

$TA = 0^{\circ} C \text{ to } +70^{\circ} C$ , VCC = +5 V +/-10%

DRQ0-3, DRQ5-7, TMODE, HLDA, SA9, IOCHRDY, RESET, /PAR, SYSCLK, /MASTER, /IOCHCK, IRQ3-15, KBINT, /INTA, OSC

| Parameter             | Symbol | Min | Max | Unit | Test Condition    |

|-----------------------|--------|-----|-----|------|-------------------|

| Input low voltage     | VIL    | VSS | 0.8 | V    | VCC = 5 +/- 0.5 V |

| Input high<br>voltage | VIH    | 2.0 | VCC | V    | VCC = 5 +/- 0.5 V |

| Input low current     | IIL    |     | -10 | uA   | VIN > VSS         |

| Input high current    | шн     |     | -10 | uA   | VIN < VCC         |

#### XD0-7

| Parameter                | Symi | bol Min      | Max    | Unit    | Test Condition    |

|--------------------------|------|--------------|--------|---------|-------------------|

| Input low<br>voltage     | VIL  | VSS          | 0.2VCC | - 0.1 V | VCC = 5 +/- 0.5 V |

| Input high<br>voltage    | VIH  | 0.2VCC + 0.9 | VCC    | V       | VCC = 5 +/- 0.5 V |

| Input low current        | IIL  |              | -10    | uA      | VIN > 0.0V        |

| Input high<br>current    | ΙΙΗ  |              | 10     | uA      | VIN < VCC         |

| Output low voltage       | VOL  |              | 0.45   | V       | IOL = 3.2mA       |

| Output high voltage      | VOH  | 2.4          |        | ٧       | IOH = -0.08mA     |

| Tristate leakage current | IOZ  | -10          | 10     | uA      | 0 V < VOUT < VCC  |

| Parameter                   | Symbol | Min   | Max   | Unit | Test Condition    |

|-----------------------------|--------|-------|-------|------|-------------------|

| Input low<br>voltage        | VIL    | VSS   | 0.8   | V    | VCC = 5V +/- 0.5V |

| Input high<br>voltage       | VIH    | 2.0   | VCC   | V    | VCC = 5V +/- 0.5V |

| Input low<br>current        | IIL    |       | -10.0 | uA   | VIN > VSS         |

| Input high<br>current       | IIH    |       | 10.0  | uA   | VIN < VCC         |

| Output low<br>oltage        | VOL    | -     | 0.45  | V    | IOL = 9.6mA       |

| Output high<br>roltage      | VOH    | 2.4   | -     | V    | IOH = -0.08mA     |

| Fristate leakage<br>current | IOZ    | -10.0 | 10.0  | uA   | 0V < VOUT < VCC   |

NPCS, ADSTB8, /DACK1-3, /EDACK, CH/F, NMI, SPEAKER, HOLD, ADSTB16, /DAEN1-2, INTR

| Parameter           | Symbol | Min | Max  | Unit | Test Condition |

|---------------------|--------|-----|------|------|----------------|

| Output low voltage  | VOL    |     | 0.45 | V    | IOL = 3.2mA    |

| Output high voltage | VOH    | 2.4 |      | V    | IOH = -0.08mA  |

T/C

Microelectronics \_\_\_\_\_

| Parameter           | Symbol | Min | Max  | Unit | Test Condition |

|---------------------|--------|-----|------|------|----------------|

| Output low voltage  | VOL    |     | 0.45 | V    | IOL = 9.6mA    |

| Output high voltage | VOH    | 2.4 |      | V    | IOH = -0.08mA  |

#### A17-23

| Parameter                | Symbol | Min   | Max  | Unit | Test Condition  |

|--------------------------|--------|-------|------|------|-----------------|

| Output low voltage       | VOL    |       | 0.45 | V    | IOL = 3.2mA     |

| Output high voltage      | VOH    | 2.4   |      | V    | IOH = -0.08mA   |

| Tristate leakage current | IOZ    | -10.0 | 10.0 | uA   | 0V < VOUT < VCC |

## SA16

| Parameter                | Symbol | Min   | Max  | Unit | Test Condition  |

|--------------------------|--------|-------|------|------|-----------------|

| Output low voltage       | VOL    |       | 0.45 | V    | IOL = 9.6mA     |

| Output high voltage      | VOH    | 2.4   |      | V    | IOH = -0.08mA   |

| Tristate leakage current | IOZ    | -10.0 | 10.0 | uA   | 0V < VOUT < VCC |

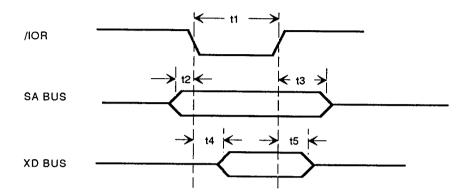

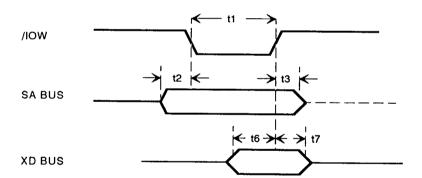

# **AC Specifications**

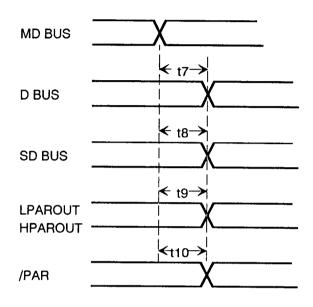

| Symbol | Parameter                                                    | Min | Max | Units           |

|--------|--------------------------------------------------------------|-----|-----|-----------------|

| t1     | /IOR or /IOW pulse width                                     | 110 |     | ns              |

| t2     | SA address valid to /IOR /IOW low setup time                 | 25  |     | ns              |

| t3     | SA address hold time from /IOR /IOW high                     | 13  |     | ns              |

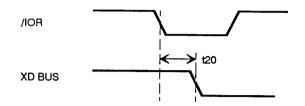

| t4     | XD data valid delay from /IOR low                            |     | 110 | ns              |

| t5     | XD data float delay from /IOR high                           | 0   | 90  | ns              |

| t6     | XD data valid to /IOW high setup time                        | 70  |     | ns              |

| t7     | XD data hold time from /IOW high                             | 15  |     | ns              |

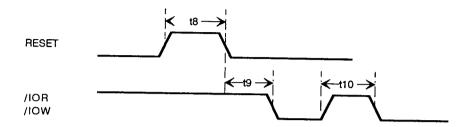

| t8     | RESET high pulse width                                       | 250 |     | ns              |

| t9     | RESET inactive to first /IOR or /IOW command                 | 4   |     | SYSCLK<br>Cycle |

| t10    | Command recovery time between successive /IOR or /IOW pulses | 125 |     | ns              |

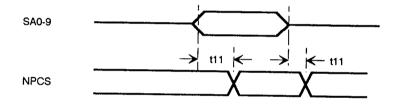

| t11    | NPCS valid from address delay                                |     | 51  | ns              |

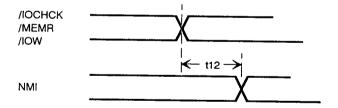

| t12    | NMI output delay                                             |     | 68  | ns              |

# **Peripheral Read Timing**

# **Peripheral Write Timing**

# **Command and Reset Timing**

# **Other Timing Waveforms**

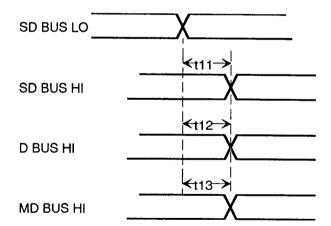

# **AC Specifications**

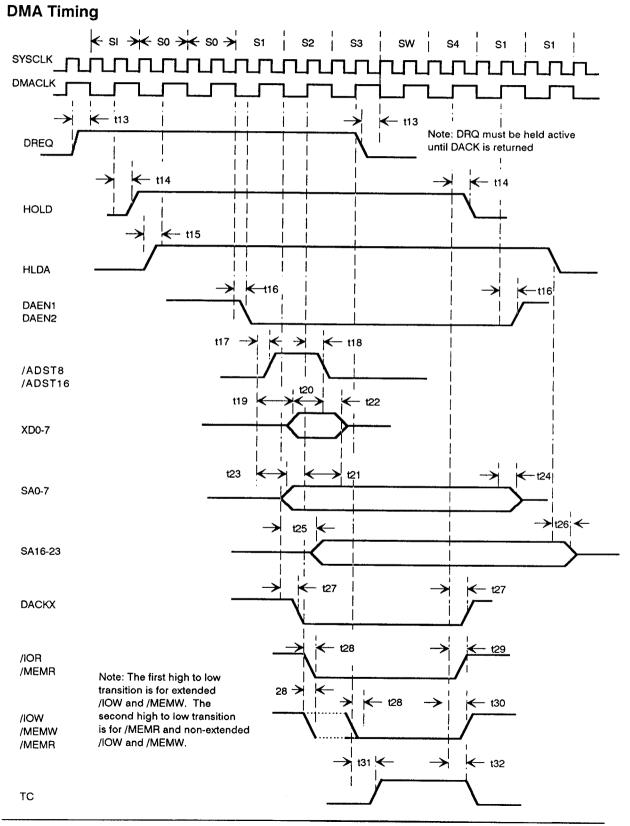

| Symbol | Parameter                                                   | Min | Max | Units |

|--------|-------------------------------------------------------------|-----|-----|-------|

| t13    | DRQ to SYSCLK high setup time                               | 0   | ,   | ns    |

| t14    | HOLD valid from SYSCLK high delay time                      |     | 50  | ns    |

| t15    | HLDA to SYSCLK high setup time                              | 25  |     | ns    |

| t16    | /DAEN1 valid from SYSCLK high delay time                    |     | 77  | ns    |

| t17    | ADSTB8 or ADSTB16 high from SYSCLK high                     |     | 72  | ns    |

| t18    | ADSTB8 or ADSTB16 low from SYSCLK high delay time           |     | 76  | ns    |

| t19    | Data float to active delay from SYSCLK high                 |     | 93  | ns    |

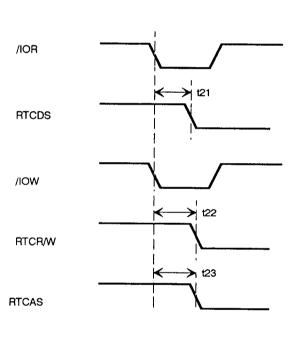

| t20    | Data to ADSTB8 or ADSTB16 low set up time                   | 70  |     | ns    |

| t21    | Data active to float delay from SYSCLK high                 |     | 92  | ns    |

| t22    | Data from ADSTB8 or ADSTB16 low HOLD time                   | 8   |     | ns    |

| t23    | low byte ADDR float to active from SYSCLK high              |     | 180 | ns    |

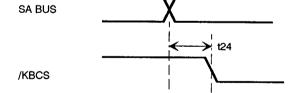

| t24    | low byte ADDR active to float delay from SYSCLK high        |     | 70  | ns    |

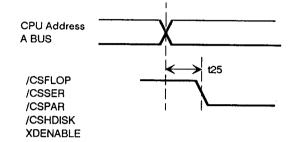

| t25    | high byte ADDR float to active delay from SYSCLK high       |     | 123 | ns    |

| t26    | high byte add active to float from HLDA low                 |     | 35  | ns    |

| t27    | /DACK valid from SYSCK high delay time                      |     | 83  | ns    |

| t28    | /IOR, /IOW, /MEMR, /MEMW active from SYSCLK high delay time |     | 53  | ns    |

| t29    | /IOR and /MEMR inactive from SYSCLK high delay time         |     | 97  | ns    |

| t30    | /IOW and /MEMW inactive from SYSCLK high delay time         |     | 80  | ns    |

| t31    | T/C active from SYSCLK high delay time                      |     | 82  | ns    |

| t32    | T/C inactive from SYSCLK high delay time                    |     | 82  | ns    |

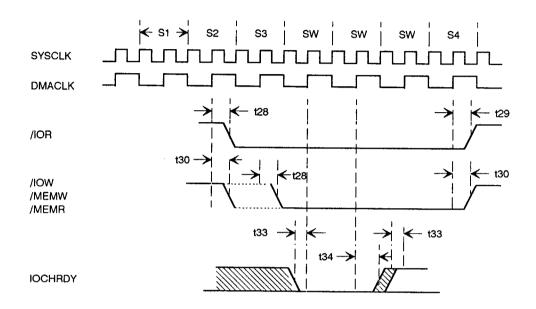

| t33    | IOCHRDY input setup time to SYSCLK high                     | 26  |     | ns    |

| t34    | IOCHRDY input hold time from SYSCLK high                    | 15  |     | ns    |

Microelectronics =

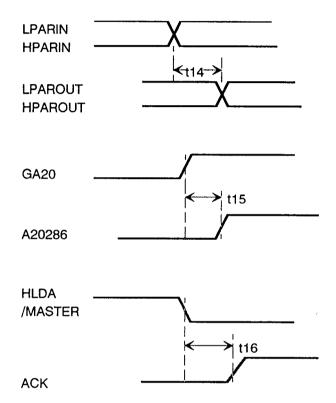

# **IOCHRDY Timing**

The first wait state is inserted by the internal circuitry of the ACC 2000. Additional wait states must be inserted using IOCHRDY.

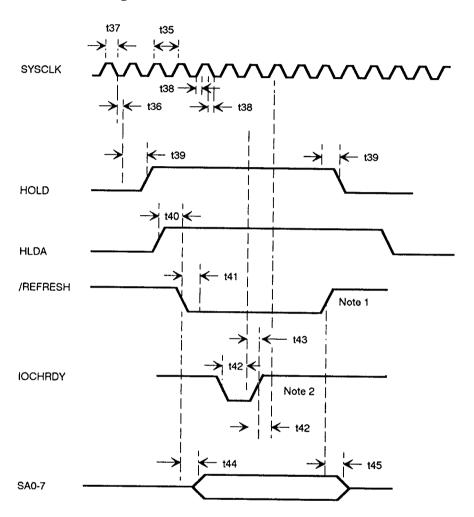

# **AC Specifications**

| Symbol | Parameter                                        | Min | Max | Units |  |

|--------|--------------------------------------------------|-----|-----|-------|--|

| t35    | SYSCLK cycle time                                | 62  |     | ns    |  |

| t36    | SYSCLK pulse width low                           | 25  |     | ns    |  |

| t37    | SYSCLK pulse width high 25                       |     |     |       |  |

| t38    | SYSCLK rise/fall time 10                         |     |     |       |  |

| t39    | HOLD valid from SYSCLK high delay time           |     | 50  | ns    |  |

| t40    | /REFRESH low delay from HLDA                     |     | 40  | ns    |  |

| t41    | /REFRESH low to SYSCLK high setup time           |     | 20  | ns    |  |

| t42    | IOCHRDY input setup time to SYSCLK high          | 26  |     | ns    |  |

| t43    | IOCHRDY input hold time from SYSCLK high         | 15  |     | ns    |  |

| t44    | REFRESH address valid delay from /REFRESH        |     | 92  | ns    |  |

| t45    | Refresh address hold time from /REFRESH inactive |     | 88  | ns    |  |

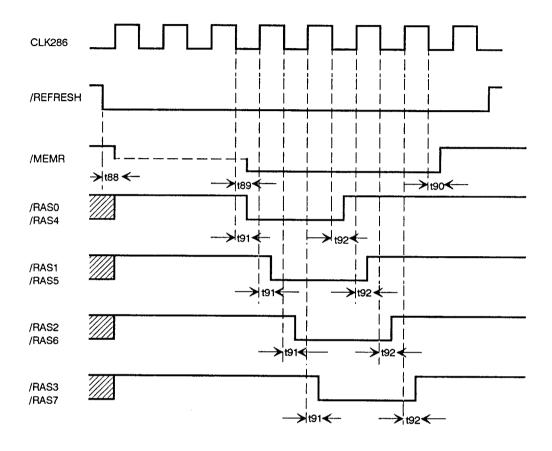

## **Refresh Timing**

#### Notes

- 1 A /REFRESH pulse is normally four SYSCLK cycles long.

- 2 /REFRESH cycles can be extended by inserting wait states using IOCHRDY.

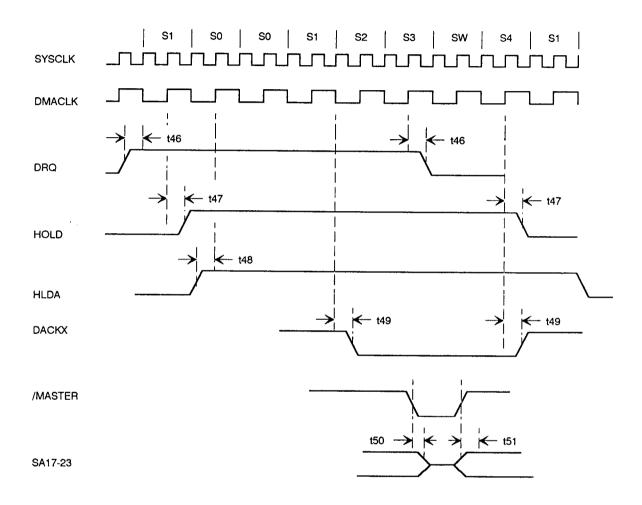

# **AC Specifications**

| Symbol | Parameter                                     | Min | Max | Units |

|--------|-----------------------------------------------|-----|-----|-------|

|        |                                               |     |     |       |

| t46    | DRQ to SYSCLK high setup time                 | 0   |     | ns    |

| t47    | HOLD valid from SYSCLK high delay time        |     | 50  | ns    |

|        |                                               |     |     |       |

| t48    | HLDA to SYSCLK high set up time               | 25  |     | ns    |

| t49    | /DACK valid from SYSCLK high delay time       |     | 83  | ns    |

| t50    | SA17-SA23 float from /MASTER low delay time   | 11  | 36  | ns    |

| t51    | SA17-SA23 active from /MASTER high delay time | 11  | 36  | ns    |

## /MASTER Timing

Note: A new bus master must be programmed in Cascade mode.

The new master must not pull /MASTER low until it has received the corresponding /DACK signal.

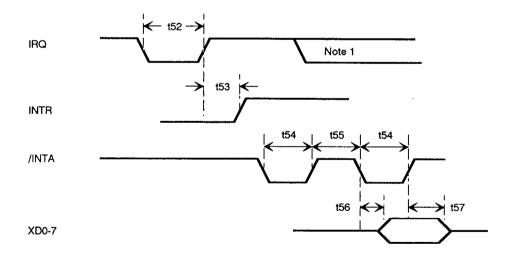

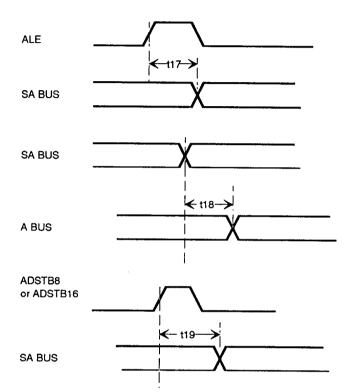

# **AC Specifications**

| Symbol | Parameter                                        | Min | Max | Units |

|--------|--------------------------------------------------|-----|-----|-------|

| t52    | Interrupt request pulse width low                | 60  |     | ns    |

| t53    | Interrupt output delay                           |     | 63  | ns    |

| t54    | /INTA pulse width low                            | 80  |     | ns    |

| t55    | /INTA to next /INTA within an INTA sequence only | 120 |     | ns    |

| t56    | XD data valid delay from /INTA low .             |     | 109 | ns    |

| t57    | XD data float delay from /INTA high              | 22  | 69  | ns    |

# Interrupt Timing

Note 1 IRQ must remain active until the first /INTA pulse.

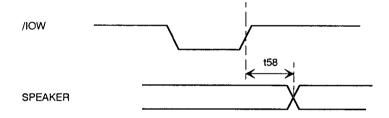

# **AC Specifications**

| Symbol | Parameter                               | Min | Max | Units |

|--------|-----------------------------------------|-----|-----|-------|

| t58    | SPEAKER valid from /IOW high delay time |     | 100 | ns    |

Microelectronics \_\_\_\_\_

# 8254 Timing

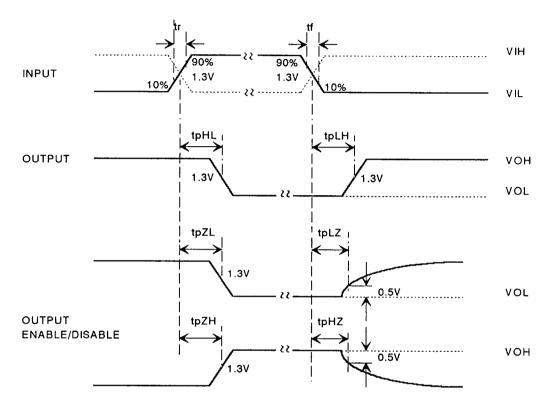

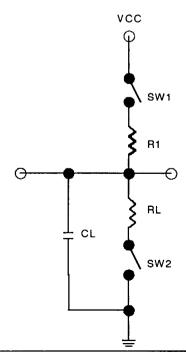

## **Load Circuit and AC Characteristics Measurement**

| Parameter    | Output Type     | Symbol | CL(p | F) R1 | RL   | SW1 | SW2 |

|--------------|-----------------|--------|------|-------|------|-----|-----|

| Propagation  | Totem pole      |        |      |       |      |     |     |

| Delay        | 3-state         | tPLH   | 50   |       | 1.0K | off | on  |

|              |                 | tPHL   | 50   |       | 1.0K | off | on  |

| Time         | Bidirectional   |        |      |       |      |     |     |

| Propagation  | Open drain or   | tPLH   | 50   | 0.5K  |      | on  | off |

| Delay time   | Open collection | tPHL   | 50   | 0.5K  |      | on  | off |

| Disable time | 3-state         | tPLZ   | 5    | 0.5K  | 1.0K | on  | on  |

|              | Bidirectional   | tPHZ   | 5    | 0.5K  | 1.0K | off | on  |

| Enable time  | 3-state         | tPZL   | 50   | 0.5K  | 1.0K | on  | on  |

|              | Bidirectional   | tPZH   | 50   | 0.5K  | 1.0K | off | on  |

# **AC Characteristics Measurement**

VIH = 3 V, VIL = 0, tr < 10 ns, tf < 5 ns

## **Load Circuit**

Microelectronics -

# ACC 2120 PC/AT Integrated System Controller

The ACC 2120 is an integrated high performance CMOS PC/AT\* system controller that integrates the following functions and logic into one single chip: clock generator and selector, bus controller, bus swap logic, coprocessor interface logic, memory decoder, command delay and wait state generation circuits, reset and shut down logic, and ADDR/DATA control logic.

#### **Features**

- 100% hardware and software compatible with the IBM\* PC/AT

- Supports Intel's 286 and 386SX microprocessors

- Built-in 80287 and 80387SX coprocessor interface logic

- Fully compatible with Intel's 82288 bus controller

- Built-in command delay and wait state generation logic

- Supports CPU operation up to 25 MHz

- Supports 16 MB on board memory

- Turbo speed change performed through hardware or software

- 1-Way, 2-Way or 4-Way page interleaved memory controller

- Optional Direct Access Memory Controller\*\*

- Simultaneous EMS and Shadow RAM \*\*

- Simultaneous extended and EMS expanded memory

- Optional Direct Memory Access mode \*\*

- Supports 64K x 1, 256K x 1, 256K x 4,

1M x 1, 1M x 4, 4 M x 1 memory and 16 MB on motherboard

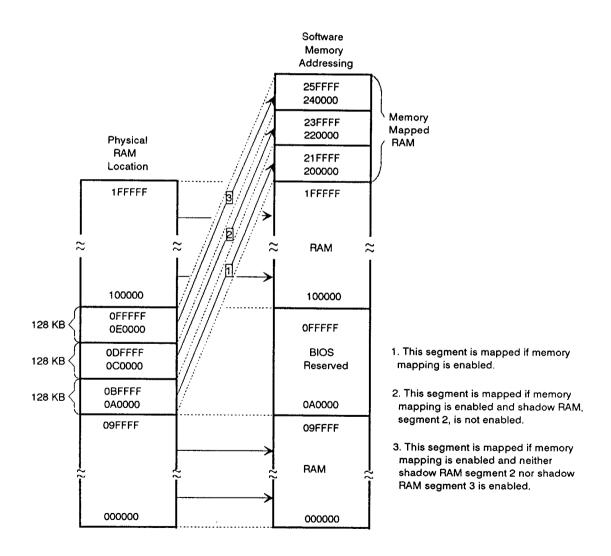

- 384K Memory mapping above the resident RAM address space

- 512K Memory Mapping above the resident RAM address space \*\*

- Supports shadow RAM for efficient BIOS execution

- Programmable wait states for ROM

- ROM chip select for 27256 or 27512

- Built-in OS/2 optimization circuitry

- Supports EMS 4.0 address translation logic with 4 map registers

- Staggered memory refresh

- 1.2 micron high performance CMOS technology

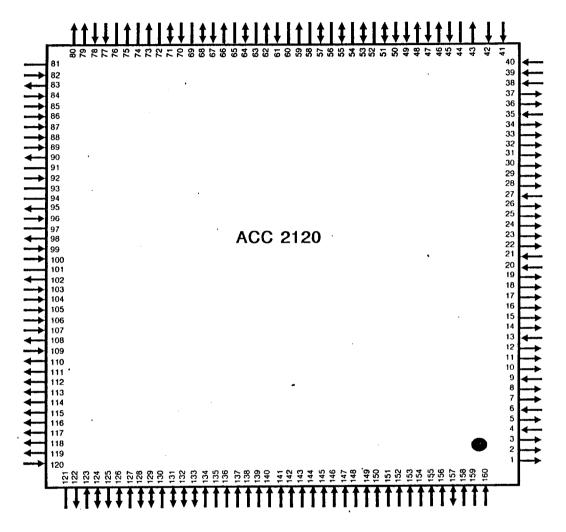

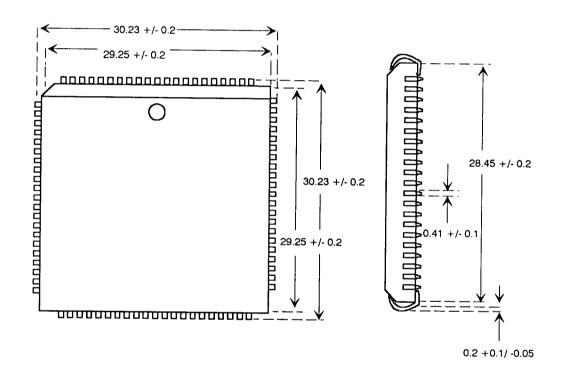

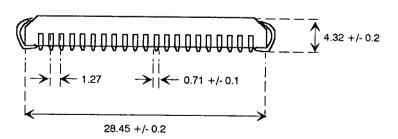

- 160-pin PFP package

- \*Trademarks of International Business Machines

- \*\*Available fourth quarter 1989

## **Block Diagram**

## Pin Diagram

| 1 /LMEMW | 21 VSS      | 41 /MCS16  | 61 VSS     | 81 Reserved | 101 Reserved | 121 N/C    | 141 VSS |

|----------|-------------|------------|------------|-------------|--------------|------------|---------|

| 2 MA0    | 22 /RAS3    | 42 /IOCS16 | 62 PCLK    | 82 KBLRST   | 102 /INTA    | 122 CLK286 | 142 AG  |

| 3 MA1    | 23 /RAS4    | 43 RESET   | 63 N/C     | 83 CLUART   | 103 /DMEM1   | 123 HLDA   | 143 A7  |

| 4 VCC    | 24 /RAS5    | 44 N/C     | 64 /SBHE   | 84 PWR/GD   | 104 /DMEM2   | 124 /SO    | 144 A8  |

| 5 MA2    | 25 /RAS6    | 45 /XDEN   | 65 N/C     | 85 16MHZ    | 105 VSS      | 125 RST286 | 145 A9  |

| 6 VCC    | 26 /RAS7    | 46 XDDIR   | 66 /MDLAT  | 86 VCC      | 106 /REFRESH | 126 /S1    | 146 A10 |

| 7 MA3    | 27 VSS      | 47 /BSY287 | 67 PWR/MX  | 87 32MHZ    | 107 NPCS     | 127 /BHE   | 147 A11 |

| B MA4    | 28 /CASOL   | 48 /BSY286 | 68 /MEMR   | 88 VSS      | 108 IRQ13    | 128 D0     | 148 A12 |

| 9 VSS    | 29 /CAS0H   | 49 VCC     | 69 N/C     | 89 HCHF     | 109 VDD      | 129 D1     | 149 A13 |

| 10 MA5   | 30 /CAS1L   | 50 VSS     | 70 VSS     | 90 TURBO    | 110 L374     | 130 VSS    | 150 VSS |

| 11 MA6   | 31 /CAS1H   | 51 /IOR    | 71 /MEMW   | 91 Reserved | 111 CSPCK    | 131 D2     | 151 A14 |

| 12 MA7   | 32 /CAS2L . |            | 72 N/C     | 92 /CDINT   | 112 /ENLBY1  | 132 D3     | 152 A15 |

| 13 VSS   | 33 /CAS2H   | 53 /IOW    | 73 /SMEMR  | 93 Reserved | 113 /ENLBY2  | 133 D4     | 153 A16 |

| 14 MAB   | 34 /CAS3L   | 54 N/C     | 74 N/C     | 94 Reserved | 114 /ENHBY   | 134 M/-IO  | 154 A17 |

| 15 MA9   | 35 VSS      | 55 SA0     | 75 /SMEMW  | 95 /ENAS    | 115 DT/-R    | 135 A0     | 155 A18 |

| 16 MA10  | 36 /CAS3H   | 56 N/C     | 76 N/C     | 96 GATEA20  | 116 MDT/-R   | 136 A1     | 156 A19 |

| 17 /RAS0 | 37 /ENROM   | 57 LA20    | 77 OSC14M  | 97 KBRST    | 117 /D245    | 137 A2     | 157 A20 |

| 18 /RAS1 | 38 VCC      | 58 N/C     | 78 IORDY   | 98 Reserved | 118 /G245    | 138 A3     | 158 A21 |

| 19 /RAS2 | 39 /0WS     | 59 ALE     | 79 CLK8042 | 99 /ERROR   | 119 /READY   | 139 A4     | 159 A22 |

| 20 VCC   | 40 /MASTER  | 60 N/C     | 80 /RESET  | 100 VCC     | 120 VCC      | 140 A5     | 160 A23 |

| Symbol               | Pin         | I/O        | Pin Descriptions                              |

|----------------------|-------------|------------|-----------------------------------------------|

| Note: All pins are 6 | mA drive ur | less other | wise noted                                    |

| /LMEMW               | 1           | 0          | Resident RAM write enable. 12 mA.             |

| MAO                  | 2           | 0          | Memory address bit. 12 mA.                    |

| MA1                  | 3           |            |                                               |

| MA2                  | 5           |            |                                               |

| MA3                  | 7           |            |                                               |

| MA4                  | 8           |            |                                               |

| MA5                  | 10          |            |                                               |

| MA6                  | 11          |            |                                               |

| MA7                  | 12          |            |                                               |

| MA8                  | 14          |            |                                               |

| MA9                  | 15          |            |                                               |

| MA10                 | 16          |            |                                               |

| /RAS0                | 17          | 0          | DRAM row address strobe. 12 mA.               |

| /RAS1                | 18          |            |                                               |

| /RAS2                | 19          |            |                                               |

| /RAS3                | 22          |            |                                               |

| /RAS4                | 23          |            |                                               |

| /RAS5                | 24          |            |                                               |

| /RAS6                | 25          |            |                                               |

| /RAS7                | 26          |            |                                               |

| /CAS0L               | 28          | 0          | DRAM column address strobe, low byte. 12 mA.  |

| /CAS1L               | 30          |            |                                               |

| /CAS2L               | 32          |            |                                               |

| /CAS3L               | 34          |            |                                               |

| /CAS0H               | 29          | 0          | DRAM column address strobe, high byte. 12 mA. |

| /CAS1H               | 31          |            |                                               |

| /CAS2H               | 33          |            |                                               |

| /CAS3H               | 36          |            |                                               |

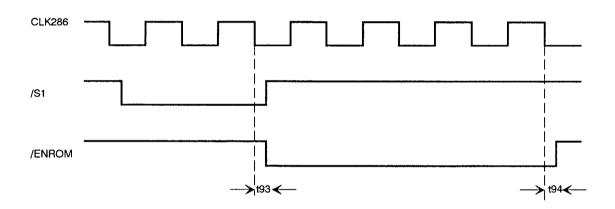

| /ENROM               | 37          | 0          | ROM chip select. Active low.                  |

| /0WS (TSTCLR)        | 39          | 1          | Zero wait state input.                        |

| /MASTER              | 40          | 1          | Signal to gain system control.                |

| /MCS16               | 41          | 1          | Memory 16-bit chip select.                    |

| /IOCS16              | 42          | ı          | I/O 16-bit chip select.                       |

| RESET                | 43          | 0          | System reset. Active high.                    |

| Symbol   | Pin | I/O | Pin Description                              |

|----------|-----|-----|----------------------------------------------|

| /XDEN    | 45  | 1   | XD enable input.                             |

| XDDIR    | 46  | 0   | XD direction output.                         |

| /BSY287  | 47  | ı   | Busy math processor input.                   |

| /BSY286  | 48  | 0   | Busy CPU output.                             |

| /IOR     | 51  | I/O | I/O read. 24 mA                              |

| /IOW     | 53  | I/O | I/O write. 24 mA                             |

| SA0      | 55  | 1/0 | System address bit 0, select low byte. 24 mA |

| LA20     | 57  | I/O | LA Bus, A20 I/O pin. 24 mA                   |

| ALE      | 59  | 0   | Address latch enable. 24 mA                  |

| PCLK     | 62  | 0   | Peripheral clock. 24 mA                      |

| /SBHE    | 64  | I/O | System bus high byte enable. 24 mA           |

| /MDLAT   | 66  | 0   | Memory data latch.                           |

| PWR/MX   | 67  | 1   | Debounce bypass.                             |

| /MEMR    | 68  | I/O | Memory read. 24 mA                           |

| /MEMW    | 71  | I/O | Memory write. 24 mA                          |

| /SMEMR   | 73  | 0   | System memory read. 24 mA                    |

| /SMEMW   | 75  | 0   | System memory write. 24 mA                   |

| OSC14M   | 77  | I   | 14.318 MHz oscillator input.                 |

| IORDY    | 78  | 1   | I/O channel ready.                           |

| CLK8042  | 79  | 0   | 8042 Clock. 12 mA                            |

| /RESET   | 80  | 0   | System reset. Active low.                    |

| Reserved | 81  |     |                                              |

| KBLRST   | 82  | 1   | Reset switch input.                          |

| Symbol           | Pin        | I/O  | Pin Description                                                                                                  |

|------------------|------------|------|------------------------------------------------------------------------------------------------------------------|

| CLUART           | 83         | 0    | UART clock 12 mA                                                                                                 |

| PWR/GD           | 84         | I    | Power good.                                                                                                      |

| 16MHZ            | 85         | 1    | 16 MHz OSC input.                                                                                                |

| 32MHZ            | 87         | 1    | System frequency OSC input.                                                                                      |

| HCHF             | 89         | 1    | Hardware Turbo mode select.                                                                                      |

| TURBO            | 90         | 0    | Turbo mode. 12 mA                                                                                                |

| Reserved         | 91         |      | Tied to VCC.                                                                                                     |

| /CDINT           | 92         | 1    | 386SX input                                                                                                      |

| Reserved         | 93         |      | Tied to VCC.                                                                                                     |

| Reserved         | 94         |      | Tied to VCC.                                                                                                     |

| /ENAS            | 95         | 0    | Real time clock address strobe enable.                                                                           |

| GATEA20          | 96         | l    | Gate A20 enable. Active low.                                                                                     |

| KBRST            | 97         | 1    | Keyboard reset.                                                                                                  |

| Reserved         | 98         |      | Do not connect.                                                                                                  |

| /ERROR           | 99         | 1    | Error status.                                                                                                    |

| Reserved         | 101        |      | Do not connect.                                                                                                  |

| /INTA            | 102        | 0    | Interrupt acknowledge. Active low.                                                                               |

| /DMEN1<br>/DMEN2 | 103<br>104 | <br> | DMA address enable for 8-bit data transfer. Active low. DMA address enable for 16-bit data transfer. Active low. |

| /REFRESH         | 106        | I    | Refresh cycle. Active low.                                                                                       |

| NPCS             | 107        | 1    | Numeric processor chip select.                                                                                   |

| IRQ13            | 108        | 0    | Interrupt request.                                                                                               |

| L374             | 110        | 0    | Latch enable for CPU data bus to system data bus conversion.                                                     |

| Symbol                                                                                                           | Pin                                                                                                                               | I/O | Pin Description                                                                                                          |  |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------|--|

| CSPCK                                                                                                            | 111                                                                                                                               | 0   | Parity error output enable.                                                                                              |  |

| /ENLBY1                                                                                                          | 112                                                                                                                               | 0   | System data bus to local data bus low byte output enable (active low). Used for 8-bit I/O port or extension memory read. |  |

| /ENLBY2                                                                                                          | 113                                                                                                                               | 0   | System/Local data bus (CSPCK=0) or Memory/Local data bus (CSPCK=1) low byte transfer enable. Active low.                 |  |

| /ENHBY                                                                                                           | 114                                                                                                                               | 0   | Enable high byte.                                                                                                        |  |

| DT/-R                                                                                                            | 115                                                                                                                               | 0   | Data transmit/receive.                                                                                                   |  |

| MDT/-R                                                                                                           | 116                                                                                                                               | 0   | Memory data transmit/receive.                                                                                            |  |

| /D245                                                                                                            | 117                                                                                                                               | 0   | Direction control for LS245.                                                                                             |  |

| /G245                                                                                                            | 118                                                                                                                               | 0   | Gate input for LS245.                                                                                                    |  |

| /READY                                                                                                           | 119                                                                                                                               | 0   | Ready signal to CPU. 12 mA                                                                                               |  |

| CLK286                                                                                                           | 122                                                                                                                               | 0   | System clock input. 24 mA                                                                                                |  |

| A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15<br>A16<br>A17 | 135<br>136<br>137<br>138<br>139<br>140<br>142<br>143<br>144<br>145<br>146<br>147<br>148<br>149<br>151<br>152<br>153<br>154<br>155 |     | CPU address bit.                                                                                                         |  |

| A20                                                                                                              | 157                                                                                                                               | I/O | 12mA                                                                                                                     |  |

| Symbol                     | Pin                                                            | I/O       | Pin Description             |  |

|----------------------------|----------------------------------------------------------------|-----------|-----------------------------|--|

| A21<br>A22<br>A23          | 158<br>159<br>160                                              | <br> <br> |                             |  |

| HLDA                       | 123                                                            | 1         | Hold acknowledge from CPU.  |  |

| /S0<br>/S1                 | 124<br>126                                                     | I/O       | Bus cycle status bit. 12 mA |  |

| RST286                     | 125                                                            | 0         | Reset CPU.                  |  |

| /BHE                       | 127                                                            | 1         | High byte enable from CPU.  |  |

| D0<br>D1<br>D2<br>D3<br>D4 | 128<br>129<br>131<br>132<br>133                                | I/O       | CPU data bus. 12 mA         |  |

| M/-IO                      | 134                                                            | 1         | Memory or I/O select.       |  |

| VCC                        | 4, 6, 20, 38,<br>49, 86, 100,<br>109, 120                      |           | +5 volts                    |  |

| vss                        | 9, 13, 21,<br>27, 35, 50, 61,<br>70, 88, 105,<br>130, 141, 150 |           | Ground                      |  |

| N.C.                       | 44, 52, 54, 56,<br>58, 60, 63, 65,<br>69, 72, 74, 76,<br>121   |           |                             |  |

## **Functional Description**

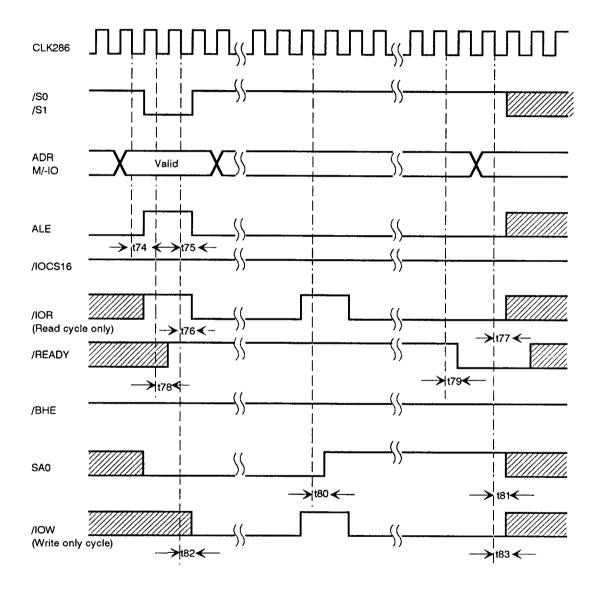

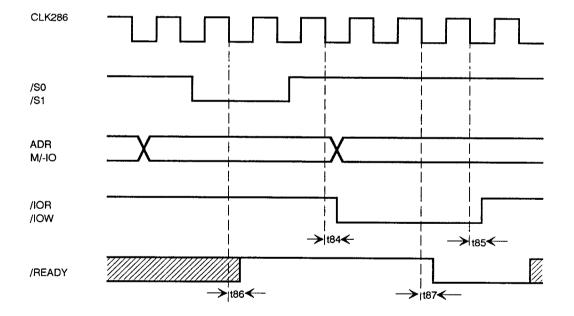

#### **Bus Controller and Converter**

The ACC 2120 CPU bus controller is functionally equivalent to Intel's 82288 multibus adapter, providing CPU bus and signal control for both system and peripheral buses. The /S0, /S1 and M/-IO signals carry data from the CPU, announcing a bus cycle and defining its type. Table 1 lists and defines the different types of bus cycles.

Table 1 ACC 2120 Bus Cycle Definitions

| COD,<br>/INTA | M/-IO | /S1 | /S0 | Bus Cycle Initiated    |

|---------------|-------|-----|-----|------------------------|

| 0 (low)       | 0     | 0   | 0   | Interrupt acknowledge  |

| 0             | 0     | 0   | 1   | Reserved               |

| 0             | 0     | 1   | 0   | Reserved               |

| 0             | 0     | 1   | 1   | Not a status cycle     |

| 0             | 1     | 0   | 0   | If $A1=1$ , then halt; |

|               |       |     |     | else, shutdown         |

| 0             | 1     | 0   | 1   | Memory data read       |

| 0             | 1     | 1   | 0   | Memory data write      |

| 0             | 1     | 1   | 1   | Not a status cycle     |

| 1 (high)      | 0     | 0   | 0   | Reserved               |

| 1             | 0     | 0   | 1   | I/O read               |

| 1             | 0     | 1   | 0   | I/O write              |

| 1             | 0     | 1   | 1   | Not a status cycle     |

| 1             | 1     | 0   | 0   | Reserved               |

| 1             | 1     | 0   | 1   | Memory instruction     |

|               |       |     |     | read                   |

| 1             | 1     | 1   | 0   | Reserved               |

| 1             | 1     | 1   | 1   | Not a status cycle     |

The CPU bus controller has four operation modes.

## **AT CPU Mode**

This mode is active when HLDA is low. The CPU bus controller generates /IOR, /IOW, /INTA, /MR288, /MW288, and DT/-R signals.

#### **DMA Mode**

DMA mode is active if HLDA and /DMEN1 or /DMEN2 signals are active. The DMA controller drives the /IOR, /IOW, /MR288, and /MW288 signals.

#### Refresh Mode

Refresh mode is active when a refresh request is output from the ACC 2000. The /MR288 signal generates the refresh for DRAM memory. /MW288, /IOR, and /IOW signals are in high impedance state.

#### **Master Mode**

Master mode is active when HLDA is active and a card in the I/O slot pulls /MASTER low. The card controls system address, data line and control line.

#### **BUS Conversion**

The ACC 2120 contains logic to convert between 16-bit and 8-bit data accessing. The /D245 and /G245 signals control this interface logic.

#### 287 Interface Control

Additional circuitry supports the decoding required to select and reset the numeric coprocessor. /287CS is a chip select decoded at addresses 0F8-0FF hex. The RST287 signal resets the math coprocessor. RST287 is activated by a system reset or by performing a write operation to I/O port 0F1 hex. IRQ13 is connected to the ACC 2000 IRQ13 line.

#### 386SX CPU Interface

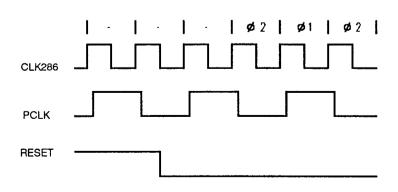

The 386SX CPU interface provides logic to convert /ADS, W/-R, and D/-C signals to equivalent 286 signals (/S0 and /S1). It also enables a timed reset, ensuring the CPU is synchronized to the system. See figure 1.

386SX CPU timing is incompatible with 286 CPU timing because the 386SX starts its cycle on the rising edge of the clock and the 286 starts its cycle on the falling edge. To correct this problem, the ACC 2120 has logic designed to invert CLK286 automatically.

#### 387SX Interface

The ACC 2120 provides an interface between the 80387SX and the 80386SX by interconnecting /ADS, /WR, M/-IO, A23, A2,

RESETIN, and CLK2 signals between the CPU and the 387SX. /READYO is fed back to the ACC 2120 from the 387SX when coprocessor cycles are terminated. A high-speed transfer of opcodes and operands between the 386SX and the 387SX occurs through a communication protocol.

Coprocessor errors are handled with an ACC 2000 request, through a standard ISA scheme from IRQ13.

The 80387SX can run in synchronous or asynchronous mode by connecting CKM to VCC or GND respectively. However, to run in asynchronous mode, the 80387SX requires an independent clock source for NUMCLK2.

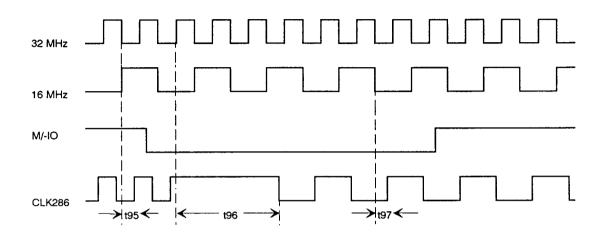

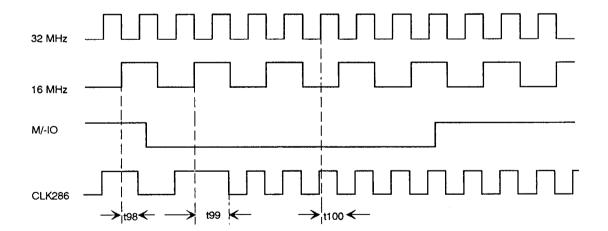

#### **Clock Generator**

The ACC 2120 Clock Generator provides clock signals to support internal timing requirements. It provides clock outputs for the CPU, the NPU, the DMA, the Keyboard Controller, and the UART. Clock signals are generated from three oscillator inputs, OSC14M, OSC16M, and OSC32M. The OSC14M is driven by a 14.31818 MHz oscillator. This frequency generates output clocks, CL287, CL8042, and CLUART. The other two oscillators are used to

Figure 1 RESET and PCLK Timing for 80386SX CPU

Microelectronics =

generate CPU and AT Bus clocks. The CPU clock is switched between these two inputs by turbo speed control logic. For normal speed and AT Bus cycles, the CPU clock is switched to OSC16M and driven by a 16 MHz oscillator. obtaining a processing speed of 8 MHz. Processing speed equals half the CPU clock frequencies. For turbo speed, the CPU clock is switched to OSC32M, with variable input frequency. A 32 MHz frequency is used for a turbo processing speed of 16 MHz. A 25 MHz or 20 MHz oscillator is used for 12.5 MHz or 10 MHz processing speed, and a 40 MHz oscillator is used for a 20 MHz processing speed. A 50 MHz oscillator is used for a speed of 25 MHz.

### **Turbo Speed Control Logic**

The system clock is switched between turbo and normal speed by either software or hardware.

If the CHF bit in the configuration register is programmed high or the HCHF signal generates a rising edge trigger, the system

clock generator can be set to turbo mode by selecting the higher speed (32 MHz) oscillator. Otherwise, a slower speed oscillator is selected, and the system clock runs at normal speed.

### **Configuration Registers**

The ACC 2120 contains thirteen configuration registers which provide a variety of functions. These functions are concerned with system initialization and software control of advanced memory control features. For system initialization, these configuration registers implement a no-cost, no-space alternative to system board DIP switches. For advanced memory control, these registers provide maximum flexibility and convenience for programming. Configuration registers are selected by the configuration index register at I/O address F2. Table 2 contains a summary of configuration registers.

Configuration registers are programmed with an indirect addressing scheme using I/O addresses F2 and F3. I/O address F2 contains

Table 2 ACC 2120 Configuration Registers

| Register | Bit 4  | Bit 3  | Bit 2      | Bit 1              | Bit 0      |

|----------|--------|--------|------------|--------------------|------------|

| 20       | TPI    |        | memory cor | nfiguration select |            |

| 21       | CHF    |        | ′          | DA/PI              |            |

| 22       |        | SH2WR  | SH2EN      | SH3WR              | SH3EN      |

| 23       | MMEN   | EMSEN  |            | ROM wait st        | ate select |

| 24       | ER0A23 | ER0A22 | ER0A21     | ER0A20             | ER0A19     |

| 25       | ER0A18 | ER0A17 | ER0A16     | ER0A15             | ER0A14     |

| 26       | ER1A23 | ER1A22 | ER1A21     | ER1A20             | ER1A19     |

| 27       | ER1A18 | ER1A17 | ER1A16     | ER1A15             | ER1A14     |

| 28       | ER2A23 | ER2A22 | ER2A21     | ER2A20             | ER2A19     |

| 29       | ER2A18 | ER2A17 | ER2A16     | ER2A15             | ER2A14     |

| 2A       | ER3A23 | ER3A22 | ER3A21     | ER3A20             | ER3A19     |

| 2B       | ER3A18 | ER3A17 | ER3A16     | ER3A15             | ER3A14     |

| 31       |        |        |            | HOTSWR             | ENGA20     |

the write-only configuration index register. F2 selects the corresponding configuration register accessed at I/O address F3. To write a value of "E8" into configuration register 2A, the configuration index register at I/O address F2 must first be written with a value of "2A," then register at I/O address F3 with a value of "E8." Configuration registers are selected by the configuration index register at I/O address F2. Table 2 contains a summary of configuration registers.

The specific functions of each configuration register are detailed below.

#### **Configuration Register 20**

| Bit | Function                    |

|-----|-----------------------------|

| 7-5 | Unused                      |

| 4   | Turbo Page Interleaved mode |

| 3-0 | Memory configuration select |

Bit 4 When set to 1, this bit selects the Turbo Page Interleaved mode which provides improved memory performance (approximately 0.4 wait states) but requires faster DRAMs. Default is zero.

#### Bits 3-0

These bits are encoded to select the type and quantity of system board DRAM. Refer to following table. Default for these bits is 9 hex.

An unused bit is ignored by the system and is always read back as a one.

Note that system board memory is organized in banks consisting of 18 bits of DRAM each (two 8-bit bytes plus two parity bits).

| Bits    | Option | Banks | Type | Total |

|---------|--------|-------|------|-------|

| 3 2 1 0 |        |       |      | DRAM  |

| 0000    | 0      | 1     | 256K |       |

|         |        | 1     | 64K  | 640K* |

| 0001    | 1      | 1     | 256K | 512K  |

| 0010    | 2      | 2     | 256K | 1M    |

| 0011    | 3      | 4     | 256K | 2M    |

| 0100    | 4      | 6     | 256K | ЗМ    |

| 0101    | 5      | 8     | 256K | 4M    |

| 0 1 1 0 | 6      | 1/2   | 1M   | 1M    |

| 0 1 1 1 | 7      | 1     | 1M   | 2M    |

| 1000    | 8      | 2     | 1M   | 4M    |

| 1001    | 9      | 4     | 1M   | M8    |

| 1010    | 10     | 6     | 1M   | 12M   |

| 1011    | 11     | 8     | 1M   | 16M   |

| 1 1 0 0 | 12     | 1     | 4M   | 8M    |

| 1 1 0 1 | 13     | 2     | 4M   | 16M   |

Option 0 has two different types of memory, one type for each bank, to obtain a total of 640K RAM.

#### **Configuration Register 21**

| Function                                   |

|--------------------------------------------|

| Unused                                     |

| Turbo mode select                          |

| Reserved                                   |

| Direct access/Page Interleaved mode select |

| Reserved                                   |

|                                            |

- Bit 4 When set to 1, this bit selects the Turbo frequency mode. When this bit is set high, the system is placed in Turbo mode. Default is zero.

- Bit 1 When set to 1, this bit selects the direct access memory control mode. This mode provides zero wait state performance but requires fast DRAM. When set to 0, this bit selects the Page interleaved memory control mode.

Microelectronics =

Page interleaved mode reduces performance by only 0.4 to 0.7 wait states, but functions with slower and less expensive DRAMs. Default for Bit 1 is zero.

Note that all reserved bits must be written to zero, even though they can read back as ones. Any readback from reserved bits can be ignored.

### **Configuration Register 22**

| garanen riogioto, LL |                                                                                                                                                       |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit                  | Function                                                                                                                                              |  |

| 7-5                  | Unused                                                                                                                                                |  |

| 4                    | Reserved                                                                                                                                              |  |

| 3                    | Shadow RAM write only mode,<br>Segment 2                                                                                                              |  |

| 2                    | Shadow RAM enable, Segment 2                                                                                                                          |  |

| 1                    | Shadow RAM write only mode,<br>Segment 3                                                                                                              |  |

| 0                    | Shadow RAM enable, Segment 3                                                                                                                          |  |

|                      |                                                                                                                                                       |  |

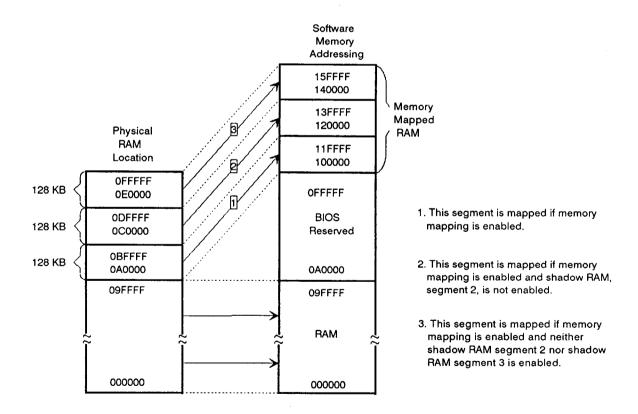

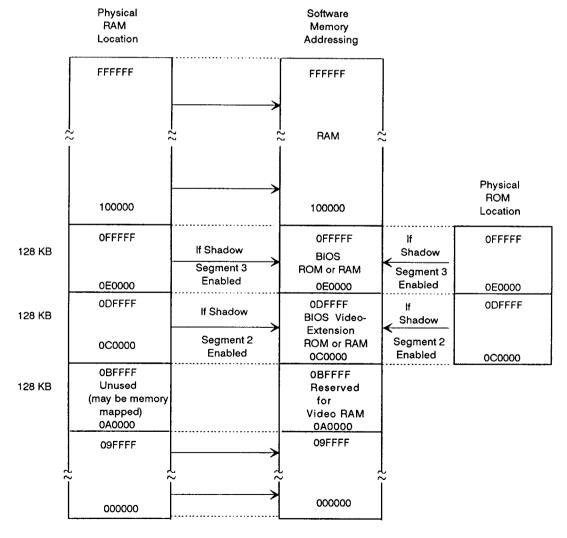

| Bit 3                | When set to 1, this bit places the Shadow RAM for Segment 2 (0C0000 to 0DFFFF) into write mode. Refer to the Shadow RAM description. Default is zero. |  |

| Bit 2                | When set to 1, this bit enables the Shadow RAM at Segment 2 (0C0000 to 0DFFFF). Default is zero.                                                      |  |

| Bit 1                | When set to 1, this bit places the Shadow RAM at Segment 3 (0E0000 to 0FFFFF) into write mode. Default is zero.                                       |  |

| Bit 0                | When set to 1, this bit enables the Shadow RAM at Segment 3                                                                                           |  |

(0E0000 to 0FFFFF). Default is zero.

### **Configuration Register 23**

| Bit | Function              | _ |

|-----|-----------------------|---|

| 7-5 | Unused                |   |

| 4   | Memory mapping enable |   |

| 3   | EMS enable            |   |

| 2   | Reserved              |   |

| 1,0 | ROM wait state select |   |

Bit 4 When set to 1, this bit enables the memory mapping feature. Default is zero.

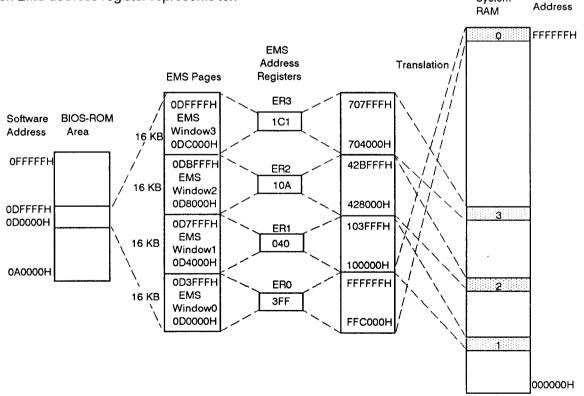

Bit 3 When set to 1, this bit enables the EMS feature. Default is zero.

Bits 1.0

These bits select the number of wait states that are inserted for all ROM read cycles. These bits default to the 3 wait state select.

| Bits | Select        |

|------|---------------|

| 1 0  |               |

| 0 0  | 1 wait state  |

| 0 1  | 2 wait states |

| 1 0  | 3 wait states |

#### **Configuration Registers 24-2B**

The ACC 2120 supports four EMS registers. Configuration register pairs 24 and 25, 26 and 27, 28 and 29, 2A and 2B, each constitute one EMS register. These pairs are defined as EMS registers 0 through 3. The contents of these pairs provide alternate address bits for A14-23 during EMS accesses. All EMS registers default to zero.

# EMS Register 0

**Configuration Register 24**

Microelectronics -

The 16 KByte EMS window for EMS register 0 is located at address range 0D0000 to 0D3FFFF.

| Bit | Definition |  |

|-----|------------|--|

| 7-5 | Unused     |  |

| 4   | ER0, A23   |  |

| 3   | ER0, A22   |  |

| 2   | ER0, A21   |  |

| 1   | ER0, A20   |  |

| 0   | ER0, A19   |  |

### **Configuration Register 25**

| Bit | Definition                            |  |

|-----|---------------------------------------|--|

| 7-5 | Unused                                |  |

| 4   | ER0, A18                              |  |

| 3   | ER0, A17                              |  |

| 2   | ER0, A16                              |  |

| 1   | ER0, A15                              |  |

| 0   | ER0, A14                              |  |

|     | · · · · · · · · · · · · · · · · · · · |  |

### EMS Register 1 Configuration Register 26

The 16 KByte EMS window for EMS register 1 is located at address range 0D4000 to 0D7FFF.

| Definition |                                                        |

|------------|--------------------------------------------------------|

| Unused     |                                                        |

| ER1, A23   |                                                        |

| ER1, A22   |                                                        |

| ER1, A21   |                                                        |

| ER1, A20   |                                                        |

| ER1, A19   |                                                        |

|            | Unused<br>ER1, A23<br>ER1, A22<br>ER1, A21<br>ER1, A20 |

### **Configuration Register 27**

| Definition |                                                        |

|------------|--------------------------------------------------------|

| Unused     |                                                        |

| ER1, A18   |                                                        |

| ER1, A17   |                                                        |

| ER1, A16   |                                                        |

| ER1, A15   |                                                        |

| ER1, A14   |                                                        |

|            | Unused<br>ER1, A18<br>ER1, A17<br>ER1, A16<br>ER1, A15 |

### EMS Register 2 Configuration Register 28

The 16 KByte EMS window for EMS register 2 is located at address range 0D8000 to 0DBFFF.

| Bit | Definition |  |

|-----|------------|--|

| 7-5 | Unused     |  |

| 4   | ER2, A23   |  |

| 3   | ER2, A22   |  |

| 2   | ER2, A21   |  |

| 1   | ER2, A20   |  |

| 0   | ER2, A19   |  |

### **Configuration Register 29**

| Bit | Definition |     |

|-----|------------|-----|

| 7-5 | Unused     |     |

| 4   | ER2, A18   |     |

| 3   | ER2, A17   |     |

| 2   | ER2, A16   |     |

| 1   | ER2, A15   | · · |

| 0   | ER2, A14   |     |

Microelectronics —

# EMS Register 3 Configuration Register 2A

The 16 KByte EMS window for EMS register 3 is located address range 0DC000 to 0DFFFF.

| Bit | Definition |  |

|-----|------------|--|

| 7-5 | Unused     |  |

| 4   | ER3, A23   |  |

| 3   | ER3, A22   |  |

| 2   | ER3, A21   |  |

| 1   | ER3, A20   |  |

| 0   | ER3, A19   |  |

### **Configuration Register 2B**

| Bit | Definition |  |

|-----|------------|--|

| 7-5 | Unused     |  |

| 4   | ER3, A18   |  |

| 3   | ER3, A17   |  |

| 2   | ER3, A16   |  |

| 1   | ER3, A15   |  |

| 0   | ER3, A14   |  |

### **Configuration Register 31**

| Bit | Function           |

|-----|--------------------|

| 7-2 | Unused             |

| 1   | Hot software reset |

| 0   | Enable gate A20    |

Bit 1 This bit triggers a CPU reset when set to 1.

Bit 0 This bit enables address A20 when set to 1.

# DRAM Configuration (including single 1M DRAM option)

The ACC 2120 has fourteen memory configuration options which use various sizes and amounts of DRAM to provide up to 16 MB of system board memory. Table 3 lists the memory options available.

Table 3 ACC 2120 Memory Options

| Memory<br>Configuration | Number of<br>Banks |      | Total<br>Memory |

|-------------------------|--------------------|------|-----------------|

| 0                       | 1                  | 256K | 640K            |

|                         | 1                  | 64K  |                 |

| 1                       | 1                  | 256K | 512K            |

| 2                       | 2                  | 256K | 1M              |

| 3                       | 4                  | 256K | 2M              |

| 4                       | 6                  | 256K | ЗМ              |

| 5                       | 8                  | 256K | 4M              |

| 6                       | 1/2                | 1M   | 1M              |

| 7                       | 1                  | 1M   | 2M              |

| 8                       | 2                  | 1M   | 4M              |

| 9                       | 4                  | 1 M  | 8M              |

| 10                      | 6                  | 1M   | 12M             |

| 11                      | 8                  | 1M   | 16M             |

| 12                      | 1                  | 4M   | 8M              |

| 13                      | 2                  | 4M   | 16M             |

Note that all DRAMs must be the same type (e.g., all 256K) on the system board except the 640K option which uses 256K and 64K DRAMs in two banks separately.

The single 1M module option (Option 6) is the only memory option that uses less than one bank of DRAM. This option is economical, using only one memory module. Performance is affected because eight bits must be converted to 16 bits (two memory cycles) for the CPU.

The ACC 2120 supports eight memory banks, each containing 18 bits of DRAM. These 18 bits comprise two 8-bit bytes, plus two parity bits, one for each byte.

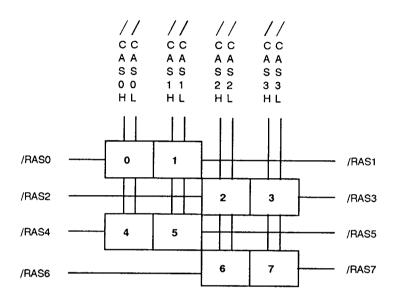

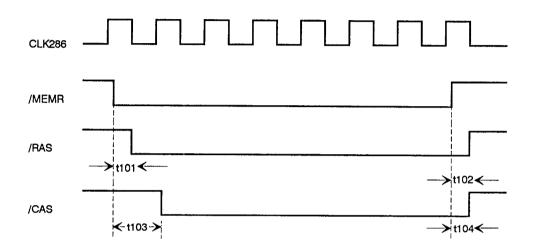

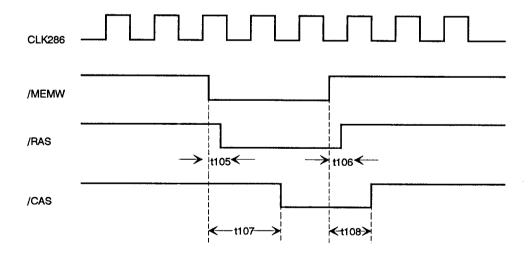

# Page Interleaved Memory Controller Page Interleaved Mode

The ACC 2120 implements a 4-way, 2-way, and 1-way page interleaved memory controller, providing optimum system performance for high speed CPUs. This option offers near Direct Access performance (approximately 0.4 to 0.7 wait state average), while operating with a slower and less expensive DRAM. The Page Interleaved Memory Controller operates on two principles: Page Mode Memory access, which is much faster than random access, and the sequential and localized patterns it follows.

The Page Interleaved Memory Controller organizes the memory array into interleaved pages by banks, operating up to four banks simultaneously in Page mode. Each bank of memory consists of 18 bits of DRAM (two 8-bit bytes plus two parity bits).