IBM Microelectronics

RGB561 PALETTE DAC Product Specification

# IBM Microelectronics

ii February 21, 1996

# IBM Microelectronics

# **Contents**

| ARCHITECTURE                                 |    |

|----------------------------------------------|----|

| Introduction                                 |    |

| Microprocessor Interface (MPI)               |    |

| Programming                                  |    |

| Address Index Register                       |    |

| Configuration Registers and Cursor Pixel Map |    |

| LUTs and WATs                                |    |

| Reserved Address Space                       |    |

| Look-Up Tables                               | •  |

| Color Look-Up Table (LUT)                    |    |

| Color LUT Addressing                         |    |

| Gamma Correction Tables                      |    |

| Cursor/Cross-Hair Look-Up Tables             |    |

| Cursor Pixel Map                             |    |

| Cursor Fixer Map                             |    |

| Window Attribute Tables (WATs)               | 4  |

| Segment Registers                            |    |

| deginent registers                           |    |

| Video                                        |    |

| Interlace support                            |    |

|                                              |    |

| Frame Buffer Interface                       | 6  |

| VRAM Interface                               |    |

| Pixel Interpretation and Bit Assignment      |    |

| Pixel Interleave                             |    |

| Maria Araba a Taba                           |    |

| Window Attribute Tables                      |    |

| Window IDs - Window Attribute Tables         |    |

| WAT Addressing                               |    |

| AUX_WAT Addressing                           |    |

| WAT Addressing Architecture                  |    |

| Pixel Formats                                | 10 |

| rixer rormats                                |    |

| Cursor/Cross-Hair Features                   | 22 |

| Cursor                                       |    |

| Cursor Location                              |    |

| Cursor Blinking                              |    |

| Cross-Hair                                   |    |

| Cross-Hair/Cursor Lock                       |    |

| Cross-Hair Location                          |    |

| Cross-Hair Scissor Clipping                  |    |

| Cross-Hair Window Clipping                   |    |

| Extended View Cross-Hair                     |    |

| Cursor / Cross-Hair Interaction              |    |

| Outdoi / Otdoo Hall Interaction              |    |

| Display Priority                             | 24 |

| Pixel Priority                               |    |

| Overlay Transparency                         |    |

| Chroma Key                                   |    |

|                                              |    |

|       | 4 6    | A .      |        |      |

|-------|--------|----------|--------|------|

| ILIN  | . /I I | \/licroo | IAAtra | nicc |

| יוכוו | vi i   | Microe   | にしいい   | ロルいつ |

| Synchronization                                                                     |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 2  |

|-------------------------------------------------------------------------------------|-----|------|-------|--------|---|-------|------|----|-------|------|---|------|------|

| Control Register                                                                    |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 2  |

|                                                                                     |     |      |       |        |   |       |      |    |       |      |   |      |      |

| Clocking                                                                            |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 20 |

| Pixel Clock                                                                         |     |      |       |        |   |       |      |    |       |      |   |      |      |

| Phase Locked Loop                                                                   |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 20 |

| External Pixel Clock                                                                |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 26 |

| Serial_Clock                                                                        |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 26 |

| Auxiliary Serial Clock                                                              |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 20 |

| Divided DOT Clock                                                                   |     |      |       |        |   |       |      |    |       |      |   |      |      |

|                                                                                     |     |      |       |        |   |       |      |    |       |      |   |      |      |

|                                                                                     |     |      |       |        |   |       |      |    |       | <br> |   | <br> |      |

| REGISTER ADDRESSES                                                                  |     |      |       |        |   |       |      |    |       |      |   |      |      |

| Register Address Table                                                              |     | <br> |       | <br>   | • | <br>  | <br> |    |       | <br> |   | <br> | . 2  |

|                                                                                     |     |      |       |        |   |       |      |    |       |      |   |      |      |

| REGISTER SUMMARIES                                                                  |     |      |       |        |   |       |      |    |       |      |   |      | 28   |

| X'0000 Revision Level Register (Read only)                                          |     |      |       |        |   |       |      |    |       |      |   |      |      |

| 7. 0000 Trovision Edvor Register (read only)                                        | , . | <br> | <br>• | <br>   | • | <br>• | <br> |    | <br>• | <br> | • | <br> |      |

| Configuration Registers                                                             |     |      |       |        |   |       |      |    |       |      |   |      | 2    |

| X'0001 Configuration Register 1 (CONF/1)                                            |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0002 Configuration Register 2 (CONF/2)                                            |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X '0002 Configuration Register 2 (CONF/2) X '0003 Configuration Register 3 (CONF/3) |     |      |       |        |   |       |      |    |       |      |   |      |      |

|                                                                                     |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0004 Configuration Register 4 (CONF/4)                                            |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0005 Interleave Control Register                                                  |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0006-0007 WAT Segment Registers                                                   |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0008-0009 AUX WAT Segment Registers                                               |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0010-0011 Chroma Key Registers                                                    |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 3  |

| X'0012-0013 Chroma Key Mask Registers                                               |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 34 |

| X'0020 SYNC Control Register                                                        |     |      |       |        |   |       |      |    |       |      |   |      |      |

|                                                                                     |     |      |       |        |   |       |      |    |       |      |   |      |      |

| PLL Programming                                                                     |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 30 |

| X'0021 PLL/VCO Divider Register                                                     |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0022 PLL Reference Register                                                       |     |      |       |        |   |       |      |    |       |      |   |      |      |

|                                                                                     |     |      |       |        |   |       |      |    |       |      |   |      |      |

| Cursor Registers                                                                    |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 3  |

| X'0030 Cursor Control Register                                                      |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0031 Cross-Hair Control Register                                                  |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0032-0033 Cursor Blink Registers                                                  |     |      |       |        |   |       |      |    |       |      |   |      |      |

|                                                                                     |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0034-0035 Cursor Hot Spot Location Regis<br>X'0036-0039 Cursor Location Registers |     |      |       |        |   |       |      |    |       |      |   |      |      |

|                                                                                     |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0040-0047 Cross-Hair Scissor Clipping Re                                          |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0048-004B Cross-Hair Location Registers                                           |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'004C-004E Cross-Hair Pattern Registers                                            |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'005F DAC Control Register                                                         |     | <br> | <br>  | <br>   |   | <br>  | <br> |    |       | <br> |   | <br> | . 4  |

|                                                                                     |     |      |       |        |   |       |      |    |       |      |   |      |      |

| Diagnostic Registers                                                                |     |      |       |        |   |       |      |    |       |      |   |      |      |

| TESTABILITY and DIAGNOSTICS                                                         |     |      |       |        |   |       |      |    |       |      |   |      |      |

| MISR Registers                                                                      |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 42 |

| X'0060-0063 MISR Signature Registers                                                |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0065 MISR Status                                                                  |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 42 |

| MISR Algorithm                                                                      |     |      |       |        |   |       |      |    |       |      |   |      |      |

| MISR Example                                                                        |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0050-0056 VRAM Bit Mask Registers                                                 |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0064 DAC Comparator                                                               |     |      |       |        |   |       |      |    |       |      |   |      |      |

| A 0004 DAG Comparator                                                               |     | <br> | <br>  | <br>٠. | • | <br>  | <br> |    | <br>• | <br> |   | <br> | . 4, |

| DDOTCLK Register                                                                    |     |      |       |        |   |       |      |    |       |      |   |      | 1    |

|                                                                                     |     |      |       |        |   |       |      |    |       |      |   |      |      |

| X'0082 Divided DOT Clock Control Register                                           | •   | <br> | <br>• | <br>٠. | • | <br>  | <br> | ٠. |       | <br> |   | <br> | . 4  |

| Curear Look He Table                                                                |     |      |       |        |   |       |      |    |       |      |   |      |      |

| Cursor Look-Up Table                                                                |     | <br> | <br>  | <br>   |   | <br>  | <br> |    | <br>  | <br> |   | <br> | . 45 |

iv February 21, 1996

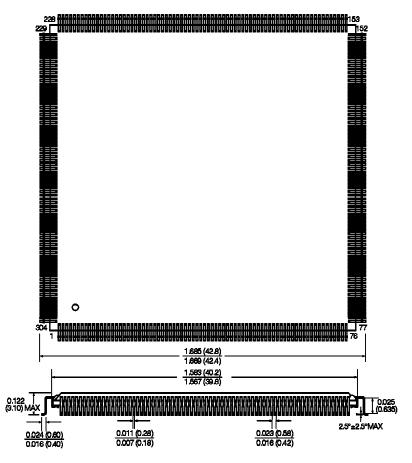

**PACKAGING**

Package Drawing - 304 C4FP

Appendix c. ERRATA

Palette Read-Back

Appendix a. APPLICATION NOTES

Quad Buffering of 8 bit Index Pixels

Multiple Frame Buffer Chroma Key

Appendix b. DOCUMENT REVISIONS

### **RGB561**

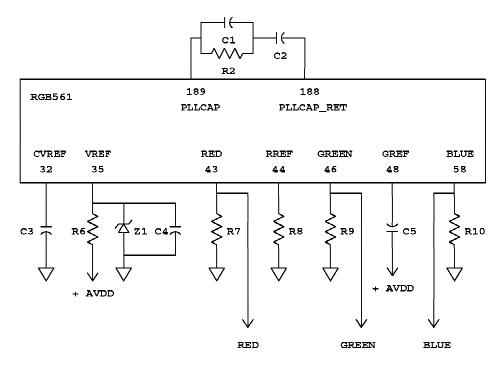

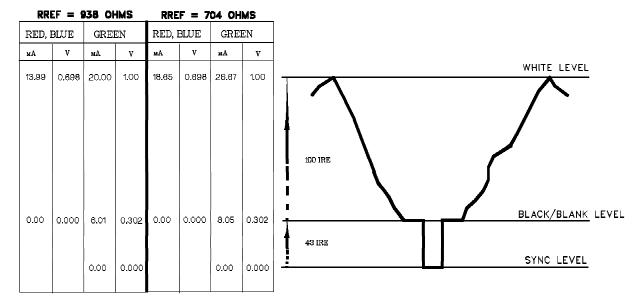

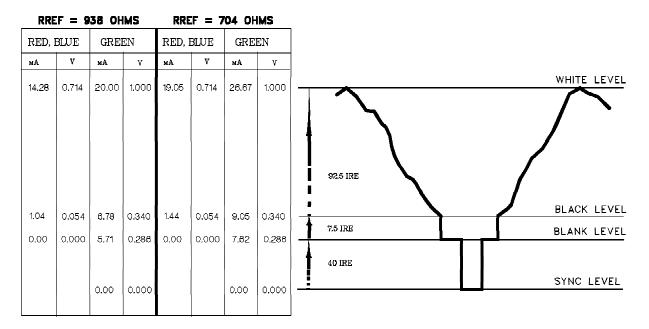

#### IBM Microelectronics X'0A10-0A1F Cursor/Cross-Hair Look-Up Tables **Window Attribute Tables** X'0E00-0E0F AUX FB WAT X'0F00-0F0F AUX\_OL\_WAT X'1000-10FF FB\_WAT X'1400-14FF OL\_WAT I/O SUMMARY 49 Signal Pins **EXTERNAL COMPONENTS** 52 **External Circuitry** Analog Voltages DAC Outputs PLL Components Signal Terminations Decoupling Circuit Schematic Component Values Performance Characteristics 54 ■DAC Output Levels **PIN LIST** Pin Assignments

# **IBM Microelectronics**

# **Figures**

| 1.  | WAI Addressing                            | 16 |

|-----|-------------------------------------------|----|

| 2.  | WAT Addressing: Common WID Mode           | 16 |

| 3.  | WAT Addressing: Split WID Mode            | 17 |

| 4.  | AUX_FB_WAT Addressing Alignment to FB_WAT | 18 |

| 5.  | Pixel Color Modes                         | 19 |

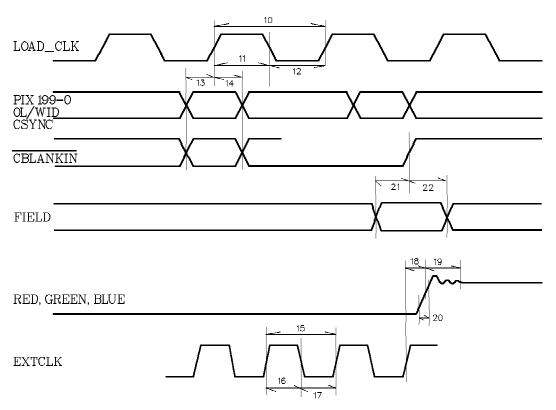

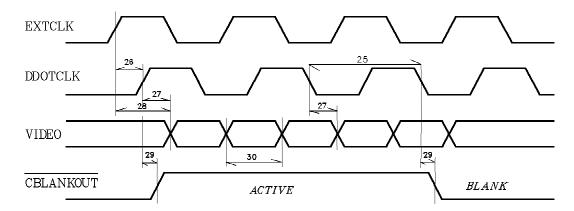

| 6.  | MPI Port Timings                          | 54 |

| 7.  | VRAM Pixel Port and Clock Timings         | 54 |

|     | VIDEO Timings                             |    |

| 9.  | Composite DAC Output (Setup=0 IRE)        | 58 |

| 10. | Composite DAC Output (Setup=7.5 IRE)      | 58 |

| 11. | Top View, heat sink not shown             | 63 |

|     |                                           |    |

vi February 21, 1996

# IBM Microelectronics

# **Tables**

| 1.  | Color Lut Address Generation                                 |

|-----|--------------------------------------------------------------|

| 2.  | Two cycle transfer: GAMMA entries                            |

| 3.  | 64x64 Cursor Pixel Screen Locations                          |

| 4.  | Cursor Pixels Mapped into 1Kx8 Memory                        |

| 5.  | Two cycle transfer: WAT entries                              |

| 6.  | Video Output Clocking                                        |

| 7.  | RGB561 VRAM to PIXEL CONFIGURATION SUMMARY                   |

| 8.  | RGB561 PIXEL TO VRAM CONFIGURATION SUMMARY                   |

| 9.  | RGB561 VRAM PIXEL BIT ASSIGNMENT 5:1 / 4:1 MUX Basic Mode    |

| 10. | RGB561 VRAM PIXEL BIT ASSIGNMENT 4:1 MUX Extended Mode       |

| 11. | RGB561 VRAM PIXEL BIT ASSIGNMENT 4:1 MUX Super Extended mode |

| 12. | RGB561 VRAM PIXEL BIT ASSIGNMENT 5:1 MUX, 30 bit/pixel Mode  |

| 13. | RGB561 VRAM PIXEL BIT ASSIGNMENT 4:1 MUX 30 bit/pixel Mode   |

| 14. | RGB561 VRAM PIXEL BIT ASSIGNMENT 8:1 MUX, Basic-A Mode       |

| 15. | RGB561 VRAM PIXEL BIT ASSIGNMENT 8:1 MUX, Basic-B Mode       |

| 16. | RGB561 Pixel Data Formats                                    |

| 17. | Overlay/Underlay Formats                                     |

| 18. | Color LUT Bypass Conversion Table                            |

| 19. | DTG Signal Summary                                           |

| 20. | Register Addresses                                           |

| 21. | MISR Register Bit Locations                                  |

| 22. | Cursor/Cross-hair look-up table entries                      |

| 23. | SIGNAL PINS                                                  |

| 24. | RGB561 Extended Pixel Data Formats                           |

|     |                                                              |

February 21, 1996 vii

IBM Microelectronics

viii February 21, 1996

### **IBM Microelectronics**

### Introduction

The RGB561 is designed to meet the large spectrum of graphics operations of high end workstations in the X Windows environment. It provides a high level of functional integration with flexibility to achieve a variety of color modes, window attributes, monitor support, and pixel performance ranges. It supports CRT displays as well as digital video data for external devices. The RGB561 can simultaneously display various visual formats with dynamic selection occurring on a pixel basis.

# **Microprocessor Interface (MPI)**

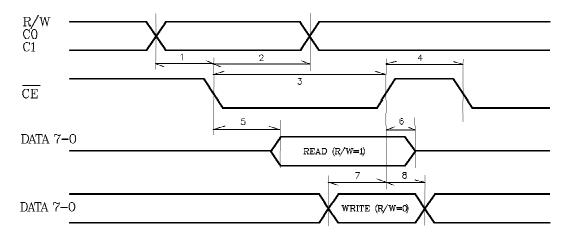

The 8 bit microprocessor interface, DATA<sub>7-0</sub>, is controlled by CO/C1/CE/RW signals, and is used to access all configuration and control registers, window attribute tables (WATs), cursor, gamma and palette look-up tables (LUTs), MISR and DAC compare registers. It is shared with the VIDEO<sub>11-0</sub> bus which supports digital data output for external applications. The control signal timings are shown in "■AC Characteristics" on page 54 and a list of the valid register addresses is summarized in Table 20 on page 27.

All registers are set to 0 by RESET with the exception of the Revision Level and reserved registers, the Color, Cursor and Gamma LUTs, the Cursor pixel map and the Window Attribute Tables, all of which must be loaded with the appropriate data through the MPI.

### **Programming**

#### **Address Index Register**

The RGB561 contains an internal 16 bit address register that is used as the pointer to all configuration registers, Look Up Tables (LUTs) and Window Attribute Tables (WATs). It is formed by the Address Index Low register and the Address Index High register.

The low order 8 bits of the address are contained in the Address Index Low register; they are stored by setting C1/C0=0/0 and writing the 8 bit value to the RGB561 Data bus. Loading the Address Index High register requires C1/C0=0/1 and a data write MPI cycle. To set an initial address to the register space the index register must be loaded in this *low/high* order to access look-up tables, WATs and the Cursor pixel map. Configuration registers do not have this low/high order requirement.

The address index register will auto increment to the next address after each read or write cycle to a configuration register or after the end of a multi-cycle LUT or WAT access. This feature can be disabled, if

desired, by forcing the msb of the address index high register to '1'. The address index register will not automatically skip unused or reserved address locations in the valid address space and requires another address load or multiple accesses to move through those address locations.

# Configuration Registers and Cursor Pixel Map

Configuration registers and cursor pixel map locations, pointed to by the Address Index register, are accessed with C1/C0=1/0. The address index register will auto increment to the next address after each read or write cycle.

#### **LUTs and WATs**

Look up tables (Palettes and Gamma Correction) and Window Attribute Tables, pointed to by the Address Index register, are accessed with C1/C0=1/1 denoting a multi-cycle access. The 10 bit *WATs and Gamma correction tables* are accessed from the 8 bit MPI bus in 2 cycles, and the *3-1Kx8 Color look-up tables* in 3 cycles, one each for red, green and blue data. If the address index register is accessed before completion of a multi-cycle access, the counter is reset and the operation is terminated.

The internal pixel clock (PIXCLK) must be active to access LUTs, WATs and cursor pixel map addresses. The PLL must be set up properly to generate the internal pixel clock or alternatively, the external pixel clock may be used. If an external pixel clock is used (EXTCLK/EXTCLK), the desired frequency range (DFR) must still be programmed in the *PLL/VCO Divider Register* to properly access LUT RAM locations.

#### Reserved Address Space

Writing to a reserved register address is ignored, reading from a reserved register address below X'1000 will return X'00 at the MPI. Reading reserved registers from address X'1000 to X'7FFF will tri-state the MPI DATA $_{7-0}$  outputs.

# IBM

#### **ARCHITECTURE**

### IBM Microelectronics

# **Look-Up Tables**

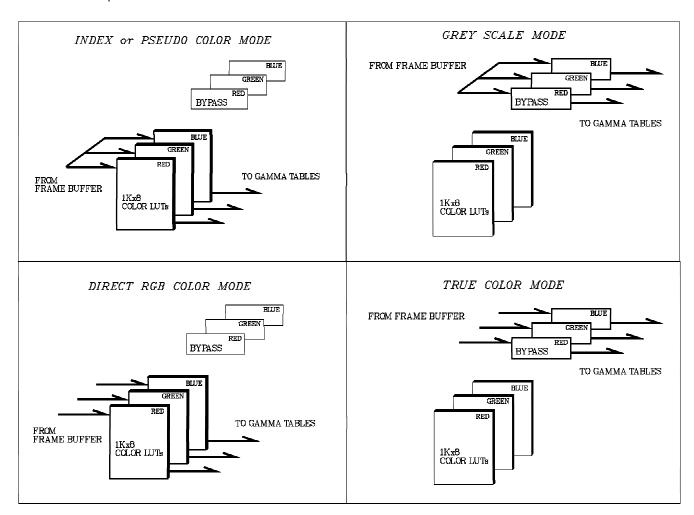

The RGB561 has three look-up tables:

Color LUTs Consist of 3 - 1K x 8 SRAMs, one

each for red, green and blue data. They are bypassed in grey scale and true color modes and are used to

address the Gamma LUTs.

Gamma LUTs Consist of 3 - 256x10 SRAMs, for

display color enhancement, and can also be bypassed. Their color output

data drives the DACs.

Cursor LUT Contains 12 - 24 bit RGB (8/8/8)

entries representing the primary and blink colors used to display the

cursor and cross-hair.

#### Color Look-Up Table (LUT)

The three independent 1Kx8 color palettes on the RGB561 yield an indirect color look-up capability of 16.7 million colors. The palette tables can also be bypassed in any true color mode. They can be read or written through the MPI at any time. Anti-sparkle circuitry will repeat the last displayed pixel color during MPI accesses, but in some instances screen artifacts may result.

Data transfer to or from the Color LUTs is a three cycle operation with 8 bits of red, green and blue data being transferred sequentially to or from the same address before the address index register increments.

#### **Color LUT Addressing**

The Color LUT can be partitioned by the system software into LUTs for each window on the screen with a minimum color depth of 64 entries. Window partitioning and bypass are controlled by the FB\_WAT and OL\_WAT data bits.

In 30 bits per pixel (bpp) mode, the full 10 bit LUT address is contained in the serialized data and no starting address modification takes place. To form a 10 bit Color LUT address for all other pixel types, the appropriate pixel or overlay input data from the serializer is combined with the Color LUT starting address taken from its respective FB\_WAT or OL\_WAT. The process is shown in Table 1. Pixel data used is shown as the left data byte of Table 18 on page 21. The relationship between VRAM input data and the pixel or overlay data used to access the LUTs is shown in Table 7 on page 7 and Figure 7 on page 54.

Table 18 on page 21 also shows the look-up table output in bypass mode for various pixel input data for each color mode.

| Table           | Table 1. Color LUT Address Generation |                 |                 |                 |                 |                 |                 |                 |                 |  |  |  |  |

|-----------------|---------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--|--|--|--|

| 9               | 8                                     | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |  |  |  |  |

| SA <sub>3</sub> | SA <sub>2</sub>                       | SA <sub>1</sub> | SA <sub>0</sub> | 0               | 0               | 0               | 0               | 0               | 0               |  |  |  |  |

| +               | <b>=</b>                              | AI <sub>7</sub> | AI <sub>6</sub> | AI <sub>5</sub> | AI <sub>4</sub> | AI <sub>3</sub> | Al <sub>2</sub> | AI <sub>1</sub> | AI <sub>0</sub> |  |  |  |  |

|                 |                                       |                 |                 |                 |                 |                 |                 |                 |                 |  |  |  |  |

| LA <sub>9</sub> | LA <sub>8</sub>                       | LA <sub>7</sub> | LA <sub>6</sub> | LA <sub>5</sub> | LA <sub>4</sub> | LA <sub>3</sub> | LA <sub>2</sub> | LA <sub>1</sub> | LA <sub>0</sub> |  |  |  |  |

$\emph{SA}$  Starting address from the window attribute table

AI Address input from Table 18 on page 21.

LA Resulting color look-up table address

### IBM Microelectronics

#### **Gamma Correction Tables**

The Gamma look-up or correction tables are used to enhance color precision and clarity for applications requiring exact replication of color data or to compensate for display differences. The 8 bit data from the color palette is used to access the corresponding 256x10 Gamma table. In bypass mode, the 10 bit output is linearized by shifting the 8 bit address input to the output MSBs and copying the 2 input MSBs to the 2 output LSBs. Gamma tables are always bypassed when cursor pixels are displayed.

Gamma tables may also be accessed through the MPI at any time, however, a read during active display time may result in visible screen artifacts. Loading the 10 bit color Gamma data entries requires a two cycle transfer before an address increment. Data fields on each access are shown in Table 2.

| Table          | Table 2. Two cycle transfer: GAMMA entries |                |                |                |                |                |                |                |                |  |  |  |

|----------------|--------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|--|--|

| 7              | 7 6 5 4 3 2 1 0 7 6                        |                |                |                |                |                |                |                |                |  |  |  |

| D <sub>9</sub> | D <sub>8</sub>                             | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |  |  |  |

|                | First Access 2ND                           |                |                |                |                |                |                |                |                |  |  |  |

#### Cursor/Cross-Hair Look-Up Tables

The cursor and cross-hair have separate primary and blink color look-up tables each containing 3-24 bit RGB data entries, the fourth value is transparency. LUT entries are shown in Table 22 on page 45.

#### **Cursor Pixel Map**

The 64 x 64 cursor is mapped into a 1K x 8 SRAM as indicated in Tables 3 and 4. Each 8 bit input to the cursor pixel map represents 4 pixel color values. The 2 bit per pixel data is used to access the Cursor LUT to select a primary or blink color based on the value in the *Cursor Control Register* (X'0030), BT.

| Table 3. 6  | 4x64 ( | Curso | Pixel | Scree  | en Loc | ation   | S      |        |        |         |

|-------------|--------|-------|-------|--------|--------|---------|--------|--------|--------|---------|

| Addr        |        | 0     | 1     | 2      | 3      |         | 60     | 61     | 62     | 63      |

| X ' 2000    | 0      | 0     | 1     | 2      | 3      |         | 60     | 61     | 62     | 63      |

| X ' 2010    | 1      | 64    | 65    | 66     | 67     |         | 124    | 125    | 126    | 127     |

| X ' 2020    | 2      | 128   | 129   | 130    | 131    |         | 188    | 189    | 190    | 191     |

| X ' 2030    | 3      | 192   | 193   | 194    | 195    |         | 252    | 253    | 254    | 255     |

| :           | :      | :     | :     | ÷      | :      | :       | :      | ÷      | :      | :       |

| X ' 23C0    | 60     | 3840  | 3841  | 3842   | 3843   |         | 3900   | 3901   | 3902   | 3903    |

| X ' 23D0    | 61     | 3904  | 3905  | 3906   | 3907   |         | 3964   | 3965   | 3966   | 3967    |

| X ' 23E0    | 62     | 3968  | 3969  | 3970   | 3971   |         | 4028   | 4029   | 4030   | 4031    |

| X ' 23F0    | 63     | 4032  | 4033  | 4034   | 4035   |         | 4092   | 4093   | 4094   | 4095    |

| Addr in the |        |       | 14200 | lacati | an af  | the fir | at 1 a | امامين | Dogiot | a = b:4 |

Addr is the register address location of the first 4 pixels Register bit placement is described in Table 4.

| Table 4. C | Table 4. Cursor Pixels Mapped into 1Kx8 Memory |                          |       |       |       |       |         |       |  |  |  |  |  |

|------------|------------------------------------------------|--------------------------|-------|-------|-------|-------|---------|-------|--|--|--|--|--|

| ADDRESS    |                                                | DATA <sub>7-0</sub> Bits |       |       |       |       |         |       |  |  |  |  |  |

|            | 7                                              | 6                        | 5     | 4     | 3     | 2     | 1       | 0     |  |  |  |  |  |

| X ' 2000   | Pixe                                           | el 0                     | Pixe  | el 1  | Pixe  | el 2  | Pix     | el 3  |  |  |  |  |  |

| X 2000     | Bit 1                                          | Bit 0                    | Bit 1 | Bit 0 | Bit 1 | Bit 0 | Bit 1   | Bit 0 |  |  |  |  |  |

| X ' 2001   | Pixel 4 Pixel 5 Pixel 6                        |                          |       |       |       | el 6  | Pixel 7 |       |  |  |  |  |  |

| X 2001     | Bit 1                                          | Bit 0                    | Bit 1 | Bit 0 | Bit 1 | Bit 0 | Bit 1   | Bit 0 |  |  |  |  |  |

|            |                                                |                          |       | :     |       |       |         |       |  |  |  |  |  |

| X'23FE     | Pixel                                          | 4088                     | Pixel | 4089  | Pixel | 4090  | Pixel   | 4091  |  |  |  |  |  |

| X 231 L    | Bit 1                                          | Bit 0                    | Bit 1 | Bit 0 | Bit 1 | Bit 0 | Bit 1   | Bit 0 |  |  |  |  |  |

| X'23FF     | Pixel                                          | 4092                     | Pixel | 4093  | Pixel | 4094  | Pixel   | 4095  |  |  |  |  |  |

| A 23FF     | Bit 1                                          | Bit 0                    | Bit 1 | Bit 0 | Bit 1 | Bit 0 | Bit 1   | Bit 0 |  |  |  |  |  |

# IBM

#### **ARCHITECTURE**

### IBM Microelectronics

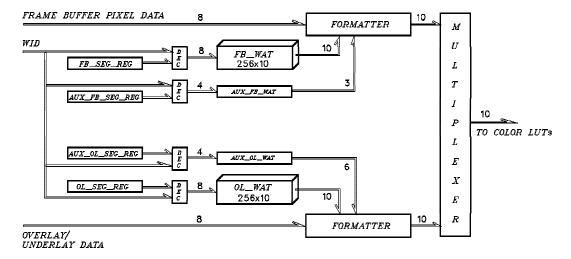

# **Window Attribute Tables (WATs)**

The Window Attribute Tables (WAT) contain pixel frame buffer and overlay window display information that varies on a pixel basis. Two - 256x10 bit WATs are available, one contains the frame buffer pixel data attributes (FB\_WAT), the other stores the overlay data attributes (OL\_WAT).

Data for the 10 bit frame buffer and overlay window attribute tables must be loaded through the MPI in two cycles, similar to that used for the gamma correction tables. Data fields on each access are shown in Table 5.

| Table          | Table 5. Two cycle transfer: WAT entries |                |                |                |                |                |                |                |                |  |  |  |

|----------------|------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|--|--|

| 7              | 7 6 5 4 3 2 1 0 7 6                      |                |                |                |                |                |                |                |                |  |  |  |

| D <sub>9</sub> | D <sub>8</sub>                           | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |  |  |  |

|                | First Access 2ND                         |                |                |                |                |                |                |                |                |  |  |  |

The definition of data stored in the WAT entries is found in "Window Attribute Tables" on page 46.

Two - 16 entry 8 bit auxiliary window attribute tables (AUX\_FB\_WAT and AUX\_OL\_WAT) contain data

characteristics for a group of windows. They are accessed through the MPI in a single cycle.

#### **Segment Registers**

Window ID (WID) bits are used to form the address into the WATs. When fewer than 8 bits of WID data are available for WAT access, the appropriate **FB\_WAT or OL\_WAT Segment Registers** are used to provide additional, most significant address bits.

The AUX\_FB\_WAT and AUX\_OL\_WAT Segment Registers perform the same function and augment the number of WID bits used to access the AUX\_FB\_WAT and AUX\_OL\_WAT when less than 4 bits are available. Only the least significant 4 bits of these registers are used to generate WAT addresses. The segment registers are loaded from the MPI in one cycle and are located from address X'0006-0009.

Refer to "WAT Addressing" on page 15 for a detailed description of WAT addressing and Figure 1 on page 16 for a block diagram of the registers associated with the window attribute tables.

#### **ARCHITECTURE**

### IBM Microelectronics

#### **Video**

The 12 bit digital  $VIDEO_{11-0}$  output of the RGB561 is used to transfer pixel data from the DAC inputs for external use (i.e. NTSC or LCD display subsystems).

The data clocked out of the VIDEO port represents the 8 MSB DAC inputs for each color. The bus is synchronized to either EXTCLK or DDOTCLK with the timings shown in Figure 8 on page 55. The 24 bit pixel DAC data is 'sliced' to provide 12 bit bus transfers. The 4 most significant bits of RGB data are provided on the rising pixel clock edge (EXTCLK or DDOTCLK) and the 4 least significant bits on the falling edge (Table 6).

The video options are controlled by bits in the *CONF/3* register. When video mode is enabled (VID), RGB data is output on the VIDEO bus during periods when blanking is inactive.

Since Video output bits 0-7 make use of the MPI data bus, it is imperative that all devices sharing the MPI data bus be tristated during active video. Active video time can be determined by checking the CBLANKOUT output of the RGB561 The MPI is available for register access only during blanking periods when the video mode is enabled.

| Table 6. Video Output Clocking                                      |                                                               |  |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| REF/EXTCLK 11 10 9 8 7 6 5 4 3 2 1 0                                |                                                               |  |  |  |  |  |  |  |  |  |  |

| RISING                                                              | G RED <sub>7-4</sub> GREEN <sub>7-4</sub> BLUE <sub>7-4</sub> |  |  |  |  |  |  |  |  |  |  |

| FALLING RED <sub>3-0</sub> GREEN <sub>3-0</sub> BLUE <sub>3-0</sub> |                                                               |  |  |  |  |  |  |  |  |  |  |

Because some monitors may be unable to sync in video mode, the DACs may be set to blank level by the Screen Control bit (CONF/2) or powered off completely using the **DAC Control Register**, DAC bit (X'005F).

#### Interlace support

The RGB561 supports interlaced operation. If interlaced operation is enabled, interleave and cursor data are controlled by the *FIELD* input. The FIELD polarity is also controlled by the CONF/3 register.

The **FIELD** signal is used in video mode to specify whether an even (0) or odd (1) scan line is displayed. For proper interleave and cursor data generation, pixel data must be presented to the RGB561 consistent with the interlace requirements.

# IBM

#### **ARCHITECTURE**

### IBM Microelectronics

### Frame Buffer Interface

The 200 bit VRAM input data can be configured into any of the operating modes listed below, using the serializer configuration registers. The modes determine the number of bits (pixel size) allocated for use by frame buffer and overlay layers, and the maximum number of WID bit planes configurable.

| MODE           | MUX<br>Ratio | FB/OL Size    | Max WID |

|----------------|--------------|---------------|---------|

| Basic          | 5:1          | 32 bits total | 8 bits  |

| Basic          | 4:1          | 32 bits total | 8 bits  |

| Extended       | 4:1          | 40 bits total | 8 bits  |

| Super Extended | 4:1          | 48 bits total | 2 bits  |

| 30 bpp         | 5:1          | 30 / 8 bits   | 2 bits  |

| Basic-B        | 8:1          | 20 bits total | 4 bits  |

| 30 bpp         | 4:1          | 30 / 16 bits  | 2 bits  |

| Basic-A        | 8:1          | 24 bits total | 8 bits  |

The **OVLY** field (CONF/1) specifies the number of FB/OL bits allocated for overlay; the remaining bits are allocated to the frame buffer. Pixel format and buffer

select options, specified in WAT, should not exceed the pixel size boundary. Alternatively, the boundary between frame buffer and overlay can vary on a per pixel basis, with the size of frame buffer and overlay pixels determined by the WAT. Care should be taken not to overlap the frame buffer and overlay for the given mode of operation.

The *LWID* bits (CONF/1) determine the number of WID planes configured. It should not exceed the limit set by the serializer configuration. The selected number of LSB will address the WAT, the remaining bits are ignored.

When loading the configuration registers it is important to specify a valid set of parameters consistent with those available or results will be unpredictable.

The serializer configuration summary and VRAM data allocations are shown in Table 7 on page 7.

# IBM Microelectronics

## **VRAM Interface**

| VRAM           | В                                      | ASIC                                   | EXTENDED              | SUPER_EXT                                                     | RGB                                                                                  | 30 bpp                                   | BASIC                 |

|----------------|----------------------------------------|----------------------------------------|-----------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------|-----------------------|

| DATA           | 5:1 MUX                                | 4:1 MUX                                | 4:1 MUX               | 4:1 MUX                                                       | 5:1 MUX                                                                              | 4:1 MUX                                  | 8:1 MUX               |

| 0-3            | PA <sub>0-3</sub>                      | PA <sub>0-3</sub>                      | PA <sub>0-3</sub>     | PA <sub>0-3</sub>                                             | PA <sub>0-3</sub>                                                                    | PA <sub>0-3</sub>                        | PA <sub>0-3</sub>     |

| 4-7            | PA <sub>4-7</sub>                      | PA <sub>4-7</sub>                      | I PA₁-7               | PA <sub>4-7</sub>                                             | PA <sub>4-7</sub>                                                                    | PA <sub>4-7</sub>                        | PA <sub>4-7</sub>     |

| 8-11           | PA <sub>8-11</sub>                     | PA <sub>8-11</sub>                     | PA <sub>8-11</sub>    | PA <sub>8-11</sub>                                            | PA <sub>8-11</sub>                                                                   | PA <sub>8-11</sub>                       | PA <sub>8-11</sub>    |

| 12-15          | PA <sub>12-15</sub>                    | PA <sub>12-15</sub>                    | PA <sub>12-15</sub>   | PA <sub>12-15</sub>                                           | PA <sub>12-15</sub>                                                                  | PA <sub>12-15</sub>                      | PA <sub>12-15</sub>   |

| 16-19          | PA <sub>16-19</sub>                    | PA <sub>16-19</sub>                    | PA <sub>16-19</sub>   | PA <sub>16-19</sub>                                           | PA <sub>16-19</sub>                                                                  | PA <sub>16-19</sub>                      | PB <sub>0-3</sub>     |

| 20-23          | PA <sub>20-23</sub>                    | PA <sub>20-23</sub>                    | PA <sub>20-23</sub>   | PA <sub>20-23</sub>                                           | PA <sub>20-23</sub>                                                                  | PA <sub>20-23</sub>                      | PB <sub>4-7</sub>     |

| 20-23<br>24-27 | PB <sub>0-3</sub>                      | 1 A20-23                               | PB <sub>0-3</sub>     | PB <sub>0-3</sub>                                             | PB <sub>0-3</sub>                                                                    | 1 A20-23                                 | DC -7                 |

|                | FD <sub>0-3</sub>                      | PB <sub>0-3</sub>                      | FD <sub>0-3</sub>     | FD <sub>0-3</sub>                                             | FD <sub>0-3</sub>                                                                    | PB <sub>0-3</sub>                        | PC <sub>0-3</sub>     |

| 28-31          | PB <sub>4-7</sub>                      | PB <sub>4-7</sub>                      | PB <sub>4-7</sub>     | PB <sub>4-7</sub>                                             | PB <sub>4-7</sub>                                                                    | PB <sub>4-7</sub>                        | PC <sub>4-7</sub>     |

| 32-35          | PB <sub>8-11</sub>                     | PB <sub>8-11</sub>                     | PB <sub>8-11</sub>    | PB <sub>8-11</sub>                                            | PB <sub>8-11</sub>                                                                   | PB <sub>8-11</sub>                       | PC <sub>8-11</sub>    |

| 36-39          | PB <sub>12-15</sub>                    | I PB <sub>12.45</sub>                  | I PB45.45             | PB <sub>12-15</sub>                                           | I PB40.45                                                                            | PB <sub>12-15</sub>                      | I PC12.15             |

| 40-43          | PB <sub>16-10</sub>                    | PB <sub>16-10</sub>                    | PB <sub>16-19</sub>   | PB <sub>16-10</sub>                                           | PB <sub>16-10</sub>                                                                  | PB <sub>16-19</sub>                      | PD <sub>0-3</sub>     |

| 44-47          | PB <sub>20-23</sub>                    | I PB <sub>20-23</sub>                  | I PB <sub>20-23</sub> | I PB <sub>20-23</sub>                                         | PB <sub>20-23</sub>                                                                  | I PB20-23                                | I PD₁-7               |

| 48-51          | I PCn_2                                | I PCn-2                                | I PCn_2               | I PCn.2                                                       | I PCn-2                                                                              | PC <sub>0-3</sub>                        | I PE <sub>0-3</sub>   |

| 52-55          | l PC₁₋ <del>7</del>                    | I PC <sub>4.7</sub>                    | I PC₄₋ <del>7</del>   | I PC <sub>4</sub> -                                           | I PC <sub>4</sub> -                                                                  | I PC <sub>4.7</sub>                      | l PE₁₋ <del>z</del>   |

| 56-59          | I PC <sub>9-11</sub>                   | PC <sub>9-11</sub>                     | l PC <sub>9-11</sub>  | I PC <sub>0.44</sub>                                          | I PC <sub>9-11</sub>                                                                 | PC 11                                    | PE <sub>9-11</sub>    |

| 60-63          | PC <sub>12-15</sub>                    | PC <sub>12-15</sub>                    | PC <sub>12-15</sub>   | PC <sub>12-15</sub>                                           | PC <sub>12-15</sub>                                                                  | PC <sub>12-15</sub>                      | PE <sub>12-15</sub>   |

| 64-67          | PC <sub>16-19</sub>                    | PC <sub>16-19</sub>                    | PC <sub>16-19</sub>   | PC <sub>16-19</sub>                                           | PC <sub>16-19</sub>                                                                  | PC <sub>16-19</sub>                      | PF <sub>0-3</sub>     |

| 68-71          | PC <sub>20-23</sub>                    | PC <sub>20-23</sub>                    | PC <sub>20-23</sub>   | PC <sub>20-23</sub>                                           | PC <sub>20-23</sub>                                                                  | PC <sub>20-23</sub>                      | PF <sub>4-7</sub>     |

| 72-75          | PD <sub>0-3</sub>                      | PD <sub>0-3</sub>                      | PD <sub>0-3</sub>     | PD <sub>0-3</sub>                                             | PD <sub>0-3</sub>                                                                    | PD <sub>0-3</sub>                        | PG <sub>0-3</sub>     |

| 76-79          | FD <sub>0-3</sub>                      | PD <sub>0-3</sub>                      | FD <sub>0-3</sub>     | PD <sub>0-3</sub>                                             | DD-3                                                                                 | PD <sub>0-3</sub>                        | FG <sub>0-3</sub>     |

|                | PD <sub>4-7</sub>                      | PD <sub>4-7</sub>                      | PD <sub>4-7</sub>     | PD <sub>4-7</sub>                                             | PD <sub>4-7</sub>                                                                    | PD <sub>4-7</sub>                        | PG <sub>4-7</sub>     |

| 80-83          | PD <sub>8-11</sub>                     | PD <sub>8-11</sub>                     | PD <sub>8-11</sub>    | PD <sub>8-11</sub>                                            | PD <sub>8-11</sub>                                                                   | PD <sub>8-11</sub>                       | PG <sub>8-11</sub>    |

| 84-87          | PD <sub>12-15</sub>                    | PD <sub>12-15</sub>                    | PD <sub>12-15</sub>   | PD <sub>12-15</sub>                                           | PD <sub>12-15</sub>                                                                  | PD <sub>12-15</sub>                      | PG <sub>12-15</sub>   |

| 88-91          | PD <sub>16-19</sub>                    | PD <sub>16-19</sub>                    | PD <sub>16-19</sub>   | PD <sub>16-19</sub>                                           | PD <sub>16-19</sub>                                                                  | I PD <sub>16-10</sub>                    | I PH <sub>0-3</sub>   |

| 92-95          | PD <sub>20-23</sub>                    | PD <sub>20-23</sub>                    | PD <sub>20-23</sub>   | PD <sub>20-23</sub>                                           | PD <sub>20-23</sub>                                                                  | PD <sub>20-23</sub>                      | PH <sub>4-7</sub>     |

| 96-99          | PE <sub>0-3</sub>                      | I —                                    | I PA <sub>24-27</sub> | PA <sub>24-27</sub>                                           | PE <sub>∩-3</sub>                                                                    | I PA24.27                                | PB <sub>9-11</sub>    |

| 00-103         | PE <sub>4-7</sub>                      | _                                      | I PA <sub>29-21</sub> | I PA <sub>29-21</sub>                                         | I PE <sub>4.7</sub>                                                                  | I PA <sub>29-21</sub>                    | I PB12.15             |

| 04-107         | PE <sub>8-11</sub>                     | <b> </b> -                             | PB <sub>24-27</sub>   | PB <sub>24-27</sub>                                           | PE <sub>8-11</sub>                                                                   | PB <sub>24-27</sub>                      | PD <sub>8-11</sub>    |

| 08-111         | PE <sub>12-15</sub>                    | _                                      | I PB <sub>28-31</sub> | PB <sub>28-31</sub>                                           | PE <sub>12-15</sub>                                                                  | PB <sub>28-31</sub>                      | PD <sub>12-15</sub>   |

| 12-115         | PE <sub>16-19</sub>                    | l _                                    | PC <sub>24-27</sub>   | PC <sub>24-27</sub>                                           | PE <sub>16-19</sub>                                                                  | PC <sub>24-27</sub>                      | PF <sub>8-11</sub>    |

| 16-119         | PE <sub>20-23</sub>                    | l _                                    | PC <sub>28-31</sub>   | PC <sub>28-31</sub>                                           | PE <sub>20-23</sub>                                                                  | PC <sub>28-31</sub>                      | PF <sub>12-15</sub>   |

| 20-123         | PA <sub>24-27</sub>                    | PA <sub>24-27</sub>                    | PA <sub>32-35</sub>   | PA <sub>40-43</sub>                                           | PA <sub>24-27</sub>                                                                  | PA <sub>32-35</sub>                      | PA <sub>16-19</sub>   |

| 24-127         | PA <sub>28-31</sub>                    | PA <sub>28-31</sub>                    | PA <sub>36-39</sub>   | PA <sub>44-47</sub>                                           | PA <sub>28-31</sub>                                                                  | PA <sub>36-39</sub>                      | PA <sub>20-23</sub>   |

| 28-131         | 1 A28-31                               | 1 A28-31                               | 1 A36-39              | DD                                                            | 1 A28-31                                                                             | PB <sub>32-35</sub>                      | DC 720-23             |

| 32-135         | PB <sub>24-27</sub>                    | PB <sub>24-27</sub>                    | PB <sub>32-35</sub>   | PB <sub>40-43</sub>                                           | PB <sub>24-27</sub>                                                                  | DD 32-35                                 | PC <sub>16-19</sub>   |

|                | PB <sub>28-31</sub>                    | PB <sub>28-31</sub>                    | PB <sub>36-39</sub>   | PB <sub>44-47</sub>                                           | PB <sub>28-31</sub>                                                                  | PB <sub>36-39</sub>                      | PC <sub>20-23</sub>   |

| 36-139         | PC <sub>24-27</sub>                    | PC <sub>24-27</sub>                    | PC <sub>32-35</sub>   | PC <sub>40-43</sub>                                           | PC <sub>24-27</sub>                                                                  | PC <sub>32-35</sub>                      | PE <sub>16-19</sub>   |

| 40-143         | PC <sub>28-31</sub>                    | PC <sub>28-31</sub>                    | PC <sub>36-39</sub>   | PC <sub>44-47</sub>                                           | PC <sub>28-31</sub>                                                                  | PC <sub>36-39</sub>                      | PE <sub>20-23</sub>   |

| 44-147         | PD <sub>24-27</sub>                    | PD <sub>24-27</sub>                    | PD <sub>32-35</sub>   | PD <sub>40-43</sub>                                           | PD <sub>24-27</sub>                                                                  | PD <sub>32-35</sub>                      | PG <sub>16-19</sub>   |

| 48-151         | PD <sub>28-31</sub>                    | PD <sub>28-31</sub>                    | I PD <sub>36-30</sub> | I PD <sub>44-47</sub>                                         | PD <sub>28-31</sub>                                                                  | I PD <sub>36-30</sub>                    | I PG <sub>20-23</sub> |

| 52-155         | PE <sub>24-27</sub>                    | -                                      | PD <sub>24-27</sub>   | PD <sub>24-27</sub>                                           | I PF                                                                                 | PD <sub>24-27</sub>                      | PH <sub>8-11</sub>    |

| 56-159         | PE <sub>29-21</sub>                    | -                                      | I PD20 24             | PD <sub>28-31</sub>                                           | PE <sub>28-31</sub>                                                                  | PD <sub>28-31</sub>                      | PH <sub>12-15</sub>   |

| 60-163         | WA <sub>0-3</sub>                      | WA <sub>0-3</sub>                      | WA <sub>0-3</sub>     | PD <sub>28-31</sub><br>WA <sub>0-1</sub> /PA <sub>34-35</sub> | PE <sub>28-31</sub><br>WA <sub>0-1</sub> /PA <sub>32-33</sub><br>PA <sub>34-37</sub> | WA <sub>0-1</sub> /PA <sub>40-41</sub>   | I PB <sub>16-10</sub> |

| 64-167         | WA <sub>4-7</sub>                      | I WA <sub>4</sub> -                    | I WA <sub>4-7</sub>   | PA <sub>36-30</sub>                                           |                                                                                      | PA <sub>42-45</sub>                      | I PB20-23             |

| 68-171         | WB <sub>0-3</sub>                      | I WBo a                                | I WB <sub>0-2</sub>   | I WB <sub>0-1</sub> /PB <sub>24-25</sub>                      | WB <sub>0-1</sub> /PB <sub>32-33</sub>                                               | I WB <sub>0-1</sub> /PB <sub>40-41</sub> | I PD16-10             |

| 72-175         | l WB <sub>4</sub> <del>7</del>         | I WB                                   | WB <sub>4-7</sub>     | PB <sub>36-39</sub>                                           | PB <sub>34-37</sub>                                                                  | PB <sub>42-45</sub>                      | PD <sub>20-23</sub>   |

| 76-179         | WC <sub>0-3</sub>                      | I WC <sub>2</sub> 2                    | WC <sub>0-3</sub>     | WC <sub>0-1</sub> /PC <sub>34-35</sub>                        | I WC <sub>0.4</sub> /PC <sub>22.22</sub>                                             | I WCo 1/PC 40 44                         | I PF40.40             |

| 80-183         | WC <sub>4-7</sub>                      | I WC <sub>4</sub> -                    | WC <sub>4</sub> 7     | PC20 20                                                       | PC <sub>34-37</sub>                                                                  | PC <sub>42-45</sub>                      | PF <sub>20-23</sub>   |

| 84-187         | WD <sub>0-3</sub>                      | WD <sub>0-3</sub>                      | WD <sub>0-3</sub>     | PC <sub>36-39</sub><br>WD <sub>0-1</sub> /PD <sub>34-35</sub> | WD <sub>0-1</sub> /PD <sub>32-33</sub>                                               | WD <sub>0-1</sub> /PD <sub>40-41</sub>   | PH <sub>16-19</sub>   |

| 88-191         | WD <sub>0-3</sub><br>WD <sub>4-7</sub> | WD <sub>0-3</sub><br>WD <sub>4-7</sub> | WD-3                  | DD 34-35                                                      | DD 32-33                                                                             | DD                                       | ' '16-19              |

| 92-195         | 1 VV D4-7                              |                                        | WD <sub>4-7</sub>     | PD <sub>36-39</sub>                                           | PD <sub>34-37</sub>                                                                  | PD <sub>42-45</sub>                      | PH <sub>20-23</sub>   |

|                | WE <sub>0-3</sub>                      | -                                      | -                     | PA <sub>32-33</sub> /PB <sub>32-33</sub>                      | WE <sub>0-1</sub> /PE <sub>32-33</sub>                                               | -                                        | SWID <sub>0-3</sub>   |

| 96-199         | WE <sub>4-7</sub>                      | -                                      | -                     | PC <sub>32-33</sub> /PD <sub>32-33</sub>                      | PE <sub>34-37</sub>                                                                  | -                                        | SWID <sub>4-7</sub>   |

# IBM Microelectronics

| PIXEL                                  | BAS     | SIC     | EXTENDED | SUPER_EXT       | RGB 3       | 0 bpp       | BASIC            |

|----------------------------------------|---------|---------|----------|-----------------|-------------|-------------|------------------|

| DATA                                   | 5:1 MUX | 4:1 MUX | 4:1 MUX  | 4:1 MUX         | 5:1 MUX     | 4:1 MUX     | 8:1 MUX          |

| A <sub>0-15</sub>                      | 0-15    | 0-15    | 0-15     | 0-15            | 0-15        | 0-15        | 0-15             |

| A <sub>16-23</sub>                     | 16-23   | 16-23   | 16-23    | 16-23           | 16-23       | 16-23       | 120-127          |

| 116-23                                 | 120-127 | 120-127 | 96-103   | 96-103          | 120-127     | 96-103      |                  |

| PA <sub>24-31</sub>                    | 120-121 |         |          |                 |             |             | _                |

| PA <sub>32-35</sub>                    | _       | _       | 120-123  | 192,193,162,163 | 162-165     | 120-123     | _                |

| PA <sub>36-39</sub>                    | _       | _       | 124-127  | 164-167         | 166,167,-,- | 124-127     | _                |

| PA <sub>40-47</sub>                    | _       | _       | _        | 120-127         | _           | 162-167,-,- | _                |

| PB <sub>0-7</sub>                      | 24-31   | 24-31   | 24-31    | 24-31           | 24-31       | 24-31       | 16-23            |

| PB <sub>8-15</sub>                     | 32-39   | 32-39   | 32-39    | 32-39           | 32-39       | 32-39       | 96-103           |

| B-15                                   | 40-47   | 40-47   | 40-47    | 40-47           | 40-47       | 40-47       | 160-167          |

| PB <sub>16-23</sub>                    |         |         |          |                 |             |             |                  |

| PB <sub>24-31</sub>                    | 128-135 | 128-135 | 104-111  | 104-111         | 128-135     | 104-111     | _                |

| PB <sub>32-35</sub>                    | _       | _       | 128-131  | 194,195,170,171 | 170-173     | 128-131     | _                |

| PB <sub>36-39</sub>                    | _       | _       | 132-135  | 172-175         | 174,175,-,- | 132-135     | _                |

| PB <sub>40-47</sub>                    | _       | _       | _        | 128-135         | -           | 170-175,-,- | _                |

| PC <sub>0-15</sub>                     | 48-63   | 48-63   | 48-63    | 48-63           | 48-63       | 48-63       | 24-39            |

| 20-15                                  | 64-71   | 64-71   | 64-71    | 64-71           | 64-71       | 64-71       | 128-135          |

| PC <sub>16-23</sub>                    | -       |         |          |                 | -           | -           |                  |

| PC <sub>24-31</sub>                    | 136-143 | 136-143 | 112-119  | 112-119         | 136-143     | 112-119     | _                |

| PC <sub>32-35</sub>                    | _       | _       | 136-139  | 196,197,178,179 | 178-181     | 136-139     | _                |

| C <sub>36-39</sub>                     | _       | _       | 140-143  | 180-183         | 182,183,-,- | 140-143     | _                |

| C <sub>40-47</sub>                     | _       | _       | _        | 136-143         |             | 178-183,-,- | _                |

| PD <sub>0-7</sub>                      | 72-79   | 72-79   | 72-79    | 72-79           | 72-79       | 72-79       | 40-47            |

| ≥0-7                                   | 80-87   | 80-87   | 80-87    | 80-87           | 80-87       | 80-87       | 104-111          |

| PD <sub>8-15</sub>                     |         |         |          |                 |             |             |                  |

| PD <sub>16-23</sub>                    | 88-95   | 88-95   | 88-95    | 88-95           | 88-95       | 88-95       | 168-175          |

| PD <sub>24-31</sub>                    | 144-151 | 144-151 | 152-159  | 152-159         | 144-151     | 152-159     | _                |

| PD <sub>32-35</sub>                    | _       | _       | 144-147  | 198,199,186,187 | 186-189     | 144-147     | _                |

| PD <sub>36-39</sub>                    | _       | _       | 148-151  | 188-191         | 190,191,-,- | 148-151     | _                |

| PD <sub>40-47</sub>                    | _       | _       | _        | 144-151         |             | 186-191,-,- | _                |

| PE <sub>0-15</sub>                     | 96-111  | _       | _        |                 | 96-111      | _           | 48-63            |

|                                        |         | _       | _        |                 |             | _           |                  |

| PE <sub>16-23</sub>                    | 112-119 | _       | _        |                 | 112-119     | _           | 136-143          |

| PE <sub>24-31</sub>                    | 152-159 | _       | _        |                 | 152-159     | _           | _                |

| PE <sub>32-37</sub>                    | _       | _       | _        | _               | 194-199     | _           | _                |

| PF <sub>0-7</sub>                      | _       | _       | _        | _               | _           | _           | 64-71            |

| PF <sub>8-15</sub>                     | _       | _       | _        |                 | _           | _           | 112-119          |

| PF <sub>16-23</sub>                    | _       | _       | _        | _               | _           | _           | 176-183          |

|                                        |         |         |          |                 |             |             |                  |

| PG <sub>0-15</sub>                     | _       | _       | _        | _               | _           | _           | 72-87<br>144-151 |

| PG <sub>16-23</sub>                    | _       | _       | _        |                 | _           | _           | 144-151          |

| PH <sub>0-7</sub>                      | _       | _       | _        | _               | _           | _           | 88-95            |

| PH <sub>8-15</sub>                     | _       | _       | _        | -               | _           | _           | 152-159          |

| PH <sub>16-23</sub>                    | -       | _       | _        | -               | -           | _           | 184-191          |

| WA <sub>0-3</sub>                      | 160-163 | 160-163 | 160-163  | 160,161,-,-     | 160,161,-,- | 160,161,-,- | _                |

| VA <sub>0-3</sub><br>VA <sub>4-7</sub> | 164-167 | 164-167 | 164-167  |                 | —           | —           | _                |

|                                        |         |         |          |                 |             |             |                  |

| WB <sub>0-3</sub>                      | 168-171 | 168-171 | 168-171  | 168,169,-,-     | 168,169,-,- | 168,169,-,- | _                |

| NB <sub>4-7</sub>                      | 172-175 | 172-175 | 172-175  |                 | -           | _           | _                |

| WC <sub>0-3</sub>                      | 176-179 | 176-179 | 176-179  | 176,177,-,-     | 176,177,-,- | 176,177,-,- | _                |

|                                        |         |         |          | 170,177,-,-     | 170,177,-,- | 170,177,-,- | _                |

| NC <sub>4-7</sub>                      | 180-183 | 180-183 | 180-183  | _               | -           | _           | _                |

| ND <sub>0-3</sub>                      | 184-187 | 184-187 | 184-187  | 184,185,-,-     | 184,185,-,- | 184,185,-,- | _                |

| ND <sub>4-7</sub>                      | 188-191 | 188-191 | 188-191  |                 |             |             | _                |

|                                        |         |         |          |                 |             |             |                  |

| NE <sub>0-3</sub>                      | 192-195 | _       | -        | -               | 192,193,-,- | _           | _                |

| WE <sub>4-7</sub>                      | 196-199 | _       | _        | -               | -           | _           | _                |

| SWID <sub>0-7</sub>                    | _       | _       | _        | _               | _           | _           | 192-199          |

| ٠,                                     |         |         | 1        | COMMON INTERLEA |             |             |                  |

# IBM Microelectronics

# Pixel Interpretation and Bit Assignment

| Table 9. RGB561 VRAM PIXEL B      | IT ASSIGNMENT 5:1 / 4                   | :1 MUX Bas              | sic Mode                |                         |                         |                               |                         |                                                                                                             |             |  |  |  |

|-----------------------------------|-----------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

|                                   |                                         |                         |                         | BIT ASSI                | GNMENT                  |                               |                         |                                                                                                             |             |  |  |  |

|                                   | W W W W W W W W W 0 0 0 0 0 0 0 0 0 0 0 | P P P P 3 3 2 2 1 0 9 8 | P P P P 2 2 2 2 7 6 5 4 | P P P P 2 2 2 2 3 2 1 0 | P P P P 1 1 1 1 9 8 7 6 | P P P P<br>1 1 1 1<br>5 4 3 2 | P P P P 1 1 0 0 1 0 9 8 | P     P     P     P     P     P       0     0     0     0     0     0       7     6     5     4     3     2 | P P 0 0 1 0 |  |  |  |

| FB WAT Pixel Format               |                                         |                         |                         |                         |                         |                               |                         |                                                                                                             |             |  |  |  |

| 8 bit RGB or INDEX                |                                         |                         |                         |                         |                         | 8                             | В                       | <b>8</b> <sub>A</sub>                                                                                       |             |  |  |  |

| 12 bit RGB                        |                                         |                         |                         |                         | 12 <sub>B</sub>         |                               |                         | 12 <sub>A</sub>                                                                                             |             |  |  |  |

| 16 bit RGB                        |                                         |                         | 16                      | В                       |                         |                               | 16                      | A                                                                                                           |             |  |  |  |

| 24 bit RGB                        |                                         | 24                      |                         |                         |                         |                               |                         |                                                                                                             |             |  |  |  |

| OL WAT Pixel Format               |                                         |                         |                         |                         |                         |                               |                         |                                                                                                             |             |  |  |  |

| 8 bit RGB or Index                |                                         | 0                       | A                       | 0                       | В                       |                               |                         |                                                                                                             |             |  |  |  |

| 6/2 bit OL/UL Index               |                                         | O <sub>A</sub>          | U <sub>A</sub>          | OB                      | <b>U</b> B              |                               |                         |                                                                                                             |             |  |  |  |

| 4/4 bit OL/UL Index               |                                         | O <sub>A</sub>          | U <sub>A</sub>          | OB                      | <b>U</b> B              |                               |                         |                                                                                                             |             |  |  |  |

| 4 bit OL Index                    |                                         | OB                      | O <sub>A</sub>          |                         |                         |                               |                         |                                                                                                             |             |  |  |  |

| WID bits                          |                                         |                         |                         |                         |                         |                               |                         |                                                                                                             |             |  |  |  |

| 8 bit WID                         | w                                       |                         |                         |                         |                         |                               |                         |                                                                                                             |             |  |  |  |

| Note: Subscripts A and B refer to | Buffer A and Buffer B re                | spectively for          | or double bu            | ffer modes.             |                         |                               |                         |                                                                                                             |             |  |  |  |

| KEL BIT ASSIGNMEN                       | IT 4:1 MU                       | X Extende                               | d Mode                                  |                                       |                                                |                                                       |                                                       |                                                       |

|-----------------------------------------|---------------------------------|-----------------------------------------|-----------------------------------------|---------------------------------------|------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

|                                         |                                 |                                         |                                         | BIT ASS                               | SIGNMENT                                       |                                                       |                                                       |                                                       |

| W W W W W W W W W 7 0 0 0 0 0 0 0 0 0 0 | P P P P 3 3 3 3 9 8 7 6         | P P P P 3 3 3 3 5 4 3 2                 | P P P P 3 3 2 2 1 0 9 8                 | P P P 1 2 2 2 2 7 6 5 4               | P P P P P P P P P P P P P P P P P P P          | P P P P P 1 1 1 1 1 5 4 3 2                           | P P P F<br>1 1 0 0<br>1 0 9 8                         | P P P P P P P P P P F 0 0 0 0 0 0 0 0 0               |

|                                         |                                 |                                         |                                         |                                       |                                                |                                                       |                                                       |                                                       |

|                                         |                                 |                                         |                                         |                                       |                                                | 8                                                     | В                                                     | 8 <sub>A</sub>                                        |

|                                         |                                 |                                         |                                         |                                       | 12 <sub>B</sub>                                |                                                       |                                                       | 12 <sub>A</sub>                                       |

|                                         |                                 |                                         |                                         |                                       | <b>6</b> <sub>B</sub>                          |                                                       | 1                                                     | <b>6</b> <sub>A</sub>                                 |