SPWS035 - JUNE 1997

- Glueless Interface Between the Peripheral Component Interconnect (PCI) Bus and the TI380C2x<sup>†</sup> and TI380C3x<sup>†</sup> Generation of Processors

- Compliant With PCI Specification, Revision 2.0<sup>‡</sup>§

- Allows Use of Existing TI2000 Drivers

- Includes TI2000 Interface Configuration Register

- Supports Bus Master Operations for High Performance

- Provides 32-Bit Address-Data Path

- Implements Address/Data Parity Checking

- Includes Internal Error Checking for Illegal Bus Operations

- Supports Direct Memory Access (DMA) Bursts With 64-Byte FIFO

- Supports EPROM Interface for Remote Program Load (RPL) Operation

- Supports Inter-Integrated Circuit (I<sup>2</sup>C) Interface for Optional Serial EEPROM for Configuration Information

- Allows Burned-In Address (BIA) to be Implemented in Configuration EEPROM

- Includes NAND Tree Structure to Allow for In-Circuit Connectivity Testing

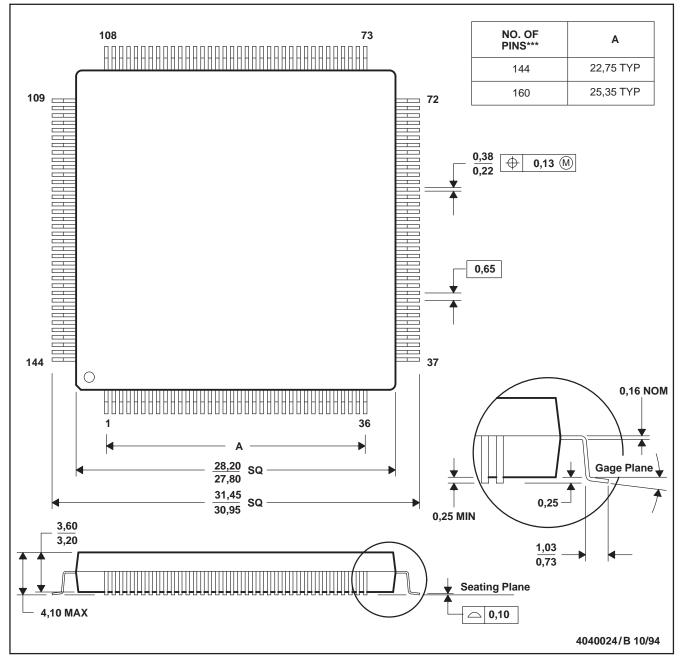

- 144-Pin JEDEC Plastic Quad Flat Package (PCM Suffix)

- Operating Temperature Range 0°C to 70°C

## description

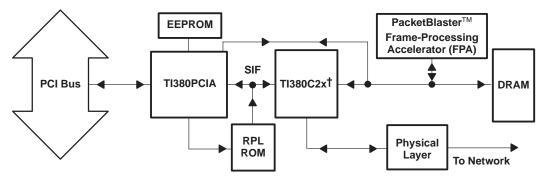

The TI380PCIA provides a glueless interface between a TI380C2x<sup>+</sup> commprocessor and the PCI bus (see Figure 1). The TI380PCIA transfers information/data between the PCI bus and the TI380C2x<sup>+</sup> system interface (SIF) using any of these three methods:

- Direct memory access (DMA)

- Direct input/output (DIO)

- Pseudo-direct memory access (PDMA)

DMA (or PDMA) transfers all data between host memory (by way of the PCI local bus) and TI380C2x<sup> $\dagger$ </sup> local memory. DIO accesses are typically used to load software into TI380C2x<sup> $\dagger$ </sup> local memory and for initializing the TI380C2x<sup> $\dagger$ </sup>.

The TI380PCIA conforms to the PCI standards found in "PCI Local Bus Specification," Revision 2.0.‡§

The TI380PCIA is available in a 144-pin JEDEC plastic quad flat package (PCM suffix) and is rated from 0°C to 70°C. It is a drop-in replacement for the TI380PCI.

Figure 1. TI380PCIA Applications Diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

- <sup>†</sup>TI380C3x devices can be used with TI380PCIA in the same way as TI380C2x devices.

- <sup>‡</sup> The "PCI Local Bus Specification", Revision 2.0, and the TI380C2x or TI380C3x series of data sheets (e.g., literature number SPWS012) should be used as references to this document.

- § Exceptions to electrical timing parameters specified in PCI Specification Revision 2.0 are described in Note 8 and Note 10 of the timing requirements section of this document.

PacketBlaster and Commprocessor are trademarks of Texas Instruments Incorporated.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

**DVANCE INFORMATION**

SPWS035 - JUNE 1997

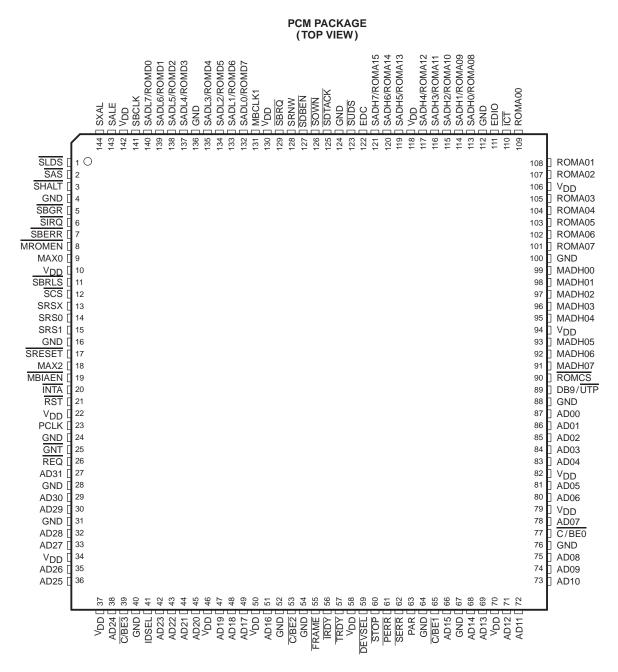

#### pin assignments

The pin assignments for the TI380PCIA (144-pin plastic quad flat package) are shown below.

NOTE: Pin 1 is positioned at the upper left corner.

## block diagram

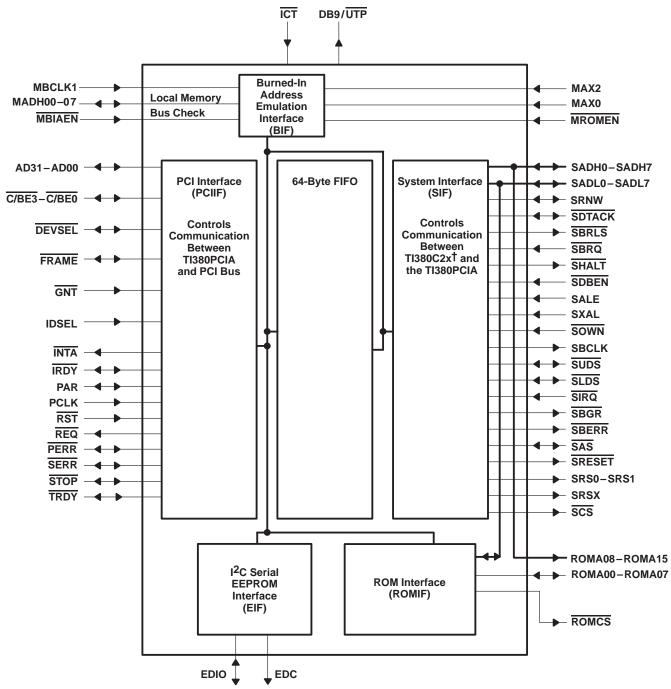

TI380PCIA can connect to up to four devices in a system: the PCI bus, the SIF bus, an optional serial EEPROM, and an optional boot ROM. The major blocks of the TI380PCIA include the PCI Interface (PCIIF), SIF, and ROM Interface (ROMIF) as shown in Figure 2.

Figure 2. TI380PCIA Block Diagram

SPWS035 - JUNE 1997

| Terminal Functions                                                           |                                                                                                 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TERMINA<br>NAME                                                              | IL<br>NO.                                                                                       | 1/o† | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| DB9/UTP                                                                      | 89                                                                                              | 0    | Connector. The value on DB9/UTP indicates the type of connector in use. Upon reset, the DB9/UTP value is 0.<br>1 = D-Shell (DB9)<br>0 = UTP/10BaseT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| GND                                                                          | 4<br>16<br>24<br>28<br>31<br>40<br>52<br>54<br>64<br>67<br>76<br>88<br>100<br>112<br>124<br>136 | I    | Ground. These pins must be attached to the common system ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ग्टन                                                                         | 110                                                                                             | i    | $\overline{\text{ICT}}$ supports in-circuit tests. $\overline{\text{ICT}}$ must be pulled high for normal operation of the TI380PCIA.<br>When pulled along with $\overline{\text{RST}}$ to a steady low state, all bidirectional signals in the TI380PCIA are configured as inputs, and all output pins of the TI380PCIA are in 3-state mode.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ROMA07<br>ROMA06<br>ROMA05<br>ROMA04<br>ROMA03<br>ROMA02<br>ROMA01<br>ROMA00 | 101<br>102<br>103<br>104<br>105<br>107<br>108<br>109                                            | I/O  | ROM address. ROMA07–ROMA00 form the least significant eight bits of the address for the RPL ROM. The most significant bits (MSBs) of the ROM address are multiplexed onto the SADHx lines.<br>When RST is driven high, the value on ROMA07–ROMA00 is latched into the board configuration register in the TI380PCIA configuration space. The value on ROMA07–ROMA00 can be provided by pullup and pulldown resistors that do not affect operation after reset. This feature allows designers to support jumpers or board stuffing options that can be sensed by software that reads the board configuration register. If pullup and pulldown resistors are not used, the contents of the board configuration register are undefined after reset. |  |  |  |

| ROMCS                                                                        | 90                                                                                              | 0    | ROMCS enables the outputs of the ROM when the ROM has been accessed. ROMCS-enable allows the data lines from the ROM to be driven.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

$\dagger I = in, O = out$

<sup>‡</sup> The TI380PCIA SIF pin names correspond to a subset of the system interface pins on a TI380C2x<sup>§</sup>. See the TI380C2x<sup>§</sup> data sheets for more information on individual pins. Like-named pins on the TI380PCIA and TI380C2x§ system interfaces are intended to be connected to each other.

§ TI380C3x devices can be used with TI380PCIA in the same way as TI380C2x devices.

¶ Typical bit-ordering for Intel<sup>™</sup> and Motorola<sup>™</sup> processor buses # The signal connecting this pin to the TI380C2x<sup>§</sup> also should be connected to a 4.7-kΩ pullup resistor.

|| The TI380PCIA BIF pin names correspond to a subset of the local memory bus interface pins on a TI380C2x§. Like-named pins on the two devices are intended to be connected to each other. Consult the TI380C2x<sup>§</sup> data sheets for more information on individual pins.

NOTE 1: The TI380PCIA allows driver software to set SBCLK output to a steady high state. This signal is driven to a steady high state during power-down operations.

Intel is a trademark of Intel Incorporated. Motorola is a trademark of Motorola, Inc.

SPWS035 - JUNE 1997

| TERMINAL                                                                                                                     |                                                                                            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                                                                                                         | NO.                                                                                        | l/ot     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| V <sub>DD</sub>                                                                                                              | 10<br>22<br>34<br>37<br>46<br>50<br>58<br>70<br>79<br>82<br>94<br>106<br>118<br>130<br>142 | I        | 5-V supply. These pins must be attached to the common system power supply plane.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                                                                                                              |                                                                                            | <u> </u> | I<br>SYSTEM INTERFACE (SIF) <sup>‡</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| SADH0/ROMA08<br>SADH1/ROMA09<br>SADH2/ROMA10<br>SADH3/ROMA11<br>SADH4/ROMA12<br>SADH5/ROMA13<br>SADH6/ROMA14<br>SADH7/ROMA15 | 113<br>114<br>115<br>116<br>117<br>119<br>120<br>121                                       | I/O      | System address/data bus—high byte. These lines make up the most significant byte (MSByte) of each TI380C2x <sup>§</sup> address word (32-bit address bus) and data word (16-bit data bus). The most significant bit (MSB) is SADH0, and the least significant bit (LSB) is SADH7.<br>Address-multiplexing bits 31–24 and bits 15–8¶<br>Data-multiplexing bits 15–8¶<br>During accesses to the ROM address space from the PCI bus, these lines provide the eight most significant address bits to the ROM. |  |  |  |

| SADL0/ROMD7<br>SADL1/ROMD6<br>SADL2/ROMD5<br>SADL3/ROMD4<br>SADL4/ROMD3<br>SADL5/ROMD2<br>SADL6/ROMD1<br>SADL7/ROMD0         | 132<br>133<br>134<br>135<br>137<br>138<br>139<br>140                                       | I/O      | System address / data bus — low byte. These lines make up the least significant byte (LSByte) of each address word (32-bit address bus) and data word (16-bit data bus). The MSB is SADL0, and the LSB is SADL7. These address lines also make up the ROM address.<br>Address-multiplexing bits 23–16 and bits 7–0¶<br>Data-multiplexing bits 7–0¶<br>During accesses to the ROM address space from the PCI bus, these lines transfer data from the ROM to the TI380PCIA.                                 |  |  |  |

| SALE                                                                                                                         | 143                                                                                        | I        | System-address latch-enable. SALE is the enable pulse used to latch the 16 LSBs of the address externally from the SADH0-SADH7 and SADL0-SADL7 buses at the start of the DMA cycle.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| SAS                                                                                                                          | 2                                                                                          | 1/0      | System-memory address strobe. SAS is an active-low address strobe that is an output during DIO and<br>an input during DMA. <sup>#</sup><br>H = Address not valid<br>L = Address is valid and a transfer operation is in progress                                                                                                                                                                                                                                                                          |  |  |  |

| SBCLK                                                                                                                        | 141                                                                                        | 0        | SIF bus clock. The TI380C2x $\ensuremath{\$}$ requires SBCLK to synchronize its bus timings for all DMA transfers (see Note 1).                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

**Terminal Functions (Continued)**

$\dagger I = in, O = out$

<sup>‡</sup> The TI380PCIA SIF pin names correspond to a subset of the system interface pins on a TI380C2x<sup>§</sup>. See the TI380C2x<sup>§</sup> data sheets for more information on individual pins. Like-named pins on the TI380PCIA and TI380C2x<sup>§</sup> system interfaces are intended to be connected to each other.

§ TI380C3x devices can be used with TI380PCIA in the same way as TI380C2x devices.

¶ Typical bit-ordering for Intel<sup>™</sup> and Motorola<sup>™</sup> processor buses

<sup>#</sup> The signal connecting this pin to the TI380C2x§ also should be connected to a 4.7-k $\Omega$  pullup resistor.

The TI380PCIA BIF pin names correspond to a subset of the local memory bus interface pins on a TI380C2x§. Like-named pins on the two devices are intended to be connected to each other. Consult the TI380C2x§ data sheets for more information on individual pins.

## **Terminal Functions (Continued)**

| TERMINAL<br>NAME                                | NO. | I/OT DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-------------------------------------------------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SYSTEM INTERFACE (SIF) <sup>‡</sup> (CONTINUED) |     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| SBERR                                           | 7   | 0                | Bus error. SBERR corresponds to the bus error signal of the 68000 microprocessor. SBERR is driven low during a DMA cycle to indicate to the TI380C2x <sup>§</sup> that the cycle must be terminated. See Section 3.4.5.3 of the <i>TMS380 Second-Generation Token Ring User's Guide</i> (SPWU005) for more information.                                                                                                                                                                                                       |  |  |  |

| SBGR                                            | 5   | ο                | System-bus grant. SBGR serves as an active-low bus grant, as defined in the standard 68000 interface.<br>H = System bus not granted<br>L = System bus granted                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| SBRLS                                           | 11  | 0                | <ul> <li>SIF bus release. SBRLS indicates to the TI380C2x<sup>§</sup> that a higher-priority device requires the SIF bus. The value on SBRLS is ignored by the TI380C2x<sup>§</sup> when DMA is not performed.</li> <li>H = The TI380C2x<sup>§</sup> can hold onto the system bus.</li> <li>L = The TI380C2x<sup>§</sup> should release the system bus upon completion of current DMA cycle. If the DMA transfer is not yet complete, the SIF rearbitrates for the SIF bus.</li> </ul>                                        |  |  |  |

| SBRQ                                            | 129 | I                | System-bus request. SBRQ is used to request control of the system bus in preparation for a DMA transfer. SBRQ is internally synchronized to SBCLK.<br>H = System bus not requested<br>L = System bus requested                                                                                                                                                                                                                                                                                                                |  |  |  |

| SCS                                             | 12  | 0                | System chip select. SCS activates the system interface of the TI380C2x§ for a DIO read or write.<br>H = Not selected<br>L = Selected                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| SDBEN                                           | 127 | I                | System data-bus enable. SDBEN causes the TI380PCIA to allow its external data buffers to begin driving data. SDBEN is accepted during both DIO and DMA.<br>H = Keep external data buffers in high-impedance state<br>L = Cause external data buffers to begin driving data                                                                                                                                                                                                                                                    |  |  |  |

| SDTACK                                          | 125 | I/O              | System data-transfer acknowledge. The purpose of SDTACK is to indicate to the bus master that a data transfer is complete. SDTACK is internally synchronized to SBCLK by the TI380C2x <sup>§</sup> . During DMA cycles, it is asserted before the falling edge of SBCLK in state T2 by the TI380PCIA to prevent a wait state. SDTACK is an input when the TI380C2x <sup>§</sup> is selected for DIO, and an output otherwise. <sup>#</sup><br>H = System bus NOT ready<br>L = Data transfer is complete; system bus is ready. |  |  |  |

| SHALT                                           | 3   | ο                | System halt/bus error retry. If SHALT is asserted along with bus error (SBERR), the adapter retries the last DMA cycle. This is the rerun operation as defined in the 68000 specification. See Section 3.4.5.3 of the <i>TMS380 Second - Generation Token Ring User's Guide</i> (SPWU005) for more information.                                                                                                                                                                                                               |  |  |  |

| SIRQ                                            | 6   | I                | System interrupt request. TI380C2x <sup>§</sup> drives SIRQ to signal an interrupt request to the host processor.<br>H = No interrupt request<br>L = Interrupt request by TI380C2x <sup>§</sup>                                                                                                                                                                                                                                                                                                                               |  |  |  |

$\dagger I = in, O = out$

<sup>‡</sup> The TI380PCIA SIF pin names correspond to a subset of the system interface pins on a TI380C2x§. See the TI380C2x§ data sheets for more information on individual pins. Like-named pins on the TI380PCIA and TI380C2x§ system interfaces are intended to be connected to each other.

$\$  TI380C3x devices can be used with TI380PCIA in the same way as TI380C2x devices.

¶ Typical bit-ordering for Intel<sup>™</sup> and Motorola<sup>™</sup> processor buses

<sup>#</sup> The signal connecting this pin to the TI380C2x§ also should be connected to a 4.7-k $\Omega$  pullup resistor.

The TI380PCIA BIF pin names correspond to a subset of the local memory bus interface pins on a TI380C2x<sup>§</sup>. Like-named pins on the two devices are intended to be connected to each other. Consult the TI380C2x<sup>§</sup> data sheets for more information on individual pins.

## **Terminal Functions (Continued)**

| TERMINAL<br>NAME                                | NO.            | ı/ot | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|-------------------------------------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SYSTEM INTERFACE (SIF) <sup>‡</sup> (CONTINUED) |                |      |                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| SLDS                                            | 1              | I/O  | Lower data strobe. SLDS is an output during DIO and an input during DMA. SLDS serves as the active-low lower data strobe. <sup>#</sup><br>H = Not valid data on SADL0-SADL7 lines<br>L = Valid data on SADL0-SADL7 lines                                                                                                                                                   |  |  |  |  |

| SOWN                                            | 126            | I    | <ul> <li>IF bus owned. SOWN signals the TI380PCIA SIF logic to indicate that the TI380C2x<sup>§</sup> has control of the SIF bus.</li> <li>TI380PCIA does not have control of the SIF bus.</li> <li>TI380PCIA has control of the SIF bus.</li> </ul>                                                                                                                       |  |  |  |  |

| SRESET                                          | 17             | 0    | System reset. SRESET is sent to initialize the TI380C2x <sup>§</sup> . It is set low whenever RST goes low or by<br>a configuration write to the MISCCTRL register.<br>H = No system reset<br>L = System reset                                                                                                                                                             |  |  |  |  |

| SRNW                                            | 128            | I/O  | System read not write. SRNW serves as a control signal to indicate a read or write cycle.<br>H = Read Cycle<br>L = Write Cycle                                                                                                                                                                                                                                             |  |  |  |  |

| SRSX<br>SRS0<br>SRS1                            | 13<br>14<br>15 | 0    | System register select. These outputs are sent to select the word or byte to be transferred during a system DIO access. The most significant bit is SRSX and the least significant bit is SRS1.          MSB       LSB         Registers selected       SRSX       SRS0                                                                                                    |  |  |  |  |

| SUDS                                            | 123            | I/O  | Upper data strobe. SUDS serves as the active-low upper data strobe. SUDS is an output during DI<br>and an input during DMA. <sup>#</sup><br>H = Not valid data on SADH0-SADH7 lines<br>L = Valid data on SADH0-SADH7 lines                                                                                                                                                 |  |  |  |  |

| SXAL                                            | 144            | I    | System extended address latch. SXAL provides the enable pulse that externally latches the most ignificant 16 bits of the 32-bit system address during DMA. SXAL is activated by the TI380C2x\$ prior to the first cycle of each block DMA transfer, and thereafter as necessary (whenever an increment of the DMA address counter causes a carryout of the lower 16 bits). |  |  |  |  |

$\dagger I = in, O = out$

<sup>‡</sup> The TI380PCIA SIF pin names correspond to a subset of the system interface pins on a TI380C2x<sup>§</sup>. See the TI380C2x<sup>§</sup> data sheets for more information on individual pins. Like-named pins on the TI380PCIA and TI380C2x<sup>§</sup> system interfaces are intended to be connected to each other.

$\$  TI380C3x devices can be used with TI380PCIA in the same way as TI380C2x devices.

¶ Typical bit-ordering for Intel<sup>™</sup> and Motorola<sup>™</sup> processor buses

<sup>#</sup> The signal connecting this pin to the TI380C2x§ also should be connected to a 4.7-k $\Omega$  pullup resistor.

I The TI380PCIA BIF pin names correspond to a subset of the local memory bus interface pins on a TI380C2x§. Like-named pins on the two devices are intended to be connected to each other. Consult the TI380C2x§ data sheets for more information on individual pins.

| Ierminal Functions (Continued)                                               |                                              |             |                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|------------------------------------------------------------------------------|----------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TERMINAL<br>NAME NO.                                                         |                                              | <i>v</i> ot | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                                              | BURNED-IN ADDRESS EMULATION INTERFACE (BIF)  |             |                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| MBCLK1                                                                       | 131                                          | 1           | Local memory bus clock 1.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| MADH00<br>MADH01<br>MADH02<br>MADH03<br>MADH04<br>MADH05<br>MADH06<br>MADH07 | 99<br>98<br>97<br>96<br>95<br>93<br>92<br>91 | I/O         | Local memory address, data, and status bus — high byte. For the first quarter of the local memory cyo<br>MADH00–MADH07 monitor address bits AX4 and A0 to A6; for the second quarter, they monitor sta<br>bits, and for the third and fourth quarters, they carry data bits 0 to 7. The most significant bit is MADH<br>and the least significant bit is MADH07. |  |  |  |  |

| MBIAEN                                                                       | 19                                           | I           | Burned-in address enable. MBIAEN enables the output of data on the MADHxx lines during BI/ accesses.                                                                                                                                                                                                                                                             |  |  |  |  |

| MAX2                                                                         | 18                                           | I           | Local memory extended address bit. For the first quarter of a local memory cycle MAX2 monitors AX2 For quarters two through four, MAX2 monitors A14.                                                                                                                                                                                                             |  |  |  |  |

| MAX0                                                                         | 9                                            | I           | ocal memory extended address bit. For the first quarter of a local memory cycle MAX0 monitors AX0. For quarters two through four, MAX0 monitors A12.                                                                                                                                                                                                             |  |  |  |  |

| MROMEN                                                                       | 8                                            | I           | MROMEN monitors the local memory bus ROM enable signal.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

## **Terminal Functions (Continued)**

$\dagger I = in, O = out$

<sup>‡</sup> The TI380PCIA SIF pin names correspond to a subset of the system interface pins on a TI380C2x<sup>§</sup>. See the TI380C2x<sup>§</sup> data sheets for more information on individual pins. Like-named pins on the TI380PCIA and TI380C2x<sup>§</sup> system interfaces are intended to be connected to each other.

TI380C3x devices can be used with TI380PCIA in the same way as TI380C2x devices.

¶ Typical bit-ordering for Intel<sup>™</sup> and Motorola<sup>™</sup> processor buses

<sup>#</sup> The signal connecting this pin to the TI380C2x<sup>§</sup> also should be connected to a 4.7-k $\Omega$  pullup resistor.

I The TI380PCIA BIF pin names correspond to a subset of the local memory bus interface pins on a TI380C2x<sup>§</sup>. Like-named pins on the two devices are intended to be connected to each other. Consult the TI380C2x<sup>§</sup> data sheets for more information on individual pins.

SPWS035 - JUNE 1997

| TERMINA | L             | ı/ot | DESCRIPTION                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|---------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME    | NO.           |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|         | PCI INTERFACE |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD31    | 27            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD30    | 29            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD29    | 30            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD28    | 32            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD27    | 33            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD26    | 35            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD25    | 36            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD24    | 38            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD23    | 42            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD22    | 43            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD21    | 44            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD20    | 45            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD19    | 47            |      | PCI address and data. A bus transaction to or from one of these pins consists of an address phase                                                                                                                                                                                                                        |  |  |  |  |  |

| AD18    | 48            |      | followed by one or more data phases.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| AD17    | 49            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD16    | 51            |      | The address phase is the clock cycle in which FRAME is asserted. During the address phase,                                                                                                                                                                                                                               |  |  |  |  |  |

| AD15    | 66            | 1/0  | AD31 – AD00 contain a physical address (32 bits). For I/O, this is a byte address; for configuration and                                                                                                                                                                                                                 |  |  |  |  |  |

| AD14    | 68            |      | memory, it is a DWORD address. During data phases, AD07–AD00 contain the LSB, and AD31–AD24                                                                                                                                                                                                                              |  |  |  |  |  |

| AD13    | 69            |      | contain the MSB. Write data is stable and valid when IRDY is asserted, and read data is stable and valid                                                                                                                                                                                                                 |  |  |  |  |  |

| AD12    | 71            |      | when TRDY is asserted. Data is transferred during those clocks where both IRDY and TRDY are                                                                                                                                                                                                                              |  |  |  |  |  |

| AD11    | 72            |      | asserted.                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| AD10    | 73            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD09    | 74            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD08    | 75            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD07    | 78            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD06    | 80            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD05    | 81            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD04    | 83            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD03    | 84            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD02    | 85            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD01    | 86            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| AD00    | 87            |      |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| C/BE3   | 39            |      | Bus command and byte-enables. During the address phase of a transaction, C/BE3-C/BE0 define the                                                                                                                                                                                                                          |  |  |  |  |  |

| C/BE2   | 53            |      | bus command. During the data phase, C/BE3–C/BE0 are used as byte-enables. The byte-enables are                                                                                                                                                                                                                           |  |  |  |  |  |

| C/BE1   | 65            | I/O  | valid for the entire data phase and they determine which byte lanes carry meaningful data. C/BE0                                                                                                                                                                                                                         |  |  |  |  |  |

| C/BE0   | 77            |      | applies to the LSB and C/BE3 applies to the MSB.                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| DEVSEL  | 59            | I/O  | Device-select. When DEVSEL is actively driven, it indicates that the driving device has decoded its address as the target of the current access. As an input, DEVSEL indicates if any device on the bus has been selected. If no PCI agent has asserted DEVSEL, then the TI380PCIA removes itself as the PCI bus master. |  |  |  |  |  |

## **Terminal Functions (Continued)**

$\dagger I = in, O = out$

<sup>‡</sup> The TI380PCIA SIF pin names correspond to a subset of the system interface pins on a TI380C2x<sup>§</sup>. See the TI380C2x<sup>§</sup> data sheets for more information on individual pins. Like-named pins on the TI380PCIA and TI380C2x<sup>§</sup> system interfaces are intended to be connected to each other.

$\$  TI380C3x devices can be used with TI380PCIA in the same way as TI380C2x devices.

¶ Typical bit-ordering for Intel<sup>™</sup> and Motorola<sup>™</sup> processor buses

<sup>#</sup>The signal connecting this pin to the TI380C2x§ also should be connected to a 4.7-k $\Omega$  pullup resistor.

The TI380PCIA BIF pin names correspond to a subset of the local memory bus interface pins on a TI380C2x§. Like-named pins on the two devices are intended to be connected to each other. Consult the TI380C2x§ data sheets for more information on individual pins.

## **Terminal Functions (Continued)**

| TERMIN         |            |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|----------------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TERMIN<br>NAME | IAL<br>NO. | vot | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                |            |     | PCI INTERFACE (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| FRAME          | 55         | I/O | Cycle frame. FRAME is driven by the current master to indicate the beginning and duration of an access. It is asserted to indicate that a bus transaction is beginning. While FRAME is asserted, data transfers continue. When FRAME is deasserted, the transaction is in the final data phase.                                                                                                                                                                                                                                        |  |  |  |

| GNT            | 25         | I   | Grant. GNT indicates to the TI380PCIA that access to the PCI bus has been granted. This is a point-to-point signal.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| IDSEL          | 41         | I   | Initialization device select. IDSEL is used as a chip-select during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| INTA           | 20         | 0   | Interrupt A. INTA is used to request an interrupt. The assertion and deassertion of INTA is asynchronous to PCLK.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| IRDY           | 56         | 1/0 | Initiator ready. IRDY indicates that the bus master can complete the current data phase of the transaction. If a data phase is completed on any clock, both IRDY and TRDY are sampled and asserted. During a write, IRDY indicates that valid data is present on AD31–AD00. During a read, it indicates that the master is prepared to accept data. Wait cycles are inserted until both IRDY and TRDY are asserted together.                                                                                                           |  |  |  |

| PAR            | 63         | 1/0 | Parity. PAR carries even parity across AD31–AD00 and C/BE3–C/BE0. It is driven by the master for address and write data phases; it is driven by the target for read data phases. PAR is valid one clock after the address phase. For data phases, PAR is valid one clock after either IRDY (for a write) or TRD (for a read) is asserted.                                                                                                                                                                                              |  |  |  |

| PCLK           | 23         | 1   | Clock. PCLK provides timing for all transactions on the PCI bus. All other PCI signals, except RST and INTA, are sampled on the rising edge of PCLK. PCLK is used to generate the SBCLK signal that goes to the TI380C2x§.                                                                                                                                                                                                                                                                                                             |  |  |  |

| PERR           | 61         | 1/0 | Parity error. PERR is for the reporting of data parity errors during all transactions. It is driven active by the agent receiving data two clocks following the data when a data parity error is detected. The minimum duration of PERR is one clock for each data phase that a data parity error is detected.<br>There are no special conditions when a PERR can be lost or when reporting of an error can be delayed. An agent cannot report a PERR until it has claimed the access by asserting DEVSEL and completing a data phase. |  |  |  |

| REQ            | 26         | 0   | Request. REQ indicates to the arbiter that TI380PCIA desires use of the bus. REQ is a point-to-point signal.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                |            |     | Reset. RST is used to hard-reset the LAN subsystem, including TI380C2x§ and the TI380PCIA.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| RST            | 21         | I   | To prevent ADxx, $\overline{C/BEx}$ , and PAR signals from floating during reset, the central device can drive these lines during reset (bus-parking) but only to a logic-low level; these cannot be driven high.                                                                                                                                                                                                                                                                                                                      |  |  |  |

| SERR           | 62         | 1/0 | System error. SERR, when enabled, reports address parity errors or any other system error where the result is catastrophic. The assertion of SERR is synchronous to the clock and meets the setup and hold times of all PCI signals.                                                                                                                                                                                                                                                                                                   |  |  |  |

| STOP           | 60         | 1/0 | Stop. STOP indicates that the current slave is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                |            |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

$\dagger I = in, O = out$

<sup>‡</sup> The TI380PCIA SIF pin names correspond to a subset of the system interface pins on a TI380C2x<sup>§</sup>. See the TI380C2x<sup>§</sup> data sheets for more information on individual pins. Like-named pins on the TI380PCIA and TI380C2x<sup>§</sup> system interfaces are intended to be connected to each other.

§ TI380C3x devices can be used with TI380PCIA in the same way as TI380C2x devices.

¶ Typical bit-ordering for Intel<sup>™</sup> and Motorola<sup>™</sup> processor buses

<sup>#</sup> The signal connecting this pin to the TI380C2x§ also should be connected to a 4.7-k $\Omega$  pullup resistor.

The TI380PCIA BIF pin names correspond to a subset of the local memory bus interface pins on a TI380C2x<sup>§</sup>. Like-named pins on the two devices are intended to be connected to each other. Consult the TI380C2x<sup>§</sup> data sheets for more information on individual pins.

## **Terminal Functions (Continued)**

| TERMINAL I/<br>NAME NO.                                                                                                                                                                                      |     | vot                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PCI INTERFACE (CONTINUED)                                                                                                                                                                                                                                                                                           |

| TRDY       57       I/O       data phase of the transaction. If a data phase is completed on any clock, both TRDY and sample-asserted. During a read, TRDY indicates that valid data is present on AD31–AD00 |     | Target ready. TRDY indicates the target agent's (that is, the TI380PCIA's) ability to complete the current data phase of the transaction. If <u>a data</u> phase is completed on any clock, both TRDY and IRDY are sample-asserted. During a read, TRDY indicates that valid data is present on AD31–AD00. During a write, TRDY indicates that the target is prepared to accept data. Wait cycles are inserted until both IRDY and TRDY and TRDY are asserted together. |                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                              |     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SERIAL EEPROM INTERFACE                                                                                                                                                                                                                                                                                             |

| EDIO                                                                                                                                                                                                         | 111 | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EEPROM data input/output is a bidirectional signal used to transfer data into or out of the EEPROM memory. Note I <sup>2</sup> C memory devices typically require a pullup resistor to V <sub>CC</sub> on this line. This is an open-drain output. If the optional EEPROM is not present, EDIO should be tied high. |

| EDC                                                                                                                                                                                                          | 122 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EEPROM clock signal used to synchronize all data in and data out of the memory. I <sup>2</sup> C memory devices typically require a pullup resistor to $V_{CC}$ on this line. If the optional EEPROM is not present, EDC should be tied low.                                                                        |

$\dagger I = in, O = out$

<sup>‡</sup> The TI380PCIA SIF pin names correspond to a subset of the system interface pins on a TI380C2x<sup>§</sup>. See the TI380C2x<sup>§</sup> data sheets for more information on individual pins. Like-named pins on the TI380PCIA and TI380C2x<sup>§</sup> system interfaces are intended to be connected to each other.

§ TI380C3x devices can be used with TI380PCIA in the same way as TI380C2x devices.

¶ Typical bit-ordering for Intel<sup>™</sup> and Motorola<sup>™</sup> processor buses

<sup>#</sup> The signal connecting this pin to the TI380C2x§ also should be connected to a 4.7-k $\Omega$  pullup resistor.

II The TI380PCIA BIF pin names correspond to a subset of the local memory bus interface pins on a TI380C2x<sup>§</sup>. Like-named pins on the two devices are intended to be connected to each other. Consult the TI380C2x<sup>§</sup> data sheets for more information on individual pins.

#### architecture

The major blocks of the TI380PCIA, illustrated in Figure 2, include the PCI interface (PCIIF), TI380C2x<sup>†</sup> interface (SIF), ROM interface (ROMIF), serial EEPROM interface (EIF), and burned-in address emulation interface (BIF). The functionality of each block is described in the following sections.

#### PCI interface (PCIIF)

The PCIIF block contains all logic needed to interact with the PCI bus and allows the TI380PCIA to assume the role of bus master or slave. This block controls all communication between the TI380PCIA and the PCI bus. All signals entering the PCIIF, as well as signals generated within the PCIIF, are synchronous to the PCLK signal.

The TI380PCIA also checks and generates parity for data presented on the PCI bus at the PCIIF.

The PCIIF generates and responds to the PCI cycles listed in Table 1.

| TI380PCIA CAN GENERATE:     | TI380PCIA RESPONDS TO:               |

|-----------------------------|--------------------------------------|

| Memory read line            | I/O reads and writes                 |

| Memory write and invalidate | Configuration reads and writes       |

| Memory write                | All types of memory reads and writes |

Table 1. PCI Interface Logic

The TI380PCIA asserts slave-initiated termination, if the initiator exceeds one data-phase transfer.

#### address decode

The TI380PCIA uses only the most significant 27 address bits present in AD31–AD00 to decode an access directed at the TI380PCIA for a TI380C2x<sup>†</sup> DIO access, and the most significant 16 bits for a ROM access. The TI380PCIA's base address selects a block of eight contiguous 32-bit memory or I/O locations for DIO access or 64K bytes of address space for ROM access. Access to each register within the selected memory, I/O, or configuration space is uniquely decoded. The decode logic returns DEVSEL as a medium-latency device.

The PCIIF logic generates control signals that propagate either to configuration registers, the SIF, ROMIF, or EIF within the TI380PCIA. The address and command/byte-enables are valid and sustained throughout each PCI cycle. Configuration registers can be accessed through configuration cycles when the TI380PCIA's address is decoded.

## address/data-parity checking and generation

The PCIIF checks and generates parity for addresses during bus master operations and for data during master and slave operations. If the PCIIF encounters SERR two PCLKs after the address phase when it is mastering the PCI bus, it terminates its transaction immediately and regains control of the TI380C2x<sup>†</sup> SIF. If the PCIIF detects any address error (even if not selected) or data parity error (only when selected) while operating as a PCI slave, or if it detects a data parity error while operating as a PCI bus master, it pulses PERR and sets bit 15 in the status register to 1. Bus transactions causing the parity error are otherwise ignored by the LAN subsystem. Any bus-mastering transaction that encounters a parity error is aborted by the TI380PCIA. This detection also prevents future bus master cycles from occuring until a reset occurs.

The TI380PCIA performs a bus master cycle when bus-mastering is enabled and the TI380C2x<sup> $\dagger$ </sup> requests the SIF bus.

The supported PCI master cycles are:

- Memory write

- Memory read line

- Memory write and invalidate

#### address/data-parity checking and generation (continued)

During PCI master cycles, PCIIF is able to handle the following:

- Master-abort termination: due to no DEVSEL response

- Slave-initiated termination: disconnect/retry and slave-abort

- Parity-error processing

#### TI380C2x<sup>†</sup> interface (SIF)

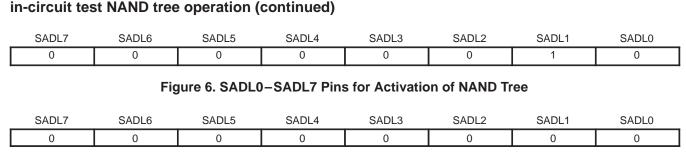

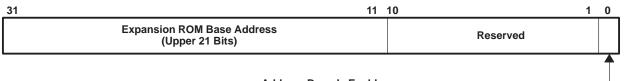

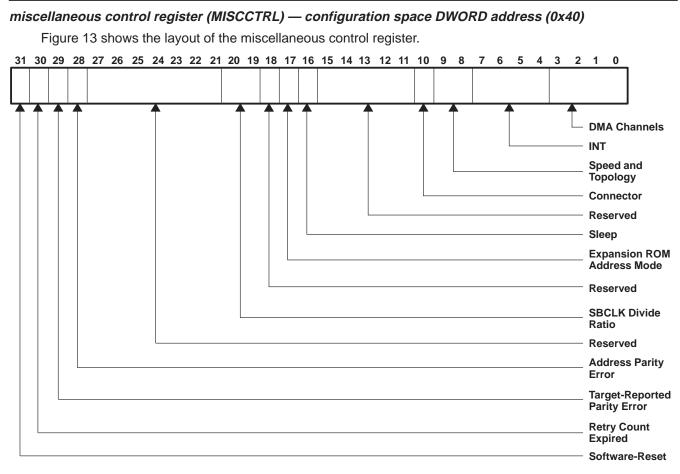

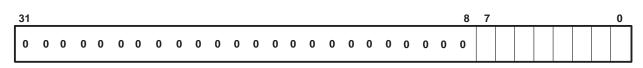

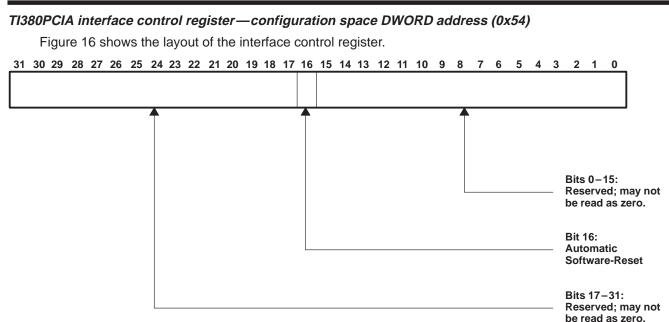

The SIF handles all communications between the TI380C2 $x^{\dagger}$  and the TI380PCIA.