## **Toshiba**

# TC8512 Gouraud Shading Processor

#### **Data Sheet**

## **Features**

- Gouraud shading at 8 Mpixels/second

- Bresenham line drawing

- Hidden surface removal (Z-buffer algorithm)

- Linear speed increase with parallel chips (up to 24 Mpixels/second) in Gouraud shading

- 16 MHz clock

- 200 mA maximum power consumption

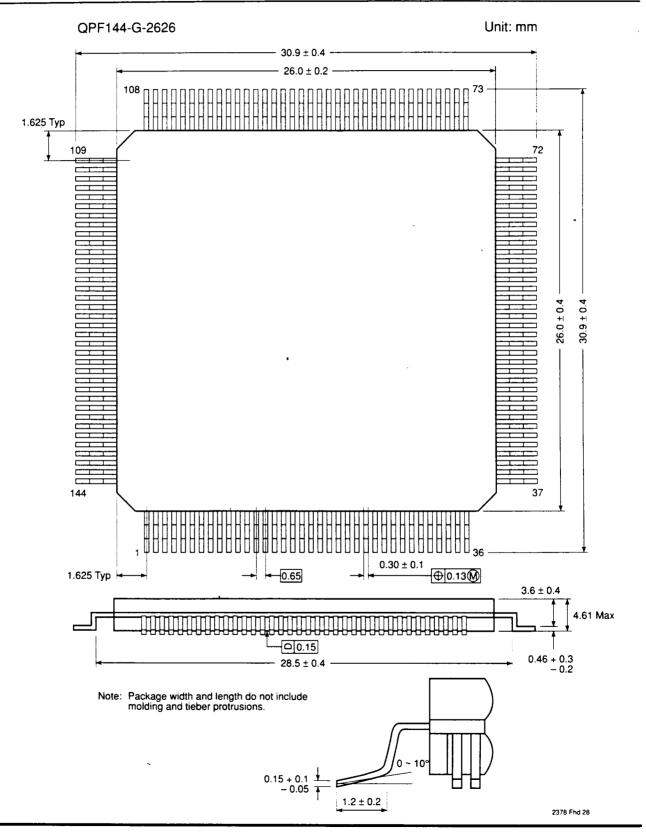

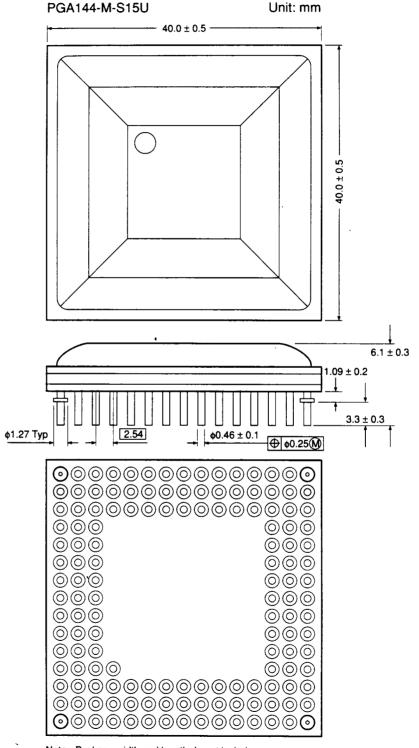

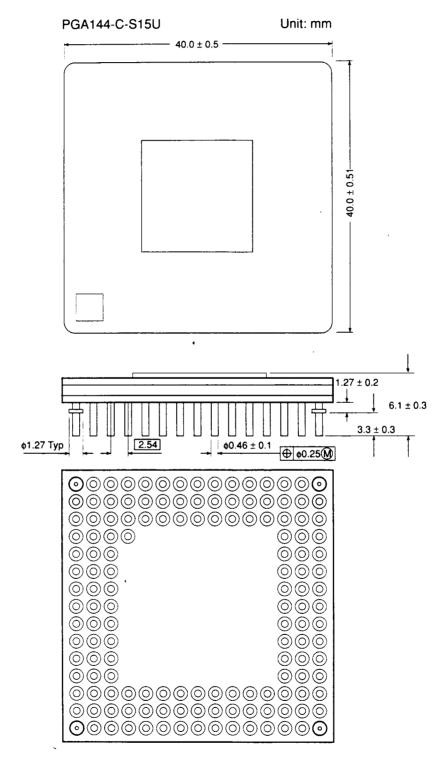

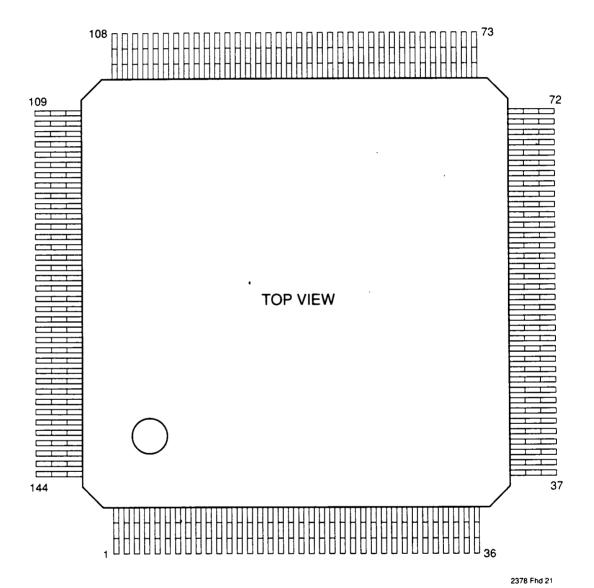

- 144-pin flat pack, PGA

## **Description**

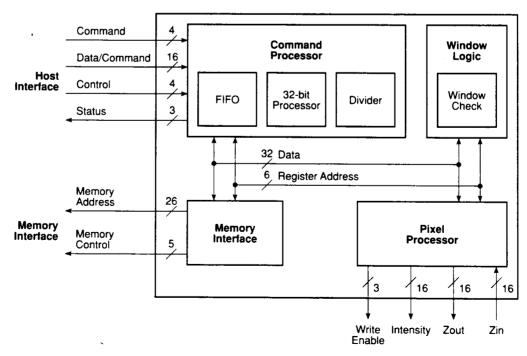

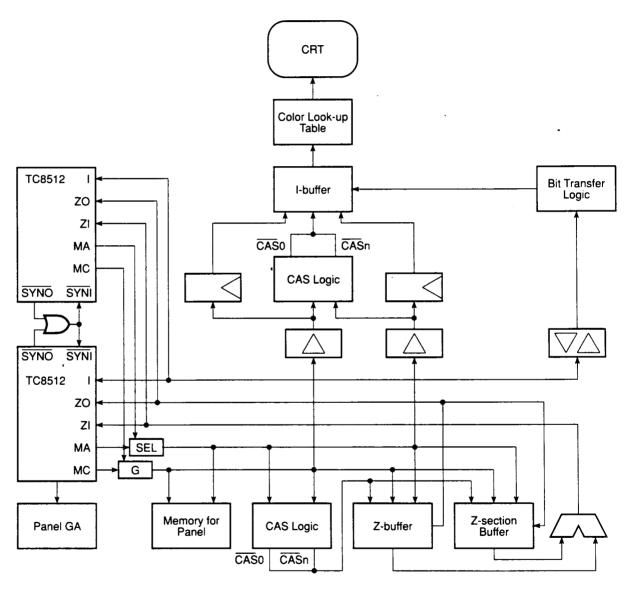

The Toshiba TC8512 Gouraud Shading Processor (Figure 1) performs fast rendering of 3-dimensional solid objects and 2-dimensional lines and polygons.

Performance as high as 6 Mpixels/sec is achieved through hardware implementation of the Gouraud shading algorithm and Bresenham line drawing algorithm. Higher performance can be obtained by running two or four chips in parallel.

The TC8512 has four 16-bit ports. One port is the host interface through which commands and data, such as color intensity values and 3-D coordinates, are downloaded. The remaining three ports connect to video RAM (VRAM).

A VRAM is a type of DRAM which has two ports. One port is a random-access port similar to a standard DRAM interface. The other port is a serial-access port, through which data is clocked in sequence by loading it into an on-chip shift register.

The TC8512 gets maximum bandwidth from video RAM by using the serial and random-access ports simultaneously. Both the color intensity (I) and depth (Z) buffers are kept in VRAM. The I-buffer can directly feed the video DACs, or it can drive the address inputs of a color lookup table. The Z-buffer is used for hiddensurface removal while an image is drawn.

Figure 1. Internal Diagram

#### **Gouraud Shading**

Smooth shading of curved surfaces is performed using Gouraud shading, a technique in which I-values are calculated by linear interpolation between the I-values at the vertices of the polygon being drawn. This standard shading algorithm is described in textbooks on computer graphics, such as *Principles of Interactive Graphics* by William Newman and Robert Sproull (McGraw-Hill).

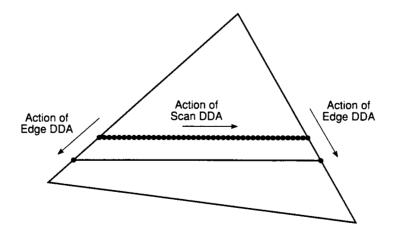

The TC8512 has separate digital differential analyzers (DDAs) for interpolating the I- and Z-values along the edges of polygons, and for interpolating between edges along a scan line.

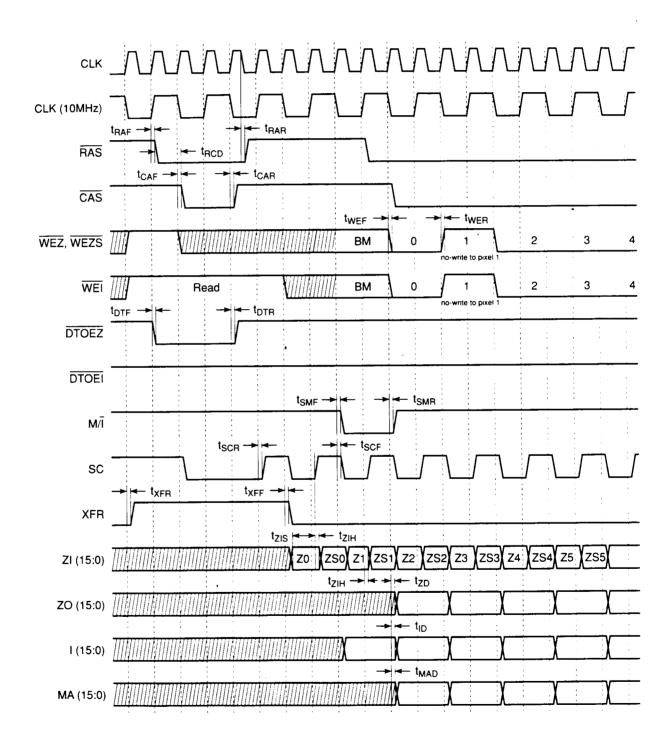

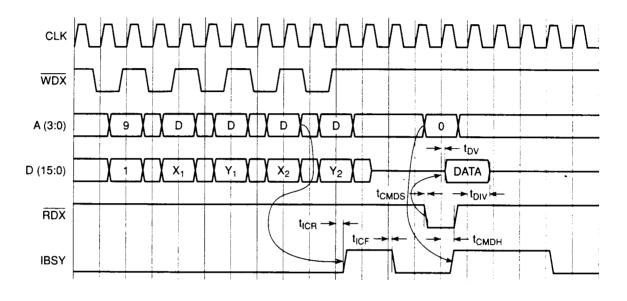

In the TC8512 implementation, the polygons are triangles. The execution of a typical drawing command consists of several cycles of data downloaded from the host for each triangle, followed by many cycles to load the triangle into VRAM (Figure 2).

#### **Constant Shading**

The TC8512 also supports constant shading, in which all of the pixels within a triangle or trapezoid are assigned the same I- and Z-values. This can be used for fast rendering of 2-dimensional images and for initializing the I- and Z-buffers to a background value. With wide I- and Z-buffers and a small amount of external circuitry, constant shading may be performed at speeds up to 96 Mpixels/sec.

#### **Line Drawing**

The TC8512 also provides line drawing at speeds up to 6 Mpixels/sec. A Bresenham algorithm is used, which gives lines drawn at different angles the appearance of equal width. Depth cueing is performed by interpolating I and Z between the two endpoints of the line.

#### **Z-Buffer Algorithm**

The TC8512 uses a Z-buffer algorithm for hiddensurface removal. This algorithm assigns a Z-coordinate for every pixel on the screen. This value represents the distance from the observer to the closest surface at that point, and it is used to control write operations when adding features to an image.

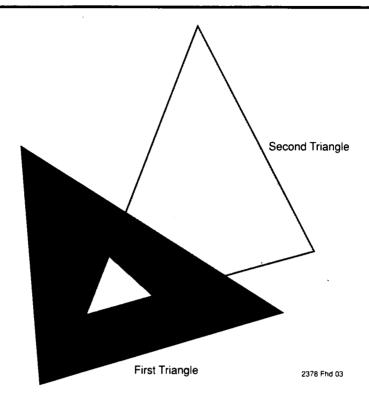

For example, the image of two intersecting triangles shown below is rendered by first loading every pixel for the first triangle. Both the I- and Z-buffers are loaded. When the second triangle is drawn, the existing Z-coordinates are checked against the new values generated for the second triangle. For those pixels in which the depth is less (i.e., those parts of the triangle which are closer to the observer), the new I- and Z-values are loaded into VRAM. Where the depth is greater, the existing contents of VRAM remain unchanged (Figure 3).

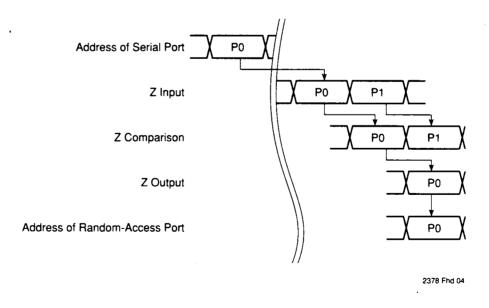

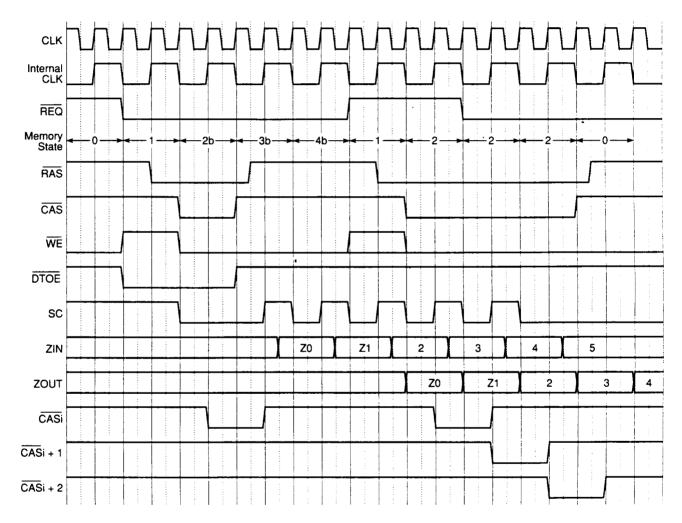

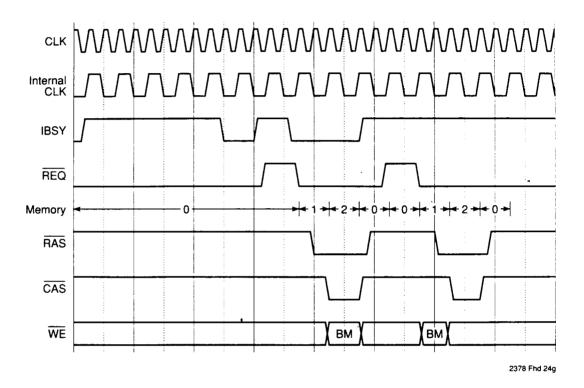

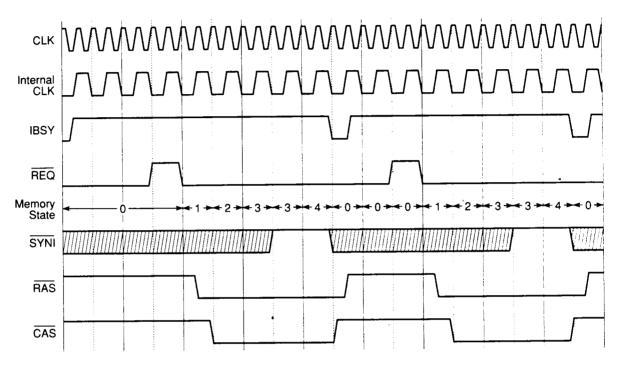

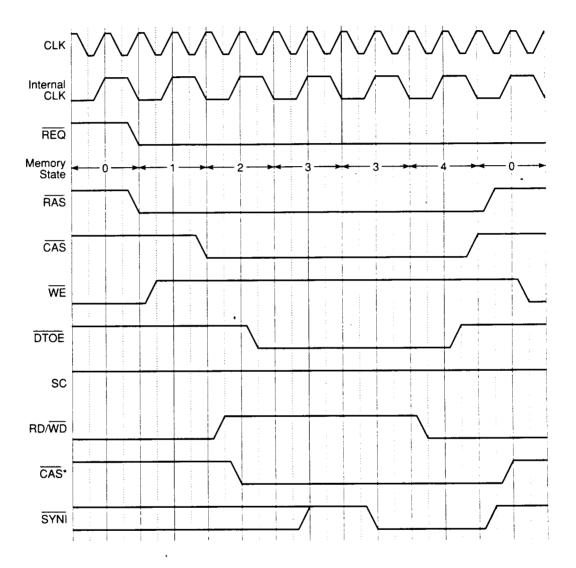

To allow filling at the rate of one pixel for each VRAM cycle, the TC8512 has three ports: one to load the new

Figure 2. Gouraud Shading Diagram (showing interpolation)

Figure 3.\* Intersecting Triangles

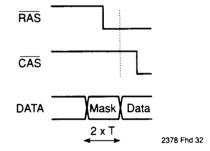

Figure 4. Pipelined Timing

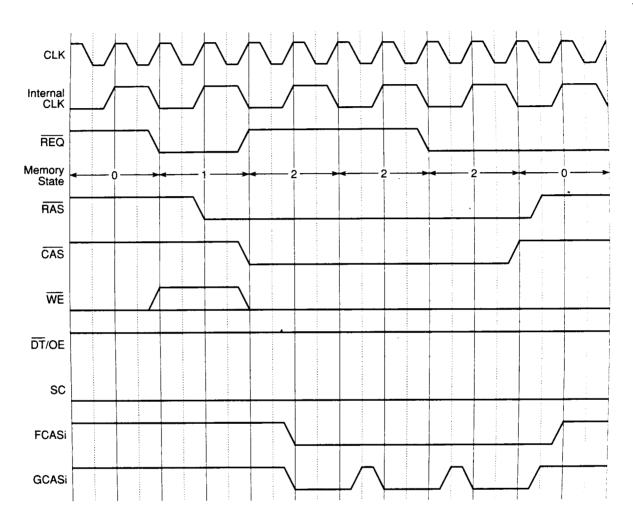

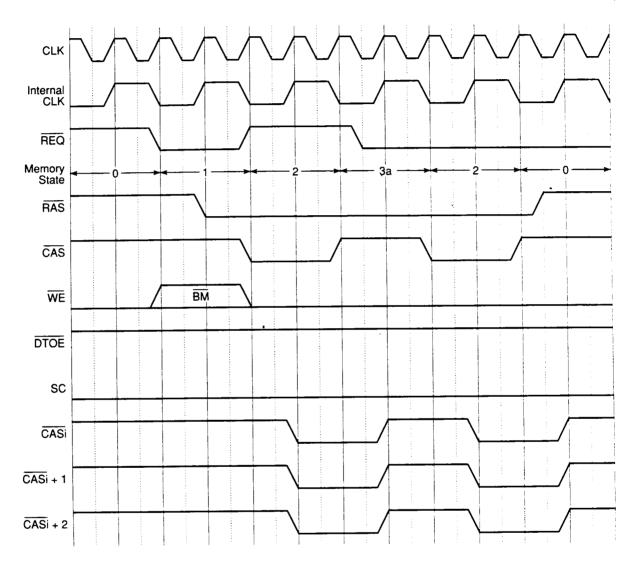

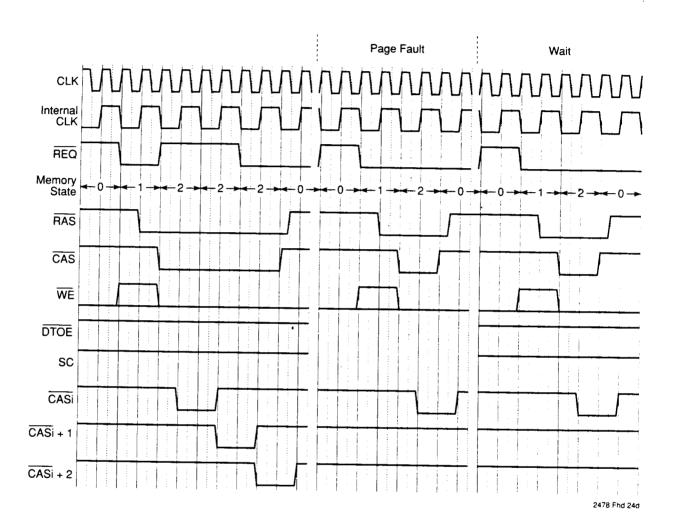

I-value, one to load the new Z-coordinate, and one to read the existing Z-coordinate. The latter is connected to the serial port of the Z-buffer VRAMs, and it reads two cycles behind the random-access port to allow pipelining the comparison of the old and new Z-coordinates as shown in the following timing diagram (Figure 4).

Higher pixel rates are achieved in systems with parallel chips. For example, a system with two chips could use one for the odd pixels and the other for the even pixels, and these pixels would be generated simultaneously.

#### **Clipping Window**

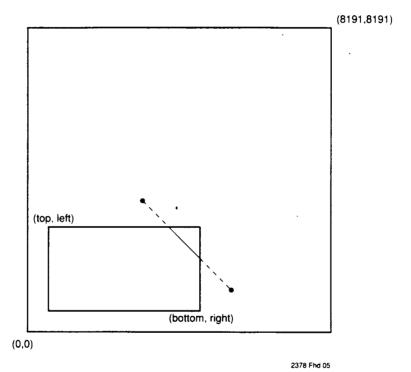

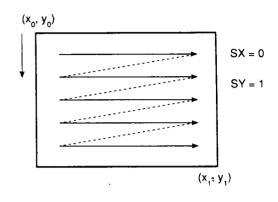

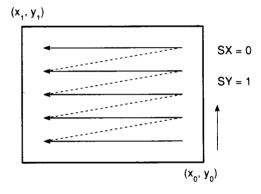

The TC8512 can be programmed to inhibit drawing outside of a rectangular window defined in the screen coordinate system (Figure 5).

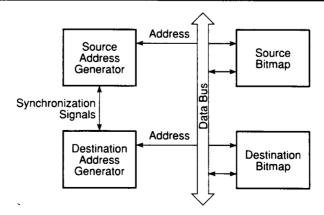

#### **Raster Copy and Scaling**

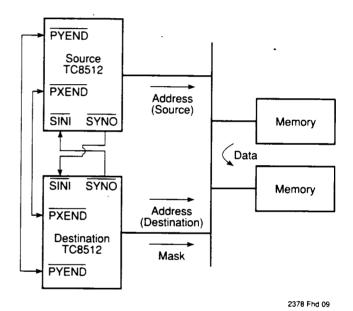

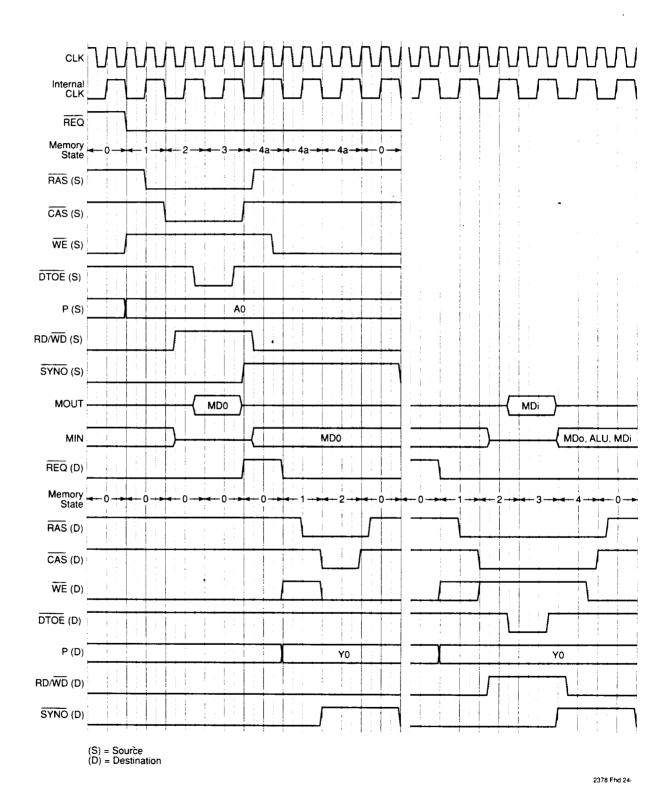

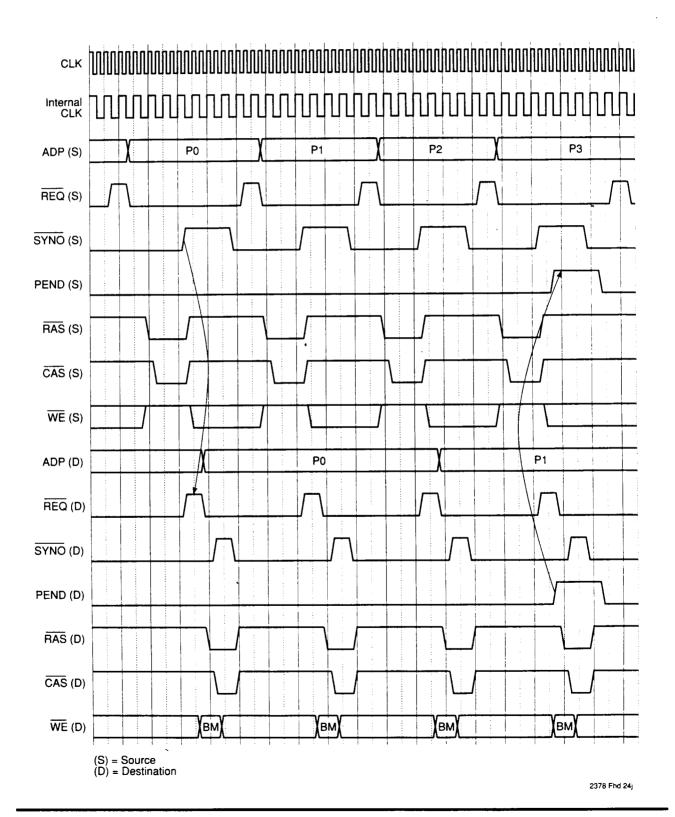

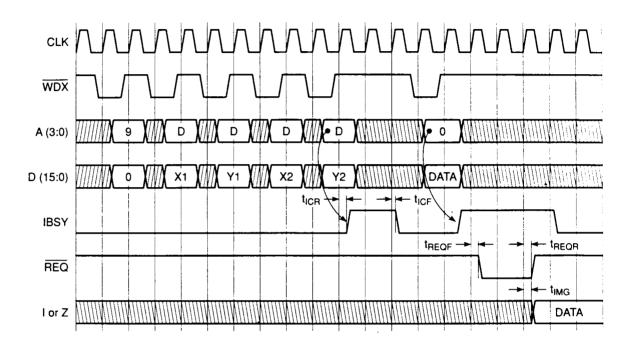

Two chips can be used as address generators in a configuration which allows rapid pixel block transfers from one memory to another. Magnification and reduction over a range from 1/64 to 64X are available in systems which implement this configuration (Figure 6).

Figure 5. Clipping Window

Figure 6. Address Generator Configuration

## **System Architecture**

The TC8512 has two interfaces, one 16-bit port connected to the host processor and three 16-bit ports connected to VRAM. The VRAM ports share a common

26-bit address bus. A block diagram of a typical two-chip configuration is shown below (Figure 7).

Figure 7. A Typical Two-Chip System

#### **Host Processor Interface**

The host processor interface receives commands and data, which are queued in an on-chip 20-bit x 16-level FIFO. It is intended that the host processor poll the NFLL line before downloading a new command. (It is also possible to use the NFLL signal to gate the DMA request when single-cycle DMA is used.)

The control signals consist of separate read and write strobe lines. Both of these signals are internally synchronized, which simplifies interface to asynchronous buses and buses running at frequency different from the TC8512.

Commands are transmitted on four signals intended for connection to the bus address. Each command also has data or subcommands which are sent on the data bus. To invoke a command, software writes data to one of the sixteen addresses decoded for the TC8512.

There are no byte enable signals; the TC8512 must be accessed strictly as a 16-bit device. Each pulse on the write strobe loads a new command, so any design which uses an 8-bit bus must perform the byte/word conversion externally.

#### **VRAM Interface**

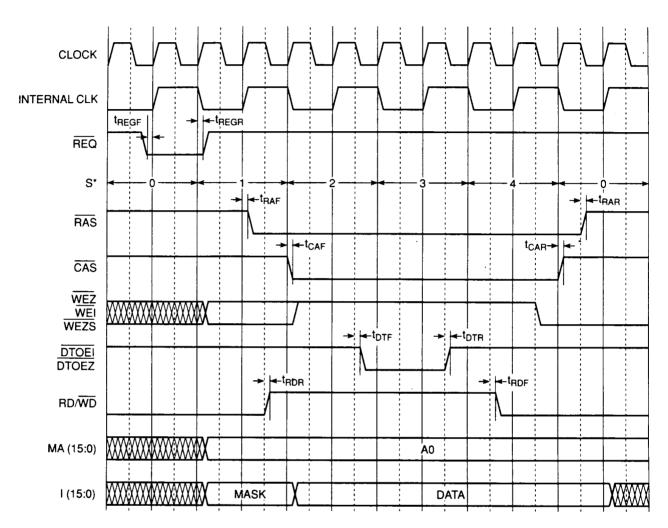

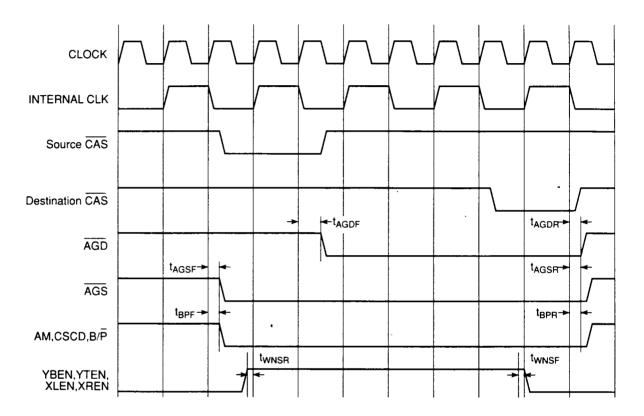

The TC8512 generates a complete set of signals for interfacing to the serial and parallel ports of VRAM. Most signals simply require buffering for connection to the VRAM banks. The VRAM address, however, requires external multiplexing. The CAS signal also requires external logic.

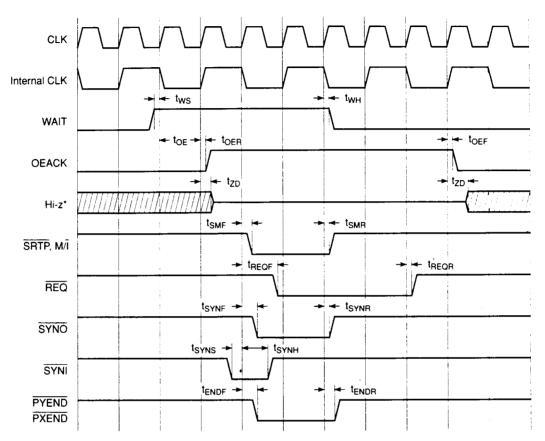

In most systems, the host processor is required to provide refresh cycles. To allow the host to take control of the VRAM bus, a handshake has been provided using the WAIT and OEACK signals.

Two image transfer modes are available for uploading or downloading images between the host processor and VRAM. In one mode, each transfer moves a single 16-bit pixel. In the FAST mode, on the other hand, each transfer moves 16 one-bit pixels. The IMODE subcommand sets the image transfer mode. (See the

Programming section, below.) The table below shows the relationship between the image transfer modes and various graphics functions.

| HSP Functions                      | Memory /            | Access Mode               |

|------------------------------------|---------------------|---------------------------|

|                                    | 1 pixel<br>(16-bit) | 16 pixels<br>(1 bit each) |

| Gouraud up shading                 | •                   |                           |

| Constant shading                   |                     | •                         |

| Depth Cuing                        | •                   |                           |

| Line Drawing color pixel pattern   | •                   | •                         |

| Address Generation                 |                     | •                         |

| Scaling Magnification/Reduction    | •                   |                           |

| Image Data Out color pixel pattern | •                   | •                         |

| Image Data In pixel horizontal     | •                   | •                         |

2378 Pgm tbl 28

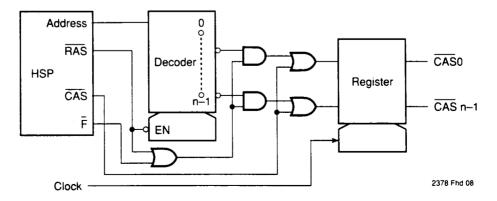

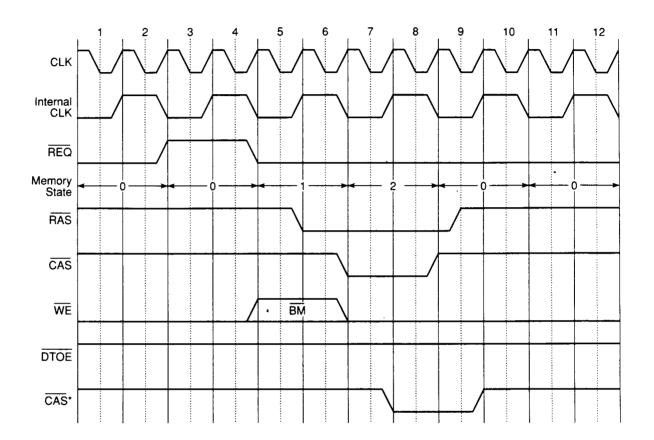

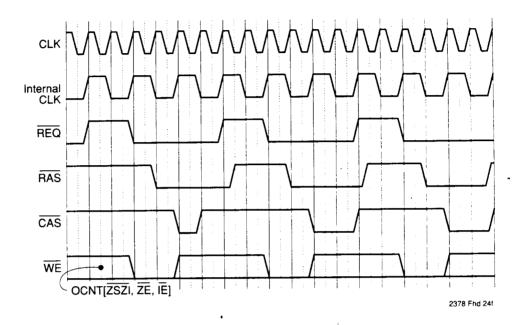

In the 1-pixel mode, the memory write logic controls the WE (write enable) signal. In FAST mode, the TC8512 generates a 16-bit mask pattern at the falling edge of the RAS signal (Figure 8). The external control circuit must latch the mask pattern, and use it to control the write-enable bit.

CAS for the VRAMs must be generated in external logic. At a minimum, the CAS signal from the TC8512 must be delayed by one clock period before being

Figure 8. Mask Timing (Fast Mode)

Figure 9. External CAS Generation

applied to VRAM. If FAST mode (i.e., 16-pixel mode) is not selected using the IMODE subcommand or if both FAST mode and FS mode (i.e., reduced CAS timing, as selected by the HCONTROL subcommand) are selected, an external circuit must be provided to decode the low address bits (Figure 9). In this case, the CAS signal from the TC8512 is used to enable the CAS signals applied to VRAM.

### **Address Generator Configuration**

In the two-chip address generator configuration, the SYNI, SYNO, PXEND, and PYEND synchronization signals are connected as shown below. The SYNI and SYNO signals are connected differently in other configurations, and the PXEND and PYEND signals are not used at all (Figure 9).

#### **Multiprocessor Configurations**

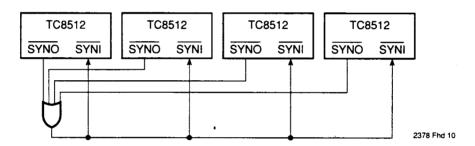

There are two ways to use multiple chips to achieve higher performance. In one method, each chip has its own I- and Z-buffers, and the pixels in these buffers are interleaved. For example, in a two-chip system (Figure 10), one chip handles the even pixels while the other chip handles the odd pixels. In a four-chip system, each chip handles every fourth pixel, and the chips are staggered one pixel apart.

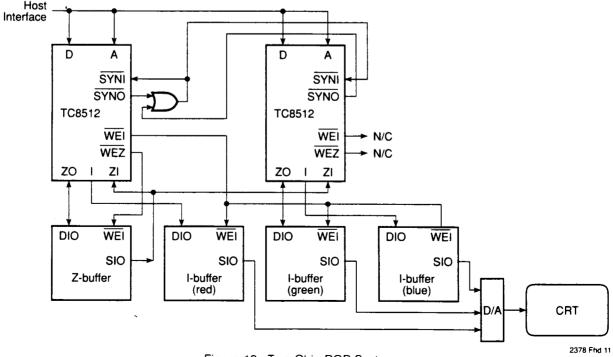

The other method is specific to RGB color systems. Here, separate I-values are used to drive the red, green, and blue video DACs. In this configuration, one chip handles interpolation in Z and one of the I-values, while the other chip handles the other two I-values.

The former method provides faster drawing rates than a single processor, while keeping the same number of I-bits. The latter method provides the same drawing rate as a single processor, while increasing the number of I-bits. The latter method is used where the I-bits are interpreted directly as the color, rather than as an index

into a color lookup table. (Lookup tables might be used with the latter method, but their purpose would be to correct for non-linearities in the conversion of digital l-values into the colors perceived by the eye.)

In any multi-chip configuration, it is necessary to synchronize the WAIT input signal (which is used during the VRAM refresh cycle) to prevent skewing. Shown below (Figure 11) is an example in which an external flip-flop is used to distribute the WAIT signal. The trailing edge of the TC8512 clock is input as the flip-flop clock.

Figure 10. Two-Chip System

WAIT D

CLK Flip-Flop

CLK Trailing edge is input

CLK CLK CLK

TC8512

CLK CLK

2378 Fhd 11A

Figure 11. Synchronization of WAIT Signal

#### **Interleaved Pixels**

When multiple chips are used to handle interleaved pixels, the SYNO outputs are ORed together and used to drive the SYNI inputs, as shown below (Figure 12) for a four-chip system. A similar configuration is used for a two-chip system.

The INIT command and HCONTROL subcommand are used to enable the two- or four-chip configurations (i.e., CSCD = 1 or 2, EXSYN = 1). The commands which set I-, Z-, X- and Y-values are downloaded to all chips simultaneously.

#### **RGB** Color

When two chips are used to drive an RGB color system (Figure 13), one chip handles the Z-buffer algorithm and one of the colors (red, green, and blue). The

second chip handles the other two colors, using its Z logic to interpolate one of the colors. The SYNI and SYNO signals are handled in the same manner used for interleaved pixels.

Unlike the interleaved pixels configuration, the INIT command initializes the chips for the uniprocessor configuration (i.e., CSCD = 0). The ZCONTROL subcommand enables hidden surface removal (i.e., ZCK = 1). The HCONTROL subcommand selects output of the internally calculated Z-coordinate (ZI = 0) and external sync (EXTSYN = 1). The commands which download X- and Y-coordinates are downloaded to both chips simultaneously, however the Z-values and each color's I-values are specific to each chip.

Figure 12. Four-Chip System

Figure 13. Two-Chip RGB System

## **Programming**

This section describes the operation of the TC8512 as seen by the programmer, including the coordinate system, default mode settings, and commands.

#### **Screen Coordinate System**

The origin of the coordinate system is the bottom left corner of the screen, at the closest distance to the observer. The X-coordinate increases toward the right, the Y-coordinate increases toward the top, and the Z-coordinate increases with greater distance from the observer. The X- and Y-coordinates are unsigned binary numbers up to 13 bits in length. The Z-coordinate is an unsigned binary number up to 16 bits in length. A screen resolution of up to 8192 x 8192 pixels can be accommodated.

#### **Default Modes**

When the TC8512 is given an INIT command, internal mode settings get set to the following default values:

- Polygon drawing mode is Gouraud shading. (See PMODE subcommand.)

- Line drawing mode does not overwrite background pixels. (See LMODE subcommand.)

- When an image is uploaded or downloaded between the host and VRAM, 16-bit pixels are assumed, (See IMODE subcommand.)

- Hidden-surface removal and depth sectioning are both disabled. (See ZCONTROL subcommand.)

- Hardware control modes are all 0. (See HCONTROL subcommand.)

- Transparency pattern has all bits set (i.e., no pixels are masked). (See TPATTERN subcommand.)

- Clipping window boundaries are at their maximum range (0 and 8192, in both X and Y). (See WIN-DOW subcommand.)

- Constant Z-sectioning depth is at its maximum value (FFFFh). (See SECTION subcommand.)

- Foreground and background colors for 2-dimensional line drawing are 1 and 0, respectively. (See COLOR subcommand.)

- Cyclic line pattern produces a solid line. (See LPATTERN subcommand.)

- A bit-planes are enabled for writes. (See MASK subcommand.)

- Magnification/reduction scale (only used with the two-chip address generator configuration) is 1 to 1. (See SCALE subcommand.)

- Line status is waiting for the first endpoint of a line or polyline. (See LSTATUS command.)

#### **Commands**

In the command descriptions that follow the summary table, on the next page, the four bits which invoke the command are shown to the left of the data applied to the sixteen-bit data bus. Typically, the command bits will come from the low address lines on the bus of the host processor, so that commands are invoked by writing data to specific bus addresses.

### Toshiba TC8512 Gouraud Shading Processor

| Command    | Hex Code | Data                            | Description                                                                                                                                                     |

|------------|----------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT       | F        | Initialization                  | System configuration and default-mode setting.                                                                                                                  |

| AUX        | E        | Auxiliary commands              | Specifies various subcommands. The AUX command is followed by one or more PARM commands.                                                                        |

| PARM       | D        | Parameters                      | Data for the subcommands specified in the AUX, IMG, and ADDR commands.                                                                                          |

| (reserved) | С        |                                 |                                                                                                                                                                 |

| i          | 1        | Color-index value (I-value)     | Downloads a 16-bit I-value for the next line or polygon vertex.                                                                                                 |

| Z          | 2        | Z-coordinate (depth value)      | Downloads a 16-bit Z-coordinate for the next line or polygon vertex.                                                                                            |

| Υ          | 3        | Y-coordinate                    | Downloads a 13-bit Y-coordinate for the next line or polygon vertex.                                                                                            |

| X          | 4        | X-coordinate                    | Downloads a 13-bit X-coordinate for the next line or polygon vertex.                                                                                            |

| T1X        | 5        | Triangle X-coordinate (LMODE 1) | In line-drawing mode 1, downloads a 13-bit X-coordinate for the first vertex of a triangle.                                                                     |

| T2X        | 6        | Triangle X-coordinate (LMODE 2) | In line-drawing mode 2, downloads a 13-bit X-coordinate for the first vertex of a triangle.                                                                     |

| (reserved) | 7        |                                 |                                                                                                                                                                 |

| LX         | . 8      | Line X-coordinate               | Downloads a 13-bit X-coordinate for the first endpoint of a line or polyline.                                                                                   |

| IMG        | 9        | Image coordinates               | Used with PARM commands to specify a transfer-direction and a rectangular region of the I-buffer for subsequent transfer by the PTRN command.                   |

| PTRN       | 0        | Pattern transfer                | Transfers 16 bits of pixel data to or from the host. The direction of transfer is controlled by the IMG command.                                                |

| ADDR       | Α        | Address transfer                | (Used only in the two-chip address generator configuration.) Used with PARM commands to transfer a rectangular region of memory between source and destination. |

| PX         | В        | Polyline X-coordinate           | Downloads a 13-bit X-coordinate for the endpoints of a polyline, after the first endpoint has been downloaded with the LX command.                              |

#### **INIT Command**

| ( | Comr | mano | t |    |    |    |                                |    |    | ( | Com | mano | t   |     |     |  |    |    |  |

|---|------|------|---|----|----|----|--------------------------------|----|----|---|-----|------|-----|-----|-----|--|----|----|--|

| 3 | 2    | 1    | 0 | 15 | 14 | 13 | 3 12 11 10 9 8 7 6 5 4 3 2 1 0 |    |    |   |     |      |     |     |     |  |    |    |  |

| 1 | 1    | 1    | 1 | AM | СТ |    |                                | ΑC | DR |   |     | CS   | ODO | csc | DNO |  | ŞI | ZE |  |

2378 Drw 01

First command given following reset initialization. It is also used whenever any of the modes it controls need to be changed. Note that all other modes get set to their default values.

AM Selects the pixel cache organization. 0 selects 4 x 4; 1 selects 16 x 1.

CT Enables the pixel cache. 0 is cache disabled; 1 is cache enabled. (The pixel cache increases the speed of some graphics operations. Early versions of the TC8512 do not implement the pixel cache. Be sure your version implements this feature before enabling this bit.)

ADDR Sets the horizontal line length. This is used to generate linear addressing for VRAM. The ADDR field is a six-bit code, which is encoded as shown below:

| coded as s | hown below:             |

|------------|-------------------------|

| Code       | Line Length (in pixels) |

| 000000     | 256                     |

| 000001     | 320                     |

| 000010     | 384                     |

| 000011     | 448                     |

| 000100     | 512                     |

| 000101     | 576                     |

| 000110     | 640                     |

| 000111     | 704                     |

| 010010     | 768                     |

| 010011     | 832                     |

| 001000     | 1024                    |

| 001001     | 1088                    |

| 001010     | 1152                    |

| 001011     | 1216                    |

| 010110     | 1280                    |

| 010111     | 1344                    |

| 100010     | 1536                    |

| 100011     | 1600                    |

| 001100     | 2048                    |

| 001101     | 2112                    |

| 001110     | 2176                    |

| 001111     | 2240                    |

| 011010     | 2304                    |

| 011011     | 2368                    |

| 100110     | 2560                    |

| 100111     | 2624                    |

| 011100     | 4096                    |

| 011101     | 4160                    |

| 011110     | 4352                    |

#### **Toshiba TC8512 Gouraud Shading Processor**

|        | 011111                | 4416                                                                                                                             |

|--------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|

|        | 101010                | 4608                                                                                                                             |

|        | 101011                | 4672                                                                                                                             |

|        | 101100                | 8192                                                                                                                             |

|        | 101101                | 8256                                                                                                                             |

|        | 101110                | 8704                                                                                                                             |

|        | 101111                | 8768                                                                                                                             |

| CSCDO  |                       | the number of chips in a multichip configuration. 0 is one two chips; 2 is four chips.                                           |

| CSCDNO | Specifies are 0, 1, 2 | the unit number in a multichip configuration. Legal values , and 3.                                                              |

| SIZE   | row addre             | the page size, so the TC8512 knows when to reload the ess into VRAM. The SIZE field is a four-bit code, which is as shown below: |

|        | Code                  | Page Size (in bytes)                                                                                                             |

|        | 0000                  | 256                                                                                                                              |

|        | 0001                  | 512                                                                                                                              |

|        | 0010                  | 1K                                                                                                                               |

|        | 0011                  | 2K                                                                                                                               |

|        | 0100                  | 4K                                                                                                                               |

|        | 0101                  | 8K                                                                                                                               |

|        | 0110                  | 16K                                                                                                                              |

|        | 0111                  | 32K                                                                                                                              |

#### **AUX and PARM Commands**

|   | ( | Comi | mano | į  |    |    |    |    |    |    |    | Da    | ıta |    |   |   |   |   |   |   |

|---|---|------|------|----|----|----|----|----|----|----|----|-------|-----|----|---|---|---|---|---|---|

| 1 | 3 | 2    | 1    | oʻ | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8     | 7   | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

|   | 1 | 1    | 1    | 0  |    |    |    |    |    |    | Sı | ipcoi | nma | nd |   |   |   |   |   |   |

|   | 1 | 1    | 0    | 1  |    |    |    |    |    |    |    | Da    | ata |    |   |   |   |   |   |   |

2378 Drw 02

The AUX and PARM commands are used together to execute several subcommands. The AUX command is issued first, with the Subcommand in its data field. Then one or more PARM commands is issued, with the data relevent to the subcommand in its data field.

#### PMODE Subcommand

| ( | Comr | mano | t |    |    |    |    |    |    |    | Da   | ıta  |    |   |   |   |   |   |   |

|---|------|------|---|----|----|----|----|----|----|----|------|------|----|---|---|---|---|---|---|

| 3 | 2    | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7    | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

| 1 | 1    | 1    | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0  | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1    | 0    | 1 |    |    |    |    |    |    | Sh | adin | g Mo | de |   |   |   |   |   |   |

2378 Drw 03

Selects one of two polygon shading modes. 0 selects Gouraud shading; 1 selects constant shading. All other values of the shading mode are reserved for future expansion.

#### LMODE Subcommand

|   | Com | mano | ż |    |    |    |    |    |    |      | Da   | ata  |     |   |   |   |   |   |   |

|---|-----|------|---|----|----|----|----|----|----|------|------|------|-----|---|---|---|---|---|---|

| 3 | 2   | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8    | 7    | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| 1 | 1   | 1    | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0    | 0   | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 1   | 0    | 1 |    |    |    |    |    | l  | _ine | Drav | ving | Mod | е |   |   |   |   |   |

2378 Drw 04

Selects one of three line drawing modes. Two of these modes are intended for 2-dimensional line drawing, in which a cyclic pattern can be used to create dotted and dashed lines. (For more information, see the description of the LPATTERN subcommand.) In mode 0, pixels in the dots or dashes are loaded from a register which specifies the foreground I-value. The parts of the line between the dots or dashes are loaded from another register, which specifies the background I-value.

In mode 1, only the foreground pixels are loaded. The background pixels are left undisturbed. This provides a transparent background, in which empty spaces between dots or dashes do not overwrite the existing contents of the l-buffer.

In mode 2 (3-D line drawing), the cyclic pattern is ignored. The I-values are interpolated between the line endpoints, which provides depth cueing. If hiddensurface removal is enabled (using the ZCONTROL subcommand), the Z-coordinates are also interpolated between endpoints.

All other values of the line drawing mode are reserved for future expansion.

#### IMODE Subcommand

|   | Com | mano | d |    |    |    |    |    |      |      | Da    | ata  |       |      |   |   |   |   |   |

|---|-----|------|---|----|----|----|----|----|------|------|-------|------|-------|------|---|---|---|---|---|

| 3 | 2   | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10   | 9    | 8     | 7    | 6     | 5    | 4 | 3 | 2 | 1 | 0 |

| 1 | 1   | 1    | 0 | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0     | 0    | 0     | 0    | 0 | 0 | 0 | 1 | 0 |

| 1 | 1   | 0    | 1 |    |    |    |    |    | Imag | je D | ata 1 | rans | fer N | Mode | , |   |   |   |   |

2378 Drw 05

Selects the image transfer mode, for uploading or downloading images between the host processor and VRAM. 0 selects 16-bit pixels, one per transfer; 1 selects 1-bit pixels, 16 per transfer. The latter mode requires external logic to steer the pixels onto the I-bus (the mode setting only affects the VRAM addressing).

All other values of the image data transfer mode are reserved for future expansion. In the two-chip address generator configuration, the 16-bit pixel mode must be used (the default mode).

The image transfer mode remains fixed until the next INIT command or IMODE subcommand is executed.

#### ZCONTROL Subcommand

|   | ( | Comr | nanc | Í |    |    |    |    |    |    |   | Da | ıta |     |     |     |   |   |   |   |

|---|---|------|------|---|----|----|----|----|----|----|---|----|-----|-----|-----|-----|---|---|---|---|

|   | 3 | 2    | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7   | 6   | 5   | 4   | 3 | 2 | 1 | 0 |

|   | 1 | 1    | 1    | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0   | 0   | 0   | 0   | 0 | 0 | 1 | 1 |

| Ì | 1 | 1    | 0    | 1 | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0   | ZCK | ZSC | ZSW | 0 | 0 | 0 | 0 |

2378 Drw 06

Controls hidden-surface removal and two forms of Z-sectioning.

ZSW Selects the source of Z-sectioning data. 0 selects a constant sectioning depth loaded using the SECTION subcommand; 1 selects a variable sectioning depth from an external Z-sectioning buffer.

ZSC Controls depth sectioning. 0 disables it; 1 enables it. (Early versions of the TC8512 do not implement depth sectioning. Be sure your version implements this feature before enabling this bit.)

ZCK Controls hidden-surface removal. 0 disables it; 1 enables it.

#### **HCONTROL Subcommand**

Z١

|  | ( | Comi | nano | t |    |    |      |    |       |     |   | D  | ata  |   |   |   |    |    |    |      |

|--|---|------|------|---|----|----|------|----|-------|-----|---|----|------|---|---|---|----|----|----|------|

|  | 3 | 2    | 1    | 0 | 15 | 14 | 13   | 12 | 11    | 10  | 9 | 8  | 7    | 6 | 5 | 4 | 3  | 2  | 1  | 0    |

|  | 1 | 1    | 1    | 0 | 0  | 0  | 0    | 0  | 0     | 0   | 0 | 0  | 0    | 0 | 0 | 0 | 0  | 1  | 0  | 0    |

|  | 1 | 1    | 0    | 1 | 0  | 0  | CORR | 0  | EXSYN | RMW | 0 | FS | BMSK | 0 | 0 | 0 | ZI | ΙE | ZE | ZSCE |

2378 Drw 07

Defines miscellaneous hardware control modes.

CORR Controls subpixel correction. 0 disables it (I- and Z-values are rounded): 1 enables it.

EXSYN Enables the SYNI input. 0 is for single-chip configurations; 1 is for multichip configurations. EXSYN is also used for image-data input synchronization.

RMW Enables read/modify/write cycles to VRAM. 0 is for separate read and write cycles: 1 is for read/modify/write cycles.

FS Enables shorter CAS-only cycles (only used when constant shading and page mode access are selected). 0 is longer cycles (4 clock periods); 1 is shorter cycles (2 clock periods).

BMSK Enables the write pulse when bit mask data is being presented (only used in 16-pixel mode). 0 is write pulse inhibited; 1 is write pulse enabled.

Selects the buffer being accessed when data is being uploaded or downloaded between the host processor and VRAM. During download, 0 sends Z-data out the Z-output bus; 1 sends I-data out the Z-output bus. During upload, 0 reads from the I-buffer; 1 reads from the Z-buffer.

IE Enables the write pulse on the I-bus when an I-value is being presented. 0 is write pulse inhibited; 1 is write pulse enabled.

ZE Enables the write pulse on the Z-bus when a Z-coordinate is being

presented. 0 is write pulse inhibited; 1 is write pulse enabled.

ZSCE Enables the write pulse on the Z-bus when Z-sectioning data is being presented (only used when Z-sectioning is enabled). 0 is write pulse inhibited; 1 is write pulse enabled.

#### TPATTERN Subcommand

|   | ( | Comi | mano | t |    |    |    |    |    |    |     | Da   | ıta   |      |    |   |   |   |   |   |

|---|---|------|------|---|----|----|----|----|----|----|-----|------|-------|------|----|---|---|---|---|---|

|   | 3 | 2    | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8    | 7     | 6    | 5  | 4 | 3 | 2 | 1 | 0 |

| ſ | 1 | 1    | 1    | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0    | 0     | 0    | 0  | 0 | 0 | 1 | 0 | 1 |

| ſ | 1 | 1    | 0    | 1 |    |    |    |    |    | Tr | ans | pare | ncy F | atte | rn |   |   |   |   |   |

2378 Drw 08

Specifies a transparency pattern. This is a mask which is ANDed with the write enable for each pixel, to allow existing images to be seen through new images loaded into VRAM. The mask is a 4 x 4 array of bits, addressed by the two LSBs of the X- and Y-addresses. If a mask bit is clear, pixels which match that bit's X and Y LSBs are not written to VRAM.

The correspondence between bits in the transparency pattern and bits in the mask is shown in the table below. Gouraud shading and 3-dimensional line drawing ignore the transparency mask.

The transparency pattern remains fixed until the next INIT command or TPATTERN subcommand is executed.

| 2 LSBs<br>of X<br>of Y | 00 | 01 | 10 | 11 |

|------------------------|----|----|----|----|

| 00                     | 0  | 1  | 2  | თ  |

| 01                     | 4  | 5  | 6  | 7  |

| 10                     | 8  | 9  | 10 | 11 |

| 11                     | 12 | 13 | 14 | 15 |

2378 Fhd 12

#### WINDOW Subcommand

| 1 | ( | Com | mano | d |    |    |    |    |    |      |       | Da    | ıta  |       |       |   |   |   |   |   |

|---|---|-----|------|---|----|----|----|----|----|------|-------|-------|------|-------|-------|---|---|---|---|---|

|   | 3 | 2   | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10   | 9     | 8     | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

|   | 1 | 1   | 1    | 0 | 0  | 0  | 0  | 0  | 0  | 0    | 0     | 0     | 0    | 0     | 0     | 0 | 0 | 1 | 1 | 0 |

|   | 1 | 1   | 0    | 1 |    |    |    |    |    | To   | op Le | eft X | Coo  | rdina | ate   |   |   |   |   |   |

|   | 1 | 1   | 0    | 1 |    |    |    |    |    | To   | op Le | eft Y | -Coo | rdina | ate_  |   |   |   |   |   |

|   | 1 | 1   | 0    | 1 |    |    |    |    |    | Bott | om F  | Right | X-C  | oord  | inate | ) |   |   |   |   |

|   | 1 | 1   | 0    | 1 |    |    |    |    |    | Bott | om F  | Right | Y-C  | oord  | inate | ) |   |   |   |   |

|   | 1 | 1   | 0    | 1 | 0  | 0  | 0  | 0  | 0  | 0    | 0     | 0     | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |

2378 Drw 09

Specifies a clipping window within the screen coordinate system. Drawing is inhibited outside of the clipping window. Pixels on the border of the clipping window are not clipped. The boundary values of the clipping window remain fixed until the next INIT command or WINDOW subcommand is executed.

#### Toshiba TC8512 Gouraud Shading Processor

#### SECTION Subcommand

| ( | Comi | mano | t |    |    |    |    |    |      |       | Da   | ata  |     |       |     |   |   |   |   |

|---|------|------|---|----|----|----|----|----|------|-------|------|------|-----|-------|-----|---|---|---|---|

| 3 | 2    | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10   | 9     | 8    | 7    | 6   | 5     | 4   | 3 | 2 | 1 | 0 |

| 1 | 1    | 1    | 0 | 0  | 0  | 0  | 0  | 0  | 0    | 0     | 0    | 0    | 0   | 0     | 0   | 0 | 1 | 1 | 1 |

| 1 | 1    | 0    | 1 |    |    |    |    | Z  | -Sec | tioni | ng D | epth | (Co | nstai | nt) |   |   |   |   |

2378 Drw 10

Define a Z-sectioning depth. This value is only used for constant Z-sectioning (see the description of the ZCONTROL subcommand). Transparency-pattern drawing is inhibited for pixels with a greater Z-coordinate (i.e., further from the observer).

#### COLOR Subcommand

| ( | Com | mano | i |    |    |    |    |    |    |      | Da   | ata   |       |   |   |   |   |   |   |

|---|-----|------|---|----|----|----|----|----|----|------|------|-------|-------|---|---|---|---|---|---|

| 3 | 2   | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8    | 7     | 6     | 5 | 4 | 3 | 2 | 1 | 0 |

| 1 | 1   | 1    | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0     | 0     | 0 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1   | 0    | 1 |    |    |    |    |    |    | Fore | grou | ınd ( | Color |   |   |   |   |   |   |

| 1 | 1   | 0    | 1 |    |    |    |    |    |    | Bac  | kgro | und ( | Colo  | • |   |   |   |   |   |

2378 Drw 11

Define the foreground and background colors (I-values) used for line drawing. In 2-dimensional line drawing, a cyclic pattern can be used to create dotted and dashed lines. (For more information, see the description of the LPATTERN subcommand.) Pixels in the dots or dashes are loaded with the foreground color. The parts of the line between the dots or dashes can be loaded with the background color.

#### LPATTERN Subcommand

|   | 1 | Com | man | d |    |    | Data  14 13 12 11 10 9 8 7 6 5 4 3 2 1 0  0 0 0 0 0 0 0 0 0 0 0 1 0 0 1  Line Pattern (bits 31-16) |    |    |     |      |        |        |       |     |   |   |   |   |   |

|---|---|-----|-----|---|----|----|----------------------------------------------------------------------------------------------------|----|----|-----|------|--------|--------|-------|-----|---|---|---|---|---|

| 1 | 3 | 2   | 1   | 0 | 15 | 14 | 13                                                                                                 | 12 | 11 | 10  | 9    | 8      | 7      | 6     | 5   | 4 | 3 | 2 | 1 | 0 |

|   | 1 | 1   | 1   | 0 | 0  | 0  | 0                                                                                                  | 0  | 0  | 0   | 0    | 0      | 0      | 0     | 0   | 0 | 1 | 0 | 0 | 1 |

|   | 1 | 1   | 0   | 1 |    |    |                                                                                                    |    |    | Lin | e Pa | atterr | ı (bit | s 31- | 16) |   |   |   |   |   |

| Γ | 1 | 1   | 0   | 1 |    |    |                                                                                                    |    |    | Lir | ne P | atter  | n (bi  | s 16  | -0) |   |   |   |   |   |

2378 Drw 12

Specifies a line pattern. This is a mask applied cyclically during 2-dimensional line drawing to create various dotted and dashed effects. These bits are ANDed with the write enable for each pixel. The first pixel is ANDed with bit 31 of the mask, the second pixel with bit 30, etc. For example, a solid line would have all bits set (111111111...1111) while a dotted line would have alternating set and clear bits, such as (11001100...1100).

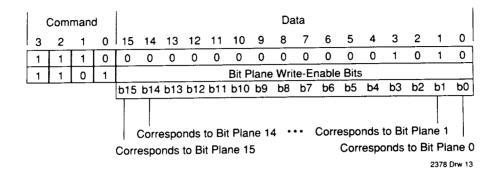

#### MASK Subcommand

Specify a mask to inhibit writes to individual bit planes. This mask is initialized after switching to 16-pixel mode.

#### SCALE Subcommand

|   | C | omi | mano | ť |     |     |    |    |    |    |   | Da | ata |   |   |   |    |   |   |   |

|---|---|-----|------|---|-----|-----|----|----|----|----|---|----|-----|---|---|---|----|---|---|---|

| 3 | 3 | 2   | 1    | 0 | 15  | 14  | 13 | 12 | 11 | 10 | 9 | 8  | 7   | 6 | 5 | 4 | 3  | 2 | 1 | 0 |

| 1 |   | 1   | 1    | 0 | 0   | 0   | 0  | 0  | 0  | 0  | 0 | 0  | 0   | 0 | 0 | 0 | 1  | 0 | 1 | 1 |

| 1 |   | 1   | 0    | 1 | S/D | AYE |    |    | -  | ۱Y |   |    | AXE |   |   |   | AX |   | _ |   |

2378 Drw 14

Specify mode settings for the two-chip address generator configuration. The magnification or reduction scale factor is independent in each dimension. The scale factor is:

(source count +1) / (destination count + 1)

For example, a value of 9 in the source chip and a value of 0 in the destination chip would result in a magnification factor of 10X.

S/D Select source or destination mode. 0 is destination; 1 is source.

AYE For magnification in Y, this bit is 0 in the source chip and 1 in the destination chip. For reduction in Y, this bit is 1 in the source chip

and 0 in the destination chip.

AY Magnification or reduction count for Y-coordinate.

AXE For magnification in X, this bit is 0 in the source chip and 1 in the

destination chip. For reduction in X, this bit is 1 in the source chip

and 0 in the destination chip.

AX Magnification or reduction count for X-coordinate.

#### Toshiba TC8512 Gouraud Shading Processor

#### LSTATUS Subcommand

| ( | Comi | mano | d |    |    |    |    |    |    |   | Da | ata |   |     |     |   |   |   |   |

|---|------|------|---|----|----|----|----|----|----|---|----|-----|---|-----|-----|---|---|---|---|

| 3 | 2    | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7   | 6 | 5   | 4   | 3 | 2 | 1 | 0 |

| 1 | 1    | 1    | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0   | 0 | 0   | 0   | 1 | 1 | 0 | 0 |

| 1 | 1    | 0    | 1 | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0   | 0 | INV | END | 0 | 0 | 0 | 0 |

2378 Drw 15

Controls line drawing. There are two states: a state which controls termination of a line or polyline (i.e., chained vectors), and a state which controls visibility. An INIT command or the last endpoint of the previous line or polyline will leave the TC8512 waiting for the first endpoint of the next line or polyline. After downloading the first endpoint, an LSTATUS subcommand is issued to enable visibility. Intermediate endpoints may be downloaded without any intervening LSTATUS subcommands. Before the last endpoint is downloaded, an LSTATUS subcommand is used to identify the last endpoint as the termination of the polyline.

Between any two points in a polyline, the LSTATUS subcommand can be used to selectively inhibit drawing of individual line segments. A second LSTATUS subcommand is used to re-enable drawing, if desired.

INV Enables line drawing between the previous endpoint and next endpoint. 0 enables drawing (i.e., visible); 1 inhibits drawing (i.e., invisible).

END Specifies whether the next endpoint will terminate a line or polyline.

0 is no termination; 1 is termination.

#### I Command

| ( | Comr | nanc | ı . |    |    |    |    |    |    |   | Da   | ıta  |   |   |   |   |   |   |   |

|---|------|------|-----|----|----|----|----|----|----|---|------|------|---|---|---|---|---|---|---|

| 3 | 2    | 1    | 0   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0    | 0    | 1   |    |    |    |    |    |    | • | I-Va | alue |   |   |   |   |   |   |   |

2378 Drw 16

Downloads an I-value for the next line or polygon vertex. This value is a 16-bit unsigned integer.

#### **Z** Command

|   | Com | man | t |    |    |    |    |    |    |    | Da  | ıta   |     |   |   |   |   |   | 1 |

|---|-----|-----|---|----|----|----|----|----|----|----|-----|-------|-----|---|---|---|---|---|---|

| 3 | 2   | 1   | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 0   | 1   | 0 |    |    |    |    |    |    | Z- | Coo | rdina | ate |   | - |   |   |   |   |

2378 Drw 17

Downloads a Z-coordinate for the next line or polygon vertex. This value is a 16-bit unsigned integer. The value increases with greater distance from the observer.

#### Y Command

|   | C | Comi | mano | t |    |    |    |    |    |    |    | Da  | ıta   |     |   |   |   |   |   |   |

|---|---|------|------|---|----|----|----|----|----|----|----|-----|-------|-----|---|---|---|---|---|---|

| : | 3 | 2    | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|   | 0 | 0    | 1    | 1 |    |    |    |    |    |    | Y- | Coo | rdina | ite |   | - |   |   |   |   |

2378 Drw 18

Downloads a Y-coordinate for the next line or polygon vertex. This value is a 13-bit unsigned integer. The value increases from the bottom to the top of the screen.

#### X Command

|   | ( | Comi | mano | t |    |    |    |    |    |    |    | Da  | ıta   |     |   |   |   |   |   |    |

|---|---|------|------|---|----|----|----|----|----|----|----|-----|-------|-----|---|---|---|---|---|----|

| ł | 3 | 2    | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7     | 6   | 5 | 4 | 3 | 2 | 1 | οl |

| Γ | 0 | 1    | 0    | 0 |    |    |    |    |    |    | X- | Coo | rdina | ite |   |   |   |   |   |    |

2378 Drw 19

Downloads an X-value for the next line or polygon vertex. This value is a 13-bit unsigned integer. The value increases from the left to the right of the screen. The order of I, Y, and Z is arbitrary, but each endpoint or vertex must be terminated by an X-coordinate. The T1X, T2X, and LX commands are special forms of the X command used to indicate the beginning of a triangle or line.

#### **T1X Command**

| ( | Comi | mano | t |    |    |    |    |    |    |    | Da  | ıta   |     |   |   |   |   |   |   |

|---|------|------|---|----|----|----|----|----|----|----|-----|-------|-----|---|---|---|---|---|---|

| 3 | 2    | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 1    | 0    | 1 |    |    |    |    |    |    | X- | Coo | rdina | ite |   |   |   |   |   |   |

2378 Drw 20

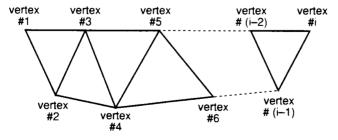

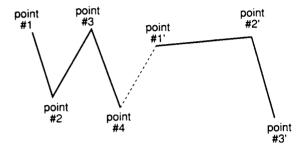

In line-drawing (LMODE) mode 1, downloads an X-value for the first vertex of a triangle. This value is a 13-bit unsigned integer. The value increases from the left to the right of the screen. The order of I, Y, and Z is arbitrary, but the vertex must be terminated by an X-coordinate. Subsequent connected triangles may be drawn as shown below.

2378 Fhd 13

#### **T2X Command**

|   | Com | man | đ |    |    |    |    |    |    |    | Da  | ata   |     |   |   |   |   |   |   |

|---|-----|-----|---|----|----|----|----|----|----|----|-----|-------|-----|---|---|---|---|---|---|

| 3 | 2   | 1   | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | 1   | 1   | 0 |    |    |    |    |    |    | X- | Coo | rdina | ıte |   |   |   |   |   |   |

2378 Drw 21

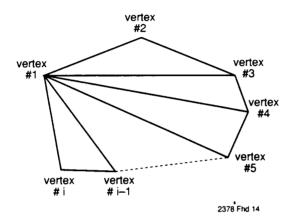

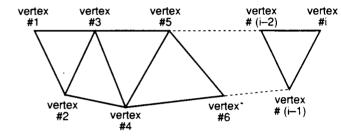

In line-drawing (LMODE) mode 2, downloads an X-coordinate for the first vertex of a triangle. This value is a 13-bit unsigned integer. The value increases from the left to the right of the screen. The order of I, Y, and Z is arbitrary, but the vertex must be terminated by an X-coordinate. Subsequent connected triangles may be drawn as shown below.

#### **LX Command**

|    | ( | Comr | nanc | t |    |    |    |    |    |    |    | Da  | ıta   |     |   |   |   |   |   |   |

|----|---|------|------|---|----|----|----|----|----|----|----|-----|-------|-----|---|---|---|---|---|---|

| 1: | 3 | 2    | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|    | 1 | 0    | 0    | 0 |    |    |    |    |    |    | X- | Coo | rdina | ite |   |   |   |   |   |   |

2378 Drw 22

Downloads an X-coordinate for the first endpoint of a line or polyline. This value is a 13-bit unsigned integer. The value increases from the left to the right of the screen. The order of I, Z, and Y is arbitrary, but the endpoint must be terminated by an X-coordinate.

#### **IMG and PARM Commands**

| 1 | Com | man | d |    |    |    |    |    |    |    | Da  | ata   |     |   |   |   |    |   |     |

|---|-----|-----|---|----|----|----|----|----|----|----|-----|-------|-----|---|---|---|----|---|-----|

| 3 | 2   | 1   | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7     | 6   | 5 | 4 | 3 | 2  | 1 | o l |

| 1 | 0   | 0   | 1 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0     | 0   | 0 | 0 | 0 | ТО | 0 | RW  |

| 1 | 1   | 0   | 1 |    |    |    |    |    |    | X- | Coo | rdina | ıte |   |   |   |    |   |     |

| 1 | 1   | 0   | 1 |    |    |    |    |    |    | Y- | Coo | rdina | ite |   |   |   |    |   |     |

| 1 | 1   | 0   | 1 |    |    |    |    |    |    | X- | Coo | rdina | ite |   |   |   |    |   |     |

| 1 | 1   | 0   | 1 |    |    |    |    |    |    | Y- | Coo | rdina | ite |   |   |   |    |   |     |

2378 Drw 23

One IMG command and four PARM commands, used in sequence, specify a rectangular region of the I-buffer for transfer to or from the host processor. If the first coordinate pair specified in the PARM commands is above and to the left of the second coordinate pair, the orientation of the data remains the same. If not, the region will be flipped in one or both dimensions. For example, if the first coordinate pair has a smaller Y-coordinate than the second, the region will be flipped in the Y-dimension.

A 16-bit data transfer occurs when the PTRN command is used. The IMODE subcommand selects whether a transfer corresponds to one 16-bit pixel or 16 1-bit pixels.

TO

During a transfer from the host to the I-buffer in 16-pixel mode, specifies whether background pixels are overwritten with the background color or left undisturbed. 0 is overwritten (opaque); 1 is undisturbed (transparent).

RW

Specifies the direction of transfer. 0 is host to I-buffer; 1 is  $\dot{\text{I}}$ -buffer to host.

#### **PTRN Command**

|   | Сс           | omr | nano | Ė |    |    |    |    |    |    |   | Da    | ıta  |   |   |   |   |   |   |   |

|---|--------------|-----|------|---|----|----|----|----|----|----|---|-------|------|---|---|---|---|---|---|---|

| 3 |              | 2   | 1    | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0 | $oxed{oxed}$ | 0   | 0    | 0 |    |    |    |    |    |    |   | Pixel | Data | a |   |   |   |   |   |   |

2378 Drw 24

Transfers 16 bits of data between the host and the I-buffer. The direction of transfer is controlled by the IMG command.

#### **ADDR and PARM Commands**

| 0 | Comi | mano | t |    |    |     |    |    |       |       | Da   | ata   |       |       |   |   |   |   |   |

|---|------|------|---|----|----|-----|----|----|-------|-------|------|-------|-------|-------|---|---|---|---|---|

| 3 | 2    | 1    | 0 | 15 | 14 | 13  | 12 | 11 | 10    | 9     | 8    | 7     | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

| 1 | 0    | 1    | 0 |    |    |     |    |    | Addre | ess ( | Gene | rato  | r Sel | ectio | n |   |   |   |   |

| 1 | 1    | 0    | 1 |    |    | *** |    |    |       | X-    | Coo  | rdina | ate   |       |   |   |   |   |   |

| 1 | 1    | 0    | 1 |    |    |     |    |    | _     | Y-    | Coo  | rdina | ate   |       |   |   |   |   |   |

| 1 | 1    | 0    | 1 |    |    |     |    |    |       | X-    | Coo  | rdina | ate   |       |   |   |   |   |   |

| 1 | 1    | 0    | 1 |    |    |     |    |    |       | Y-    | Coo  | rdina | ate   |       |   |   |   |   |   |

2378 Drw 25

These commands are used, only in the two-chip address generator configuration, to transfer a rectangular region of memory between source and destination

A sequence of one ADDR command and four PARM commands is issued twice. The first sequence specifies a rectangular block of pixels in the source region of memory. The second sequence specifies a block in the destination region. After both sequences are issued, a transfer of pixels between source and destination occurs.

In each sequence, the ADDR command is issued first, with an address generator selection in its data field (0 for the source, 1 for the destination). Four PARM commands are then issued, with the coordinates for the rectangular region of memory in the data fields.

#### **PX Command**

|   | Comi | mano | t  |    |    |    |    |    |    |    | Da  | ıta   |     |   |   |   |   |   |   |

|---|------|------|----|----|----|----|----|----|----|----|-----|-------|-----|---|---|---|---|---|---|

| 3 | 2    | 1    | ٥. | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| 1 | 0    | 1    | 1  |    |    |    |    |    |    | X- | Coo | rdina | ate |   |   |   |   |   |   |

2378 Drw 26

Downloads an X-coordinate for the endpoints of a polyline, after an initial endpoint has been downloaded with the LX command. This value is a 13-bit unsigned integer. The value increases from the left to the right of the screen. The PX command is used only for 2-dimensional line drawing, in which I- and Z-values are not required.

## **Programming Examples**

The following sections are examples of command sequences sent to the TC8512. Each example is accompanied by an illustration of the function being executed.

| COMMAND    | DATA CONTENTS                                                                            |

|------------|------------------------------------------------------------------------------------------|

| AUX        | PMOD (polygon mode)                                                                      |

| PARM       | Gouraud Shading (=0)                                                                     |

| AUX        | ZCNT                                                                                     |

| PARM       | Z Buffer Y/N, Z Section Y/N                                                              |

| ı          | I value of Vertex #1                                                                     |

| Z          | Z value of Vertex #1                                                                     |

| Υ          | Y value of Vertex #1                                                                     |

| T1X<br>T2X | X value of Vertex #1 for Triangle (Mode 1)<br>X value of Vertex #1 for Triangle (Mode 2) |

| ı          | I value of Vertex #2                                                                     |

| Z          | Z value of Vertex #2                                                                     |

| Υ          | Y value of Vertex #2                                                                     |

| X          | X value of Vertex #2                                                                     |

|            |                                                                                          |

| •          |                                                                                          |

|            |                                                                                          |

| I          | I value of Vertex #(i-1)                                                                 |

| Z          | Z value of Vertex #(i-1)                                                                 |

| Y          | Y value of Vertex #(i-1)                                                                 |

| ×          | X value of Vertex #(i-1)                                                                 |

| ı          | I value of Vertex #i                                                                     |

| Z          | Z value of Vertex #i                                                                     |

| Y          | Y value of Vertex #i                                                                     |

| X          | X value of Vertex #i                                                                     |

2378 Pgm tbl 15

#### **Triangles with Gouraud Shading**

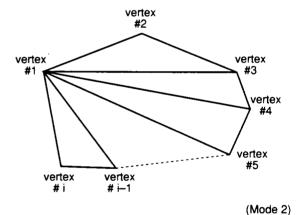

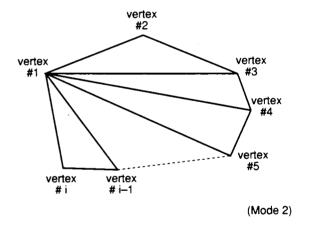

This example shows triangles in which an additional triangle can be defined by downloading an additional vertex. Either a T1X or T2X command may be used, to invoke either of two input modes, as shown below.

(Mode 1)

,

## **Triangles with Constant Shading**

This example shows triangles in which an additional triangle can be defined by downloading an additional

vertex. Either a T1X or T2X command may be used, to invoke either of two input modes, as shown below.

| COMMAND    | DATA CONTENTS                                                                            |

|------------|------------------------------------------------------------------------------------------|

| AUX        | PMOD (polygon mode)                                                                      |

| PARM       | Gouraud Shding (=1)                                                                      |

|            |                                                                                          |

| 1          | I value of Vertex #1                                                                     |

| Z          | Z value of Vertex #1                                                                     |

| Υ          | Y value of Vertex #1                                                                     |

| T1X<br>T2X | X value of Vertex #1 for Triangle (Mode 1)<br>X value of Vertex #1 for Triangle (Mode 2) |

| Y          | Y value of Vertex #2                                                                     |

| X          | X value of Vertex #2                                                                     |

| Υ          | Y value of Vertex #3                                                                     |

| X          | X value of Vertex #3                                                                     |

| Υ          |                                                                                          |

| X          |                                                                                          |

| Υ          | Y value of Vertex #(i-1)                                                                 |

| X          | X value of Vertex #(i-1)                                                                 |

| Z          | Z value of Vertex #i                                                                     |

| Y          | Y value of Vertex #i                                                                     |

| X          | X value of Vertex #i                                                                     |

vertex vertex vertex vertex vertex vertex #1 #3 #5 # (i-2) #i

vertex vertex vertex vertex vertex vertex vertex vertex #2 vertex #6 # (i-1)

-(Mode 1)

2378 Pgm tbl 16

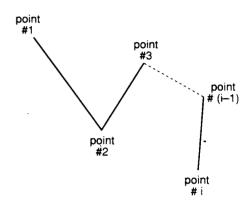

## **Line Drawing with Depth Cueing**

| COMMAND | DATA CONTENTS                        |

|---------|--------------------------------------|

| AUX     | LMOD (line drawing mode)             |

| PARM    | Depth Cueing (=2)                    |

| AUX     | ZCNT                                 |

| PARM    | Z Buffer Y/N, Z Section Y/N          |

|         |                                      |

|         |                                      |

|         |                                      |

| I       | I value of Point #1                  |

| Z       | Z value of Point #1                  |

| Y       | Y value of Point #1                  |

| LX      | X value of Point #1 for Line Drawing |

| I       | I value of Point #2                  |

| Z       | Z value of Point #2                  |

| Υ       | Y value of Point #2                  |

| Х       | X value of Point #2                  |

| AUX     | LSTA (line status)                   |

| PARM    | Polyline/Separate Line               |

| 1       | I value of Point #3                  |

| Ζ,      | Z value of Point #3                  |

| Y       | Y value of Point #3                  |

| ×       | X value of Point #3                  |

| AUX     | LSTA (line status)                   |

| PARM    | Polyline/Separate Line               |

2378 Fhd 17

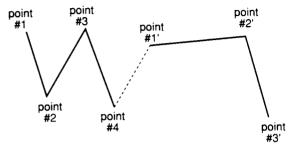

## 2-D Line Drawing

| COMMAND | DATA CONTENTS                         |

|---------|---------------------------------------|

| INIT    | System Configuration def. CT=0/1      |

| AUX     | LMOD (line drawing mode)              |

| PARM    | Line (Opaque = 0, Transparent = 1)    |

|         |                                       |

|         |                                       |

| ·       |                                       |

| Y       | Y value of Point #1                   |

| LX      | X value of Point #1 for Line Drawing  |

| AUX     | LSTA (line status)                    |

| PARM    | Polyline/Separate Line                |

| Y       | Y value of Point #2                   |

| PX      | X value of Point #2                   |

| Y       | Y value of Point #3                   |

| PX      | X value of Point #3                   |

| AUX     | LSTA (line status)                    |

| PARM    | Polyline/Separate Line                |

| Y       | Y value of Point #4                   |

| PX      | X value of Point #4                   |

| Y       | Y value of Point #1'                  |

| LX      | X value of Point #1' for Line Drawing |

| Y       | Y value of Point #2'                  |

| PX      | X value of Point #2'                  |

| Υ       | Y value of Point #3'                  |

| PX      | X value of Point #3'                  |

2378 Fhd 18

2378 Pgm tbl 18

## Image Data Transfer to and from Host Processor

| COMMAND | DATA CONTENTS                            |

|---------|------------------------------------------|

| AUX     | LMOD (image Data I/O)                    |

| PARM    | 16 pixel (=0), 1 pixel of 16bit (=1)     |

| AUX     | HCNT (Hardware Control Mode)             |

| PARM    | Read Modify Write (Y/N)                  |

| IMG     | Image data I/O, Opaque/Transparent       |

| PARM    | Square for Image Out x (x <sub>0</sub> ) |

| PARM    | Square for Image Out y (y <sub>0</sub> ) |

| PARM    | Square for Image Out x (x,)              |

| PARM    | Square for Image Out y (y,)              |

2378 Fhd 19

## 2-D Line Drawing

| COMMAND | DATA CONTENTS                         |

|---------|---------------------------------------|

| INIT    | System Configuration def. CT=0/1      |

| AUX     | LMOD (line drawing mode)              |

| PARM    | Line (Opaque = 0, Transparent = 1)    |

|         |                                       |

|         | ·                                     |

|         |                                       |

| Υ       | Y value of Point #1                   |

| LX      | X value of Point #1 for Line Drawing  |

| AUX     | LSTA (line status)                    |

| PARM    | Polyline/Separate Line                |

| Y       | Y value of Point #2                   |

| PX      | X value of Point #2                   |

| Y       | Y value of Point #3                   |

| PX      | X value of Point #3                   |

| AUX     | LSTA (line status)                    |

| PARM    | Polyline/Separate Line                |

| Y       | Y value of Point #4                   |

| PX      | X value of Point #4                   |

| Y       | Y value of Point #1'                  |

| LX      | X value of Point #1' for Line Drawing |

| Y       | Y value of Point #2'                  |

| PX      | X value of Point #2'                  |

| Y       | Y value of Point #3'                  |

| PX      | X value of Point #3'                  |

2378 Fhd 18

2378 Pgm tbl 18

## **Pin Descriptions**

### **Pin Designations**

The table shown below matches pin numbers to signal names. Note that different numbers are used for the

two package types. All VDD pins must be connected to the +5V power rail. All GND pins must be connected to ground.

| Pin No. (PGA) | Pin No. (QFP) | I/O     | Signal Name |

|---------------|---------------|---------|-------------|

| 1             | 144           | 3-STATE | DTOEI       |

| 2             | 3             | 0       | ADGD        |

| 3             | 6             | 1/0     | 115         |

| 4             | 8             | I/O     | l13         |

| 5             | 11            | 1/0     | l10         |

| 6             | 14            | 1/0     | 17          |

| 7             | 15            | I/O     | 16          |

| 8             | 17            | I/O     | 14          |

| 9             | 20            | I/O     | 13          |

| 10            | 21            | I/O     | 12          |

| 11            | 25            | 3-STATE | WEZ         |

| 12            | 27            | 1       | ZI15        |

| 13            | 28            | t       | ZI14        |

| 14            | 32            | 1       | ZI11        |

| 15            | 36            | ı       | Z17         |

| 16            | 39            | ı       | ZI5         |

| 17            | 42            | ı       | ZI2         |

| 18            | 44            | ı       | Z10         |

| 19 ,          | 47            | 1/0     | ZO13        |

| 20            | 50            | 1/0     | ZO10        |

| 21            | 51            | 1/0     | ZO9         |

| 22            | 53            | 1/0     | <b>Z</b> O7 |

| 23            | 56            | PWR     | VDD         |

| 24            | 57            | GND     | vss         |

| 25            | 61            | I/O     | ZO1         |

| 26            | 63            | 0       | REQ         |

| 27            | 64            | 0       | SYNO        |

| 28            | 67            | I/O     | PYEND       |

| 29            | 72            | 0       | AM          |

| 30            | 75            | 0       | XLEN        |

| 31            | 78            | 1       | RESET       |

| 32            | 80            | ı       | RDX         |

| 33            | 83            | 0       | IBSY        |

| 34            | 86            | 1/0     | DO          |

| 35            | 87            | 1/0     | D1          |

| 36            | 89            | 1/0     | D3          |

| 37         92         I/O         D4           38         93         I/O         D5           39         97         I/O         D9           40         99         I/O         D11           41         100         I/O         D12           42         104         I         A0           43         108         3-STATE         MA25           44         111         3-STATE         MA23           45         114         3-STATE         MA20           46         116         3-STATE         MA18           47         119         3-STATE         MA15           48         122         3-STATE         MA12           49         123         3-STATE         MA11           50         125         PWR         VDD           51         128         3-STATE         MA9           52         129         3-STATE         MA8           53         133         I/O         MA4           54         135         I/O         MA2           55         136         I/O         MA1           56         140         3-STATE <th>Pin No. (PGA)</th> <th>Pin No. (QFP)</th> <th>1/0</th> <th>Signal Name</th> | Pin No. (PGA) | Pin No. (QFP) | 1/0     | Signal Name |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------|-------------|

| 39   97   1/O   D9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37            | 92            | 1/0     | D4          |

| 40         99         I/O         D11           41         100         I/O         D12           42         104         I         A0           43         108         3-STATE         MA25           44         111         3-STATE         MA23           45         114         3-STATE         MA20           46         116         3-STATE         MA18           47         119         3-STATE         MA15           48         122         3-STATE         MA12           49         123         3-STATE         MA12           49         123         3-STATE         MA11           50         125         PWR         VDD           51         128         3-STATE         MA9           52         129         3-STATE         MA8           53         133         I/O         MA4           54         135         I/O         MA2           55         136         I/O         MA1           56         140         3-STATE         CAS           57         143         O         RD/WD           58         2 <t< td=""><td>38</td><td>93</td><td>1/0</td><td>D5</td></t<>                       | 38            | 93            | 1/0     | D5          |

| 41         100         I/O         D12           42         104         I         A0           43         108         3-STATE         MA25           44         111         3-STATE         MA23           45         114         3-STATE         MA20           46         116         3-STATE         MA18           47         119         3-STATE         MA15           48         122         3-STATE         MA12           49         123         3-STATE         MA12           49         123         3-STATE         MA11           50         125         PWR         VDD           51         128         3-STATE         MA9           52         129         3-STATE         MA8           53         133         I/O         MA4           54         135         I/O         MA2           55         136         I/O         MA1           56         140         3-STATE         CAS           57         143         O         RD/WD           58         2         I         WAIT           59         4                                                                                      | 39            | 97            | 1/0     | D9          |

| 42         104         I         A0           43         108         3-STATE         MA25           44         111         3-STATE         MA23           45         114         3-STATE         MA20           46         116         3-STATE         MA18           47         119         3-STATE         MA15           48         122         3-STATE         MA12           49         123         3-STATE         MA11           50         125         PWR         VDD           51         128         3-STATE         MA9           52         129         3-STATE         MA8           53         133         I/O         MA4           54         135         I/O         MA4           54         135         I/O         MA4           54         135         I/O         MA1           56         140         3-STATE         CAS           57         143         O         RD/WD           58         2         I         WAIT           59         4         O         ADGS           60         7         I/O                                                                                  | 40            | 99            | 1/0     | D11         |

| 43         108         3-STATE         MA25           44         111         3-STATE         MA23           45         114         3-STATE         MA20           46         116         3-STATE         MA18           47         119         3-STATE         MA15           48         122         3-STATE         MA12           49         123         3-STATE         MA11           50         125         PWR         VDD           51         128         3-STATE         MA9           52         129         3-STATE         MA9           53         133         I/O         MA4           54         135         I/O         MA2           55         136         I/O         MA1           56         140         3-STATE         CAS           57         143         O         RD/WD           58         2         I         WAIT           59         4         O         ADGS           60         7         I/O         I14           61         10         I/O         I9           63         16         I/O                                                                                  | 41            | 100           | 1/0     | D12         |

| 44         111         3-STATE         MA23           45         114         3-STATE         MA20           46         116         3-STATE         MA18           47         119         3-STATE         MA15           48         122         3-STATE         MA12           49         123         3-STATE         MA11           50         125         PWR         VDD           51         128         3-STATE         MA9           52         129         3-STATE         MA8           53         133         I/O         MA4           54         135         I/O         MA2           55         136         I/O         MA1           56         140         3-STATE         CAS           57         143         O         RD/WD           58         2         I         WAIT           59         4         O         ADGS           60         7         I/O         I14           61         10         I/O         I11           62         12         I/O         I9           63         16         I/O                                                                                        | 42            | 104           | 1       | <b>A</b> 0  |

| 45 114 3-STATE MA20 46 116 3-STATE MA18 47 119 3-STATE MA15 48 122 3-STATE MA12 49 123 3-STATE MA11 50 125 PWR VDD 51 128 3-STATE MA9 52 129 3-STATE MA8 53 133 I/O MA4 54 135 I/O MA2 55 136 I/O MA1 56 140 3-STATE CAS 57 143 O RD/WD 58 2 I WAIT 59 4 O ADGS 60 7 I/O I14 61 10 I/O I11 62 12 I/O I9 63 16 I/O I5 64 22 I/O I1 65 23 I/O I0 66 26 3-STATE WEI 67 29 I ZI13 68 31 I ZI12 69 35 I ZIB 70 38 I ZI6 71 40 I ZI4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 43            | 108           | 3-STATE | MA25        |