# **FEATURES**

# ■ 64-bit graphics engine with integrated 3D game acceleration

- Perspective textures mapping

- FilterJet™ fast bilinear filtering

- Lit, copy, decal, and blend textures

- Palettized textures (compressed textures)

- Mono rasterization (single-pass lighting)

- Stipple transparency

- Rendering of points, lines, and triangles

- 16-bit Z-buffer

- Gouraud shading

- Alpha blending, fog, and transparency

- Display list processing for maximum performance

- Texture mirroring and clamping

- 3D-clipping support

- Texture composition

- Full RGB specular lighting

# ■ High-performance 64-bit GUI accelerator

- Hardware clipping

- Three-operand BitBLT (bit boundary block transfer)

- Color expansion for 8-, 16-, 24-, and 32-bpp modes

- Stretch BitBLT

#### ■ AGP 1.0/PCI v2.1-compliant 66-MHz bus master

- DMA maximizes system performance

- Host-rendered/cached texture maps

# **■** TV output

Digital output to support next generation of TV encoders

#### ■ Integrated VGA controller

(cont.)

# High-Performance 3D AGP Graphics Accelerator

# **OVERVIEW**

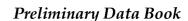

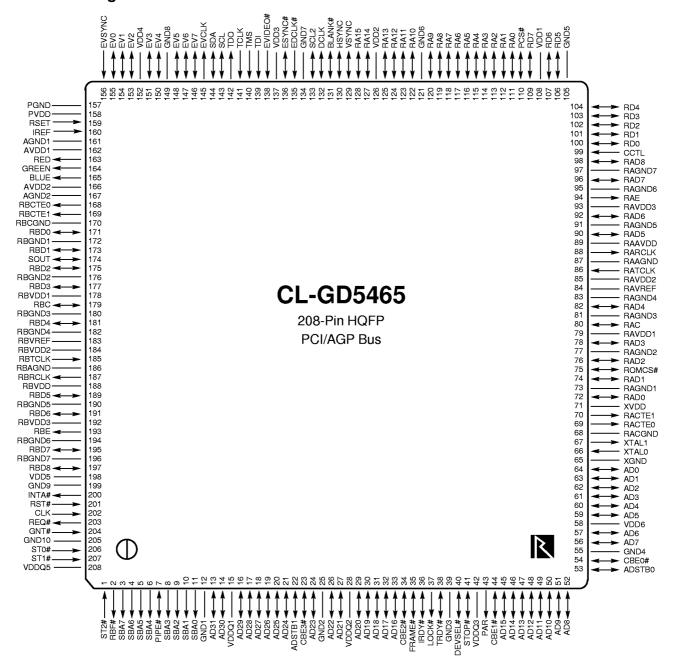

The CL-GD5465 is the third generation of the Laguna™ family of Rambus®-based 2D/3D graphics accelerators. The CL-GD5465 supports Intel® AGP (accelerated graphics port) and Microsoft® Direct3D™, enabling arcade-level 3D game play on desktop computers. In addition to superior 3D capabilities, the CL-GD5465 also offers a high level of 2D performance and video quality.

Based on TextureJet™ technology, the CL-GD5465 offers highly efficient hardware texture-map management. An AGP interface further enhances the texture management by providing high bandwidth between the system memory and the graphics subsystem. The CL-GD5465 is designed to optimize Microsoft Direct3D performance. This device is also compatible with other 3D game APIs on the market.

The CL-GD5465 integrates a 3D engine, a 2D engine, a 24-bpp palette RAMDAC, clock

(cont.)

Version 2.0 May 1997

# FEATURES (cont.)

#### ■ Video playback acceleration

- Single-pass X, Y interpolated scaling

- Hardware occlusion for three video windows

- YUV-to-RGB conversion

- Color and chroma key

- Single overlay window

# ■ Rambus<sup>®</sup> memory architecture

- Concurrent and low-latency devices supported

- Single memory for color-buffer, video, Z-buffer, and texture store

- 600 Mbytes/sec.

#### ■ MPEG-2/DVD acceleration

- DMA bursting

- Support for planar YUV 4:2:0 frees CPU of conversion burden

- Advanced hardware de-interlacing

#### ■ V-Port<sup>™</sup> for peripheral expansion

- MPEG-2 decoder

- TV tuner

- Teleconferencing

#### ■ Integrated 230-MHz palette DAC and clock synthesizer

- Supports resolutions up to  $1600 \times 1200$  at 85 Hz

- True-color operation up to  $1024 \times 768$

- Hardware cursor

- Microsoft® PC 97 and NEC 98—compliant architecture

# **OVERVIEW** (cont.)

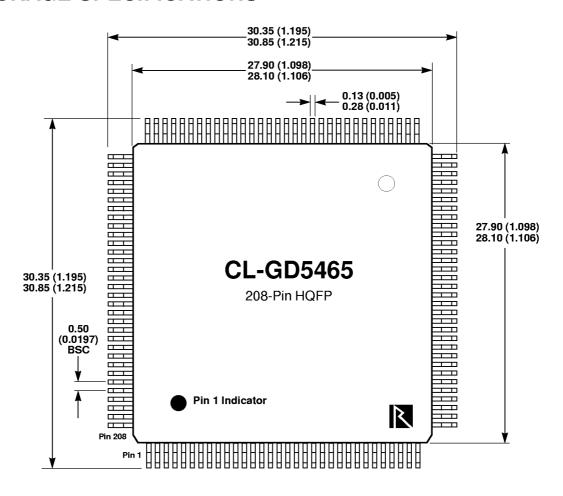

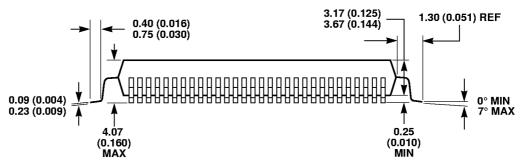

generators, a V-Port™ bus, and digital TV-out circuits in a standard 208-pin HQFP package. The RAM-DAC can operate at 230 MHz, allowing 1600 × 1200 resolution at 85-Hz refresh. The 3D engine features single-pass rendering capability, CPU-independent local display list processing, CPU-independent multi-buffer support, and OpenGL™ support. The 2D engine is based on previous Laguna family members and offers performance and feature enhancements.

The V-Port, GPIO, and I<sup>2</sup>C bus interfaces provide a glueless connection to external devices to play back disk-based video files (including MPEG-2) and to provide TV-in-a-window, closed captioned, Intercast™, and video conferencing.

The CL-GD5465 is a single-channel device with bandwidth of 600 Mbytes per second. While maintaining the same pin layout, future Laguna family members will use two Rambus channels to increase the bandwidth to 1.3 Gbytes per second.

#### APPLICATIONS SUPPORT

- Technical reference manuals and design kit complete data book, electrical specifications, register set definitions, pin descriptions, reference designs, and applications information.

- BIOS and driver release kits contains user guides, PDR (problem description report) forms, source code license agreement, and quality assurance procedures.

- PCI board evaluation kit adapter card including CL-GD5465, on-board BIOS, and 2-Mbyte RDRAM shipped with complete design package (schematics, Gerber® files) and software drivers.

#### **■** Electronic information services

- ftp: ftp.cirrus.com

- World Wide Web: http://www.cirrus.com/

- BBS: (510) 440-9080

- Fax-on-demand: (510) 249-4200

#### LOCALIZATION

- Simplified Chinese

- Traditional Chinese

- Czech

- Danish

- Dutch

- Finnish

- French

- German■ Hungarian

- Italian

- Japanese

- Korean

- Norwegian

- Polish

- Brazilian Portuguese

- Portuguese

- **■** Russian

- Latin AmericanSpanish

- Spanish

- Swedish

- Thai

D1-2 FEATURES/OVERVIEW PRELIMINARY DATA BOOK v2.0 May 1997

# SOFTWARE DRIVERS SUPPORT

Cirrus Logic provides an extensive and expanding range of software drivers to enhance the resolution and performance of many software packages. The following table lists the Cirrus Logic software drivers for the CL-GD5465.

| Software Drivers                                                                       | Resolution Supported                                       | No. of Colors         |

|----------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------|

| Microsoft® Windows®,                                                                   | 640 × 480, 800 × 600, 1024 × 768, 1280 × 1024, 1600 × 1200 | 256 (8 bit)           |

| Microsoft® DCI Provider (display control interface),                                   | 640 × 480, 800 × 600, 1024 × 768, 1280 × 1024              | 65,536 (16 bit)       |

| Microsoft <sup>®</sup> Windows <sup>®</sup> 95,<br>Microsoft <sup>®</sup> DirectDraw™, | 640 × 480, 800 × 600, 1024 × 768                           | 16.8 million (24 bit) |

| Microsoft® Direct3D™                                                                   | 640 × 480, 800 × 600, 1024 × 768                           | 16.8 million (32 bit) |

|                                                                                        | 640 × 480, 800 × 600, 1024 × 768, 1280 × 1024, 1600 × 1200 | 256 (8 bit)           |

| Microsoft® Windows NT™                                                                 | 640 × 480, 800 × 600, 1024 × 768, 1280 × 1024              | 65,536 (16 bit)       |

| Wilcrosoft® Williams IN I III                                                          | 640 × 480, 800 × 600, 1024 × 768                           | 16.8 million (24 bit) |

|                                                                                        | 640 × 480, 800 × 600, 1024 × 768                           | 16.8 million (32 bit) |

| AutoCAD®,                                                                              | 640 × 480, 800 × 600, 1024 × 768, 1280 × 1024, 1600 × 1200 | 256 (8 bit)           |

| AutoShade® with Renderman™,                                                            | 640 × 480, 800 × 600, 1024 × 768, 1280 × 1024              | 65,536 (16 bit)       |

| 3D Studio™,<br>  MicroStation®                                                         | 640 × 480, 800 × 600, 1024 × 768                           | 16.8 million (24 bit) |

| OC/0® - 2 W                                                                            | 640 × 480, 800 × 600, 1024 × 768, 1280 × 1024              | 256 (8 bit)           |

| OS/2 <sup>®</sup> v3.x, Warp                                                           | 640 × 480, 800 × 600, 1024 × 768                           | 65,536 (16 bit)       |

| VPM™<br>(video port manager)                                                           | Resolution-independent                                     | _                     |

| Apple™ PowerMAC®                                                                       | 640 × 480, 800 × 600, 1024 × 768, 1280 × 1024              | 16.8 million          |

# **BIOS SUPPORT**

- Fully IBM® VGA-compatible BIOS

- VBE (VESA® BIOS Extension) v2.0 support

- AGP/PCI support

- DPMS (display power management signaling) and DDC2B support in ROM

- Plug-and-play support

# **UTILITIES**

- Manufacturing test

- Video-mode configuration utility: CLMODE

- Configured OEM system integration: OEMSI

- Resolution switching utility: WINMODE

- RAMBIOS utility

- Screen centering utility

- Register editor and viewer

# **TABLE OF CONTENTS**

| 1.       | PIN INFORMATION               | D1-5  | 3.2.6      | V-Port™                                        | D1-23         |

|----------|-------------------------------|-------|------------|------------------------------------------------|---------------|

| 1.1      | Pin Diagram — PCI/AGP Bus     |       | 3.2.7      | RAMDAC                                         | D1-23         |

| 1.2      | Pin Summary                   |       | 3.2.8      | Video Pipeline                                 | D1-23         |

| 1.2.1    | Host Interface Pins           | D1-6  | 3.2.9      | Programmable Frequency Synthesize              | r D1-23       |

| 1.2.2    | ROM/VMI Interface             | D1-7  | 3.2.10     | O CRT Controller                               | D1-23         |

| 1.2.3    | Rambus® Pins                  | D1-8  | 3.2.1      | 1 I <sup>2</sup> C Ports                       | D1-23         |

| 1.2.4    | Monitor Pins                  | D1-9  | 3.2.12     | 2 VMI v1.4                                     | D1-23         |

| 1.2.5    | TV Output Pins                | D1-10 | 3.3        | Functional Operation                           | D1-23         |

| 1.2.6    | Boundary Scan Pins            | D1-10 | 3.3.1      | 2D Graphics Engine                             | D1-23         |

| 1.2.7    | Clock Pins                    | D1-11 | 3.3.2      | 3D Graphics                                    | D1-24         |

| 1.2.8    | Power and Ground Pins         | D1-11 | 3.3.3      | Display Refresh                                | D1-24         |

| 2.       | DETAILED PIN                  |       | 3.3.4      | Playback and Capture by the V-Port™            | D1-24         |

| <b>-</b> | DESCRIPTIONS                  | D1-12 | 3.3.5      | Playback by the Host Bus                       | D1-24         |

| 2.1      | PCI/AGP Pins                  |       | 3.3.6      | I <sup>2</sup> C (DDC/External Device Control) | D1-24         |

| 2.2      | ROM/VMI Pins                  |       | 3.3.7      | BIOS Read                                      |               |

| 2.3      | Rambus® Pins                  |       | 3.4        | Performance Notes                              |               |

| 2.3.1    | Rambus® Channel A             |       | 3.5        | Compatibility                                  |               |

| 2.3.2    | Rambus® Channel B             | D1-17 | 3.6        | Board Testability                              | D1-25         |

| 2.4      | Monitor Pins                  |       | 4.         | CONFIGURATION TABLES                           | D1-26         |

| 2.5      | TV Output Pins                | D1-18 | 4.1        | Video Modes                                    | D1-26         |

| 2.6      | Boundary Scan Pins            | D1-19 | 4.2        | Power-Up Configuration                         | D1-30         |

| 2.7      | Clock Pins                    |       | 5.         | VGA REGISTER I/O MAP                           | D1-33         |

| 2.8      | Power and Ground Pins         | D1-19 |            |                                                |               |

| 3.       | <b>FUNCTIONAL DESCRIPTION</b> | D1-21 | 6.         | ELECTRICATIONS                                 | D1 24         |

| 3.1      | General                       | D1-21 | 0.4        | SPECIFICATIONS                                 |               |

| 3.2      | Functional Blocks             | D1-22 | 6.1<br>6.2 | Absolute Maximum Ratings                       |               |

| 3.2.1    | Host Interface                | D1-22 | 6.3        | DC Specifications                              |               |

| 3.2.2    | 2D Graphics Engine            | D1-22 | 6.4        | List of Timings                                |               |

| 3.2.3    | 3D Graphics Engine            | D1-22 |            |                                                |               |

| 3.2.4    | Memory Controller (Rambus®)   | D1-22 | 7.         | PACKAGE SPECIFICATIONS                         | ປາ-4 <i>/</i> |

| 325      | VGA Core                      | D1-22 | Ω          | ORDERING INFORMATION                           | D1_//2        |

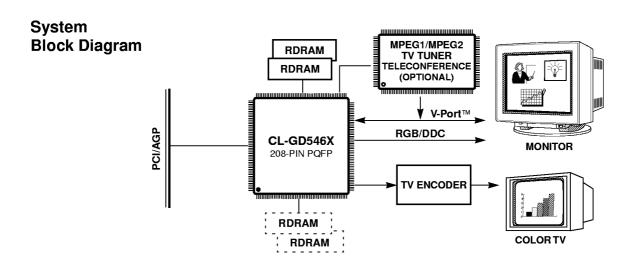

# 1. PIN INFORMATION

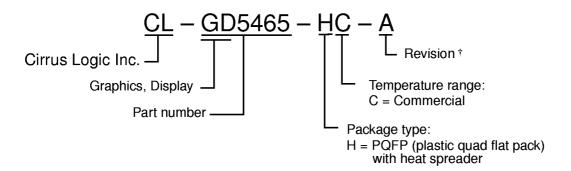

The CL-GD5465 is available in a 208-pin high-performance quad-flat pack device for the PCI/AGP bus interface.

# 1.1 Pin Diagram — PCI/AGP Bus

# 1.2 Pin Summary

The following tables list each CL-GD5465 pin by name, functional pin type, and number(s). Functional pin types are abbreviated as follows:

| Туре            | Abbreviation |

|-----------------|--------------|

| Input           | I            |

| Output          | 0            |

| Input/output    | I/O          |

| Tristate output | TS           |

| Power           | PWR          |

| Туре           | Abbreviation                     |

|----------------|----------------------------------|

| Ground         | GND                              |

| Open collector | ОС                               |

| ·_,            | Indicates ascending pin numbers  |

|                | Indicates descending pin numbers |

| <b>'#'</b>     | Indicates active-low             |

# 1.2.1 Host Interface Pins

Table 1-1. Host Interface — PCI Bus

| Name           | Туре | Pull-up | I <sub>OH</sub> (mA) | I <sub>OL</sub> (mA) | Load (pF) | Pin Number(s)                                          |

|----------------|------|---------|----------------------|----------------------|-----------|--------------------------------------------------------|

| RST#           | I    | -       | -                    | -                    | -         | 201                                                    |

| CLK            | I    | -       | -                    | -                    | -         | 202                                                    |

| GNT#           | I    | -       | -                    | -                    | -         | 204                                                    |

| PAR            | 0    | -       | -2                   | 8                    | 50        | 43                                                     |

| REQ#           | 0    | -       | -                    | -                    | -         | 203                                                    |

| INTA#          | TS   | -       | -2                   | 8                    | 50        | 200                                                    |

| FRAME#         | I/O  | -       | -2                   | 8                    | 50        | 35                                                     |

| IRDY#          | I/O  | -       | -2                   | 8                    | 50        | 36                                                     |

| TRDY#          | I/O  | -       | -2                   | 8                    | 50        | 38                                                     |

| DEVSEL#        | I/O  | -       | -2                   | 8                    | 50        | 40                                                     |

| STOP#          | I/O  | -       | -2                   | 8                    | 50        | 41                                                     |

| AD[31:0]       | I/O  | -       | -2                   | 8                    | 50        | 13–14, 16–21, 24, 26–27, 29–33,<br>45–52, 56–57, 59–64 |

| CBE[3:0]#      | I/O  | -       | -2                   | 8                    | 50        | 23, 34, 44, 54                                         |

| ADSTB1 (IDSEL) | I/O  | -       | -2                   | 8                    | 50        | 22                                                     |

| ADSTB0         | I/O  | -       | -2                   | 8                    | 50        | 53                                                     |

| LOCK#          | 0    | -       | -2                   | 8                    | 50        | 37                                                     |

| ST[2:0]#       | I    | _       | _                    | _                    | _         | 1, 207, 206                                            |

| RBF#           | 0    | -       | -2                   | 8                    | 50        | 2                                                      |

| SBA[7:0]       | 0    | _       | -2                   | 8                    | 50        | 3–6, 8–11                                              |

| PIPE#          | I/O  | _       | -2                   | 8                    | 50        | 7                                                      |

D1-6 PIN INFORMATION PRELIMINARY DATA BOOK v2.0 May 1997

# 1.2.2 ROM/VMI Interface

These pins are used for the BIOS ROM interface, as a connection to a VMI v1.4 peripheral, or as the interface to the VGA feature connector.

Table 1-2. ROM/VMI Interface

| ROM     | ∨мі                | Feature<br>Connector | Test<br>Output | Туре | Pull-<br>up | I <sub>OH</sub> | I <sub>OL</sub> | Load (pF) | Pin<br>Number(s) |

|---------|--------------------|----------------------|----------------|------|-------------|-----------------|-----------------|-----------|------------------|

| EVIDEO# | VACTIVE            | EVIDEO#              | -              | ı    | -           | _               | _               | -         | 138              |

| ESYNC#  | _                  | ESYNC#               | _              | I/O  | _           | -4              | 8               | 50        | 136              |

| EDCLK#  | VREF               | EDCLK#               | _              | ı    | -           | _               | _               | -         | 135              |

| SCL2    | I2CCLK             | -                    | -              | 1/0  | -           | -               | 8               | -         | 133              |

| DCLK    | PIXCLK             | DCLK                 | _              | 1/0  | _           | -4              | 8               | 50        | 132              |

| BLANK#  | HREF               | BLANK#               | _              | 1/0  | _           | -4              | 8               | 50        | 131              |

| HSYNCa  | _                  | HSYNC                | _              | I/O  | _           | -4              | 8               | 50        | 130              |

| VSYNC   | _                  | VSYNC                | _              | I/O  | _           | -4              | 8               | 50        | 129              |

| RA15    | I2CDAT             | _                    | _              | I/O  | _           | _               | 8               | 50        | 128              |

| RA14    | VID0               | P0                   | T24            | I/O  | _           | -4              | 8               | 50        | 127              |

| RA13    | VID1               | P1                   | T25            | I/O  | _           | -4              | 8               | 50        | 125              |

| RA12    | VID2               | P2                   | T26            | I/O  | _           | -4              | 8               | 50        | 124              |

| RA11    | VID3               | P3                   | T27            | I/O  | _           | -4              | 8               | 50        | 123              |

| RA10    | VID4               | P4                   | T28            | I/O  | _           | -4              | 8               | 50        | 122              |

| RA9     | VID5               | P5                   | T29            | I/O  | _           | -4              | 8               | 50        | 120              |

| RA8     | VID6               | P6                   | T30            | I/O  | _           | -4              | 8               | 50        | 119              |

| RA7     | VID7               | P7                   | T31            | I/O  | _           | -4              | 8               | 50        | 118              |

| RA6     | DS# or RD#         | _                    | Т8             | I/O  | _           | -4              | 8               | 50        | 117              |

| RA5     | R/W# or WR#        | _                    | Т9             | I/O  | _           | -4              | 8               | 50        | 116              |

| RA4     | DTACK# or<br>READY | -                    | T10            | I/O  | -           | -4              | 8               | 50        | 115              |

| RA3     | HA3                | -                    | T11            | I/O  | -           | -4              | 8               | 50        | 114              |

| RA2     | HA2                | -                    | T12            | 1/0  | _           | -4              | 8               | 50        | 113              |

| RA1     | HA1                | _                    | T13            | I/O  | _           | -4              | 8               | 50        | 112              |

| RA0     | HA0                | _                    | T14            | I/O  | _           | -4              | 8               | 50        | 111              |

| PCS#    | CS#                | _                    | T15            | I/O  | _           | -4              | 8               | 50        | 110              |

| RD7     | HD7                | _                    | T7             | I/O  | _           | -4              | 8               | 50        | 109              |

| RD6     | HD6                | _                    | T6             | I/O  | _           | -4              | 8               | 50        | 107              |

| RD5     | HD5                | _                    | T5             | I/O  | _           | -4              | 8               | 50        | 106              |

**Table 1-2. ROM/VMI Interface** (cont.)

| ROM    | VMI | Feature<br>Connector | Test<br>Output | Туре | Pull-<br>up | Іон | l <sub>OL</sub> | Load (pF) | Pin<br>Number(s) |

|--------|-----|----------------------|----------------|------|-------------|-----|-----------------|-----------|------------------|

| RD4    | HD4 | _                    | T4             | I/O  | _           | -4  | 8               | 50        | 104              |

| RD3    | HD3 | _                    | Т3             | I/O  | _           | -4  | 8               | 50        | 103              |

| RD2    | HD2 | _                    | T2             | I/O  | _           | -4  | 8               | 50        | 102              |

| RD1    | HD1 | _                    | T1             | I/O  | _           | -4  | 8               | 50        | 101              |

| RD0    | HD0 | _                    | T0             | I/O  | _           | -4  | 8               | 50        | 100              |

| ROMCS# | _   | _                    | _              | I/O  | _           | -4  | 8               | 50        | 75               |

a HSYNC and VSYNC are also listed in Table 1-5.

#### 1.2.3 Rambus® Pins

The CL-GD5465 has only one Rambus Channel — Rambus Channel A. Rambus Channel B pins are reserved for future Laguna family members, and are not implemented on the CL-GD5465. The Rambus Channel pins, including SOUT, are not 5-V tolerant. See Section 6.2 on page 35 for restrictions.

Table 1-3. Rambus® Channel A Pins

| Name     | Туре | Pin Number(s)                      |

|----------|------|------------------------------------|

| RAD[8:0] | I/O  | 98, 96, 92, 90, 82, 78, 76, 74, 72 |

| RARCLK   | 0    | 88                                 |

| RATCLK   | I    | 86                                 |

| RACTE1   | 0    | 70                                 |

| RACTE0   | 0    | 69                                 |

| RAC      | I/O  | 80                                 |

| RAE      | 0    | 94                                 |

| RAVREF   | ı    | 84                                 |

| CCTL     | I    | 99                                 |

D1-8 PIN INFORMATION PRELIMINARY DATA BOOK v2.0 May 1997

Rambus Channel B pins are not implemented on the CL-GD5465 (except SOUT, pin 174), but are reserved for future Laguna family members.

Table 1-4. Rambus® Channel B Pins

| Name     | Туре | Pin Number(s)                               |

|----------|------|---------------------------------------------|

| RBD[8:0] | I/O  | 197, 195, 191, 189, 181, 177, 175, 173, 171 |

| RBRCLK   | 0    | 187                                         |

| RBTCLK   | ı    | 185                                         |

| RBCTE1   | 0    | 169                                         |

| RBCTE0   | 0    | 168                                         |

| RBC      | I/O  | 179                                         |

| RBE      | 0    | 193                                         |

| RBVREF   | ı    | 183                                         |

| SOUT     | I/O  | 174 (not 5-V tolerant, see Section 6.2)     |

# 1.2.4 Monitor Pins

The following pins connect to the DB15 monitor connector. The two control pins for the DACs are included.

Table 1-5. Monitor Pins

| Name   | Туре | Pull-up <sup>a</sup> | I <sub>OH</sub> (mA) | I <sub>OL</sub> (mA) | Load (pF) | Pin Number(s) |

|--------|------|----------------------|----------------------|----------------------|-----------|---------------|

| RED    | 0    | -                    |                      |                      |           | 163           |

| GREEN  | 0    | -                    |                      | Analog out           | out       | 164           |

| BLUE   | 0    | _                    |                      |                      | 165       |               |

| RSET   | I    | _                    | _                    | _                    | _         | 159           |

| IREF   | I    | _                    | _                    | _                    | _         | 160           |

| HSYNCa | I/O  | 250K                 | -4                   | 8                    | 50        | 130           |

| VSYNC  | I/O  | 250K                 | -4                   | 8                    | 50        | 129           |

| SDA    | I/O  | -                    | -                    | 8                    | 50        | 144           |

| SCL    | I/O  | _                    | _                    | 8                    | 50        | 143           |

<sup>&</sup>lt;sup>a</sup> HSYNC and VSYNC are also listed in Table 1-2.

# 1.2.5 TV Output Pins

These pins interface to the CL-GD1052/GD1053 TV encoder. A strapping option allows EV[7:0] to be redefined as P[7:0]. This option precludes their use as TV outputs.

Table 1-6. TV Output Pins

| Name   | Pixel<br>Bus | Test<br>Output | Туре | Pull-up <sup>a</sup> | I <sub>OH</sub> (mA) | I <sub>OL</sub> (mA) | Load (pF) | Pin<br>Number(s) |

|--------|--------------|----------------|------|----------------------|----------------------|----------------------|-----------|------------------|

| EVCLK  | -            | _              | 0    | -                    | -4                   | 8                    | 50        | 145              |

| EV7    | P7           | T23            | I/O  | _                    | -4                   | 8                    | 50        | 146              |

| EV6    | P6           | T22            | I/O  | -                    | -4                   | 8                    | 50        | 147              |

| EV5    | P5           | T21            | I/O  | -                    | -4                   | 8                    | 50        | 148              |

| EV4    | P4           | T20            | I/O  | -                    | -4                   | 8                    | 50        | 150              |

| EV3    | P3           | T19            | I/O  | -                    | -4                   | 8                    | 50        | 151              |

| EV2    | P2           | T18            | I/O  | -                    | -4                   | 8                    | 50        | 153              |

| EV1    | P1           | T17            | I/O  | _                    | -4                   | 8                    | 50        | 154              |

| EV0    | P0           | T16            | I/O  | -                    | -4                   | 8                    | 50        | 155              |

| EVSYNC | -            | _              | l    | _                    | _                    | _                    | _         | 156              |

# 1.2.6 Boundary Scan Pins

The boundary scan (IEEE 1149.1) is not implemented on the CL-GD5465. These pins should be 'no connects'.

Table 1-7. Boundary Scan Pins

| Name | Туре | Pull-up | I <sub>OH</sub> (mA) | I <sub>OL</sub> (mA) | Load<br>(pF) | Pin Number(s) |

|------|------|---------|----------------------|----------------------|--------------|---------------|

| TDI  | I    | _       | _                    | -                    | -            | 139           |

| TMS  | ı    | _       | -                    | _                    | _            | 140           |

| TCLK | I    | _       | _                    | _                    | _            | 141           |

| TDO  | 0    | _       | -4                   | 8                    | 50           | 142           |

D1-10 PIN INFORMATION PRELIMINARY DATA BOOK v2.0 May 1997

# 1.2.7 Clock Pins

Table 1-8. Clock Pins

| Name         | Туре | Pull-up | I <sub>OH</sub> (mA) | I <sub>OL</sub> (mA) | Load<br>(pF) | Pin Number(s) |

|--------------|------|---------|----------------------|----------------------|--------------|---------------|

| XTAL0 (RCLK) | I    | _       | _                    | _                    | -            | 66            |

| XTAL1        | 0    | _       | _                    | _                    | _            | 67            |

# 1.2.8 Power and Ground Pins

Table 1-9. Power and Ground Pins

| Name         | Туре                                             | Pin Number(s)                                |

|--------------|--------------------------------------------------|----------------------------------------------|

| VDD[6:1]     | Digital power (core logic)                       | 198, 152, 137, 126, 108, 58                  |

| VDDQ[5, 3:1] | Digital power (AGP I/O)                          | 208, 42, 28, 15                              |

| RAVDD[3:1]   | Digital power (Rambus Channel A interface cell)  | 93, 85, 79                                   |

| RAAVDD       | Analog power (Rambus Channel A interface cell)   | 89                                           |

| RBVDD[3:1]   | Digital power (Rambus Channel B interface cell)  | 192, 184, 178                                |

| RBAVDD       | Analog power (Rambus Channel B interface cell)   | 188                                          |

| XVDD         | Power (Reference oscillator and Rambus PLL)      | 71                                           |

| PVDD         | Power (VCLK PLL)                                 | 158                                          |

| AVDD[2:1]    | Power (DACs)                                     | 166, 162                                     |

| GND[10:1]    | Digital ground (core logic and I/O)              | 205, 199, 149, 134, 121, 105, 55, 39, 25, 12 |

| RAGND[7:1]   | Digital ground (Rambus Channel A interface cell) | 97, 95, 91, 83, 81, 77, 73                   |

| RAAGND       | Analog ground (Rambus Channel A interface cell)  | 87                                           |

| RACGND       | Ground (Rambus Channel A ClockToEnd drivers)     | 68                                           |

| RBGND[7:1]   | Digital ground (Rambus Channel B interface cell) | 196, 194, 190, 182, 180, 176, 172            |

| RBAGND       | Analog ground (Rambus Channel B interface cell)  | 186                                          |

| RBCGND       | Ground (Rambus Channel B ClockToEnd drivers)     | 170                                          |

| XGND         | Ground (Reference oscillator and Rambus PLL)     | 65                                           |

| PGND         | Ground (VCLK PLL)                                | 157                                          |

| AGND[2:1]    | Ground (DACs)                                    | 167, 161                                     |

# **DETAILED PIN DESCRIPTIONS**

The following tables provide a detailed description of each CL-GD5465 pin by name and functional type. Functional pin types are abbreviated as follows:

| Туре            | Abbreviation |

|-----------------|--------------|

| Input           | I            |

| Output          | 0            |

| Input/output    | I/O          |

| Tristate output | TS           |

| Power           | PWR          |

| Туре           | Abbreviation                     |

|----------------|----------------------------------|

| Ground         | GND                              |

| Open collector | ОС                               |

| ·'             | Indicates ascending pin numbers  |

| ÷              | Indicates descending pin numbers |

| <b>'#'</b>     | Indicates active-low             |

# 2.1 PCI/AGP Pins

Table 2-1. Host Interface — PCI/AGP Bus

| Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

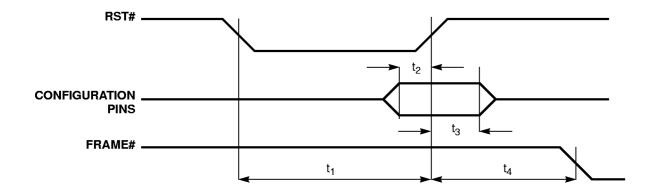

| RST#   | I    | System Reset #: This active-low input initializes the CL-GD5465 to a known state. Configuration bits are loaded on the rising (trailing) edge of this signal. The Subsystem ID registers are loaded from the BIOS ROM after the trailing edge of this signal.                                                                                                                                                                |

| CLK    | ı    | <b>PCI Bus Clock:</b> This is the bus timing reference for the CL-GD5465. All synchronous PCI bus activity is referenced to the rising edge of this clock.                                                                                                                                                                                                                                                                   |

| GNT#   | ı    | <b>Bus Grant #:</b> This active-low input indicates the arbiter has determined that the CL-GD5465 can become master of the PCI bus.                                                                                                                                                                                                                                                                                          |

| PAR    | TS   | <b>Parity:</b> This pin provides even parity across AD[31:0] and CBE[3:0]#. The CL-GD5465 asserts correct parity when it drives the bus. The CL-GD5465 does not check parity. Correct parity is asserted by the CL-GD5465 (as a target) in the data phase of reads. When the CL-GD5465 is a bus master, it provides correct parity in the address phase and for writes in the data phase.                                    |

| LOCK#  | 0    | LOCK #: This pin indicates an atomic operation that may require multiple transactions to complete.                                                                                                                                                                                                                                                                                                                           |

| REQ#   | 0    | Bus Request #: This active-low output requests mastership of the PCI bus.                                                                                                                                                                                                                                                                                                                                                    |

| INTA#  | TS   | Interrupt Request #: This active-low output indicates that the CL-GD5465 has an interrupt pending. See register CR11 for a description of the controls for this pin. This pin is functionally an open-drain output driver. INTA# can be tied directly to ground if interrupts are not required. In this case, the CL-GD5465 does not claim an interrupt.                                                                     |

| FRAME# | I/O  | <b>Cycle Frame #:</b> This pin is driven by the current master to indicate the beginning and duration of an access. When the CL-GD5465 is a bus master, this output is a sustained tristate as defined in the PCI specification. FRAME# is asserted to indicate the beginning of a bus transaction. While FRAME# is asserted, data transfers continue. The transaction is in its final data phase when FRAME# is deasserted. |

| IRDY#  | I/O  | Initiator Ready #: This pin indicates the initiating agent's ability to complete the current data phase. When the CL-GD5465 is a bus master, this output is a sustained tristate as defined in the PCI specification. A data phase is completed on any clock cycles that IRDY# and TRDY# are both asserted.                                                                                                                  |

D1-12 May 1997 PRELIMINARY DATA BOOK v2.0

Table 2-1.

Host Interface — PCI/AGP Bus (cont.)

| Name              | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                           |                                                                                                              |  |

|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| TRDY#             | I/O  | <b>Target Ready #:</b> This pin indicates the target agent's ability to complete the current data phase. This output is a sustained tristate as defined in the PCI specification. This pin is an input for palette snooping when the CL-GD5465 is a target. When the CL-GD5465 is a bus master, this pin is an input.                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                           |                                                                                                              |  |

| DEVSEL#           | I/O  | <b>Device Select #:</b> This output is driven active-low when the CL-GD5465 has decoded its address as the target of the current access. This output is a sustained tristate as defined in the PCI specification. This pin is an input for palette snooping when the CL-GD5465 is a target. When the CL-GD5465 is a bus master, this pin is an input.                                                                                                                  |                                                                                                                                                                                                                                                                                                                           |                                                                                                              |  |

| STOP#             | I/O  | tion. This output is a sustained                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Stop #:</b> This active-low output indicates a request to the bus master to stop the current transaction. This output is a sustained tristate as defined in the PCI specification. This pin is an input for palette snooping when the CL-GD5465 is a target. When the CL-GD5465 is a bus master, this pin is an input. |                                                                                                              |  |

| AD[31:0]          | I/O  | Address/Data: These multiplexed and bidirectional pins are used to transfer system address and data during any memory or I/O operation. During the first clock of a transaction, these pins contain a 32-bit physical byte address. During subsequent clocks, they contain data.                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                           |                                                                                                              |  |

| CBE[3:0]#         | I/O  | Command/Byte Enable #: These multiplexed pins are used to transfer the bus command and the byte enables. During the address phase of the operation, CBE[3:0]# define the bus command (refer to Table 2-2). The CL-GD5465 responds as a target to the values listed in the following table. When the CL-GD5465 is a bus master, it generates memory read and memory write commands. During the data phase(s), these pins are used as byte enables.  Table 2-2. Commands |                                                                                                                                                                                                                                                                                                                           |                                                                                                              |  |

|                   |      | CBE[3:0]#                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Command Type                                                                                                                                                                                                                                                                                                              |                                                                                                              |  |

|                   |      | 02h                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I/O read                                                                                                                                                                                                                                                                                                                  |                                                                                                              |  |

|                   |      | 03h                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I/O write                                                                                                                                                                                                                                                                                                                 |                                                                                                              |  |

|                   |      | 06h                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Memory read                                                                                                                                                                                                                                                                                                               |                                                                                                              |  |

|                   |      | 07h                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Memory write                                                                                                                                                                                                                                                                                                              |                                                                                                              |  |

|                   |      | Ah                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Configuration read                                                                                                                                                                                                                                                                                                        |                                                                                                              |  |

|                   |      | Bh                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Configuration write                                                                                                                                                                                                                                                                                                       |                                                                                                              |  |

| ADSTB1<br>(IDSEL) | I    | figuration strapping (RA[6:4]). In PCI modes, this input is a cl read and write cycles.                                                                                                                                                                                                                                                                                                                                                                                | nip select in place of the upper 24                                                                                                                                                                                                                                                                                       | pin depends on the host bus con-<br>4 address bits during configuration<br>6] and CBE[3:2]#. This pin is not |  |

Table 2-1. Host Interface — PCI/AGP Bus (cont.)

| Name              | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADSTB0<br>(M66EN) | I/O  | AD Strobe: The definition of this pin depends on the host bus configuration strapping (RA[6:4]). In 133-MHz AGP mode, this input strobes data on pins AD[15:0] and CBE[1:0]#. This pin is not used for 66-MHz AGP mode.  In 66-MHz PCI mode, this pin is an input. If this pin is '1' at the trailing edge of RESET, the system runs at 66 MHz and the CL-GD5465 selects the medium DEVSEL speed. If this pin is '0' at the trailing edge of RESET, the system is going to run at 33 MHz and the CL-GD5465 selects the fast DEVSEL speed.  In 33-MHz PCI mode, this pin is an output and is driven low (even during RESET). This indicates to the PCI bus that this PCI device is not capable of 66-MHz operation; the fast DEVSEL speed is selected. |

| ST[2:0]#          | I    | <b>Status #:</b> In AGP mode, this bus provides information from the arbiter to a master on what the master can do. This bus has meaning to the master when its GNT# is asserted and must be otherwise ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RBF#              | 0    | Read Buffer Full #: When this output is low, it indicates that the CL-GD5465 is ready to receive previously requested low-priority read data. This pin is not used in PCI mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SBA[7:0]          | 0    | Sideband Address: This pin is not used in AGP pipelined addressing or PCI modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PIPE#<br>(SBSTB)  | I/O  | Pipelined Request #: The definition of this pin depends on the host bus configuration strapping (RA[6:4]). PIPE# is asserted with FRAME# for the PCI master cycles in AGP Stealth mode. This pin is not used in PCI modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# 2.2 ROM/VMI Pins

# Table 2-3. ROM/VMI Pins

| Name                 | Туре | Description                                                                                                                                                                                                                                                                                                   |

|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EVIDEO#<br>(VACTIVE) | I    | <b>Enable Video #:</b> If the CL-GD5465 is not configured for VMI, this pin controls the buffers on the feature connector pixel bus (either RA[14:7] or EV[7:0]). If the CL-GD5465 is configured for VMI, this input is VACTIVE. VACTIVE indicates that valid pixel data is being transmitted on the VID bus. |

| ESYNC#               | I/O  | <b>Enable Sync and Blank #:</b> If the CL-GD5465 is not configured for VMI, this pin controls the buffers of the feature connector HSYNC, VSYNC, and BLANK# pins. If the CL-GD5465 is configured for VMI, this pin is a general-purpose I/O.                                                                  |

| EDCLK#<br>(VREF)     | I    | <b>Enable Dot Clock #:</b> If the CL-GD5465 is not configured for VMI, this input is used to the control the buffer on DCLK. If the CL-GD5465 is configured for VMI, this is the VREF input.                                                                                                                  |

| DCLK<br>(PIXCLK)     | I/O  | <b>Dot Clock:</b> If the CL-GD5465 is not configured for VMI, this is the feature connector DCLK pin. The buffer is controlled by EDCLK#. If the CL-GD5465 is configured for VMI, this is the PIXCLK input.                                                                                                   |

| BLANK#<br>(HREF)     | I/O  | <b>BLANK #:</b> If the CL-GD5465 is not configured for VMI, this is the feature connector BLANK# I/O. The buffer is controlled with ESYNC#. If the CL-GD5465 is configured for VMI, this is the HREF input.                                                                                                   |

| HSYNC <sup>a</sup>   | I/O  | Horizontal Sync: This output supplies the horizontal synchronization signal to the monitor. The polarity of this output is programmable. This pin is put into high-impedance when ESYNC# is low.                                                                                                              |

D1-14 DETAILED PIN DESCRIPTIONS May 1997 PRELIMINARY DATA BOOK v2.0

Table 2-3.

ROM/VMI Pins (cont.)

| Name     | Туре | Description                                                                                                                                                                                                                                                                                                                                                       |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSYNC    | I/O  | <b>Vertical Sync:</b> This output supplies the vertical synchronization signal to the monitor. The polarity of this output is programmable. This pin is put into high-impedance when ESYNC# is low.                                                                                                                                                               |

| RA15     | I/O  | <b>ROM Address 15:</b> This pin supplies address bit 15 if the CL-GD5465 is configured for a 64K BIOS. This pin is also the data pin for the second I <sup>2</sup> C interface. If a pull-down resistor is installed on RA15, the CL-GD5465 is configured for a 32K BIOS and this pin is only used for the second I <sup>2</sup> C interface.                     |

| RA[14:7] | I/O  | <b>ROM Address [14:7]:</b> These pins supply address bits 14 through 7. If the CL-GD5465 is configured for VMI mode, these pins are also the video input bus (VID[0–7]). If no pull-down resistor is installed on RA1, these pins are also used for the feature connector pixel bus (P[0–7]). If the CL-GD5465 is in Test mode, these pins are used for T[24–31]. |

| RA6      | I/O  | <b>ROM Address 6:</b> This pin supplies address bit 6. If the CL-GD5465 is configured for VMI mode, this pin supplies DS# or RD#, according to the VMI mode. If the CL-GD5465 is in Test mode, this pin is used for T8.                                                                                                                                           |

| RA5      | I/O  | <b>ROM Address 5:</b> This pin supplies address bit 5. If the CL-GD5465 is configured for VMI mode, this pin supplies R/W# or WR#, according to the VMI mode. If the CL-GD5465 is in Test mode, this pin is used for T9.                                                                                                                                          |

| RA4      | I/O  | <b>ROM Address 4:</b> This pin supplies address bit 4. If the CL-GD5465 is configured for VMI mode, this pin is used for DTACK# or READY, according to the VMI mode. If the CL-GD5465 is in Test mode, this pin is used for T10.                                                                                                                                  |

| RA[3:0]  | I/O  | <b>ROM Address [3:0]:</b> These pins supply address bits 13 through 0. If the CL-GD5465 is configured for VMI mode, these pins also supply the host address (HA[3:0]). If the CL-GD5465 is in Test mode, these pins are used for T[11–14].                                                                                                                        |

| PCS#     | I/O  | VMI Peripheral Chip Select #: If the CL-GD5465 is configured for VMI mode, this pin supplies the chip select. If the CL-GD5465 is in Test mode, this pin is used for T15.                                                                                                                                                                                         |

| RD[7:0]  | I/O  | <b>ROM Data [7:0]:</b> These pins are the ROM data bus. If the CL-GD5465 is configured for VMI mode, these pins are the host data bus (HD[7:0]). If the CL-GD5465 is in Test mode, these pins are used for T[7:0].                                                                                                                                                |

| ROMCS#   | I/O  | <b>ROM Chip Select #:</b> This pin enables the ROM data onto the RD bus. If this pin is tied to low (it may be tied directly to ground) at RESET, the ROM is disabled.                                                                                                                                                                                            |

| SCL2     | I/O  | Serial Data Clock 2: This pin is used with RA15 to mechanize the second I <sup>2</sup> C port. This is the clock pin; RA15 is the data pin.                                                                                                                                                                                                                       |

<sup>&</sup>lt;sup>a</sup> HSYNC and VSYNC are also listed in Table 2-6.

# 2.3 Rambus® Pins

The CL-GD5465 has one Rambus channel — Rambus Channel A. The pins for a Rambus Channel B are allocated, but not used on the CL-GD5465.

The Rambus channels must be designed properly for acceptable results. The trace routing, width, and spacing are all very important. Refer to Appendix B1, "Layout Guidelines" for Rambus channel design information.

# 2.3.1 Rambus® Channel A

Table 2-4. Rambus® Channel A Pins

| Name     | Туре | Description                                                                                                                                                                                                                                              |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAD[8:0] | I/O  | Rambus A Data [8:0]: This is the bidirectional data bus for Rambus Channel A. These are low-swing signals as defined in the Rambus electrical specifications.                                                                                            |

| RARCLK   | 0    | Rambus A Receive Clock: Data to the RDRAMs (request and write data packets) are aligned to this clock. This clock is used by the RDRAM to sample data it receives from the CL-GD5465.                                                                    |

| RATCLK   | I    | Rambus A Transmit Clock: Data from the RDRAMs (read data and acknowledge packets) are aligned to this clock. This clock is transmitted by the RDRAM along with the data and used by the CL-GD5465 to sample the data from the RDRAM.                     |

| RACTE1   | 0    | Rambus A ClockToEnd 1: This pin is driven by the CL-GD5465 to the end of the memory expansion module.                                                                                                                                                    |

| RACTE0   | 0    | Rambus A ClockToEnd 0: This pin is driven by the CL-GD5465 to the end of the main Rambus channel.                                                                                                                                                        |

| RAC      | I/O  | Rambus A Control: This bidirectional pin is used to frame packets, transmit part of the Rambus operation code, and terminate transactions prematurely on Rambus Channel A. This is a lowswing signal as defined in the Rambus electrical specifications. |

| RAE      | 0    | Rambus A Enable: This output resets or enables the RDRAMs for Rambus Channel A. This is a low-swing signal as defined in the Rambus electrical specifications.                                                                                           |

| RAVREF   | I    | Rambus A Voltage Reference: This is the logic threshold voltage for low-swing signals for Rambus Channel A.                                                                                                                                              |

| CCTL     | I/O  | <b>Rambus Current Control Program:</b> This pin is used for the calibration of the RAC output current drivers for both channels. A resistor approximately the value of $1/2~R_{TERM}$ must be connected between this pin and $V_{TERM}$ .                |

D1-16 DETAILED PIN DESCRIPTIONS PRELIMINARY DATA BOOK v2.0 May 1997

# 2.3.2 Rambus® Channel B

The Rambus Channel B pins are not implemented on the CL-GD5465 and are not internally connected to the pins (except SOUT, pin 174), but are reserved for future Laguna family members.

Table 2-5. Rambus® Channel B Pins

| Name     | Туре | Description                                                                                                                                                                                                                                                                              |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RBD[8:0] | I/O  | Rambus B Data [8:0]: This is the bidirectional data bus for Rambus Channel B. These are low-swing signals as defined in the Rambus electrical specifications.                                                                                                                            |

| RBRCLK   | 0    | Rambus B Receive Clock: Data to the RDRAMs (request and write data packets) are aligned to this clock. This clock is used by the RDRAM to sample data it receives from the CL-GD5465.                                                                                                    |

| RBTCLK   | I    | Rambus B Transmit Clock: Data from the RDRAMs (read data and acknowledge packets) are aligned to this clock. This clock is transmitted by the RDRAM along with the data and used by the CL-GD5465 to sample the data from the RDRAM.                                                     |

| RBCTE1   | 0    | Rambus B ClockToEnd 1: This pin is driven by the CL-GD5465 to the end of the memory expansion module.                                                                                                                                                                                    |

| RBCTE0   | 0    | Rambus B ClockToEnd 0: This pin is driven by the CL-GD5465 to the end of the main Rambus channel.                                                                                                                                                                                        |

| RBC      | I/O  | Rambus B Control: This bidirectional pin is used to frame packets, transmit part of the Rambus operation code, and terminate transactions prematurely and Rambus Channel B. This is a low-swing signal as defined in the Rambus electrical specifications.                               |

| RBE      | 0    | Rambus B Enable: This output is used to reset or enable the RDRAMs for Rambus Channel B. This is a low-swing signal as defined in the Rambus electrical specifications.                                                                                                                  |

| RBVREF   | I    | Rambus B Voltage Reference: This is the logic threshold voltage for low-swing signals for Rambus Channel B.                                                                                                                                                                              |

| SOUT     | 0    | Rambus Serial Output: This output initializes the RDRAMs in both Rambus channels. It is used in performing refresh when the RDRAMs are in Power Down mode (this feature is not implemented in the CL-GD5465).  This pin is not 5-V tolerant, see Section 6.2 for additional information. |

# 2.4 Monitor Pins

Table 2-6. Monitor Pins

| Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                             |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RED   | 0    | Analog Red Video: This analog output supplies current corresponding to the red value of the pixel being sent to the monitor. Each DAC output is typically terminated to monitor ground with a 75- $\Omega$ , 2-percent resistor. This resistor, in parallel with the 75- $\Omega$ resistor in the monitor, yields a 37.5- $\Omega$ impedance to ground. |

| GREEN | 0    | <b>Analog Green Video:</b> This analog output supplies current corresponding to the green value of the pixel being sent to the monitor. See the description of RED for information regarding the termination of this pin.                                                                                                                               |

| BLUE  | 0    | <b>Analog Blue Video:</b> This analog output supplies current corresponding to the blue value of the pixel being sent to the monitor. See the description of RED for information regarding the termination of this pin.                                                                                                                                 |

| RSET  | I    | <b>DAC Current Set:</b> A resistor from this pin to DACVSS sets the full-scale current output of the DACs. The value of this resistor is typically 135 $\Omega$ . The following equation is derived in Appendix B5, "Signature Generator".                                                                                                              |

|       |      | $RSET = \frac{2.52 \text{ V} \bullet \text{Load}}{\text{VFullScale}}$ Equation 2-1                                                                                                                                                                                                                                                                      |

| IREF  | I    | <b>DAC Current Reference:</b> This pin is connected to a $0.1$ - $\mu F$ capacitor that is returned to AVDD. This capacitor stabilizes the internal DAC current reference.                                                                                                                                                                              |

| HSYNC | I/O  | <b>Horizontal Sync:</b> This output supplies the horizontal synchronization signal to the monitor. The polarity of this output is programmable. This pin is put into high-impedance when ESYNC# is low.                                                                                                                                                 |

| VSYNC | I/O  | <b>Vertical Sync:</b> This output supplies the vertical synchronization signal to the monitor. The polarity of this output is programmable. This pin is put into high-impedance when ESYNC# is low.                                                                                                                                                     |

| SCL   | I/O  | Serial Clock: This is the clock pin of the first I <sup>2</sup> C port.                                                                                                                                                                                                                                                                                 |

| SDA   | I/O  | Serial Data: This is the data pin of the first I <sup>2</sup> C port.                                                                                                                                                                                                                                                                                   |

# 2.5 TV Output Pins

Table 2-7. TV Output Pins

| Name    | Туре | Description                                                                                                                                                                                                                             |

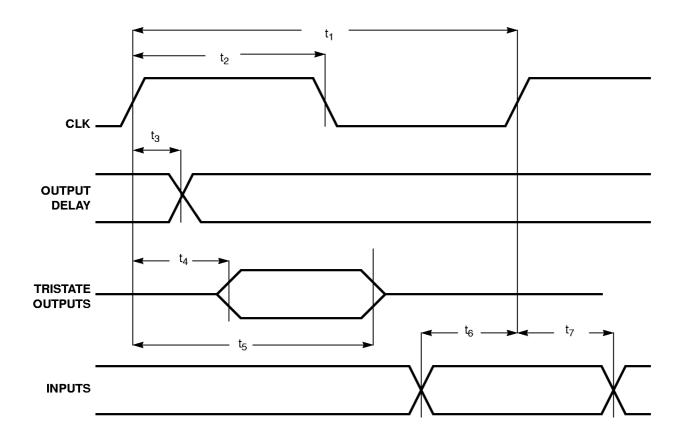

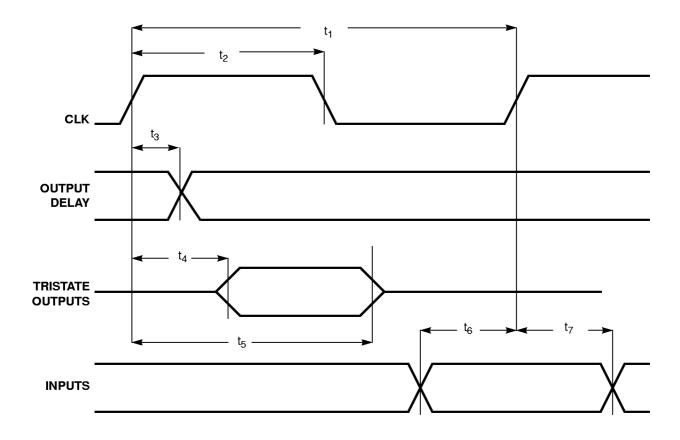

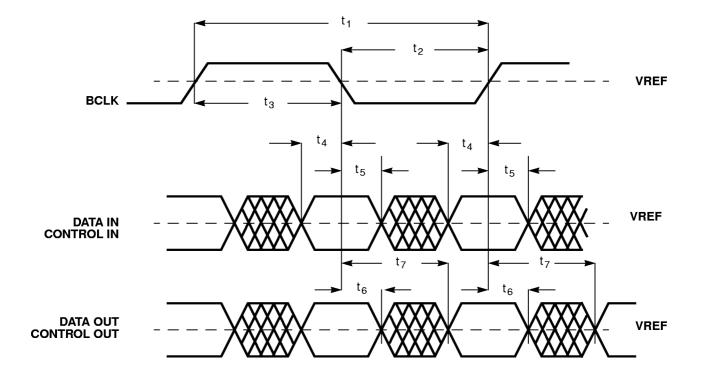

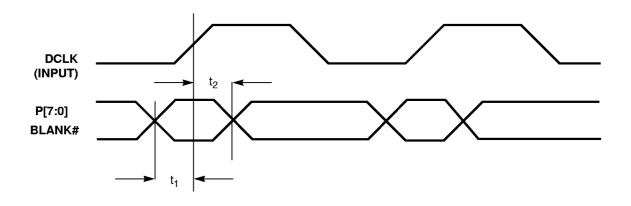

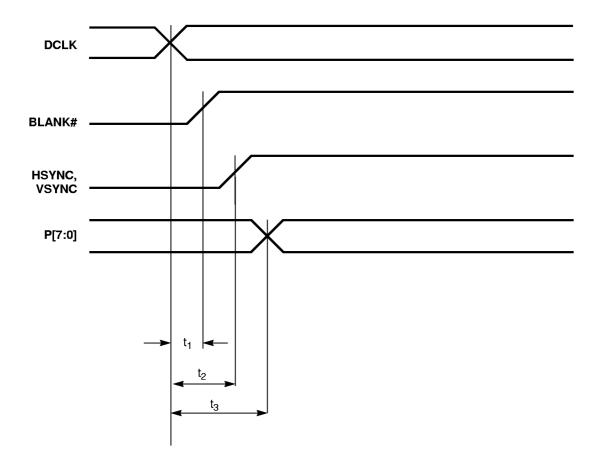

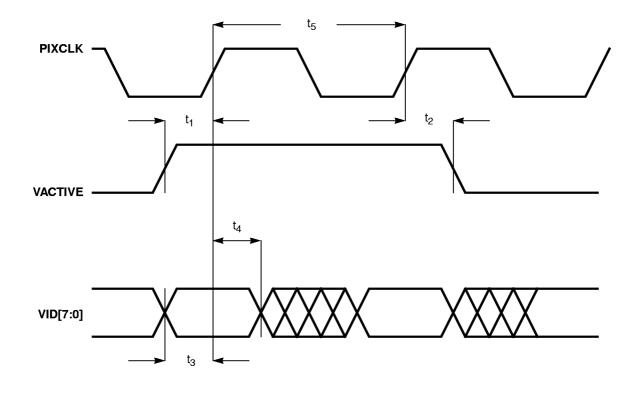

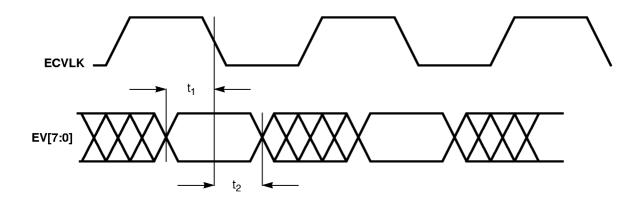

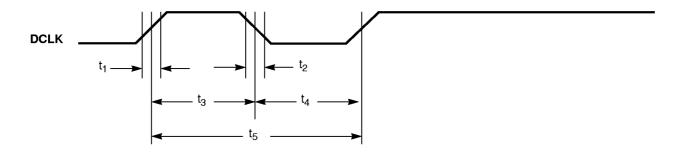

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|