### US005706415A

## United States Patent [19]

## Kelley et al.

[11] Patent Number:

5,706,415

[45] Date of Patent:

Jan. 6, 1998

| [54] | METHOD AND APPARATUS FOR           |

|------|------------------------------------|

|      | DISTRIBUTED INTERPOLATION OF PIXEL |

|      | SHADING PARAMETER VALUES           |

[75] Inventors: Michael Kelley, San Mateo; Stephanie Winner, Santa Clara, both of Calif.

[73] Assignee: Apple Computer, Inc., Cupertino, Calif.

[21] Appl. No.: 812,563

[56]

[22] Filed: Dec. 20, 1991

5543 7 . 616

395/126, 163, 166, 129, 131, 132, 505

### References Cited

### U.S. PATENT DOCUMENTS

| 4,594,673 | 6/1986  | Holly 395/121                |

|-----------|---------|------------------------------|

| 4,658,247 | 4/1987  | Gharachorloo                 |

| 4,697,178 | 9/1987  | Heckel 395/122               |

| 4,791,582 | 12/1988 | Ueda et al                   |

| 4,805,116 | 2/1989  | Liang et al 395/129          |

| 4,815,009 | 3/1989  | Blatin 395/129               |

| 4,819,192 | 4/1989  | Kuragano et al 395/126 X     |

| 4,866,637 | 9/1989  | Gonzalez-Lopez et al 395/126 |

| 4,885,703 | 12/1989 | Deering 395/122              |

| 4,897,803 | 1/1990  | Calarco et al 395/166        |

| 4,945,500 | 7/1990  | Deering                      |

| 5,001,651 | 3/1991  | Rehme et al 395/126          |

| 5,025,405 | 6/1991  | Swanson 395/126 X            |

| 5,113,362 | 5/1992  | Harston et al 364/723        |

| 5,115,402 | 5/1992  | Matsushiro et al 395/141     |

| 5,123,085 | 6/1992  | Wells et al 395/121          |

| 5,128,872 | 7/1992  | Malachowsky et al 395/162    |

| 5,148,381 | 9/1992  | Sprague 364/723              |

| 5,153,937 | 10/1992 | Wobermin et al 395/131       |

| 5,157,388 | 10/1992 | Kohn 395/162 X               |

| 5,163,127 | 11/1992 | Ikumi et al 395/126          |

| 5,214,753 | 5/1993  | Lee et al 395/125            |

| 5,222,204 | 6/1993  | Swanson 395/127              |

| 5,249,264 | 9/1993  | Matsumoto 395/122 X          |

| 5,253,335 | 10/1993 | Mochizuki et al 395/122      |

| 5,261,041 | 11/1993 | Susman 395/122 X             |

|           |         |                              |

| 5,268,995 | 12/1993 | Diefendorff et al | 395/122 |

|-----------|---------|-------------------|---------|

| 5,278,949 | 1/1994  | Thayer            | 395/126 |

| 5,307,449 | 4/1994  | Kelley et al      | 395/119 |

### OTHER PUBLICATIONS

Foley et al., "Computer Graphics Principles and Practice", Second Edition, Addison-Wesley Publishing Company, 1990, pp. 736-739.

"Computer Graphics Principles and Practice Second Edition", by Foley, Van Dam, Feiner and Huges, published by the Addision Wesley Publishing Corp., pp. 885–886 and pp. 899–900.

"Pyramidal Parametrics", by Lance Williams, Computer Graphics vol. 17 No. 3, Jul. 1983.

Oka, Masaaki, et al., "Real-Time Manipulation of Texture-Mapped Surfaces," Computer Graphics, vol. 21, No. 4, pp. 181–188 (Jul. 1987).

Deering, Michael, et al., "The Triangle Processor and Norman Vector Shader: A VLSI System for High Performance Graphics," Computer Graphics, vol. 22, No. 4, pp. 21–30 (Aug. 1988).

### (List continued on next page.)

Primary Examiner—Mark K. Zimmerman

Attorney, Agent, or Firm—Blakely, Sokoloff, Taylor &

Zafman

### [57] ABSTRACT

A method and apparatus for generating pixel shading values in a computer controlled display system. Generally, the apparatus is embodied in a rendering pipeline, where each stage of the pipeline performs a particular pixels shading function, so that pixels are shaded in a distributed and direct fashion. The method of the present invention includes the steps of: deriving a pixel interpolation value from an object description, providing a first and second shading parameters and the pixel interpolation value to a first shader, generating the first shading value for the pixel, providing second and third shading parameters and the pixel interpolation value to a second shader and generating second shading value for the pixel.

## 5 Claims, 19 Drawing Sheets

### OTHER PUBLICATIONS

Kirk, David, et al., "TheRendering Architecture of the DN10000VS," Computer Graphics, vol. 24, No. 4 pp. 299–307 (Aug. 1990).

Fuchs, Henry, et al., "Pixel-Planes 5: A Heterogeneous Multiprocessor Graphics System Using Processor Enhanced-Memories," Computer Graphics, vol. 22, No. 4, pp. 239–246(Aug. 1988).

Akeley, Kurt, et al., "High-Performance Polygon Rendering," Computer Graphics, vol. 22, No. 4, pp. 239–246 (Aug. 1988).

Gharachorloo, et al. "Subnanosecond Pixel Rendering with Million Transistor Chips," Computer Graphics, vol. 22, No. 4, pp. 41–49, Aug. 1988.

Deering et al. "The Triangle Processor and Normal Vector Shader: A VLSI System for High Performance Graphics," Computer Graphics, vol. 22, No. 4, pp. 21–30, Aug. 1988. Gharachorloo et al. "A Characterization of Ten Rasterization Techniques" Computer Graphics, vol. 23, No. 3, pp. 355–368, Jul. 1988.

Fuchs, et al. "Pixel-Planes 5: A Heterogeneous Multiprocessor Graphics System Using Processor-Enhanced Memories," Computer Graphics, vol. 23, No. 3, pp. 79–88, Jul. 1989.

Potmesil, et al. "The Pixel Machine: A Parallel Image Computer," Computer Graphics, vol. 23, No. 3, pp. 69–78, Jul. 1989.

Excerpts from Foley and Van Dam (Second Edition), Articles 3.6.3, 15.6, and 18.7.2/3. A total of 12 pages.

Fiume, et al. "A Parallel Scan Conversion Algorithm with Anti-Aliasing for a General-Purpose Ultracomputer," Coputer Graphics, vol. 17, No. 3, pp. 141–150, Jul. 1983.

Niimi, et al. "A Parallel Processor System for Three-Dimensional Color Graphics," Computer Graphics, vol. 18, No. 3, pp. 67-76, Jul. 1984.

Fussell, et al. "A VLSI-Oriented Architecture for Real-Time Raster Display of Shaded Polygons," Graphics Interface, May 1982, pp. 373–380.

FIGURE 1 (PRIOR ART)

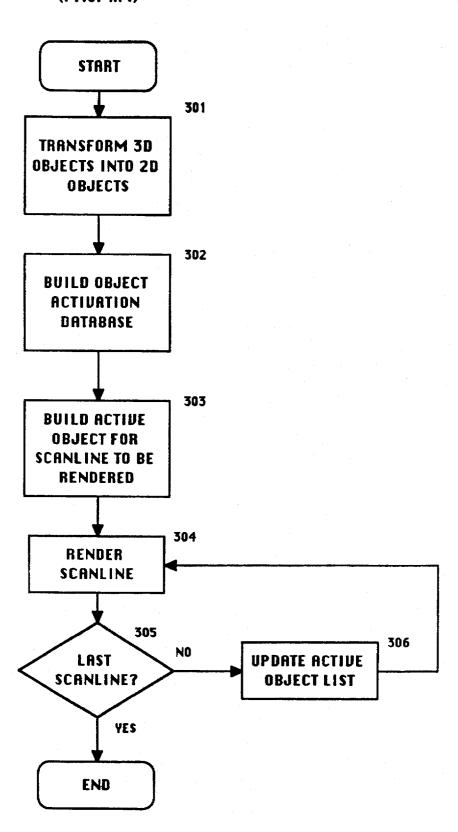

Figure 3a (Prior Art)

FIGURE 4

FIGURE 5

FIGURE 6a

FIGURE 6b

FIGURE 8A

FIGURE 8C

FIGURE 9

FIGURE 10

Figure 11

FIGURE 13

MUX1404 **%** MUX1409 1433 ¥ ₩2 **W**3 ₩4 Figure 14b **6**M 9M MUX1417 X ₩8 **X** MUX1403 1450

Sheet 19 of 19

### METHOD AND APPARATUS FOR DISTRIBUTED INTERPOLATION OF PIXEL SHADING PARAMETER VALUES

### BACKGROUND OF THE INVENTION

### 1. Field of the Invention

The present invention relates to the field of computer controlled display systems, in particular, devices for rendering pixels for displaying 3-dimensional graphical images.

### 2. Description of the Related Art

As the processing capability of computer systems has grown, so have the ways of displaying data generated by the computer systems. Many vocations now use computer systems as a fundamental tool. For example, in the area of architectural design, 3-Dimensional graphical images (or 3-D images) of buildings or other structures are dynamically created and manipulated by a user. A computer system is able to capture and process data in order to display the 3-D image, in a time that is much faster than could be done 20 manually. As computer hardware technology has advanced, so has the development of various methods, techniques and special purpose devices for rapidly displaying and manipulating 3-D images.

A 3-D image is represented in a computer system as a 25 collection of graphical objects. Generally, there are two known approaches to providing high performance generation of 3-D images. A first approach focuses on rapidly drawing the graphical objects that comprise the 3-D graphics image. This approach is referred to hereinafter as the object 30 approach. The object approach embodies a hidden surface removal algorithm commonly known as the screen Z-buffer algorithm. A second approach looks to processing the graphical objects with respect to the scanlines on which they would appear on a display. The second approach is referred 35 to hereinafter as the scanline approach. The two approaches involve certain trade-offs. These trade-offs include cost, performance, function, quality of image, compatibility with existing computer systems and usability.

As mentioned above, a 3-D image will be represented in 40 a computer system as a collection (or database) of graphical objects. The database may have been created through the use of any of a number of commercially available application software packages. The database may be in any of a number common that the 3-D graphical objects are polygons (e.g. triangles) or some other high level object. The process of transforming a collection of graphical objects into a 3-D image is termed rendering. Literally, the rendering process takes object information and converts it to a pixel represen- 50 tation. It is in the rendering process where the object and scanline approaches differ.

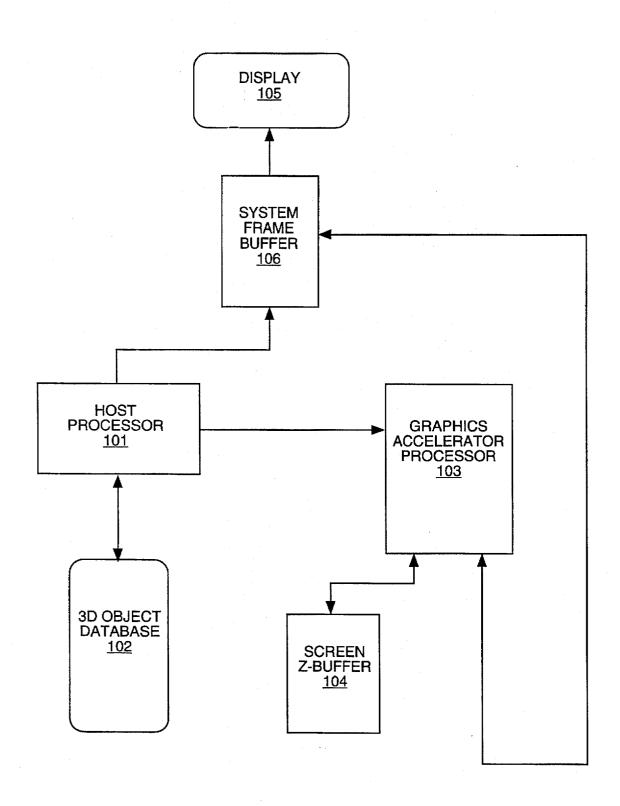

In the object approach, the majority of the function related to the rendering process is performed by specially designed the necessary operations to create the pixel representation of the objects. The pixel representation may then be used by a display system to "draw" the graphical object on a display screen. A schematic of the object approach is illustrated in FIG. 1. In FIG. 1, a general purpose host computer 101 is 60 used to maintain and create a 3-D Object Database 102. As described above, the 3-D Object Database contains the 3-D Objects which comprise the 3-D image. Coupled to the host processor 101 is a system frame buffer 106. The system frame buffer 106 is further coupled to the display 105. The 65 system frame buffer 106 contains the data, e.g. RGB values, for each pixel in the display 105.

The primary components of the object approach are embodied in the graphics accelerator processor 103 and the screen Z-Buffer 104. The graphics accelerator processor 103 performs various graphical functions such as transformations and clipping. The screen Z-Buffer 104 is used for hidden surface removal. During the rendering process for a graphical image, the rendered pixels are transferred to the system frame buffer 106.

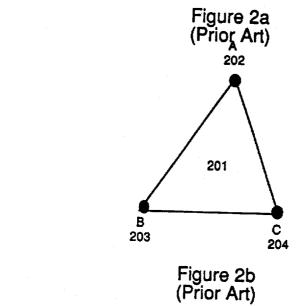

Using the object approach, each of the 3-D objects in the 10 database 102 is rendered individually. Using a triangle object as an example, the rendering process generally involves the following steps, and is illustrated in FIG. 2a-2c:

- 1. Derive a 2-D triangle from the graphical object definition. The transformation step, as illustrated in FIG. 2a, results in a triangle 201 with vertices A 202, B 203 and C 204.

- 2. Perform any necessary dipping of the object. Clipping refers to removing portions of the object that are not within the bounds of a predetermined viewing area.

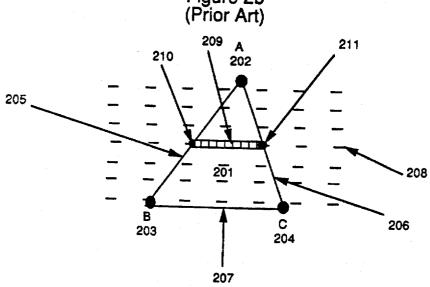

- 3. Generate horizontal spans for the object. A horizontal span refers to a portion of the object that intersects a scanline. A span is comprised of one or more pixels. For example, in FIG. 2b, see span 209. Typically this occurs through a linear vertical interpolation of the object.

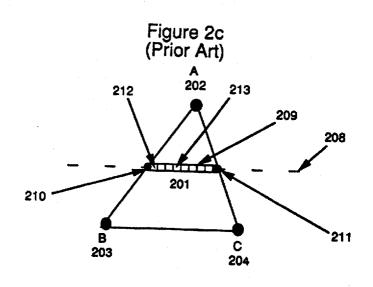

- 4. Generate values for each of the pixels in the span. This process is commonly referred to as horizontal interpolation. FIG. 2c illustrates horizontal interpolation. This step will include such functions as shading of the pixels, hidden surface removal and storing the pixel values into a screen RGB frame buffer.

- 5. Repeat steps 3 and 4 until the object has been rendered.

- 6. Repeat steps 1, 2, 3, 4, and 5 until all the objects have been rendered.

The Step 1 derivation of a 2-D triangle is needed in order to map into the two-dimensional coordinate systems that are typically used by known display systems. The third coordinate of a 3-D graphical object is depth (e.g. "Z value"), and is used to determine whether or not the object is behind another object and thus out of view (i.e. hidden).

Vertical interpolation, as described in Step 3 above, is illustrated in FIG. 2b. Vertical interpolation is typically performed in the following fashion. First, active edges are of standard graphics formats (e.g. PHIGS or GKS). It is 45 determined. An active edge is defined as an edge of the object that intersects a scanline that is being processed. A span is defined as the pixels on the scanline that would connect the two intersection points of the active edges. The triangle 201 is comprised of edges 205, 206 and 207. The edge 205 is defined by the segment connecting vertices A 202 and B 203, the edge 206 is defined by the segment connecting vertices A 202 and C 204 and the edge 207 is defined by the segment connecting vertices B 203 and C 204. Generally, for any particular scanline, there will be 2 graphics accelerators. These graphics accelerators perform 55 active edges. The exception being when an edge is horizontal. For example, in FIG. 2b, for scanline 208, the active edges are 205 and 206. Thus, for scanline 208, there is a span 209 for object 201.

The next step is to determine the coordinates of the end-points 210 and 211 of span 209. First it must be understood that each active edge is simply a line. Thus, the difference between successive points in the line are linear. As the vertical ordinate is simply the current scanline, only the horizontal ("X") value need be calculated. Typically, this is done using a forward differencing calculation. In forward differencing a constant, say  $\Delta p$  is determined that is between each horizontal coordinate (e.g. using the formula Δp=P1-

P0/Y1-Y0, where P1 and P0 are pertinent pixel values, such as "R" of RGB, at Y1 and Y0 for the respective end-points of an edge). Thus, the horizontal coordinate value may be determined by simply adding  $\Delta p$  to the previous corresponding coordinate value. It is known that using forward differ- 5 encing makes other techniques of improving rendering performance, e.g. parallel processing, more difficult.

A non-desirable aspect of the forward differencing technique is that a high number of bits are required to be stored and propagated in order to retain the necessary numerical 10 precision needed for graphics applications. This is a tradeoff to eliminating certain operations, namely division operations, that would otherwise be required in the vertical interpolation process.

Referring to FIG. 2c, shading the pixels in span 209 is 15 then performed. Shading refers to establishing the values for the pixels comprising the span 209. The coordinates of the successive pixels on the span may be determined through the means such as a counter. Horizontal interpolation to determine shading values for each of the pixels may occur using 20 either linear interpolation or perspective corrected interpolation. In any event, as the values for a pixel 212 are determined, the values for subsequent pixels, e.g. pixel 213 can be estimated through horizontal interpolation.

screen Z-Buffer algorithm. The screen Z-Buffer algorithm provides for hidden surface removal. Hidden surface removal is necessary for the display of 3-D images, since the surfaces in view depend on the vantage point from the object that are "behind" another object. The hidden surface removal Z-Buffer algorithm is known in the art and requires a local frame buffer. The screen contains the pixel values of objects as they are rendered. As the location of any object may be anywhere on the screen, the local frame buffer must 35 have enough storage to support the display of all pixels on the display. Once all the objects have been rendered, the local frame buffer is transferred to the system frame buffer for display.

The Z-Buffer method utilizes the fact that each object has 40 an attribute, typically called a Z-value, which is a 3rd dimensional ordinate. Alow Z-value indicates that the object (or portion of the object) is closer to the viewer than an object with a high Z-value. The Z-Buffer stores a Z-value for each pixel on a display. During the rendering process, the 45 Z-value of a pixel being processed is compared to Z-value in a corresponding location in the Z-buffer. If the Z-value of the pixel being processed is smaller than the value in the corresponding location in the Z-buffer, then the Z-value of the pixel being process is placed in the corresponding 50 location in the Z-buffer. Additionally, the pixel value of the pixel being processed will be placed in the screen frame buffer, since is is now the "closest" to the viewer.

Some of the tradeoffs of object/z-buffer rendering include: the requirement of Z-buffer memory, screen frame buffer 55 memory (in addition to a system frame buffer), and the difficulty in building a modular type of system due to a constraint of the Z-Buffer memory needing to be close to the screen buffer. As a result of such hardware requirements, the object approach can be a costly approach.

In the scanline approach the 3-D image is rendered a scanline at a time, rather than an object at a time. Thus, all objects intersecting a particular scanline are processed before writing to the scanline location in the frame buffer. The scanline approach utilizes two passes. In the first pass, 65 3-D objects are transformed into 2-D objects and a scanline object activation list is built. In the second pass, each of the

scanlines are rendered. The flow of the scanline approach is illustrated in FIG. 3a. As in hardware rendering, transformation of the 3-D objects into 2-D objects occurs, step 301. Concurrent with the step 301, an Object Activation Database is built, step 302. The steps 301 and 302 comprise the first

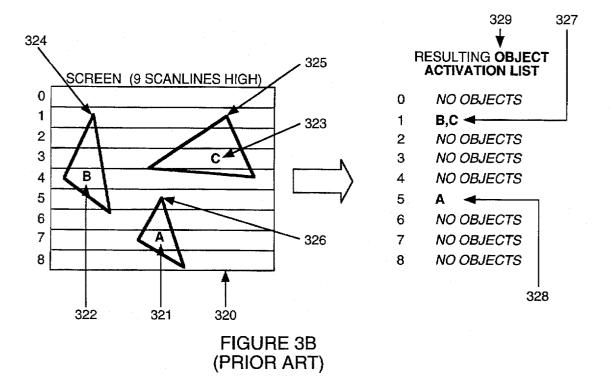

The Object Activation Database provides, for each scanline, a list of objects which first become active on that scanline. By becoming active, that object may be displayed on that scanline. This typically occurs by identification of the highest point of an object (i.e. its lowest Y-coordinate), and assigning it to the activation list of the corresponding scanline. The relationship of the Object Activation Database to the displayed objects is illustrated in FIG. 3b. In FIG. 3b a display screen 320 is 9 scanlines high. The scanlines 0-8 are numbered from low to high down the left hand side of the display screen 320. Objects A 321, B 322 and C 323 are to be displayed on the display screen 320. It is apparent that Object A 321 has a highest point 326 (which is on scanline 5), Object B 322 has a highest Point 324 (which is on scanline 1) and Object C 323 has a highest Point 325 (also on scanline 1).

Still referring to FIG. 3b, the resulting Object Activation List Database 329 is illustrated. As the points 324 and 325 As noted above, the object approach generally utilizes the 25 are on scanline 1, a scanline 1 entry 327 contains the corresponding objects, namely Object B 322 and Object C 323. Additionally, a scanline 5 entry 328 contains the Object A 321.

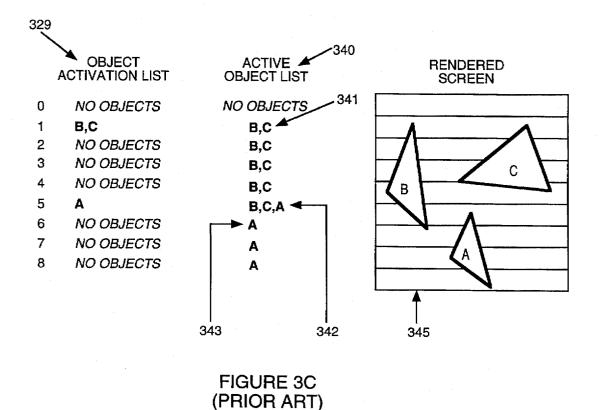

Referring back to FIG. 3a, once the Object Activation viewing direction and refers to the "hiding" of areas of an 30 Database 329 is generated and all the 3-D Objects have been transformed, an Active Object List is created, step 303. The Active Object List provides a source of identifying for the scanline being processed, the objects which are active (i.e. portions of which are displayable on that scanline). The Active Object List may contain either descriptive information of the 2-D object (e.g. coordinate information and shading parameter values) or may contain information defining the active edges of the 2-D object (also including shading parameter values). FIG. 3c illustrates the contents of an Active Object List 340 with respect to the screen and Object Activation List 329 of FIG. 3b. In Active Object List 340, a scanline 1 entry 341 contains the objects B and C. The objects B and C remain as an entry for scanlines 2-5. In scanline 5 entry 342, object A is included (as this is where the object A is first displayed). As objects B and C are no longer displayed after scanline 5, they are not in a scanline 6 entry 343. The entries for scanlines 6-8 are comprised solely of object A. Rendered Screen 345 illustrates how the objects would be rendered.

Referring back to FIG. 3a, once the object Activation List is created, the rendering process begins, step 304. As with hardware rendering, the next steps include 1) vertical interpolation, to determine the coordinates (and shading parameters of the coordinates) of a horizontal span that corresponds to a particular object on a particular scanline, and 2) horizontal interpolation, for determining the individual pixel values for the pixels within the span. Vertical interpolation occurs for every active object on a scanline. Once the coordinates for the horizontal span and corresponding shading parameters have been determined, vertical interpolation is completed and horizontal interpolation begins. When all the pixels in the span have been shaded, horizontal interpolation for the span is completed. This shading process is embodied in step 304. Step 304 is repeated for all the objects on the active object list. Finally, a test is made to determine if the last scanline has been processed, step 305. If the final scanline has not been

processed, the active object list is updated to reflect the active objects for the next scanline, step 306. The step 306 is generally identical in function to step 303. If the last scanline has been processed, the processing for that graphical image is complete. The steps 303-306 comprise the 5

An important distinction between the vertical interpolation process in the scanline approach and the object approach is that in the scanline approach portions of multiple objects are rendered at one time. Thus, appropriate storage is required to retain all the forward differencing information that will be used as all the objects are being interpolated. For example, if 10 units of storage are required for storing the forward differencing information for one object, 50 units of storage are required for storing the forward differencing information for  $\hat{\mathbf{5}}$  objects. Additionally,  $^{15}$ since forward differencing is being used, there is an interscanline dependence so that the scanlines must be processed in sequential order.

Scanline rendering provides benefits over object rendering that include eliminating the need for a frame Z-Buffer 20 and a screen RGB Buffer, each of which usually are the size

A known system that utilized scanline rendering in combination with a pipelined object approach is discussed in the publication "Computer Graphics Principles and Practice 25 Second Edition" by Foley, VanDam, Feiner and Huges published by the Addison Wesley Publishing Corporation at Pages 885-886. The system described provides separate processing units for creating an Object Activation Database, Active Object List, Visible Span Generation (i.e. Vertical 30 Interpolation) and Pixel Shading (i.e. Horizontal Interpolation). However, the system as described did not provide for parallel pipelines.

A parallel pipeline system was described in the aforementioned "Computer Graphics Principles and Practice Second 35 Edition" publication at Pages 899-900. The system described utilized a technique termed object-parallel rasterization. In this system multiple objects are processed in

The tradeoffs discussed above were often premised on an 40 idea that it is desirable to minimize the number of computations that need to be performed. An example is the forward differencing technique for linear interpolation. In order to minimize division operations, a larger amount of data must be moved and stored through the system. With the matura- 45 tion of semiconductor technology, the cost of circuitry to perform logic operations has decreased. Thus, it has become viable to design systems that utilize processing power and minimize memory. This is especially desirable when space is a consideration, since storage tends to take up a sizable 50 amount of valuable space on an electrical circuit.

As described above, known rendering systems typically perform a high number of linear interpolations. It would be desirable to provide a method and means where these linear interpolations may be performed in an efficient manner.

Known high quality 3-D rendering systems are inherently expensive and incapable of incorporating new functionality without significant re-design of the inherent architecture of the rendering system. It would be desirable to provide a rendering system that is scalable to user needs. It is an object 60 of the present invention to provide such a system.

It is a further object of the present invention to provide an interpolation means that does not present the bandwidth and data storage requirements associated with forward differencing based techniques.

It is a further object of the present invention to increase rendering performance of graphical images through the

rendering of multiple scanlines, without requiring a multiple increase in data bandwidth requirements.

### SUMMARY

A method and apparatus for generating pixel shading values in a computer controlled display system, is disclosed. Generally, the rendering apparatus is embodied in a rendering pipeline, where each stage of the pipeline performs a particular shading function. Pixel shading information is passed through each stage of the pipeline via set-up tokens and pixel interpolation tokens.

The present invention describes a method of shading pixels that provides for distributed interpolation of shading parameter values. The method of the present invention includes the steps of: deriving a pixel interpolation value from an object description, providing a first and second shading parameters and the pixel interpolation value to a first shading means, generating a first shading value for the pixel, providing second and third shading parameters and the pixel interpolation value to a second shading means and generating second shading values for the pixel.

### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a schematic drawing of a prior art rendering

FIG. 2a illustrates the representation of an object as a triangle.

FIG. 2b illustrates a triangle mapped to a display screen.

FIG. 2c illustrates pixels in a horizontal span of a triangle when mapped to a display screen.

FIG. 3a is a flowchart illustrating a prior art scanline method for rendering a 3-D image.

FIG. 3b illustrates an Object Activation Database as utilized in a prior art scanline method for rendering a 3-D

FIG. 3c illustrates an Active Object List as utilized in a prior art scanline method for rendering a 3-D image.

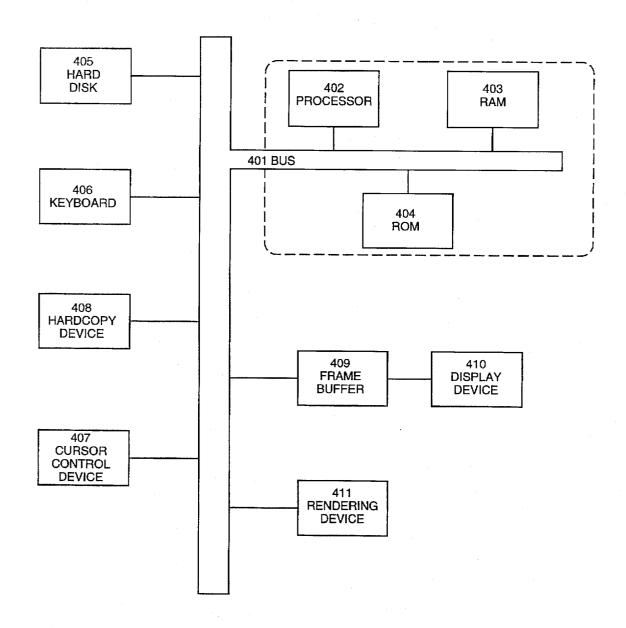

FIG. 4 illustrates a computer system as may be utilized by the preferred embodiment of the present invention.

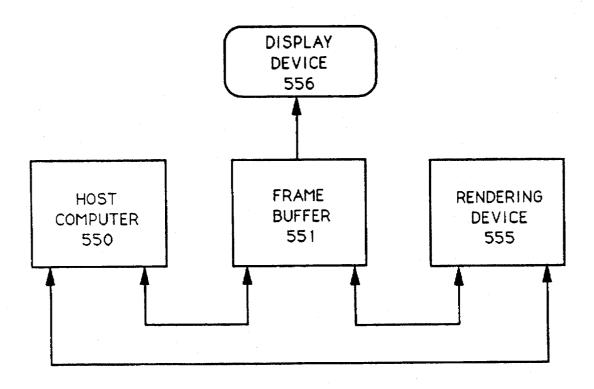

FIG. 5 illustrates a graphics accelerator coupled to a computer system and a display device as may be utilized by the preferred embodiment of the present invention.

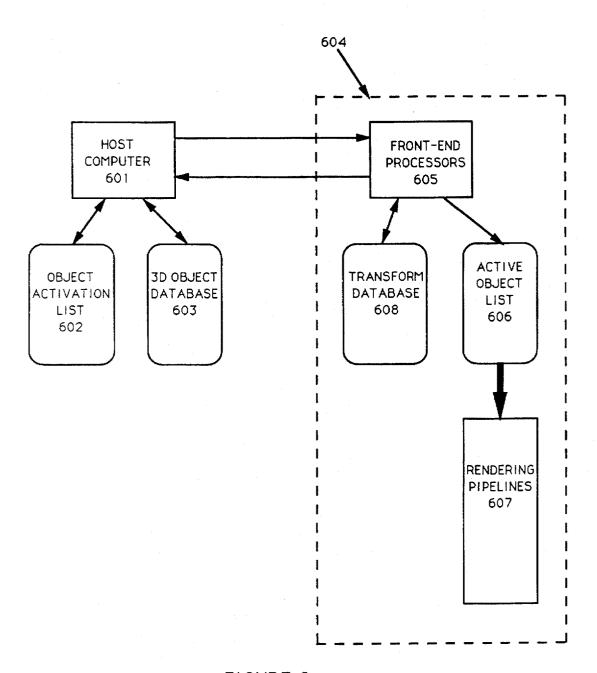

FIG. 6a illustrates a first graphics accelerator architecture as may be utilized by the preferred embodiment of the present invention.

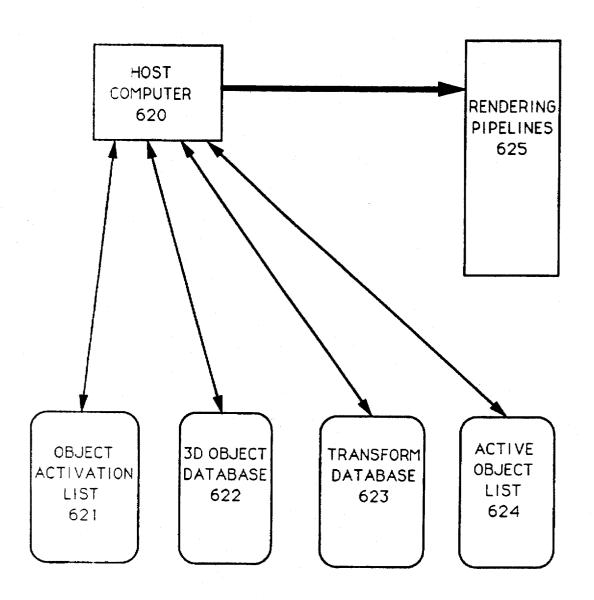

FIG. 6b illustrates a second graphics accelerator architecture as may be utilized by the preferred embodiment of the present invention.

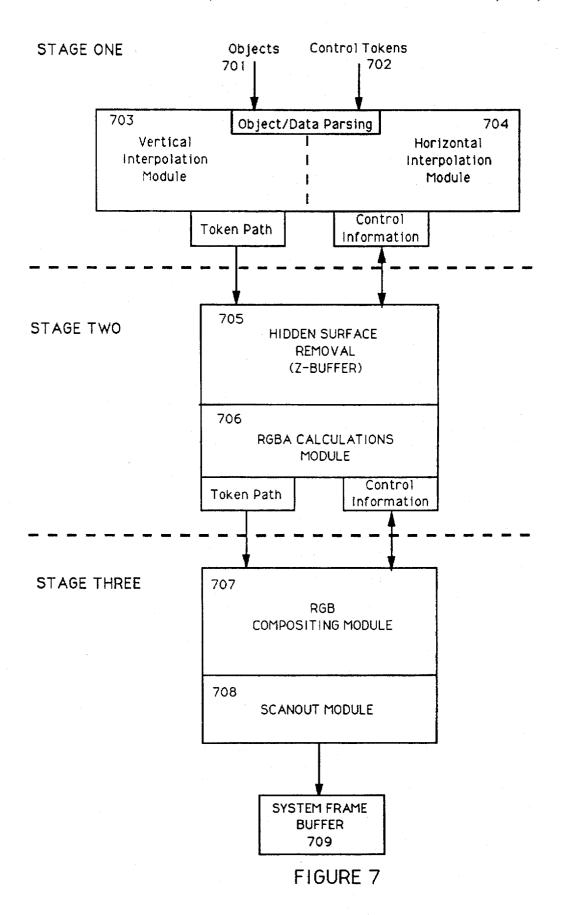

FIG. 7 illustrates a graphics pipelines as may be utilized by the preferred embodiment of the present invention.

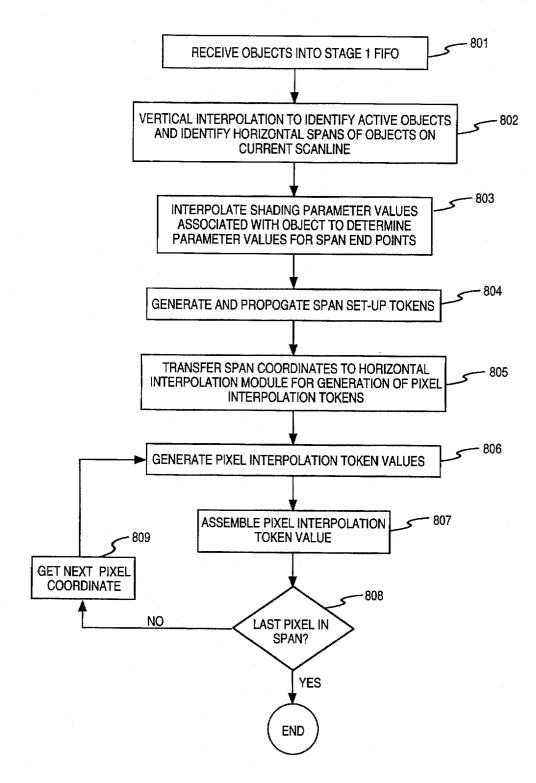

FIG. 8a is a flowchart of the flow of operation for a stage 1 (of FIG. 7) as may be utilized by the preferred embodiment of the present invention.

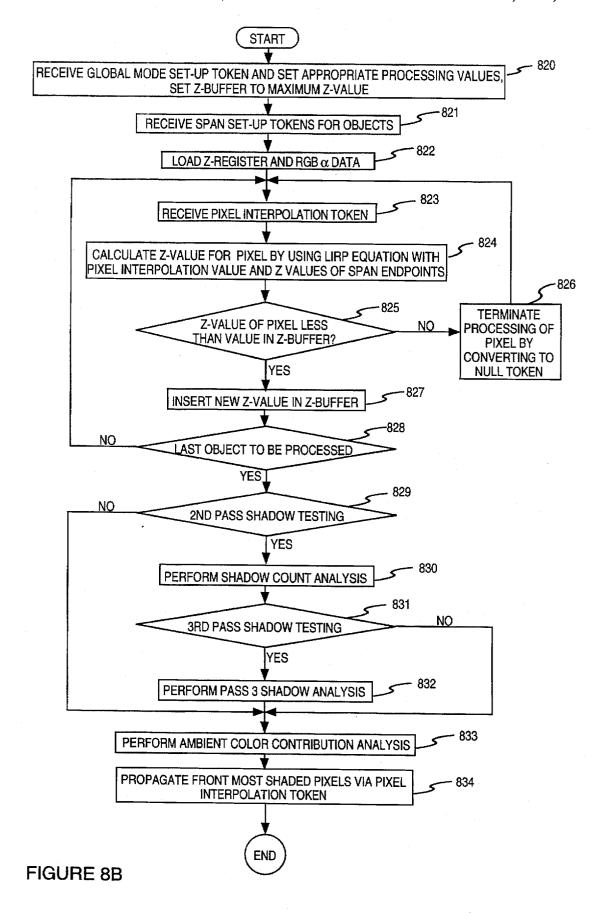

FIG. 8b is a flowchart of the flow of operation for a stage 2 (of FIG. 7) as may be utilized by the preferred embodiment of the present invention.

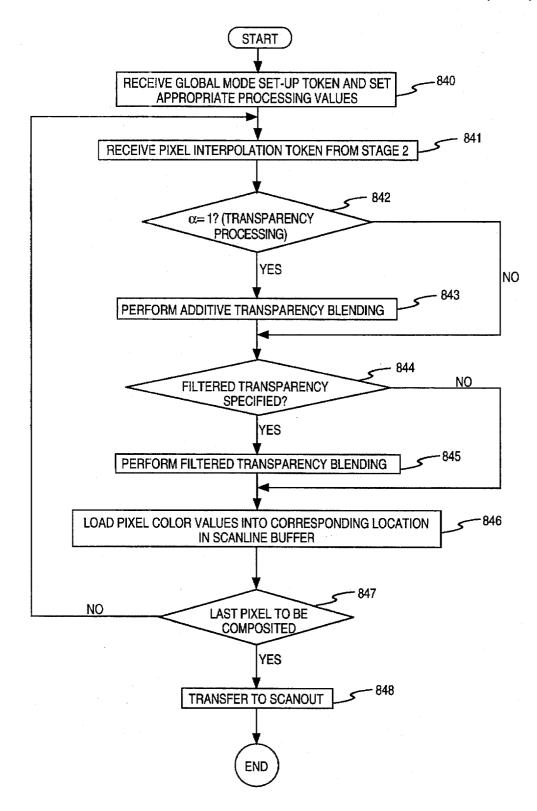

FIG. 8c is a flowchart of the flow of operation for a stage 3 (of FIG. 7) as may be utilized by the preferred embodiment of the present invention.

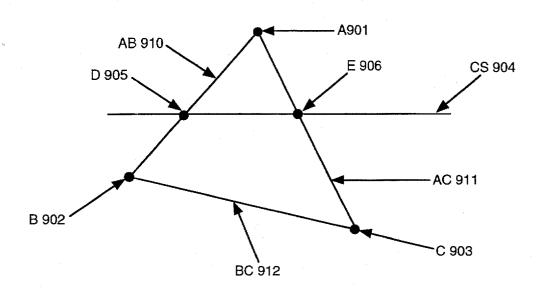

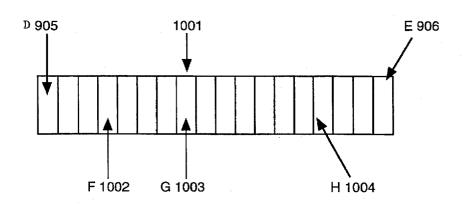

FIG. 9 illustrates an example of Vertical Interpolation in 65 the preferred embodiment of the present invention.

FIG. 10 illustrates an example of Horizontal Interpolation in the preferred embodiment of the present invention.

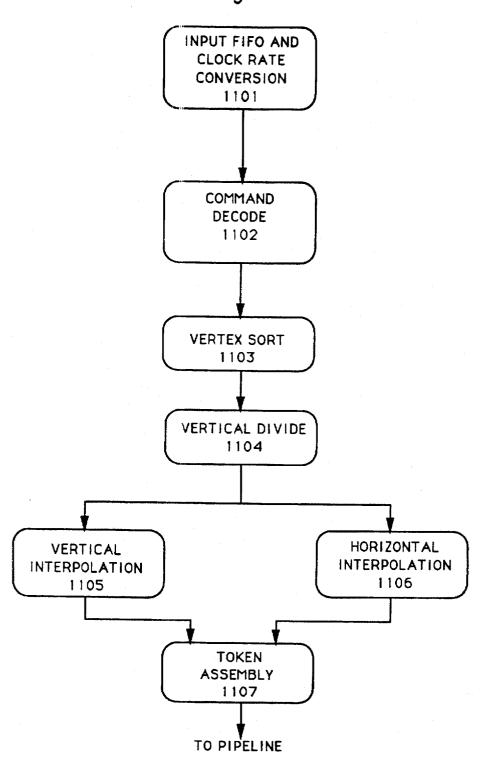

FIG. 11 illustrates the functional blocks of the Stage 1 processing unit as may be utilized by the preferred embodiment of the present invention.

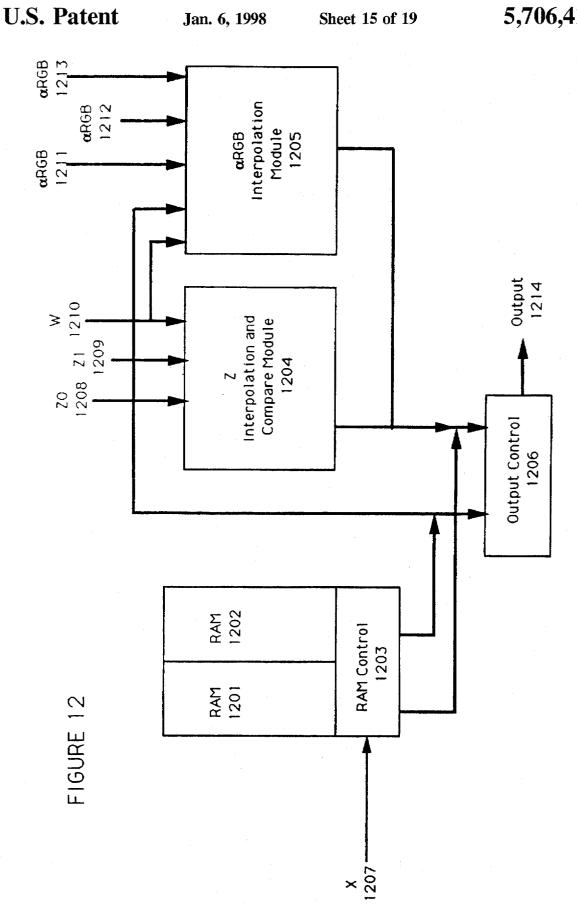

FIG. 12 is a schematic functional diagram of a Stage 2 and/or Stage 3 processing unit as may be utilized by the 5 preferred embodiment of the present invention.

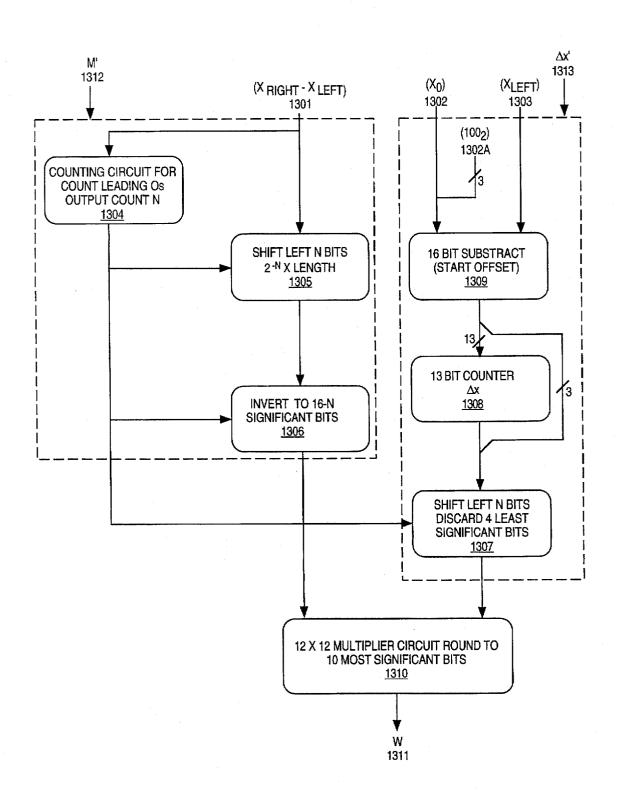

FIG. 13 is a schematic representation of a circuit for determining the pixel interpolation weight as may be utilized by the preferred embodiment of the present invention.

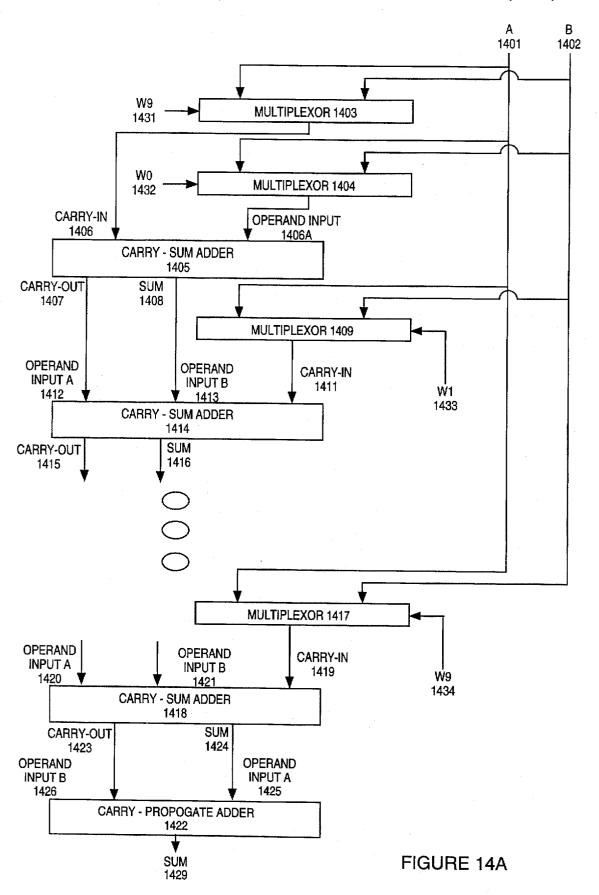

FIG. 14a is a schematic representation of a circuit for calculating a linear interpolation value as may be utilized by the preferred embodiment of the present invention.

FIG. 14b illustrates the bit positions of a weighting value as may be utilized by the preferred embodiment of the  $_{15}$  present invention.

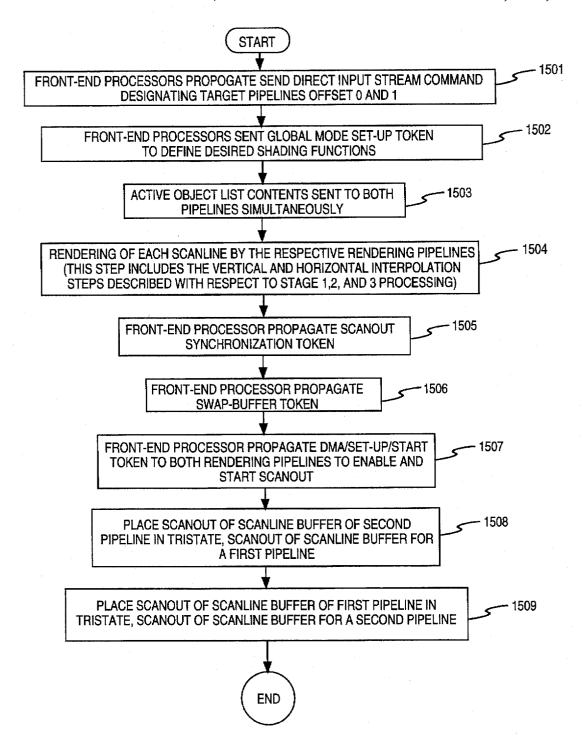

FIG. 15 is a flowchart illustrating the processing flow of multiple parallel rendering pipelines as may be utilized in the preferred embodiment of the present invention.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

A method and apparatus for rendering multiple scanlines in a computer controlled display system is described. In the following description, numerous specific details are set forth such as data structures, in order to provide a thorough understanding of the present invention. It will be apparent, however, to one skilled in the art that the present invention may be practiced without these specific details. In other instances, well-known circuits, control logic and coding techniques have not been shown in detail in order not to unnecessarily obscure the present invention.

# Overview of the Computer System of the Preferred Embodiment

The computer system of the preferred embodiment is described with reference to FIG. 4. The present invention may be implemented on a general purpose microcomputer, such as one of the members of the Apple® Macintosh® family, one of the members of the IBM Personal Computer family, or one of several work-station or graphics computer devices which are presently commercially available. In any event, a computer system as may be utilized by the preferred embodiment generally comprises a bus or other communi- 45 cation means 401 for communicating information, a processing means 402 coupled with said bus 401 for processing information, a random access memory (RAM) or other storage device 403 (commonly referred to as a main memory) coupled with said bus 401 for storing information 50 and instructions for said processor 402, a read only memory (ROM) or other static storage device 404 coupled with said bus 401 for storing static information and instructions for said processor 402, a data storage device 405, such as a magnetic disk and disk drive, coupled with said bus 401 for 55 storing information and instructions, an alphanumeric input device 406 including alphanumeric and other keys coupled to said bus 401 for communicating information and command selections to said processor 402, a cursor control device 407, such as a mouse, track-ball, cursor control keys, 60 etc, coupled to said bus 401 for communicating information and command selections to said processor 402 and for controlling cursor movement. Additionally, it is useful if the system includes a hardcopy device 408, such as a printer, for providing permanent copies of information. The hardcopy 65 device 408 is coupled with the processor 402 through bus

R

Also coupled to the computer system of the preferred embodiment is a frame buffer 409 which is further coupled to a display device 410, preferably a display device capable of displaying color graphics images. The frame buffer 409 contains the pixel data for driving the display device 410. The display device 410 would be further coupled to a rendering device 411, also known as a graphics accelerator. Typically, such a rendering device 411 is coupled to the bus 401 for communication with the processor 402 and frame buffer 409. The preferred embodiment is implemented for use on a Macintosh computer available from Apple Computer, Inc. of Cupertino, Calif.

FIG. 5 illustrates in more detail, a rendering device as coupled to a host computer system in the preferred embodiment. First, a host computer system 550 is coupled to a frame buffer 551 and a rendering device 555. The host/frame buffer coupling 552 is an optional coupling when the rendering device is installed. Such a coupling may be desirable in instances where the rendering device 555 is not being utilized, e.g. when the application being executed does not require the display of 3-D graphical images.

The host/rendering device coupling 553 is typically through a means such as the bus 401, described above with reference to FIG. 4. The rendering device/frame buffer coupling 554 is also typically over a DMA means. The information flowing over this coupling will typically consist of pixel data of images or scanlines that have already been rendered. Finally, the frame buffer 551 is coupled to the display device 556, wherein pixel data to drive the presentation of the graphical image is stored.

The rendering device of the preferred embodiment operates with display systems with fast raster support. Fast raster support refers to raster scan display systems where the frame buffer 551 can accept incoming scanlines of display data at high speed. Besides graphics applications, fast raster support is typically used for applications such as display of video data. Thus, the system of the preferred embodiment is compatible with systems that have support for video applications.

As will be described in more detail below, the preferred embodiment of the present invention utilizes a scanline approach to rendering. From a computer system design standpoint, the principle advantages in utilizing a scanline approach are the reduction of bandwidth between the graphics accelerator and the host/frame buffer, reduced requirements for low latency communication between the graphics accelerator and the host/frame buffer, and increased coherence of the data transferred from the graphics accelerator and the host/frame buffer. Moreover, for a given desired performance of the combined computer system and graphics accelerator, these advantages reduce both the cost of the computer system without the graphics accelerator, the cost of the graphics accelerator itself.

### Shading Algorithm of the Preferred Embodiment

Before a pixel is shaded, it must be determined whether it is front most. As will be described in detail below, this occurs in the preferred embodiment through a scanline Z-Buffer algorithm. Once it is determined which pixels of an object are visible, a shading algorithm is used to determine pixel values (i.e. their color). Typically, the shading algorithm will take into account material properties of the object surface and the sources of light in the scene to determine the color of the pixel. In the preferred embodiment, a Phong Shading is performed at the endpoint vertices of a span while Gouraud shading is performed for the pixels across the span.

$\sim$  10

Material properties in the preferred embodiment include a diffuse RGB color, specular power (shininess), specular RGB color and surface normal. Light sources in the preferred embodiment include an infinite light source and an ambient light source. Finally, in the preferred embodiment, 5 shading is based on a diffuse reflection model with the option of adding a specular reflection model.

The color of a particular pixel in an object can be most accurately calculated as the sum of the diffuse, specular, and ambient contributions for each of the color components. The specific diffuse color component, in this case the color red, is calculated by the formula:

### Diffuse Color,= $L_{pr}K_{dr}(L\cdot N)$

where  $L_{pr}$  is the red color component of the (point) light source,  $K_{dr}$  is the diffuse red component of the surface, L is the light vector, and N is the normal to the surface. All vectors are normalized. The calculation is repeated for each color component.

Specular reflection describes the light reflected from shiny surfaces. The specular color is determined by the product of the light and the specular color of the surface attenuated by the angle between the direction of the viewpoint and the reflection of light. Highlights are described by specular reflection. The red component of a the color of a pixel due to specular reflection is calculated by the equation:

Specular Color,=

$$L_{pr}K_{sr}(R\cdot V)^n$$

where  $L_{pr}$  is the intensity of the red component of the (point) light source,  $K_{sp}$  is the red component of the specular color, R is the reflection of the light vector off of the surface, and V is the reversed eye vector (the vector from the surface to the eye), and n is the specular reflection coefficient (i.e. the specular power). All vectors are normalized.

The ambient color contribution is calculated by the equation:

### Ambient Color,=LarKar

where  $L_{ar}$  is the intensity of the ambient light source and  $k_{ar}$  is the ambient color of the surface.

For each of the above color contribution components RGB, the calculations are repeated. The method of the preferred embodiment calculates pixel values in this fashion. However, as objects only have such RGB values defined at vertex points, interpolation techniques are used to determine values at points within the object. It is such an interpolation technique for determining pixel values that is implicit in the rendering architecture of the preferred embodiment.

Although the preferred embodiment utilizes a technique with Phong shading at the vertices coupled with Gouraud interpolations, it would be apparent that other shading techniques may be used. Such alternative shading techniques include, but are not limited to full Gouraud Shading or Torrence-Sparrow shading.

### Rendering Architecture of the Preferred Embodiment

The rendering architecture of the preferred embodiment is premised on a scanline algorithm. As described with reference to prior art systems, the scanline algorithm renders an image by scanline. Briefly, the scanline algorithm is a two pass algorithm. The first pass is used to set up databases of information that are used to drive the actual scanline rendering process. In the first pass, a 2-D object is derived from

each 3-D object in a 3-D object database. During this process, the scanline upon which the object would first be displayed (first in the sense of the order of drawing scanlines to the display device), i.e. become "active", is determined. This information is used to create an Object Activation Database, where the entries in the database define the objects that become "active" on a particular scanline.

In the second pass, the Object Activation Database is used to create a dynamic list of objects which are "active" on the scanline(s) currently being rendered. This list is called the Active Object List. The Active Object List is then provided to shading means which create the pixel values for the scanline(s) currently being rendered. The Active Object List is updated as objects become "active" or "inactive" on the scanline(s) to be rendered next.

It is known to those skilled in the art that an object may typically be represented by a data structure which contains coordinate information and shading parameter values. In the preferred embodiment, a triangle object is represented by 3 coordinate points, where each of the coordinate points has shading parameter values. The segments which interconnect the 3 coordinate points define the bounds of the triangle. Further in the preferred embodiment a quadrilateral object is definable. A quadrilateral will be similarly defined, except that it will define 4 coordinate points (each with corresponding shading parameter values). In the preferred embodiment, a quadrilateral may be provided to the rendering pipeline, but it would be converted into a pair of triangles for rendering (each utilizing 3 of the 4 coordinate points).

Alternative systems hardware schematics as may be utilized by the preferred embodiment are illustrated in FIGS. 6a and 6b. Referring to FIG. 6a, a host computer 601, e.g. a microprocessor, is coupled to a graphics accelerator 604 so that certain functions in the rendering process are carried out by the host and the accelerator. The host computer 601 maintains a 3-D Object Database 603 and creates an Object Activation Database 602. As described above, the 3-D Object Database 603 contains a list of the 3-D objects which comprise the 3-D Graphical Image, while the Object Activation Database 602 contains a list for each scanline, of the objects which are first displayed on that scanline.

The graphics accelerator 604 is comprised of front-end processors 605 and rendering pipelines 607. The front-end processors 605 perform a plurality of functions in the rendering process. First, with respect to the first pass of the scanline algorithm, the front-end processors 605 perform dipping and transformation functions and provide the Host computer 601 with information for each object indicating the scanline on which the object first becomes active. With respect to the second pass, the front-end processors 605 receive 3D-object information from the Host computer 601 to create an Active Object List 606. The Active Object List 606 identifies objects which are "active" or to be drawn, on the particular scanline being processed. The front end processor 605 also provide control instruction to the rendering pipelines 607. Such control instructions are in the form of control tokens, and are discussed in greater detail below. The front end processors 605, are preferably floating point processors or Reduced Instruction Set Computer (RISC) pro-

Also illustrated in FIG. 6a is a transformation database 608. The transformation database 608 is used as a matter of convenience to resolve object accessing problems that occur due to the data structures used in creating the transformation matrices when transforming 3-D Objects to 2-Dimensional Objects.

Finally, the graphics accelerator includes one or more rendering pipelines 607. The rendering pipelines receive control information from the front-end processors 605 and the object information from the active object list 606 to perform the actual calculating of pixel values for each pixel 5 in a scanline. The rendering pipelines 607 are discussed in greater detail below.

An alternative implementation is illustrated in FIG. 6b. The primary difference between this alternative implementation and that illustrated in FIG. 6b is the elimination of front-end processors and separate storage means for the transform database and Active Object List. Referring to FIG. 6b, the host processor 620 performs the functions of the front-end processors 605 of FIG. 6a. Likewise, transform database 623 and Active Object List 624 are coupled to and maintained by host processor 620. The host processor 620 then provides the contents of the Active Object List to one or more rendering pipelines 625, for rendering.

The embodiment illustrated in FIG. 6b is desirable in implementations where performance is sacrificed in relation to cost. As the embodiment in FIG. 6b utilizes fewer components then that in FIG. 6a, its total cost would be lower. However, as the host processor is called on to do more work, rendering performance will be impacted.

In whichever form, a graphics accelerator will typically be one or more printed circuit boards coupled to the computer systems. Coupling of the graphics accelerator was discussed above in reference to FIG. 5. In order to simplify the description of the the rendering pipelines of the preferred embodiment, the processor that provides the objects from the Active Object List to the rendering pipelines will be termed a control processor. In this context, the control processor would refer to the alternative configurations found in FIGS. 6a and 6b.

As will be described below, the rendering pipelines in the preferred embodiment utilize a means for directly interpolating pixel values and determining the x-coordinates of horizontal spans. As compared to prior art systems, the means of the preferred embodiment significantly reduces the amount of data storage for an Active Object List and significantly reduces the data bandwidth requirements.

With regard to the Active Object List, when utilizing traditional forward differencing techniques the Active Object List will contain all the shading parameter data for 45 each active object. It is estimated that the direct evaluation method of the preferred embodiment would provide a 50% storage savings. This is caused by the requirement that 2n bits of precision are required for a value, in order to retain n bits of precision after an arithmetic function is performed. For example, forward differencing an n bit parameter requires storing a 2n current parameter value (pi) and a 2n parameter delta (pD), resulting in a parameter to be represented by 4n bits. Direct interpolation only requires the end-points, i.e. 2n bits of storage. As the number of parameters increases, the storage savings becomes more significant. In the preferred embodiment material properties parameters diffuse RGB, α (alpha or transparency), specular RGB, specular reflectivity  $(N_s)$ , surface normal  $(N_x, N_y, N_z)$ and Z are interpolated and propagated through the pipeline. As shading functionality increases, the number or parameters required to describe the object will increase. Note that other parameters such as specular ambient and diffuse light parameters remain constant and thus need not be interpolated in the pipeline.

Correspondingly, the data bandwidth (or aggregate data flow) required to move the objects is decreased. As data must be moved from the Active Object List to the rendering pipelines, a reduced quantity of data results in a reduced bandwidth. Further, forward differencing requires reading Pi-1 and  $\Delta p$  for 4N bits, then writing back Pi to the Active Object List (another 2N bits) for a total of 6N bits. As described above, in direct evaluation, only 2N bits will be transferred to/from the Active Object List. This results in a 3X savings in the required Active Object List bandwidth of a system that directly interpolates the end-points. Moreover, the unidirectional data flow of direct evaluation also simplifies system design.

It should be noted that in the preferred embodiment the graphics acceleration may directly access the system frame buffer. Thus, inherent in the preferred embodiment is a Direct Memory Access (DMA) means which will allow the graphics accelerator to scanout rendered scanlines directly to the system frame buffer.

Using direct evaluation also reduces the computation necessary to set-up the active object list as slope divisions and parameter delta calculation (i.e. the  $\Delta P$ ) are not necessary. These steps (performed by the front-end processors) are often expensive because of the care taken to avoid introducing error in the forward differencing calculation.

A desirable effect provided by direct evaluation is that it facilitates the rendering of multiple scanlines in parallel. Because the primitives in the active list contain no information dependent on vertical position, the same data can be fed into multiple pipelines, each configured to perform vertical interpolation for a different scanline. By contrast, the forward differencing algorithm changes the primitive description every scanline, so it is difficult to use the same data to drive the rendering of multiple scanlines.

### Description of the Rendering Pipeline

The rendering pipeline of the preferred embodiment is designed to generate one shaded pixel per pipeline clock cycle. As described above, the rendering in the preferred embodiment utilizes the scanline approach. Using traditional forward differencing linear interpolation techniques, the rendering of multiple scanlines simultaneously is made difficult because of the inter-scanline dependencies. The rendering pipeline of the preferred embodiment avoids such difficulties through the use of multiple parallel pipelines and direct evaluation of coordinate and parameter values.

As described above, forward differencing requires high data bandwidth. During the shading of pixels, i.e. horizontal interpolation, a given pixel typically will require over 200 bits of data to be transferred for each shading function. A known technique for minimizing data bandwidth problems is to provide for fast interconnection between components. However, this may create other problems such as synchronization and control. In connection with direct evaluation, the preferred embodiment further minimizes the required bandwidth through direct and distributed evaluation of a pixel interpolation token. This negates the need to send all the shading data required for a pixel down the pipeline. Endpoint values for all parameters are first sent whereupon an interpolation weight need only be provided for each pixel. Direct and distributed evaluation will be discussed in greater detail below with respect to horizontal interpolation. Operation of the Rendering Pipelines

Data and control information is transferred between various stages in the rendering pipeline area as "tokens". "Tokens" as utilized in the preferred embodiment, refer to a fixed structure for sending and receiving data and control information. In any event, prior to receiving objects, the

rendering pipelines must be provided with setup information, to define the rendering functions that will be performed. In the preferred embodiment, this occurs by propagation of a global mode setup token through the pipeline. The global mode setup token is described in greater 5 detail in the section entitled Tokens. Briefly, the global mode setup token is generated by the control processor (i.e. FIG. 6a or the host processor per FIG. 6b) and is used to enable diffuse or specular shading, shadowing and a transparency

13

Once the pipeline has been set-up, the rendering pipelines may receive objects to be rendered. First, a Direct Input Stream Token is sent to the pipelines to designate which rendering pipelines will receive the forthcoming input stream. For objects, all the rendering pipelines may receive 15 the input stream. However, if it is an instruction to cause a particular processing unit to perform a particular function, the rendering pipeline can be designated as appropriate by the Direct Input Stream Token. Next, the objects are sent down to the pipelines in corresponding DRAW instructions. 20 A DRAW instruction merely indicates to the pipeline that an object or more precisely, a span, is to be rendered. The DRAW instruction is followed by data describing 2, 3, or 4 vertices. Loading 4 vertices causes an independent quadrilateral to be drawn. For a quadrilateral to be drawn; the 25 vertices are loaded in the order V0... V3. A quadrilateral is drawn as two triangles. A triangulation field in the DRAW command indicates along which axis to split the quadrilateral. Loading 3 vertices causes the triangulation field to be ignored.

Loading 2 vertices indicates that a strip of connected quadrilaterals is being drawn. A quadrilateral strip is always begun with a detached quadrilateral loading all 4 vertices. The immediately following DRAW command reloads V0/V1, and causes 2 more triangles to be drawn, triangulated as indicated by the triangulation field, and sharing previously loaded V2/V3. The subsequent DRAW reloads V2/V3, sharing the previous V0/V1, and so on, always swapping which 2 vertices are loaded. The triangulation field allows the triangulation axis of each quadrilateral to be specified independently; because the vertex order is swapped for every quadrilateral, leaving the triangulation bit constant will result in the crosshatch triangulation pattern.

FIGS. 7 and 8a-8c describe operation of the rendering pipelines as an object is being rendered. Referring to FIG. 7, 45 in the preferred embodiment the rendering pipeline, such as pipeline 607, is comprised of at least 3 stages. Stage one derives interpolation values, spans and pixels for the objects. Stage two performs hidden surface removal, shadow functions and performs ambient color calculations. In Stage 50 three, a compositing function is performed as well as scanout of a rendered scanline. As each stage provides for standard passing of information and synchronization of operation within the pipeline, additional shading functions, such as texturing, may be added between stages two and 55 three. In the preferred embodiment, Gouraud shading is preformed. If alternative shading methods are desired, such as Phong shading, additional stages between state two and three, may be included. Each of the stages is discussed in greater detail below.

Stage One

In Stage 1, object descriptions (hereinafter objects) 701 from an active object list and control tokens 702 are input into a stage 1 processing means. The stage 1 processing means acts as a pre-processor, for receiving and pre-processing the objects for rendering. A first function performed in stage one is vertical interpolation (via vertical

interpolation module 703). A primary purpose of vertical interpolation is to identify the X-coordinates for horizontal spans corresponding to the active objects in the scanline being processed. The vertical interpolation module also generates set-up tokens describing the span and it's shading parameters. The set-up tokens are forwarded to succeeding stages in the pipeline. A second function performed is setup for horizontal interpolation (via horizontal interpolation module 704). Horizontal interpolation is the process by which pixels in a span are shaded. The horizontal interpolation process is distributed in that separate stages perform separate shading functions. The horizontal interpolation module 704 generates Pixel interpolation tokens for each pixel in the span.

14

FIG. 8a describes stage 1 processing in more detail. First, the objects from the active object list, corresponding to the identified scanline, are sent to the stage one input, step 801. It should be recalled that the data representing the objects include the coordinates of the vertices and shading parameters at the vertices. As the objects are sent down in a "burst" mode, a First In First Out (FIFO) queue is provided which stores the objects prior to their being processed. The stage one processing unit may suspend transfer of objects via provided control signals. Once the objects are input into the pipeline, they are serially processed within Stage One (but the processing of an individual object may occur in parallel). The first step for pre-processing an object for the pipeline, is vertical interpolation to identify a horizontal span of the object, step 802. A horizontal span is identified by the end coordinates representing the portion of the object that is displayable on the scanline being processed. As the scanline being processed represents a Y-coordinate, the X-coordinate is identified by determining the intersection point of a scanline and a corresponding active edge. Following the calculation of the span coordinates, corresponding parameter values are then generated for the span end-points, step 803. This is accomplished by linearly interpolating the

Next, span parameter set-up tokens are generated and sent down the pipeline, step 804. Such span parameter set-up tokens contain the RGB values or Z-values for the endpoints of the span that were generated in step 803. It should be noted that certain tokens will only be used by certain successive stages. For example, stage 3 does not use Z-value set-up tokens. If a particular stage does not require the information contained in a particular token, that token will be ignored.

endpoints of the active edges with respect to the scanline

being processed. The details of vertical interpolation are

described in more detail below.

Next, setup for horizontal interpolation of the span is performed. Horizontal interpolation refers to the interpolation of the parameter values of the end-points of a span, across the pixels in the span. The set-up for horizontal interpolation requires transfer of the coordinate points of the span, step 805, and the generation of a pixel interpolation token, step 806. A pixel interpolation token consists of the pixel coordinates and a pixel interpolation weight value. The pixel coordinates are determined by simply counting across the span starting at the left most endpoint on the span. Generation of the pixel interpolation token is described in greater detail below with respect to horizontal interpolation. Next, the corresponding Pixel Interpolation token is assembled and sent down the pipeline, step 807. A check will be made to determine whether it is the last pixel in the span, step 808. If it is not the last pixel in the span, the next pixel coordinates are generated (typically by counting to the next horizontal pixel value), step 809, and the process repeats starting at step 806.

The steps 802-809 will be repeated for all the objects received in the FIFO. As there may be some overlap in processing, i.e. more than one object may be processed through the pipeline at one time, there is typically no check after the generation of a pixel interpolation token to see if 5 there are any more objects in the object FIFO. Moreover, some of the steps may overlap. For example, the generation of span parameter values may occur during the horizontal interpolation set-up processing.

Stage Two

Referring back briefly to FIG. 7, a first function of Stage Two is hidden surface removal (via hidden surface removal module 705). The hidden surface removal module 705 utilizes a Z-Buffer algorithm to eliminate pixels that will not be shaded, because they are "behind" other objects (i.e. not 15 front most). Shadow analysis, to further eliminate pixels that will not be shaded, may also be performed in conjunction with Z-analysis. The shadow analysis is also performed by the hidden surface removal module 705. Stage 2 also performs an ambient color calculation on the visible pixels (via 20 RGBA module 706), and places these values into the Pixel Interpolation Token. The output of stage two are the front most, non-shadowed spans, as well as tokens that are flowing unprocessed through the pipeline, e.g. null tokens.

FIG. 8b illustrates the steps performed in Stage Two. 25 First, prior to receiving any object data, the stage two processing unit receives the Global Mode set-up token, step 820. The Global mode set-up token is used to set appropriate processing criteria for the desired rendering functionality. Next, the span parameter set-up tokens generated in stage 30 one are received, step 821, and the relevant data (i.e. Z and RGB $\alpha$  values) is loaded into registers embodied within the processing unit, step 822.

Stage 2 processing begins when a Pixel Interpolation token is received, step 823. First a corresponding Z-value for 35 the pixel is calculated, step 824. The Z value for the pixel is calculated by directly evaluating a linear interpolation (LIRP) function, using an interpolation weight value contained within the pixel interpolation token. When comparing Z-values, a lower Z-value means that the object is closer to 40 the viewer. In this context, this means that a first object with a higher Z-value than a second object, will be behind and thus hidden by the second object. It should be noted that the Z-buffer will always be initialized to a maximum Z-value so that it will have a valid value to compare incoming Z-values 45 with. This horizontal interpolation of the Z-values of the various pixels in the span is described in more detail below. Once the Z-value of the pixel has been determined, a comparison is then made of the Z value for the pixel with a Z value at the corresponding pixel location in the Z buffer, step 825. If the Z value of the pixel is greater than the value in the corresponding location in the Z buffer, processing of the pixel is terminated, step 826. Termination of processing of the pixel involves converting the corresponding token into a null token, whereupon it will flow through the pipeline 55 unprocessed. If the value is less than or equal to the value in the Z buffer, then the new lower Z-value is returned to the Z-buffer, step 827 and a check for the last object is made, step 828. If it is not the last object, the next pixel interpolation token is received, step 823. If it is the last object then 60 it must be determined if pixel elimination because of shadowing will be performed. A first check to see if Second pass analysis will be performed, step 829. This second pass is performed if the shadow count flag in the global mode setup token is set. If yes, second pass analysis is performed, step 65 830, otherwise it is determined if third pass shadow testing is to be performed, step 831. If yes, third pass analysis is

performed, step 832. The aforementioned shadow analysis is described in greater detail below. In any event, the next step will be to determine the RGB ambient color contributions for the pixel, step 833. This simply involves linear interpolation of the pixel based on the endpoint parameter values of the corresponding span. Once this is performed, the RGB values are placed back into the pixel interpolation token and the token is propagated to the next stage. Stage Three

In Stage Three, a compositing function is performed (via RGB composition module 707). Compositing involves the generation of pixel values due to transparency of objects. This will typically occur when multiple objects have identical Z-values. A transparency value that is associated with an object is termed  $\alpha$ . The a value represents the percentage of the final color value that the corresponding object contributes. For example, an object with an  $\alpha$  of 50, will contribute 50% of the final color pixel value. In the preferred embodiment two types of transparency calculations are performed, additive transparency and filtered transparency. In additive transparency, the existing values are simply added to the incoming color value after being scaled by  $\alpha$ .

In filtered transparency the new color value is linearly interpolated with the old color value to generate the filtered color value. In filtered transparency, the Relative Weight used for the interpolation function is the value provided with the incoming color data, i.e.  $\alpha$ .

Finally, in the stage 3 a scanline buffer in scanout module 708 is used to collect the final values of the pixels for the scanline being processed. Once all the objects in the scanline have been processed, the contents of the scanline buffer is transferred to the system frame buffer 709.

FIG. 8c further illustrates Stage Three processing in the rendering pipeline. As in Stage Two, the global mode setup token received, step 840, and the appropriate processing parameters are set. In this case the processing parameters will dictate which of additive or filtered transparency mode will be used. Next, Pixel Interpolation tokens are received, step 841. The first step is to determined if transparency processing will not be performed by checking if  $\alpha=1$ , step 842. If  $\alpha=1$ , then the pixel color values will be loaded into the scanline buffer, step 846 (since the incoming pixel shading values provide 100% of the blended color value). If transparency processing has been specified, additive transparency is performed, step 843. Next, it will be determined if filtered transparency will be performed, step 844. If yes, filtered transparency blending is performed, step 845. Once the blending has occurred and a new color value has been generated or if now filtered transparency blending is performed, the new pixel color values is loaded into the corresponding location in the scanline buffer, step 846.

It is then determined if the final pixel has been processed, step 847. If the last pixel has not been processed, the next pixel interpolation token is received, step 841. If the last pixel in the last span has been processed, the contents of the scanline buffer is transferred to the system frame buffer via a scanout, step 848. As described above, it is the system frame buffer that is used to drive the display means. It should be noted that in the preferred embodiment, the scanline buffer is double buffered. This will allow the contents of the scanline buffer to be transferred to the frame buffer while a new scanline is being processed.

Vertical Interpolation

As defined above, vertical interpolation is the process by which the X-coordinates of the end-points on a span are determined. A span is the portion of an object that is visible on the scanline being rendered. The vertical interpolation of

the preferred embodiment is achieved by a direct solution method that uses object description information and the identify of the scanline. Vertical interpolation for an object on a scanline being rendered is illustrated with respect to FIG. 9. Referring to FIG. 9, the coordinate points for the vertices of the object are A(Xa,Ya) 901, B(Xb, Yb) 902 and C(Xc,Yc) 903. The scanline being processed is Ycs 904.

In this example, the coordinate points for the object being processed are: Xa=60, Ya=20, Xb=40, Yb=150, and Xc=80, Yc=180. The current scanline Ycs=100. By the process of 10 Vertex Sort (which is described in greater detail below), the active edges of the object for Ycs are determined to be AB 910 and AC 911. An active edge is merely one that intersects the current scanline. An edge is considered active if it satisfies the equation:

### Y-top<Y current scanline<=Y-bottom,

where the Y coordinate increases from top to bottom. For the edge AB 910 Y-top=Ya=20, and Y-bottom=Yb=150; so that 20<100<=150 and the equation is satisfied. For the edge AC 911 Y-top=Ya=20, and Y-bottom=Yc=180; so that 20<100<=180 and the equation is satisfied. With respect to edge BC 912 Y-top=Yb=150, and Y-bottom=Yc=180; so that the equation 150<100<=180 is not satisfied and edge BC 912 25 is not an active edge.

The X-coordinate for the points where each scanline intersects an active edge is calculated by first determining a relative weight w for the edge on scanline Ycs using the formula:

$$W = (Y_{cs} - Y_0)/(Y_n - Y_0)$$

where  $Y_{cs}$  is the current scanline,  $Y_0$  is the highest scanline ordinate value (lowest in numerical value) of the active edge <sup>35</sup> and  $Y_n$  is the lowest scanline ordinate value (highest in numerical value) of the active edge.

The X-coordinate is then determined by directly evaluating the linear interpolation equation:

$$X = X_0(1 - W) + X_1 W$$

where  $X_0$  is the leftmost horizontal coordinate of the active edge and  $X_1$  is the rightmost coordinate of the active edge.

With respect to FIG. 9, the active edge AB 910 intersects the current scanline 904 at point D  $(X_0, Y_{cs})$  905. The active edge AC intersects the current scanline 904 at point E  $(X_1, Y_{cs})$  906. For the point D 905, the relative weight is

$$W = (Ycs - Ya)/(Yb - Ya)$$

= (100-20)/(150-20)

= 80/130

= 8/13.

Inserting this into the linear interpolation equation, the X-coordinate is determined as

$$X_0 = Xb(1-W) + Xa(W)$$

= 40(5/13) + 60(8/13)

= 200/13 + 480/13

= 680/13

= 524/13

which is rounded to 53. Thus, the coordinates for point D 905 are (53, 100).

18

For the point E 906, the relative weight is

$$W = (Ycs - Ya)/(Yc - Ya)$$

$$= (100 - 20)/(180 - 20)$$

$$= 80/160$$

$$= 1/2.$$

Inserting this into the linear interpolation equation, the X-coordinate is determined as

$$X_1 = X_2(1 - W) + X_2(W)$$

=  $60(1/2) + 80(1/2)$

=  $30 + 40$

=  $70$

Thus, the coordinates for point E 906 are (70, 100).

When using such interpolation techniques, fractional components may arise due to the divisions required in achieving the W value. This may result in the rendering of pixels on the boundaries between two triangles twice, or missing pixels to be rendered. To account for such fractional components, a rule is adopted that pixel centers in both the X and Y directions are at X.50 and Y.50, respectively. With respect to FIG. 9, the pixel center for the point A 901 (60, 20) would be (60.50, 20.50). Further, a pixel is covered if the equation

### min<pixel co-ordinate<=max

is satisfied. In order for a point to be included in a horizontal span, the point coordinates are compared to the X-coordinate characteristics of the endpoints of the span and the Y-coordinate characteristics endpoints of the active edges for the object the span is associated with. Referring again to FIG. 9 for a point to be within the horizontal span defined by the points D 905 and E 906, the following criteria must be met:

For the X-Coordinate:  $53.50 < X_n <= 70.50$ ; and for the Y-Coordinate:  $100.50 < Y_n <= 100.50$ .

40

By using < (less than) for comparison on one side and >= (greater than or equal to), the rendering of pixels on the boundaries between two triangles twice, or missing pixels, is avoided. Here the Y coordinate value will typically be satisfied because it refers to the scanline being rendered.

Generation of Shading Parameters for Span Set-up Tokens The shading parameter values, i.e. the RGB, Z and  $\alpha$ values, at each of the span endpoints are calculated in the same manner as the X-coordinate. Since W has been previously calculated, it is simply a matter of inserting the provided shading parameter values at the endpoints of the active edges into the linear interpolation function. Referring back to FIG. 9, the endpoints D 905 and E 906, the provided parameter values at each of the endpoints of the active edges, i.e. points A 901, B 902 and C 903, are provided as input to the linear interpolation function. For example, the shading parameters at endpoint D 905 may be calculated 60 using the linear interpolation equation as  $P_D = P_B(1 - W_D) +$  $P_A(W_D)=P_B(5/13)+P_A(8/13)$ ; where  $P_A$  is the provided parameter value at point A 901, P<sub>B</sub> is the provided parameter value at point B 902 and P<sub>D</sub> is the interpolated parameter value at point D 905. Similarly, the shading parameters for the endpoint E 906 may be calculated using the linear interpolation equation as  $P_E = P_A(1 - W_E) + P_C(W_E) = (P_A + P_C)$ 2; where  $P_A$  is the provided parameter value at point A 901,

19 ·

$P_C$  is the provided parameter value at point C 903 and  $P_E$  is the interpolated parameter value at point E 906. These shading parameter values at the endpoints of the span are calculated and propagated through the rendering pipeline through corresponding span set-up tokens.

Generation of a Pixel Interpolation Token

As described above with respect to Stage 1, pixel interpolation tokens are generated after span coordinates have been defined. These end-points, say Xa and Xb, are received by the Horizontal interpolation module, which immediately 10 compares them to determine which is leftmost. It is assumed that Xa is leftmost. If Xb is leftmost, Xa and Xb are swapped. In this scheme, an interpolation weight value W=0 reference refers to the left end of the span (i.e. Xa). A W=1 described above, the interpolation weight value W refers to the relative weight for a direct interpolation function which is used to determine the value of a pixel.

Creating a Pixel Interpolation token requires the generation of two numbers: the target pixel address X and the 20 interpolation weight W. The target pixel address X generation is accomplished by counting from the leftmost X value generated from the vertical interpolation step. For generating W, the method of interpolation must first be determined. In the preferred embodiment, a linear interpolation method 25 taining 1 pixel per clock rendering speeds, the rendering is used. It would be apparent to one skilled in the art to use other interpolation methods, e.g. perspective corrected interpolation. It should be noted that use of alternative interpolation methods would have an effect on W as well as an effect on the direct solution method of linear interpolation 30 utilized in each of the succeeding processing units. It is anticipated that a perspective corrected implementation may be used to calculate W, while the linear interpolation methods retained within each of the processing units, thus enabling a perspective corrected implementation without 35 requiring the replacement of all the processing units of a rendering pipeline.

In the preferred embodiment a function W(X) is calculated for each span. The function W(X) is defined as:

W(X)=(X-X)left)'(Xright-Xleft).

Since a linear interpolation of the pixels across the span is being performed, the slope m of the W(X) function is constant and can be computed once for the span via the equation:

m=1/(Xright-Xleft).

Thus, by substitution the W(X) function can be reduced to the equation:

W(X)=m(X-X)left).

This function is desirable since it minimizes the division operations that would need to be performed for the span. So for each pixel in the span, the x-coordinates of the pixel 55 being rendered and the left most endpoint of the span are inserted into the W(X) function in order to derive the interpolation weight W for that pixel.

FIG. 10 illustrates several pixel locations in a span 1001. The span 1001 was derived using the vertical interpolation 60 of the preferred embodiment with respect to FIG. 9. In any event, counting sequentially as described above, a pixel F 1002 has coordinates (56, 100). The corresponding pixel interpolation weight is calculated as  $W_F = 56 - 53/70 - 53 = 3/70$ 17. A pixel G 1003 has coordinates (61, 100) and a corre- 65 sponding pixel interpolation weight that is calculated as  $W_G=61-53/70-53=8/17$ . Finally, a pixel H 1004 has coor-

dinates (67, 100) and a corresponding pixel interpolation weight that is calculated as  $W_H=67-53/70-53=14/17$ . Horizontal Interpolation

Horizontal interpolation generally refers to the shading of 5 the consecutive pixels within a span. As described above, the first stage of the pipeline performs set-up for the horizontal interpolation process by calculating pixel weighting values, assembling pixel interpolation tokens and generating span set-up tokens. In the preferred embodiment the shading functions are distributed. Each stage or processing unit performs a separate and distinct function in the rendering of a pixel. In the rendering process, horizontal interpolation requires the greatest amount of processing resource.

Advanced shading models require a great deal of data to reference refers to the right end of the span (i.e. Xb). As 15 render a pixel. For example, a Z buffered Phong shading calculation requires Z, diffuse color (RGBad), specular color (RGBs), specular power (Ns), and surface normal vector (NxNyNz) as inputs. Depending on accuracy, this represents about 150 bits of data which must be generated per pixel. To perform the shading of the preferred embodiment, approximately 224 bits would be required. The width of this data contributes to the high cost of known high quality rendering hardware.

> To reduce the width of the data path, while still mainpipeline of the preferred embodiment utilizes distributed parameter interpolation for determining the value of pixels in a span. As described above, each processing unit in the pipeline performs a certain part of the rendering functionality. Each processing unit requires specific parameter data (e.g. the Z buffer processing unit requires the interpolated Z value for each pixel) in order to calculate it's predetermined function. So, set-up tokens generated in stage 1 with the parameter information are first sent down the pipeline. Storage mediums, e.g. registers are embodied within each processing unit for storing the left and right parameter values of the current span (e.g. the Z buffer processing unit has  $Z_0$  and  $Z_1$  registers). Rather than passing actual interpolated parameter values down the pipe, the pixel rendering process is driven by the Pixel Interpolation token. As described above, this token includes W, representing an interpolation weight between 0 and 1. As each processing unit receives the Pixel Interpolation token, it performs a linear interpolation of the left and right span values to calculate the interpolated parameter value for the pixel. So at a pixel location N, in a span with left endpoint A and right endpoint B, a shading parameter value P<sub>N</sub> may be calculated by using the linear interpolation function

$P_N = P_A(1-W) + P_B(W)$ .

50

Because a typical span is several pixels wide, distributed parameter interpolation reduces the amount of data that must flow down through the pipeline. For, example, to do the Z buffer calculation for a 7 pixel wide span, first a Span Setup token is sent, initializing the  $Z_0$  and  $Z_1$  registers (32 bits each). This requires the same bandwidth as sending two actual interpolated Z values down the pipeline. However, after this stage, each pixel in the span only requires a W value to drive direct interpolation means embodied in each of the processing units. In a comparison of a relative bandwidth, sending 7 interpolated Z-Values down the pipeline requires 224 bits, while rendering 7 pixels by sending interpolated values requires 7\*32+7\*10=134 bits. This results in a 50% reduction in data bandwidth requirements. In fact, because many parameters are distributed, and all are interpolated by the same 10 bit W value, the overall saving may be much higher.

Effectively this technique increases silicon complexity to reduce dependence on fast interconnections between processing units. Each processing unit requires multipliers for the interpolation function, whereas typical rendering hardware only needs an accumulator to implement a forward differencing algorithm. Although similar techniques could be used to distribute the forward differencing algorithm (although savings are lower, because more setup accuracy is required), there are other factors which favor distributing the parameter interpolation function. Distributed Parameter 10 Interpolation allows the use of perspective corrected interpolation-forward differencing is limited to linear interpolation. Perspective corrected interpolation provides superior texture mapping quality by avoiding the distortions inherent in linear interpolation.