# Permedia4®

Programmer's Guide - Volume I

# **DRAFT ONLY**

# PROPRIETARY AND CONFIDENTIAL INFORMATION

# 3Dlabs®

# Permedia4®

Programmer's Guide - Volume I

PROPRIETARY AND CONFIDENTIAL INFORMATION

**Issue 2**

i

## **Proprietary Notice**

The material in this document is the intellectual property of **3D***labs*. It is provided solely for information. You may not reproduce this document in whole or in part by any means. While every care has been taken in the preparation of this document, **3D***labs* accepts no liability for any consequences of its use. Our products are under continual improvement and we reserve the right to change their specification without notice. **3D***labs* may not produce printed versions of each issue of this document. The latest version will be available from the **3D***labs* web site.

- **3D***labs* products and technology are protected by a number of worldwide patents. Unlicensed use of any information contained herein may infringe one or more of these patents and may violate the appropriate patent laws and conventions.

- **3D***labs* is the worldwide trading name of **3D***labs* Inc. Ltd.

- **3D***labs*, Permedia4 and Permedia are registered trademarks of **3D***labs* Inc. Ltd.

Microsoft, Windows and Direct3D are either registered trademarks or trademarks of Microsoft Corp. in the United States and/or other countries. OpenGL is a registered trademark of Silicon Graphics, Inc. All other trademarks are acknowledged and recognized.

© Copyright **3D***labs* Inc. Ltd. 1999. All rights reserved worldwide.

Email: info@3dlabs.com Web: http://www.3dlabs.com

**3D**labs Ltd.

Meadlake Place

Thorpe Lea Road, Egham

Surrey, TW20 8HE

United Kingdom Tel: +44 (0) 1784 470555

Fax: +44 (0) 1784 470699

**3D**labs K.K

Shiroyama JT Mori Bldg 16F

40301 Toranomon

Minato-ku, Tokyo, 105, Japan

Tel: +81-3-5403-4653

Fax: +91-3-5403-4646

**3D**labs Inc.

480 Potrero Avenue

Sunnyvale, CA 94086,

United States Tel: (408) 530-4700

Fax: (408) 530-4701

# **Change History**

| Document | Issue | Date         | Change                                                      |

|----------|-------|--------------|-------------------------------------------------------------|

| 160.3.0  | 1     | 1 October 99 | First DRAFT Issue.                                          |

| 160.3.0  | 2     | 16 June 2001 | Improvements/corrections to LB and FB; removed incorrect    |

|          |       |              | footnote ref to PEREN004 (DMA Continue); clarified opaque   |

|          |       |              | span color masking; corrected PixelSize use; deleted FCP    |

|          |       |              | reference in GID position text, changed PCI map access from |

|          |       |              | 2&4 to 1&2.                                                 |

#### Contents Proprietary Notice......i Contents 1.1 1.2 Further Reading ......1-2 ARCHITECTURE OVERVIEW.......2-1 2.1 Functional Overview.....2-1 2.2 2.3 2.3.1 Task Switching 2-3 2.4 Processor evolution and programming changes ......2-3 2.4.1 2.4.2 PROGRAMMING MODEL...... 3-1 3.1.1 3.1.2 Efficiency Issues and Register Types 3-2 3.2 3.2.1 FIFO control 3-3 3.2.2 The DMA Interface 3-5 3.2.3 Vertex Loading for Primitives and Data Re-ordering 3-13 3.2.4 Backface Cull and Texture Setup Functions 3-15 3.3 3.4 3.5 3.6 3.6.1 3.7 3.8 3.8.1 Context Dump/Restore 3-21 3.8.2 3.9

| 4.1 Introduction  4.2 Localbuffer (LB)                                                                                                                                                       | 4-1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.2.1 Localbuffer Management 4.2.2 Layout 4.2.3 Pixel Formats 4.2.4 Pixels and Spans 4.2.5 Clearing the Localbuffer using FBWrite 4.2.6 GID field 4.2.7 Stencil Field 4.2.8 FrameCount Field | 4-1  |

| 4.2.2 Layout                                                                                                                                                                                 | 4-1  |

| 4.2.3 Pixel Formats                                                                                                                                                                          | 4-1  |

| <ul> <li>4.2.4 Pixels and Spans</li> <li>4.2.5 Clearing the Localbuffer using FBWrite</li> <li>4.2.6 GID field</li> <li>4.2.7 Stencil Field</li> <li>4.2.8 FrameCount Field</li> </ul>       | 4-2  |

| 4.2.5 Clearing the Localbuffer using FBWrite 4.2.6 GID field                                                                                                                                 | 4-3  |

| 4.2.6 GID field                                                                                                                                                                              | 4-3  |

| 4.2.7 Stencil Field                                                                                                                                                                          | 4-3  |

| 4.2.8 FrameCount Field                                                                                                                                                                       | 4-4  |

|                                                                                                                                                                                              | 4-4  |

| 429 Texture Mat Storage                                                                                                                                                                      | 4-4  |

| 7.2.) 1 Caput 1.1.49 Storage                                                                                                                                                                 | 4-5  |

| 4.2.10 Source and Destination Reads                                                                                                                                                          | 4-5  |

| 4.2.11 LB Writes                                                                                                                                                                             | 4-7  |

| 4.3 Framebuffer (FB)                                                                                                                                                                         | 4-9  |

| 4.3.1 Framehuffer Management                                                                                                                                                                 | 4-10 |

| 4.3.2 Framehuffer Layout                                                                                                                                                                     | 4-10 |

| 4.3.3 Block Writes                                                                                                                                                                           | 4-10 |

| 4.3.4 Pixels and Spans                                                                                                                                                                       | 4-11 |

| 4.4 Double Buffering                                                                                                                                                                         | 4-12 |

| 4.4.1 BitBlt Double Buffering                                                                                                                                                                | 4-13 |

| 4.4.2 Page Flipping                                                                                                                                                                          | 4-13 |

| 4.4.3 Video Output                                                                                                                                                                           | 4-14 |

| 4.4.4 Texture Map Management                                                                                                                                                                 | 4-14 |

| 4.4.5 Source and Destination Address Calculation                                                                                                                                             | 4-14 |

| 4.4.6 Origin and Stripe Data                                                                                                                                                                 | 4-14 |

| 4.4.7 Write Combining                                                                                                                                                                        | 4-14 |

| 4.5 Suspend and Swap on Frame Blank                                                                                                                                                          | 4-15 |

| 4.6 Downloading Data                                                                                                                                                                         | 4-15 |

| 4.7 Controlling the VTG or RAMDAC                                                                                                                                                            | 4-15 |

| 4.8 Texture Mapping                                                                                                                                                                          | 4-16 |

| 4.8.1 Texture Memory Layouts                                                                                                                                                                 | 4-16 |

| 4.8.2 Address Calculation                                                                                                                                                                    | 4-17 |

| 4.8.3 Primary Cache                                                                                                                                                                          | 4-18 |

| 4.9 Virtual Texture Management                                                                                                                                                               |      |

| 4.9.1 Mapping an Address                                                                                                                                                                     | 4-21 |

|   | 4.9.2    | Logical Page Mapping                        | 4-21        |

|---|----------|---------------------------------------------|-------------|

|   | 4.9.3    | Translation Look-aside Buffer (TLB)         | 4-22        |

|   | 4.9.4    | Logical Page Table                          | 4-22        |

|   | 4.9.5    | Memory Allocation                           | 4-24        |

|   | 4.9.6    | Programming Notes for Non-Host Textures     | 4-20        |

|   | 4.9.7    | Programming Notes for Host Textures         | 4-29        |

|   | 4.10 3D  | and Other Textures                          | 4-31        |

|   | 4.10.1   | 3D Textures                                 | 4-31        |

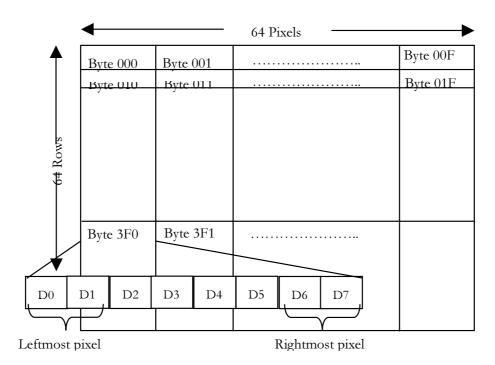

|   | 4.10.2   | Bitmaps                                     | 4-32        |

|   | 4.10.3   | Indexed Textures                            | 4-33        |

|   | 4.10.4   | YUV 422 Textures                            | 4-33        |

|   | 4.10.5   | Borders                                     | 4-33        |

|   | 4.11 Tex | ture Implementation                         | 4-34        |

|   | 4.11.1   | Overview                                    | 4-34        |

|   | 4.11.2   | Memory Interfaces                           | 4-37        |

|   | 4.11.3   | Translation Look-Aside Buffer (TLB)         | 4-40        |

|   | 4.11.4   | Memory Allocater                            | 4-40        |

|   | 4.11.5   | Dispatcher                                  | 4-41        |

|   | 4.12 Tex | ture DMA Controller                         | 4-41        |

| 5 | VIDEO    | SYSTEM                                      | <b>5-</b> 1 |

|   | 5.1 Vid  | eo Unit                                     | 5-1         |

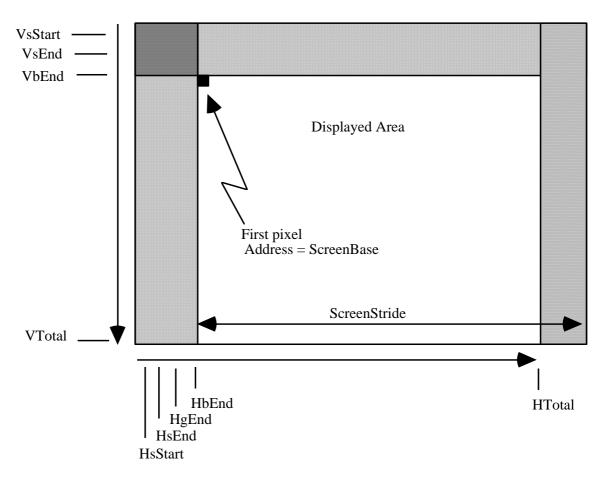

|   | 5.1.1    | Programming The Video Unit Timing Registers | 5-1         |

|   | 5.1.2    | Setting the display memory region           | 5-2         |

|   | 5.1.3    | Setting Video Timing Parameters             | 5-2         |

|   | 5.1.4    | Configuring the VideoUnit                   | 5-4         |

|   | 5.1.5    | Video FIFO control                          | 5-7         |

|   | 5.1.6    | Example Timing Values                       | 5-8         |

|   | 5.2 RA   | MDAC                                        | 5-10        |

|   | 5.2.1    | Programming The RAMDAC registers            | 5-10        |

|   | 5.2.2    | Basic RAMDAC Configuration                  | 5-12        |

|   | 5.2.3    | Color Palette RAM                           | 5-13        |

|   | 5.2.4    | Panning The Video Display                   | 5-14        |

|   | 5.2.5    | Configuring The Cursor                      | 5-15        |

|   | 5.2.6    | Digital Flat Panel Display Output           | 5-17        |

|   | 5.2.7    | Programming The Clocks                      | 5-17        |

|   | 5.3 Vid  | eo Overlay                                  | 5-19        |

#### Front Matter

| 5.3.1 | Programming The Video Overlay Unit Registers5-20  |

|-------|---------------------------------------------------|

| 5.3.2 | Basic Video Overlay Configuration5-20             |

| 5.3.3 | Scaling Images Through The Video Overlay Unit5-23 |

| 5.3.4 | Interlaced Video With The Video Overlay Unit5-24  |

| 5.3.5 | Video Overlay Unit Fifo Control5-25               |

1

# Introduction

The Permedia4 family of high performance PCI/AGP graphics processors combine workstation class 3D graphics acceleration and state of the art 2D performance in a single chip. All 3D rendering operations are accelerated by Permedia4, including Gouraud shading, depth buffering, antialiasing, alpha blending and texture mapping.

Implemented around a scaleable memory architecture, Permedia4 reduces the cost and complexity of delivering high performance 3D graphics within a windowing environment - making it ideal for a wide range of graphics products from PC boards to high end workstation accelerators.

This document has been written as the reference for programmers and system designers who wish to develop software to drive the Permedia4. There are separate manuals for related members of the Permedia, GLINT Gamma and GLINT Delta families. Familiarity with the OpenGL Specification will be useful when reading this document.

#### 1.1 How to use this manual

The *Permedia4 Programmers' Guide* (Volumes I and II) should be read together with the *Permedia4 Reference Guide*, which contains all of the register descriptions. The Programmers Guide is in two volumes. The present volume contains:

- Chapter 2 an overview of Permedia4, its capabilities and architecture, and highlights key differences between the Permedia4 and GLINT MX or Permedia2/3.

- Chapter 3 details of the programming model for the chip, including the DMA interface, host bypass route to unified framebuffer, vertex loading and context changing.

- Chapter 4 describes the data structures that Permedia4 supports in the framebuffer and the localbuffer, including virtual texture management

- Chapter 5 describes the Video System including timing, RAMDAC and overlays.

In Volume II of the Programmers Guide we examine Permedia4 graphics rendering. The chapters begin with an overview and discussion of 3d and 2d graphics pipelining, followed by a walkthrough of the major functional groups (Scissor, Fog, Alpha Test, etc.) and a closing discussion of initialization and performance issues. In addition, volume II contains two appendices and a glossary:

- Appendix A gives the format used in the pseudocode examples throughout the document.

- Appendix B gives example code for rendering a triangle accurately.

- Following the body of the manual, a glossary of technical terms defines many of the 2D/3D graphics terms used throughout.

## 1.2 Further Reading

- Permedia4 Reference Guide, 3Dlabs

- Permedia4 Architecture Overview, 3Dlabs

- OpenGL Programming Guide, Jackie Neider et al, Reading MA: Addison-Wesley

- OpenGL Reference Manual, Jackie Neider et al, Reading MA: Addison-Wesley

- The OpenGL Graphics System: A Specification (Version 1.1), Mark Segal and Kurt Akeley, SGI (see below)

- PCI Local Bus Specification Rev2.1, 1Jun95, PCI Special Interest Group, PO Box 14070, Hillsboro, Oregon 97214 (503-797-4207)

- Multiprocessor Methods For Computer Graphics Rendering, Scott Whitman, ISBN 0-86720-229-7

- Microsoft WIN32 Software Development Kit 3.1, Microsoft

- Windows NT 3.1 Graphics Programming, Emeryville CA, Ziff-Davis Press

- The X Window System, Sebastopol CA, O'Reilly & Associates Inc.

- The X Window System Server, Elias Israel and Erik Fortune, Digital Press

- Computer Graphics: Principles and Practice, James D. Foley et al, Reading MA: Addison-Wesley

2

# **Architecture Overview**

#### 2.1 Functional Overview

Permedia4 is a 3D graphics processor consisting of a geometry set-up processor and rastering engine together with external interfaces. It fully implements the functionality of "The OpenGL Machine" from edge walk and span interpolation through fragment level processing including:

- Point, Line, Triangle and Bitmap primitives

- Flat and Gouraud shading

- Texture and Fog

- Antialiasing

- Scissor and Stipple

- Alpha test, Stencil test, Depth (Z) buffer test

- Alpha Blending

- Dithering

- Logical Operations

- Writemasks, spans and images

The 300 MFLOPS geometry set-up unit accepts vertex, color, depth, fog and texture parameters in IEEE single precision floating point format. It is both OpenGL and Direct3D compliant and supports the Direct3D TLVERTEX data type and the DirectX 6 Flexible Vertex Format (FVF) extensions.

Systems using Permedia4 can easily be configured to address a wide range of price, performance and functionality points by simply tuning the external memory design. Permedia4 supports 8, 16 and 32-bit RGBA and 8-bit color index framebuffers.

The unified memory can be up to 32Mbytes in size. Permedia4 also supports DMA mode virtual texture and demand page texturing using a 4K local L2 texture cache to incrementally access up to 256MB of addressable host texture.

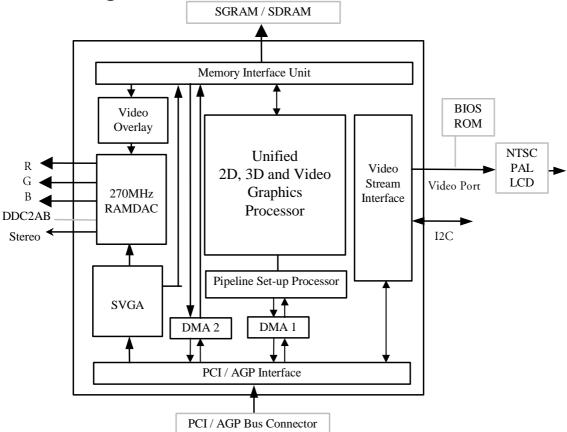

# 2.2 Block Diagram

Figure 2-1 High level blocks in the Permedia4 architecture

#### 2.3 Host Interfaces

The Permedia4 architecture consists of a Graphics Core augmented by I/O and memory interfaces as shown in Figure 2-1. There are three external interfaces: the Host Bus Interface (PCI/AGP Local Bus), the SGRAM/SDRAM unified memory Interface, and a Video Stream interface.

There are two ways to program the graphics processor, either by writing to memory mapped registers, or by sending command packets to the input FIFO (which may be done by HostIn DMA or programmed IO). Both methods produce tag data that is sent to the pipeline.

A write to a register creates a tag/data pair "message" which has a tag formed from the lower bits of the address. This tag and the data associated with it are sent to the input FIFO. If the data has been written directly to the input FIFO address range (or fetched by DMA) a special tag marking it as part of a packet is sent with the data to the input FIFO. The decode process converts packets into tag/data streams, so that after this process both methods of progaming are indistinguishable.

Conceptually Permedia4 can be viewed as either a register file or a message passing system. As a register file, it appears as a flat block of memory-mapped registers. When a driver is initialized it maps the register file into address space. Each register has an associated address tag containing the offset from the file base in multiples of 8 bytes

(since all registers reside on a 64-bit boundary). The most straightforward way to load a data value into a register is to write the data to its mapped address.

As a message passing system, Permedia4 consists of processing units connected in a long pipeline with message-passing communication between adjacent units. There is a small amount of buffering between units, the size being appropriate to the local communications requirements and unit throughput. Although the units operate asynchronously they are in practice synchronised by the common clocks.

Units are in fact functional groupings - virtual units - rather than strictly physical entities. For example, although Frame and Local Buffer "units" exist they operate on contiguous, unified memory. The difference is that local buffer functions involve GID, stencil and depth facilities while frame buffer functionality primarily relates to the 8/16/32 bpp color formats.

Each unit can be disabled, and the host can mimic any unit in the chain by inserting messages which that unit would normally generate, effectively bypassing the unit. The host can also directly access the framebuffer, and context dump/restore is also supported.

When the control registers have been primed with the data needed to render the primitive, the render process is triggered by writing to a Command register such as **Render2D** or **ContinueNewLine**.

### 2.3.1 Task Switching

Where multiple applications wish to make simultaneous access to Permedia4, it is the responsibility of the software driving the chip to handle loading and to load the correct state. Permedia4 has been designed to support a number of different software architectures. Facilities available include:

- Synchronous operation a new task can load its context without waiting for current rendering to complete

- All loadable states can be read back

- Sync command to flush all rendering can be polled or return an interrupt

# 2.4 Processor evolution and programming changes

Although part of the same family as the Permedia 1 and 2, Permedia 4 functionality changes affect almost all areas of operation, including performance and feature benefits and programming differences from earlier chipsets such as Permedia 3. Performance and feature changes include:

- Increased clock speeds

- Low latency command DMA

- 2M drawn texture-mapped polygons/sec

- 250M perspective correct, bilinear filtered, dual texture texels/sec

- 125M perspective correct, per pixel MIP-mapped trilinear filtered, texture mapped, depth buffered, fogged and blended pixels/sec

- 8M backface-culled polygons/sec

- Enhanced Texture format (Delta) unit

- Support for HDTV screen resolutions, e.g. 1920x1080

- Optimized for 32-bit displays at resolutions up to 2048x1536

- 266 MHz AGP 4X DMA and Execute Mode support

- 3.3V and 1.5V AGP signal support

- 128 bit internal bus

- LCD flat panel and TV display support

- MPEG2 compatible video playback acceleration with motion compensation, hardware scaling and filtering

#### 2.4.1 Programming changes from earlier products

Relative to the GLINT MX or Permedia2, for example, there are a large number of new, changed or deleted registers. There are also a significant number of minor corrections in implementation. These result in significant programming changes, particularly in

- buffer addressing,

- · register width,

- · context management,

- texture formatting,

- · bitmask spans and span alignment,

- logical operations,

- unit enabling,

- non-linear Z,

- pixel size definition and subpixel correction,

- scale by Q, texture wrap and LOD calculations

- OGL blend modes with multiple texturing

- DMA interrupts

...as well as minor changes in register and bitfield nomenclature and functionality.

## 2.4.2 Permedia3/Permedia4 Programming Differences

Relative to Permedia3, changes to Permedia4 primarily affect hardware, improving reliability and performance by removing technical obstacles, clearing errata and adding bandwidth enhancements, particularly support for PCI 2.2 and the AGP4X bus standard. Programming changes are noteworthy but few:

- Introduction of a new DeltaFormat unit with early backface cull and texture functionality

- Additional OGL Alphablend interpolations

- A number of bitwise register changes

For a list of errata changes refer to the *Permedia3 Errata* document and the *Permedia4 Reference Guide* volume I, section 1.2 - P3/P4 Differences.

3

# **Programming Model**

This chapter describes the programming model for Permedia4. It describes the interface conceptually rather than detailing specific registers and their exact usage. In-depth descriptions of how to program Permedia4 for specific drawing operations may be found in later chapters. Register specifications may be found in the *Permedi3 Reference Guide*.

## 3.1 Permedia4 as a Register file

Of the two I/O models (Message passing or Register file) of Permedia4 the simplest approach is to view it as a flat block of memory-mapped registers. This register file appears as part of Region 0 of the PCI address map<sup>1</sup>. When a Permedia4 host software driver is initialized it maps the register file into its address space.

Each register has an associated address tag giving its offset from the base of the register file. Since all registers reside on a 64-bit boundary, the tag offset is measured in multiples of 8 bytes. The obvious way to load a value into a register is to write the data to its mapped address.

In reality, the chip interface comprises a 32-entry deep FIFO, and each write to a register causes the written *value* and the register's *address tag* to be written as a new entry in the FIFO. Programming Permedia4 to draw a primitive then consists of writing initial values to the appropriate registers followed by a write to a command register. The last write triggers the start of rendering.

Permedia4 has more than 850 registers. These are individually defined in the *Permedia4 Reference Guide* (RG). All registers are 32 bits wide and should be 32-bit addressed. Many registers are paired to allow 64bit data handling or split into bit fields for mode setting.

*Note:* Bit 0 is the least significant bit.

In future chip revisions the register file may be extended and currently unused bits in certain registers may be assigned new meanings. Developers should ensure that only defined registers are written to and that undefined bits in registers are written as zeros. The exception to this rule is in some floating point registers where good practice is to use sign extended values.

Fields marked "not used" in register definitions are not usually being considered for internal use or development. Fields marked "reserved" are either used internally or reserved for future development.

# 3.1.1 Register Types

Permedia4 has three main types of register:

- Control Registers

- Command Registers

**3D**labs

<sup>1</sup> See the Permedia Reference Guide (chapter 2) for more information about the PCI map.

#### Internal Registers

#### 3.1.1.1 Control Registers

Most registers are Control Registers. These are updated only by the host - Permedia4 effectively uses them as read-only registers. Examples of control registers are the Scissor Clip unit min and max registers (**ScissorMaxXY**, **ScissorMinXY**). Once initialized by the host, the chip only reads these registers to determine the scissor clip extents.

#### 3.1.1.2 Command Registers

Command Registers are those which, when written to, start a rendering task (although some command registers such as **ResetPickResult** or **Sync** perform other tasks).

There are two types of command registers: begin-draw and continue-draw:

- Begin-draw commands start rendering with the values specified by the control registers.

- Continue draw commands cause drawing to continue with internal register values as

they were when the previous drawing operation completed. Using continue-draw

commands can significantly reduce the amount of data that has to be loaded when

drawing multiple connected objects such as polylines.

#### **Render** and **ContinueNewLine** are typical command registers.

*Note:*

For convenience in this document we often refer to "sending a Render command" rather than saying "the Render Command register is written to, which initiates drawing".

#### 3.1.1.3 Internal Registers

Internal Registers are not writeable by host software. They are used internally by the chip to keep track of changing values. Some control registers have corresponding internal registers. When a begin-draw command is sent the internal registers are updated with the values in the corresponding control registers before rendering starts. If a continue-draw command is sent then this update does not happen and drawing continues with the current values in the internal registers.

For example, during line drawing the **StartXDom** and **StartY** control registers specify the (x, y) coordinates of the first point in the line. When a begin-draw command is sent these values are copied into internal registers. As the line drawing progresses these internal registers are updated to contain the (x, y) coordinates of the pixel being drawn. When drawing has completed the internal registers contain the (x, y) coordinates of the next point that would have been drawn. If a continue-draw command is now given these final (x, y) internal values are not modified and further drawing uses these values. If a begin-draw command had been used the internal registers would have been re-loaded from the StartXDom and StartY registers.

Internal registers can usually be ignored except when context switching. It is helpful to appreciate that they exist in order to understand the continue-draw commands.

## 3.1.2 Efficiency Issues and Register Types

Software developers wishing to write device drivers for Permedia4 should become familiar with the different types of registers. Some control registers such as the **StartX** and **StartY** registers have to be updated for almost every primitive whereas other control registers

such as the **ScissorMaxXY** or the **LogicalOpMode** can be updated much less frequently. Pre-loading of the appropriate control registers can reduce the amount of data that has to be loaded into the chip for a given primitive thus improving efficiency. In addition, as described above, the final values in internal registers can sometimes be used for subsequent drawing operations.

The cross-reference listing in the *Permedia4 Reference Guide* (Chapter 6) identifies the graphics registers by type.

Due to the structure of the internal HyperPipeline, when several graphics control registers are being loaded it is slightly more efficient to load them in pipeline order. For instance registers in the rasterizer should be loaded before registers in the GID/Stencil/Depth unit.

#### 3.2 Permedia I/O Interface

There are two ways to program the graphics processor: either by writing to memory mapped registers, or by sending command packets to the input FIFO (which may be done by HostIn DMA or programmed IO). Both methods convert to tag/data "messages" that are sent to the pipeline, as described earlier<sup>2</sup>.

#### 3.2.1 FIFO control

The actual register is not updated until Permedia4 processes an entry. When the chip is busy performing a time consuming operation (e.g. drawing a large polygon), and not draining the FIFO very quickly, it is possible for the FIFO to become full. If a write to a register is performed when the FIFO is full no entry is put into the register.

#### 3.2.1.1 PCI Disconnect

Setting bit 0 of the **FIFODiscon** register to 1 enables FIFO disconnection. It does not require host polling, but forces host write retries until the data is accepted. This may affect other time-critical peripherals on the PCI bus, e.g. sound cards, and sometimes drops interrupts. Despite the speed advantage it is therefore advisable to avoid this approach when large primitives are likely to slow FIFO clearing.

#### 3.2.1.2 Polling InFIFOSpace

The input FIFO is 32 entries deep and each entry consists of a tag/data pair. The **InFIFOSpace** register can be read to determine how many entries are free. The value returned by this register will never be greater than 32<sup>3</sup>.

An example of loading registers using the FIFO is given below. The pseudocode fills a series of rectangles. Details of the conventions used in the pseudocode examples may be found in Appendix B.

Assume that the data to draw a single rectangle consists of 8 words (including the **Render** command).

```

Note: Some data values are in 16.16 fixed point format. for (i = 0; i < nrects; ++i) { while (*InFIFOSpace < 8);

```

<sup>&</sup>lt;sup>2</sup> Chapter 2, section 3.

<sup>&</sup>lt;sup>3</sup> When the InFIFOspace register is read, the value must be clamped to a maximum of 120 before it is used - refer to *Permedia4 Errata and Alerts*, PEREN0011.

```

// wait for room

StartXDom(rect->x1 << 16);

StartXSub(rect->x2 << 16);

dXDom(0x0);

dXSub(0x0);

Count(rect->y2 - rect->y1);

YStart(rect->y1 << 16);

dY(1 << 16);

Render(PERMEDIA4_TRAPEZOID_PRIMITIVE);

}

```

Checking the status of the FIFO before each write is inefficient so it is checked before loading the data for each complete rectangle. Since the FIFO is 32 entries deep, a further optimization is to wait for all 32 entries to be free after every second rectangle. Further optimization is possible by moving **dXDom**, **dXSub** and **dY** outside the loop (as they are constant for each rectangle) and doing the FIFO wait after every third rectangle.

The **InFIFOSpace** FIFO control register contains a count of the number of entries currently free in the FIFO. The chip increments this register for each entry it removes from the FIFO and decrements it every time the host puts an entry into the FIFO.

The graphics core registers cannot be read through the core FIFO interface. Command buffers generated to be sent to the FIFO interface can be read directly using the DMA controller.

#### 3.2.1.3 Direct writes to the FIFO

In addition to writing to the register file you can send data directly to the core via the input FIFO. Any address in the PCI region 0 address map range can be read (normally a program will choose the first address and use this as the address for the output FIFO). All 32-bit addresses in this region perform the same function – the range of addresses is provided for data transfer schemes which force the use of incrementing addresses.

Writing to a location in this address range provides raw access to the input FIFO. Thus the same address can be used for both input and output FIFOs. Reading gives access to the output FIFO; writing gives access to the input FIFO.

When writing to a memory-mapped register the register file has a unique address for each register. This allows Permedia4 to construct the appropriate tag, associate it with the data and inserted the tag/data pair into the input FIFO.

When writing to the raw FIFO address an address tag description must first be written *followed by* the associated data. In fact, the format of the tag descriptions and their data is identical to that described below for DMA buffers<sup>4</sup>. The DMA mechanism can be thought of as an automatic way of writing to the raw input FIFO address.

Note: When writing to the raw FIFO address the FIFO full condition must still be checked by reading the **InFIFOSpace** register. However, writing tag

\_

<sup>&</sup>lt;sup>4</sup> Instead of using the Permedia DMA it is possible to transfer data to Permedia 4 by constructing a DMA-style buffer of data and then copying each item in this buffer to the raw input FIFO address. Based on the tag descriptions and data written Permedia 4 constructs tag/data pairs to enter as real FIFO entries.

descriptions does not put tag entries into the FIFO – it simply establishes a set of tags to be paired with the subsequent data.

Because direct writes to the FIFO do not place tag values in the FIFO itself, the FIFO space can be used for data only - free space need be ensured only for actual data items that are written (not the tag values). For example, where e.g. each tag is followed by a single data item, it would be possible to do 32 writes to an empty buffer before checking for free space.

See the *Permedia4 Reference Guide* for more details of the Graphics Processor FIFO Interface address range.

#### 3.2.2 The DMA Interface

Loading registers directly via the FIFO can be an inefficient way to download data. The FIFO can accommodate only a small number of entries, so it has to be interrogated often to find out how much space is left. Also, if an API function requires a large amount of data then the function cannot return until almost all the data has been consumed. This may take some time depending on the types of primitives being drawn.

To avoid these problems Permedia4 provides an on-chip DMA controller which can be used to load data from arbitrary sized (< 64K 32-bit words) host buffers into the FIFO. The DMA may be either rectangular or sequential. The address of the latest DMA data read from memory (for the input DMA only) can be readback; this allows the progress of the DMA to be monitored and the DMA buffer reused as soon as it is free. The readback is resynchronizing so the pipeline does not have to be sync'd first.

#### 3.2.2.1 DMA Operation

The normal mode of operation is to build a series of small DMA buffers in system memory and then send commands to the input FIFO to load them. These commands may be for complete DMA operations or continue operations to extend the current DMA. Continues are more efficient and should be used where possible.

Two DMA buffers can be maintained at the same time. If a new address is sent, it can be read from the FIFO before the current DMA completes. At chip reset the *BusMasterEnable* bit in the **CFGCommand** register must be set to allow DMA to operate (see the *Permedia4 Reference Guide* for further details). Then, for the simplest form of DMA, the host software has to prepare a host buffer containing register address tag descriptions and data values.

The host then writes the base address of this buffer to the **DMAAddress** register and the count of the number of words to transfer to the **DMACount** register. Writing to the **DMACount** register starts the DMA transfer and the host can now perform other work.

In general, if the complete set of rendering commands required by a given call to a driver function can be loaded into a single DMA buffer, then the driver function can return immediately. Meanwhile, in parallel, Permedia4 is reading data from the host buffer and loading it into its FIFO. In addition, some algorithms require that data be loaded multiple times (e.g. drawing the same object across multiple clipping rectangles). Since the DMA only reads the buffer data it can be downloaded many times simply by restarting the DMA. This can be very beneficial if composing the buffer data is a time consuming task.

An additional mechanism, the **HostInID** register, can be used to mark any point in the command stream so that the use of index and vertex buffers can be monitored. This is a register that is loaded with an ID field; like the DMA address register, this can be read at any time.

To prevent overflows the DMA controller automatically waits until there is room in the FIFO before doing any transfers. The only restriction on the use of DMA control registers is that before attempting to reload the **DMACount** register the host software must wait until previous DMA has completed. The **DMAAddress** register can, however, be reloaded while the previous DMA is in progress since the address is latched internally at the start of the DMA transfer.

#### 3.2.2.2 Typical use

Many display driver functions can be implemented using the following skeleton structure:

```

do any pre-work

DMAAddress(address of dma_buffer);

while (*DMACount != 0); // wait for DMA to complete

// note use of backoff algorithm here

copy render data into DMA buffer

DMACount(number of words in DMA buffer)

return

```

A further optimization is to use a double buffered mechanism with two DMA buffers. This allows the second buffer to be filled before waiting for the previous DMA to complete thus further improving the parallelism between host and Permedia4 processing.

```

do any pre-work

get free DMA buffer and mark as in use

put render data into this new buffer

DMAAddress(address of new buffer)

while (*DMACount != 0)

; // wait for DMA to complete

// using a back off algorithm

DMACount(number of words in new buffer)

mark the old buffer as free

return

```

Double Buffering is discussed in greater detail in Chapter 4, section 10.

In general the DMA buffer format consists of a 32-bit address tag description word followed by one or more data words. The DMA buffer consists of one or more sets of these formats. The following paragraphs describe the different types of tag description words that can be used.

#### 3.2.2.3 DMA Tag Description Format

When DMA is performed each 32-bit tag description in the DMA buffer conforms to the following format:

A packet is made up of a header followed by some number of data items. The format of the header is:

| Bits  | Field         | Description                            |                   |

|-------|---------------|----------------------------------------|-------------------|

| 0-3   | Offset        | Index into 16 tags in each group       |                   |

| 4-13  | Group         | 16 tags usually grouped by association |                   |

| 14-15 | Туре          | Type of packet,                        |                   |

|       |               | 0 = hold tag                           | 1 = increment tag |

|       |               | 2 = indexed tag                        | 3 = reserved      |

| 16-31 | Count or mask | Meaning changes with type of packet    |                   |

Figure 3.1 DMA Tag Description Format

There are 3 different tag addressing modes for DMA: hold, increment and indexed. The different DMA modes are provided to reduce the amount of data which needs to be transferred, hence making better use of the available DMA bandwidth.

**Hold**: Tag formed from group and offset, kept constant for the next count + 1 data

items.

**Increment**: Tag formed from group and offset, incremented by one for each of the next

count + 1 data items.

**Index**: Tag formed from group (offset ignored) and mask showing which of the 16

tags in the group are valid. Tags formed in incrementing order and paired with

the data.

These are described in DMA Tags below.

#### 3.2.2.4 DMA and Security

To avoid accidental writes during DMAs to registers which can hang the entire graphics pipeline, Permedia4 supports a security mode. When the **Security** register *secure* bit is set the following tags are filtered out of DMA command buffers:

FilterMode

**VTGAddress**

**VTGData**

Security

**DMARectangleWrite**

DMAOutputCount

DMAFeedback

ContextDump

ContextRestore

ContextData

#### 3.2.2.5 DMA Tags - Hold Format

In this format the 32-bit tag description contains a tag value and a count specifying the number of data words following in the buffer. The DMA controller writes each of the data words to the same address tag. This is useful e.g. for image download where pixel data is continuously written to the FrameBuffer. The bottom 11 bits specify the register to which the data should be written; the high-order 16 bits specify the number of data words (minus 1) which follow in the buffer and which should be written to the address tag

Note: The 2-bit mode field for this format is zero so a given tag value can simply be loaded into the low order 16 bits.

A special case of this format is where the top 16 bits are zero indicating that a single data value follows the tag (*i.e.* the 32-bit tag description is simply the address tag value itself). This allows simple DMA buffers to be constructed which consist of tag/data pairs. For example to render a horizontal span 10 pixels long starting from (2,5) the DMA buffer could look like this:

| StartXDom                  |

|----------------------------|

| 2 << 16                    |

| StartY                     |

| 5 << 16                    |

| StartXSub                  |

| 12 << 16                   |

| Count                      |

| 1                          |

| Render                     |

| (trapezoid render command) |

#### 3.2.2.6 DMA Tags - Increment Format

| address-tag with Count=n-1, Mode=1 |  |

|------------------------------------|--|

| value 1                            |  |

|                                    |  |

| value n                            |  |

This format is similar to the Hold format except that as each data value is loaded the address tag is incremented (the value in the DMA buffer is not changed; Permedia4 updates an internal copy). Thus, this mode allows contiguous Permedia4 registers to be loaded by specifying a single 32-bit tag value followed by a data word for each register.

The low-order 11 bits specify the address tag of the first register to be loaded. The 2 bit mode field is set to 1 and the high-order 16 bits are set to the count (minus 1) of the number of registers to update. To enable use of this format, the Permedia4 register file has been organized so that registers which are frequently loaded together have adjacent address tags. For example, the 32 **AreaStipplePattern** registers can be loaded as follows:

| AreaStipplePattern0, Count=31, Mode=1 |

|---------------------------------------|

| row 0 bits                            |

| row 1 bits                            |

|                                       |

| row 31 bits                           |

#### 3.2.2.7 DMA Tags - Indexed Format

Permedia4 address tags are 11 bit values. For the purposes of the Indexed DMA Format they are organized into major groups and within each group there are up to 16 tags. The low-order 4 bits of a tag give its offset within the group. The high-order bits give the major group number. The *Permedia4 Reference Guide* (chapter 6) lists the individual registers with their Major Group and Offset.

This format allows up to 16 registers within a group to be loaded while still only specifying a single address tag description word.

| address tag with Mask, Mode=2 |  |

|-------------------------------|--|

| value 1                       |  |

|                               |  |

| value n                       |  |

If the Mode of the address tag description word is set to Indexed mode then the high-order bits are used as a mask to indicate which registers within the group are to be used. The bottom 4 bits of the address tag description word are unused.

The group is specified by bits 4 to 8. Each bit in the mask is used to represent a unique tag within the group. If a bit is set then the corresponding register will be loaded. The number of bits set in the mask determines the number of data words that should be following the tag description word in the DMA buffer. The data is stored in order of increasing corresponding address tag. For example,

| 0x003280F0 |  |

|------------|--|

| value 1    |  |

| value 2    |  |

| value 3    |  |

The Mode bits are set to 2 so this is indexed mode. The Mask field (0x0032) has 3 bits set so there are three data words following the tag description word. Bits 1, 4 and 5 are set so the tag offsets are 1, 4 and 5. The major group is given by the bits 4-8 which are 0x0F (in indexed mode bits 0-3 are ignored). Thus the actual registers to update have address tags 0x0F1, 0x0F4 and 0x0F5 corresponding to registers dRdx, dGdx and dRdyDom. These are updated with value 1, value 2 and value 3 respectively.

#### 3.2.2.8 DMA Example

The following pseudo-code example shows how to draw a series of rectangles using the DMA controller. This example uses a single DMA buffer and the simplest case which is Hold Mode for the tag description words in the buffer.

```

UINT32 *pbuf;

DMAAddress(physical address of dma_buffer)

while (*DMACount != 0)

; // wait for DMA to complete

```

```

pbuf = dma_buffer;

*pbuf++ = Permedia4TagdXDom;

*pbuf++ = 0;

*pbuf++ = Permedia4TagdXSub;

*pbuf++ = 0;

*pbuf++ = Permedia4TagdY;

*pbuf++ = 1 << 16;

for (i = 0; i < nrects; ++i) {

*pbuf++ = Permedia4TagStartXDom;

*pbuf++ = rect->x1 << 16; // Start dominant edge

*pbuf++ = Permedia4TagStartXSub

*pbuf++ = rect->x2 << 16; // Start of subordinate

*pbuf++ = Permedia4TagCount;

*pbuf++ = rect->y2 - rect->y1;

*pbuf++ = Permedia4TagYStart;

*pbuf++ = rect->v1 << 16;

*pbuf++ = Permedia4TagRender;

*pbuf++ = Permedia4 TRAPEZOID PRIMITIVE;

}

// initiate DMA

DMACount((int)(pbuf - dma_buffer))

```

The example assumes that a host buffer has been previously allocated and is pointed at by "dma buffer".

#### 3.2.2.9 DMA Buffer Addresses

Host software must generate the correct DMA buffer address for the DMA controller. Normally this means that the address passed to Permedia4 must be the physical address of the DMA buffer in host memory. The buffer must also reside at contiguous physical addresses as accessed by Permedia4. On a system which uses virtual memory for the address space of a task, some method of allocating and mapping contiguous physical memory within this space must be used.

Note:

This does not apply to Virtual Texturing using the TextureDownloadControl register with SlaveTexture enabled for DMA texel data. Texture pages are relocatable and do not need to be contiguous in local memory.

If the virtual memory buffer maps to non-contiguous physical memory then the buffer must be divided into sets of contiguous physical memory pages and each of these sets transferred separately. In such a situation the whole DMA buffer cannot be transferred in one go; the host software must wait for each set to be transferred. Often the best way to handle these fragmented transfers is via an interrupt handler.

#### 3.2.2.10 DMA Interrupts

Permedia4 provides interrupt support as an alternative means of determining when a DMA transfer is complete. If enabled, the interrupt is generated whenever the **DMACount** register changes from having a non-zero to having a zero value. Since the **DMACount** register is decremented every time a data item is transferred from the DMA buffer this happens when the last data item is transferred from the DMA buffer:

To enable the DMA interrupt, the *OutputDMA* bit must be set in the **CommandDMA** register. The interrupt handler should also check the *ControlDMA* flag bit in the **IntFlags** register to determine that a DMA interrupt has actually occurred. To clear the interrupt, reset the flag by writing a 1 to the **IntFlags** *ControlDMA* flag bit.

A typical use of DMA interrupts might be as follows:

```

prepare DMA buffer

DMACount(n);  // start a DMA transfer

prepare next DMA buffer

while (*DMACount != 0) {

mask interrupts

set DMA Interrupt Enable bit in IntEnable register

sleep on interrupt handler wake up

unmask interrupts

}

```

```

DMACount(n) // start the next DMA sequence

```

The interrupt handler could then be:

```

if (*IntFlags & DMA Flag bit) {

reset DMA Flag bit in IntFlags

send wake up to main task

}

```

Interrupts are complicated and depend on the facilities provided by the host operating system. The above pseudocode only hints at the system details.

This scheme frees the host processor for other work while DMA is being completed. Since the overhead of handling an interrupt is often quite high for the host processor, the scheme should be tuned to allow a period of polling before sleeping on the interrupt.

#### 3.2.2.11 Using Run Length Encoding

Image data frequently contains runs of the same pixel data. Run Length Encoding (RLE) is a convenient image compression method which counts adjacent identical pixel values instead of replicating them. This does not speed up the image transfer from the core's viewpoint (it still needs to read the data) but it reduces the amount of data carried over the PCI bus and, potentially, the host effort in processing/copying the image data.

When run length encoding is enabled then any data (but not tags) which matches the 32 bit run length value is added to the run length count instead of being written to the FIFO. The accumulated run length is written to the FIFO when:

- The new 32 bit word is different from the run being encoded.

- A new scanline is started.

- The end of the primitive occurs.

The amount of data produced during the run length encoding is not known when the DMA controller is set up so an alternative mechanism is used to tell the DMA controller the upload data has finished. This is done by using the **EndOfFeedback** command. When detected in the DMA controller the DMA can be terminated as all the data has been received.

Tags are not included in the FIFO and an extra bit (on the FIFO width) is used to tell the DMA controller to finish. This bit is only set when an **EndOfFeedback** tag is received during RLE processing. This allows run length data to be uploaded at twice the rate available with an external DMA controller.

Note: There is the potential for the software to hang if the Permedia4 Output DMA controller is in feedback mode and the RunLengthEncodeData bit is not set.

If the RLE bit is not set during Feedback mode DMA, the **EndOfFeedback** tag is ignored by the DMA controller, hence the software will not be informed the upload has finished. The graphics core, etc. will continue to function as normal but the Output DMA controller will loop forever discarding data once the buffer count has expired. If the software is running with a time-out the Output DMA controller can be recovered by setting the *RunLengthEncodedData* bit in the **FilterMode** register and sending an **EndOfFeedback**.

Note: This situation only arises during Feedback Mode DMA with RLE, since in all other cases the amount of data to load is known.

Software must make allowance for the fact than run length encoding is not guaranteed to result in a smaller representation of the image and in the worst case could double the size.

Run length encoding is done 32 bits at a time irrespective of the pixel depth and is masked by the RLEMask before the comparison is done. This allows bits in the data to be excluded from the test, e.g. because they are unused and have 'random' values. The masked data is returned.

## 3.2.3 Vertex Loading for Primitives and Data Re-ordering

The I/O units support various strategies to make data loading more efficient including early culling, vertex loading and texture formatting, described below.

#### 3.2.3.1 Primitives

Further I/O pre-processing may be done if the data represents a primitive. Vertex data for primitives can be loaded into the Permedia4 graphics memory space in a number of ways. It can be:

- written directly to the appropriate vertex store

- loaded indirectly from an index into a vertex array, or

- loaded as part of a special vertex sequence corresponding to one of the following primitive types:

| Name          | Description                                                                   |

|---------------|-------------------------------------------------------------------------------|

| TriangleList  | Individual triangles with no shared vertices.                                 |

| TriangleFan   | Triangles with a common center vertex, and another shared vertex between each |

|               | adjacent triangle.                                                            |

| TriangleStrip | Triangles with two shared vertices between adjacent triangles.                |

| LineList      | Individual lines with no shared vertices.                                     |

| LineStrip     | Lines joined head to tail.                                                    |

| PointList     | Individual points                                                             |

Each of these is available in an indexed form (e.g. **IndexedTriangleList**) and a vertex form (e.g **VertexTriangleList**). The indexed form specifies vertices through an index into a vertex array; the vertex form specifies a vertex array directly, so the vertices must be in the correct order.

The register tag marks the start of a primitive and the data field is a count of the number of vertices to be processed. If the number is zero then the data is assumed to be inline and the primitive is terminated by another primitive command.

**IndexedVertex** or **IndexedDoubleVertex** can be used as inline indices into a vertex array by first sending the **IndexedTriangleList** primitive (for example) with data equal to zero. **IndexedVertex** supplies a single 32 bit index into the array, **IndexedDoubleVertex** supplies two 16 bit indices into the vertex array.

The vertex data can be loaded without specifying a primitive type using **Vertex0**, **Vertex1**, and **Vertex2**. These registers specify the vertex store to load, and the data field holds the index into the array. The **VertexData** register is used for inline vertex data.

The format of the vertex is specified by four controls:

• The vertex size controls the amount of memory each vertex takes (i.e. the Stride).

- The tag list describes the order of the data within the vertex, so the tag loaded into TagList0 defines the data type of the first entry in the vertex.

- The VertexFormat mask controls which data elements are present, so if bit 0 is clear but bit 1 set, the first data element read is associated with TagList1 instead of TagList0.

- The VertexValid mask specifies which items of data within the current vertex should be read

Typically we would use the tag list to define the order in which data is delivered. The format mask and vertex size set modes (so if z is enabled the z bit in the format mask is set and the vertex size increased by 1).

The **VertexValid** mask is generally used for multi-pass algorithms, such as emulation of multiple textures. The vertex structure holds several sets of texture coordinates for the same x,y,z coordinates, and on each pass a different set is enabled by defining it as valid. Because invalid data is discarded the format only needs to recognize a single field (although the vertex size must be big enough to include all data).

A state register supports context switching within a primitive. This allows a primitive such as a triangle strip to be interrupted part way through and then restarted cleanly. If data is being read by DMA it completes before a sync can get through the pipeline: this applies to single vertices read in by inline indexes and to multiple vertices read in via index arrays.

To restart an interrupted primitive the **HostInState** register should be restored along with the rest of the pipeline and the primitive continued from the point at which it was broken.

A simple 2D line primitive is enabled by setting the *Line2D* bit in the **VertexControl** register. This works in conjunction with **LineList** or **LineStrip** and the **LineCoord01** and **LineCoord10** registers. Only XY data (packed in one word) can be sent in this mode. The contents of the tag list are ignored.

#### 3.2.3.2 Data Re-ordering

In addition to vertex processing, I/O processing supports data re-ordering for a write combined FIFO. Up to 64 bytes (16x32 bit words) can be sent out of order, stored, and issued in the correct order. Write combined acesses are identified by the address space they are sent to, and this is passed down the input FIFO by a flag. Typically:

A counter cycles through the the registers trying to write them out in ascending order. While the next register required is flagged "not valid" the process locks.

Note:

This mechanism assumes that the maximum amount of write buffering in the CPU is 64 bytes and that the if multiple buffers are supported they are flushed according to address.

#### 3.2.4 Backface Cull and Texture Setup Functions

In addition to vertex loading and re-ordering, it is possible to cull triangles facing away from the viewer to avoid unnecessary rendering overheads<sup>5</sup>. This is controlled by the *backfacecull* bit in the **DeltaMode** register and by the *TextureEnable* and *RejectNegativeFace* bits in the **DrawTriangle** command.

Note:

Backface cull was supported in Permdia3, but in Permedia4 it is implemented ahead of the delta unit to avoid loading vertex data for a triangle that will subsequently be culled.

A typical backface cull algorithm would be:

```

ScreenArea = dXac * dYbc - dXbc * dYac;

if (ScreenArea is negative or zero && RejectNegativeFace)

abort processing and discard draw command;

else if (ScreenArea is positive or zero && !RejectNegativeFace)

abort processing and discard draw command;

else

continue processing;

where:

dXac = a.x - c.x; // etc for each parameter.

```

#### 3.2.4.1 Texture Setup

When texture is enabled in the **DeltaMode** register and the relevant **Draw** command, Permedia4 can also perform some texture optimization functions:

- ForceQ used in unusual cases where the application does not want perspective correction of textures and either does not supply equal Q values or supplies no Q at all. Permedia4 either over-rides or makes up the numbers as appropriate.

- EqualQ used to avoid rounding problems where the chip encounters calculations of the form 1/(1/x) and x isn't a power of 2.

- Share S,T,Q used to provide S, T or Q values for the second texture when

multitexturing if the application only supplies data for texture 0 but indicates that both

textures should use the same set of texture coordinates.

These functions are enabled in the <u>DeltaFormatControl</u> register - for details see the *Permedia4 Reference Guide* volume II.

#### 3.2.4.2 Texture Wrap

Generally, textures are interpolated linearly from start value to end value under Direct3D rules. (For a general description of Texture Interpolation and Level of Detail (LOD) principles please refer to the *Permedia4 Programmer's Guide* volume II, section 5.2) For

<sup>&</sup>lt;sup>5</sup> A D3D compliance requirement

cylindrical objects, texture interpolation neds to take the shortest distance from start value to end value.

The implementation looks at the difference in texture co-ordinates along the one edge and if it is greater than  $\frac{1}{2}$  then 1.0 is subtracted from the start value. If the difference is less than  $-\frac{1}{2}$  then 1.0 is added to the start value. The effect of these operations is to move the start value to the 'other side' of the end value, so the direction of interpolation is flipped. The operation is repeated for n-1 sides, where n is the number of vertices in the primitive.

*Note:*

Tthis relies on texture units downstream handling co-ordinates outside the range 0 to 1 and repeating the texture accordingly. This is done for each set of texture co-ordinates individually.

The algorithm for triangles is:

if

$$((a.s - c.s) > 0.5)$$

$a.s = 1.0$ ;

else if  $((a.s - c.s) < -0.5)$

$a.s += 1.0$ ;

if  $((b.s - c.s) > 0.5)$

$b.s = 1.0$ ;

else if  $((b.s - c.s) < -0.5)$

$b.s += 1.0$ ;

The algorithm for lines is:

if

$$((a.s - b.s) > 0.5)$$

$a.s = 1.0;$

else if  $((a.s - b.s) < -0.5)$

$a.s += 1.0;$

Texture co-ordinates for points are not modified.

#### 3.2.4.3 Per-poly Mipmapping

Polygon Mipmapping generates a Level of Detail (LOD) value for the x,y area of an entire triangle. This requires determining a ratio between the triangle area and the projected area in the texture map taken from the S,T coordinates. The ratio determines the LOD value which is sent to the downstream texture units.

The calculation is as shown below.

*Note:* The triangle x,y area has already been calculated if Backface Cull is enabled.

```

ScreenArea = dXac * dYbc - dXbc * dYac;

TextureArea = (dSac * dTbc - dSbc * dTac) * TextureLODScale;

LOD = (exponent of texture area - exponent of screen area) / 2;

```

```

if (LOD < 0) LOD = 0; if (LOD > 0xF) LOD = 0xF; // LOD is 4.8 format, fraction always set to zero. LOD <<= 8; where: dXac = a.x - c.x; 	 // etc 	 for each 	 parameter. repeat for S1 and T1 using TextureLODScale1.

```

The LOD is clamped to lie between 0 and 15 inclusive.

Note

Subtracting the exponents is an easy way of getting the ratio of the two values. The divide by 2 is applied because logs of areas are being compared so it is equivalent of a square root.

**TextureLODScale** is used to control the appearance of the texture; making it larger makes the texture over-filtered, making it smaller makes the texture under-filtered. This operation is done to both sets of texture co-ordinates (if enabled) and there is a separate **TextureLODScale1** for S1 and T1. For a general discussion of LOD interpolation refer to Volume II, section 5.2.

When the LOD has been calculated it is sent to the texture coord unit in either the LOD (for S and T) or LOD1 (for S1 and T1) registers as appropriate.

#### 3.2.4.4 Texture Shift

Texture Shift is a means of recovering significance bits from the integer of a texture to the fraction part where the integer has become very large relative to the range (e.g. 70.0 to 70.5) but is actually redundant because the texture repeats.

The shift function finds the vertex with the largest Q and subtracts the integer parts of those S,T texture coordinates from the other vertices' coordinates. The integer part is rounded to an even value to avoid interference with mirrored textures (refer to Volume II, section 5.2.2.1, <u>Texture Coordinate Wrapping Modes</u>. Texture Shift is enabled by the **DeltaFormatControl** register *TextureShift* bit.

#### 3.2.4.5 Scale by **Q**

This function multipleis the S,T values for each vertex of a triangle by the vertex's Q value. This anticipates the Divide by Q operation performed later during perspective correction.

# 3.3 Output FIFO

An output FIFO provides data readback from Permedia4. Each entry in this FIFO is 32 bits wide and can hold tag or data values. This differs from the input FIFO whose entries are always tag/data pairs (effectively 41 bits – 9 bits for the tag and 32 bits for the data).

The **FilterMode** register controls the type of data written to the output FIFO.. This register allows filtering of output data in various categories including the following:

- Depth: output in this category results from an image upload of the Depth buffer.

- Stencil: output in this category results from an image upload of the Stencil buffer.

- Color: output in this category results from an image upload of the framebuffer.

- Synchronization: synchronization data is sent in response to a **Sync** command.

The **FilterMode** register uses 2 bits for each category. Setting the least significant bit (0x1) enables output of the register *tag* for that category. Setting the most significant bit (0x2) enables output of the *data* for that category. If both tag and data output are enabled the tag is written first to the FIFO followed by the data. The **FilterMode** register is described in more detail in Chapter 5 - Graphics Programming.

For example, to perform an image upload from the framebuffer the **FilterMode** register should have output enabled for the *FBColorData* bit. Then the rectangular area to be uploaded should be described to the rasterizer. Each pixel read from the framebuffer is then placed into the output FIFO. If the output FIFO becomes full Permedia4 blocks internally until space becomes available.

It is the programmer's responsibility to read all data from the output FIFO. For example, it is important to know how many pixels should result from an image upload and to read exactly that many from the FIFO.

To read data from the output FIFO the **OutFIFOWords** register should first be read to establish the number of entries in the FIFO (reading from the FIFO when it is empty returns undefined data). Then read the same number of 32-bit data items from the FIFO. Repeat the procedure until all the expected data or tag items have been read. The address of the output FIFO is described below.

Note:

All expected data must be read back. The graphics core will block if the FIFO becomes full. Programmers must be careful to avoid the deadlock condition that will result if the host is waiting for space to become free in the input FIFO while Permedia4 is waiting for the host to read data from the output FIFO.

# 3.4 Other Interrupts

Permedia4 also provides interrupt facilities for the following:

- Sync: If a Sync command is sent and the Sync interrupt has been enabled then once all rendering has been completed, a data value is entered into the Host Out FIFO, and a Sync interrupt is generated when this value reaches the output end of the FIFO. Synchronization is described further in the next section.

- External: this provides the capability for external hardware on a Permedia4 board (such as an external video timing generator) to generate interrupts to the host processor.

- Error: if enabled the error interrupt will occur when Permedia4 detects certain error conditions, such as an attempt to write to a full FIFO.

- Vertical Retrace: if enabled a vertical retrace interrupt is generated at the start of the video blank period.

Each of these are enabled and cleared in a similar way to the DMA interrupt. See **IntEnable** in the *Permedia4 Reference Guide* for more details.

# 3.5 Synchronization

There are three main cases where the host must synchronize with the graphics core:

1. before reading back from registers

- 2. before directly accessing the framebuffer or the localbuffer via the bypass mechanism

- 3. framebuffer management tasks such as double buffering (though this may be better handled using the **SuspendUntilFrameBlank** command).<sup>6</sup>

Synchronizing with Permedia4 implies waiting for any pending DMA to complete **and** waiting for the chip to complete any processing currently being performed. The following pseudo-code shows the general scheme:

```

Permedia4Data data;

// wait for DMA to complete

while (*DMACount != 0) {

poll or wait for interrupt

}

while (*InFIFOSpace < 2) {

// wait for free space in the FIFO

}

// enable sync output and send the Sync command

data.Word = 0;

data. Filter Mode Synchronization = 0x1;

FilterMode(data.Word);

Sync(0x0);

/* wait for the sync output data */

do {

while (*OutFIFOWords == 0)

// poll waiting for data in output FIFO

} while (*OutputFIFO != Sync tag);

```

Initially we wait for DMA to complete as normal. We then also have to wait for space to become free in the FIFO (since the DMA controller actually loads the FIFO). We need space for 2 registers: one to enable generation of an output sync value, and the **Sync** command itself. The enable flag can be set at initialization time. The output value will be generated only when a **Sync** command has actually been sent, and Permedia4 has then completed all processing.

Rather than polling it is possible to use a **Sync** interrupt as mentioned in the previous section. As well as enabling the interrupt and setting the filter mode, the data sent in the **Sync** command must have the most significant bit set in order to generate the interrupt. The interrupt is generated when the tag or data reaches the output end of the Host Out FIFO. Use of the Sync interrupt has to be considered carefully as Permedia4 will generally empty the FIFO more quickly than it takes to set up and handle the interrupt.

<sup>&</sup>lt;sup>6</sup> And ref *Permedia*<sup>4</sup> *Errata and Alerts*, PEREN004 - Check FIFO space before sending HostIn DMA commands.

## 3.6 Host Framebuffer Bypass

Normally, the host will access the framebuffer indirectly via commands sent to the FIFO interface. However, Permedia4 maps the complete framebuffer as a linear 32-bit addressable memory region. Access to the framebuffer via this memory mapped route is independent of the Permedia4 FIFO.

Drivers may choose to use direct access to the framebuffer for algorithms which are not supported by Permedia4. The framebuffer bypass supports big-endian, little-endian and GIB-endian formats. These are described in a later section.

A driver making use of the framebuffer bypass mechanism should synchronize framebuffer accesses made through the FIFO with those made directly through the memory map. If data is written to the FIFO followed by a direct access to the framebuffer, the FIFO may not have had a chance to complete before the bypass access happens.

Once mapped in, the framebuffer can be read or written with 8, 16 or 32-bit accesses. Permedia4 does not use bank switching since it is a PCI device and the PCI bus provides a 32 bit address space<sup>7</sup>.

The framebuffer is accessible via Regions 1 and 2 of the PCI address map.!

#### 3.6.1 Framebuffer Dimensions and Depth

Address calculation is controlled by the **FBWriteMode** register and the address is a function of X, Y, **FBWriteBufferAddr**, **FBWriteBufferOffset**, **FBWriteBufferWidth** and **PixelSize** parameters. The X and Y parameters are passed in the active fragment or span registers. The Address, Offset and Width are specified independently for each of the write buffers defined in **LBWriteFormat**.

The address calculation is further modified by the mode bits: *Origin*, *StripePitch*, *StripeHeight* and *Layout*.

Once the framebuffer parameters have been defined, determining the visible screen width and height becomes a clipping issue. The visible screen width and height are set up in the **ScreenSize** register and enabled by setting the *ScreenScissorEnable* bit in the **ScissorMode** register.

The framebuffer depth (8, 16 or 32-bit) is controlled by the **PixelSize** register. This register provides a 2 bit field to control which of the three pixel depths is being used. The pixel depth can be changed at any time without the need for any synchronization but should normally be set at initialization.<sup>8</sup>

# 3.7 Host Localbuffer Bypass

As with the framebuffer, the localbuffer can be mapped in and accessed directly. The host should synchronize with Permedia4 before making any direct access to the localbuffer.

In Permedia4, Localbuffer access is defined as reads from up to four mappable destinations, or writes to a single mappable destination. Addresses for reads and writes

7

<sup>&</sup>lt;sup>7</sup>On address limited buses such as ISA, devices limit the amount of address space that they occupy by using bank switching hardware. This typically provides a 64K byte window through which part of the framebuffer is visible. The region 0 Video Stream hardware registers define which part of the framebuffer is visible through this window - refer to the *Permedia4 Reference Guide*, chapter 4.

<sup>&</sup>lt;sup>8</sup> On earlier systems without span operation it was useful to change the pixel depth temporarily to optimize some 2D rendering operations. This is no longer necessary but code written to use the technique will continue to work provided pixel size is set using the **PixelSize** register.

are managed locally, i.e. the base address, offset value and width are not shared with the read address generation.

Localbuffer management facilities are described in section 4.2 - Localbuffer. The localbuffer is accessible via Regions 1 and 3 of the PCI address map. Localbuffer bypass supports big-endian and little-endian formats, described in *Byte Swapping*, below.

# 3.8 Register Read back and Context Dump/Restore

In some operating environments multiple tasks want access to the Permedia4 chip. Sometimes a server task or driver wants to arbitrate access to Permedia4 on behalf of multiple applications. In other situations a host process may wish to extract specific information on the fly, usually for diagnostic purposes. In both these cases register readback is required, but in the former a simple global context switch is involved, while in the other we want selective readback.

# 3.8.1 Context Dump/Restore