# P9/P10<sup>®</sup>

# Programmer's Guide

# **DRAFT**

PROPRIETARY AND CONFIDENTIAL INFORMATION

# 3Dlabs®

# P9/P10<sup>®</sup>

Programmer's Guide

**DRAFT**

Issue 2

Front Matter P10 Programmers Guide

P10 Programmers Guide Front Matter

#### **Proprietary Notice**

The material in this document is the intellectual property of **3D**/abs®. It is provided solely for information. You may not reproduce this document in whole or in part by any means. While every care has been taken in the preparation of this document, **3D**/abs accepts no liability for any consequences of its use. Our products are under continual improvement and we reserve the right to change their specification without notice. **3D**/abs may not produce printed versions of each issue of this document. The latest version will be available from the **3D**/abs web site.

**3D***labs* products and technology are protected by a number of worldwide patents. Unlicensed use of any information contained herein may infringe one or more of these patents and may violate the appropriate patent laws and conventions.

**3D***labs* ® is the worldwide trading name of **3D***labs* Inc. Ltd.

**3D***labs*, GLINT, GLINT Gamma, PERMEDIA, OXYGEN AND POWERTHREADS are trademarks or registered trademarks of **3D***labs* Ltd., **3D***labs* Inc. Ltd or **3D***labs* Inc.

Microsoft, Windows and Direct3D are either registered trademarks or trademarks of Microsoft Corp. in the United States and/or other countries. OpenGL is a registered trademark of Silicon Graphics, Inc. All other trademarks are acknowledged and recognized.

© Copyright 3Dlabs Inc. Ltd. 2001. All rights reserved worldwide.

Email: info@3dlabs.com Web: http://www.3dlabs.com

**3D**/abs Ltd.

Meadlake Place

Thorpe Lea Road, Egham

Surrey, TW20 8HE

United Kingdom

Tel: +44 (0) 1784 470555

Tel: +44 (0) 1784 470555 Fax: +44 (0) 1784 470699 **3D**/abs K.K. Shiroyama JT Mori Bldg 16F 40301 Toranomon Minato-ku, Tokyo, 105, Japan Tel: +81-3-5403-4653 Fax: +91-3-5403-4646

**3D**/abs Inc. 480 Potrero Avenue Sunnyvale, CA 94086, United States Tel: +1 (408) 530-4700 Fax: +1 (408) 530-4701 Front Matter P10 Programmers Guide

### **Change History**

| Document   | Issue | Date       | Change                 |

|------------|-------|------------|------------------------|

| 174.1.4 01 | 1     | 25/06/2001 | Creation               |

| 174.1.4 02 | 2     | 17/10/2001 | Final edit and release |

P10 Programmers Guide Front Matter

| Table o      | f Contents                                                            |      |

|--------------|-----------------------------------------------------------------------|------|

| 1 INTR       | ODUCTION                                                              | 1-1  |

| 1.1 lr       | ntroduction                                                           | 1-1  |

| 1.2 H        | ow to Use This Manual                                                 | 1-1  |

| <b>2</b> MEM | ORY                                                                   | 2-2  |

| 2.1 D        | ata Formats                                                           | 2-2  |

| 2.1.1        | Local Memory Data Format                                              | 2-2  |

| 2.1.2        | Bypass Accesses                                                       | 2-3  |

| 2.1.3        | GPIO Data Format                                                      | 2-3  |

| 2.1.4        | Re-circulating Data                                                   | 2-4  |

| 2.2 N        | lemory Management Introduction                                        | 2-4  |

| 2.2.1        | Advantages and Disadvantages of Virtual Memory                        | 2-4  |

| 2.3 A        | ddress Translation Without Page Faulting                              | 2-4  |

| 2.3.1        | Address Translation Initialisation                                    | 2-4  |

| 2.4 N        | lemory Management With Page Faulting                                  | 2-7  |

| 2.4.1        | Page Table Format Revisited                                           | 2-8  |

| 2.4.2        | DMA Controller                                                        | 2-8  |

| 2.4.3        | Page Replacement Algorithms                                           | 2-10 |

| 3 INPU       | T AND OUTPUT                                                          | 3-1  |

| 3.1 W        | here to store commands and data                                       | 3-1  |

| 3.1.1        | Host memory                                                           | 3-1  |

| 3.2 P        | rogramed I/O vs. DMA                                                  | 3-2  |

| 3.2.1        | The Input Message Port                                                | 3-2  |

| 3.2.2        | The DMA Interface                                                     | 3-2  |

| 3.3 C        | ircular DMA Buffers                                                   | 3-3  |

| 3.3.1        | Layout, Read/Write Pointers and Scheduling - Software Implementation: | 3-3  |

| 3.4 D        | MA 3-4                                                                |      |

| 3.5 D        | ual Command Streams                                                   | 3-4  |

| 3.5.1        | DMA stream                                                            | 3-5  |

| 3.5.2        | Vertex and Index Data Stream                                          | 3-5  |

| 3.5.3        | Output DMA                                                            | 3-5  |

| 3.6 N        | Iultiple Contexts                                                     | 3-5  |

| 3.6.1        | Context Switching                                                     | 3-5  |

| 3.6.2        | User-induced and Isochronous Switches                                 | 3-6  |

| 3.6.3        | Context Scheduling                                                    | 3-6  |

| 3.6.4        | Driver Controlled Scheduling:                                         | 3-6  |

| 3.6.5        | Context Security                                                      | 3-6  |

| 3.7 V        | ertex and Index Buffers (GPIO)                                        | 3-7  |

| 3.7.1        | Organizing data in memory                                             | 3-8  |

| 3.7.2        | Caching                                                               | 3-8  |

| 3.7.3        | Preparing to Draw Primitives                                          | 3-8  |

| 3.7.4        | Drawing Primitives                                                    | 3-9  |

| 3.8 D        | ownloading Textures                                                   | 3-9  |

Front Matter P10 Programmers Guide

| 3.9        | DX     | (VA Driver                                        | 3-10 |

|------------|--------|---------------------------------------------------|------|

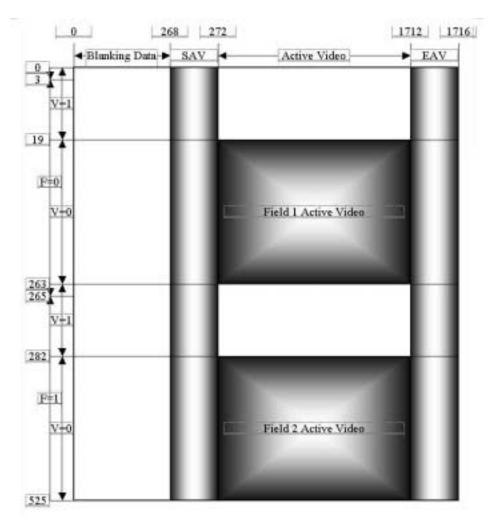

| 3.1        | IO Vid | deo Port                                          | 3-10 |

| 3          | .10.1  | Video Stream Formats                              | 3-10 |

| 3          | .10.2  | SAV and EAV Timing Reference Signals              | 3-11 |

| 3          | .10.3  | DTV Display Formats                               | 3-11 |

| 3          | .10.4  | Fields and Frame                                  | 3-12 |

| 3          | .10.5  | Frames and Memory                                 | 3-13 |

| 3          | .10.6  | Frame Interrupts                                  | 3-13 |

| 3          | .10.7  | Programming Summary                               | 3-13 |

| 3          | 10.8   | Programming Example                               | 3-14 |

| 3          | .10.9  | Register Interface                                | 3-16 |

| 3.1        | I1 Up  | load Facilities                                   | 3-17 |

| <b>4</b> F | PROG   | RAMMING OVERVIEW                                  | 4-1  |

| 4.1        | l Tra  | ansformation and Lighting                         | 4-1  |

| 4          | 1.1    | GP10                                              | 4-1  |

| 4          | 1.2    | Vertex Shading Unit                               | 4-1  |

| 4.2        | 2 Te   | xture and Rendering                               | 4-2  |

| 4          | .2.1   | Texture Coordinate Programme                      | 4-2  |

| 4          | .2.2   | Shading                                           | 4-2  |

| 4          | 2.3    | Framebuffer Processing                            | 4-3  |

| 4          | .2.4   | How to draw a Gouraud-shaded triangle             | 4-3  |

| 4.3        | 3 Fix  | red mode and state registers                      | 4-3  |

| 4.4        | 1 Pro  | ogrammable Units                                  | 4-3  |

| 4          | 4.1    | Vertex Shading Introduction                       | 4-3  |

| 4          | 4.2    | Texture Co-ordinate Unit (TCU) Introduction       | 4-9  |

| 4          | 4.3    | Introduction to Shading                           | 4-25 |

| 5 I        | NITIA  | LIZATION                                          | 5-1  |

| 5.1        | l Me   | emory Allocation (typical positions for LB, FB)   | 5-1  |

| 5.2        | 2 Pa   | ge Tables                                         | 5-1  |

| 5.3        | 3 Co   | ntext Record Registers                            | 5-1  |

| 5.4        | 4 Pro  | ograms                                            | 5-1  |

| 5          | 4.1    | Program Initialization                            | 5-1  |

| 5          | 4.2    | Specifying program start addresses                | 5-2  |

| 5          | 4.3    | Downloading programs                              | 5-2  |

| 5          | 4.4    | Downloading pixel address unit programs           | 5-2  |

| 5          | 4.5    | Downloading other unit programs                   | 5-3  |

| 5          | .4.6   | Setting program start addresses for tile programs | 5-3  |

| 5          | .4.7   | Running programs                                  | 5-3  |

| 5.5        | 5 Vic  | deo Output                                        | 5-3  |

| 5          | .5.1   | Programming the Video Mode, RAMDAC and LUTs       | 5-4  |

|            | .5.2   | Using Video Scaling                               | 5-6  |

| 5          | .5.3   | Dual Head Video Output                            | 5-6  |

| 5          | 5.4    | Digital Video Output                              | 5-8  |

| P10 Programmers Guide | Front Matter |

|-----------------------|--------------|

|-----------------------|--------------|

|          | IRONIZATION                                                                                | 6-1   |

|----------|--------------------------------------------------------------------------------------------|-------|

| -        | nchronization with Core and with VTG                                                       | 6-1   |

| 6.1.1    | Synchronizing Video Channel Updates with Video Output                                      | 6-1   |

| 6.1.2    | Synchronizing the Core with Video Output                                                   | 6-1   |

|          | alidating Caches                                                                           | 6-1   |

| 6.2.1    | Texture Cache Control                                                                      | 6-1   |

| 6.2.2    | Pixel and Local Buffer Cache Control                                                       | 6-2   |

| 6.3 Inte | errupts                                                                                    | 6-2   |

| 6.3.1    | Interrupts & Synchronization                                                               | 6-2   |

| IMAGE    | DOWNLOAD (HOW TO, SETUP)                                                                   | 7-1   |

| 7.1 Pix  | el Data                                                                                    | 7-1   |

| 7.1.1    | Native download setup                                                                      | 7 - 1 |

| 7.1.2    | Native download operation                                                                  | 7 - 2 |

| 7.1.3    | Translating downloads                                                                      | 7-3   |

| 7.1.4    | Palettised translating downloads                                                           | 7-3   |

| 7.1.5    | Downloads with patterned brushes                                                           | 7-5   |

| 7.2 Te   | cture maps (download, MIPmap generation)                                                   | 7-5   |

| 7.3 Biti | mask data                                                                                  | 7-8   |

| 7.3.1    | Opaque Monochrome Bitmap Downloads                                                         | 7 -8  |

| 7.3.2    | Rendering Host Memory Font Glyphs/Transparent Downloads                                    | 7-9   |

| 7.3.3    | Font Glyph Downloads To Offscreen Cache                                                    | 7-9   |

| 7.4 Per  | forming uploads                                                                            | 7-10  |

| 7.4.1    | Up load setup                                                                              | 7-10  |

| 7.4.2    | Up load operation                                                                          | 7-10  |

| 7.4.3    | Monochrome uploads                                                                         | 7-11  |

| RENDE    | ERING                                                                                      | 8-1   |

| 8.1 Pro  | gram-to-program parameter consistency                                                      | 8-1   |

|          | ecting the primitive type for the vertex stream target (triangles, polymode, 2D            |       |

| _        | es/clears)                                                                                 | 8-1   |

| 8.3 Ve   | rtex Processing                                                                            | 8-1   |

| 8.3.1    | Transformation                                                                             | 8-2   |

| 8.3.2    | Texture Operation                                                                          | 8-3   |

| 8.3.3    | Fog                                                                                        | 8-6   |

| 8.3.4    | Lighting                                                                                   | 8-7   |

| 8.3.5    | User Clip Planes                                                                           | 8-11  |

| 8.3.6    | Projection and Viewport Mapping                                                            | 8-11  |

| 8.4 Sh   | ading (Gouraud, flat, modulate etc.)                                                       | 8-12  |

| 8.4.1    | Flat Shading                                                                               | 8-13  |

| 8.4.2    | Gouraud Shading (Diffuse and Specular)                                                     | 8-14  |

| 8.4.3    | Texture Based Shading                                                                      | 8-15  |

| 8.5 Tex  | kturing                                                                                    | 8-16  |

| 8.5.1    | Texture co-ordinate generation (1D, 2D, 3D; sharing the work on multiple co-ordinate sets) | 8-16  |

| 8.5.2    | Colour Lookup                                                                              | 8-18  |

| 8.5.3    | Bump Environment Mapping                                                                   | 8-19  |

Front Matter P10 Programmers Guide

|    | 8.5. | 4 Cube Mapping                                                                      | 8-22         |

|----|------|-------------------------------------------------------------------------------------|--------------|

| 8  | 8.6  | Localbuffer processing (setting up the mode registers)                              | 8-24         |

| 8  | 8.7  | Framebuffer processing (Dithering, Logical Ops, Blending, Accumulation buffers/deep | buffers)8-26 |

|    | 8.7. | 1 Configuring the Frame Buffers                                                     | 8-26         |

|    | 8.7. | 2 Loading the Pixel Unit and Pixel Address Unit Programs                            | 8-27         |

|    | 8.7. | 3 Blending                                                                          | 8-29         |

|    | 8.7. | 4 Dithering                                                                         | 8-31         |

|    | 8.7. | 5 Accumulation Buffers                                                              | 8-31         |

| 8  | 8.8  | 2D Operations (blits, pattern fills, fonts, pixel depth conversions, 2D logic ops.) | 8-34         |

|    | 8.8. | 1 Simple Solid Color Operations                                                     | 8-34         |

|    | 8.8. | 2 Color Pattern Operations                                                          | 8-35         |

|    | 8.8. | 3 Monochrome Pattern Fills                                                          | 8-38         |

|    | 8.8. | 4 Screen To Screen Copies (BitBlt)                                                  | 8-39         |

|    | 8.8. | 5 Text Font Rendering                                                               | 8-41         |

|    | 8.8. | 6 Bitmap Depth Conversion                                                           | 8-43         |

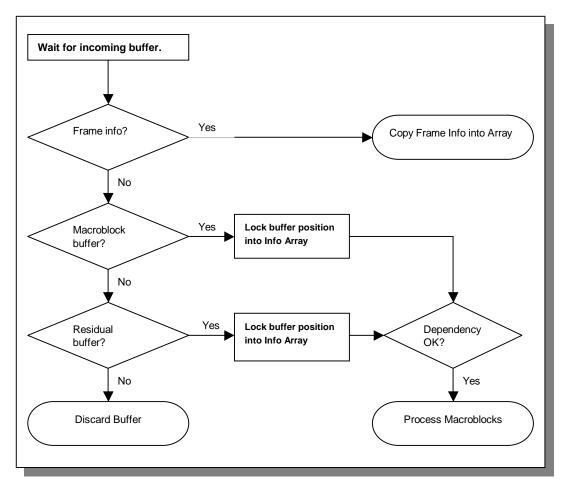

| 8  | 8.9  | Video Operations and the DXVA Driver                                                | 8-43         |

|    | 8.9. | 1 Video scaling (replication and pixel dropping)                                    | 8-43         |

|    | 8.9. | 2 Using the Isochronous channel for video overlays                                  | 8-44         |

|    | 8.9. | 3 Probe & Locking                                                                   | 8-44         |

|    | 8.9. | 4 Main Function Loop                                                                | 8-44         |

|    | 8.9. | 5 Implementation                                                                    | 8-46         |

|    | 8.9. | 6 Summary                                                                           | 8-67         |

| 9  | ΑN   | ITIALIASING                                                                         | 9-1          |

| (  | 9.1  | Sample point position (how many sample points)                                      | 9-1          |

| (  | 9.2  | OpenGL Antialiasing (triangles, dual line patterns, points)                         | 9-2          |

| ć  | 9.3  | Full Scene AA (FSAA, Multi sampling, Super sampling)                                | 9-3          |

| 10 | EX   | OTICA                                                                               | 10-1         |

| •  | 10.1 | Beyond ordinary graphics functions (imagination, examples)                          | 10-1         |

| •  | 10.2 | Vertex Shader applications                                                          | 10-1         |

|    | 10.2 | 2.1 Tessellation                                                                    | 10-1         |

|    | 10.2 | 2.2 Displacement Mapping                                                            | 10-3         |

| •  | 10.3 | Texture Co-ordinate applications                                                    | 10-5         |

|    | 10.  | 3.1 Convolution                                                                     | 10-5         |

|    | 10.  | 3.2 High Order or Multi-tap Filters                                                 | 10-5         |

|    | 10.  | 3.3 Ray Casting                                                                     | 10-7         |

|    | 10.  | 3.4 Bump Mapping                                                                    | 10-7         |

|    | 10.4 | Pixel applications                                                                  | 10-9         |

| 11 | GL   | OSSARY & INDEX                                                                      | 11-1         |

P10 Programmers Guide Memory

1

### Introduction

#### 1.1 Introduction

The P10 and P9 Graphics Processors are the first of a radical new chipset series with a highly scalable, multi-texture/multi-fragment per clock cycle architecture. This industry-leading design uses extensive parallelism and programmability to provide future-proof support for new, texture-intensive APIs such as Microsoft DX8.

Using *programmable T&L* and *programmable pixel shaders* in conjunction with highly optimised fixed-function units results in a simpler, faster and more flexible design.

Programmable registers also allow dynamic reconfiguration of the number of vertex shaders, the number of texture pipes and the number of rasterizers per chip to deliver the greatest possible throughput under changing task conditions.

Fixed-function registers for specialised tasks have been optimised for simplicity and speed with hand-polished main routines and the removal of legacy code. Memory bandwidth and DMA performance have been enhanced with support for high-density DDR memory configurations up to 8 x 8Mx32 (when available) and low overhead circular buffers to provide up to 17Gbytes/second peak throughput.

3Dlabs has achieved this without compromising its long-standing commitment to quality 3D rendering. P10 delivers accuracy, stability and full OpenGL compliance while providing a feature-rich device with unparalled real-world single-chip graphics performance.

#### 1.2 How to Use This Manual

The *Programmers' Guide* should be read together with the *Reference Guide* which contains all of the referenced register descriptions.

This manual uses hyperlinks in **MSWord** file distributions to improve ease of access to relevant information for online users. To enable hyperlinks, the complete *Reference Guide* and *Programmer's Guide* file set should be in a single Windows directory or folder.

Where both P10 and P9 are in use, they should be placed in a common directory. All crosslinks use relative addressing. Configured variants are color-coded:

Register Title [p9] - Indicates a configured register

Configured content [P9] – Indicates a field or other content which is differently configured for P9, P10 etc.

References to "P10" should be considered applicable to P9 unless there is a specific configuration variant.

Minor changes are released progressively but only rolled up into a major release level when the volume of changes warrants it. Readers are therefore advised to check the file dates and download the current version of their document set from the 3Dlabs website to ensure accuracy.

The Programmers Guide:

- Contains an overview of P10, its capabilities and architecture, highlighting key differences between P10 and earlier chips.

- details the programming model for the chip, including DMA circular buffers, host bypass to unified framebuffer, programmable unit encoding and examples, vertex loading and context caching.

- describes the data structures that P10 supports in the framebuffer and the localbuffer.

- describes the Video System including timing, RAMDAC and overlays.

- In Appendix A gives the format used in the pseudocode examples throughout the document.

- In Appendix B (TBC) gives further examples for unit microcoding

Memory P10 Programmers Guide

2

# **Memory**

#### 2.1 Data Formats

As data is gathered, cached as vertices, indexed, DMAd, transformed, clipped and rendered it takes a number of forms, from raw input to floats and fixed integers, to vectors and normals, to rendered primitives and video bus data. Much of this is common and described in industry reference standards. However in some respects P10 is unusual, particularly in its use of tiled memory instead of conventional linear memory.

#### 2.1.1 Local Memory Data Format

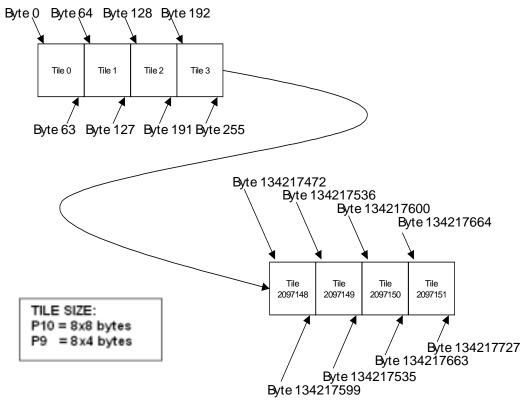

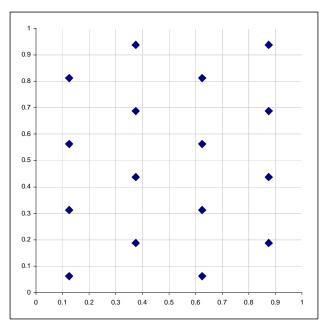

In this architecture data is **not** laid out in the traditional linear model. Instead all data is grouped into tiles (the size of which is chip-specific) which are then stacked through memory. Instead of addressing by byte position, data is accessed by tile number, as shown in the following illustration:

Figure 2.1 Linear Tile Addressing [P10]

P10 Programmers Guide Memory

Normally, each tile corresponds to a region of a buffer (perhaps the framebuffer or a texture); if the data type held in the buffer needs more than one byte per entry the bytes are held in separate tiles so this is called a 'byte planar' format.

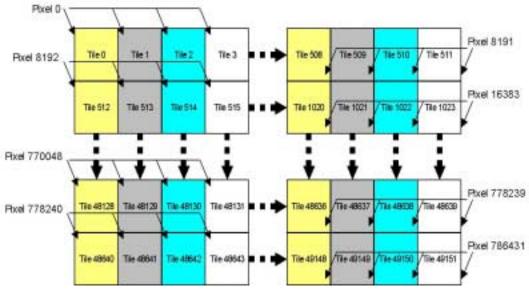

Figure 2.2 Tile to Pixel Mapping

This diagram shows a 1024x768 screen at 8 bits per pixel. At 32 bits per pixel each color component takes one byte so consecutive tiles hold red, green, blue, and alpha. The 1024x768 screen looks like this:

Figure 2.3 Tile to Color Byte Mapping

#### 2.1.2 Bypass Accesses

The PCI Bypass Unit connects the PCI bus with the P10 memory controller. It provides a "bypass" path around the graphics core, through which software can read and write local memory directly. The memory controller reads and writes 64bytes at a time from local memory. The PCI Bypass unit has the following functions:

- Combine writes from the bus interface to reduce memory bandwidth requirements.

- Track outstanding memory writes to determine when all data has reached memory.

- Cache read data from the memory to reduce subsequent bus interface read latency.

- Optionally convert between linear and planar byte tile memory accesses based on the bypass address.

For a full definition of the registers controlling the Bypass mechanism refer to the *P10 Reference Guide* Bypass Registers

PCI Bypass can be configured to read/write from the host to local graphics memory with or without memory format conversion. The data should be converted if its destination is ultimately the graphics core, but not if it is intended for the GPIO units. For example, if a texture is transferred from host into local memory destined for the graphics core, then format conversion should be enabled. (Or alternatively the format conversion has to be done by the host in software.)

A command stream (e.g. an OpenGL display list) on the other hand is usually written to local memory with the intention that it will be read by the GPIO units. In this case no conversion should be enabled. The next section describing the GPIO Data Format expands on this point.

#### 2.1.3 GPIO Data Format

The GPIO input can read either from host memory or from local graphics memory. The GPIO interprets memory as a standard linear byte stream format (not the planar byte tile format). More details are given in a <u>later section on GPIO</u> about the alignment requirements of the data, byte swapping capabilities, the multiple simultaneous data buffers that can be set up, etc.

Memory P10 Programmers Guide

Since the memory is interpreted as a linear byte stream, when the host is building a command stream into a buffer in host memory the data should be written in the normal linear fashion. The GPIO can read the command stream from host memory using DMA and will interpret the data as expected.

This also applies when the host is building a command stream in local graphics memory. The local memory is mapped in by the host using the Bypass mechanism – which in this case should be set to its conventional linear mode. When the GPIO later reads the same memory, the memory subsystem will return the data in tiles. However each tile is simply interpreted as a linear stream of 64 bytes so the net result is that the command stream is interpreted correctly.

#### 2.1.4 Re-circulating Data

The difference between the two formats - planar byte tile for the graphics core and linear bytes for the GPIO – means that some care is required where command data is recirculated from graphics core to the GPIO. For example, during <u>displacement mapping</u> vertex data, generated by a Vertex Shader program, is written out to local memory and then read back in via the GPIO.

Some suggested solutions to the memory reformatting necessary for this case form a part of <u>section 10.2.2</u> that describes the implementation of displacement mapping in detail.

#### 2.2 Memory Management Introduction

P10 provides the basic tools for implementing a memory management system. The mechanisms provided are:

- a page table to map a logical address to a physical address and determine the validity of pages;

- an interrupt to indicate a page fault;

- a DMA controller to facilitate the transfer of pages between system memory and graphics memory under software control.

We discuss the usefulness of these approaches in the following sections.

#### 2.2.1 Advantages and Disadvantages of Virtual Memory

The page table mechanism provided by P10 allows a level of indirection to be set up that maps from a logical address space to a physical address space. This flexibility gives rise to the advantages provided by the concept of virtual memory.

One of the advantages of virtual memory is that of easier and more efficient management of a physical memory resource. When a memory management system is running it has to handle numerous allocate and free requests of different sizes and at different times. Typically over time this leads to fragmentation of the physical memory, so that the unused sections of memory can be scattered about the address range in small pieces. This can lead to situations where an Allocate request for a contiguous address range cannot be satisfied by any of the available unused contiguous address ranges, despite the fact that the unused memory in total would be sufficient to satisfy the request. Virtual memory makes it possible to handle this situation by exporting a contiguous logical address range that satisfies the allocation request. The logical to physical mapping allows the logical address range to be supported by numerous unused physical pages that are not at physically contiguous addresses.

Another advantage of virtual memory is the ability to be able to support situations where the memory requirements exceed the size of the physical memory available (which therefore could not be supported with a simple physical memory management). Virtual memory allows the physical memory to be treated as a fast cache, which can be used in combination with host memory and even host disk space to support memory requirements much greater than just the cache size.

The only disadvantage of virtual memory is the possible impact the memory address translation may have on the memory access performance. Any performance impact obviously depends on the implementation.

## 2.3 Address Translation Without Page Faulting

This section considers the possibility of simply enabling address translation on P10 to improve physical memory management efficiency. In this case the logical address space can be considered as the same range as the physical address space and the page faulting mechanism is not used.

#### 2.3.1 Address Translation Initialisation

A number of control registers manage the behaviour of the memory controller. For a full definition of these control registers refer to the *Reference Guide* volume 2, : Control Registers. All registers are on 64 bit

P10 Programmers Guide Memory

boundaries except the fifo registers which are packed to allow bursts. The register definitions show addresses in multiples of 32 bits.

Firstly, the memory should be idle before any changes are made, which can be tested by checking the busy flag in the <u>MemoryControl</u> register. Then the following registers need to be set up:

#### 2.3.1.1 MemoryPageTableLower and MemoryPageTableUpper

The *Type* bitfield is set to Video if the page tables are being held in local memory (which is the preferred option for best address translation performance).

The address at which the page table entries are to be defined is given as a page address, not byte address, and can make use of a maximum of 52 bits. The lower 20bits of the address are written appropriately in **MemoryPageTableLower** and the upper bits in **MemoryPageTableUpper**.

#### 2.3.1.2 MemoryPageTableLimit

The size of the desired logical address range precisely defines the number of page table entries needed. One page table entry is needed for every 4K of logical address range. The total size of the page table entries (in units of pages) is written to the **MemoryPageTableLimit** register.

Address translation can be enabled/disabled differently per memory access type using the **MemoryTranslationEnable** register:

- The Bypass bit controls bypass read/write accesses.

- The Texture bit controls texture read accesses.

- The GraphicsProcessor bit controls graphics core read/write accesses, apart from texture accesses.

- The CommandProcessor bit controls the GPIO read accesses.

- The Video bits control the read accesses made for video refresh.

- [P9] The Segment bits control the upper 2 bits of system address if translation is disabled<sup>1</sup>

A typical scenario will be to enable translation consistently for all accesses, apart perhaps from the video accesses.

#### 2.3.1.3 MemoryPageTableLimit exceeded

If a virtual (byte) address exceeds the virtual address range implied by the Pager Table limit then page 0 of the Page Table is examined and defines how the "Out of Range" access is handled. Later sections (below) describe how pagetable entries can be initialised to report page faults.

#### Page Table Format

Each table entry allows for a 64bit byte-aligned physical address, and to achieve this each entry takes 64 bits and is packed on 64 bit boundaries. The format of a page-table entry is:

<sup>&</sup>lt;sup>1</sup> The P9 virtual address range is 4G. If virtual addressing is turned off the upper 2 bits of the address indicate the type of memory access (video memory, PCI, AGP) which takes the range down to 1G. As system address can be above 1G the segment bits suplement the address. They are only used when virtual addressing is off and are really there for debug.

Memory P10 Programmers Guide

| Bit   | Name            | Description                              |

|-------|-----------------|------------------------------------------|

| 0-1   | State           | 0 = Invalid                              |

|       |                 | 1 = Not Resident                         |

|       |                 | 2 = Read Only                            |

|       |                 | 3 = Read/Write                           |

| 2     | ContinueOnFault | 0 = Stall until fault fixed              |

|       |                 | 1 = Report fault and continue            |

| 3-5   | Size            | 0 = 4K byte page size                    |

|       |                 | 1 = 8K byte page size                    |

|       |                 | 2 = 16K byte page size                   |

|       |                 | 3 = 32K byte page size                   |

|       |                 | 4 = 64K byte page size                   |

|       |                 | 5 = 128K byte page size                  |

|       |                 | 6 = 256K byte page size                  |

|       |                 | 7 = 512K byte page size                  |

| 6-7   | Туре            | 0 = Video                                |

|       |                 | 1 = System (PCI)                         |

|       |                 | 2 = System (AGP)                         |

|       |                 | 3 = Reserved                             |

| 8-11  | Reserved        |                                          |

| 12-63 | PhysicalPage    | Start address of the 4K page in physical |

|       |                 | memory                                   |

**Table 2.1 Format for Page Table Entries**

#### 2.3.1.4 The State Field

Expanding the State bitfield in more detail:

- A value of 0 marks the page as invalid; accessing an invalid page is an error and will result in a page fault interrupt.

- A value of 1 marks the page as valid but not resident in physical memory and accessing the page will

result in a page fault interrupt.

- A value of 2 marks the page as valid, resident and read only. Write access to this page will result in a page fault interrupt.

- A value of 3 marks the page as valid, resident and allows write as well as read access.

At start of day, prior to any allocations from the logical address space, the State field for all entries will be 0. Then, as allocations proceed, for a non-paging scheme the relevant entries will be updated to values of either 2 or 3 and only reset to 0 when the allocation is explicitly freed.

#### 2.3.1.5 ContinueOnFault Field

The ContinueOnFault field allows P10 to support complex virtual texture paging operations.

ContinueOnFault is normally 0. As defined by the State field, a page access may result in a page fault which causes an interrupt and stalls the page access. This allows the device driver to either:

- signal an access error or

- repair the fault, change the page state, and restart the access.

However if *ContinueOnFault* = 1, the page access takes place regardless of whether a page fault interrupt has been signalled or not.

The <u>PhysicalPage</u> field in the Page Table must always be a valid address when <u>ContinueOnFault</u> is set Similarly when <u>MemoryTranslationEnable</u> enables <u>Bypass</u>, then the bypass accesses automatically act as if <u>ContinueOnFault</u> is set regardless of the Page Table entry, and the entry for bypass access must always be associated with a valid physical page.. This safeguard prevents the system locking out all bus accesses due to a bus access fault when bus access is needed to repair the fault.

Note: Continue-on-Fault uses the physical address so the offending access is performed **before** the fault is flagged.

P10 Programmers Guide Memory

#### 2.3.1.6 PhysicalPage and Size Fields

Pages in memory are always 4K bytes, and each 4K page has its own page table entry, with the <a href="PhysicalPage">PhysicalPage</a> field giving the start address of that 4K page in physical memory. The Size field in the page-table provides further information about allocation, indicating that a number of 4K pages are allocated consecutively and start on a suitable boundary. For example, if the Size field has the value "2" it indicates this page is one of a group of four consecutive 4K byte pages in physical memory, and also that the logical and physical start addresses of this 16K "page" are aligned to a 16K byte boundary. The Size field allows address translation hardware to optimise reading of the page tables and reduce the number of TLB updates, although the hardware can choose to ignore this information and will still operate correctly (because the PhysicalPage field always contains the correct start address for each individual 4K page regardless of any Size information). Where possible buffers should be allocated with the largest page size possible. A 4K byte page holds 64 tiles which run horizontally across the screen. Moving vertically will result in a TLB miss for every tile if large pages are not used. A 512K byte page will hold 128 lines of a 1024 wide screen of 32 bit pixels.

#### 2.3.1.7 *Type* Field

The *Type* bitfield is set to 0 if the physical memory is local graphics memory. Values of 1 or 2 are used when the memory has been allocated from host system memory and in addition has been locked down to a physical page of system memory. The DMA transfer protocol to access the system memory is either PCI (1) or AGP (2). If the system memory is cacheable memory then using PCI protocol will guarantee to give the right results (cache snooping occurs). If AGP protocol is wanted then the host software will need to take care of any cache flushing required explicitly. The Type field can be different for each page table entry, so in general the physical memory can be a mixture of local and system memory.

The *PhysicalPage* field normally holds the physical address of the page. This is a 64bit byte address to support extended addressing into system memory. The address is actually given in units of pages so the bitfield is 52 bits wide.

#### 2.4 Memory Management With Page Faulting

This section describes the use of page faulting in combination with address translation to achieve a system that can support large memory requirements (typically greater than the physical local memory available).

Note: This section assumes that the reader is familiar with P10's plain address translation support, described in section 2.3, Address Translation.

The basic method is to define a logical address range that can be much larger than the size of the local physical memory. Then the physical memory is treated as a fast cache that can be used in combination with system memory to support the logical address range. Every 4K of logical address range has a corresponding page table entry. A subset of these entries is mapped to physical memory. Some of the other entries are mapped instead to system virtual memory that acts as backing store. Any memory accesses within the address range of a page table that does *not* map to physical memory is arranged to cause a page fault interrupt and the graphics core is stalled.

The interrupt gives the system host an opportunity to reallocate the mappings in the page table entries. First the host arranges for the entry that faulted to be given a page in physical memory. This may involve reusing a physical address that was previously allocated to another entry. (The other entry is therefore updated to map to appropriate backing store and loses its physical mapping.) The host then has to arrange for the physical address to be loaded with the correct data for the faulting entry. This will typically involve first locking down the system memory acting as backing store. A DMA controller is then available to copy the data from system physical memory to the physical memory allocated for the faulting page table entry. Once the physical page and its data are in place, the host finally signals for the hardware to proceed again.

A typical memory management scheme can provide two types of allocation from the logical address range:

- One type creates a mapping to physical addresses that are then permanently fixed to that allocation and never released for re-use until the whole allocation is explicitly freed. Allocations for graphics buffers such as front and back buffers and depth buffers are typical cases.

- The other type of allocation maps to physical addresses where these addresses are allowed to be reallocated as new allocation requests are invoked (i.e. allows the paging mechanism to operate). Texture maps are a typical example of use for this allocation type.

Memory P10 Programmers Guide

#### 2.4.1 Page Table Format Revisited

The *State* bitfield is set to 1 for any entries that are being used for a logical allocation but do not currently map to a physical address. In this case the *PhysicalPage* field can be used by the host memory management to hold a system virtual address that points to the data. The Type field is set to 0 if the data is to be copied into a local memory physical address.

The ContinueOnFault field is typically set to 0, which causes the graphics core to stall until a page fault is signalled as fixed (i.e. correct data in a physical page is present).

All transactions that cause a fault must complete eventually and it is not possible to kill an operation that has been started. If it is important that, for example, a write to read-only page does not complete, the page should be remapped to a safe area of memory.

Note that transactions originating as slave PCI/AGP accesses are not suspended if they fault. Suspending bus transactions could cause deadlock, so the hardware behaviour in this case is that the access completes and the fault is reported to indicate there has been an error. These slave accesses correspond to bypass reads or writes, which should therefore always be to a page that is present and valid.

#### 2.4.2 DMA Controller

When a page fault is detected data will normally have to be transferred from system memory to video memory. This may be done directly by the CPU reading system data and writing it directly to the chip, or by programming the DMA controller. The sequence of operations to fix a fault will usually be:

- 1. Fault detected.

- 2. Retrieve ID giving cause of fault retrieved from the PageControl fifo.

- 3. Remedy determined, list of pages to be paged out and paged in constructed.

- 4. DMA and table update commands sent to PageControl fifo.

Note: Page Control FIFO operations which cause a Page Table update use a logical page number which is not validated against the <u>PageTableLimit</u> register.

The cause of the page fault is communicated to the host via 4 dwords through the Page control fifo. These dwords are read from the fifo in order, while the <u>pagecontrolfifocount!=0</u>

| FIFO Fault Word      | Description                                              |

|----------------------|----------------------------------------------------------|

| Fault ID             | The ID identifies the source of the address fault and is |

|                      | used to restart the correct part of the memory           |

|                      | controller. The ID matches the bit field values defined  |

|                      | for the MemoryTranslation Enable command (see            |

|                      | below).                                                  |

| Logical page address | The actual page that faulted.                            |

| Table entry (1)      | 64bit page entry from the page Low 32 bits               |

| • • •                | table that caused the fault (differs                     |

| Table entry (2)      | from logical page address when High 32 bits              |

| 1                    | Page Table. Size > 4                                     |

Table 2.2 FIFO Page Fault Data

| ID Value | Fault Location         |

|----------|------------------------|

| 0        | Graphics Processor     |

| 1        | VGA                    |

| 2        | Command Processor      |

| 3        | Bypass                 |

| 4        | Reserved               |

| 5        | Reserved               |

| 6        | Video Processor Head 0 |

| 7        | Video Processor Head 1 |

Table 2.3 Page Fault Location ID Values

From this information the backing store for the faulting address can be identified and the fault processed.

P10 Programmers Guide Memory

If the system memory used as source or destination of paging is not locked down then the CPU must handle the copy directly through the bypass. Table update commands should still be sent through the PageControl fifo to ensure correct ordering. All commands sent to the PageControl fifo take 4 dwords (1 AGP fast write). The format is:

| Word       | Bits       |                         |

|------------|------------|-------------------------|

| 1          | 0,1        | Command                 |

|            |            | 0 = Table update        |

|            |            | 1 = System to video DMA |

|            |            | 2 = Video to system DMA |

|            |            | 3 = Invalidate          |

|            | 2          | Interrupt on completion |

|            | 39         | Reserved                |

|            | 1031       | Page                    |

| Command =  | Table up   | date                    |

| 2          | 0.31       | Table entry             |

| 3          | 031        | Table entry             |

| Command =  | DMA (eit   | her type)               |

| 2          | 05         | Reserved                |

|            | 67         | Туре                    |

|            |            | 0 = Reserved            |

|            |            | 1 = PCI                 |

|            |            | 2 = AGP                 |

|            | 811        | Reserved                |

|            | 12.31      | System page             |

| 3          | 031        | System page             |

| Command =  | Invalidate | e                       |

| 2          | 0.31       | Reserved                |

| 3          | 031        | Reserved                |

| All comman | ds         |                         |

| 4          | 07         | Restart                 |

|            | 815        | Reserved                |

|            | 1623       | Suspend                 |

|            | 2431       | Reserved                |

#### Table 2.4 Page Control FIFO Update Command Structure

The first word holds the type of command in the lower 2 bits. The options are to:

- modify a page table entry

- transfer data from system to video memory

- transfer data from video to system memory, or

- invalidate the entries in the TLB (translation look-aside buffer, a cache of page table entries).

An additional bit indicates that an interrupt should be raised when the command has completed. The upper bits of the first word hold a page number that this command will use.

The following 2 words are interpreted according to the command:

Memory P10 Programmers Guide

• When doing a page table update the second and third words hold the page table data that should be loaded into the table at the address given previously.

- If the command is a DMA then the page number specified in the first word is taken as the address in local memory. The following two words specify the system address (which is a page aligned 64 bit address).

- If the command is to invalidate the TLB, the second and third words are reserved.

The fourth word holds a mask of the possible source of memory transactions that should be suspended before this command starts, and restarted after it completes. This gives control over the accesses to areas of memory that are being updated to resolve a page fault.

When a page fault occurs, the memory controller halts all further processing on the source of the fault. As there are several sources, each with their own dedicated fifo into the memory controller, page translations can be done in parallel.

After the host has performed all the necessary transferring of data and page table updates to satisfy the page fault, the chip must be signaled to indicate that the faulting source can continue with its access request. The memory controller is told to continue with processing on a faulted source by raising the corresponding bit in the restart field of the fourth word. This not only allows processing to restart on that source, but also invalidates the associated TLB cache, thus causing the TLB entries that have been outdated by the page fault handling to be re-loaded.

When using the Restart mask in operations such as Table Update a suspend mask must also be used. The Suspend mask must have bits set for every currently-suspended source.

#### 2.4.2.1 Manipulating multiple 4K pages

Special considerations apply to page faults where several pages of memory need to be updated. For the entire duration of the updates, the relevant <u>suspend</u> bit in the fourth word of the update command sent to the Page Control FIFO must be held high. This ensures that the memory controller maintains the fault as blocking the associated source.

On the last page manipulation operation, the relevant restart bit is held high and the memory controller is finally restarted.

This mode of operation is required when dealing with several pages at a time. The host has the option to perform a number of page updates when a fault occurs, rather than fixing up only the page that faulted. This might be an advantage for performance reasons, if the host knows that related pages are also very likely to be needed. Overhead costs such as the OS calls required to lock down system memory can be amortised over a larger number of page updates.

Also, the *suspend* bit is required to be held high when dealing with faults on pages that have sizes larger than 4K, because the DMA engine can only handle 4K of data at a time and so the data must be copied in 4K chunks.

#### 2.4.3 Page Replacement Algorithms

When a new physical page is needed to satisfy a page fault it is possible that an existing page will have to be reused. There are three commonly used page replacement algorithms: least recently used (LRU), first-in first-out (FIFO), and random.

**LRU** is generally considered the best algorithm. It replaces the page that has been least recently used (i.e. was last used further back in time than any other). It relies on future activity being similar to past activity. Its draw back is the cost of maintaining a list of page usage. Most UNIX systems use modified LRU that replaces the full list with an approximation constructed periodically by a paging demon.

**FIFO** replaces the page that was loaded further back in time than any other. This is subtly different to LRU because it does not take usage into account. In this case, data which is frequently accessed over a long period of time can still get swapped out and then back in again. Windows NT uses this algorithm because the management overheads are much lower (per page fault instead of per access).

**Random** replacement simply picks the page to replace at random, and is normally the worst algorithm, although it can improve performance of some list processing with particularly random access patterns.

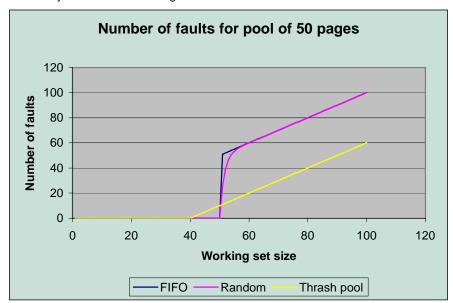

P10 hardware does not track page usage data (i.e. per access), so the LRU algorithm is not an option, but the FIFO algorithm is a recommended option. Consider the behaviour of the replacement algorithms for two common scenarios: thrashing and working set replacement.

**Thrashing** happens when the amount of texture needed for a given frame is greater than the pool of pages available. In this situation the LRU algorithm gives the worst performance. Simplifying the situation, assume that all texture is accessed linearly, each page being used once in each frame. The LRU algorithm

P10 Programmers Guide Memory

replaces the oldest page, which means that by the end of the frame every page will have been swapped - i.e. there is no reuse. The performance of LRU is good up to the point where one more page than there is room for is needed, at which point it collapses and requires every page to be loaded each frame. FIFO performance is similar. Random replacement is slightly better than FIFO because there is a (small) chance that useful data is retained.

The best way to handle thrashing appears to be to allocate a new 'thrash pool' which is separate to the normal working set pool. When thrashing is detected the working set pool is left as it is and all new pages are loaded into the thrash pool. This prevents useful pages being swapped out and only thrashes the overflow from the working set. The replacement algorithm used within the thrash pool can be the same as is normally used for the working set.

The chart shows steady state page replacement performance when the system is thrashing; it assumes a working pool of 50 pages and working set that ranges from zero to 100 pages. The chart shows that FIFO performance hits a cliff as soon as the working set is bigger than the pool. Random replacement is better because, at least with relatively few pages over the pool size, some useful data is retained. Reserving space for the thrash pool makes it start issuing faults earlier (10 pages are reserved), but as the working set size increases it is better at keeping useful data resident.

Thrashing can be detected by counting the number of faults reported in a frame. If it reaches the number of pages in the working pool the system is thrashing. There is no easy way to detect the end of thrashing after switching over to using the thrash pool, other than to occasionally switch back to working pool.

Working set replacement occurs when the scene drawn changes and some textures are no longer used and new ones need to be loaded. This situation favours LRU replacement. FIFO is a close approximation except for textures that are common across multiple scenes. These will age and be swapped out, only to be needed again within the same frame or the next one. Reloading common textures can be detected and minimized if the frame number that a page is swapped out is recorded in the replacement list. If it is reloaded in the same or next frame, then it can be treated as common and moved to a common pool that is kept resident. If the working pool starts to thrash then the common pool is added to the working pool so that pages that are no longer common can be swapped out.

3

# **Input and Output**

#### 3.1 Where to store commands and data

#### 3.1.1 Host memory

In general DMA buffers are written once by the CPU and are read only once by the graphics chip. For this reason it may be more efficient to store them in host memory where they can be accessed quickly by the CPU and then 'sucked' across the bus at AGP 4X rates.

Earlier 3Dlabs GLINT chips used this approach and it may still be the most efficient way for P10 in many cases. On legacy chips the overhead of starting a DMA was quite large which meant that performing many small DMA's was inefficient. P10 by contrast is very efficient for small DMAs.

#### 3.1.1.1 Framebuffer vs. Host Memory

A problem with storing DMA buffers and other data structures in host memory is Host Memory Contention. This arises where the host AGP chipset can't get access to host memory because it is being used by another process (e.g. SCSI controller or CPU). (This problem is characteristic of low-end PC systems with built-in graphics controllers that partition part of host memory and use it as the framebuffer.) The latest Pentium 4-class systems offer much improved memory performance but memory contention is still likely to be a problem. For this reason items accessed frequently by the graphics chip should be stored in the framebuffer.

#### 3.1.1.2 Framebuffer

Traditionally the framebuffer for a 3D graphics card consists of a front buffer, back-buffer and a cache of 3D textures, 2D bitmaps, fonts and various other 'surfaces'.

It makes sense for objects that need to be accessed frequently by the graphics chip (and infrequently by the host) to be stored in the framebuffer. Data structures such as **OpenGL Display Lists**, which are compiled once by the CPU and read multiple times by the graphics chip, used to be considered ideal candidates for framebuffer storage. Because of their size (100 Mbytes or more for high-end CAD applications) it often wasn't possible to fit them into a 32MB framebuffer. With P10's Logical Memory it is now possible to have a large virtual framebuffer (2 GB) and page in parts of data structures as needed.

There can also be a problem with **framebuffer memory contention** (video refresh etc) however it should be less noticeable than host memory contention because the memory interface of the graphics card is fast and optimized for the task whereas PC memory is generally slower and less specialized.

#### 3.1.1.3 Host chipset/CPU implications

Traditionally graphics chips have been programmed by storing graphics chip commands and data in DMA buffers. These buffers tended to be physically contiguous, non-pageable memory and were either **cacheable** (when the card is plugged into a PCI bus) or **uncached** (when plugged into an AGP bus).<sup>2</sup>

Note: If P10 Logical Memory is enabled the DMA buffer no longer needs to be contiguous - the graphics chip can scatter-gather the pages from host memory. However the memory should be 'locked down' on the host side (to stop the O/S paging it out) and also be shown as non-pageable to P10 so that it does in turn does not try to page it out.

When Intel added **USWC** (i.e. write-combining) support into their X86 processor, this small CPU cache provided a significant throughput boost when copying data into an uncached DMA buffer. USWC works by grouping up writes to USWC memory in a small cache and sending them in a burst rather than in single transactions.

The framebuffer can also be marked as USWC. This means that any writes to it will have their AGP burst size optimized in the same way as writes to a host memory DMA buffer.

<sup>&</sup>lt;sup>2</sup> PCI chipsets snoop the CPU cache which is why PCI supports cached memory but AGP does not.

Intel further tweaked the USWC support in the Pentium 4 processor, making it more difficult to use efficiently. However it is now possible to use **cached AGP DMA** buffers and an efficient instruction to flush the specific CPU cache lines before starting a DMA. This is not "privileged" – it can be called from applications where previously the flush instruction cleared all cache lines but was only callable by the kernel.

Unlike earlier chips, P10 supports **AGP Fast Writes.** This feature improves performance when writing directly to the framebuffer and makes it possible to store the DMA buffer in the framebuffer itself.

Note: Storing the DMA buffer in the framebuffer may not improve performance but it does use valuable framebuffer memory.

#### 3.2 Programed I/O vs. DMA

The simplest method of getting data into a piece of hardware is to write it, one word at a time, into some sort of input register. The problem with this is that a large FIFO buffer is required on this register in order to smooth over periods when the hardware can not consume the incoming data stream fast enough. Such large FIFOs are expensive in hardware terms and so undesirable. The host must also regularly check the amount of free space in this FIFO so as not to overflow it.

The alternative method is for the host to write its data stream into a normal memory buffer somewhere and let the hardware read it out via DMA as and when it is ready. Using standard system or graphics memory for this means there is no additional hardware cost for having very large buffers (e.g. 1MB or more). It also means that there can be an arbitrary number of independant buffers. So multiple processes can be filling in their own private buffers without fear of interference.

#### 3.2.1 The Input Message Port

Due to these performance limitations of the FIFO scheme, it was decided to include such a facility only as a debugging tool. The interface presented to the user is a very simple message port without any buffering (i.e. a 1-deep FIFO). The registers for controlling this are:

- IMsgReady

- IMsgTag

- IMsgData0 -> IMsgData3

The **IMsgReady** register contains a single bit which indicates the status of the IMP. If it is set, then data can be written to the other registers. This must be checked before every message/command which is sent to this port.

**IMsgTag** contains the 10-bit tag value and a 2-bit size. The 1-based size field indicates how many of the **IMsgData**# registers will be used to provide the data field. Writing the last 32-bit data value will trigger the sending of the message. Messages are always sent with 128 bits of data, if fewer bits are provided by the user, the following defaults are used:

IMsgData0: must be provided

IMsgData1: IEEE float 0.0

IMsgData2: IEEE float 0.0

IMsgData3: IEEE float 1.0

There is one message port for each rendering channel through the P10 core (see section 3.5, "<u>Dual Command Streams</u>").

#### 3.2.2 The DMA Interface

The proper way of getting data into the chip is to use DMA.

implements a sophisticated <u>circular buffer scheme</u> in hardware. The basic idea is to make the whole process as efficient as possible. This means keeping the buffer management overheads to a minimum.

The scheme is based around a hardware managed buffer with two pointers in to it. One is the chip's read pointer, the other is the host's write pointer. Basic operation is that the host will write to the front of the buffer and increment the write pointer. The chip will then start reading this data, incrementing the read pointer as it goes. By having both of these pointers as hardware registers, the chip will always know how much data is available for reading, and the host can always find out exactly how much data has been processed.

The buffer is initialised at start of day by setting **CbufAddr**, the logical address to read from (the start of the buffer). This can be in host memory or in video memory (see earlier for the pros and cons of each).

- Byte swapping enables if required.

- CBufEnableBusy:

- The context address if required (see section 3.6, <u>Multiple Contexts</u>).

The read and write pointers (CBufWrPtr & CBufRdPtr) can then be used. These are given as 32-bit word offsets from the start of the buffer. This means that the user's code does not need to worry about where the buffer is mapped in to the hardware's logical address space.

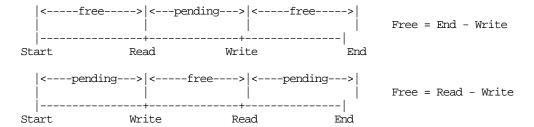

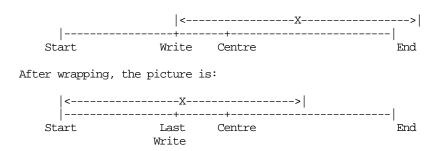

#### 3.3 Circular DMA Buffers

Because the read and write pointers are hardware managed, the buffer can be treated as a single, circular DMA buffer with a transfer granularity of one 32-bit word.

Wrapping around the end of the buffer is achieved by the simple operation of writing the write pointer back at the start. The DMA engine has no concept of where the end of the buffer is, it only knows what the highest write pointer value was and will read up to there. It does know what the buffer's start address value was though. So when the write pointer is set to a lower value than it was previously, this is interpreted as:

- Old (higher) value = end of buffer read from read pointer to here

- New (lower) value = 'current end' of next buffer read from start to here

The only restriction on the value put in the write pointer is that the engine must have finished reading any old data which was 'underneath' the new stuff. I.e., it must not overtake the read pointer. From a software point of view, this is a valid restriction anyway because if it happens, then the host will have been over writing data which had not yet been transferred.

#### 3.3.1 Layout, Read/Write Pointers and Scheduling - Software Implementation:

In general, the host will want to send DMA data in chunks of one or more complete commands. At the very least, it must not split a tag from its associated data. Also, the DMA code does not want to be reading or writing across the AGP bus for every word of dta which is to be added to the buffer. This implies a scheme involving three basic operations:

- Wait for X words of space

- Queue some data

- Send all gueued data

#### 3.3.1.1 Wait For Space:

This should be called before any chunk of data is added to the DMA queue. It must reserve at least as much space as there is data to queue. However, there is no need to get the figure exactly right, there is no problem or penalty if too much space is reserved (as long as it is not hugely inaccurate) as the buffer itself will normally be several orders of magnitude larger than the request.

What this operation needs to do is to add the requested size to the current write pointer and compare this new, potential write pointer to the current hardware read pointer. If it has gone past, then the routine must block in some manner until the read pointer has moved on enough.

#### A Mental Block

There are a number of ways the blocking can be achieved depending upon the intended application, the level of OS support, etc. The most basic is to simply poll the read pointer continuously until it reaches a suitable value. To avoid hogging the AGP bus, this polling loop should contain some sort of delay even if it is only executing a processor no-op instruction several hundred (or thousand, according to CPU speed) times.

A more system friendly approach would be to use some sort of OS provided semaphore mechanism. Command IDs (see below) could be inserted into the DMA stream at strategic intervals (e.g. after any particular large render command, or just every X words). For safety, the wait routine should probably add its own ID as well, just to make sure there is one in the buffer somewhere (although this means that the wait must always leave some space after it and never allow the buffer to fill completely).

The wait routine would then call the OS to block its process until a specific semaphore object has been signalled. The **CommandId**s would be set to generate an interrupt and the interrupt handler would signal this object and so wake the wait process.

Of course, care must be taken to ensure that the semaphore is cleared, signalled and waited on in a sensible order otherwise the **CommandId** could get missed and the system would deadlock.

#### Learning to Read:

Care must be taken when examining the read pointer because it can be in two different positions relative to the write pointer giving different calculations of how much fress space there is:

#### Round and Round and Round and ...

If the new write pointer is actually outside of the DMA buffer, i.e. it has run off the end, then the code must wrap around to the start again. In theory this is simply a case of starting the free space test again with a base address of zero rather than the current write pointer.

In practice, there is a problem if the request is for more than half the buffer size. For example, a request is made for X words and does not fit in the remaing space, X is also more than half the buffer size:

The problem here is that the last write pointer, and hence the place the read pointer will eventually stop at, is not far enough in for the request to be satisfied no matter how long the routine waits for.

- There are a number of solutions to this problem:

- Do not allow requests of more than half the buffer size;

- Keep track of the last write pointer and treat the buffer as empty when the read pointer matches it;

- Always queue some fake data at the start of the buffer when wrapping (e.g. a CommandId tag which

will be consumed by the DMA engine itself and so not interfere with any ongoing rendering). This will

ensure that the read pointer always wraps along with the wait routine and so will present an empty

(less two words for the CommandId tag) buffer.

#### 3.3.1.2 Queue Some Data:

This would be done by having a software only copy of the write pointer which is incremented as data is written into the buffer at its position.

#### **3.3.1.3 Send The Data:**

This is simply a case of copying the above software write pointer into the hardware one.

#### 3.4 DMA

DMA use in P10 is covered in previous sections on the <u>DMA Interface</u> (sect. 3.2.2) and <u>Circular DMA</u> (section 3.3) and in Isochronous DMA (section 3.5 below).

#### 3.5 Dual Command Streams

P10 supports two independent input streams: Graphics Processing (3D and regular 2D) and Isochronous.

#### 3.5.1 DMA stream

Input streams can be:

- Regular DMA

- Circular buffer (up to 16, automatically scheduled)

- From host memory or on-card memory

- At two levels of hierarchy

#### 3.5.2 Vertex and Index Data Stream

The GPIO unit supports two forms of caching of vertex and index data. Data can be cached either in the unit itself or in a post-T+L form further down the pipeline. The latter method can only be used with indexed primitives. This is discussed further in Section 3.7.2, <u>Caching</u> Indexed Vertex Arrays can use 8, 16 and 32 bit indices.

- Two sets of indices

- Index caching to control vertex caches

- · Independent lines, triangles and quads only

Vertex Array Elements may be:

- 1 to 4 words per parameter

- 1 to 16 parameters per element

- 1 to 16 disjoint parameter streams

...and are fully DX8 compatible

#### 3.5.3 Output DMA

The Output DMA stream returns data to host memory or local memory. It supports Image uploads and State return

#### 3.6 Multiple Contexts

In a modern system, there can be several different applications all wanting to draw their own private displays. The architecture provides dedicated support for up to sixteen completely independant rendering streams. As there is only one pipeline through the geometry and rasteriser engines, these different streams are multiplexed together at the DMA engine level.

Basically, there are sixteen different sets of read and write pointers, enables and base addresses. These operate entirely independently and so can be written to or read from by multiple processes or threads (even if they are running concurrently on multiple processors) without fear of interference.

This is achieved via a DMA scheduler. It is the scheduler's job to arbitrate between the various active DMA contexts and to keep the rest of the chip informed as to which context it is processing work for.

#### 3.6.1 Context Switching

In addition to issuing the DMA requests for each context as appropriate, the scheduler also tells the rest of the chip whether a given DMA request belongs to a different context from the previous one or not.?? In the case where the new request is for a new context, the old context's hardware state must be saved away and the new one's restored.

As previously mentioned, each context has an enable register which contains a context address. This is the logical tile address that the hardware state for that context is saved to. All impotnant state for the geometry and rasteriser units is saved and restored in this manner. The only exceptions are the internal registers of some of the programmable units. See the sections on each unit for details on programming for safe context switching.

#### 3.6.2 User-induced and Isochronous Switches

TBA

#### **3.6.2.1** Time Stamps

**TBA**

#### 3.6.3 Context Scheduling

The scheduler is based around a FIFO queing mechanism. Whenever a given context's write pointer is updated by the host, that context is added to the FIFO. If the context is already in the FIFO, the two requests are simply concatenated. Thus the FIFO can never overflow no matter how much work the host is queueing up.

As long as the output pipe from the scheduler is unblocked, the context at the head of the FIFO will be removed and whatever work it has outstanding will be forwarded to the DMA engine proper to be processed.

There is also a timeout mechanism which can be used to prevent context thrashing. For example, if two contexts are continuously being given tiny amounts of work to do then the scheduler can end up switching at the same rate and so issuing very inefficient, tiny DMAs with a full context save and restore on either side. If a time out value is set, then although the work will be issued for the context at the head of the queue as and when it comes in, that context will not be removed until after the time out expires. This will hold the next context off for a while and let it build up a reasonable amount of work which will subsequently be issued in a single, larger, more efficient lump. It also removes the majority of the context save and restores.

In practice, the timeout mechanism may not be necessary. If the chip can keep up with the requests no matter how inefficient they are, then there is no problem. If it can not, then it will back up behind which ever unit is busy. When the blockage reaches the scheduler, it will cease removing entries from its FIFO and begin concatenating requests. As soon as the blockage is gone, these larger requests will be issued. The pipeline between the scheduler and the DMA engine proper is very short so inefficient DMA requests will quickly stall the scheduler. Thus the whole susyem is fairly well self-regulating

#### 3.6.4 Driver Controlled Scheduling:

Under certain circumstances, it may be necessary for the driver to exercise some control over the order in which the various contexts are processed.

The simple level of control is the **SuspendUsr** register. This is a bit field of suspend flags, one for each of the sixteen user contexts. Any context whose bit is set will be blocked from placing its entry in the scheduler's FIFO. So this can be used to temporarily suspend one or more contexts until some particular condition has been met.

If more control is required, then the driver can take over the entire scheduling process and do everything manually. This is done by enabling the time out interrupt and the time out itself. The driver can then set the suspend mask to only allow one particular context to run. When the timeout interrupt occurs, the mask can be updated to allow a different context to run. In this way, the driver can schedule the various contexts in any order it sees fit in a completely deterministic manner irrespective of how the applications themselves are wanting to queue up their work..

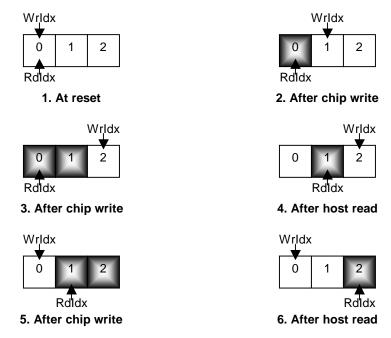

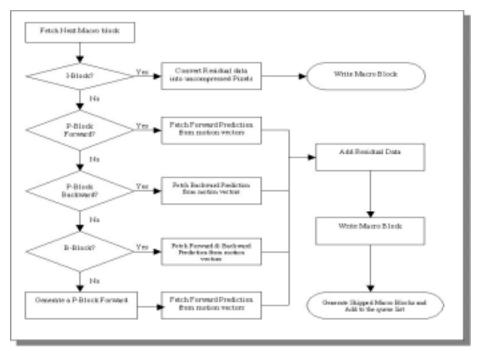

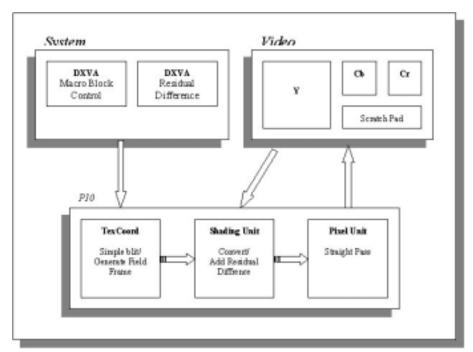

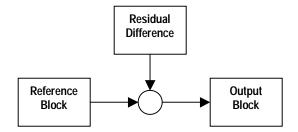

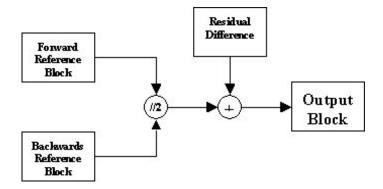

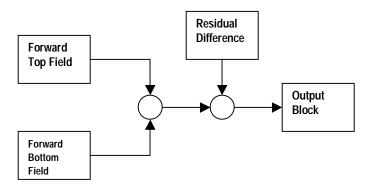

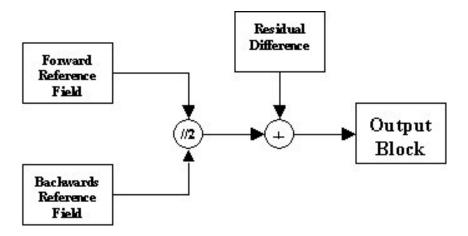

#### 3.6.5 Context Security