# GLINT R4®

Reference Guide Volume I -Overview

## **DRAFT ONLY**

## PROPRIETARY AND CONFIDENTIAL INFORMATION

# 3Dlabs®

# GLINT R4®

Reference Guide Volume I -Overview

## PROPRIETARY AND CONFIDENTIAL INFORMATION

**Issue 2**

#### **Proprietary Notice**

The material in this document is the intellectual property of **3D** labs. It is provided solely for information. You may not reproduce this document in whole or in part by any means. While every care has been taken in the preparation of this document, **3D** labs accepts no liability for any consequences of its use. Our products are under continual improvement and we reserve the right to change their specification without notice. 3Dlabs may not produce printed versions of each issue of this document. The latest version will be available from the **3D***labs* web site.

**3D***labs* products and technology are protected by a number of worldwide patents. Unlicensed use of any information contained herein may infringe one or more of these patents and may violate the appropriate patent laws and conventions.

**3D***labs* is the worldwide trading name of **3D***labs* Inc. Ltd.

**3D***labs*, GLINT and PERMEDIA are registered trademarks of **3D***labs* Inc. Ltd.

Microsoft, Windows and Direct3D are either registered trademarks or trademarks of Microsoft Corp. in the United States and/or other countries. OpenGL is a registered trademark of Silicon Graphics, Inc. All other trademarks are acknowledged and recognized.

© Copyright **3D***labs* Inc. Ltd. 1999. All rights reserved worldwide.

**3D**labs K.K.

Fax: +91-3-5403-4646

Email: info@3dlabs.com Web: http://www.3dlabs.com

3Dlabs Ltd.

Meadlake Place Shiroyama JT Mori Bldg 16F Thorpe Lea Road, Egham 40301 Toranomon Surrey, TW20 8HE Minato-ku, Tokyo, 105, Japan United Kingdom Tel: +81-3-5403-4653

Tel: +44 (0) 1784 470555

Fax: +44 (0) 1784 470699

3Dlabs Inc.

480 Potrero Avenue Sunnyvale, CA 94086, **United States** Tel: (408) 530-4700

Fax: (408) 530-4701

## Change History

| Document | Issue | Date           | Change                                                                                                                                                                                                                                                                                                            |

|----------|-------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 160.5.1  | 1     | 06 October 99  | Creation                                                                                                                                                                                                                                                                                                          |

| 160.5.1  | 2     | 05 December 99 | Corrected DMA description (1.16); VSA VBE modes 102, 104, 106 removed; consistent use of GLINT R4; errata updates; PCI Address maps and regions tables; add Delta Switch, MUX and updated Delta unit; PCI address map corrections; rewrite introduction; analog and digital striping, summary table; volume index |

## Table of Contents

| 1 | FU  | JNCTIC | ONAL OVERVIEW 1                                   | -1  |

|---|-----|--------|---------------------------------------------------|-----|

|   | 1.1 | Intro  | duction1                                          | -1  |

|   | 1.2 | Chan   | ges from P3/P41                                   | -3  |

|   | 1.3 | Funct  | tional Blocks1                                    | 5   |

|   | 1.4 | AGP,   | PCI Interface1                                    | -5  |

|   | 1.4 | .1     | Unified 2D/3D/Video Integrated Graphics Processor | -6  |

|   | 1.4 | .2     | Memory Interface                                  | -6  |

|   | 1.4 | .3     | SVGA                                              | -6  |

|   | 1.4 | .4     | RAMDAC                                            | -7  |

|   | 1.4 | .5     | Video Overlay                                     | -8  |

|   | 1.4 | .6     | DMA1DMA31                                         | -8  |

|   | 1.4 | .7     | Video Streaming                                   | -8  |

|   | 1.4 | .8     | ROM support                                       | -8  |

| 2 | Αſ  | DDRES  | SS MAPS AND REGIONS 2                             | -1  |

|   | 2.1 | PCI (  | Configuration Region2                             | 2-1 |

|   | 2.2 | Regio  | on Zero Address Map2                              | 2-2 |

|   | 2.3 | PCI A  | Address Regions                                   | 2-3 |

| 3 | VI  | DEO U  | NIT AND RAMDAC 3                                  | -1  |

|   | 3.1 | RAM    | DAC Characteristics                               | -1  |

|   | 3.1 | .1     | Display Resolutions                               | -1  |

|   | 3.1 | .2     | Display Data Channels (DDC)                       | -1  |

|   | 3.2 | Displ  | ay Timing Values3                                 | 5-2 |

1

## **Functional Overview**

#### 1.1 Introduction

GLINT R4 is a high performance PCI/AGP graphics processor and rasterizer that balances high quality 3D polygon and textured graphics acceleration with 2D acceleration, and state-of-the-art MPEG1/MPEG2 playback with a fast integrated SVGA core, integrated RAMDAC and video ports.

GLINT R4 is optimized to work with GLINT *Gamma* geometry engines to deliver exceptional processing bandwidth for workstation applications. This includes dual on-chip setup units, 64MB fast local memory, virtual texture caching, AGP4X bus support and multi-rasterizer capability.

GLINT R4 offers significant advances over earlier rasterizers in both raw performance and functionality:

| GLINT R4 Summary                                 |             |  |  |  |

|--------------------------------------------------|-------------|--|--|--|

| Interface and Memory                             |             |  |  |  |

| Memory bus width (bits)                          | 128 bits    |  |  |  |

| Core clock speed (MHz) – Provisional             | 125         |  |  |  |

| Max. memory                                      | 64Mbytes    |  |  |  |

| AGP with sideband and pipelining, 2x/4x protocol | V           |  |  |  |

| AGP I/O Signal voltage - dual voltage            | 1.5V / 3.3V |  |  |  |

| PCI Bus Aperture                                 | 128 bits    |  |  |  |

| Multi-rasterizer support and stripe ownership    | V           |  |  |  |

| Low-latency command DMA                          | V           |  |  |  |

| Write-combined command FIFO                      | V           |  |  |  |

| Independant DMA machines                         | 7           |  |  |  |

| SSE dynamic load balancing                       | V           |  |  |  |

| Unified SGRAM or SDRAM incl. SGRAM block write   | <b>✓</b>    |  |  |  |

| Context dump and restore in hardware             | <b>✓</b>    |  |  |  |

| Statistic collection and extent picking          | <b>✓</b>    |  |  |  |

| Texture Mapping                                  |             |  |  |  |

| Texture read units                               | 2           |  |  |  |

| Texture compositing                              | <b>✓</b>    |  |  |  |

| GLINT R4 Summary                                                 |          |  |  |  |

|------------------------------------------------------------------|----------|--|--|--|

| Single-pass dual texturing                                       | V        |  |  |  |

| Single-pass bump mapping with surface texture                    | V        |  |  |  |

| Hardware texture paging                                          | V        |  |  |  |

| Per polygon and per pixel mipmapping                             | V        |  |  |  |

| Bilinear and trilinear filtering, emulated anisotropic filtering | <b>V</b> |  |  |  |

| Bump mapping, 3D textures, RGBA and palletized textures          | <b>V</b> |  |  |  |

| 2k on-chip texture cache (max map size 2Kx2K)                    | V        |  |  |  |

| Virtual texture management, logical texture addressing           | V        |  |  |  |

| 3D Features                                                      |          |  |  |  |

| Max. Z-buffer depth (bits)                                       | 32       |  |  |  |

| Non-Linear 15 - 24-bit Z-buffer                                  | <b>✓</b> |  |  |  |

| (Direct3D and OpenGL)                                            |          |  |  |  |

| W-Buffer Emulation with Non-Linear Z-buffer (Direct3D)           | <b>'</b> |  |  |  |

| Destination Alpha, Alpha and color key tests                     | V        |  |  |  |

| All OpenGL and Direct3D blend modes                              | V        |  |  |  |

| Native support for Direct3D vertex formats                       | limited  |  |  |  |

| OpenGL 1.1/1.2 compliant / ready                                 | V        |  |  |  |

| Fogging, Fog table                                               | V        |  |  |  |

| Full hardware edge anti-aliasing                                 | V        |  |  |  |

| YUV - RGB conversion                                             |          |  |  |  |

| Specular and diffuse lighting support                            | V        |  |  |  |

| 2D Features                                                      |          |  |  |  |

| Logic Ops for mode registers                                     | V        |  |  |  |

| Single-register tag index setup for 2d primitives                | V        |  |  |  |

| Stretch and high-speed blts                                      | V        |  |  |  |

| Font caching                                                     | V        |  |  |  |

| DMA Packing / unpacking on output / input                        | V        |  |  |  |

| 32x32 stipple pattern                                            | V        |  |  |  |

| Run-length encode / decode                                       | V        |  |  |  |

| Anti-aliased line and triangle setup                             | V        |  |  |  |

| Bitmaps and rectangular scissor clip                             | V        |  |  |  |

| GLINT R4 Summary                                  |          |  |  |  |  |

|---------------------------------------------------|----------|--|--|--|--|

| Buffer Formats                                    | •        |  |  |  |  |

| Unified framebuffer/localbuffer                   | <b>✓</b> |  |  |  |  |

| Flexible GID, stencil and depth formats           | V        |  |  |  |  |

| Stencil planes                                    | 8        |  |  |  |  |

| GID bits                                          | 4        |  |  |  |  |

| Simultaneous framebuffer accesses                 | 4        |  |  |  |  |

| Any width framebuffer/localbuffer texture         | V        |  |  |  |  |

| 2d buffer tiling                                  | V        |  |  |  |  |

| Video/DVD                                         |          |  |  |  |  |

| Hardware video overlay                            | V        |  |  |  |  |

| 15 color on-chip cursor                           | <b>✓</b> |  |  |  |  |

| Display resolutions to 2048x1536x32 @ 60Hz        | <b>✓</b> |  |  |  |  |

| Hardware scaling and filtering                    | V        |  |  |  |  |

| Digital Video out                                 | V        |  |  |  |  |

| MPEG Motion compensation                          | V        |  |  |  |  |

| Memory to DVD accelerator DMA                     | V        |  |  |  |  |

| Flat panel LCD support, parallel bus panel output | V        |  |  |  |  |

| Video Genlock to any video source, R4 pixel bus   | V        |  |  |  |  |

| Integrated 300MHz RAMDAC                          | V        |  |  |  |  |

| LUT Accuracy                                      | 8        |  |  |  |  |

| Video overlay blend                               | 2 bit    |  |  |  |  |

| Video overlay with stretch and bilinear filtering | bilinear |  |  |  |  |

| Software                                          |          |  |  |  |  |

| SoftImage Compliant                               | V        |  |  |  |  |

| LightWave 6.0 (Win '98 and NT)                    | V        |  |  |  |  |

| Power Management                                  |          |  |  |  |  |

| DPMS for monitors                                 | V        |  |  |  |  |

| Memory array power-down                           | <b>v</b> |  |  |  |  |

| Dynamic clock control                             | <b>✓</b> |  |  |  |  |

**Table 1.1 GLINT R4 Enhancement Summary**

### 1.2 Changes from P3/P4

GLINT R4 removes a number of constraints found in Permedia3 and Permedia4. For more information see *GLINT R4 Errata* in Volume IV. The most significant pipeline change relative to the Permedia family is the use of dual on-chip setup (Delta) units which are primarily intended to provide the front-end capacity needed when working with geometry accelerators such as the GLINT *Gamma* chipset family. A switch unit allocates Draw and

Render commands to each Delta unit and a MUX recombines them for downstream processing.

The GLINT R4 setup units are designed to provide fast slope calculations and vertex data conversion to complement the functionality of the *Gamma* geometry engine. This pairing allows, for example, up to 16 simultaneous light sources and a throughput of 4.75M lit, transformed triangles/sec. in a typical *Gamma* plus GLINT R4 combination board.

There are several changes which specifically address the geometry accellerator + GLINT R4 combination. These provide a unified programming view of the chips when used in tandem. However GLINT R4 can function as a standalone rasterizer and still offer the significant price/performance benefits of dual setup engines, 64MB memory, 2K local cache, up to 256MB virtual texture etc.

Some of the GLINT R4 changes are:

**ReadMonitorMode** Monitors memory reads operations to reduce dependence on

the Suspend Reads mechanism to block out-of-sequence updates when subsequent framebuffer writes do not overlap.

SetDeltaPort Improved port setting capability for test use

Begin/End OGL-type primitve definition bounding supported

**DeltaMode** Bitfield modifications to extend *Gamma* compatibility (e.g.

TargetChip field). Redundant functionality (e.g. multi-texture

setup) removed, flat shading added.

FilterMode Support for external (i.e. Gamma) DMA

**EndOfFeedback** RLE mode filtering is not used with external DMA because the

tags are needed - see FilterMode in Volume III.

**ContextDump** Integrates Gamma and R4 states dump/restore in one

command.

ScanLineOwnership Multi-rasterizer support enhancements including stripe and

scanline ownership parameters

**Stripe Management** Support for stripe width, height, offset and ID parameters in

Framebuffer and local buffer operations.

**Point, Line, Triangle** and other aliased and antialiased primitive drawing modes

supported with logical operators (PointModeAnd,

LineModeOr...)

There are other graphics processing changes (relative to Permedia3 in particular) which are either documented in the Errata chapter in volume IV or are documented as core registers but not specifically identified (e.g. where the register is a deprecated legacy but retained for backward compatibility).

Changes in hardware registers are not specifically identified, but are largely confined to AGP4X support etc. in the **ChipConfig** register *AutoCal Enable*, *Alternate DeviceID Enable* and the provision of a series of Test registers (**TestInputRdy**, **TestOutputControl** etc.) which are documented in volume II.

#### 1.3 Functional Blocks

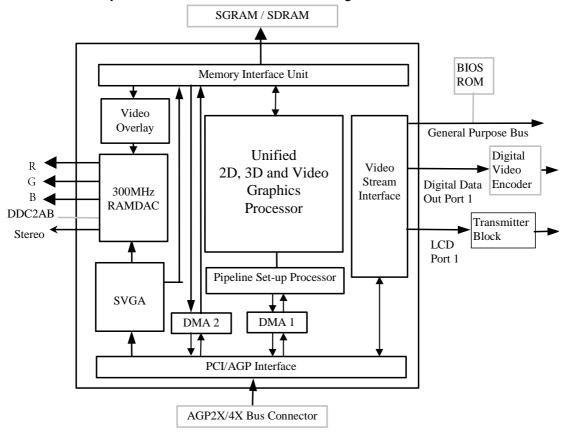

The major functional blocks are shown in Figure 1-1.

Figure 1-1 Chip Level Block Diagram

#### 1.4 AGP/PCI Interface

The PCI interface conforms to the PCI Local Bus standard Revision 2.2. GLINT R4 is a PCI Local Bus Target, a PCI Local Bus Read Master, and a PCILocal Bus Write Master. It is also an AGP read master with support for pipelined reads and sideband addressing.

The PCI interface has an input FIFO for passing data to the Graphics Core, and an output FIFO for buffering up data to be read from the Graphics Core. The input FIFO is 256 words deep, the output FIFO is 8 words deep. A DMA controller is provided in the PCI interface to allow GLINT R4 to read data directly into the Graphics Core input FIFO or directly out of the output FIFO.

AGP 4X is Intel's high performance, component level interconnect targeted at 3D display applications, which uses a 66MHz PCI specification as an operation baseline and provides significant performance extensions to the PCI specification.

The specification for GLINT R4's AGP implementation is:

- 266 MHz transfer rate

- DMA and execute mode support

- Sideband addressing

Implementing these features enables GLINT R4 to achieve better than 1 GByte per second bandwidth from the host for instructions, textures, video data (limited by the host system throughput).

The add-in slot defined for AGP uses a connector body which is not compatible with the PCI connector. Boards designed for use in an AGP slot are not mechanically interchangeable with PCI boards.

GLINT R4 is also fully compliant with the AGP2X standard, including support for both 3.3VDC and 1.5VDC drivers.

#### 1.4.1 Unified 2D/3D/Video Integrated Graphics Processor

The graphics core in GLINT R4 accelerates the key operations for 3D and 2D applications. For further information on the functionality of the graphics processor (GP), refer to chapter 5, Graphics Registers, in volume 2.

#### 1.4.2 Memory Interface

The local memory is used to store color, depth, stencil, and texture data. For more information on the different data types and usage refer to Chapter 9 - Memory System.

The memory is organized as 1 to 4 blocks (blocks 0-3) of SGRAM or SDRAM. The memory interface is 128 bits wide with control lines for 4 blocks of memories (0-3). Block zero must always be fitted as the SVGA uses this area for local storage. Any other combination of banks may be fitted, but for contiguous memory banks should be added from 1 to 3.

GLINT R4 makes use of special SGRAM features including block fill and write-per-bit masking. SDRAM may be used in place of SGRAM if it is identical to SGRAM except for missing block write and write per bit masks.

#### 1.4.3 **SVGA**

The on-chip SVGA unit is register level compatible with standard VGA devices and requires no software emulation. It natively supports all standard VGA modes and certain VESA VBE extended modes.

The following standard VESA VBE extended video modes are supported - those not supportable by the SVGA unit may be supported using the Graphics Processor:

Table 1-2 VESA VBE Graphics Modes

| Mode<br>(hex) | Pixels    | Colors        | Window-<br>ed | Lin-<br>ear | Support-<br>able in<br>SVGA | Support-<br>able in<br>GP |

|---------------|-----------|---------------|---------------|-------------|-----------------------------|---------------------------|

| 0x100         | 640x400   | 256           | ✓             | 1           | 1                           | 1                         |

| 0x101         | 640x480   | 256           | 1             | 1           | 1                           | 1                         |

| 0x103         | 800x600   | 256           | 1             | 1           | ×                           | 1                         |

| 0x105         | 1024x768  | 256           | 1             | 1           | ×                           | 1                         |

| 0x107         | 1280x1024 | 256           | 1             | 1           | ×                           | 1                         |

| 0x109         | 320x200   | 32K (5:5:5:1) | ✓             | 1           | ×                           | 1                         |

| 0x10D         | 320x200   | 64K (5:6:5)   | ✓             | 1           | ×                           | 1                         |

| 0x10F         | 320x200   | 16.8M (8:8:8) | ✓             | 1           | ×                           | 1                         |

| 0x110         | 640x480   | 32K (5:5:5:1) | ✓             | 1           | X                           | 1                         |

| 0x111         | 640x480   | 64K (5:6:5)   | ✓             | 1           | ×                           | 1                         |

| 0x112         | 640x480   | 16.8M (8:8:8) | ✓             | 1           | ×                           | 1                         |

| 0x113         | 800x600   | 32K (5:5:5:1) | ✓             | 1           | ×                           | 1                         |

| 0x114         | 800x600   | 64K (5:6:5)   | ✓             | 1           | X                           | 1                         |

| 0x115         | 800x600   | 16.8M (8:8:8) | ✓             | 1           | ×                           | 1                         |

| 0x116         | 1024x768  | 32K (5:5:5:1) | ✓             | 1           | ×                           | 1                         |

| 0x117         | 1024x768  | 64K (5:6:5)   | ✓             | 1           | ×                           | 1                         |

| 0x118         | 1024x768  | 16.8M (8:8:8) | ✓             | 1           | X                           | 1                         |

| 0x119         | 1280x1024 | 32K (5:5:5:1) | ✓             | 1           | X                           | 1                         |

| 0x11A         | 1280x1024 | 64K (5:6:5)   | ✓             | 1           | X                           | 1                         |

| 0x11B         | 1280x1024 | 16.8M (8:8:8) | 1             | 1           | ×                           | 1                         |

The following VESA VBE text modes are supportable in the SVGA:

Table 1-3 VESA VBE Text Modes

|            | 140.0 1 0 120/1122 10/110400 |  |  |  |  |

|------------|------------------------------|--|--|--|--|

| Mode (hex) | Characters (col/row)         |  |  |  |  |

| 0x108      | 80x60                        |  |  |  |  |

| 0x109      | 132x25                       |  |  |  |  |

| 0x10A      | 132x43                       |  |  |  |  |

| 0x10B      | 132x50                       |  |  |  |  |

| 0x10C      | 132x60                       |  |  |  |  |

GLINT R4 allows VESA bankswitching to be done through the bypass to enable additional VESA mode support. ModeX is also supported.

#### **1.4.4 RAMDAC**

GLINT R4 incorporates a high performance 300MHz 128-bit RAMDAC. It supports typical screen resolutions up to 1600x1200 with refresh rates of 96Hz or 1920x1080 with refresh rates of 90Hz, or 2048x1536 at 60Hz. It supports packed pixel formats, with color depths

of 8, 16, and 32 bits per pixel. It has dot-clock phase locked loops (PLLs) and triple 8-bit D/A converters. The RAMDAC contains a 64x64x2 bit cursor array to support a 2, 4, or 16 color hardware cursor with cursor shapes cache.

#### 1.4.5 Video Overlay

The video overlay is used to display incoming video data on screen. The overlay selection is based on a transparent color, the overlay key, which can be any RGB color or alpha value. Optionally, the overlay can be blended with the main image by using a 2-bit blend factor. A filter process supports zooming and shrinking at any rate. It combines four pixels into one by using bilinear filtering to achieve best results. Furthermore the filtered output is optionally converted from YUV to RGB color space format.

#### 1.4.6 DMA1..DMA3

#### 1.4.6.1 DMA1 Controller – System to Graphics Core and Graphics Core to System

- Autonomous set-up/fetch parallelism

- No wait state maximum transfer rate

- Programmable block size large DMA buffers

- Separate DMA controllers for upload and download can run concurrently

#### 1.4.6.2 DMA2 Controller - System to Memory and Memory to System

- Fast texture/image uploads and downloads

- Separate DMA controllers for upload and download can run concurrently

- DMA Controller supports scatter/gather

- Fast software MPEG2 download, fast frame capture

#### 1.4.6.3 Interrupt Controller

- End-of-DMA allows DMA chaining

- VSYNC efficient double buffering

- Scanline special effects

- Texture invalid

- Bypass DMA interrupt

- I2C start condition alert host to start of I2C transfer

- Sync indicates graphics core is idle

- Error e.g. writing to a full FIFO

#### 1.4.7 Video Streaming

GLINT R4 supports digital video output. The 24-bit streamed output is designed to work with common PAL/NTSC encoders or flat panel controllers.

#### 1.4.8 ROM support

GLINT R4 supports a Flash ROM. This ROM may store code needed for device-specific initialization and the SVGA BIOS.

2

## **Address Maps and Regions**

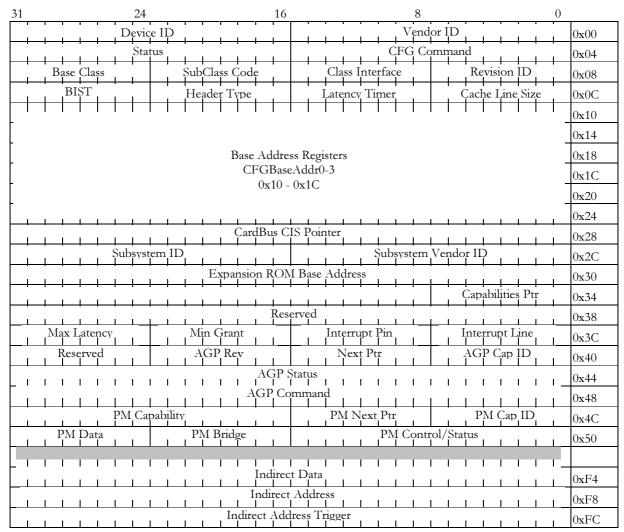

#### 2.1 PCI Configuration Region

The PCI Configuration Region provides information that satisfies the needs of current and anticipated system configuration mechanisms. Configuration registers are read and modified via the Configuration registers (see volume II).

**PCI Configuration Region**

## 2.2 Region Zero Address Map

The GLINT R4 region zero address map is shown in Table 2-1:

| Address Range          | Region Select                               | Byte Swap/<br>Write Combined |

|------------------------|---------------------------------------------|------------------------------|

| 0000.0000 -> 0000.02FF | Control Status                              | No                           |

| 0000.0300 -> 0000.03FF | Bypass Control                              | No                           |

| 0000.0400 -> 0000.0FFF | Repeat of the Control and Bypass<br>Decodes | No                           |

| 0000.1000 -> 0000.1FFF | Memory Control                              | No                           |

| 0000.2000 -> 0000.2FFF | GP FIFO Access                              | No                           |

| 0000.3000 -> 0000.30FF | Video Control                               | No                           |

| 0000.3100 -> 0000.3FFF | Video Overlay Control                       | No                           |

| 0000.4000 -> 0000.4FFF | RAMDAC                                      | No                           |

| 0000.5000 -> 0000.57FF | VS GP                                       | No                           |

| 0000.5800 -> 0000.5FFF | VSCtl                                       | No                           |

| 0000.6000 -> 0000.6FFF | VGA Control                                 | No                           |

| 0000.7000 -> 0000.7FFF | TextureData FIFO                            | No                           |

| 0000.8000 -> 0000.FFFF | GP Registers                                | No                           |

| 0001.0000 -> 0001.01FF | Control Status                              | Yes                          |

| 0001.0300 -> 0001.03FF | Bypass Control                              | Yes                          |

| 0001.0400 -> 0001.0FFF | Repeat of the Control and Bypass<br>Decodes | Yes                          |

| 0001.1000 -> 0001.1FFF | Memory Control                              | Yes                          |

| 0001.2000 -> 0001.2FFF | GP FIFO Access                              | Yes                          |

| 0001.3000 -> 0001.37FF | Video Control                               | Yes                          |

| 0001.3800 -> 0001.3FFF | Video Overlay Control                       | Yes                          |

| 0001.4000 -> 0001.4FFF | RAMDAC                                      | Yes                          |

| 0001.5000 -> 0001.57FF | VS GP                                       | Yes                          |

| 0001.5800 -> 0001.5FFF | VSCtl                                       | Yes                          |

| 0001.6000 -> 0001.6FFF | VGA Control                                 | Yes                          |

| 0001.7000 -> 0001.7FFF | TextureData FIFO                            | Yes                          |

| 0001.8000 -> 0001.FFFF | GP Registers                                | Yes                          |

Table 2-1 Region Zero Address Map

## 2.3 PCI Address Regions

GLINT R4 has seven base address regions, as shown in Table 2-2:

| Region | Address<br>Space | Bytes | Description            | Comments                 |

|--------|------------------|-------|------------------------|--------------------------|

| Config | Configuration    | 256   | PCI Configuration      | PCI special              |

| Zero   | Memory           | 128K  | Control Registers      | Relocatable              |

| One    | Memory           | 128M  | Memory Aperture<br>One | Relocatable              |

| Two    | Memory           | 128M  | Memory Aperture<br>Two | Relocatable              |

| Three  | I/O              | 16    | Indirect Access I/O    | Optional and Relocatable |

| ROM    | Memory           | 64 K  | Expansion ROM          | Relocatable              |

| VGA    | Memory &<br>I/O  | _     | VGA Access             | Optional and Fixed       |

Table 2-2 GLINT R4 PCI Address Regions

3

### **Video Unit and RAMDAC**

GLINT R4 incorporates a high performance 300MHz RAMDAC The video unit and RAMDAC should be configured to display the framebuffer data with the format, resolution, and refresh frequency required.

#### 3.1 RAMDAC Characteristics

- High resolution 300 MHz, 128-bit RAMDAC

- Supporting screen resolutions up to 1600x1200@96Hz or 1920x1200@82Hz refresh rate

- Supports packed pixel formats

- Color depths of 8, 16 and 32 bits/pixel

- Dot clock phase-locked loop (PLL)

- Triple 8-bit D/A converters

- 64x64x2-bit cursor array to support a 2, 4 or 15 color hardware cursor with cursor shapes cache

- Analog and digital striping

#### 3.1.1 Display Resolutions

GLINT R4 supports all the standard screen resolutions at ergonomic refresh rates. For each resolution and color depth in the table below, the frequency figure represents the refresh rate supported using the VESA generalized Timing formula with 50% of the memory bandwidth used for screen refresh and 50% for drawing assuming a pixel clock of 300MHz.

| Resolution | 8 bpp   | 16 bpp  | 32 bpp  |

|------------|---------|---------|---------|

| 320x200    | 220 Hz  | 220 Hz  | 220 Hz  |

| 640x480    | 220 Hz  | 220 Hz  | 220 Hz  |

| 800x600    | 220 Hz  | 220 Hz  | 220 Hz  |

| 1024x768   | 217 Hz  | 217 Hz  | 217 Hz  |

| 1152x864   | 176 Hz  | 176 Hz  | 176 Hz  |

| 1280x1024  | 137 Hz  | 137 Hz  | 137 Hz  |

| 1600x1200  | 96 Hz   | 96 Hz   | 96 Hz   |

| 1920x1080  | 90 Hz   | 90 Hz   | 90 Hz   |

| 1920x1200  | 82.3 Hz | 82.3 Hz | 82.3 Hz |

**Table 3.2 Display Resolutions**

Resolutions are driver and memory limited. A 32MB framebuffer for example can support 2048x1200 @ 32bit colour, 32bit Z; or 2048x1536 @ 32bit colour, 16bit Z.

#### 3.1.2 Display Data Channels (DDC)

Two control lines are dedicated on GLINT R4 to support DDC1 and DDC2AB+ monitor configuration utilities. The DDC2 serial bus is independent of the serial bus in the video stream interface.

3-2

## 3.2 Display Timing Values

Table 3-1 Timing Values for 640x480 16 BPP 75Hz

| Parameter    | Hex   | Decimal |

|--------------|-------|---------|

| HTotal       | 0x065 | 101     |

| HsStart      | 0x003 | 3       |

| HsEnd        | 0x00B | 11      |

| HbEnd        | 0x016 | 22      |

| HgEnd        | 0x016 | 22      |

| VTotal       | 0x1F5 | 501     |

| VsStart      | 0x000 | 0       |

| VsEnd        | 0x003 | 3       |

| VbEnd        | 0x016 | 22      |

| ScreenStride | 0x050 | 80      |

| ScreenBase   | 0x000 | 0       |

| VideoControl | 0x029 | 41      |

Table 3-2 Timing Values for 800x600 32 BPP 75Hz

| Parameter    | Hex   | Decimal |

|--------------|-------|---------|

| HTotal       | 0x103 | 259     |

| HsStart      | 0x00A | 10      |

| HsEnd        | 0x01E | 30      |

| HbEnd        | 0x03C | 60      |

| HgEnd        | 0x03C | 60      |

| VTotal       | 0x272 | 626     |

| VsStart      | 0x000 | 0       |

| VsEnd        | 0x003 | 3       |

| VbEnd        | 0x01B | 27      |

| ScreenStride | 0x0C8 | 200     |

| ScreenBase   | 0x000 | 0       |

| VideoControl | 0x029 | 41      |

| INDEX                       |          |                                         |     |

|-----------------------------|----------|-----------------------------------------|-----|

| AGP 2X                      | 1-5      | RAMDAC                                  | 1-7 |

| AGP/PCI Interface           | 1-5      | RAMDAC Characteristics                  | 3-1 |

| address regions             | 2-3      | Region Zero Address Map                 | 2-2 |

| Changes from P3/P4          | 1-3      | SGRAM                                   |     |

| Display Data Channels (DDC) | 3-1      | block fill                              |     |

| Display Resolutions         | 3-1      | bit-masking                             | 1-6 |

| Display Timing Values       | 3-2      | SVGA                                    | 1-6 |

| DMA1DMA3                    | 1-8      | Table 1-2 VESA VBE Graphics Modes       | 1-7 |

| Enhancement summary         | 1-1, 1-3 | Table 3- 1 Timing                       | 3-2 |

| Flash ROM                   | 1-8      | Timing Values for 800x600 32 BPP        | 3-2 |

| input FIFO                  | 1-5      | Unified 2D/3D/Video Integrated Graphics |     |

| Introduction                | 1-1      | Processor                               | 1-6 |

| Memory Interface            | 1-6      | VESA bankswitching                      | 1-7 |

| ModeX                       | 1-7      | VESA VBE Text Modes                     | 1-7 |

| PCI Address Regions         | 2-3      | Video Overlay                           | 1-8 |

| PCI Configuration Region    | 2-1      | Video Unit and RAMDAC                   | 3-1 |

| PCI Local Bus standard      | 1-5      |                                         |     |