# GLINT R4®

Programmer's Guide - Volume II

## **DRAFT ONLY**

## PROPRIETARY AND CONFIDENTIAL INFORMATION

# 3Dlabs®

# GLINT R4®

Programmer's Guide - Volume II

## PROPRIETARY AND CONFIDENTIAL INFORMATION

**Issue 3**

i

## **Proprietary Notice**

The material in this document is the intellectual property of **3D** labs. It is provided solely for information. You may not reproduce this document in whole or in part by any means. While every care has been taken in the preparation of this document, 3Dlabs accepts no liability for any consequences of its use. Our products are under continual improvement and we reserve the right to change their specification without notice. **3D** labs may not produce printed versions of each issue of this document. The latest version will be available from the **3D**labs web site.

- **3D** labs products and technology are protected by a number of worldwide patents. Unlicensed use of any information contained herein may infringe one or more of these patents and may violate the appropriate patent laws and conventions.

- **3D***labs* is the worldwide trading name of **3D***labs* Inc. Ltd.

- **3D***labs*, GLINT R4 and GLINT R4 are registered trademarks of **3D***labs* Inc. Ltd.

Microsoft, Windows and Direct3D are either registered trademarks or trademarks of Microsoft Corp. in the United States and/or other countries. OpenGL is a registered trademark of Silicon Graphics, Inc. All other trademarks are acknowledged and recognized.

© Copyright **3D** *labs* Inc. Ltd. 1999. All rights reserved worldwide.

Email: info@3dlabs.com Web: http://www.3dlabs.com

3Dlabs Ltd.

**3D**labs K.K

Meadlake Place Thorpe Lea Road, Egham

Shiroyama JT Mori Bldg 16F 40301 Toranomon Minato-ku, Tokyo, 105, Japan

Surrey, TW20 8HE United Kingdom

Tel: +81-3-5403-4653

Fax: +91-3-5403-4646

Tel: +44 (0) 1784 470555

Fax: +44 (0) 1784 470699

3Dlabs Inc.

480 Potrero Avenue Sunnyvale, CA 94086, United States

Tel: (408) 530-4700 Fax: (408) 530-4701

## **Change History**

| Document | Issue | Date            | Change                                                         |

|----------|-------|-----------------|----------------------------------------------------------------|

| 160.4.2  | 1     | 1 Dec 99        | First DRAFT Issue.                                             |

| 160.4.2  | 2     | 25 January 2000 | Extensive updates                                              |

| 160.4.2  | 3     | 18 June 2001    | Clarified OpaqueSpan bit; fixed Initialization example values  |

|          |       |                 | for stencil position and width, GID; removed index entries and |

|          |       |                 | traces of FBReadMode, deleted Windowbase references,           |

|          |       |                 | corrected GID test control (no longer in Windows reg),         |

|          |       |                 | Stencil source data field.                                     |

## **Contents**

| Propr  | rietary Notice                               | i    |

|--------|----------------------------------------------|------|

| Chan   | ge History                                   | ü    |

| Conte  | ents iii                                     |      |

| GRAPHI | CS PROGRAMMING                               | 7-1  |

| 7.1    | The Graphics Pipeline                        | 7-1  |

| 7.1.1  | Router                                       | 7-3  |

| 7.1.2  | Initialization                               | 7-3  |

| 7.1.3  | Dominant and Subordinate Sides of a Triangle | 7-3  |

| 7.1.4  | Register Set Up for Depth Testing            | 7-4  |

| 7.1.5  | Subpixel Correction                          | 7-4  |

| 7.2    | Pipeline Overviews                           | 7-5  |

| 7.2.1  | A day in the life of a 3D triangle           | 7-5  |

| 7.2.2  | A day in the life of a 2D primitive          |      |

| RASTER | RIZER AND 2D SETUP                           | 8-1  |

| 8.1    | Description                                  | 8-1  |

| 8.1.1  | Trapezoids                                   | 8-2  |

| 8.2    | Antialiasing                                 | 8-4  |

| 8.2.1  | Antialias Application                        | 8-4  |

| 8.2.2  | Polygon Antialiasing Considerations          | 8-5  |

| 8.2.3  | Registers                                    | 8-6  |

| 8.2.4  | Antialias Example                            | 8-6  |

| 8.2.5  | Antialiasing Primitive Types                 | 8-6  |

| 8.2.6  | Points                                       | 8-9  |

| 8.2.7  | Lines                                        | 8-12 |

| 8.2.8  | Polygons                                     | 8-15 |

| 8.3    | Span Operations                              | 8-18 |

| 8.3.1  | Mode changes in Span Operations              | 8-19 |

| 8.3.2  | Alpha Filtering                              | 8-20 |

| 8.3.3  | Span Mask Processing                         | 8-20 |

| 8.3.4  | Block Write                                  | 8-21 |

| 8.3.5  | Pixel Sizes                                  | 8-21 |

| 8.3.6  | Bitmaps, Spans and Images                    | 8-22 |

| 8.4    | Rasterizer Mode                              | 8-32 |

| 8.4.2   | Multi-rasterizer Operation           | 8-33  |

|---------|--------------------------------------|-------|

| 8.4.3   | Rasterizer Unit Registers            | 8-33  |

| 8.4.4   | Render Command                       | 8-36  |

| 8.5     | 2D Setup                             | 8-42  |

| 8.5.1   | Glyph rendering                      | 8-42  |

| SCISSOF | R, STIPPLE AND COLOR DDA UNITS       | 9-1   |

| 9.1     | Scissor Unit                         | 9-1   |

| 9.1.1   | User Scissor Test                    | 9-1   |

| 9.1.2   | Screen Scissor Tests                 | 9-1   |

| 9.1.3   | Scissor Registers                    | 9-2   |

| 9.1.4   | Span Operations and the Scissor Unit | 9-3   |

| 9.1.5   | Scissor Example                      | 9-3   |

| 9.2     | Stipple Unit                         | 9-3   |

| 9.2.1   | Area Stippling                       | 9-4   |

| 9.2.2   | Line Stippling                       | 9-5   |

| 9.2.3   | Span Operations and Stippling        | 9-5   |

| 9.2.4   | Registers                            | 9-5   |

| 9.2.5   | Examples                             | 9-7   |

| 9.2.6   | Line Stipple Example                 | 9-8   |

| 9.2.7   | Area Stipple Pattern Example         | 9-8   |

| 9.3     | Color DDA Unit                       | 9-9   |

| 9.3.1   | RGBA and Color-Index(CI) Modes       | 9-10  |

| 9.3.2   | Gouraud Shading                      | 9-11  |

| 9.3.3   | Flat Shading Example                 | 9-12  |

| 9.3.4   | Gouraud Shaded Trapezoid Example     | 9-12  |

| 9.3.5   | Gouraud Shaded Line Example          | 9-13  |

| LO      | CALBUFFER READ/WRITE                 | 10-1  |

| 10.1.1  | Mode Registers                       | 10-2  |

| 10.2    | Window register                      | 10-4  |

| 10.3    | Pixel Ownership (GID) Test Unit      | 10-4  |

| 10.3.1  | Pixel Ownership Test                 |       |

| 10.4    | Stencil Test                         | 10-7  |

| 10.4.1  | Registers                            |       |

| 10.4.2  | Stencil Example                      | 10-10 |

| 10.5    | Denth Test                           | 10-11 |

| 10.5.1 | Registers                           | 10-13 |

|--------|-------------------------------------|-------|

| 10.5.2 | Depth Example                       | 10-15 |

| TEX    | (TURE MAPPING                       | 11-1  |

| 11.1.1 | Compatibility with Earlier Chipsets | 11-1  |

| 11.2   | Texture Co-ordinate Generation      | 11-2  |

| 11.2.1 | Calculate texture coordinates       | 11-2  |

| 11.2.2 | Level of Detail calculation         | 11-3  |

| 11.2.3 | Texture Read                        | 11-6  |

| 11.2.4 | Filter Modes                        |       |

| 11.2.5 | Texel Formatting                    | 11-12 |

| 11.2.6 | Lookup Table (LUT)                  | 11-16 |

| 11.2.7 | Texture Filtering and Alpha Mapping | 11-17 |

| 11.2.8 | Texture Color Compositing           | 11-18 |

| 11.2.9 | Implementation                      | 11-29 |

| VOL    | LUME II INDEX                       | 33    |

7

## **Graphics Programming**

GLINT R4 provides a rich variety of operations for 2D and 3D graphics supported by its pipeline architecture. Primarily intended as a rasterizer, the R4 also has an onboard Delta setup unit for standalone operation.

In this chapter, section §7.1 shows the basic units in the Pipeline. The following chapters describe a typical rendering process for a Gouraud shaded triangle and looks at each of the units in detail.

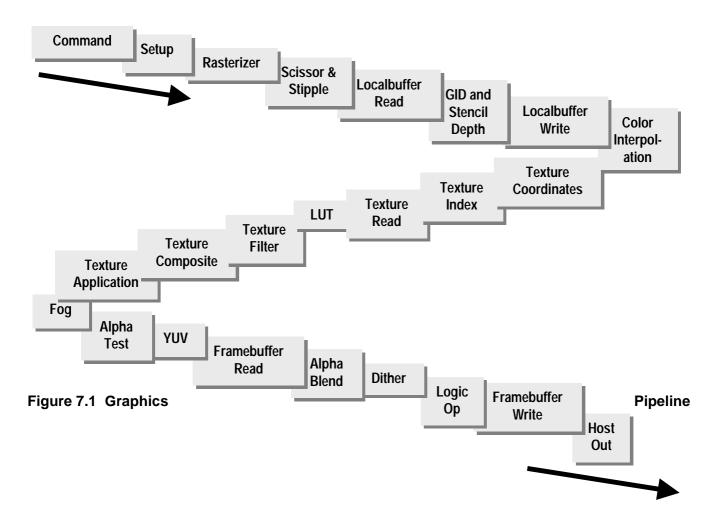

## 7.1 The Graphics Pipeline

Figure 7.1 shows a schematic of the pipeline. In this diagram, the localbuffer contains the pixel ownership values (known as Graphic IDs), the Depth (Z) and Stencil buffer. The framebuffer contains the Red, Green, Blue and Alpha bitplanes. The units in the HyperPipeline are:

- Rasterizer scan converts the given primitive into a series of fragments for processing by the rest of the pipeline.

- Scissor Test clips out fragments that lie outside the bounds of a user defined scissor rectangle and also performs screen clipping to stop illegal accesses outside the screen memory.

- Stipple Test masks out certain fragments according to a specified pattern. Line and area stipples are available.

- GID (Pixel Ownership) is concerned with ensuring that the location in the framebuffer for

the current fragment is owned by the current visual. Comparison occurs between the given

fragment and the Graphic ID value in the localbuffer, at the corresponding location, to

determine whether the fragment should be discarded.

- Stencil Test conditionally discards a fragment based on the outcome of a test between the

given fragment and the value in the stencil buffer at the corresponding location. The

stencil buffer is updated dependent on the result of the stencil test and the depth test.

- Depth Test conditionally discards a fragment based on the outcome of a test between the depth value for the given fragment and the value in the depth buffer at the corresponding location. The result of the depth test can be used to control the updating of the stencil buffer.

- Color DDA is responsible for generating the color information (RGBA or Color Index(CI))

associated with a fragment.

- Texture is concerned with mapping a portion of a specified image (texture) onto a fragment. The process involves interpolating to determine the texel coordinates including perspective division, reading the texels, filtering to calculate the texture color, and application which applies the texture color to the fragment color.

- Fog blends a fog color with a fragment's color according to a given fog factor. Fogging is used for depth cueing images and to simulate atmospheric fogging.

- Antialias Application combines the incoming fragment's alpha value with its coverage value when antialiasing is enabled.

- Alpha Test conditionally discards a fragment based on the outcome of a comparison between the fragments alpha value and a reference alpha value.

- Alpha Blending combines the incoming fragment's color with the color in the framebuffer at the corresponding location.

- Color Formatting converts the fragment's color into the format in which the color information is stored in the framebuffer. This may optionally involve dithering.

- Logical Op/Framebuffer Mask performs Logical Operations between the fragment and destination, and optionally applies a writemask.

- Host Out optionally gathers statistics for picking and extent checking, and returns data to the host for image uploads.

.

<sup>&</sup>lt;sup>1</sup> That is, provides the access functionality to the areas of memory used for LB storage.

The Pipeline structure of GLINT R4 is very efficient at processing fragments. For example, texture mapping calculations are not actually performed on fragments that are clipped off by scissor testing. This approach saves substantial computational effort.

To obtain the best results when programming for pipelined processing, however, you need to be aware of what all the pipeline stages are doing at any time. For example, many operations require both a read and/or write to the localbuffer and framebuffer. Because these are at different points in the pipeline the programmer must enable and control data read/write from/to the framebuffer – simply setting a logical operation to XOR and enabling logical operations will not have the desired effect.

The R4 introduces additional optimization to help the programmer manage memory accesses. The **ReadMonitor** unit allows Local and Framebuffer writes without waiting for earlier memory operations to complete where different polygons are affected. The result is a significant reduction in rendering latency, particularly for small polygons.

#### **7.1.1** Router

As discussed in Volume I, the register address space can be seen conceptually as either a message passing system or a flat address map. This allows some significant adaptive performance enhancements. One important performance feature of the pipeline is the Router. This is essentially a switch which allows the order of some of the units to be swapped, by setting or clearing the *Sequence* bit of the **RouterMode** register.

Textured primitives are typically more processor-intensive than non-textured primitives. When the *Sequence* bit is set, fragments are tested against the GID (Pixel Ownership), Stencil and Depth(Z) before the texture value is calculated. If the fragment fails any of these tests nothing is drawn so texture value calculations can be skipped - leading to higher performance.

OpenGL defines the order of operations on a fragment as texture, alpha test, stencil then depth(Z), which is the sequence used when the <code>Sequence</code> bit in the Router register is cleared. However, if the alpha test is disabled (or cannot reject fragments) then OpenGL compatible semantics are maintained even if the operation order is changed to the more efficient stencil, depth(Z), texture, and alpha test.

The order can be dynamically reconfigured at any time without any need to synchronize simply by writing to the Order bit.

#### 7.1.2 Initialization

GLINT R4 requires many of its registers to be initialized in a particular way regardless of what is to be drawn. For instance, the screen size and appropriate clipping must be set up. Normally this only needs to be done once and for clarity this example assumes that all initialization has already been done. More details may be found later in this volume.

Other states (e.g. enabling Gouraud shading and depth buffering) change occasionally though rarely on a per primitive basis.

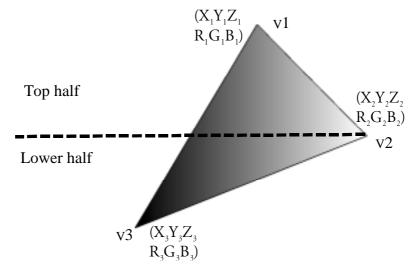

#### 7.1.3 Dominant and Subordinate Sides of a Triangle

The dominant side of a triangle is that with the greatest range of Y values. The choice of dominant side is optional when the triangle is either flat bottomed or flat topped.

GLINT R4 always draws triangles from the dominant edge towards the subordinate edges. This simplifies the calculation of set up parameters as will be seen below.

Figure 7.2 Dominant and Subordinate Sides of a Triangle

## 7.1.4 Register Set Up for Depth Testing

Internally GLINT R4 uses fixed point arithmetic. The formats for each register are described in the *Reference Guide*. Each depth value must be converted into a 2's complement 16.32 bit fixed point number and then loaded into the appropriate pair of 32 bit registers (**DZdxL**, **DZdxU, DZdyDomL, DZdyDomU**). The 'Upper' or 'U' registers store the integer portion, whilst the 'Lower' or 'L' registers store the 16 bit LSB, left justified and zero filled.

For the example triangle, R4 would need its registers set up as follows:

```

// Load the depth start and delta values

// to draw a triangle

ZstartU (Z1_MS)

ZstartL (Z1_LS)

dZdyDomU (dZdy13_MS)

dZdyDomL (dZdy13_LS)

dZdxU (dZdx_MS)

dZdxL (dZdx_LS)

```

#### 7.1.4.1 RasterizerMode

The R4 rasterizer has a number of mode bits which take effect until cleared and therefore tend to affect many primitives. These primarily involve bit mask operations described below. For details refer to the *Reference Guide*, **RasterizerMode** register. In the case of the Gouraud shaded triangle the default value for these modes is suitable.

#### 7.1.5 Subpixel Correction

GLINT R4 supports subpixel correction of interpolated values when rendering aliased trapezoids (smooth shaded, textured, fogged or depth buffered). Subpixel correction ensures that all interpolated parameters associated with a fragment (color, depth, fog, texture) are correctly sampled at the fragment's center. This correction is required to ensure consistent shading of objects made from many primitives.

Subpixel correction is not applied to antialiased primitives<sup>2</sup>.

\_

<sup>&</sup>lt;sup>2</sup> This applies only to antialiased primitives generated via the *Gamma* front end accelerator.

Control of subpixel correction is in the **Render** command register described below, and can be selected in bit settings for individual primitives (**DrawLine**, **DrawTriangle**. A full code example is given in the Appendices.

#### 7.2 Pipeline Overviews

Before we review each unit in detail it is worth looking in general terms at how a graphic primitive passes through the pipeline, what messages are generated and what happens in each unit. Some simplifications have been made in the description to avoid detail which would otherwise complicate what is in fact a very simple process.

The descriptions concentrate on what happens as a fragment flows down the message stream. It is important to remember that at any instant in time there are many fragments flowing down the message stream and the further they get the more processing has occurred.

## 7.2.1 A day in the life of a 3D triangle

This section previews the render process for a typical 3D graphics primitive, the Gouraud shaded, depth buffered, dithered triangle.

For this example assume that the triangle is to be drawn into a window which has its colormap set for RGB as opposed to color index operation. This means that all three color components; red, green and blue, must be handled. Also, assume the coordinate origin is bottom left of the window and drawing will be from top to bottom. GLINT R4 can draw from top to bottom or bottom to top.

For clarity the equations are shown in full in the appendices, though in practice there are many common terms and factors which need only be computed once and normally the OGL driver performs all the necessary interpolations.

Consider a triangle with vertices, v1, v2 and v3 where each vertex comprises X, Y and Z coordinates, shown below. Each vertex has a different color made up of red, green and blue (R, G and B) components. The alpha component is omitted for this example.

Figure 7.3 Example Triangle

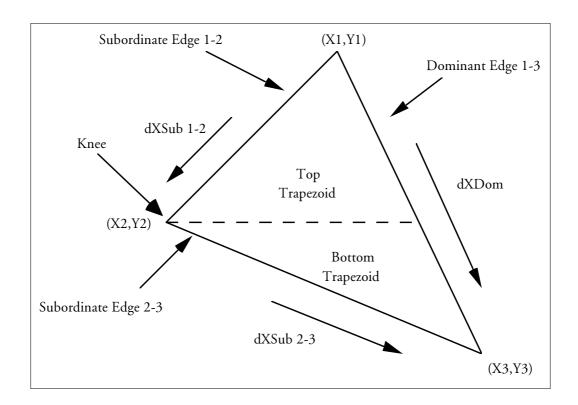

The diagram makes a distinction between top and bottom halves because GLINT R4 is designed to rasterize (a) screen aligned trapezoids, and (b) flat-topped or -bottomed triangles; as shown below:

Figure 7.4 Screen aligned trapezoid and flat topped triangle

#### 7.2.1.1 **Delta Unit**

The drawing process starts by generating and loading vertex data in the Delta Unit:

- 1. The application generates the triangle vertex information and makes the necessary OpenGL calls to draw it.

- The OpenGL server/library gets the vertex information, transforms, clips and lights it. The

vertex coordinates and color values are written into the vertex stores (in the Delta Unit)

and the **DrawTriangle** command is issued.

- 3. The Delta Unit calculates the initial values and derivatives for the values to interpolate (X<sub>left</sub>, X<sub>right</sub>, red, green, blue and depth) for unit change in dx and dxdy<sub>left</sub>. All these values are in fixed point integer and have unique message tags. Some of the values (the depth derivatives) have more than 32 bits to cope with the dynamic range and resolution so are sent in two halves Finally, once the derivatives, start and end values have been sent the 'render triangle' message begins the rendering process.

- 4. The derivative, start and end parameter messages are received and filter down the message stream to the appropriate units. The depth parameters and derivatives to the Depth Unit; the RGB parameters and derivative to the Color DDA Unit; the edge values and derivatives to the Rasteriser Unit.

#### 7.2.1.2 Rasterizer

The 'render triangle' message is received by the rasteriser unit and all subsequent messages (from the host) are blocked until the triangle has been rasterised (but not necessarily written to the framebuffer). A 'prepare to render' command is passed on so any other units can prepare themselves.

The Rasteriser Unit walks the left and right edges of the triangle and fills in the spans between. As the walk progresses messages are send to indicate the direction of the next step: StepX or StepYDomEdge.

#### 7.2.1.3 Rasterizer 'Edge walking' - Calculating the Slope for each Side

GLINT R4 draws filled shapes such as triangles as a series of spans with one span per scanline. Therefore it needs to know the start and end X coordinate of each span. These are determined by 'edge walking'. This process involves adding one delta value to the previous

span's start X coordinate and another delta value to the previous span's end x coordinate to determine the X coordinates of the new span. These delta values are in effect the slopes of the triangle sides. To draw from left to right and top to bottom, the slopes of the three sides are calculated as:

$$dX_{23} = \frac{X_3 - X_2}{Y_3 - Y_2}$$

$$dX_{13} = \frac{X_3 - X_1}{Y_3 - Y_1}$$

$$dX_{12} = \frac{X_2 - X_1}{Y_2 - Y_1}$$

This triangle will be drawn in two parts, top down to the 'knee' i.e. vertex 2 and then from there to the bottom. The dominant side is the left side so for the top half:

The start X,Y, the number of scanlines, and the deltas (above) give GLINT R4 enough information to edge walk the top half of the triangle. However, to indicate that this is not a flat topped triangle (GLINT R4 is designed to rasterize screen aligned trapezoids and flat topped triangles), the same start position in terms of X must be given twice as StartXDom and StartXSub.

To edge walk the lower half of the triangle, selected additional information is required. The slope of the dominant edge remains unchanged, but the subordinate edge slope needs to be set to:

Also the number of scanlines to be covered from Y2 to Y3 needs to be given. Finally to avoid any rounding errors accumulated in edge walking to X2 (which can lead to pixel errors), StartXSub must be set to X2.

The data field holds the current (x, y) coordinate. One message is sent per pixel within the triangle boundary. These messages, or fragments, are divided into two groups, active and passive. Fragments always start off in the active group but may be changed to the passive group if the pixel fails one of the tests (e.g. depth) on its path down the message stream. The two groups are distinguished by a single bit in the message tag.

The fragments (in either form) are always passed throughout the length of the message stream and are used by all the DDA units to keep their interpolation values in step. Any other messages pertaining to fragments always precede the fragment in the message stream.

The messages hold X, Y, color and coverage data for each fragment <sup>3</sup>. The data field expands between units to accommodate additional data when necessary.

<sup>&</sup>lt;sup>3</sup>The coverage field is only used for antialiasing. For aliased primitives the coverage field holds a dErr value used for subpixel correction.

#### 7.2.1.4 Rasterizing the Triangle

We are almost ready to draw the triangle. Setting up the registers as described here and sending the **Render** command draws the top half of the example triangle first.

To draw the example triangle, all the bit fields within the **Render** command should be set to 0 except the PrimitiveType which should be set to trapezoid and the *SubPixelCorrection Enable* bit which should be set to TRUE.

```

\label{eq:continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous

```

After the **Render** command has been issued the registers in R4 can immediately be altered to draw the lower half of the triangle. Only two registers need be loaded and the **ContinueNewSub** command sent. Once R4 has received **ContinueNewSub** it starts drawing the sub-triangle.

```

// Set-up the delta and start for the new edge StartXSub (X2<<16)  dXSub \ (((X3-X2)<<16)/(Y3-Y2))  // Draw sub-triangle  ContinueNewSub \ (Y2-Y3) \qquad // \ Draw \ lower \ half

```

#### 7.2.1.5 Scissor and Stipple

This unit does 4 tests on the fragment (as embodied by the active step message). The screen scissor test takes the coordinates associated with the fragment, converts them to be screen

relative (if necessary) and compares them against the screen boundaries. (The other three tests - user scissor, line stipple and area stipple - are disabled in this example.) If the enabled tests pass then the active fragment is forwarded to the next unit, otherwise it is changed into a passive step and then forwarded.

#### 7.2.1.6 Router

In this example the Router is set up so the Depth test occurs before the texture operations (i.e. **RouterMode** Sequence bit = 1).

#### 7.2.1.7 Local Buffer Read

In general terms the Local Buffer Read Unit reads the Graphic ID, Stencil and Depth information from the Local Buffer and passes it to the next unit. This includes performing the GID test on fragments, checking cache and local buffer for data, and data formatting. See volume I - Localbuffer - for more information

#### 7.2.1.8 Stencil and Depth

When an active fragment is received the internal stencil and depth values are compared with the fragment's as specified in the **StencilMode** and **DepthMode** registers. If the enabled tests pass then the new local buffer data is written back to the fragment, which is forwarded to the next unit.

If any of the enabled tests fail then equivalent passive step message is forwarded instead (a local buffer write may still be done). The Depth DDA is stepped to update the local depth value.

#### 7.2.1.9 Local Buffer Write

The Local Buffer Write Unit calculates the address, formats the GID, Stencil and Depth data and (if writes are enabled) passes the formatted data and address to the Memory Controller.

The memory is much wider than the pixel data so any writes are first done into a write combine buffer which is flushed to memory as required. See volume I - Localbuffer - for more information.

The fragment is forwarded to the next unit.

#### 7.2.1.10 Color DDA

The Color DDA unit responds to an active fragment by updating the fragment's color field and sending this to the next unit. The color field holds the *current* RGBA value from the DDA. After the step message is sent the DDA is incremented in the correct direction, ready for the next pixel.

#### 7.2.1.11 Texturing, Fog and Alpha Tests

In this example, Texturing, Fog and Alpha Tests are disabled so the fragments are forwarded unchanged.

#### 7.2.1.12 Framebuffer Read

In general terms Framebuffer Read reads the color information from the framebuffer and passes it onto the next unit. It is functionally similar to the Localbuffer but handles color data

rather than GID, depth and stencil data, write-combined operations and Patch2 and Patch32\_2 formats. See volume I - Framebuffer - for more information.

#### 7.2.1.13 Alpha Blend

The formatting of the Framebuffer data is deferred until the Alpha Blend Unit as it is the only unit which needs to match buffer formats with the internal formats.

In this example no alpha blending or logical ops are taking place so reads are disabled and fragments pass through unaltered.

#### 7.2.1.14 Dither

The Dither Unit uses the least significant bits of the (X, Y) coordinate information from the step message to dither the color field. Part of the dithering process is to convert from the internal color format into the format of the framebuffer. The new color is inserted back into the color field and the fragment forwarded.

#### 7.2.1.15 Logical Ops

In this example Logical Ops are disabled so the fragments pass through.

#### 7.2.1.16 Framebuffer Write

The Framebuffer Write Unit calculates the address and (if writes are enabled) passes the formatted data and address to the Memory Controller.

The memory is much wider than the pixel data so any writes are first done into a write combine buffer and only when this needs to be flushed is the Memory Controller given the write command - see volume I - Framebuffer - for more information.

#### 7.2.1.17 Host Out

The Host Out Unit deals with host synchronisation and statistics. In this example it simply consumes any fragments which reach this point in the message stream.

#### 7.2.2 A day in the life of a 2D primitive

GLINT R4 introduces an alternative method for rendering which is particularly suited to 2D operations. These are pure 2D without any 3D functionality such as depth or stencil testing or alpha blending.

2D drawing works on spans of pixels, where a span is always 64 pixels sequentially along a scanline. The core now works on 64 pixels in parallel (in addition to processing multiple spans along the length of the message stream) and a pixel can be 8, 16 or 32 bits in size. Spans can be read, written, copied, uploaded or downloaded. A span can have a constant color or a variable color per pixel in the span.

The primitive we are going to look at is a fill with a constant color through a bit mask held in the texture memory. The zero bits in the bit mask do not cause the corresponding pixels in the framebuffer to be written to. The fill shape is a rectangle for simplicity, but could be any shape (with suitable decomposition into primitives GLINT R4 understands). As usual, we refer to "units" along the message stream but these are more accurately considered as functional groupings than physical entities.

#### 7.2.2.1 Initialization

The application generates the rectangle information and makes the necessary Windows API calls to draw it.

#### 7.2.2.2 2D Set Up Unit

The NT device driver gets the rectangle information and uses the **Render2D** command to set up and rasterise the rectangle. Other state data and information is also set up, as discussed below.

#### 7.2.2.3 Rasterizer

The 'render trapezoid' message is received by the rasteriser unit and all subsequent messages (from the host) are blocked until the trapezoid has been rasterised (but not necessarily written to the framebuffer). The **Render** message has the *FastFillEnable* bit set. A 'prepare to render' message is also passed on internally so any other units can prepare themselves.

The Rasteriser Unit walks the left and right edges of the trapezoid (a rectangle in this case) and fills in the spans between the left and right hand edges. As the walk progresses messages are sent to indicate the direction of the next step. These internal SpanStep commands control the subsequent processing of the span fragment.

#### 7.2.2.4 Scissor and Stipple Unit

Scissor and Stipple Unit. This unit does 3 tests on the span (as embodied by the SpanStep message). The screen scissor test takes the coordinates associated with the SpanStep message, converts them to be screen relative (if necessary) and compares the pixel mask against the screen boundaries and clears the bits for pixels which lie outside the screen boundary. The pixel mask is potentially further reduced using the scissor tests (applied in a similar way). The area stipple test is disabled for this example but, if it was enabled would potentially remove further pixels after suitable alignment. The modified SpanStep message is forwarded to the next unit.

#### 7.2.2.5 Color DDA

The Color DDA unit does not respond to the SpanStep messages so they just pass through.

#### 7.2.2.6 Texture Coordinate and Index

The Texturing Coordinate Unit responds to the SpanStep message and appends the u, v coordinates of the texel where the bit mask data for this span is held. The S and T DDAs are set up to step through the bit mask pattern. The SpanStep is forwarded on to the next unit.

The Texture Index Unit converts the uv coordinate in the SpanStep message into an ij coordinate of the texel where the bit mask data for this span is held. The SpanStep is forwarded on to the next unit.

#### 7.2.2.7 Texturing, Fog and Alpha

The Texture Read Unit converts the ij coordinate into a physical address where the texel data is held. The texel data is read (maybe sourced from the secondary cache) and zero extended up to 64 bits if the bit mask was held as 8, 16, or 32 bits. After being optionally inverted or mirrored it is ANDed with the pixel mask field in the SpanStep message and forwarded to the next unit.

The remaining texture units, Fog and Alpha Tests Units do not respond to the SpanStep messages so they just pass through.

#### 7.2.2.8 Localbuffer Read, Stencil/Depth and Localbuffer Write

The LB Read, Stencil/Depth, LB Write Units do not respond to the SpanStep messages (in this example) so they just pass through.

#### 7.2.2.9 Framebuffer Read

In general terms the Framebuffer Read Unit reads the color information from the framebuffer and forwards it to the next unit. More specifically for spans it calculates the linear address in the framebuffer of the required data. This is done using the (X, Y) position recorded internally and locally stored information on the 'screen width' and window base address. The span is decomposed into a series of memory aligned reads.

In this example no logical ops are taking place so reads are disabled and hence no read address is sent to the Memory Controller. The span tags just pass through.

#### 7.2.2.10 Alpha Blend and Dither

The Alpha Blend and Dither Units do not respond and the span data simply passes through.

#### 7.2.2.11 Logical Ops

The Logical Ops are disabled so the Span data passes through.

#### 7.2.2.12 Framebuffer Write

The Framebuffer Write Unit calculates the address, aligns the pixel mask to the memory block write boundaries and passes these to the Memory Controller. The pixel data previously set up in the **FBColor** Register can be written, ideally using the block fill capability of the SGRAM. The Span data is passed on to the next unit.

#### 7.2.2.13 Host Out

7-12

The Host Out Unit is concerned with synchronisation with the host - for this example it simply consumes any messages which reach this point in the message stream.

8

## **Rasterizer and 2D Setup**

The rasterizer decomposes a primitive into a series of fragments for processing by the rest of the HyperPipeline.

GLINT R4 can directly rasterize:

- aliased screen aligned trapezoids

- aliased single pixel wide lines

- · aliased single pixel points

- antialiased screen aligned trapezoids

- antialiased circular points

All other primitives are treated as one or more of the above, for example an antialiased line is drawn as a series of antialiased trapezoids.

2D Operations can be largely implemented using the **Render2D** and **Render2Dglyph** registers. These, together with the **GlyphData** and **GlyphPosition** registers constitute a functional subunit of the Rasterizer and are discussed below.

## 8.1 Description

The rasterizer unit scan converts the given primitive into a list of pixel coordinates which meet the rasterisation rules of OpenGL, X and NT. In addition to generating the coordinates, the order in which pixels are visited is also defined (by the **Render** command) so the local DDA units in the Texture, Color, Fog and Depth units can incrementally keep in step.

When a primitive is antialiased the percentage coverage of the primitive within the scan converted pixels is calculated for later use in the alpha blend unit. The same method of antialiasing is used for all primitives<sup>4</sup>.

The primitive is scan converted to a higher resolution (e.g. 4x4 sub samples per Render command) and the number of sub pixel sample points covered is counted. The ratio of covered sample points to total number of sample points gives the coverage weighting by which to adjust the color.

The rasterisation process steps through along the Y axis and calculates the two intersection points for this scanline. For normal rasterisation the pixels between these two intersection points are filled in. During antialiasing a step of Y/4 (for example) is used and within each scan line four pairs of intersections are calculated per scanline. The coverage for each of the four sub pixel scanline makes in a pixel (on this scanline) are calculated and summed.

The coordinates passed to the rasterizer can be window relative or screen relative. The rasterizer treats both the same. Conversion to memory addresses does not happen until they reach the Local Buffer and Framebuffer Units.

\_

<sup>&</sup>lt;sup>4</sup> Applies to *Gamma* interface only.

8-2

The Rasterizer is not concerned whether the origin is the bottom left or top left and again it is the Local Buffer and Framebuffer Units which take this into account when calculating the memory address. Obviously if the direction of scan conversion is important then the parameters must match up with the origin definition to give the desired effect.

Note:

Long term mode information is held in the **RasterizerMode** command and short term mode information (which only applies to the primitive being rasterised) is passed with the **Render** command.

#### 8.1.1 Trapezoids

GLINT R4's basic area primitive is the screen aligned trapezoid, discussed in the previous chapter. This is characterized by having top and bottom edges parallel to the X axis. The side edges may be vertical (a rectangle), but are usually diagonal. The top or bottom edges can degenerate into points in which case we are left with either flat topped or flat bottomed triangles.

Any polygon can be decomposed into screen aligned trapezoids or triangles. Usually, polygons are decomposed into triangles because the interpolation of values over non-triangular polygons is ill defined. The rasterizer does handle flat topped and flat bottomed 'bow tie' polygons which are a special case of screen aligned trapezoids.

X's definition of a polygon is more complex than OpenGL's. It can be concave and self intersecting. In the non convex case the best thing is for X to do is to decompose the polygon into a series of spans and render them as 1 pixel high rectangles. For any convex polygons X can decompose them into screen aligned trapezoids as a further optimisation over just using spans. X does not support antialiased polygons.

#### 8.1.1.1 Edge Matching for Meshes, Fans etc.

Adjacent triangles or polygons which share an edge or vertex must be drawn so that pixels which make up the edge or vertex are drawn once only. This may be achieved by omitting the pixels down the left or the right sides and the pixels along the top or lower sides. GLINT R4 follows the convention of omitting the pixels down the right hand edge. Control of whether pixels along the top or lower sides are omitted depends on the start Y value and the number of scanlines to be covered. With the example, if StartY = Y1 and the number of scanlines is set to Y1toY2, the lower edge of the top half of the triangle will be excluded. This excluded edge is drawn as the top of the lower half of the triangle.

To minimize delta calculations, triangles may be scan converted from left to right or from right to left. The direction depends on the dominant edge, that is *the edge which has the maximum range of Y values*. Rendering always proceeds from the dominant edge towards the relevant subordinate edge. In the example above, the edge with the greatest Y range (dominant) is on the right so rendering will be from right to left.

Figure 8.1 Rasterizing a triangle

The sequence of actions required to render a triangle (with a 'knee') are:

- Load the edge parameters and derivatives for the dominant edge and the first subordinate edges in the first triangle.

- Send the **Render** command. This starts the scan conversion of the first triangle, working from the dominant edge. This means that for triangles where the knee is on the left we are scanning right to left, and vice versa for triangles where the knee is on the right.

- Load the edge parameters and derivatives for the remaining subordinate edge in the second triangle.

- Send the **ContinueNewSub** command. This starts the scan conversion of the second triangle.

| Render Data Field |   |                     |   |                          |   |  |

|-------------------|---|---------------------|---|--------------------------|---|--|

| AreaStippleEnable | 1 | LineStippleEnable   | 0 | PrimitiveType            | 1 |  |

| FastFillEnable    | 0 | FastFillIncrement   | Х | UsePointTable            | 0 |  |

| AntialiaseEnable  | 0 | AntialiasingQuality | Х | ResetLineStipple         | Χ |  |

| SyncOnBitMask     | 0 | SyncOnHostData      | 0 | TextureEnable            | 1 |  |

| FogEnable         | 1 | CoverageEnable      | 0 | SubPixelCorrectionEnable | 1 |  |

$$\begin{aligned} & \text{StartXDom} \ (X_1) \\ & \text{dXDom} \ ((X_3\text{-}\ X_1)/(Y_3\text{-}\ Y_1)) \end{aligned}$$

$\begin{array}{l} \operatorname{StartXSub}\left(X_{1}\right) \\ \operatorname{dXSub}\left((X_{2}\text{-}\ X_{1})/(Y_{2}\text{-}\ Y_{1})\right) \\ \operatorname{StartY}\left(Y_{1}\right) \\ \operatorname{dY}\left(\text{-}1.0\right) \\ \operatorname{Count}\left(Y_{1}\text{-}\ Y_{2}\right) \\ \operatorname{Render} \\ \operatorname{StartXSub}\left(X_{2}\right) \\ \operatorname{dXSub}\left((X_{3}\text{-}\ X_{2})/(Y_{3}\text{-}\ Y_{2})\right) \end{array}$

ContinueNewSub (Y2 - Y3) // Bottom half

Note:

If both edges need to be reloaded to continue on with the bottom half of the polygon then issue ContinueNewSub (0) and then ContinueNewDom (count). The ContinueNewSub (0) will just update the DDA with the new start value but not draw any scanlines. Alternatively, if the accuracy of the DDA end values is good enough and can be used as the start values for the next trapezoid then the delta values can be updated and the Continue message used.

The sub pixel correction is only needed if color, depth, fog or texture interpolation is being used.

After the **Render** command has been sent the registers can be updated immediately to draw the second half of the triangle. Only two registers need to be loaded to do this, followed by the **ContinueNewSub** command. When the first triangle has been drawn and the **ContinueNewSub** command issued, GLINT R4 starts drawing the sub-triangle and the **ContinueNewSub** command register is loaded with the remaining number of scanlines to be rendered.

## 8.2 Antialiasing

Antialias application controls the way the coverage value generated by the rasterizer combines with the color generated in the color DDA units. The application depends on the color mode - RGBA or Color Index (CI).

Note:

The following comments apply to rasterization of polygons set up in the front end Gamma chip. R4 does not directly support antialiasing in standalone mode.

### 8.2.1 Antialias Application

When antialiasing is enabled by setting the **AntialiasMode** *Enable* bit and the **Render** register's *CoverageEnable* bit, the fragment's color and alpha is weighted by the percentage area of the pixel covered by the fragment. The coverage weighting is determined by the Rasteriser and varies from 0 to 100% "saturation".

If antialiasing is not enabled the fragment is forwarded for alpha testing.

The mode (RGBA or CI) is set using the *ColorMode* bit in the **AntialiasMode** register. In RGBA mode the color value is multiplied by the coverage value calculated in the rasterizer (its range is 0% to 100%). The RGB values remain unchanged unless the *ScaleColor* bit is also set. Color scaling is not required by OGL and may reduce performance.

In CI mode the coverage value is placed in the lower 4 bits of the color field. The Color Look Up Table is assumed to be set up so that each color has 16 intensities associated with it, one per coverage entry.

#### 8.2.2 Polygon Antialiasing Considerations

A number of issues should be considered when using GLINT R4 to render antialiased polygons. Depth buffering cannot be used with GLINT R4 antialiasing. This is because the order the fragments are combined in is critical in producing the correct final color. Polygons must therefore be depth sorted, and rendered front to back, using the alpha blend modes: SourceAlphaSaturate for the source blend function and One for the destination blend function. In this way the alpha component of a fragment represents the percentage pixel coverage, and the blend function accumulates coverage until the value in the alpha buffer equals one, at which point no further contributions can be made to a pixel.

Although this technique works well in many cases, it is an approximation. Consider the case below which shows three polygons of equal depth which intersect a single pixel. In this case there would ideally be a contribution from each of the polygons. However, if the rendering order is polygon A followed by polygon B, each of which contributes approximately 50% pixel coverage, then polygon C will make no contribution to the pixel as the alpha value is saturated (50%+50%=100%).

Figure 8-2 Polygon Antialiasing

When antialiasing general scenes with no restrictions on rendering order, the accumulation buffer is the preferred choice. This is indirectly supported on GLINT R4 via image uploading and downloading, with the accumulation buffer residing on the host.

When antialiasing, interpolated parameters which are sampled within a fragment (color, fog and texture), sometimes are not representative of a continuous sampling of a surface so care should be taken when rendering smooth shaded antialiased primitives. This problem does not occur in aliased rendering, as the sample point is consistently at the center of a pixel. See *The OpenGL Programming Guide* for more details of antialiasing.

#### 8.2.3 Registers

The **AntialiasMode** register provides the enables described earlier:

| Name             | Type             | Offset  | Format              |

|------------------|------------------|---------|---------------------|

| AntialiasMode    | Alpha Test       | 0x8808  | Bitfield            |

| AntialiasModeAnd | Alpha Test       | 0x ABF0 | Bitfield Logic Mask |

| AntialiasModeOr  | Alpha Test       | 0x ABF8 | Bitfield Logic Mask |

|                  | Control register |         | <u> </u>            |

| Bits | Name        | Read | Write | Reset | Description                                                                                                                                                                                                |

|------|-------------|------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Enable      | V    | V     | X     | When set, scales the fragment's alpha value under control of the remaining bits in this register and the coverage value. When clear, the fragment's alpha value is not changed.  0 = Disable    1 = Enable |

| 1    | Color Mode  | ~    | ~     | X     | This bit defines the fragment's color format:  0 = RGBA                                                                                                                                                    |

| 2    | Scale Color | ~    | ~     | X     | This bit, when set allows the coverage value to scale                                                                                                                                                      |

| 331  | Unused      | 0    | 0     | X     |                                                                                                                                                                                                            |

Notes: For the coverage application to take place the enable in the **AntialiasMode** register must be qualified by the *CoverageEnable* bit in the **Render** command register.

Figure 8-3 Antialias Mode Register

#### 8.2.4 Antialias Example

Enable antialiasing for an RGBA primitive:

```

// Set AA application for RGBA primitive

begin.AntialiasEnable = GLINT_R4_TRUE

antialiasMode.AntialiasEnable = GLINT_R4_TRUE

antialiasMode.ColorMode = GLINT_R4_TRUE

AntialiasMode(antialiasMode)

// Set the blend mode to an appropriate value if

// blending is required. Not shown.

// When issuing a Render command the CoverageEnable

// bit should be set in addition to the antialias

// unit being enabled:

// render.CoverageEnable = GLINT_R4_TRUE

```

## 8.2.5 Antialiasing Primitive Types

R4 uses a subpixel point sampling algorithm to antialias primitives. R4 can directly rasterize antialiased trapezoids and points. Other primitives are composed from these base primitives.

The rasterizer associates a coverage value with each fragment produced when antialiasing. This value represents the percentage coverage of the pixel by the fragment. GLINT R4 supports two levels of antialiasing quality:

- normal, which represents 4x4 pixel subsampling

- high, which represents 8x8 pixel subsampling

Selection between these two is made by the *AntialiasingQuality* bit in the **Render**, **PointMode**, **TriangleMode** or **LineMode** registers.

Use the **FlushSpan** command to terminate rendering an antialiased primitive. This is necessary because of the way R4 maintains antialiasing continuity.

When rendering a primitive which does not complete on a scanline boundary, R4 retains antialiasing information about the last sub-scanline(s) it has processed but does not generate fragments for them unless a **FlushSpan** command is received. The commands **ContinueNewSub, ContinueNewDom** or **Continue** can then be used to maintain continuity between adjacent trapezoids, which allows complex antialiased primitives to be built up from simple trapezoids or points.

To illustrate this consider using screen aligned trapezoids to render an antialiased line. The line will in general consist of three screen aligned trapezoids as shown in the diagram below.

Figure 8-4 Antialiased Line

The procedure to render the line is as follows:

```

// Set-up the blend and coverage application units

// as appropriate – not shown

// In this example only the edge deltas are shown

// loaded into registers for clarity. In reality

// start X and Y values are required. This example

// uses 4x4 antialiasing.

```

```

// Render Trapezoid A

dY(1 \le 14)

dXDom(dXDom1<<14)

dXSub(dXSub1<<14)

Count(count1 << 2)

render.PrimitiveType = GLINT R4_TRAPEZOID

render.AntialiasEnable = GLINT R4_TRUE

render.AntialiasQuality = GLINT R4 MIN ANTIALIAS

render.CoverageEnable = GLINT R4_TRUE

Render(render)

// Render Trapezoid B

dXSub(dXSub2<<14)

ContinueNewSub(count2<<2)

// Render Trapezoid C

dXDom(dXDom2<<14)

ContinueNewDom(count3<<2)

// Now we have finished the primitive flush out

// the last scanline

FlushSpan()

```

*Note:*

When rendering antialiased primitives, any count values should be given in subscanlines. For example if the quality is 4x4 then the count will be 4 times the number of scanlines completely covered by the primitive plus the number of subscanlines contained in the remaining partially covered scanlines. Also, if using 4x4 quality then any delta value must be divided by 4. If using 8x8 quality then the multiply/divide factor is 8.

When rendering, *AntialiasEnable* must be set in the **AntialiasMode** register to scale the fragment's color by the coverage value. An appropriate blending function should also be enabled. See the Antialias Application and Alpha Blend sections for more details.

Note: When rendering antialiased bow-ties the coverage value on the cross-over scanline may be incorrect.

#### 8.2.5.1 Antialiased Polygons

As for other primitives, the following comments apply to rasterization of polygons set up in the front end Gamma chip. R4 does not directly support antialiasing in standalone mode.

Antialiased polygons (or more precisely, screen aligned trapezoids) are scan converted by walking the trapezoid's edges to a higher resolution (x4, say). The coverage for a specific pixel is calculated by summing the coverage each of the sub scanlines contributes. More specific details are given in the implementation section.

Care needs to be taken when trapezoids (from the same polygon) meet part way through a scan line. The span of pixels cannot be generated until the second trapezoid is available as it will contribute to the coverage in this scanline. If, on the last trapezoid, the scan line is only part covered then a 'flush' command is needed to generate the coverage for these pixels as there is no follow-on trapezoid.

#### 8.2.5.2 Stippling during Rasterizing

Normally, stipple processing is accommodated in the Stipple Unit. This covers all stipple requirements for OpenGL (e.g. aliased lines, polygons) and most other platforms, e.g. X. Details are given in the Stipple Unit section.

The Rasterizer does provide additional stipple functionality, for example stippling requirements for X which cannot be met by the Stipple Unit:

- Arbitrary stipple on lines.

- Arbitrary stipple on polygons, especially rectangles.

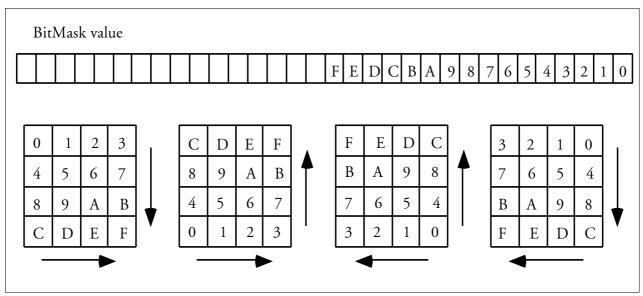

The bit mask unit in the rasterizer (normally used for characters) can give an arbitrary stipple to any primitive. The stipple pattern required is loaded into the **BitMaskPattern** register 32 bits at a time, in the order in which the pixels in the primitive are generated. The state of each bit in the bit mask determines if an active pixel is generated or a passive one. One bit in the stipple sequence is required for each pixel in the primitive.

This stippling method is independent of the Stipple Unit and can replace its function or be used as a second level of stippling.

#### 8.2.5.3 Stipple Lines (X)

The standard OpenGL method of stippling lines can be used in X for the more restricted case where the mark/space ratio of the stipple is the same. X allows an arbitrary stipple pattern to be defined using the Bitmap facility. Here the host provides a number of bit mask words where each bit corresponds to one pixel in the line. The state of this bit determines whether the associated pixel is generated or skipped.

#### **8.2.6** Points

Points are the easiest of all primitives to scan convert but there are a number of special cases. The main questions are whether the point is antialiased or not, and its size.

All the DDA related parameters are held constant over a point (a point may cover many pixels), and between points in a Begin/End set. Before any point rasterisation is done the host must have set up the Texture, Color, Fog and Depth units so they maintain a constant value and don't increment between pixels in a point.

In OpenGL no stipple operations are defined for points so stippling must be disabled. This can be done by changing the stipple mode (see Stipple Unit) or by setting the stipple operation in the **Render** command to 'none'. This later method is much easier for the software to use.

R4 does not support a **DrawPoint** command because points do not require setup calculations. Instead points can be individually loaded as below, or set up as line segments and rendered as points.

#### 8.2.6.1 Aliased Points (OpenGL)

For points larger than one pixel, trapezoids should be used. The fields in the **Render** command register are described in detail later, however, in this case the *PrimitiveType* field in the **Render** command should be set to equal GLINT R4 POINT PRIMITIVE.

#### 8.2.6.2 Worked example – one-pixel points

A series of one pixel points  $P(X_1, Y_1)$ ,  $P(X_2, Y_2)$  ...  $P(X_n, Y_n)$  are required. The **Render** command is set up as shown:

| Render Data Field |   |                     |   |                          |   |  |

|-------------------|---|---------------------|---|--------------------------|---|--|

| AreaStippleEnable | 0 | LineStippleEnable   | 0 | PrimitiveType            | 2 |  |

| FastFillEnable    | 0 | FastFillIncrement   | X | UsePointTable            | X |  |

| AntialiaseEnable  | X | AntialiasingQuality | X | ResetLineStipple         | X |  |

| SyncOnBitMask     | X | SyncOnHostData      | X | TextureEnable            | 1 |  |

| FogEnable         | 1 | CoverageEnable      | 0 | SubPixelCorrectionEnable | 0 |  |

StartXDom (X<sub>1</sub>)

StartY (Y<sub>1</sub>)

Render

StartXDom (X<sub>2</sub>)

StartY (Y2)

Render

... ...

StartXDom (Xn)

. . .

StartY (Yn)

Render

#### 8.2.6.3 Aliased Points (X)

X only has single pixel sized points so these are rendered by sending any of the step commands with the (X, Y) position encoded in the data field for each point to render.

#### 8.2.6.4 Antialiased Points (OpenGL)

R4 can render antialiased points using the *Gamma* front end to define OpenGL points. Antialiased points are treated as circles, with the coverage of the boundary fragments ranging from 0% to 100%. For information about available sizes and the Points Table, see the **AAPointSize** register in the R4 Reference Guide, volume III.

#### R4 supports:

- point diameters of 0.5 to 16.0 in steps of 0.25 for 4x4 antialiasing

- point diameters of 0.25 to 8.0 in steps of 0.125 for 8x8 antialiasing

...using the AntiAliasQuality bit in the Render or PointMode register

To scan convert an antialiased point as a circle R4 traverses the boundary in sub scanline steps to calculate the coverage value. For this, the sub scanline intersections are calculated incrementally using a small table. The table holds the change in X for a step in Y. Symmetry is used so the table only holds the delta values for one quadrant.

The pattern of table accesses, additions and subtractions are shown in Figure 2.3 below for an odd diameter point. On the diagram the symbol +/-= Table[n] by an arrow indicates the contents of the **PointTable** at address n are added/subtracted to move along the arrow.

**StartXDom**, **StartXSub** and **StartY** are set to the top or bottom of the circle and **dY** set to the subscanline step. In this example the point table will have three entries.

Figure 2-3 Antialiasing an odd-diameter point.

Note: in the case of an even diameter, the last of the required entries in the table is set to zero.

The GLINT R4 Reference Guide gives full details of how the point table is laid out.

Note that the table is configurable and point shapes other than circles can be rendered. Also if the **StartXDom** and **StartXSub** values are not coincident then horizontal thick lines with rounded ends, can be rendered.

The point looks like this and we will render from bottom to top. The origin is assumed to be bottom left and we are using 4x4 antialiasing quality. The point's diameter is 3 pixels, or 12 sub scanlines. The point table is assumed to be set up already.

| Render Data Field |   |                     |   |                          |   |  |

|-------------------|---|---------------------|---|--------------------------|---|--|

| AreaStippleEnable | 0 | LineStippleEnable   | 0 | PrimitiveType            | 1 |  |

| FastFillEnable    | 0 | FastFillIncrement   | X | UsePointTable            | 1 |  |

| AntialiaseEnable  | 1 | AntialiasingQuality | 0 | ResetLineStipple         | X |  |

| SyncOnBitMask     | 0 | SyncOnHostData      | X | TextureEnable            | 1 |  |

| FogEnable         | 1 | CoverageEnable      | 1 | SubPixelCorrectionEnable | 0 |  |

StartXDom (X)

StartXSub (X)

StartY (Y)

dY (1.0/4.0)

Count (12)

Render

FlushSpan ()

The SubPixelCorrection bit may be turned on to enable correction of the color, depth, fog and texture values at the start of a scanline.

#### 8.2.7 Lines

There are two accepted way of drawing lines: using a DDA, or Bresenham's algorithm. Bresenham's algorithm has an advantage over DDAs because no divide is necessary. This has some benefits, particularly for 2D. For OpenGL we use the DDA method because the cost of the divide is acceptable and is needed to calculate the gradient of any color or depth change.

Lines are specified by their end points (accurate to 4 bits of sub pixel position) and rate of change in X and Y per step along the major axis of the line.

#### 8.2.7.1 Aliased Lines (OpenGL and X)

Single pixel wide aliased lines are drawn using a DDA algorithm so all it needs by way of input data is StartX, StartY, dX, dY and length. The algorithm just calculates:

```

while (length--)

\{ X = X + dx

Y = Y + dy

plot ((int)X, (int)Y)

\}

```

The variables X, Y, dx and dy are all fixed point numbers. The conversion to memory address using the X, Y coordinate is done in the memory read units.

8.2.7.2 Worked example - Aliased PolyLine (OpenGL)

A two segment polyline from  $(X_1, Y_1)$  to  $(X_2, Y_2)$  to  $(X_3, Y_3)$  is required. Both segments are X major, so: abs  $(X_{n+1} - X_n) > abs (Y_{n+1} - Y_n)$

Note: For individual line segments or the first line segment in a polyline the line stipple is reset (as shown).

| Render Data Field  |   |                     |   |                          |   |

|--------------------|---|---------------------|---|--------------------------|---|

| AreaStipple Enable | 0 | LineStippleEnable   | 1 | PrimitiveType            | 0 |

| FastFillEnable     | 0 | FastFillIncrement   | X | UsePointTable            | 0 |

| AntialiaseEnable   | 0 | AntialiasingQuality | X | ResetLineStipple         | 1 |

| SyncOnBitMask      | 0 | SyncOnHostData      | 0 | TextureEnable            | 1 |

| FogEnable          | 1 | CoverageEnable      | 0 | SubPixelCorrectionEnable | 0 |

```

\begin{array}{l} \operatorname{StartXDom}\left(X_{1}\right) \\ \operatorname{dXDom}\left(\pm1.0\right) \\ \operatorname{StartY}\left(Y_{1}\right) \\ \operatorname{dY}\left((Y_{2}\text{-}Y_{1})/\!(X_{2}\text{-}X_{1})\right) \\ \operatorname{Count}\left(\operatorname{abs}\left(X_{2}\text{-}X_{1}\right)\right) \\ \operatorname{Render} \\ \operatorname{dXDom}\left(\pm1.0\right) \\ \operatorname{dY}\left((Y_{3}\text{-}Y_{2})/\!(X_{3}\text{-}X_{2})\right) \\ \operatorname{ContinueNewLine}\left(\operatorname{abs}\left(X_{3}\text{-}X_{2}\right)\right) \end{array}

```

Note:

The use of ContinueNewLine is not recommended for OpenGL because the DDA units will start with a slight error as compared with the value they would have been loaded with for the second and subsequent segments. The fractional bits of the DDA can be forces to zero or half on the ContinueNewLine action.

#### 8.2.7.3 Aliased Wide Lines (OpenGL)

There is no direct support for wide lines. The OpenGL server has two options:

- Wide lines can be drawn by repeating a single pixel wide line, but offset by one pixel in X for X major lines or one pixel in Y for Y major lines. Any values interpolated along the line (e.g. color) will need to be re-initialised at the start of each individual line. This is easily done with the Render command.

- 2. Wide lines can be converted to parallelograms (the ends of a wide line are parallel to the edge of the screen in OpenGL) and then rendered as polygons.

As you might expect neither method is the best in all cases. For vertical or near vertical lines method 2 will cause fewer page breaks in memory so should be faster. However if there is any stippling then method 1 is likely to be much faster. Method 1 is the simpler method and is the preferred implementation.

A single wide line from  $(X_1, Y_1)$  to  $(X_2, Y_2)$  is required. The line is 3 pixels wide. The line is X major so abs  $(X_2 - X_1) >$ abs  $(Y_2 - Y_1)$ .

| Render Data Field |   |                     |   |                          |   |

|-------------------|---|---------------------|---|--------------------------|---|

| AreaStippleEnable | 0 | LineStippleEnable   | 1 | PrimitiveType            | 0 |

| FastFillEnable    | 0 | FastFillIncrement   | X | UsePointTable            | 0 |

| AntialiaseEnable  | 0 | AntialiasingQuality | X | ResetLineStipple         | 1 |

| SyncOnBitMask     | 0 | SyncOnHostData      | X | TextureEnable            | 1 |

| FogEnable         | 1 | CoverageEnable      | 0 | SubPixelCorrectionEnable | 0 |

$StartXDom(X_1 - 1)$

$dXDom(\pm 1.0)$

StartY (Y<sub>1</sub>)

$dY ((Y_2 - Y_1)/(X_2 - X_1))$

Count (abs  $(X_2 - X_1)$ )

Render

$StartXDom(X_1)$

Render

StartXDom  $(X_1 + 1)$

Render

#### 8.2.7.4 Aliased Wide Lines (X)

Individual wide lines in X have square ends and multiple connected wide lines have a range of joint styles. X needs to convert the wide lines either to polygons, or to a series of spans, to achieve the desired effect.

#### 8.2.7.5 Antialiased Lines (OpenGL)

Antialiased lines on R4 are supported via the *Gamma* OpenGL interface only - the onboard Delta unit does not implement antialiased lines.

Antialiased lines of any width are drawn as antialiased polygons (see below). If stipple is enabled then the line is drawn as a series of polygons to match up with the stipple parameters, using the *RepeatFactor*, *StippleMask* and *Mirror* fields in the **LineMode** or **LineStippleMode** registers. The line width is defined in the AALineWidth register as a floating point number.

### 8.2.8 Polygons

The only non-triangle polygons the rasteriser handles are screen aligned trapezoids. These are characterised by having the top and bottom edges parallel to the X axis. The side edges may be vertical but are more usually diagonal. The top or bottom edges can degenerate into points in which case we are left with flat topped or flat bottomed triangles. Any polygon can be decomposed into this shape, however the sample OpenGL server always decomposes polygons<sup>5</sup> into triangles because the interpolation of values over non-triangular polygons is ill defined.

| The raster | riser does | handle | vertical | 'bow tie' |

|------------|------------|--------|----------|-----------|

| polygons.  |            |        |          |           |

As part of the rasterisation process a number of parameters (color, depth, fog and texture) are calculated for each fragment generated. These are calculated in the DDA unit down stream under the guidance of the rasteriser step messages. The ideal way to calculate these values is to use the fragments XY coordinate and substitute this into the plane equation for each parameter in turn. This technique gives the best result, however it is computationally expensive so it is normal to use an incremental method such as a DDA to approximate to it. The DDA method introduces some errors of its own:

- An incremental error due to the finite precision of the delta values. To overcome this source of errors enough fractional bits are used so that the error cannot propagate into the actual bit range of the DDA where the parameter value is extracted from.

- The start value for a parameter, P, can be nearly dPdx (one step in the X direction) out because the value calculated as a result of a Y step (shown as a circle in the following

<sup>&</sup>lt;sup>5</sup>Excluding the special case of screen aligned rectangles.

diagram) corresponds to the value of the sample on the edge and not at the center of the first fragment to be drawn.

It is necessary to correct for this error to eliminate bright edge artefacts and achieve high quality rendering.

This correction is needed for every scanline. A similar correction is needed at the start of the primitive because the parameter value at the start vertex is unlikely to lie on the horizontal center of a pixel so needs adjustment in Y. This correction is handled by software.

If dErr is the distance the edge is away from the pixel's center (must be < 1) and dPdx is the change in P for unit change in x then the correct value at the first sample point is:

The distance dErr is sent internally by the rasteriser in PrepareToRender and Step messages. The multiplication is done in the DDA units whenever these messages are received, but only update Px on the **SubPixelCorrection**register if the LS bit of the data field is set. The correction dErr is sent as a 7 bit 2's complement 1.6 fixed point format. The dErr value sent in the messages is the dErr needed for the next scanline (of the first one in the case of a PrepareToRender).

#### 8.2.8.1 Sub Pixel Correction not Supported for Antialiased Primitives

Sub pixel correction must be enabled by the *SubPixelCorrectionEnable* bit in the **Render** command if it is required. See the *GLINT R4 Reference Guide* for more information.

Antialiasing presents a much more complex problem to solve in that the sample point for the parameters must be inside the boundary of the fragment, but this may not be the center of the pixel anymore. Near horizontal edges can give rise to a dErr value which approaches the width of the screen (or window). Two methods can be used to overcome this:

- The sample point can be moved to be within the boundary by 'micro nudging' the DDAs in X and Y.

- The parameter being interpolated can be integrated over the interior sub pixel sample points and then divided by the number of interior points (this is the method in the OpenGL spec).

In both these cases the changes to the DDA units are too extensive given the other problems antialiasing presents (the coverage calculation doesn't take into account sub pixel visibility and doesn't work well with a depth buffer). No sub pixel corrections are done for antialised primitives.

#### 8.2.8.2 Antialiased Triangle

The triangle looks like this and is rendered from top to bottom. The origin is assumed to be bottom left. Antialias quality is 4x4:

| Render Data Field |   |                     |   |                          |   |  |  |  |

|-------------------|---|---------------------|---|--------------------------|---|--|--|--|

| AreaStippleEnable | 1 | LineStippleEnable   | 0 | PrimitiveType            | 1 |  |  |  |

| FastFillEnable    | 0 | FastFillIncrement   | X | UsePointTable            | 0 |  |  |  |

| AntialiaseEnable  | 1 | AntialiasingQuality | 0 | ResetLineStipple         | X |  |  |  |

| SyncOnBitMask     | 0 | SyncOnHostData      | 0 | TextureEnable            | 1 |  |  |  |

| FogEnable         | 1 | CoverageEnable      | 1 | SubPixelCorrectionEnable | 1 |  |  |  |

*Note:*

The DDA units need to have their sample point biased from the center of the pixel to the lower edge of the pixel so the DDA units can be tracked properly with the walk messages. This can be done by calculating the start values for integer Y values rather than at Y+0.5 as would normally be done.

The sub pixel correction is only needed if color, depth, fog or texture interpolation is being used.

### 8.3 Span Operations

Many 2D rendering operations can be implemented more efficiently using span operations, enabled with the *FastFillEnable* bit in **Render** and **Render2D**. For both 2D textures and rasterizer bit mask operations the improvement can be from about 40 Mpixels/s to 400 Mpixels/s.

GLINT R4's span filling implementation can be used for image upload, image download, filling with constant color, filling with a pattern, characters (i.e. bit masks), copies, and copies with logical ops. Any trapezoid can be used and the scanning direction can be left-to-right or right-to-left. Benefits of span fill for 2D operations include:

- Better utilization of SGRAM block fill (where memory devices permit) for solid, stippled and patterned fills and character bitmaps.

- Span mechanism is independent of pixel size makes maximum use of framebuffer bandwidth for 8, 16 and 32 bit pixels.

- Multiple pixels processed in parallel

- No alignment restrictions any span operation may be performed to any pixel alignment for all pixel sizes.

- Page break overheads are spread over many more read/write operations during a BitBlt operation – performance of BitBlts is much closer to peak memory bandwidth

- Both window- and screen-relative operations supported

- Scissor clipping can be used in conjunction with span operations

If any reads are enabled, span operations are converted into a series of normal memory reads. The memory data returned is aligned and sent on in 64 bit words for further processing.

Note: This differs from earlier chips where the memory interface was responsible for decoding the span mask and returning the appropriate aligned data.

Span reads are only supported when the pixel data is laid out in the Linear or Patch64 formats. 32\_2 and patch\_2 formats do not support spans (but packed support is available for non-span rasterization - see **Packed8Pixels** and **Packed16Pixels** in the *GLINT R4 Reference Guide*.)

If source and destination reads are enabled then the source data is read first and stored in the scratch pad ram. Then the destination data is read and packed into 64 bit words and sent on. After each destination word is sent the corresponding source word from the scratch pad ram is read and sent on. The destination buffers are read in increasing numerical order.

Page breaks are kept to a minimum by reading all the data from a buffer for a span before moving onto the next buffer (for the same span mask).

The span operation does have some restrictions:

• Stencil and Depth tests are not available. These units just ignore the commands associated with fast span fills.

- Gouraud shading, alpha tests, alpha blend and dither operations are not available.

- If GIDs are being used for window clipping then spans cannot be used at full speed as they normally ignore GID information and write to all pixels in the span. However the result writes 4 pixels per cycle.

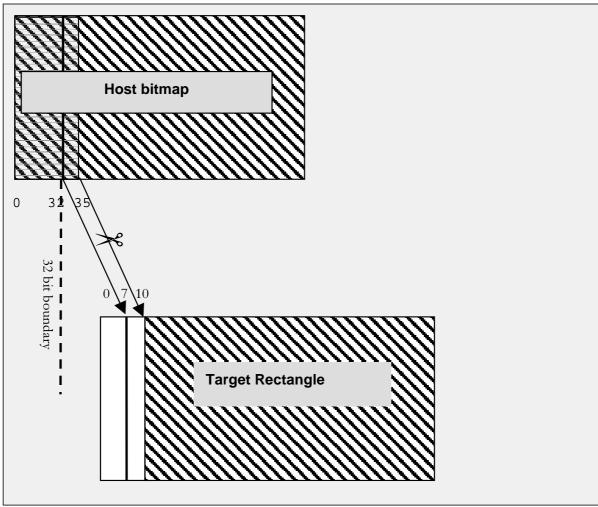

When span operation is enabled the rasterizer divides the pixels between the left- and right-hand edges of the polygon or rectangle into a succession of spans, each 64 pixels wide.

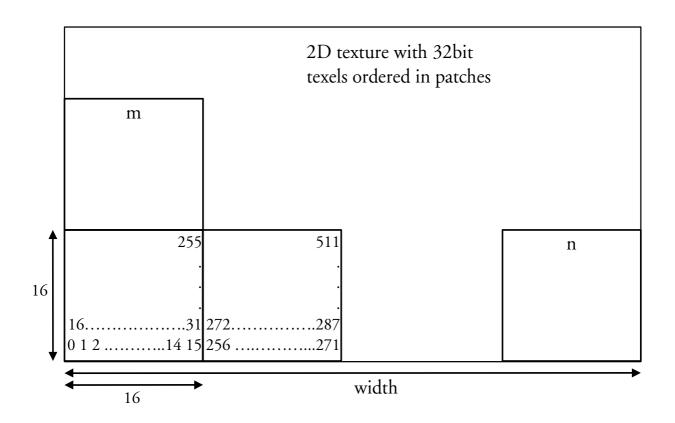

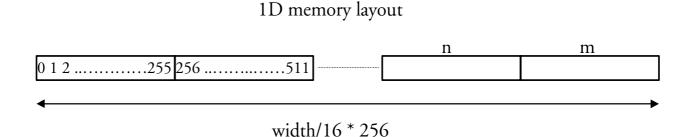

Each span is described by a 64 bit wide span mask and each pixel in the span has a corresponding bit in the span mask. If a bit in the span mask is set, then the corresponding pixel will be read and/or written. The least significant bit in the span mask (bit 0) corresponds to the leftmost pixel on the screen for the span.