# 3Dlabs®

# GLINT<sup>®</sup> Gamma Hardware Reference Manual

# **Proprietary Notice**

The material in this document is the intellectual property of **3D***labs*. It is provided solely for information. You may not reproduce this document in whole or in part by any means. While every care has been taken in the preparation of this document, **3D***labs* accepts no liability for any consequences of its use. Our products are under continual improvement and we reserve the right to change their specification without notice. **3D***labs* may not produce printed versions of each issue of this document. The latest version will be available from the **3D***labs* web site.

**3D***labs* products and technology are protected by a number of worldwide patents. Unlicensed use of any information contained herein may infringe one or more of these patents and may violate the appropriate patent laws and conventions.

**3D***labs* is the worldwide trading name of **3D***labs* Inc. Ltd.

**3D***labs*, GLINT Gamma and PERMEDIA are registered trademarks of **3D***labs* Inc. Ltd.

Microsoft, Windows and Direct3D are either registered trademarks or trademarks of Microsoft Corp. in the United States and/or other countries. OpenGL is a registered trademark of Silicon Graphics, Inc. All other trademarks are acknowledged and recognized.

© Copyright **3D***labs* Inc. Ltd. 1999. All rights reserved worldwide.

Email: info@3dlabs.com Web: http://www.3dlabs.com

Meadlake Place

Thorpe Lea Road, Egham

Surrey, TW20 8HE

United Kingdom

Tel: +44 (0) 1784 470555

Fax: +44 (0) 1784 470699

Shiroyama JT Mori Bldg 16F 40301 Toranomon Minato-ku, Tokyo, 105, Japan Tel: +81-3-5403-4653 Fax: +91-3-5403-4646

**3D***labs* Inc. 480 Potrero Avenue Sunnyvale, CA 94086, United States Tel: (408) 530-4700 Fax: (408) 530-4701

# **Change History**

| Document | Issue | Date       | Change                                             |

|----------|-------|------------|----------------------------------------------------|

| 149.3.0  | 1     | 3 Sept 97  | First Draft                                        |

| 149.3.0  | 2     | 22 Sept 97 | Index added. Style changes.                        |

| 149.3.0  | 3     | 25 Sept 97 | Style changes.                                     |

| 149.3.0  | 4,5,6 | 19 Nov 97  | Typographical and style corrections.               |

| 149.3.0  | 7     | 30 June 99 | Minor typographical and administrative corrections |

# 1. Contents

|    | •    | prietary Noticeange History                         |    |

|----|------|-----------------------------------------------------|----|

| 1. |      | Contents                                            |    |

| 2. | I    | Introduction                                        |    |

|    | 2.1  | What is the GLINT Gamma?                            | 1  |

|    | 2.2  |                                                     |    |

| 3. | F    | Functional Overview                                 |    |

| -  | 3.1  |                                                     |    |

|    | 3.2  |                                                     |    |

|    | 3.3  | **                                                  |    |

|    | 3.4  | ě                                                   |    |

|    | 3.5  |                                                     |    |

|    | 3.6  | 6                                                   |    |

|    | 3.7  |                                                     |    |

|    | 3.8  | <u> </u>                                            |    |

| 4. | P    | PCI Configuration Region                            | 11 |

|    | 4.1  | Internal Function Configuration Registers           | 11 |

|    | 4.2  |                                                     |    |

|    | 4.3  |                                                     |    |

|    | 4.4  |                                                     |    |

|    | 4.5  |                                                     |    |

|    | 4.6  |                                                     |    |

|    | 4.7  |                                                     |    |

|    | 4.8  | Indirect Region 0 access though configuration space | 24 |

|    | 4.9  | Base Addresses                                      | 25 |

|    | 4.10 | 0 Gamma Functions                                   | 27 |

| 5. | P    | Region 0 - Control Registers                        | 28 |

|    | 5.1  | Region 0 Address Map                                | 28 |

|    | 5.2  | Control Status Registers                            | 28 |

|    | 5.3  | Graphics Core Registers                             | 53 |

|    | 5.4  | Graphics Core FIFO Interface                        | 53 |

| 6. | F    | Electrical Data                                     | 55 |

|    | 6.1  | Absolute Maximum Ratings                            | 55 |

|    | 6.2  | č                                                   |    |

|    | 6.3  | •                                                   |    |

| 7. | P    | Pin Information                                     | 60 |

|    | 7.1  | Alphabetical Pin Listing                            | 61 |

|    | 7.1  | 1                                                   |    |

| 8. | ,    | Package Dimensions                                  |    |

|    |      | C                                                   |    |

| 9. | C    | Gamma System Design                                 |    |

|    | 9.1  | Termination / Pull-ups                              | 67 |

| 9.2    | Secondary device IDSel wiring | 67 |

|--------|-------------------------------|----|

| 9.3    | GLINT side-band signals       | 67 |

| 9.4    | Using a secondary bus master  | 67 |

| 10. Tl | hermal Characteristics        | 68 |

| 10.1   | Device Characteristics        | 68 |

| 10.2   | Thermal Model                 | 68 |

| 10.3   | Operation Without Heatsink    | 69 |

| 10.4   | Operation With Heatsink       | 69 |

| Index  |                               | 70 |

# **Figures**

| Figure 2-1 Functional Overview             | 2 |

|--------------------------------------------|---|

| Figure 2-2 Address generation circuitry    |   |

| Figure 3-1 Configuration Region            |   |

| Figure 4-1 Graphics Core Registers         |   |

| Figure 4-2 Graphics Core FIFO Interface    |   |

| Figure 5-1 Clock Waveform Timing           |   |

| Figure 5-2 Clock Referenced Input Timing   |   |

| Figure 5-3 PCIClk Referenced Output Timing |   |

| Figure 5-4 SCIClk Referenced Output Timing |   |

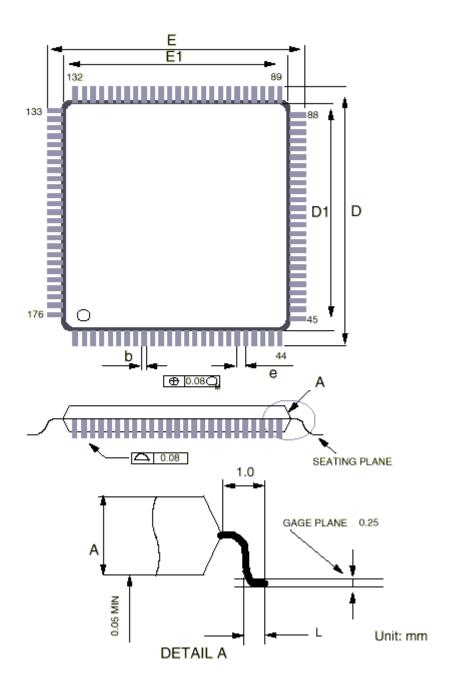

| Figure 6-1 Pin Numbering                   |   |

| Figure 6-2 Mechanical Diagrams             |   |

# **Tables**

| Table 2-1 Gamma Configuration Bit Definitions                    | 3  |

|------------------------------------------------------------------|----|

| Table 2-2 External Function Enable Pins (Mode control for Gamma) | 4  |

| Table 2-3 Delta compatible Mode Pins                             |    |

| Table 2-4 Delta compatible Configuration Pins                    | 5  |

| Table 2-5 Delta compatible Hard coded configuration bits         |    |

| Table 2-6 Serial Mode Operation: EEPROM Pins                     | 5  |

| Table 2-7 Serial Mode Operation: Configuration Pins              |    |

| Table 2-8 Serial Mode Operation: EEPROM Bit Definitions          | 6  |

| Table 2-9 Gamma PCI Address Regions.                             | 7  |

| Table 2-10 VGA Address Aliasing                                  | 9  |

| Table 2-11 VGA Address Regions                                   | 9  |

| Table 3-1 Gamma PCI Address Regions.                             | 27 |

| Table 4-1 Region Zero Address Map.                               | 28 |

| Table 4-2 Control Status Register Address Map                    | 30 |

| Table 5-1 Absolute Maximum Ratings                               | 55 |

| Table 5-2 DC Specifications                                      | 55 |

| Table 5-3 PCI Signal DC Specifications                           | 55 |

| Table 5-4 Test Loads for AC Timing                               | 56 |

| Table 5-5 Clock Waveform Timing                                  | 56 |

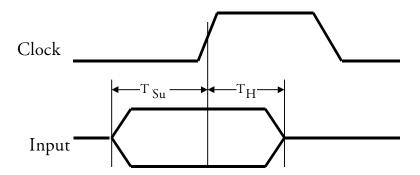

| Table 5-6 PCIClk Referenced Input Timing                         | 57 |

| Table 5-7 SCIClk Referenced Input Timing                         | 57 |

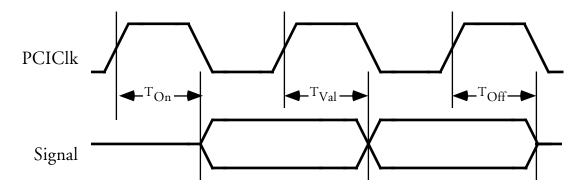

| Table 5-8 PCIClk 33MHz Referenced Output Timing                  | 58 |

| Table 5-9 PCIClk 66MHz Referenced Output Timing                  | 58 |

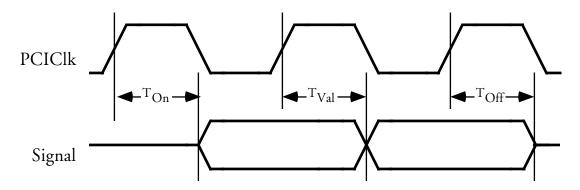

| Table 5-10 SCIClk Referenced Output Timing                       | 59 |

| Table 6-1 Alphabetical Pin Listing                               |    |

| Table 6-2 Numerical Pin Listing                                  | 64 |

| Table 6-3 176 pin PQFP Package Dimensions                        |    |

| Table 8-1 Operation With Heatsink                                | 69 |

# 2. Introduction

This document has been written as the reference for hardware and system designers who wish to develop hardware or software using the GLINT® Gamma geometry processor. A familiarity with the functionality of the GLINT rendering devices is assumed in this document.

#### 2.1 What is the GLINT Gamma?

GLINT Gamma is a lighting and geometry processor, designed to break the 3D lighting and geometry bottleneck on PCs. GLINT Gamma implements the full 3D lighting and geometry pipeline for any 3Dlabs rendering device, e.g. GLINT 500TX, GLINT MX, etc. The lighting and geometry calculations in GLINT Gamma are general purpose and may be used to accelerate any 3D API, including OpenGL, Direct3D and Apple's QuickDraw 3D.

The GLINT Gamma contains two on-chip PCI Local Bus interfaces: the primary interface communicates with the host processor and the secondary interface communicates with other PCI devices such as GLINT 500TX, GLINT MX or an SVGA device.

GLINT Gamma functions as a AGP/PCI to PCI multi-function adapter. So, in addition to calculating the geometric information, the GLINT Gamma can act as a bridge between the PCI bus and multiple graphics devices. This capability may be used in various ways:

- Driving twin GLINT 500TX or GLINT MX devices for increased rendering speed;

- Driving a GLINT rendering device plus an SVGA device for 3D acceleration with onboard VGA.

# 2.2 The GLINT Family

The GLINT 500TX and MX graphics processors provide 100% OpenGL compliant rendering combined with state-of-the-art Windows acceleration. VRAM framebuffer support enables the high screen resolutions required by professional applications such as CAD and visualization.

The GLINT Gamma is completely compatible with GLINT 500TX and MX rendering devices providing a glueless hardware interface. The GLINT Gamma programming model is fully compatible with the other GLINT devices.

# 3. Functional Overview

The GLINT Gamma adds extra 3D graphics acceleration to the 3Dlabs' rendering devices by implementing the geometry, lighting, slope and setup calculations for 3D primitives in hardware. The processing required on the host is greatly reduced and much less data is passed from the host to the graphics subsystem.

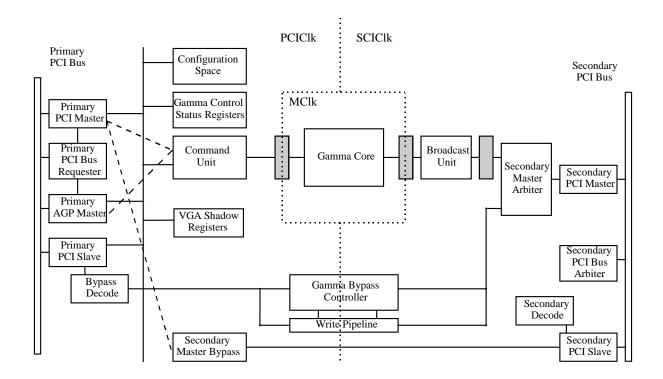

Figure 3-1 Functional Overview

For PCI accesses, if the access is for the Graphics Processor, it is directed towards the Command unit. If it is for a secondary target, the access is directed towards the Gamma Bypass Controller. The bus interface contains a number of PCI Configuration Registers and also various Control Status registers for the Gamma.

#### 3.1 Reset Mode Control

A number of the parameters for the bus interface are set at reset time. There are two modes of reset configuration control in Gamma. The first mode is Delta compatible, the second uses a Serial EEPROM (Serial Mode) to allow greater configuration set-up control. In Delta compatible mode there are some hardwired mode pins. In both modes some of the reset state is configured using resistors connected to *configuration pins*. These pins normally form part of the Gamma operation, but are tri-state at reset. The state of *configuration pins* is sampled on the trailing edge of reset.

The resulting reset state is stored as Configuration bits within Gamma.

| Configuration Bit       | Description                                                 |

|-------------------------|-------------------------------------------------------------|

| PCI66MHzCapable         | 1 = 66MHz Capable                                           |

| AGPCapable              | 1 = AGP Capable                                             |

| SBACapable              | 1 = AGP Sideband Addressing Capable                         |

| BaseClassZero           | 1 = force PCI Base Class Code to be zero                    |

| PCIMinGnt[7:6]          | top two bits of PCI Minimum Grant register                  |

| PCIMaxLat[7:6]          | top two bits of PCI Maximum Latency register                |

| ExtDevice1              | 1 = Enable external device 1                                |

| ExtDevice2              | 1 = Enable external device 2                                |

| ExtDevice3              | 1 = Enable external device 3                                |

| ExtVGAMode              | 0 = No VGA                                                  |

|                         | 1 = External device 1 is a VGA device                       |

|                         | 2 = External device 3 is a VGA device                       |

|                         | 3 = No VGA                                                  |

| VGANonAlias             | See 2.6 VGA Support for definitions of the VGANonAlias      |

| VGAControl              | See 2.6 VGA Support for definitions of the VGA control bits |

| GlintEn1                | 1 = External Device 1 is a GLINT device                     |

|                         | 0 = External Device 1 is any other device                   |

| GlintEn2                | 1 = External Device 2 is a GLINT device                     |

|                         | 0 = External Device 2 is any other device                   |

| MultiGLINTAp            | Multi GLINT aperture size control:                          |

|                         | if GlintEn1 = 1 and GlintEn2 = 1 then                       |

|                         | 00 = 0M DISABLED                                            |

|                         | 01 = 16M                                                    |

|                         | 10 = 32M                                                    |

|                         | 11 = 64M                                                    |

|                         | else                                                        |

|                         | DISABLED                                                    |

| SubsystemVendorID[15:0] | Subsystem Vendor ID                                         |

| SubsystemID[15:0]       | Subsystem ID                                                |

Table 3-1 Gamma Configuration Bit Definitions

# 3.1.1 Delta compatible configuration mode

Delta compatible configuration mode is provided to allow a Gamma chip to be placed directly onto current Delta boards without any hardware changes. All new designs should use the Gamma serial configuration mode.

In Delta compatible mode, the configuration bits are loaded from mode and configuration pins, in exactly the same way as Delta. Some configuration bits are hard-coded and cannot be used in this mode of operation. To switch to Serial configuration mode the ExtFunc pins are set to 00b. This setting would never be used on any current Delta board design, so making the new mode backwards compatible with current Delta boards.

The configuration pins are listed in the tables below:

| Mode Pin     | Description    | Mode                 |

|--------------|----------------|----------------------|

| ExtFunc[1:0] | 00Ь            | Serial Configuration |

|              | 01b            | Delta Compatible     |

|              | ExtDevice1 = 1 | -                    |

|              | ExtDevice2 = 0 |                      |

|              | ExtDevice3 = 0 |                      |

|              | 10b            | Delta Compatible     |

|              | ExtDevice1 = 0 | _                    |

|              | ExtDevice2 = 1 |                      |

|              | ExtDevice3 = 0 |                      |

|              | 11b            | Delta Compatible     |

|              | ExtDevice1 = 1 | _                    |

|              | ExtDevice2 = 1 |                      |

|              | ExtDevice3 = 0 |                      |

Table 3-2 External Function Enable Pins (Mode control for Gamma).

| Mode Pin         | Description                                                    |

|------------------|----------------------------------------------------------------|

| AGPSBA[0]        | 1 = Report legacy PCI Base class BaseClassZero = 1b            |

| (was ModeCtl[0]) | 0 = Report PCI 2.1 Base class BaseClassZero = 0b               |

| AGPSBA[1]        | 1 = PCIMaxLat[7:6] = 00b PCIMinGnt[7:6] = 11b                  |

| (was ModeCtl[1]) | 0 = PCIMaxLat[7:6] = 11b PCIMinGnt[7:6] = 11b                  |

| VGAEnable        | 1= External Device 1 is VGA device ExtVGAMode = 01b            |

|                  | 0 = No VGA present ExtVGAMode = 00b                            |

|                  | Note: Delta compatibility mode only supports External Device 1 |

|                  | as VGA                                                         |

Table 3-3 Delta compatible Mode Pins.

| Configuration Pin | Description                          |

|-------------------|--------------------------------------|

| GLINTInDis[0]     | Target device 0 GLINT control        |

|                   | Pull low (4K7) if GLINT GlintEn1 = 1 |

|                   | else Pull High (4K7) GlintEn1 = 0    |

| GLINTInDis[1]     | Target device 1 GLINT control        |

|                   | Pull low (4K7) if GLINT GlintEn2 = 1 |

|                   | else Pull High (4K7) GlintEn2 = 0    |

Table 3-4 Delta compatible Configuration Pins

| Configuration Bits      | Value | Note |

|-------------------------|-------|------|

| PCI66MHzCapable         | 0b    |      |

| AGPCapable              | 0Ь    |      |

| SBACapable              | 0b    |      |

| VGANonAlias             | 0b    |      |

| VGAControl              | 0000Ь |      |

| SubsystemVendorID[15:0] | 0000h | 1    |

| SubsystemID[15:0]       | 0000h | 1    |

Table 3-5 Delta compatible Hard coded configuration bits.

Note 1: In Delta compatible mode the subsystem registers are Write-once, reset to 0000h.

# 3.1.2 Serial configuration mode

In serial configuration mode the Gamma configuration bits are set from configuration pins, and from a serial EEPROM. The EEPROM chosen for use with Gamma is the Xicor X84041-3 or X84041-2.7. For more information on this part please refer to the Xicor data sheet. Other serial EEPROMs may be usable if they are 100% compatible with the Xicor part.

| Pin        | Description                 |

|------------|-----------------------------|

| SerialCEN  | Serial EEPROM Chip Enable   |

| SerialOEN  | Serial EEPROM Output Enable |

| SerialWEN  | Serial EEPROM Write Enable  |

| SerialData | Serial EEPROM Data bit      |

Table 3-6 Serial Mode Operation: EEPROM Pins.

| Configuration Pin   | Description                                             |

|---------------------|---------------------------------------------------------|

| SerialData          | Pull High (4k7) if external VGA target present          |

|                     | else Pull Low (4k7)                                     |

| SerialOEN:SerialWEN | Secondary PCI Bus Clock Control Set using 4k7 Pull-     |

|                     | ups and pull-downs for following codes.                 |

|                     | 00b = SCIClk[0:3] = PCIClk                              |

|                     | 01b = SCIClk[0:3] = PCIClk                              |

|                     | 10b = SCIClk[0:3] = PCIClk/2                            |

|                     | 11b = SCIClk[0:3] = PCIClk/2                            |

| VGAEnable           | In serial mode this pin is used to set the value of the |

|                     | 66MHz capable bit in the Configuration Status register. |

|                     | 0b = 66MHz capable bit not set                          |

|                     | 1b = 66MHz capable bit set                              |

Table 3-7 Serial Mode Operation: Configuration Pins.

| EEPROM Data Bit | Configuration Bits      |

|-----------------|-------------------------|

| 0               | AGPCapable              |

| 1               | SBACapable              |

| 2               | BaseClassZero           |

| [4:3]           | PCIMinGnt[7:6]          |

| [6:5]           | PCIMaxLat[7:6]          |

| 7               | ExtDevice1              |

| 8               | ExtDevice2              |

| 9               | ExtDevice3              |

| [11:10]         | ExtVGAMode              |

| 12              | VGANonAlias             |

| [16:13]         | VGAControl              |

| 17              | GlintEn1                |

| 18              | GlintEn2                |

| [20:19]         | MultiGLINTAp[1:0]       |

| [47:32]         | SubsystemVendorID[15:0] |

| [63:48]         | SubsystemID[15:0]       |

Table 3-8 Serial Mode Operation: EEPROM Bit Definitions

Note That the ExtVGAMode bits are qualified by the configuration state on the SerialData pin. If the hardware configuration is set such that VGA target is defined to be absent, the EEPROM bits will be ignored, and ExtVGAMode will be set to 00b.

Bits 0 to 20 of the Gamma configuration are visible in the **ChipConfig** register. This register can be read back over the PCI bus. Some of the bits are writeable and may be modified by the host processor if required — see **ChipConfig** register specification in this

document. The PCI66MHzCapable, and subsystem Vendor ID, and subsystem ID are visible only in the appropriate PCI configuration register.

# 3.2 Gamma multi-function support

The GLINT Gamma includes circuitry to allow multiple single function PCI devices attached to its secondary bus to look like a single PCI multi-function device. To achieve this the Gamma device adjusts the results of certain secondary device configuration space accesses.

#### 3.2.1 PCI Multi-function indication

To indicate a multi-function device all functions must return Bit 7 of the Header Type register set to a '1'. This bit is set by Gamma during a read of a secondary device Header Type register.

# 3.2.2 PCI 66MHz capable

To indicate 66MHz capability all functions must return Bit 5 of the Header Type register set to a '1'. This bit is set by Gamma during a read of a secondary device Status register if the Gamma PCI66MHzCapable configuration bit is set.

# 3.2.3 Force Legacy Class Codes

If BaseClassZero is set, GLINT Gamma will override the PCI base and sub class reported by devices on the secondary PCI bus. GLINT Gamma and any GLINT rendering device on the secondary PCI bus will have 00h reported as their PCI base class and 00h reported as their PCI sub-class. Any VGA device on the secondary PCI bus will have 00h reported as its PCI base class and 01h reported as its PCI sub-class.

# 3.3 PCI Address Regions

The Gamma PCI interface implements four PCI Address Regions, shown in Table 2-2.

The standard VGA-compatible Memory and I/O Space addresses are decoded when the Gamma has been suitably configured. These addresses do not form a single contiguous region, but are mentioned in the table for completeness.

| Region | Address Space | Bytes   | Description          | Comments    |

|--------|---------------|---------|----------------------|-------------|

| Config | Configuration | 256     | PCI Configuration    | PCI special |

| Zero   | Memory        | 128K    | Control Registers    | relocatable |

| Two    | Memory        | Note 1. | Multi-GLINT aperture | relocatable |

| ROM    | Memory        | 0K      | Expansion ROM        | No ROM      |

| VGA    | Memory & I/O  |         | VGA Addresses        | Note 2.     |

Table 3-9 Gamma PCI Address Regions.

- Note 1: Multi-GLINT aperture size is variable. Size is set by EEPROM configuration bits at reset.

- Note 2: VGA Addresses are decoded by Gamma when then VGA Present configuration bit is set to be processed by VGA chip on the secondary Bus.

# 3.4 PCI Configuration Space

The PCI Configuration Space provides a set of 'hooks' which satisfies the needs of current and anticipated system configuration mechanisms. The configuration registers are accessed and modified by the use of PCI Configuration Read and Write commands, and will normally be initialized by BIOS or similar low-level code at system power-up and reset.

Sixty four bytes of the Configuration Registers are predefined within the PCI Specification and are supported by the Gamma. These are defined in Section 28.2 of this document, and are all implemented within the PCI Bus Interface. Registers are provided for device identification, PCI control and status, and as base address registers for the relocatable memory regions. Registers are also provided to allow the reading and writing of the Gamma configuration serial EEPROM.

# 3.5 Gamma Control Registers

The Gamma Region Zero is a 128KByte region containing the control registers, and ports to and from the graphics processor. The control space is mapped in twice within the 128KByte region. In Delta compatible mode the second 64K the registers are mapped to be byte swapped for big endian hosts. For Dual GLINT systems when in Serial mode, Region zero can be configured to allow both GLINT control regions to be visible, the second GLINT being in the second 64K of this region.

A number of Control Status Registers are implemented within the PCI Bus Interface, including registers for interrupt and error handling, reporting graphics processor input FIFO status, and DMA control. All other registers on the Target GLINT are visible through the Gamma Control register space to allow for minimum software changes in supporting a Gamma Device.

# 3.6 VGA Support

The bus interface can be configured to respond to the standard VGA-compatible Memory and I/O Space addresses configuring ExtVGAMode. The interface will then respond to Memory addresses A0000h through BFFFFh.

Gamma can be configured to allow accesses to a number of I/O addresses to allow different types of VGA device to be used on the secondary bus.

#### 3.6.1 VGA Aliasing

Aliases of the VGA I/O addresses will be decoded as defined below:

| Decode Type      | Address operation          | VGANonAlias | VGAControl(3) |

|------------------|----------------------------|-------------|---------------|

| 10 Bit aliasing  | Bits 31-10 are ignored     | 0b          | 0b            |

| partial aliasing | Bits 31-16 must be 0000h   | 0b          | 1b            |

|                  | Bits 15-10 are ignored     |             |               |

| Full decode      | Bits 31-10 must be 000000h | 1b          | xb            |

Table 3-10 VGA Address Aliasing.

#### 3.6.2 VGA decode control

The VGA address ranges to be decoded can be configured in Serial mode, as set out in the table below:

| I/O Address range        | Type    | Configuration |

|--------------------------|---------|---------------|

|                          |         | Control       |

| 3B0h - 3BBh, 3C0h - 3DFh | VGA     | VGAControl(0) |

|                          |         | 1 = disabled  |

|                          |         | 0 = enabled   |

| 2E8h, 2EAh - 2EFh        | XGA     | VGAControl(1) |

|                          |         | 1 = disabled  |

|                          |         | 0 = enabled   |

| 102h                     | Special | VGAControl(2) |

|                          |         | 1 = disabled  |

|                          |         | 0 = enabled   |

Table 3-11 VGA Address Regions.

In Delta compatible mode VGAControl(3-0) is set to 0h and VGANonAlias to set to 0b. This enables the decoding of all the I/O address ranges with full 10 bit address aliasing to make Gamma fully compatible with Delta in this mode.

# 3.7 VGA register shadowing

The GLINT Gamma shadows a number of the VGA I/O control registers to allow it to work transparently in all systems. These shadow registers ensure that Gamma only responds to the correct VGA memory addresses, and I/O addresses for the current VGA set-up.

This shadowing allows a Gamma to co-exist with a monochrome adapter which is something that was not possible with a GLINT Delta.

# 3.8 Multi-GLINT aperture

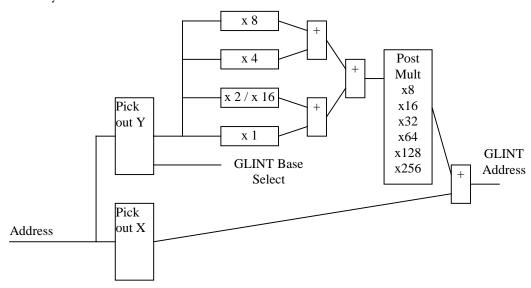

The Gamma Multi-GLINT aperture supports two GLINTS with non-shared framebuffers. Addresses into the aperture consist of a Y and an X component. To simplify calculations the X Span into the aperture is always a power of 2. The size of the Gamma aperture is set at reset.

The Aperture Address generator multiplies the Y address by the GLINT X span and then adds the result to the X address.

GLINT X spans supported are 320, 512, 640, 800, 1024, 1152, 1280, 1600, 1920 In 8 bits, 16 bits and 32 bits per pixel.

The address generator can hand GLINT framebuffer aperture sizes of 4M, 8M, 16M, and 32 Mbytes.

Figure 3-2 Address generation circuitry

Note: The Y address used in forming the GLINT address is ½ of the Input Y address, and the bottom bit of the Input Y address is used to select which GLINT Base address to use in the framebuffer access.

# 4. PCI Configuration Region

The PCI Configuration Region provides at set of 'hooks' which satisfies the needs of current and anticipated system configuration mechanisms. The configuration registers are accessed and modified by the use of Configuration Read and Write commands.

As GLINT Gamma is a multi-function device, the configuration space is split into eight 256 bytes blocks. GLINT Gamma has one internal function and up to 3 external functions.

GLINT Gamma will only respond to configuration space accesses for which devices exist. In Delta mode, hardware mode pins are used to indicate which of the external functions are populated in the system.

# **4.1 Internal Function Configuration Registers**

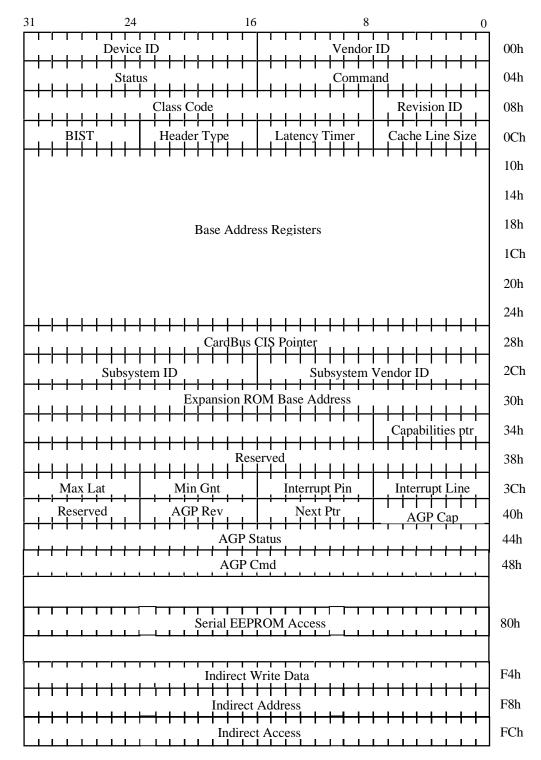

64 bytes of the Configuration registers are predefined within the PCI Specification and are supported by GLINT Gamma. The remaining 192 Bytes are device specific AGP capabilities are configured in a number of registers in this device specific area. All other registers are unused by GLINT Gamma, returning the value zero.

Figure 4-1 Configuration Region.

#### **4.2 Device Identification**

#### 4.2.1 Vendor ID

Vendor identification number.

# CFGVendorId

**Region:** Config Read Only

Offset: 00h Reset Value: 3D3Dh

Bits 0-15 3D3Dh

3Dlabs company code

#### 4.2.2 Device ID

Device identification number.

# CFGDeviceId

Region: Config Read Only

Offset: 02h Reset Value: 0008h

Bits 16-31 0008h

**GLINT Gamma Device number**

#### 4.2.3 Revision ID

Revision identification number.

# CFGRevisionId

Region: Config Read Only

Offset: 08h Reset Value: Revision Number

The revision ID register returns the following code:

Bits 0-7 Revision

01h = Revision R01

# 4.2.4 Class Code Register

# CFGClassCode

Region: Config Read Only

Offset: 09h Reset Value: 0B4000h

Bits 8-15 00h

Device class

Bits 16-23 40h

Sub class. PCI Definition: Co-Processor (unknown type)

Bits 24-31 0Bh

Base class. PCI Definition: Processor.

# 4.2.5 Header Type

# CFGHeaderType

Region:ConfigRead OnlyOffset:0EhReset Value:80hBits 16-2380h

Header Type. PCI Definition: Multi-function device

#### **4.3 Device Control**

# 4.3.1 Command Register

The command register controls the ability of a device to generate and respond to PCI cycles. Writing zero to this register disconnects the device from the PCI for all except configuration accesses. All necessary bits within the command register are supported for the functionality contained in GLINT Gamma.

# CFGCommand

| Region:    | Config                                       | Read/Write                                       |             |                                                             |

|------------|----------------------------------------------|--------------------------------------------------|-------------|-------------------------------------------------------------|

| Offset:    | 04h                                          | Reset Value:                                     | 0000h       |                                                             |

| Bit 0      | I/O access enab                              | ole<br>amma has no I/O                           | space regi  | (Read Only)                                                 |

| Bit 1      |                                              | enable<br>emory space acces<br>emory space acces |             | ET)                                                         |

| Bit 2      | Master enable  0 = Disable ma  1 = Enable ma | aster accesses. (RI                              | ESET)       |                                                             |

| Bit 3      | Special Cycle a  0 = GLINT Ga                |                                                  | onds to spe | (Read Only) ecial cycle accesses.                           |

| Bit 4      | •                                            | and Invalidate ena                               |             | (Read Only)<br><b>Iemory Write and Invalidate accesses.</b> |

| Bit 5      | VGA palette sn<br><b>0 = GLINT G</b> a       | oop enable<br>amma is not a VG                   | A device.   | (Read Only)                                                 |

| Bit 6      | Parity error rep<br><b>0 = GLINT G</b>       | ort enable<br>amma does not re                   | port pari   | (Read Only)<br>ty errors.                                   |

| Bit 7      | Address/Data s<br><b>0 = GLINT G</b>         | tepping enable<br>amma does not do               | o stepping  | (Read Only)                                                 |

| Bit 8      | SERR driver e  0 = GLINT Ga                  | nable<br>amma does not re                        | port parit  | (Read Only)<br>y errors.                                    |

| Bit 9      |                                              | ck-to-back enable<br><b>T Gamma maste</b> r      | does not    | (Read Only) implement fast back-to-back accesses.           |

| Bits 10-15 | Reserved <b>000000b</b>                      |                                                  |             |                                                             |

# **4.4 Device Status**

# 4.4.1 Status Register

The Status Register is used to record status information for PCI related events. The definition for each bit is given below.

Reads to this register behave normally. Writes function differently in that bits can be reset but not set. A bit is reset whenever the register is written and the data in the corresponding bit location is a 1.

# **CFGStatus**

| Region:    | Config                                                              | Read Only                                  |                                                   |

|------------|---------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------|

| Offset:    | 06h                                                                 | Reset Value:                               | 00h                                               |

| Bits 16-19 | Reserved (Read <b>0.0000b.</b>                                      | Only)                                      |                                                   |

| Bits 20    | Cap_List (Read<br>Configured by<br>0 = no addition<br>1 = AGP Capal | AGPCapable.<br>nal capabilities ov         | er PCI2.1                                         |

| Bit 21     | 0 = Gamma is                                                        | 66MHz capable o<br>33 MHz capable o        | configuration pin<br>only.<br>( in an AGP system) |

| Bit 22     | UDF Supported  0 = Gamma do                                         |                                            | er-definable configurations.                      |

| Bit 23     |                                                                     | ck Capable (Read<br>n accept fast back     | Only)<br>-to-back PCI transactions.               |

| Bit 24     |                                                                     | or Detected (Read<br>king not impleme      | Only)<br>ented on the Gamma.                      |

| Bits 25-26 | DEVSEL Timir<br><b>01b = The Gan</b>                                | -                                          | SEL# at medium speed.                             |

| Bit 27     |                                                                     | Abort (Read Only<br>a never signals T      |                                                   |

| Bit 28     |                                                                     |                                            | s master whenever<br>h Target-Abort.              |

| Bit 29     |                                                                     |                                            | s master whenever<br>h Master-Abort.              |

| Bit 30     |                                                                     | n Error (Read Only<br>na never asserts a s |                                                   |

| Bit 31     |                                                                     | Error (Read Only king is not imple         | )<br>mented by the Gamma.                         |

#### **4.5 Miscellaneous Functions**

#### 4.5.1 BIST

Optional register used for control and status of BIST (built-in self-test).

# **CFGBist**

**Region:** Config Read Only

Offset: 0Fh Reset Value: 00h

Bits 24-31 BIST (Read only)

00h. BIST unsupported by GLINT Gamma over the PCI interface.

# 4.5.2 Latency Timer

This register specifies, in PCI bus clocks, the value of the Latency Timer for this PCI bus master.

# CFGLatTimer

Region: Config Read/Write

Offset: 0Dh Reset Value: 00h

Bits 8-15 Latency Timer Count

Sets the maximum number of PCI clock cycles for master burst accesses.

#### 4.5.3 Cache Line Size

This register specifies the cache line size in units of 32 bit words. It is only implemented for masters which use the 'Memory write and invalidate' command. GLINT Gamma does not use this command.

# CFGCacheLine

Region: Config Read Only

Offset: 0Ch Reset Value: 00h

Bits 0-7 Cache Line Size

00h. Cache line size unsupported.

#### 4.5.4 Maximum Latency

This register specifies how often the PCI device needs to gain access to the PCI bus. Two EEPROM bits are used to set the top two bits of this register, and the lower bits are always zero. (Possible register values are thus limited to 00h, 40h, 80h, and C0h.)

# **CFGMaxLat**

| Region:  | Config                            | Read Only      |     |

|----------|-----------------------------------|----------------|-----|

| Offset:  | 3Fh                               | Reset Value: 8 | 30h |

| Bits 0-5 | Maximum Later<br><b>00.0000b</b>  | ісу            |     |

| Bit 6    | Maximum Later<br>Set by the bit P | •              |     |

| Bit 7    | Maximum Later<br>Set by the bit P | •              |     |

#### 4.5.5 Minimum Grant

This register specifies how long a burst period the PCI device needs. Two EEPROM bits are used to set the top two bits of this register, and the lower bits are always zero. (Possible register values are thus limited to 00h, 40h, 80h, and C0h.)

# CFGMinGrant

| Region:  | Config                         | Read Only    |            |

|----------|--------------------------------|--------------|------------|

| Offset:  | 3Eh                            | Reset Value: | Configured |

| Bits 0-5 | Minimum Gran                   | t[5:0]       |            |

| Bit 6    | Minimum Gran  Set by the bit P |              |            |

| Bit 7    | Minimum Gran  Set by the bit F | L. 3         |            |

# 4.5.6 Interrupt Pin

The Interrupt Pin register tells the BIOS which interrupt line GLINT Gamma uses.

# CFGIntPin

**Region:** Config Read Only

Offset: 3Dh Reset Value: 001h

Bits 8-15 Interrupt Pin

01h GLINT Gamma uses Interrupt pin A

# 4.5.7 Interrupt Line

The Interrupt Line register is an 8 bit register used to communicate interrupt line routing information.

# **CFGIntLine**

Region: Config Read/Write

Offset: 3Ch Reset Value: 00h

Bits 0-7 Interrupt Line

#### 4.5.8 CardBus CIS Pointer

This optional register is not implemented by the Gamma.

# **CFGCardBus**

Region: Config Read Only

Offset: 028h Reset Value: 0000.0000h

Bits 0-31 CardBus Pointer

0000.0000h = Not implemented

#### 4.5.9 Subsystem Vendor ID

This register identifies the vendor of the add-in board on which the Gamma device resides.

In Delta Compatible reset mode it has a reset value of zero, and can only be written to once; all subsequent writes are discarded. Both bytes of this register should be initialized by the Gamma BIOS after a reset.

In Serial Mode the Subsystem ID is read only and is loaded from the Serial EEPROM.

# CFGSubsystemVendorId

**Region:** Config Read Only / Write Once

Offset: 02Ch Reset Value: configured

Bits 0-15 Subsystem Vendor ID

#### 4.5.10 Subsystem ID

This register is used to identify the add-in board on which the Gamma device resides.

In Delta Compatible reset mode it has a reset value of zero, and can only be written to once; all subsequent writes are discarded. Both bytes of this register should be initialized by the Gamma BIOS after a reset.

In Serial Mode the Subsystem ID is read only and is loaded from the Serial EEPROM.

# CFGSubsystemId

| Region:    | Config       | Read Only / W | rite Once  |

|------------|--------------|---------------|------------|

| Offset:    | 02Eh         | Reset Value:  | configured |

| Bits 16-31 | Subsystem ID |               |            |

# 4.5.11 Capabilities Pointer

The Capabilities Pointer register is an eight bit register used to provide an offset into the configuration space for the first item in a capabilities list. It is used by the Gamma device in an AGP system to point to the AGP capability registers.

# CFGCapPtr

| Region:  | Config                                                                                   | Read Only    |            |

|----------|------------------------------------------------------------------------------------------|--------------|------------|

| Offset:  | 34h                                                                                      | Reset Value: | configured |

| Bits 0-7 | Capability Ptr Configured by AGPCapable 00h. when AGPCapable = 0 40h when AGPCapable = 1 |              |            |

# 4.6 AGP Registers

#### 4.6.1 Capability ID

This register specifies that the device has AGP capability

# CFGCapID

**Region:** Config Read Only

Offset: 40h Reset Value: configured

Bit 0-7 Capability ID

Configured by AGPCapable 00h if AGPCapable = 0 02h if AGPCapable = 1

#### 4.6.2 Next Ptr

This register specifies the device has no next capability item.

# **CFGNextPtr**

**Region:** Config Read Only

Offset: 41h Reset Value: 00h

Bit 8-15 Next Ptr

00h = no further capabilities in list

#### 4.6.3 AGP Revision

This register specifies the revision of the AGP spec the device conforms to.

# **CFGAGPRev**

Region: Config Read Only

Offset: 42h Reset Value: configured

Bit 16-19 Minor Rev

Configured by AGPCapable 0h if AGPCapable = 0 0h if AGPCapable = 1

Bit 20-23 Major Rev

Configured at reset by AGPCapable

00h if AGPCapable = 0 01h if AGPCapable = 1

# 4.6.4 AGP status

This register describes the AGP capabilities of the device.

# CFGAGPStatus

| Region:   | Config                  | Read Only                                                            |                 |

|-----------|-------------------------|----------------------------------------------------------------------|-----------------|

| Offset:   | 44h                     | Reset Value:                                                         | configured      |

| Bit 0-1   | 0h if AGP               | l by AGPCapable<br>Capable = 0<br>Capable = 1                        |                 |

| Bit 2-8   | Reserved                |                                                                      |                 |

| Bit 9     | 0 if AGPC               | l by AGPCapable an<br>apable = 0 or SBACa<br>apable = 1 and SBAC     | pable = 1       |

| Bit 10-23 | Reserved                |                                                                      |                 |

| Bit 24-31 | Configure<br>00h if AGI | number of AGP req<br>1 by AGPCapable<br>PCapable = 0<br>PCapable = 1 | uests supported |

#### 4.6.5 AGP Command

This register specifies the revision of the AGP spec the device conforms to.

# **CFGAGPCommand**

| Region:   | Config                                                           | Read/Write                             |                          |

|-----------|------------------------------------------------------------------|----------------------------------------|--------------------------|

| Offset:   | 48h                                                              | Reset Value:                           | 00000000h                |

| Bit 0-1   | DataRate<br>0 = AGP disabl<br>1 = 1X transfer                    |                                        |                          |

| Bit 2-7   | Reserved                                                         |                                        |                          |

| Bit 8     | AGPEnable  0 = AGP Mastering Disabled  1 = AGP Mastering Enabled |                                        |                          |

| Bit 9     |                                                                  | ddressing Disable<br>ddressing Enablec |                          |

| Bit 10-23 | Reserved                                                         |                                        |                          |

| Bit 24-31 | RQDepth<br><b>Maximum num</b>                                    | nber of AGP reque                      | ests which can be queued |

#### **4.7 Serial EEPROM Access**

#### 4.7.1 Serial EEPROM Access Register

This register is used to access the Configuration Serial EEPROM. Reads and writes of the EEPROM can be initiated by setting up the correct stream of read and write accesses to the bottom bit of this register. For details of the read / write patterns to be used, see the XICOR data sheet on the X84041 operation. Note the EEPROM is also programmable and readable through a region 0 register.

# CFGSerialEnable

| Region:   | Config                 | Read/Write   |           |

|-----------|------------------------|--------------|-----------|

| Offset:   | 80h                    | Reset Value: | 00000000h |

| Bit 0     | Serial EEPROM Data Pin |              |           |

| Bits 1-31 | Reserved               |              |           |

# 4.8 Indirect Region 0 access though configuration space

Three configuration registers are provided to allow indirect accesses to region 0 through configuration space accesses. The offset to the region that is to be accessed is loaded into the Indirect Address register. For a write access, the data to be written is loaded into the Indirect Write Data register. The write access is then initiated by writing to the Indirect Access register. The data value written into the Indirect Access register is ignored. For a read access a read of the Indirect Access register returns the values at the current Indirect Address offset.

#### 4.8.1 Indirect Write Data

The Indirect Write Data register holds data value which will be written with Indirect write access.

# CFGIndirectWriteData

Region: Config Read/Write

Offset: F4h Reset Value: 00000000h

Bits 0-31 Indirect write data

#### 4.8.2 Indirect Address

The Indirect Address register holds the address offset for Indirect accesses.

# CFGIndirectAddress

Region: Config Read/Write

Offset: F8h Reset Value: 00000000h

Bit 0-22 Address offset within region

Bit 23-27 Reserved

Bit 28-31 Base Address select

0 = Base Address 0

1 to 7 = Reserved

#### 4.8.3 Indirect Access

Accessing the Indirect access register initiates the indirect region 0 access.

# CFGIndirectAccess

Region: Config Read/Write

Offset: FCh Reset Value: 00000000h

Bits 0-31 Writes: Data value ignored

Reads: Indirect access read data value

Bit 0-31 Indirect data

# **4.9 Base Addresses**

The base address registers allow the boot software to relocate PCI devices in the address spaces. At system power-up device independent software must be able to determine which devices are present, build a consistent address map, and determine if a device has an expansion ROM. All undefined Base address registers are read only and return the value 0000.0000h. GLINT Gamma does not have an expansion ROM and so the expansion ROM base address is also read only, returning the value 0000.0000h.

#### 4.9.1 Base Address 0 Register

The Base Address 0 Register contains the GLINT Gamma control space offset. The control registers are in memory space. They are not prefetchable and can be located anywhere in 32 bit address space.

# CFGBaseAddr0

| Region:    | Config                               | Read/Write        |                                                        |

|------------|--------------------------------------|-------------------|--------------------------------------------------------|

| Offset:    | 10h                                  | Reset Value:      | 0000.0000h                                             |

| Bits 0-3   | Address Type <b>0h Memory</b>        | y Space, not pre  | Read Only<br>fetchable, in 32 bit address space        |

| Bits 4-16  | Size indication <b>000h Indicate</b> | es that the contr | Read Only ol registers must be mapped into 128 KBytes. |

| Bits 17-31 | Base offset  Loaded at boot          | time to set offse | et of the control register space.                      |

# 4.9.2 Base Address 2 Register

The Base Address 2 Register contains the base address of the Gamma Multi GLINT aperture, and defines the size and type of this region.

# CFGBaseAddr2

| Region:    | Config                                                                                                          | Read/Write          |                                              |

|------------|-----------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------|

| Offset:    | 18h                                                                                                             | Reset Value:        | 0000.0000h                                   |

| Bits 0-3   | Address Type <b>0h Memo</b>                                                                                     | ory Space, not pre  | Read Only fetchable, in 32 bit address space |

| Bits 4-xx  | Size Indication (Read Only)  These bits are zero, Region size set at configuration to 16M, 32M, 64M or disabled |                     |                                              |

| Bits 31-xx | Base Address<br><b>Loaded at bo</b>                                                                             | ot time to set offs | et of the Multi GLINT aperture               |

#### 4.10 Gamma Functions

As a PCI multi-function device Gamma can have up to 4 functions. If Gamma is configured as AGP capable the Gamma function is always the first function. This is because the AGP capable function is always assumed to be the first function in a multi-function device. When not AGP capable the order of the functions is affected by the **ExtVGAMode** mode bits.

| PCI | AGP / No VGA      | Device 1 VGA      | Device 3 VGA      |

|-----|-------------------|-------------------|-------------------|

| 0   | Gamma Function    | External Device 1 | External Device 3 |

| 1   | External Device 1 | Gamma Function    | Gamma Function    |

| 2   | External Device 2 | External Device 2 | External Device 1 |

| 3   | External Device 3 | External Device 3 | External Device 2 |

| 4   |                   |                   |                   |

| 5   |                   |                   |                   |

| 6   |                   |                   |                   |

| 7   |                   |                   |                   |

Table 4-1 Gamma PCI Address Regions.

# 5. Region 0 - Control Registers

#### 5.1 Region 0 Address Map

The Gamma Region Zero is a 128KByte region containing the control registers, and ports to and from the graphics processor. The control space is mapped in twice within the 128KByte region. In Delta compatible mode the second 64K the registers are mapped to be byte swapped for big endian hosts. Region zero can be configured in other ways for dual GLINT systems. See the **CSRAperture** register specification for details.

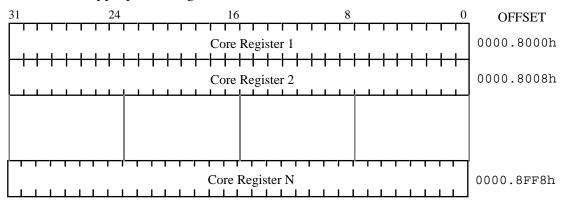

A large part of this region is not actually Gamma registers, but actually the registers of the Glint Target device sitting below Gamma. This allows Gamma to be a transparent as possible to the driver software.

| Address Range          | Region Select  | Register Location |

|------------------------|----------------|-------------------|

| 0000.0000 -> 0000.0FFF | Control Status | Gamma / Target    |

| 0000.1000 -> 0000.1FFF | Target Control | Target            |

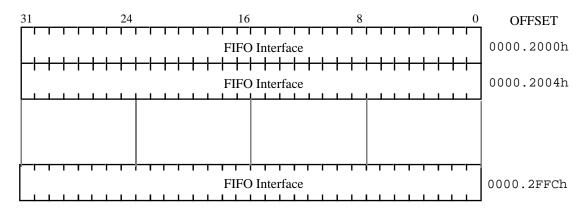

| 0000.2000 -> 0000.2FFF | GP FIFO Access | Gamma / Target    |

| 0000.3000 -> 0000.7FFF | Target Control | Target            |

| 0000.8000 -> 0000.FFFF | GP Registers   | Gamma / Target    |

| 0001.0000 -> 0001.0FFF | Control Status | Gamma / Target    |

| 0001.1000 -> 0001.1FFF | Target Control | Target            |

| 0001.2000 -> 0001.2FFF | GP FIFO Access | Gamma / Target    |

| 0001.3000 -> 0001.7FFF | Target Control | Target            |

| 0001.8000 -> 0001.FFFF | GP Registers   | Gamma / Target    |

Table 5-1 Region Zero Address Map.

### **5.2 Control Status Registers**

The GLINT Gamma Control Status Register region is split into two sections. The lower section allows direct access to the control status registers of the GLINT rendering device connected to GLINT Gamma. Some of the registers in this section are actually GLINT Gamma registers which are shadowing GLINT 500TX or MX operations for software compatibility with systems without GLINT Gamma.

The upper section has additional GLINT Gamma registers which are documented below. Refer to the appropriate GLINT 500TX or MX Hardware Reference Manual for details on registers in the lower region.

Writes to any reserved or undefined registers in the Control Status area will be discarded; reads will return the value zero.

For information on the target register definitions please refer to the appropriate target Hardware Reference Manual.

| Address Range         | Register         | Register Location | Notes |

|-----------------------|------------------|-------------------|-------|

| 0000.0000             | ResetStatus      | Gamma/Target      | 1     |

| 8000.0008             | IntEnable        | Target            | 2     |

| 0000.0010             | IntFlags         | Target            | 2     |

| 0000.0018             | InFIFOSpace      | Gamma             |       |

| 0000.0020             | OutFIFOWords     | Target            | 2     |

| 0000.0028             | DMAAddress       | Gamma             |       |

| 0000.0030             | DMACount         | Gamma             |       |

| 0000.0038             | ErrorFlags       | Target            | 2     |

| 0000.0040             | VClkCtl          | Target            | 2     |

| 0000.0048             | TestRegister     | Target            | 2     |

| 0000.0050 - 0000.0058 | Target Registers | Target            | 2     |

| 0000.0060             | DMAControl       | Gamma             |       |

| 0000.0068             | FIFODiscon       | Target            | 2     |

| 0000.0070 - 0000.07F8 | Target Registers | Target            | 2     |

| 0000.0080             | OutDMA           | Gamma             |       |

| 0000.0088             | OutDMACount      | Gamma             |       |

| 0000.0090 - 0000.03F8 | Target Registers | Target            | 2     |

| 0000.0400 - 0000.07F8 | Target Registers | Target            | 3     |

| 0000.0800             | GResetStatus     | Gamma             |       |

| 0000.0808             | GIntEnable       | Gamma             |       |

| 0000.0810             | GIntFlags        | Gamma             |       |

| 0000.0818 - 0000.0830 | Reserved         | Gamma             |       |

| 0000.0838             | GErrorFlags      | Gamma             |       |

| 0000.0840             | Reserved         | Gamma             |       |

| 0000.0848             | GTestRegister    | Gamma             |       |

| 0000.0850 - 000.0860  | Reserved         | Gamma             |       |

| 0000.0868             | GFIFODis         | Gamma             |       |

| 0000.0870             | GChipConfig      | Gamma             |       |

| 0000.0878             | GCSRAperture     | Gamma             |       |

| 0000.0880 - 0000.0BF8 | Reserved         | Gamma             |       |

| 0000.0C00             | PageTableAddr    | Gamma             |       |

| 0000.0C08             | PageTableLength  | Gamma             |       |

| 0000.0C10             | Reserved         | Gamma             |       |

| 0000.0C18             | Reserved         | Gamma             |       |

| 0000.0C20             | Reserved         | Gamma             |       |

| 0000.0C28             | Reserved         | Gamma             |       |

| 0000.0C30             | Reserved         | Gamma             |       |

| 0000.0C38             | DelayTimer       | Gamma             |       |

| 0000.0C40             | CommandMode      | Gamma             |       |

| 0000 00/0             | C 1L . E . 11       |       |

|-----------------------|---------------------|-------|

| 0000.0C48             | CommandIntEnable    | Gamma |

| 0000.0C50             | CommandIntFlags     | Gamma |

| 0000.0C58             | CommandErrorFlags   | Gamma |

| 0000.0C60             | CommandStatus       | Gamma |

| 0000.0C68             | CommandFaultingAddr | Gamma |

| 0000.0C70             | VertexFaultingAddr  | Gamma |

| 0000.0C78             | Reserved            | Gamma |

| 0000.0C80             | Reserved            | Gamma |

| 0000.0C88             | WriteFaultingAddr   | Gamma |

| 0000.0C90             | Reserved            | Gamma |

| 0000.0C98             | FeedbackSelectCount | Gamma |

| 0000.0CA0             | Reserved            | Gamma |

| 0000.0CA8             | Reserved            | Gamma |

| 0000.0CB0             | Reserved            | Gamma |

| 0000.0CB8             | GammaProcessorMode  | Gamma |

| 0000.0CC0 - 0000.0CF8 | Reserved            | Gamma |

| 0000.0D00             | VGAShadow           | Gamma |

| 0000.0D08             | MultiGLINTAperture  | Gamma |

| 0000.0D10             | MultiGLINT1         | Gamma |

| 0000.0D18             | MultiGLINT2         | Gamma |

| 0000.0D20 - 0000.0EF8 | Reserved            | Gamma |

| 0000.0F00             | SerialAccess        | Gamma |

| 0000.0F08 - 0000.0FF8 | Reserved            | Gamma |

Table 5-2 Control Status Register Address Map.

- Note 1: Writing to this register Resets both the Target device and Gamma. The access is sent to the target and snooped by Gamma

- Note2: The specification for other Target Registers can be found in the appropriate Hardware Reference Manual

- Note 3: The address offset range 0400h 07F8h is passed through to the target device to allow visibility of the GLINT registers overlaid by Gamma registers. This is possible because not all address bits are used in the register space decode of GLINT chips.

#### 5.2.1 Reset Status Register

Writing to the reset status register forces a software reset of the GLINT Gamma Graphics Core. The software reset does not reset the GLINT Gamma primary PCI interface. It is provided for software diagnostics in case an incorrect register set up locks up the GLINT Gamma internal GC.

The software reset takes a number of cycles and the GC must not be used during the reset. A flag in the register is provided which shows that the software reset is still in progress.

For more information on the operation of the GLINT Gamma at reset. Various mode pins are sampled at reset, these pins are described in section 2.1.

#### DResetStatus

**Region:** Zero Read/Write

Offset: 00h Reset Value: 0000.0000h

Bits 0-30 Reserved

Bit 31 Software Reset Flag

0 = GLINT Gamma is ready for use

1 = GLINT Gamma is being reset and must not be used

#### 5.2.2 Input FIFO Space Register

The Input FIFO Space register shows the number of words that can currently be written to the input FIFO. This register can be read at any time.

## **InFIFOSpace**

Region: Zero Read Only

Offset: 18h Reset Value: 0000.0021h

Bits 0-31 Input FIFO Space

The number of empty words in the input FIFO. This number of words can be written

before checking "InFIFOSpace" again.

#### 5.2.3 DMA Start Address

When using the legacy DMA controller to load the graphics processor, the DMA Start Address register should be loaded with the PCI address of the first word in the buffer to be transferred. In Queued DMA mode writes to this register are ignored.

Writing to the DMA Start Address register loads the address into the DMA address counter. Once a DMA has been initiated, the next DMA start address may be loaded. A read of this register returns the last start value loaded even if the DMA is already underway.

#### DMAAddress

Region: Zero Read/Write

Offset: 28h Reset Value: 0000.0000h

Bits 0-31 DMA Start Address

PCI start address for PCI master read transfer to the graphics processor core.

#### 5.2.4 DMA Count

When using the legacy DMA controller to load the graphics processor, the DMA Count register should be loaded with the number of words to be transferred in the DMA operation. In Queued DMA mode writes to this register are ignored.

The action of loading a word greater than zero initiates the DMA operation. The value read back from this register indicates the current number of words left to be transferred. Writes to this register will be ignored if a DMA is in progress, but can be read at any time.

#### DMACount

Region: Zero Read/Write

Offset: 30h Reset Value: 0000.0000h

Bits 0-23 DMA Count

Number of words to be transferred in the DMA operation

Bits 24-31 Reserved

## 5.2.5 DMA Control Register

The DMA control register sets up the data transfer modes for the DMA controllers. Data transfer can be set to byte swapped for big endian hosts.

## DMAControl

| Region:   | Zero                                                                 | Read/Write                                       |                                        |

|-----------|----------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|

| Offset:   | 60h                                                                  | Reset Value:                                     | 0000.0000h                             |

| Bit 0     | InDMA Byte Sw<br>This field shout<br>0 = Standard.<br>1 = Byte Swapp | ld only be change                                | ed when the InDMA controller is idle.  |

| Bit 1     | InDMA using A  0 = DMA uses I  1 = DMA uses A                        | PCI Master                                       |                                        |

| Bit 2     |                                                                      | hrottle<br>BF# and IRDY# 1<br>st data when spac  |                                        |

| Bit 3     |                                                                      | l Disable<br>Read Requests m<br>Read Requests di |                                        |

| Bit 4     | OutDMA Byte S This field shou  0 = Standard.  1 = Byte Swapp         | ld only be change                                | ed when the OutDMA controller is idle. |

| Bit 5     |                                                                      |                                                  | -                                      |

| Bit 6     |                                                                      |                                                  |                                        |

| Bits 7-31 | Reserved                                                             |                                                  |                                        |

#### 5.2.6 OutDMA Start Address

When using the Out DMA controller to upload the graphics processor output FIFO, the Out DMA Start Address register should be loaded with the PCI address where the first word of the upload data is to be transferred.

Writing to the OutDMA Start Address register loads the address into the OutDMA address counter. Once a DMA has been initiated, the next DMA start address may be loaded. A read of this register returns the last start value loaded even if the DMA is already underway.

#### OutDMAAddress

**Region:** Zero Read/Write

Offset: 80h Reset Value: 0000.0000h

Bits 0-31 Out DMA Start Address

PCI start address for PCI master write

transfer from the graphics processor core output FIFO.

#### 5.2.7 Out DMA Count

The Out DMA Count register should be loaded with the number of words to be transferred in the DMA operation. The action of loading a word greater than zero initiates the DMA operation. The value read back from this register indicates the current number of words left to be transferred. Writes to this register will be ignored if it is non-zero, but can be read at any time.

#### OutDMACount

Region: Zero Read/Write

Offset: 88h Reset Value: 0000.0000h

Bits 0-23 Out DMA Count

Number of words to be transferred in the DMA operation.

Bits 16-31 Reserved

#### 5.2.8 Gamma Reset Status Register

Writing to the reset status register causes a software reset of Gamma. The software reset does not reset the bus interface. The reset takes a number of cycles to complete during which the graphics processor should not be used. A flag in the register shows that the software reset is still in progress.

The GResetStatus register is different to the ResetStatus register in that only the Gamma device is reset, not the Target Device below Gamma. This register is normally for hardware diagnostic purposes only. The software operation is undefined if the Gamma is reset without resetting the Target Device.

#### GResetStatus

Region: Zero Read/Write

Offset: 800h Reset Value: 0000.0000h

Bits 0-30 Reserved

Bit 31 Software Reset Flag

0 = Gamma is ready for use.

1 = Gamma is being reset and must not be used.

## 5.2.9 Gamma Interrupt Enable Register

The Interrupt Enable Register selects which internal conditions are permitted to generate a bus interrupt. Three interrupt sources are defined below. At reset all interrupt sources are disabled.

# GIntEnable

| Region:    | Zero                                                                  | Read/Write   |            |

|------------|-----------------------------------------------------------------------|--------------|------------|

| Offset:    | 808h                                                                  | Reset Value: | 0000.0000h |

| Bit 0      | DMA Interrupt  0 = Disable inter  1 = Enable inter                    | errupt.      |            |

| Bit 1-2    | Reserved                                                              |              |            |

| Bit 3      | Error Interrupt Enable  0 = Disable interrupt.  1 = Enable interrupt. |              |            |

| Bits 4-12  | Reserved                                                              |              |            |

| Bit 13     | Command Inters  0 = Disable inter  1 = Enable inter                   | errupt.      |            |

| Bits 14-31 | Reserved                                                              |              |            |

#### 5.2.10 Gamma Interrupt Flags Register

The Interrupt Flags Register shows which interrupts are outstanding. Flag bits are reset by writing to this register with the corresponding bit set to a one. Flags at positions where the bits are set to zero will be unaffected by the write. The exception to this is bit 13, which is the Command interrupt Flag. This bit is cleared by clearing all bits the Command Unit Interrupt Flags Register **CommandIntFlags**.

## **GIntFlags**

| Region:    | Zero                                                          | Read/Write          |                                  |

|------------|---------------------------------------------------------------|---------------------|----------------------------------|

| Offset:    | 810h                                                          | Reset Value:        | 0000.0000h                       |

| Bit 0      | DMA Flag  0 = No interrupt  1 = Interrupt o                   |                     |                                  |

| Bit 1-2    | Reserved                                                      |                     |                                  |

| Bit 3      | Error Flag  0 = No interrupt  1 = Interrupt o                 |                     |                                  |

| Bits 4-12  | Reserved                                                      |                     |                                  |

| Bit 13     | Command Inter Flag set when a 0 = No interrup 1 = Interrupt o | any bits set in the | Command Interrupt Flags register |

| Bits 14-31 | Reserved                                                      |                     |                                  |

#### 5.2.11 Gamma Error Flags Register

The Error Flags register shows which errors are outstanding in Gamma. Flag bits are reset by writing to this register with the corresponding bit set to a one. Flags at positions where the bits are set to zero will be unaffected by the write. The exception to this is bit 13, which is the Command Error Flag. This bit is cleared by clearing all bits the Command Unit Error Flags Register

## GErrorFlags

| Region:    | Zero                                                         | Read/Write                              |                                                                                                         |

|------------|--------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------|

| Offset:    | 838h                                                         | Reset Value:                            | 0000.0000h                                                                                              |

| Bit 0      | Input FIFO Err Flag set on wri 0 = No error. 1 = Error outst | te to full input F                      | IFO.                                                                                                    |

| Bits 1-2   | Reserved                                                     |                                         |                                                                                                         |

| Bit 3      | -                                                            | ect or register acc<br>i.e. when the DM | tess to input FIFO while DMA<br>(ACount register is not zero).                                          |

| Bit 4-6    | Reserved                                                     |                                         |                                                                                                         |

| Bit 7      | -                                                            | either Master abo<br>e CFGStatus regis  | rt or Target abort occurs while PCI Master access in<br>ter can be read to determine the type of error. |

| Bit 8      | Reserved                                                     |                                         |                                                                                                         |

| Bit 9      | In DMA Overw Flag set in lega 0 = No error. 1 = Error outst  | acy mode if the In                      | DMACount register is written when it is not zero                                                        |

| Bit 10     |                                                              | •                                       | utDMACount register is written when it is not zero                                                      |

| Bits 11-12 | Reserved                                                     |                                         |                                                                                                         |

| Bit 13     | Command Error Flag set when a 0 = No error. 1 = Error outst  | any bits set in the                     | Command Error Flags register                                                                            |

| Bits 14-31 | Reserved                                                     |                                         |                                                                                                         |

#### 5.2.12 Gamma Test Register

For hardware test purposes only. Setting a bit in this register causes the corresponding unit to be put into test mode.

## GTestRegister

**Region:** Zero Read/Write

Offset: 848h Reset Value: 0000.0000h

#### 5.2.13 FIFO Disconnect Register

The FIFO Disconnect Register enables input FIFO disconnect on GLINT Gamma. Disconnect is disabled at reset.

#### DFIFODis

**Region:** 0 Read/Write

Offset: 868h Reset Value: 0000.0000h

Bit 0 Input FIFO Disconnect enable

0 = Disabled (RESET)

1 = Enabled

Bits 1-31 Reserved

#### 5.2.14 Gamma Chip Configuration Register

Most of Gamma configuration bits are visible through the **GChipConfig**. This register can then be read back over the PCI bus, to allow the host to determine how the Gamma chip has been configured, and to modify various fields of the configuration if required.

# GChipConfig

Region: Zero Read/Write

Offset: 870h Reset Value: (configured)

Bits 21-31

Reserved