# 3D labs®

# GLINT $500TX^{\text{\tiny TM}}$

Hardware Reference Manual

The material in this document is the intellectual property of 3Dlabs. It is provided solely for information. You may not reproduce this document in whole or in part by any means. While every care has been taken in the preparation of this document, 3Dlabs accepts no liability for any consequences of its use. Our products are under continual improvement and we reserve the right to change their specification without notice.

3Dlabs products and technology are protected by a number of worldwide patents. Unlicensed use of any information contained herein may infringe one or more of these patents and may violate the appropriate patent laws and conventions.

3Dlabs is the worldwide trading name of 3Dlabs Inc. Ltd.

3Dlabs and GLINT are registered trademarks and PERMEDIA is a trademark of 3Dlabs Inc. Ltd.

Microsoft, Windows and Direct3D are either registered trademarks or trademarks of Microsoft Corp. in the United States and/or other countries. OpenGL is a registered trademark of Silicon Graphics, Inc. Macintosh and Power Macintosh are registered trademarks and QuickDraw is a trademark of Apple Computer Inc. All other trademarks are acknowledged and recognized.

© Copyright 3Dlabs Inc. Ltd. 1997. All rights reserved worldwide.

3Dlabs Inc. 181 Metro Drive, Suite 520 San Jose, CA 95110 United States Tel: (408) 436 3455 Fax: (408) 436 3458

3Dlabs Ltd. Meadlake Place Thorpe Lea Road. Egham Surrey, TW20 8HE United Kingdom Tel: +44 (0) 1784 470555

Fax: +44 (0) 1784 470699

Email: info@3dlabs.com Web: http://www.3dlabs.com

# Change History

| Document | Issue | Date           | Change                                                                                                           |

|----------|-------|----------------|------------------------------------------------------------------------------------------------------------------|

| 106.1.56 | 1     | 29 April<br>96 | First Release                                                                                                    |

|          | 2     | 14 May 96      | Updates to Chapters 3, 4, 5, 8, 9, 10, 11, 12 and Appendix A added.                                              |

|          | 3     | 4 June 96      |                                                                                                                  |

|          | 4     | 5 Mar 97       | Typing corrections to sections 3.2.1, 4.2.16, 7.3, 9.2, 9.3, 9.3.1, 9.8, 11.5.1, A.1. Style change. Index added. |

# Contents

| 1. GLINT 500TX Functional Overview                  | . 1 |

|-----------------------------------------------------|-----|

| 1.1 Introduction                                    | . 1 |

| 1.2 Notation                                        | . 1 |

| 1.3 GLINT 500TX Graphics Core                       | . 2 |

| 1.4 PCI Interface                                   | . 2 |

| 1.5 Big-endian Processor Support                    |     |

| 1.6 Localbuffer Memory Interface                    |     |

| 1.7 Framebuffer Memory Interface                    |     |

| 1.8 Shared Framebuffer/Shared Localbuffer Interface |     |

| 1.9 Video Timing Generation                         |     |

| 1.10 External Video Logic Interface                 |     |

| 1.11 Reset Configuration Control                    |     |

| 1.12 Expansion EPROM support                        |     |

|                                                     |     |

| 2. PCI Configuration Region                         | . 5 |

| 2.1 Device Identification                           | . 6 |

| 2.2 Device Control                                  |     |

| 2.3 Device Status                                   | . 9 |

| 2.4 Miscellaneous Functions                         | 10  |

| 2.5 Base 12                                         |     |

| 2.6 Expansion ROM Interface                         | 16  |

| 3. Region 0 - Control Registers                     | 17  |

| 3.1 Region 0 Address Map                            | 17  |

| 3.2 Localbuffer Registers                           |     |

| 3.3 Framebuffer Registers                           | 35  |

| 3.4 Graphics Core Registers                         |     |

| 3.5 Graphics Core FIFO Interface                    | 43  |

| 4. Internal Video Timing Generator                  | 44  |

| 4.1 Overview of Internal VTG features               | 44  |

| 4.2 Internal VTG Register Set                       |     |

| 4.3 VTG Configuration                               |     |

| 4.4 VRAM Serial Port Control                        |     |

| 4.5 VTG Example                                     |     |

| 5. External Video Control Registers                 | 64  |

| 5.1 External Video Interface Signal Definitions     | 64  |

| 5.2 LUT-DAC Interface.                              |     |

| 5.3 Resetting External Circuitry                    |     |

| 6. Localbuffer                                      |     |

| 6.1 Configurations - DRAM Types.                    |     |

| o.i Comiguations Divitivi Types                     | υU  |

| 6.2 PCI Region 1 and Region 3 Address Map         |     |

|---------------------------------------------------|-----|

| 6.3 Localbuffer Memory Types                      |     |

| 6.4 Localbuffer Example Configuration             |     |

| 6.5 Shared Localbuffer                            |     |

| 7. Framebuffer                                    | 70  |

| 7.1 Configurations - VRAM Types and Features      |     |

| 7.2 PCI Region 2 and Region 4 Address Map         |     |

| 7.3 Shared Framebuffer/Shared Memory Interface    |     |

| 7.4 Framebuffer Timing                            |     |

| 7.5 VRAM Requirements                             |     |

| 7.6 External Timing Generator                     |     |

| 7.7 Framebuffer Configurations                    |     |

| 8. GLINT 500TX Register Set                       | 80  |

| 9. Electrical Data                                | 00  |

|                                                   |     |

| 9.1 Absolute Minimum/Maximum Ratings              |     |

| 9.2 DC Specifications                             |     |

| 9.3 AC Specifications                             | 84  |

| 10. Pin Information.                              | 105 |

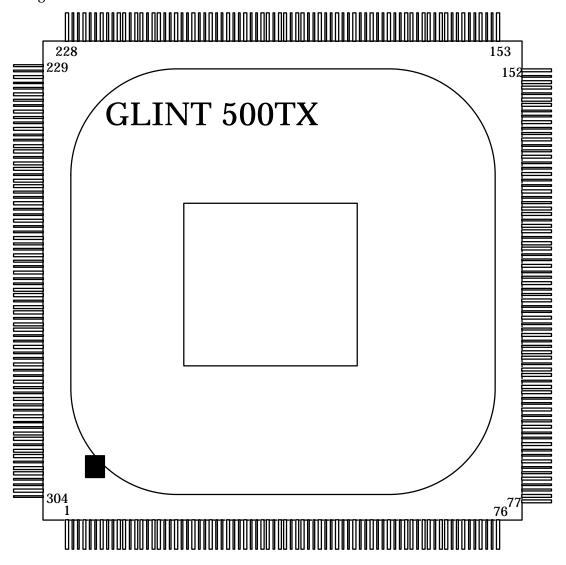

| 10.1 Package Pinout                               | 105 |

| 10.2 Pin Descriptions                             |     |

| 10.3 Pin Lists.                                   | 110 |

| 11. Thermal Management                            | 116 |

| 11.1 Device Characteristics                       | 116 |

| 11.2 Thermal Model                                |     |

| 11.3 Operation Without Heatsink                   |     |

| 11.4 Operation With Heatsink                      |     |

| 11.5 Heatsink Attachment                          |     |

| 12. Reset Control and Test Mode                   | 119 |

| 12.1 Reset                                        | 110 |

| 12.2 Clock Operation at Reset                     |     |

| 12.3 Reset Localbuffer Configuration              |     |

| 12.4 Reset Framebuffer Configuration              |     |

| 12.5 Production Test Mode                         |     |

| 13. Package Dimensions                            | 125 |

|                                                   |     |

| App. A GLINT 300SX and 500TX Hardware Differences | 126 |

| Index                                             | 199 |

| Tables      |                                                       |   |

|-------------|-------------------------------------------------------|---|

| Table 1-1.  | Localbuffer DRAM Types                                | 3 |

| Table 1-2.  | Maximum Pixel Clock Support                           |   |

| Table 1-3.  | PCI Address Regions                                   |   |

| Table 2-1.  | Configuration Region.                                 |   |

| Table 2-2.  | Expansion ROM Connections                             |   |

| Table 4.1.  | Options For Serial Port Control                       |   |

| Table 5-1.  | External Video Signals                                |   |

| Table 6-1.  | Localbuffer Sizes With 4Mbit Technology Memories      |   |

| Table 6-2.  | Localbuffer Sizes With 16Mbit Technology Memories     |   |

| Table 6-3.  | Localbuffer Field Sizes.                              |   |

| Table 6-4.  | Localbuffer Visible Bypass Memory                     |   |

| Table 7-1.  | Framebuffer Configurations                            |   |

| Table 7-2.  | Framebuffer Pixel Packing                             |   |

| Table 7-3.  | Framebuffer Visible Bypass Memory                     |   |

| Table 7-4.  | Shared Memory Configuration                           |   |

| Table 7-5.  | Primary Controller Signals                            |   |

| Table 7-6.  | Secondary Controller Signals                          |   |

| Table 7-7.  | Timing Generator Pins                                 |   |

| Table 7-8.  | Framebuffer Addressing in Dual-CAS Mode               |   |

| Table 8-1.  | GLINT 500TX Configuration Region Registers            |   |

| Table 8-2.  | GLINT 500TX Region 0 Registers                        |   |

| Table 9-1   | Absolute Minimum/Maximum Ratings                      |   |

| Table 9-2   | DC Specifications                                     |   |

| Table 9-3   | PCI Signal DC Specifications                          |   |

| Table 9-4   | Non PCI Signal DC Specifications                      |   |

| Table 9-5   | Test Loads For AC Timing                              |   |

| Table 9-6   | Clock Waveform Timing                                 |   |

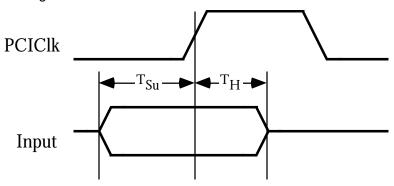

| Table 9-7   | PCIClk Referenced Input Timing                        |   |

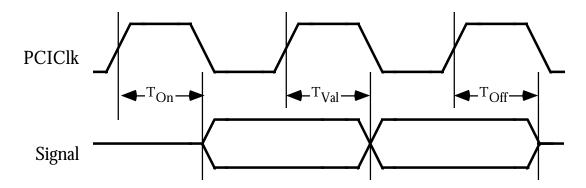

| Table 9-8   | PCIClk Referenced Output Timing                       |   |

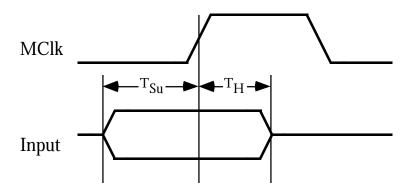

| Table 9-9   | MClk Referenced Input Timing                          |   |

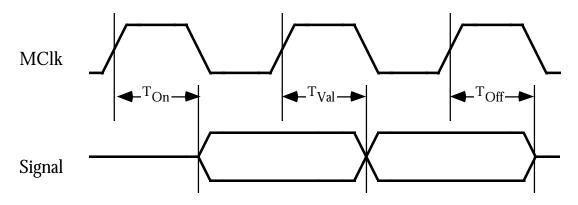

| Table 9-10  | MClk Referenced Output Timing                         |   |

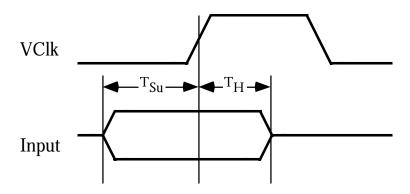

| Table 9-11  | VClk Referenced Input Timing                          |   |

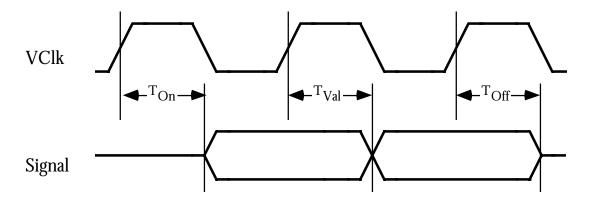

|             | VClk Referenced Output Timing                         |   |

| Table 9-13  | Framebuffer Timing                                    |   |

|             | VRAM Access Time Requirements                         |   |

| Table 9-15  | Localbuffer Timing - Fast-page mode                   |   |

| Table 9-16. | Localbuffer Access Time Requirements - Fast Page Mode |   |

|             | Localbuffer Timing - EDO mode                         |   |

|             | Localbuffer Access Time Requirements - EDO Mode       |   |

|             | ROM Read Timings.                                     |   |

|             | ROM Access Times.                                     |   |

|             | LUT-DAC Timings                                       |   |

|             | LUT-DAC Access Times.                                 |   |

|             | Pin Descriptions                                      |   |

| Table 10-2. | Alphabetical Pin Listing                     | 110 |

|-------------|----------------------------------------------|-----|

|             | Numerical Pin Listing                        |     |

|             | 304 pin CQFP Package Thermal Characteristics |     |

|             | GLINT 500TX Functional Mode                  |     |

| Table 12-2. | GLINT 500TX Board ATE Mode                   | 124 |

| Table 13-1. | 304 pin CQFP Package Dimensions              | 125 |

| Table A-1.  | Shared Framebuffer and Localbuffer Options   | 126 |

| Table A-2   | Extended Pin Functionality                   | 128 |

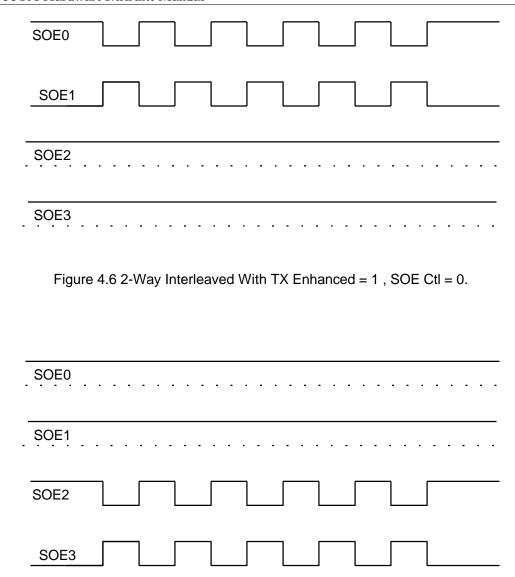

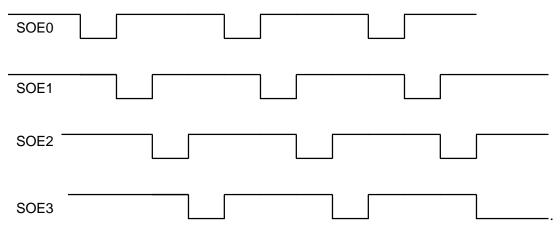

#### **Figures** Figure 1-1 Figure 2-1 Figure 3-1. Figure 4-1. Figure 4-2. Horizontal Timing.......54 Figure 4-3. Figure 4.4 Serial Control of 1-Way interleaved Display...... 58 2-Way Or 4-Way interleaved Serial Port With 64bit RAMDAC................ 59 Figure 4.5 2-Way Interleaved With TX Enhanced = 1, SOE Ctl = 0. ..... 60 Figure 4.6 2-Way Interleaved With TX Enhanced = 1, SOE Ctl = 1......60 Figure 4.7 4-Way interleaved Serial Port. 61 Figure 4.8 Figure 5-1 Figure 6-1 Figure 7-1 Figure 7-2 Figure 7-3 Figure 7-4. Figure 7-5 Figure 7-6 Figure 9-1 Figure 9-2 Figure 9-3 PCIClk Referenced Output Timing ...... 87 Figure 9-4 Figure 9-5 Figure 9-6 Figure 9-7 Figure 9-8 Figure 9-9

## GLINT 500TX Functional Overview

## 1.1 Introduction

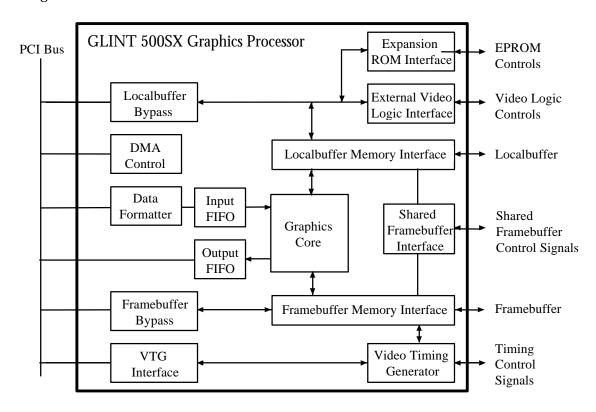

The GLINT 500TX high performance graphics processor combines workstation class 3D graphics acceleration and state of the art 2D performance in a single chip. All 3D rendering operations are accelerated by the GLINT 500TX, including Gouraud shading, texture mapping, depth buffering, antialiasing and alpha blending.

Implemented around a scaleable memory architecture, the GLINT 500TX reduces the cost and complexity of delivering high performance 3D graphics within a windowing environment - making it ideal for a wide range of graphics products from PC boards to high end workstation accelerators.

Figure 1-1 GLINT 500TX Functional Units

#### 1.2 Notation

The following notational conventions are used in this book.

A signal name ending in N indicates an active low signal, e.g. PCIFrameN.

n-m indicates a bit field from bit n to bit m, e.g. 7-0 specifies bits 7 through 0 inclusive.

Use of the letter h indicates a hexadecimal number, e.g. 6Fh is a hexadecimal number.

Use of the letter b indicates a binary number, e.g. 1010b is a binary number.

Use of the letter X indicates that a value is undefined, e.g. XXXh is a undefined hexadecimal number.

#### 1.3 GLINT 500TX Graphics Core

The Graphics Core (GC) in the GLINT 500TX accelerates the key operations for 3D and 2D applications. For further information on the functionality of the GC refer to the GLINT 500TX Programmers Reference Manual.

#### 1.4 PCI Interface

The PCI interface conforms to the PCI Local Bus standard Revision 2.1. The GLINT 500TX is a PCI Local Bus Target and a PCI Local Bus Read Master.

The host interface includes the configuration registers, the GLINT 500TX control registers, and two bypass paths: one to the Localbuffer memory and one to the Framebuffer memory.

The PCI interface has an input FIFO for passing data to the Graphics Core, and an output FIFO for buffering up data to be read from the Graphics Core. The input FIFO is 32 words deep. The output FIFO is 8 words deep.

A DMA controller is provided in the PCI interface to allow the GLINT 500TX to read data directly into the Graphics Core input FIFO.

## 1.5 Big-endian Processor Support

The GLINT 500TX provides support for big-endian processors. A big-endian processor will generate byte swapped big-endian data on the PCI local bus, commonly known as gib-endian.

All the regions on the GLINT 500TX can accept gib-endian data. The configuration space is set by a control pin at reset time and the GLINT 500TX control registers are always visible little and gib-endian.

The Localbuffer and Framebuffer each have two PCI apertures whose endian is programmable.

## 1.6 Localbuffer Memory Interface

The Localbuffer memory is used to store off screen pixel associated information. This includes Depth (Z), Stencil, and texture data.

The Localbuffer consists of one or two banks of DRAM giving from 2 to 48 Mbytes of storage. A Localbuffer width of 0 to 48 bits is supported. The number of bits populated in any hardware implementation will depend on software requirements. The memory control signals are programmable to allow for optimum operation at different GLINT 500TX clock speeds with memory systems using -50 to -80 speed DRAM parts. Page sizes from 256 to 2048 are supported. EDO DRAM is also supported.

The Localbuffer interface provides a link to the PCI Local Bus to allow host accesses to bypass the Graphics Core.

Table 1-1. Localbuffer DRAM Types

| DRAM Generic types |

|--------------------|

| 256K x 16/18       |

| 512k x8/9          |

| 1M x 4             |

| 1M x 16/18         |

| 2M x 8/9           |

| 4M x 4             |

DRAMs used must support fast page-mode or Extended-DataOut and CAS-BEFORE-RAS refresh.

## 1.7 Framebuffer Memory Interface

The GLINT 500TX can address a Framebuffer of between 2MByte and 32MBytes of VRAM. A Framebuffer data width of 64 bits is supported. The VRAMs supported include 256kx4, 256kx8 and 256kx16. The VRAMs must support split transfer cycles.

The memory control signals are programmable to allow for optimum operation at different GLINT 500TX clock speeds with a range of memory speeds allowing -60 to -80 VRAMs to be used. The GLINT 500TX can make use of VRAM write masks and block fill mode, if available, to improve performance.

LUT-DACs with 64 and 128 bit pixel buses are supported. For more information on LUT-DAC support refer to External Video Control (Section 5).

GLINT 500TX interfaces directly to most Framebuffers, however Framebuffers with greater than 16 memory parts require external buffering of the address and control lines.

The Framebuffer interface also provides a link to the PCI Local Bus to allow host accesses to bypass the Graphics Core.

The GLINT 500TX supports 32, 16, and 8 bit packed framestores.

#### 1.8 Shared Framebuffer/Shared Localbuffer Interface

The GLINT 500TX provides a mechanism to share the Framebuffer and/or the Localbuffer with another device. The GLINT 500TX can be programmed to either perform the sharing arbitration (primary controller) or act as a slave (secondary controller).

## 1.9 Video Timing Generation

The GLINT 500TX has an internal timing generator and VRAM transfer controller for simple Framebuffer configurations. For more complex configurations an external timing generator and transfer controller is required.

The maximum video clock (VClk) for the GLINT 500TX is 80MHz. The video clock is derived from the video output pixel clock. The pixel clock is divided by the number of serial port interleaved banks. So if the pixel clock is 135MHz and there are 4 serial port interleaved banks, the video clock to the GLINT 500TX will be clocked at 33.75MHz.

Maximum GLINT 500TX video clock rates (assuming 50MHz VRAMs) are shown in table 1-2.

Table 1-2. Maximum Pixel Clock Support

| Pixel Width | Serial Interleave | Maximum Pixel |

|-------------|-------------------|---------------|

|             |                   | Frequency     |

| 32 bit      | 4                 | 200MHz        |

| 16 bit      | 8                 | 400MHz        |

| 8 bit       | 16                | 800MHz        |

## 1.10 External Video Logic Interface

The GLINT 500TX can control external video logic such as the video output LUT-DAC. The address and data lines for the control come from the Localbuffer interface. Control signals are provided to allow standard LUT-DACs to be connected directly to the GLINT 500TX. Some LUT-DACs will require a small amount of glue logic.

## 1.11 Reset Configuration Control

A number of parameters for the GLINT 500TX are set at reset time, such as Localbuffer and Framebuffer memory size and speed. The reset state is configured with resistors connected to the Localbuffer data pins. The state of the data pins is sampled on the rising edge of the reset line. See Reset Control (Section 12) for more details.

## 1.12 Expansion EPROM support

The GLINT 500TX supports an expansion EPROM. This EPROM may store code needed for device-specific initialization and expansion of the boot time code.

#### 1.13 GLINT 500TX Address Map

The GLINT 500TX has six PCI base address regions:

Table 1-3. PCI Address Regions

| Region        | Description                             |

|---------------|-----------------------------------------|

| Configuration | PCI configuration region                |

| 0             | GC control region                       |

| 1             | Aperture 0 access to Localbuffer memory |

| 2             | Aperture 0 access to Framebuffer memory |

| 3             | Aperture 1 access to Localbuffer memory |

| 4             | Aperture 1 access to Framebuffer memory |

| ROM           | Expansion ROM                           |

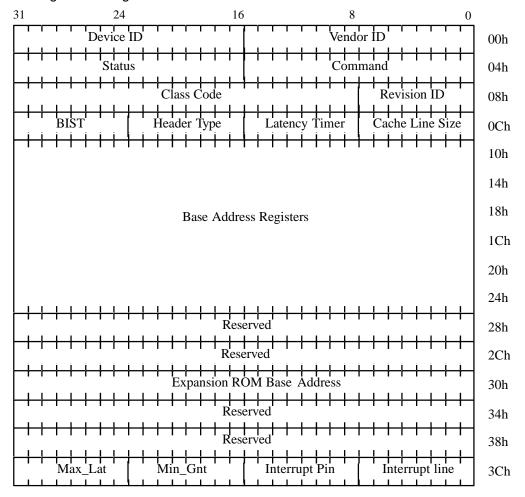

## 2. PCI Configuration Region

The PCI Configuration Region provides at set of 'hooks' which satisfies the needs of current and anticipated system configuration mechanisms. The configuration registers are accessed and modified by the use of Configuration Read and Write commands.

Sixty four bytes of the Configuration registers are predefined within the PCI Specification and are supported by the GLINT 500TX. The remaining 192 Bytes are device specific and are unused by the GLINT 500TX.

Table 2-1. Configuration Region.

#### 2.1 Device Identification

#### 2.1.1 Vendor ID

Vendor identification number.

## **CFGVendorId**

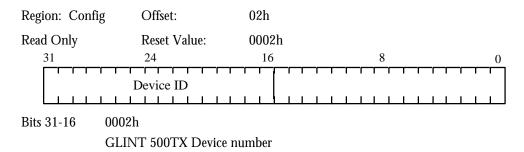

#### 2.1.2 Device ID

Device identification number.

## **CFGDeviceId**

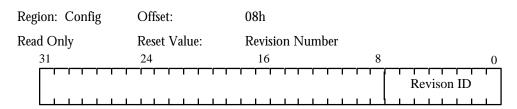

#### 2.1.3 Revision ID

Revision identification number.

## **CFGRevisionId**

The revision ID register returns the following code:

Bits 7 - 0 Revision

$$01h = Revision R01$$

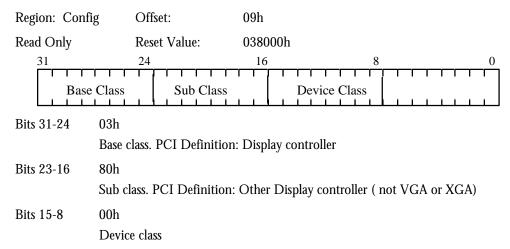

## 2.1.4 Class Code Register

## **CFGClassCode**

NB. Some operating systems may expect a device of Class 03h 80h to contain a VGA device and fail to boot correctly if no VGA device is present. The GLINT 500TX has no in-built VGA and hence this problem may occur. To avoid this problem setting the 'Base Class Zero' field of the FBMemControl register using a configuration resistor causes the Class Code register to return 00h 00h (Backward Compatibility Class). - see section 3.3.1

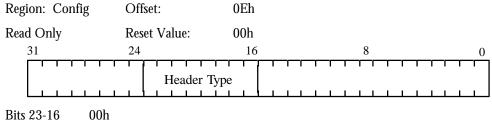

## 2.1.5 Header Type

# **CFGHeaderType**

Header Type. PCI Definition: Single function device

#### 2.2 Device Control

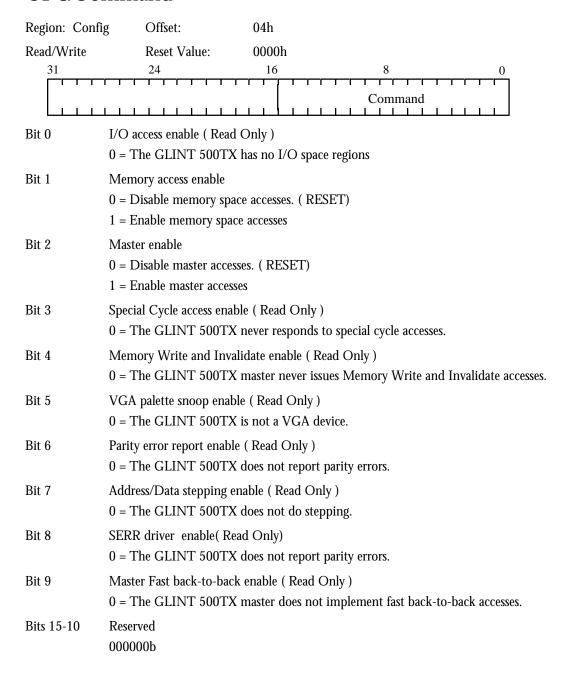

## 2.2.1 Command Register

The command register provides control over a device's ability to generate and respond to PCI cycles. Writing zero to this register disconnects the device from the PCI for all except configuration accesses. All necessary bits within the command register are supported for the functionality contained in the GLINT 500TX.

## **CFGCommand**

#### 2.3 Device Status

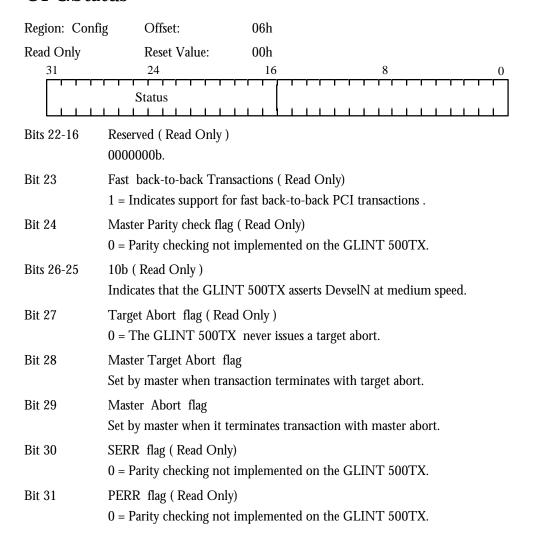

## 2.3.1 Status Register

The Status Register is used to record status information for PCI related events. The definition for each bit is given below.

Reads to this register behave normally. Writes function differently in that bits can be reset but not set. A bit is reset whenever the register is written and the data in the corresponding bit location is a 1.

## **CFGStatus**

#### 2.4 Miscellaneous Functions

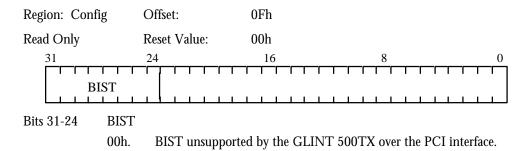

#### 2.4.1 BIST

Optional register used for control and status of BIST.

## **CFGBist**

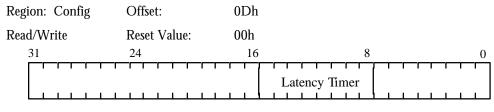

## 2.4.2 Latency Timer

This register specifies, in PCI bus clocks, the value of the Latency Timer for this PCI bus master.

## **CFGLatTimer**

Bits 15-8 Latency Timer Count

Sets the maximum number of PCI clock cycles for master burst accesses.

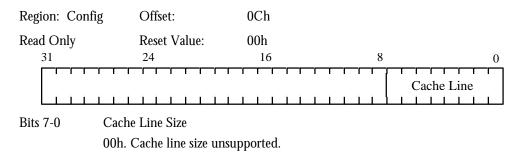

#### 2.4.3 Cache Line Size

This register specifies the cache line size in units of 32 bit words. It is only implemented for masters which use the 'Memory write and invalidate' command. The GLINT 500TX does not use this command.

## **CFGCacheLine**

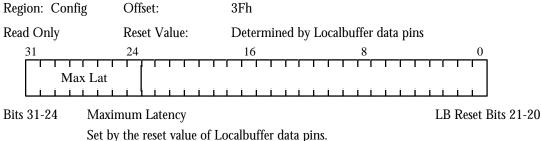

## 2.4.4 Maximum Latency

This register specifies how often the PCI device needs to gain access to the PCI bus.

## **CFGMaxLat**

Set by the reset value of Localbuffer data pins. Possible values are: 00h, 40h, 80h, and C0h.

#### 2.4.5 Minimum Grant

This register specifies the duration of a burst period required by the PCI device.

## **CFGMinGrant**

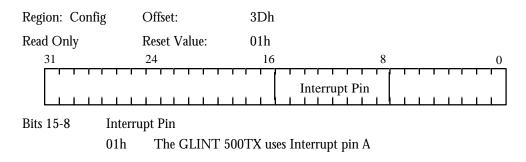

#### 2.4.6 Interrupt Pin

The Interrupt Pin register tells the BIOS which interrupt line is used by the GLINT 500TX.

# **CFGIntPin**

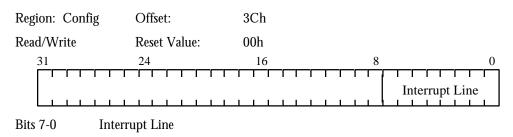

#### 2.4.7 Interrupt Line

The Interrupt Line register is an 8 bit register used to communicate interrupt line routing information.

## **CFGIntLine**

#### 2.5 Base

The base address registers allow the boot software to relocate PCI devices in the address spaces. At system power-up device independent software must be able to determine what devices are present, build a consistent address map, and determine if a device has an expansion ROM.

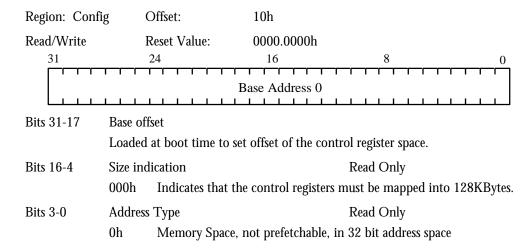

## 2.5.1 Base Address 0 Register

The Base Address 0 Register contains the GLINT 500TX control space offset. The control registers are in memory space. They are not prefetchable and can be located anywhere in 32 bit address space.

## CFGBaseAddr0

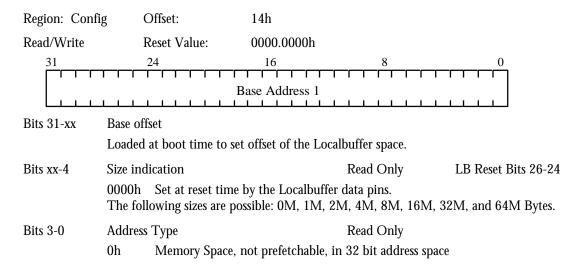

#### 2.5.2 Base Address 1 Register

The Base Address 1 Register contains the GLINT 500TX aperture 0 Localbuffer offset. The Localbuffer is in memory space. It is not prefetchable and can be located anywhere in 32 bit address space.

## CFGBaseAddr1

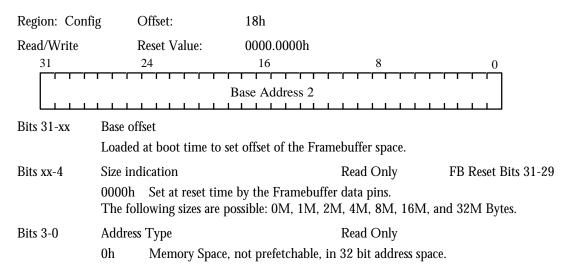

## 2.5.3 Base Address 2 Register

The Base Address 1 register contains the GLINT 500TX aperture 0 Framebuffer offset. The Framebuffer is in memory space. It is not prefetchable and can be located anywhere in 32 bit address space.

# CFGBaseAddr2

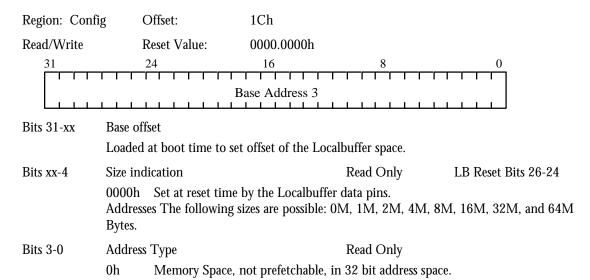

## 2.5.4 Base Address 3 Register

The Base Address 3 Register contains the GLINT 500TX aperture 1 Localbuffer offset. Aperture 1 is always the same size as aperture 0.

## CFGBaseAddr3

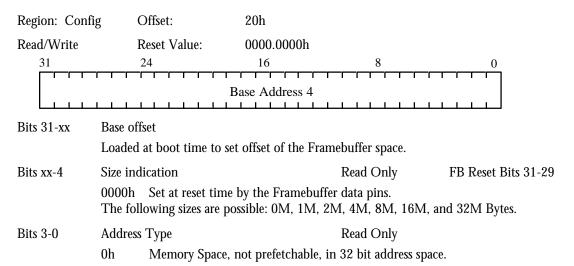

## 2.5.5 Base Address 4 Register

The Base Address 4 register contains the GLINT 500TX aperture 1 Framebuffer offset. Aperture 1 is always the same size as aperture 0.

## CFGBaseAddr4

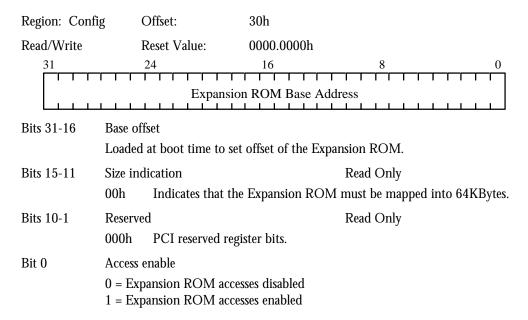

## 2.5.6 Expansion ROM Base Address

The Expansion ROM Base register is the offset address for the expansion ROM. The ROM is in memory space.

## **CFGRomAddr**

## 2.6 Expansion ROM Interface

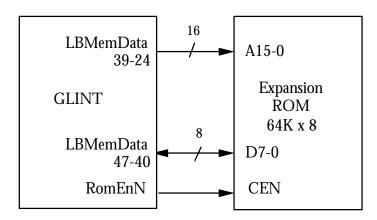

A 64K x 8 bit interface is provided for an expansion ROM. This interface is read only from the PCI .The address and data lines share pins with the Localbuffer data bus as defined in table 2-2.

Table 2-2. Expansion ROM Connections

| Signal        | Pins used        | Description                                 |

|---------------|------------------|---------------------------------------------|

| RomAddr(15-0) | LBMemData(39-24) | Expansion ROM Address lines.                |

| RomData(7-0)  | LBMemData(47-40) | Expansion ROM Data bus.                     |

| RomEnN        | RomEnN           | Expansion ROM read strobe (negative active) |

Figure 2-1 Expansion ROM interface

## 3. Region 0 - Control Registers

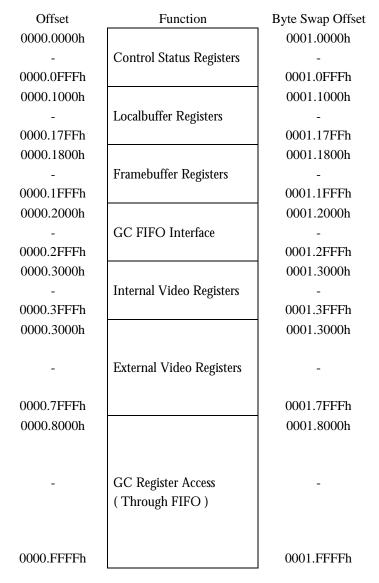

## 3.1 Region 0 Address Map

The GLINT 500TX region 0 is a 128KByte region containing the control registers and ports to and from the Graphics Core.

The control space is mapped in twice in the 128KByte region. In the second 64K the registers are mapped to be byte swapped for big endian hosts.

Figure 3-1. Region 0 Address Map

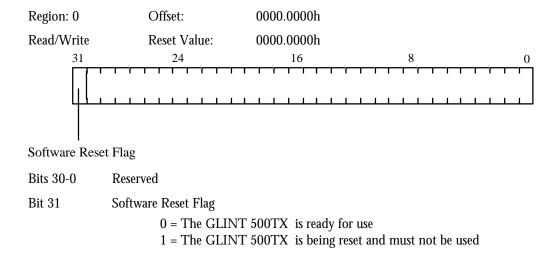

## 3.1.1 Reset Status Register

Writing to the reset status register forces a software reset of the GLINT 500TX Graphics Core. The software reset does not reset the PCI interface. It is provided for software diagnostics in case an incorrect register set up locks up the internal GC.

The software reset takes a number of cycles and the GC must not be used during the reset. A flag in the register is provided which shows that the software reset is still in progress.

For more information on the operation of the GLINT 500TX at reset please refer to Reset Control (Section 12).

## ResetStatus

## 3.1.2 Interrupt Enable Register

The Interrupt Enable Register allows for a number of GLINT 500TX flags to generate a PCI interrupt. Five interrupt sources are defined below. At reset all interrupts sources are disabled.

## IntEnable

Bit 0 DMA interrupt enable

0 = Disable interrupt (RESET)

1 = Enable interrupt

Bit 1 Sync interrupt enable

0 = Disable interrupt (RESET)

1 = Enable interrupt

Bit 2 External interrupt enable

0 = Disable interrupt (RESET)

1 = Enable interrupt

Bit 3 Error interrupt enable

0 = Disable interrupt (RESET)

1 = Enable interrupt

Bit 4 Vertical retrace interrupt enable

0 = Disable interrupt (RESET)

1 = Enable interrupt

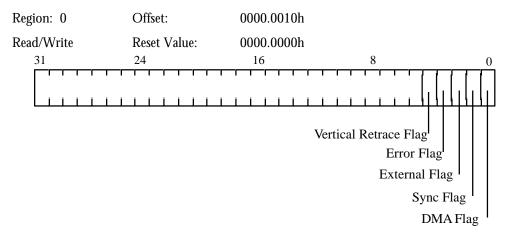

## 3.1.3 Interrupt Flags Register

The Interrupt Flags Register shows which interrupts are outstanding on the GLINT 500TX.

Flag bits are reset by writing to this register with the corresponding bit set to a 1. Flags at positions where the bits are set to 0 will be unaffected by the write.

# **IntFlags**

Bit 0 DMA Flag

0 = No interrupt (RESET)

1 = Interrupt outstanding

Bit 1 Sync Flag

0 = No interrupt (RESET)

1 = Interrupt outstanding

Bit 2 External Flag

0 = No interrupt (RESET)

1 = Interrupt outstanding

Bit 3 Error Flag

0 = No interrupt (RESET)

1 = Interrupt outstanding

Bit 4 Vertical Retrace Flag

0 = No interrupt (RESET)

1 = Interrupt outstanding

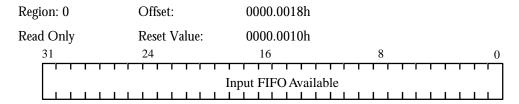

## 3.1.4 Input FIFO Space Register

The input FIFO space register indicates the number of words that can currently be written to the input FIFO. This register can be read at any time and used to allow the controlling software to efficiently send data to the GLINT 500TX. If the DMA controller for the FIFO is in use, the value read is a snapshot of the current FIFO status.

# **InFIFOSpace**

#### Bits 31-0 Input FIFO Space

Valid range: 0 to 16.

The number of empty words in the input FIFO. This number of words can be written before checking again for FIFO space availability. Although the input FIFO is 32 words deep, the maximum Input FIFO space returned is 16 for compatibility with GLINT 300SX.

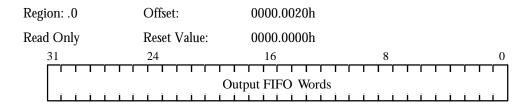

## 3.1.5 Output FIFO Words Register

The output FIFO words register indicates the number of words currently in the output FIFO. This register can be read at any time and used to allow the controlling software to efficiently read output data from the GLINT 500TX.

## **OutFIFOWords**

#### Bits 31-0 Output FIFO Words

Valid range: 0 to 8.

The number of valid words in the output FIFO. This number of words can be read before checking for more words.

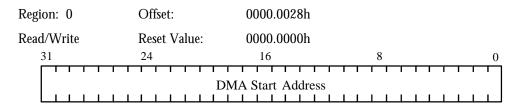

#### 3.1.6 DMA Start Address

The DMA address should be loaded with the first PCI address for the buffer to be transferred to the GC when using the DMA controller.

Writing to the DMA start address register loads the address into the DMA address counter. Once a DMA has been set off the next DMA start address may be loaded. A read of this register returns the last start value loaded even if the DMA is underway.

## **DMAAddress**

Bits 31-0 DMA Start Address

PCI start address for PCI master read transfer to the Graphics Core.

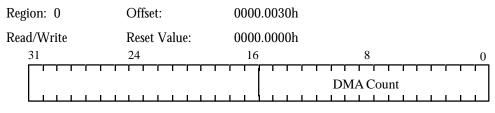

#### 3.1.7 DMA Count

The DMA count register should be loaded with the number of words to be transferred in the DMA operation. The action of loading a word count greater than zero sets off the DMA operation. The value read back from this register indicates the current number of words left to be transferred.

This register should only be written to if the count is zero. It can be read at any time.

## **DMACount**

Bits 15-0 DMA Count

Valid Range: 0 to 65535

Number of words to be transferred in DMA operation.

Undefined action if this register is written to when it is not zero.

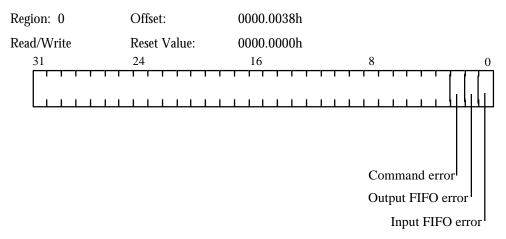

## 3.1.8 Error Flags Register

The Error Flags Register shows which errors are outstanding on the GLINT 500TX.

Flag bits are reset by writing to this register with the corresponding bit set to a 1. Flags at positions where the bits are set to 0 will be unaffected by the write.

## **ErrorFlags**

Bit 0 Input FIFO Error Flag

Flag set on write to full input FIFO

0 = No error (RESET)

1 = Error outstanding

Bit 1 Output FIFO Error Flag

Flag set on read from empty output FIFO

0 = No error (RESET)

1 = Error outstanding

Bit 2 Command Error Flag

Flag set on incorrect mixing of accesses to the input FIFO space and the GC register space

0 = No error (RESET)

1 = Error outstanding

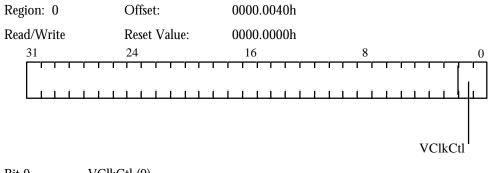

## 3.1.9 Video Clock Control Register

The video clock control Register drives two physical pins on the GLINT 500TX. These pins are used to program the video clock PLL chip.

# **VClkCtl**

Bit 0 VClkCtl (0)

Bit 1 VClkCtl (1)

## 3.1.10 Test Register

The test register is not to be used by any user software. Writes to this register have an undefined effect.

The GLINT 500TX powers up in functional mode.

# TestRegister

| Bit 0  | Rasterizer        |

|--------|-------------------|

| Bit 1  | Scissor Stipple   |

| Bit 2  | Color DDA         |

| Bit 3  | Fog               |

| Bit 4  | Alpha test        |

| Bit 5  | LB read           |

| Bit 6  | GID Stencil Depth |

| Bit 7  | LB write          |

| Bit 8  | FB read           |

| Bit 9  | Alpha blend       |

| Bit 10 | Dither            |

| Bit 11 | Logicops          |

| Bit 12 | FB Write          |

| Bit 13 | Host out          |

| Bit 14 | Texture Address   |

| Bit 15 | Texture Read      |

| Bit 16 | Texture Color     |

| Bit 17 | Router            |

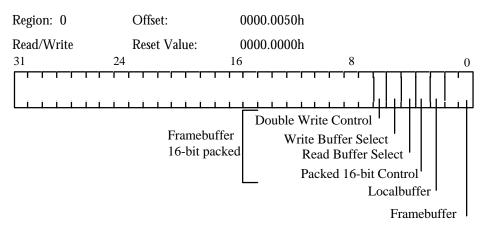

## 3.1.11 Aperture 0 Control Register

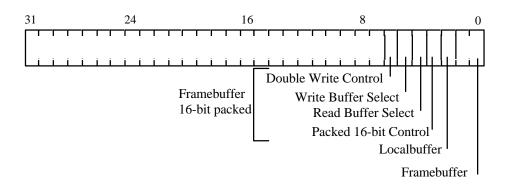

The aperture 0 control Register sets up the data transfer modes for the Localbuffer visible in region 1 and the Framebuffer in region 2.

The Localbuffer can be set to be byte swapped for big endian hosts.

The Framebuffer can be set to be byte swapped and half word swapped for big endian hosts.

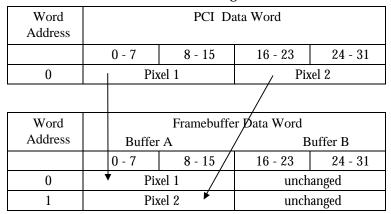

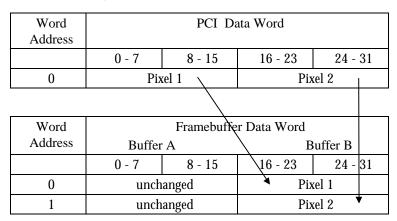

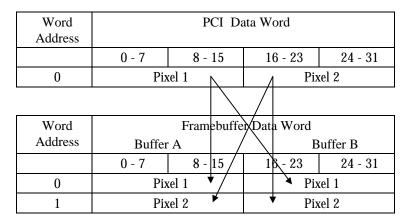

The Framebuffer can be used in a mode whereby two 16-bit buffers (A and B) are interleaved together on a per-pixel basis. Each 32bit word contains a 16 bit pixel from buffer A and the equivalent pixel from buffer B. Control bits are provided to allow reading and writing of Buffers A and B as contiguous 16-bit packed buffers, despite their being pixel-interleaved within memory. Each 32-bit read or write access over the PCI bus thus transfers two 16-bit pixels to either Buffer A or Buffer B as selected by the fields below.

# Aperture0

| Bits 1-0 | Framebuffer Byte Control                                  |

|----------|-----------------------------------------------------------|

|          | 0 = Standard<br>1 = Byte Swapped<br>2 = Half Word Swapped |

|          | 3 = Reserved                                              |

| Bit 2    | Localbuffer Byte control                                  |

|          | 0 = Standard<br>1 = Byte Swapped                          |

| Bit 3    | Packed 16-bit (1:5:5:5) Framebuffer Control               |

|          | Turns on 16-bit packed accesses.                          |

|          | 0 = disable packed 16-bit framebuffer                     |

|          | 1 = enable packed 16-bit framebuffer                      |

| Bit 4    | Packed 16-bit Read Buffer Select                          |

|          | 0 = select Buffer A for read accesses                     |

|          | 1 = select Buffer B for read accesses                     |

Bit 5 Packed 16-bit Write Buffer Select

0 = select Buffer A for write accesses1 = select Buffer B for write accesses

Bit 6 Packed 16-bit Double Write Control

Allows a write access to be performed to both Buffer A and Buffer B simultaneously.

0 = disable double writes

1 = enable double writes

## 3.1.12 Aperture 1 Control Register

The aperture 1 control Register sets up the data transfer modes for the Localbuffer visible in region 3 and the Framebuffer in region 4.

The Localbuffer can be set to be byte swapped for big endian hosts.

The Framebuffer can be set to be byte swapped and half word swapped for big endian hosts.

The Framebuffer can be used in a mode whereby two 16-bit buffers (A and B) are interleaved together on a per-pixel basis. Each 32bit word contains a 16 bit pixel from buffer A and the equivalent pixel from buffer B. Control bits are provided to allow reading and writing of Buffers A and B as contiguous 16-bit packed buffers, despite their being pixel-interleaved within memory. Each 32-bit read or write access over the PCI bus thus transfers two 16-bit pixels to either Buffer A or Buffer B as selected by the fields below.

## Aperture1

Region: 0 Offset: 0000.0058h Read/Write Reset Value: 0000.0000h

Bits 1-0 Framebuffer Byte Control

0 = Standard

1 = Byte Swapped

2 = Half Word Swapped

3 = Reserved

Bit 2 Localbuffer Byte control

0 = Standard

1 = Byte Swapped

Bit 3 Packed 16-bit (1:5:5:5) Framebuffer Control

Turns on 16-bit packed accesses.

0 = disable packed 16-bit framebuffer

1 = enable packed 16-bit framebuffer

Bit 4 Packed 16-bit Read Buffer Select

0 = select Buffer A for read accesses

1 = select Buffer B for read accesses

Bit 5 Packed 16-bit Write Buffer Select

0 = select Buffer A for write accesses1 = select Buffer B for write accesses

Bit 6 Packed 16-bit Double Write Control

Allows a write access to be performed to both Buffer A and Buffer B simultaneously.

0 = disable double writes1 = enable double writes

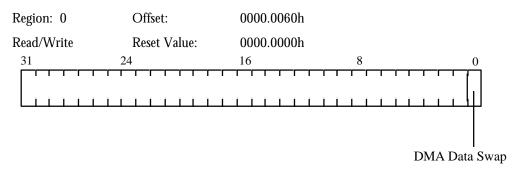

### 3.1.13 DMA Control Register

The DMA control Register sets up the data transfer modes for the DMA controller. Data transfer can be set to byte swapped for big endian hosts.

## **DMAControl**

Bit 0 DMA Byte Swap Control

0 = Standard

1 = Byte Swapped

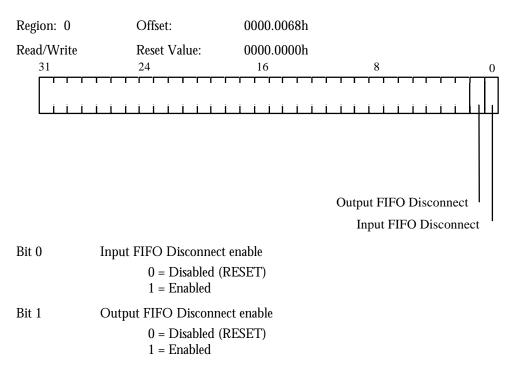

### 3.1.14 FIFO Disconnect Register

The FIFO Disconnect Register enables input FIFO and output FIFO disconnect on the GLINT 500TX.

Input FIFO and Output FIFO Disconnect are disabled at reset.

## **FIFODis**

N.B. If a GLINT Delta is used with the GLINT 500TX, then the Input FIFO Disconnect must always be enabled on the GLINT 500TX

#### 3.2 Localbuffer Registers

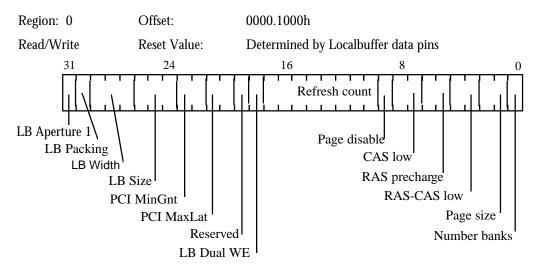

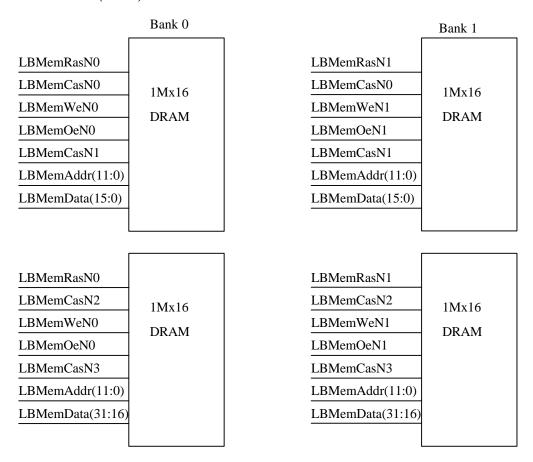

#### 3.2.1 Localbuffer Memory Control

The Localbuffer memory control register sets the characteristics of the Localbuffer DRAM. The register is initialized at reset time by setting values on Localbuffer data pins (see Reset Control, Section 12). Care must be taken when modifying this register to ensure that the DRAM will function within its worst case timings.

# LBMemoryCtl

Bit 0 Number of banks

LB Reset Bit 0

Defines the number of banks of CAS interleaved memory in the localbuffer.

0 = 1 bank

1 = 2 banks

Bits 2-1 Page size

LB Reset Bits 2-1

Defines the page size of the DRAM of the memory in the localbuffer. If there are 2 banks of memory, the effective page size is twice this value.

0 = 256 pixels

1 = 512 pixels

2 = 1024 pixels

3 = 2048 pixels

Bits 4-3 RAS-CAS low

LB Reset Bits 4-3

Defines the number of MClks that RAS is asserted before CAS is asserted during a memory access.

0 = 2 clocks

1 = 3 clocks

2 = 4 clocks

3 = 5 clocks

Bits 6-5 **RAS Precharge** LB Reset Bits 6-5 Defines the RAS Precharge time in terms of MClk periods. 0 = 2 clocks 1 = 3 clocks 2 = 4 clocks 3 = 5 clocks Bits 8-7 CAS low LB Reset Bits 8-7 Defines the CAS low time during a localbuffer access in terms of MClk periods. 0 = 1 clock 1 = 2 clocks 2 = 3 clocks 3 = 4 clocks Bit 9 LB Reset Bit 9 Page mode disable Asserting this bit will cause all localbuffer accesses to perform a full DRAM memory cycle. i.e. Fast Page mode is never used. 0 = Page mode enabled 1 = Page mode disabled Bits 17-10 Refresh count This field can be used to optimize the DRAM refresh period to the system MClk and the DRAM used for the localbuffer. The refresh period is the value of this field x 16 x MClk period. The Reset value is 20h. Bit 18 Localbuffer dual Write enables Read Only LB Reset Bit 18 x16 DRAM parts come with either 2CAS line and 1 WE line or 1CAS line and 2 WE. The preferred memory parts for GLINT dual CAS lines, however asserting this bit field allows Dual WE parts to be used. In this case, the LBMemCasN lines should be connected to the DRAM WE lines, and the LBMemWeN lines should be connected to the DRAM CAS lines. When x4 or x8 parts are used, this bit should not be set. 0 = Dual CAS1 = Dual Write Enables Bit 19 LB Reset Bit 19 Reserved Read Only Bits 21-20 **PCI Maximum Latency** Read Only LB Reset Bits 21-20 Form the top 2 bits of the configuration space Maximum Latency register Bits 23-22 PCI Minimum Grant Read Only LB Reset Bits 23-22 Form the top 2 bits of the configuration space Minimum Grant register Bits 26-24 Localbuffer visible region size Read Only LB Reset Bits 26-24 0 = 1 MBvte1 = 2 MBytes 2 = 4 MBytes 3 = 8 MBytes 4 = 16 MBytes 5 = 32 MBytes 6 = 64 MBytes 7 = 0 MBytes

| Bits 29-27 | Localbuffer width                                                       | Read Only | LB Reset Bits 29-27 |

|------------|-------------------------------------------------------------------------|-----------|---------------------|

|            | 0 = 16 Bit                                                              |           |                     |

|            | 1 = 18 Bit                                                              |           |                     |

|            | 2 = 24 Bit                                                              |           |                     |

|            | 3 = 32 Bit                                                              |           |                     |

|            | 4 = 36 Bit                                                              |           |                     |

|            | 5 = 40  Bit                                                             |           |                     |

|            | 6 = 48 Bit                                                              |           |                     |

|            | 7 = Other width                                                         |           |                     |

| Bit 30     | Localbuffer Bypass Packing                                              | Read Only | LB Reset Bit 30     |

|            | 0 = 64 bit Localbuffer bypass step $1 = 32$ bit Localbuffer bypass step |           |                     |

| Bit 31     | Second Localbuffer aperture                                             | Read Only | LB Reset Bit 31     |

|            | 0 = Disabled                                                            |           |                     |

|            | 1 = Enabled                                                             |           |                     |

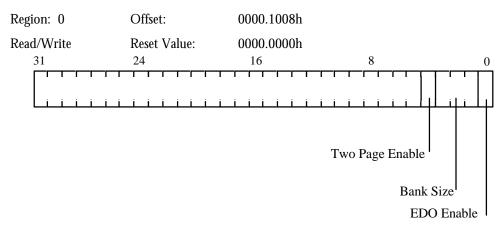

#### 3.2.1 Localbuffer Memory EDO

The Localbuffer memory EDO register enables and controls the use of EDO DRAM for the Localbuffer and controls the number of page detectors used to control the Localbuffer.

## **LBMemoryEDO**

Bit 0 EDO enable

Enables EDO functionality in the localbuffer.

0 = EDO disabled

(RESET)

1 = EDO enabled

Bits 3-1 Bank Size

0 = Second memory bank disabled (RESET)

1 = Second bank starts at 256K pixels

2 = Second bank starts at 512K pixels

3 = Second bank starts at 1M pixels

4 = Second bank starts at 2M pixels

5 = Second bank starts at 4M pixels

6 = Second bank starts at 8M pixels

7 = Reserved

Bit 4 Two Page enable

Enables a separate page detectors for each bank of memory.

0 = Single Page detector

(RESET)

1 = Two Page Detectors Enabled

# N.B. Bits 31 to 20 of this register return bits 31 to 20 of the LBMemoryCtl register when read.

#### 3.3 Framebuffer Registers

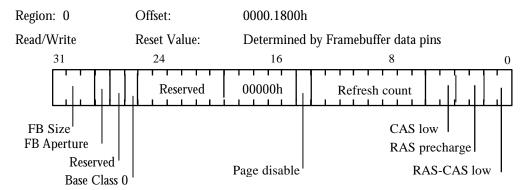

#### 3.3.1 Framebuffer Memory Control

The Framebuffer memory control register sets the characteristics of the Framebuffer VRAM. The register is initialized at reset time by setting values on Localbuffer data pins (see Reset Control, Section 12). Care must be taken when modifying this register to ensure that the VRAM will function within its worst case timings.

# **FBMemoryCtl**

Bits 1-0 RAS-CAS low

FB Reset Bits 1-0

Defines the period from RAS asserted to CAS asserted during a framebuffer access in terms of MClks.

0 = 2 clocks

1 = 3 clocks

2 = 4 clocks

3 = 5 clocks

Bits 3-2 RAS Precharge

FB Reset Bits 3-2

Defines the RAS Precharge period in MClks.

0 = 2 clocks

1 = 3 clocks

2 = 4 clocks

3 = 5 clocks

Bits 5-4 CAS low

FB Reset Bits 5-4

Determines the CAS active time during a framebuffer memory access.

0 = 1 clock

1 = 2 clocks

2 = 3 clocks

3 = 4 clocks

Bit 13-6 Refresh count

This field can be used to optimize the VRAM refresh period to the system MClk and the VRAM used for the framebuffer. The refresh period is the value of this field x 16 x MClk period.

Reset value 20h

Bit 14 Page mode disable

FB Reset Bit 6

Asserting this bit will cause all framebuffer accesses to perform a full VRAM memory cycle.

i.e. Fast Page mode is never used.

0 = Page mode enabled

1 = Page mode disabled

Bits 19-15 00000h Read only

Bits 21-20 Reserved

Bit 22 EDO DRAM

FB Reset Bit 22

This field is for informational purposes only and can be used to correctly configure the

Localbuffer through software.

0 = Fast Page Mode DRAM fitted for Localbuffer

1 = EDO DRAM fitted for Localbuffer

Bits 25-23 Reserved

FB Reset Bits 25-23

Bit 26 Base Class Zero

Read only

FB Reset Bit 26

$0 = GLINT\ 500TX\ returns\ a\ PCI\ Base\ class\ and\ sub-class\ of\ 03h\ 80h$

1 = GLINT 500 TX returns a PCI Base Class and sub-Class of 00h 00h

See Section 2.1.4

Bit 27 Reserved Read only

FB Reset Bit 27

Bit 28 Framebuffer Aperture 1 Enable

Read only

FB Reset Bit 28

Bits 31-29 Framebuffer Visible Region Size

Read only

FB Reset Bits 31-29

0 = 1 MByte

1 = 2 MBytes

2 = 4 MBytes

3 = 8 MBytes

4 = 16 MBytes

5 = 32 MBytes

6 = Reserved

7 = 0 MBytes

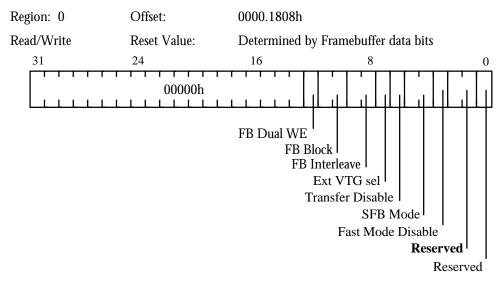

#### 3.3.2 Framebuffer Mode Select

The Framebuffer mode select register sets the mode of the Framebuffer VRAM. The register is initialized at reset time by setting values on Localbuffer data pins (see Reset Control, Section 12).

### **FBModeSel**

Bit 0 Framebuffer Width Read Only

This field always returns the value 1 indicating that the Framebuffer width is 64 bits for backward compatibility with the GLINT 300SX.

Bits 2-1 Reserved

This field always returns the value 3.

Bit 3 Fast Mode Disable

FB Reset Bit 10

Setting this field turns off some of the memory access optimizations.

0 = Fast mode enabled

1 = Fast mode disabled

Bit 5-4 Shared Framebuffer Mode

Read only

FB Reset Bits 12-11

If TX Enhanced mode is not set, this 2 bit field determines the Shared Framebuffer mode.

0 = Disabled

1 = Arbiter ( Primary controller)

2 = Requester (Secondary controller)

3 = Reserved

This is compatible with GLINT 300SX.

In TX enhanced mode is set , then this field is used in conjunction with the TX Enhanced Shared Memory and SFBModeSwap fields of the TX Shared Memory Control register to determine Shared memory control. See section 7.3 for more details

Bit 6 Transfer disable

FB Reset Bit 13

0 = Video memory transfer cycles enabled

1 = Video memory transfer cycles disabled

Bit 7 External VTG Select

FB Reset Bit 14

0 = Select internal Video Timing Generator1 = Select external Video Timing Generator

Bits 9-8 Framebuffer interleave

FB Reset Bits 16-15

This field determines how many interleaved banks of memory are available. e.g. Framebuffer Width = 1 and Framebuffer Interleave = 1 means 2 x64bit banks of memory interleaved by CAS.

0 = 1 way

1 = 2 way

2 = 4 way

3 = Reserved

#### Bits 11-10 Framebuffer block fill size

FB Reset Bits 18-17

The field is used by the memory controller to perform VRAM block fill and selects the block fill size of an individual VRAM. It can be used by the software in conjunction with the values in the Framebuffer Width field and the Framebuffer Interleave field to determine the actual block fill size available to GLINT.

0 = Block fill unsupported

1 = 4 pixel per VRAM block fill

2 = 8 pixel per VRAM block fill

3 = Reserved

#### Bit 12 Framebuffer Dual Write Enables

FB Reset Bit 19

x16 VRAM parts come with either 2 CAS line and 1 WE line or 1CAS line and 2 WE. The preferred memory parts for GLINT have dual CAS lines, however asserting this bit field allows Dual WE parts to be used. In this case, the FBMemCasN lines should be connected to the VRAM WE lines, and the FBMemWeN lines should be connected to the VRAM CAS lines. When x4 or x8 parts are used, this bit should not be set.

0 = Dual CAS VRAMs

1 = Dual WE VRAMs

#### Bits 31-13 00000h

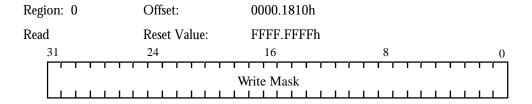

### 3.3.3 Framebuffer Graphics Core Write Mask

The Framebuffer GC write mask register is a read only register to allow the current Graphics Core write mask to be read. This register is for diagnostic purposes only.

### **FBGCWrMask**

Bits 31-0 Graphics Core Write Mask

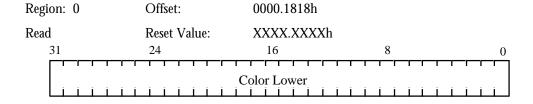

#### 3.3.4 Framebuffer Graphics Core Color Lower

The Framebuffer GC color lower register is a read only register to allow the current Graphics Core color low 32 bits to be read. This register is for diagnostic purposes only.

## **FBGCColorLower**

Bits 31-0 Graphics Core Color Mask

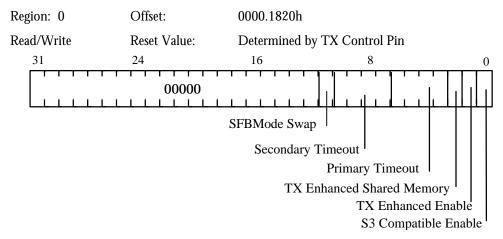

#### 3.3.5 Framebuffer TX Shared Memory Control

The Framebuffer TX shared memory control register sets the characteristics of shared framebuffer interface for the GLINT 500TX..

### FBTXMemCtl

Bit 0 S3 Compatible Enable

Sets the Framebuffer memory controller to be compatible with the S3 964/968

Bit 1 TX Enhanced Enable

Read Only TX Control Pin

Indicates that certain GLINT 500TX enhanced features are available

Bit 2 TX Enhanced Shared Memory

Read Only

FB Reset Bit 20

This bit can only be set if the TXEnhanced pin is pulled high.

In TX enhanced mode this value is used together with the Shared Framebuffer Mode bits in the FBModeSel register and the SFBModeSwap field to determine the Shared Memory configuration. See Section 7.3.

Bits 6-3 Primary Timeout

This 4 bit field provides a timeout count for the Shared Memory arbiter. When GLINT 500TX is a primary controller it will ignore requests from the secondary controller until the timeout counter has reached zero. The timeout period is  $MClk\ x\ 16$ .

Reset value 0h

Bits 10-7 Secondary Timeout

This 4 bit field provides a timeout counter for the Shared Memory arbiter. When GLINT 500TX is a primary controller, the timeout counter is used to gate requests from the GLINT 500TX for the memory bus when the secondary controller has the bus. The timeout period is MClk x 16.

Reset value 0h

Bit 11 SFBModeSwap

Read Only

FB Reset Bit 21

In TX enhanced mode this value is used together with the Shared Framebuffer Mode bits in the FBModeSel register and the TXEnhanced SharedMemory field to determine the Shared Memory configuration. See Section 7.3.

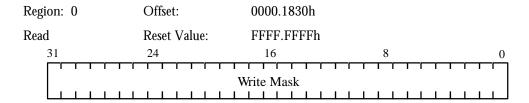

### 3.3.6 Framebuffer Bypass Write Mask

The Framebuffer write mask register defines the hardware write used for bypass accesses.

## **FBWrMaskk**

Bits 31-0 Graphics Core Write Mask

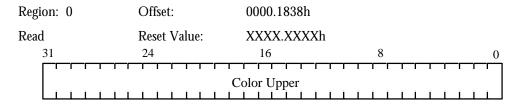

### 3.3.7 Framebuffer Graphics Core Color Upper

The Framebuffer GC color upper register is a read only register to allow the current Graphics Core color high 32 bits to be read. This register is for diagnostic purposes only.

## **FBGCColorUpper**

Bits 31-0 Graphics Core Color Upper

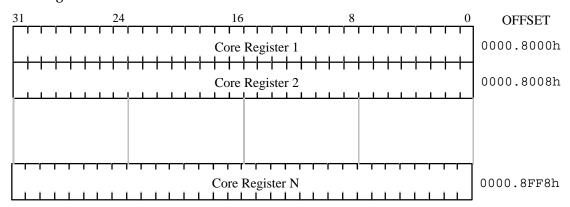

### 3.4 Graphics Core Registers

All the Graphics Core registers in the GLINT 500TX are addressed in this part of region 0. The address for each register and associated data fields is defined in the GLINT Programmers Reference Manual.

Note. Not all the available register locations are used within the Graphics Core. The registers are on 64 bit boundaries.

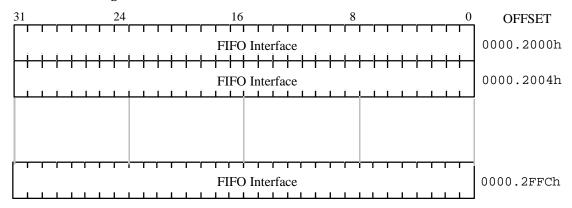

#### 3.5 Graphics Core FIFO Interface

The Graphics Core FIFO interface provides a port through which both GC register addresses and data can be sent to the input FIFO. A range of 4 KBytes of host space is provided although all data may be sent through one address in the range. ALL accesses go directly to the FIFO, the range is provided to allow for data transfer schemes which force the use of incrementing addresses. Before writing to the input FIFO the user must check that there is sufficient space by reading the InFIFOSpace register.

If the FIFO interface is used, then data is typically sent to the GLINT 500TX in pairs, an address word which addresses the register to be updated, followed by the data to be sent to the register. Note that the GC registers can not be read through this interface. Command buffers generated to be sent to the input FIFO interface may be read directly by the GLINT 500TX by using the DMA controller.

A data formatting scheme is provided to allow for multiple data words to be sent with one address word where adjacent or grouped registers are being written, or where one register is to be written many times.

For more information on the direct FIFO interface data buffer formats please refer to the GLINT Programmers Reference Manual.

Note. The FIFO interface can be accessed at 32 bit boundaries. This is to allow a direct copy from a DMA format buffer.

## Internal Video Timing Generator

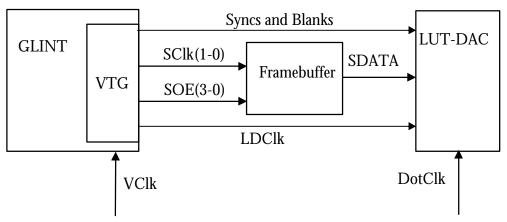

The GLINT 500TX provides a timing generator to enable a complete framebuffer to be implemented with just the addition of VRAM, video clock generator and a suitable RAMDAC. The timing generator produces appropriate Horizontal and Vertical Syncs and Blanks from an external video clock. It controls the instigation of VRAM transfer cycles in the Framebuffer Interface and provides the VRAM transfer addresses. It also controls the VRAM serial clocks and serial output enables.

It is anticipated that GLINT 500TX will be used with more complex framebuffers than the internal timing generator can drive. For this reason, the timing generator can be disabled and the Framebuffer Interface can be controlled by external circuitry to generate VRAM transfer cycles.

The timing generator is controlled through a series of registers accessible from the PCI bus. There is no access to the timing generator from the GLINT 500TX core.

The timing generator operates entirely from a video clock (VClk). Suitable internal resynchronization occurs between the timing generator and both the PCI interface (PCIClk) and the Framebuffer Interface (MClk).

Figure 4-1. Video Timing Generator

#### 4.1 Overview of Internal VTG features

- Generates VSync, HSync, CompositeBlank, CompositeSync, all with programmable polarity.

- 12 bit horizontal and vertical counters.

- Video clock of up to 80 MHz.

- Linearly mapped framebuffer.

- VRAMs with split transfer required.

- VRAMs with and without QSF.

- Programmable size of VRAM split register 128 or 256.

- Programmable transfer address at start of frame for double buffering support.

- 1, 2 or 4 way Interleaving of VRAM serial outputs.

#### 4.2 Internal VTG Register Set

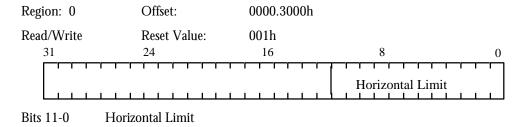

### 4.2.1 Horizontal Limit

The Horizontal Limit register defines the horizontal period of the video display. The internal horizontal counter is clocked by VClk. This counter starts at 1, counts to the value set in the Horizontal Count limit register and resets to 1 again.

### **VTGHLimit**

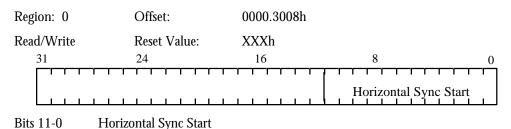

#### 4.2.2 Horizontal Sync Start Register

The Horizontal Sync starts when the internal Horizontal Counter reaches the value stored in the Horizontal Sync Start register.

## VTGHSyncStart

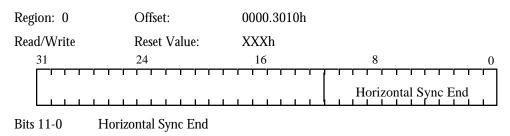

### 4.2.3 Horizontal Sync End

The Horizontal Sync ends when the internal Horizontal Counter reaches the value stored in the Horizontal Sync End register.

## **VTGHSyncEnd**

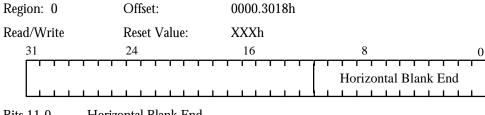

#### 4.2.4 Horizontal Blank End

The Horizontal Blank starts when the internal Counter is reset to 1. The Horizontal Blank ends when the internal Horizontal Counter reaches the value stored in the Horizontal Blank End register.

## **VTGHBlankEnd**

Bits 11-0 Horizontal Blank End

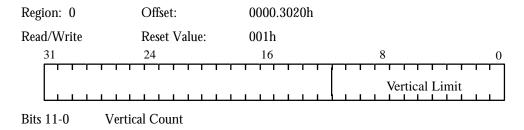

#### 4.2.5 Vertical Limit

The Vertical Limit register defines the vertical period of the video display. The internal vertical counter is clocked by VClk at the start of every Horizontal line. This counter starts at 1, counts to the value set in the Vertical Count limit register and resets to 1 again.

### VTGVLimit

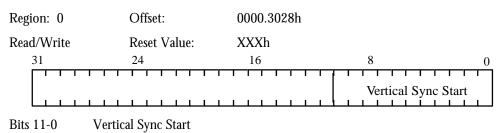

#### 4.2.6 Vertical Sync Start

The Vertical Sync starts when the internal Vertical Counter reaches the value stored in the Vertical Sync Start register.

# VTGVSyncStart

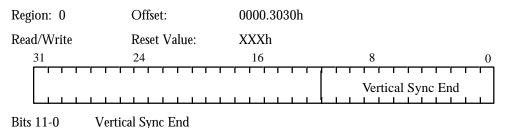

#### 4.2.7 Vertical Sync End

The Vertical Sync ends when the internal Vertical Counter reaches the value stored in the Vertical Sync End register.

## VTGVSyncEnd

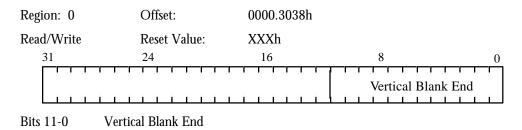

#### 4.2.8 Vertical Blank End

The Vertical Blank ends when the internal Vertical Counter reaches the value stored in the Vertical Blank End register.

## **VTGVBlankEnd**

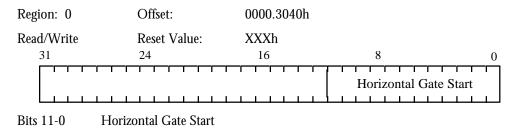

#### 4.2.9 Horizontal Gate Start

The Horizontal Gate is an internal signal used to gate the VRAM serial clocks SClk0 and SClk1. Between HGate Start and HGate End, the serial clocks are enabled. The Horizontal Gate is typically set to the inverse of Horizontal Blank with a possible shift to allow for external delays in the Blank and serial clock/data paths. The internal Horizontal Gate signal starts when the internal Horizontal Counter matches Horizontal Gate Start register.

## **VTGHGateStart**

#### 4.2.10 Horizontal Gate End

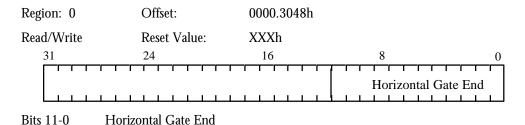

The internal Horizontal Gate signal ends when the internal Horizontal Counter matches the Horizontal Gate End register.

## **VTGHGateEnd**

#### 4.2.11 Vertical Gate Start

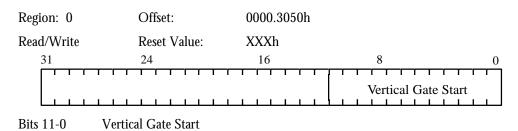

The internal Vertical Gate signal is used to reset the VRAM transfer cycle controller to perform a full transfer at the start of a frame. It is typically active for the Horizontal line before the end of vertical blank. The internal Vertical Gate signal starts when the internal Vertical Counter matches Vertical Gate Start register.

### VTGVGateStart

#### 4.2.12 Vertical Gate End

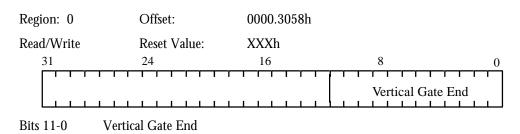

The internal Vertical Gate signal ends when the internal Vertical Counter matches the Vertical Gate End register.

## VTGVGateEnd

### 4.2.13 Polarity Control

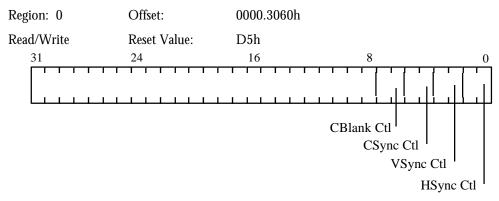

The Polarity Control Register determines the polarities of the output signals HSync, VSync, CBlank and CompSync.

# **VTGPolarity**

Bits 1-0 HSync Ctl

0 = Active High

1 = Forced High

2 = Active Low

3 = Forced Low

Bits 3-2 VSync Ctl

0 = Active High

1 = Forced High

2 = Active Low

3 = Forced Low

Bits 5-4 CSync Ctl

0 = Active High

1 = Forced High

2 = Active Low

3 = Forced Low

Bits 7-6 CBlank Ctl

0 = Active High

1 = Forced High

2 = Active Low

3 = Forced Low

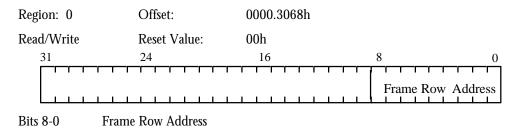

#### 4.2.14 Frame Row Address register

The contents of the Frame Row Address register determines the VRAM row loaded into the VRAM shift register at the start of frame. While the frame is active, VRAM split transfers are generated to reload the VRAM shift register. The transfer addresses required are automatically generated internally, starting from this value. At the start of the next frame, a full transfer reloads the shift register with the row specified by this register again. The full transfer split register start address is always zero.

This register can be programmed for double-buffering, if the framebuffer is large enough, by starting the buffers on two different rows and altering the value to swap buffers.

To avoid any possible display artifact, this register should not be changed at the time the VRAM full transfer cycle is occurring at the start of frame. It is recommended that the register is updated during the active vertical period.

## VTGFrameRowAddr

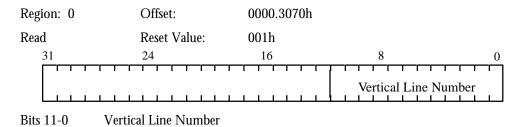

#### 4.2.15 Vertical Line Number

This read only register returns the value of the internal Vertical counter. It can be used to determine when the display is in the vertical blanking interval.

The display is in vertical blanking if the Vertical Line Number is between 1 and the value in the Vertical Blank End register. The display is active if the Vertical Line number is greater than the Vertical Blank End value.

## VTGVLineNumber

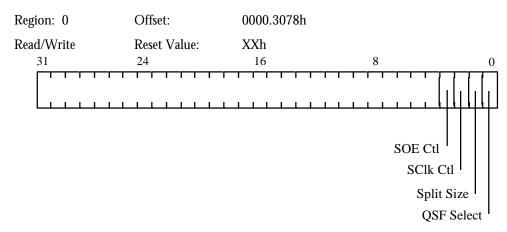

#### 4.2.16 Serial Clock Control

## VTGSerialClk

Bit 0 QSF Select

0 = External QSF

1 = Internal QSF

When this bit is asserted, the transfer address generator counts VRAM serial clocks and generates an internal QSF signal to initiate VRAM transfer cycles. When this bit is negated, the QSF pin is used to initiate transfer cycles. ( IBM 4M VRAM do not generate QSF, so an internal QSF must be generated).

Bit 1 Split Size

0 = 128 word split transfer register

1 = 256 word split transfer register

This bit is set to reflect the size of the VRAM transfer register in split transfer mode. 0 = 128, 1 = 256. Most 256Kx4 and 256Kx8 VRAMs have a split register of 256. IBM 4M VRAMs have a split register size of 128. This field is used in the generation of the internal QSF.

Bit 2 SClk Ctl

This field is used to control the generation of SCLK0 and SCLK1 as described in section 4.4 below

Bit 3 SOE Ctl

This field is used to control the generation of SOE0 , SOE1, SOE2 and SOE3 as described in section 4.4 below.

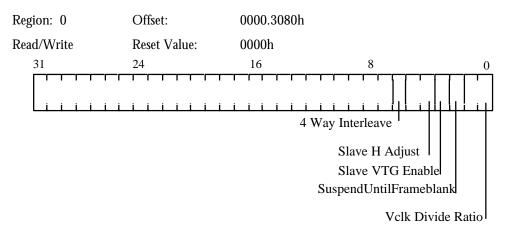

#### 4.2.17 Mode Control

### VTGModeCtl

#### Bits 1-0 VCLK Divide Ratio

0 = Use VCLK undivided

1 = Use VClk/2

2 = Use VClk/4

3 = Use VClk/8

GLINT 500TX can generate a LDClk which is divided down from the incoming VCLK. The VClk Divide ratio is used to select the division .The SClk and SOE signals are derived from the LDClk. Normal usage has this field at 0.

#### Bit 2 SuspendUntilFrameBlank Enable

0 = Complete immediately

1 = wait for VBLANK

The GLINT 500TX has a mechanism in the Graphics Core to flush outstanding writes to the framebuffer and then suspend any succeeding reads or writes until the next vertical blank period. This field is used to enable this feature in the timing generator. If the field is not set then no suspension occurs. This is the reset condition. The field should not be set until the timing generator is running to avoid the possibility of suspending the Graphics Core when no VBLANK will occur.

#### Bit 3 Slave VTG Enable

0 = Disable

1 = Enable

This field enables the syncing of the timing generator to an external VSYNC. The master VSYNC is input to the GLINT 500TX on the QSF pin. The polarity of the VSYNC is taken to be the polarity of the internal VSYNC defined in the VTGPolarity register.

52

### Bits 5-4 Slave Hadjust

0 = adjust by 0 VClks

1 = adjust by 1 VClks

2 = adjust by 2 VClks

3 = adjust by 3 VClks

This field allows the internal timing generator to be adjusted by a number of VClks relative to the incoming master VSYNC.

Bit 6 4-way Interleave Enable

0 = Disable

1 = Enable

When this bit is set, and the TXEnhanced pin is pulled high, then two additional Serial O/p enables are generated allowing 4 banks of memory to be interleaved into the RAMDAC.

#### 4.3 VTG Configuration

#### 4.3.1 Horizontal Timing Specifications.

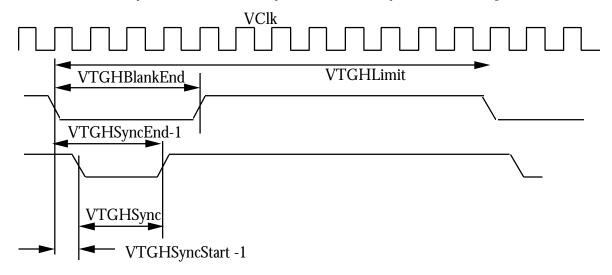

A Horizontal counter (VTGHCount) runs off VClk. The counter starts at 1 and counts to the value in VTGHLimit and then reloads. This defines the Horizontal period. i.e. VTGHLimit x VClkPeriod. The horizontal blank and sync timing is derived from this counter and the values stored in the parameter registers.

At reset VTGHLimit is reset with '1'. This effectively freezes the counter until the VTGHLimit register is loaded.

Horizontal blank starts at VTGHCount = 1.

Horizontal blank ends at VTGHCount = VTGHBlankEnd.

Horizontal blank width = VTGHBlankEnd x VClkPeriod.

Horizontal sync. starts at VTGHcount = VTGHSyncStart and ends at VTGHSyncEnd.

Horizontal sync. width = (VTGHsyncEnd - VTGHSyncStart) x VClkperiod.

Figure 4-2. Horizontal Timing

#### 4.3.2 Vertical Timing Specifications.

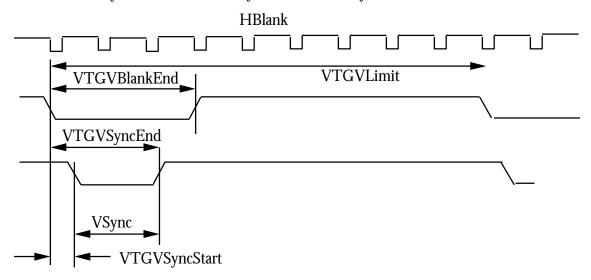

The vertical signals are specified in terms of numbers of lines. A vertical counter (VTGVCount) counts lines starting at 1 and counts to the value in VTGVLimit and then reloads. The vertical period or frame rate is defined as VTGVLimit x Horizontal period. This is VTGVLimit x VTGHLimit x VClkPeriod. The vertical blank and sync timing is derived from this counter and the values stored in the parameter registers.

At reset VTGVLimit is reset with '1'. This effectively freezes the counter until the VTGVLimit register is loaded.

Vertical Blank is asserted on the active edge of Horizontal blank

Vertical blank starts at VTGVCount = 1 and

Vertical blank ends at VTGVCount = VTGVBlankEnd.

Vertical blank width = VTGVBlankEnd x HorizontalPeriod.

The Vertical sync is asserted on the active edge of Horizontal sync.

Vertical sync starts at (VTGVCount = VTGVSyncStart -1)

Vertical sync ends at VTGVSyncEnd - 1

Vertical sync. width = (VTGVsyncEnd - VTGVSync start) x HorizontalPeriod

Figure 4-3. Vertical Timing

#### 4.3.3 Sync and Blank Generation

Composite Sync (CompSync.) is the logical OR of HSync and VSync.

Composite Blank (CBlank) is the logical OR of HBlank and VBlank.

VSync, HSync, CompSync and CBlank are all outputs from GLINT 500TX. The polarity of these signals is controlled by the Polarity Control Register.

#### 4.3.4 Vertical and Horizontal Gate Specification

Hgate is generated from VTGHGateStart and VTGHGateEnd in the same way as Hsync. i.e.

Hgate = (VTGHGateEnd - VTGHGateStart) x VClkPeriod

Similarly VGate is generated from VTGVGateStart and VTGVGateEnd

VGate = (VTGVGateEnd - VTGVGateStart) x HorizontalPeriod.

VGate and HGate are used to control the VRAM transfer requester and to gate the VRAM serial clock. HGate is typically set to be the inverse of HBlank with a shift of a number of clocks to allow the VRAM serial data to reach the RAMDAC synchronized correctly to the blanking signal. VGate is typically set during the line before the end of Vertical Blank.

#### 4.3.5 VRAM Transfer Control

The video display from GLINT 500TX is generated by connecting the framebuffer VRAM serial ports to the RAMDAC. The VRAM serial shift registers must be kept loaded with the correct data to generate the display. The framebuffer must be linearly mapped to use the internal timing generator/transfer address controller.

At the end of the vertical blanking, a VRAM full transfer cycle is performed using the address loaded in the Frame Row Address register. This defines the VRAM RAS address start point.

The VRAM serial clock (SClk) is gated with HGate and VGate to only clock during the active part of active lines. If an external QSF signal is available which indicates when the VRAM shift register is half empty, split transfer cycles are performed which reload the empty half of the shift register. This continues until the end of the frame.

If no external QSF signal is available then the Internal QSF bit of the Serial Clock Control register must be set. An internal QSF is generated by effectively counting SClks until the size of the VRAM split register is reached and QSF is toggled. Split register sizes of both 256 bits and 128 bits are supported by setting the Split RegisterSize bit of the Serial Clock Control register appropriately.

For a split register size of 256, the row address and column address bit 8 is incremented every time QSF toggles. For a split register size of 128, the row address and column address bits 8 and 7 are incremented every time QSF toggles.

### 4.4 VRAM Serial Port Control

There are numerous ways of controlling the framebuffer serial port to generate the display. The serial port interleave may be one, two or four way depending on the number of banks of memory and the RAMDAC port width. The register settings for these different interleaves is listed in Table 4.1 below.

Table 4.1. Options For Serial Port Control

| 4way | TX<br>Enhance | SOE<br>Ctl | SClk<br>Ctl | Display    | SClk freq. | serial port interleave |

|------|---------------|------------|-------------|------------|------------|------------------------|

|      | d             | Cu         | Cu          | source     |            |                        |

| X    | 0             | 0          | 0           | SOE0       | LDCLK      | 1-way bank0            |

| X    | 0             | 1          | 0           | SOE1       | LDCLK      | 1-way bank1            |

| X    | 0             | X          | 1           | SOE0,1     | LDCLK/2    | 2-way bank0,1          |

| 0    | 1             | 0          | 1           | SOE0,1     | LDCLK/2    | 2-way bank0,1          |

| 0    | 1             | 1          | 1           | SOE2,3     | LDCLK/2    | 2-way bank2,3          |

| 1    | 1             | X          | X           | SOE0,1,2,3 | LDCLK/4    | 4way                   |

The first 3 modes are compatible with GLINT 300SX. The latter 3 modes are new to GLINT 500TX.

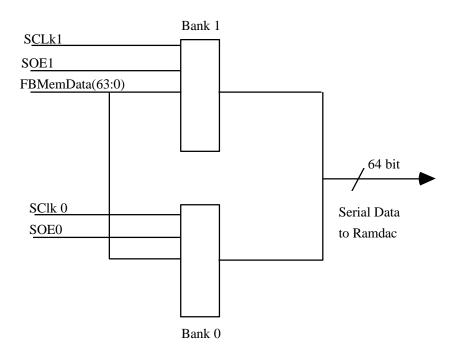

#### 4.4.1 One-Way Interleaved

Serial data is clocked out of either Bank 0 or Bank 1. This is controlled using the SOE Ctl field of the Serial Clock Control register. There is no dynamic switching from bank 0 to bank 1.

SClk0 and SClk1 are identical in this case and are gated versions of the RAMDAC LDClk.

Figure 4.4 Serial Control of 1-Way interleaved Display.

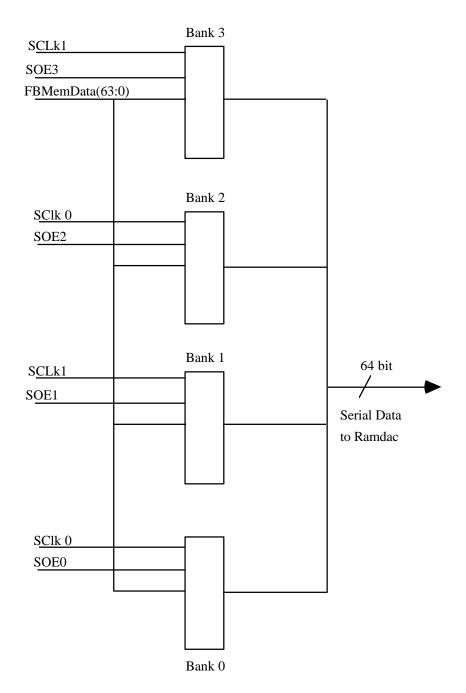

#### 4.4.2 Two-Way Interleaved

In this mode, Bank 0 and Bank 1 are interleaved, and the display is taken alternately from each using SOE0 and SOE1. SCLK0 and SCLK1 are again gated on during the active scan line and run at RAMDAC LDClk/2. This is compatible with GLINT 300SX.

If the GLINT 500TX has the TXEnhanced pin pulled high, then the SOE2 and SOE3 pins are activated. These can be used to allow display from an additional 2 banks of memory. In two-way interleaved mode the SOE Ctl field of the Serial Clock Control register is used to select whether the Bank 0 and Bank 1 are outputting data onto the Serial data bus, or whether Bank 2 and Bank 3 are used.

Figure 4.5 2-Way Or 4-Way interleaved Serial Port With 64bit RAMDAC.

Figure 4.7 2-Way Interleaved With TX Enhanced = 1, SOE Ctl = 1.

#### 4.4.3 Four-Way Interleaved

This mode is connected to the VRAM serial port exactly the same way as the two-way interleaved mode. The GLINT 500TX drives the SOE of each of the 4 banks low in turn. Note that banks 0 and 2 are connected to SCLK0 and banks 1 and 3 to SCLK1.

Figure 4.8 4-Way interleaved Serial Port.

If a 64-bit RAMDAC is used, then the interleave of the VRAM serial port must match the interleave of the VRAM random port as defined in the Interleave field of the FBModeSel register.

If a 128-bit RAMDAC is used, then the interleave of the VRAM serial port must be half the interleave of the VRAM random port.

In general, the higher the interleave value of the serial port, the faster the pixel rate that can be displayed and hence the higher the resolution . However, more banks of memory must be fitted.

4.5 VTG Example

The timing specification for the VESA 800 x 600 at 60 Hz mode 6Ah are as follows :-

|                | Horizontal |            | Vertical   |           |

|----------------|------------|------------|------------|-----------|

|                | Time       | Characters | Time       | Lines     |

| Dot Clock      | 40 MHz     |            |            |           |

| Sync. Polarity | Positive   |            | Positive   |           |

| Frequency      | 37.879 KHz |            | 60.3165 Hz |           |

| Period         | 26.4 uS    | 132        | 16.579 ms  | 628 lines |

| Blanking Time  | 6.4 uS     | 32         | 0.739 ms   | 28 lines  |

| Sync Width     | 3.2 uS     | 16         | 0.106 ms   | 4 lines   |

| Back Porch     | 2.2 uS     | 11         | 0.607 ms   | 23 lines  |

| Active Time    | 20.0 uS    | 100        | 15.840 ms  | 600 lines |

| Front Porch    | 1.0 uS     | 5          | 0.026 ms   | 1 line    |

For a system with 32 bits per pixel and a 2 to 1 interleave on the serial data i.e. VLCK = Dot Clock / 2 then the following register values can be used.

| Register Name | Value        | Explanation                            |

|---------------|--------------|----------------------------------------|

|               |              |                                        |

| VTGHLimit     | 528          | 132 x 8 pixel chars. 2 pixels per VCLK |

| VTGHSyncStart | 20           | Front porch *8 /2                      |

| VTGHSyncEnd   | 84           | (FrontPorch + SyncWidth)*8/2           |

| VTGHBlankEnd  | 128          | (Blanking time ) *8/2                  |

| VTGVLimit     | 628          | Vertical Period                        |

| VTGVSyncStart | 2            | Front Porch +1                         |

| VTGVSyncEnd   | 6            | Front Porch + SyncWidth +1             |

| VTGVBlankEnd  | 28           | Blanking Time                          |

| VTGHGateStart | HBlankEnd -2 | Example value ( system dependent)      |

| VTGHGateEnd   | HLimit -2    | Example value ( system dependent)      |

| VTGVGateStart | VBlankEnd -1 |                                        |

| VTGVGateEnd   | VBlankEnd    |                                        |

## 5. External Video Control Registers

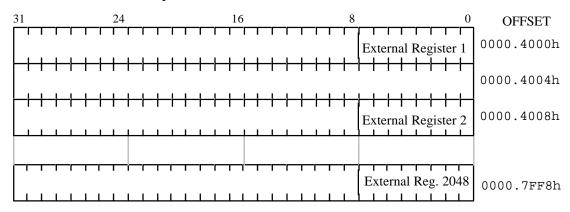

GLINT 500TX provides an 8 bit general purpose interface to allow external devices to be addressed from the PCI. This interface has a 16Kbyte address space and is specified as the external video control register region. It allows up to 2048 x 8bit registers to be accessed on 64 bit boundaries. On a typical system, this interface is used to address the LUT-DAC. On more advanced designs, when an external video timing generator or other controllable video circuitry is used, these can also be addressed through this register space. The interface consists of address, data and two control lines. The address and data lines share pins with the Localbuffer data pins.

#### 5.1 External Video Interface Signal Definitions

The following signals are defined for the External Video Interface:

Table 5-1. External Video Signals

| Signal               | Pins used        | Description                                                                                  |

|----------------------|------------------|----------------------------------------------------------------------------------------------|

| Ext VidAddress(13-3) | LBMemData(37-27) | External Video register Address lines. Note that the registers are on 64 bit PCI boundaries. |

| ExtVidData(7-0)      | LBMemData(47-40) | External Video Data bus.                                                                     |

| DacRdN               | DacRdN           | External Video register read strobe (negative active)                                        |

| DacWrN               | DacWrN           | External Video register write strobe (negative active)                                       |

See Chapter 9 for signal waveforms and timing.

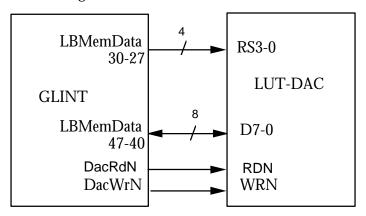

### 5.2 LUT-DAC Interface.

A typical LUT-DAC would be connected to GLINT 500TX through the External Video Interface as shown in figure 5-1.

Figure 5-1 Typical LUT-DAC Interface.

When additional External Video circuitry is required, the DacRdN, DacWrN and ExtVidAddress must be externally decoded to generate any required select or control lines.

## 5.3 Resetting External Circuitry

External circuitry connected to GLINT may need a reset signal. This cannot be obtained directly from the PCI reset line as this can only have one load, the GLINT chip itself. GLINT uses two of its external circuitry control pins, RomEnN and DacWrN, when asserted together to indicate a reset. The pins are asserted when either the PCIRstN line to GLINT is asserted or when GLINT is reset by software.

Reset is indicated for the full length of a PCI reset and for 64 MClk cycles when a soft reset is initiated.

# 6. Localbuffer

# 6.1 Configurations - DRAM Types.

The GLINT 500TX uses the Localbuffer to store depth, stencil, Fast Clear, Graphics ID and texture information. The Localbuffer may be up to 48 bits wide. The following tables indicate typical Localbuffer configurations.

Table 6-1. Localbuffer Sizes With 4Mbit Technology Memories

| Memory<br>Device Type | Localbuffer<br>Width | No of<br>Devices | Banks of<br>Memory | Size in<br>MBytes | External<br>Buffering |  |

|-----------------------|----------------------|------------------|--------------------|-------------------|-----------------------|--|

| 256K x 16             | 32                   | 4                | 2                  | 2                 | No                    |  |

|                       | 48                   | 6                | 2                  | 3                 | No                    |  |

| 512K x 8              | 32                   | 4                | 1                  | 2                 | No                    |  |

|                       | 40                   | 5                | 1                  | 2.5               | No                    |  |

|                       | 48                   | 6                | 1                  | 3                 | No                    |  |

| 512K x 8              | 32                   | 8                | 2                  | 4                 | No                    |  |

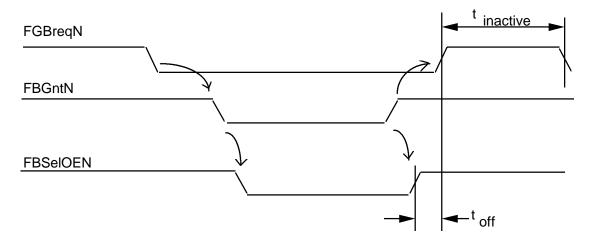

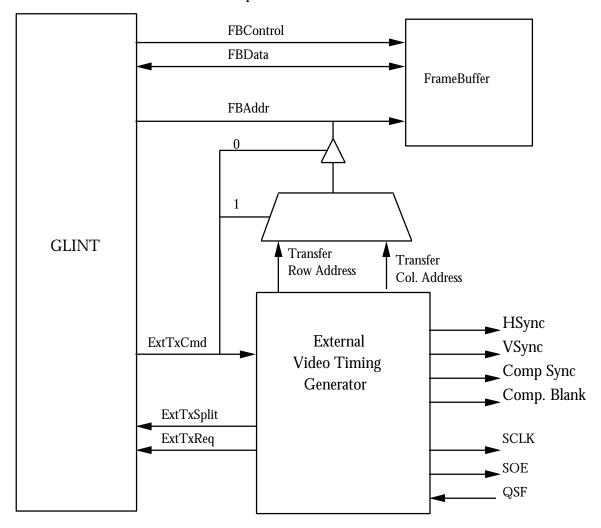

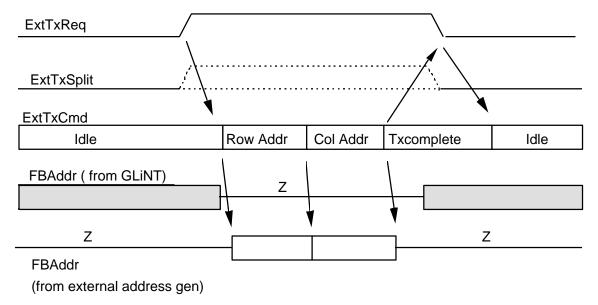

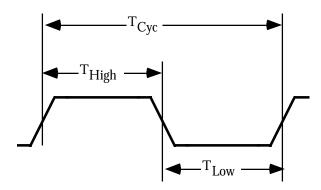

|                       | 40                   | 10               | 2                  | 5                 | No                    |  |