December 12, 2012

The specifications in this RFC publication are preliminary and subject to change without notice. Periodic changes to this publication may be incorporated in new additions or supplements to this publication. This publication is provided "AS IS" and IBM Corporation makes no warranty of any kind, expressed or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

IBM® and POWER® are trademarks of IBM Corp., registered in many jurisdictions worldwide.

Notice to U.S. Government Users—Documentation Related to Restricted Rights—Use, duplication or disclosure is subject to restrictions set fourth in GSA ADP Schedule Contract with IBM Corporation.

© Copyright International Business Machines Corporation, 1994, 2012. All rights reserved.

## **RFC02183: Transactional Memory**

Significance: Major

Status: New

Date: December 12, 2012 Target Version: 2.07 Source Version: 2.06

Books and sections affected:

Book 1:

Section 1.4.5 Categories

Section 2.2 Instruction Execution Order

Section 2.3.1 Condition Register

Section 3.2.2 Fixed-Point Exception Register Section 3.3.18 Move To/From System Register

Section 3.3.18 Move 10/From System Regist

Instructions

### Book 2:

Section 1.1 Definitions

Section 1.7.3.1 Reservations

Section 1.7+ Transactions [Category: Transactional Memory]

O di na 1 de l'ilory]

Section 4.1 Parameters Useful to Application Programs

Section 4.3.2 Data Cache Instructions

Section 4.4.3 Memory Barrier Instructions

Chapter 7+ Transactional Memory Facility [Category: Transactional Memory]

Section B.3+ Transactional Lock Elision [Category:

Transactional Memory]

#### Book 3-S:

Section 2.6 Processor Compatibility Register

Section 3.2.1 Machine State Register

Section 3.2.1+ State Transitions Associated with the Transactional Memory Facility [Category: Transactional Memory]

Section 3.3.1 System Linkage Instructions

Section 3.3.2 Power-Saving Mode Instructions

Section 4.4.2+ Transactional Memory Instructions

[Category: Transactional Memory]

Section 4.4.3 Move To/From System Register Instructions

Section 5.7.8: Reference and Change RecordingTo convey that transactional accesses are permitted to modify R/C/TS bits before the transaction commits, and even if the transaction fails, make the following changes in Figure 25:

Section 5.9.3.1 SLB Management Instructions Section 5.9.3.3 TLB Management Instructions

Section 5.10.1 Page Table Updates

Sectino 6.4.3 Interrupt Processing Section 6.5 Interrupt Definitions Section 6.5.9 Program Interrupt

Section 6.5.14 Trace Interrupt [Category: Trace]

Section 6.5.21+ Facility Unavailable Interrupt

Section 6.7 Exception Ordering Section 6.7 Exception Ordering Section 6.8 Interrupt Priorities

### Appendices:

Appendix C. Platform Support Requirements

Appendix D. Complete SPR List

Appendices G-J Opcode Map and Lists

#### Summary:

Transactional memory is a shared-memory synchronization construct allowing an application to perform a sequence of storage accesses that appear to occur atomically with respect to other threads.

### **Motivation**

As systems include increasing levels of multiprocessing, and power constraints gate the performance improvements obtainable from frequency scaling, further performance gains are dependent on finding and exploiting parallelism. The described transactional memory architecture is motivated by several software usage cases, each involving optimistic execution as a means of exposing parallelism.

- Optimistic execution of lock-based programs.

Through speculative execution, the transactional facility will be used to execute lock-based critical sections without acquiring a lock, providing the benefits of fine-grain locking to applications whose locking protocols have not been carefully tuned for performance.

- Transactional programming in high-level languages. The transactional programming model is an evolving industry-wide standard, offering programmer productivity advantages relative to lockbased shared memory programs. The Power ISA extensions described here will ensure that Power systems are competitive in support for this programming model.

- 3. Checkpoint/Rollback usage. This architecture will be used by some applications for its ability to

checkpoint and restore architectural state, independent of its atomic storage access guarantees.

Changes to the Books

### Book 1:

### Section 1.4.5 Categories

Add "Transactional Memory", abbreviation "TM", notes "Full hardware Transactional Memory support" to the table after Trace.

#### Section 2.2 Instruction Execution Order

Insert a new third bullet in the first bulleted list, adding transaction failure to the list of things that can cause instruction fetching to be redirected.

------ Begin text ------

In general, instructions appear to execute sequentially, in the order in which they appear in storage. The exceptions to this rule are listed below.

- Branch instructions for which the branch is taken cause execution to continue at the target address specified by the Branch instruction.

- Trap instructions for which the trap conditions are satisfied, and System Call instructions, cause the appropriate system handler to be invoked.

- Transaction failure will eventually cause the transaction's failure handler, implied by the tbegin. instruction, to be invoked. See the programming note following the tbegin. description in Section

- Exceptions can cause the system error handler to be invoked, as described in Section 1.10, "Exceptions" on page 23.

- Returning from a system service program, system trap handler, or system error handler causes execution to continue at a specified address.

----- End text -----

### Section 2.3.1 Condition Register

Extend the current 6th bullet to include tcheck. (NOTE THAT OTHER RFCs ALSO CHANGE THIS LIST.)

----- Begin text -----

The bits in the Condition Register are grouped into eight 4-bit fields, named CR Field 0 (CR0), ..., CR Field 7 (CR7), which are set in one of the following ways.

- Specified fields of the CR can be set by a move to the CR from a GPR (mtcrf, mtocrf).

- A specified field of the CR can be set by a move to the CR from another CR field (mcrf), from XER<sub>32:35</sub> (*mcrxr*), or from the FPSCR (*mcrfs*).

- CR Field 0 can be set as the implicit result of a fixed-point instruction.

- CR Field 1 can be set as the implicit result of a floating-point instruction.

- CR Field 6 can be set as the implicit result of a vector instruction.

- A specified CR field can be set as the result of a Compare instruction or of a tcheck instruction (see

- CR Field 1 can be set as the implicit result of a decimal floating-point instruction.

Insert the following text before the store conditional paragraph, describing how TM instructions set the CR. ----- Begin text -----

----- End text -----

With the exception of tcheck, the Transactional Memory instructions set CR0<sub>0:2</sub> indicating the state of the facility prior to instruction execution, or transaction failure. A complete description of the meaning of these bits is given in the instruction descriptions in <insert crossref to TM description (Book II, Section 8.5?)>. These bits are interpreted as follows:

| CR0      | Description                                                 |

|----------|-------------------------------------------------------------|

| 000    0 | Transaction state of Non-transactional prior to instruction |

| 010    0 | Transaction state of Transactional prior to instruction     |

| 001    0 | Transaction state of Suspended prior to instruction         |

| 101    0 | Transaction failure                                         |

The tcheck instruction similarly sets bits 1 and 2 of CR field BF to indicate the transaction state, and additionally sets bit 0 to TDOOMED, as defined in <insert cross ref to TM description (Section 8.2.1?)>.

| CR field BF        | Description                                                 |

|--------------------|-------------------------------------------------------------|

| TDOOMED    00    0 | Transaction state of Non-transactional prior to instruction |

| TDOOMED    10    0 | Transaction state of Transactional prior to instruction     |

| TDOOMED    01    0 | Transaction state of Suspended prior to instruction         |

### Programming Note

Setting of bit 3 of the specified CR field to zero by tcheck and of field CR03 to zero by other TM instructions is intended to preserve these bits for future function. Software should not depend on the bits being zero.

----- End text -----

### Section 3.2.2 Fixed-Point Exception Register

Modify the description of FXCC to include tcheck.

## Section 3.3.18 Move To/From System Register Instructions

Add TFHAR, TFIAR, TEXASR, and TEXASRU to the mtspr table.

Near the end of the mtspr description, add a statement that a move to a TM SPR in other than Non-transactional state causes a TM Bad Thing type Program interrupt

----- Begin text

| decimal | SPR <sup>1</sup>                      | Register             |

|---------|---------------------------------------|----------------------|

| decimal | spr <sub>5:9</sub> spr <sub>0:4</sub> | Name                 |

| 1       | 00000 00001                           | XER                  |

| 8       | 00000 01000                           | LR                   |

| 9       | 00000 01001                           | CTR                  |

| 13      | 00000 01101                           | AMR <sup>5</sup>     |

| 128     | 00100 00000                           | TFHAR <sup>5</sup>   |

| 129     | 00100 00001                           | TFIAR <sup>5</sup>   |

| 130     | 00100 00010                           | TEXASR <sup>5</sup>  |

| 131     | 00100 00011                           | TEXASRU <sup>5</sup> |

| 256     | 01000 00000                           | VRSAVE               |

| 512     | 10000 00000                           | SPEFSCR <sup>2</sup> |

| 896     | 11100 00000                           | PPR <sup>3</sup>     |

| 898     | 11100 00010                           | PPR32 <sup>4</sup>   |

- Note that the order of the two 5-bit halves of the SPR number is reversed.

- <sup>2</sup> Category: SPE.

- Category: Server; see Book III-S.

- 4 Category: Phased-In. See Section 3.1 of Book II.

- 5 Category: Transactional Memory. See <crossref to Bk2 Ch 7+>.

If execution of this instruction is attempted specifying an SPR number that is not shown above, or an SPR number that is shown above but is in a category that is not supported by the implementation, one of the following occurs.

- If spr<sub>0</sub> = 0, the illegal instruction error handler is invoked.

- If spr<sub>0</sub> = 1, the system privileged instruction error handler is invoked.

If an attempt is made to execute *mtspr* specifying a TM SPR in other than Non-transactional state, a TM Bad Thing type Program interrupt is generated.

A complete description of this instruction can be found in Book III.

### **Special Registers Altered:**

See above

Zero the output for mfspr specifying the TFIAR when executed from a privilege level lower than that in which the TFIAR was set. Add TFHAR, TFIAR, TEXASR, and TEXASRU to the mfspr table.

------ Begin text

# Move From Special Purpose Register XFX-form

mfspr RT,SPR

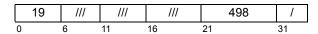

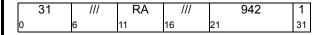

| 31 | RT | spr 339 | /  |

|----|----|---------|----|

| 0  | 6  | 11 21   | 31 |

$n \leftarrow spr_{5,9} \mid \mid spr_{0:4}$  if n = 129 then see Book III-S else

if length(SPR(n)) = 64 then RT  $\leftarrow$  SPR(n)

else RT  $\leftarrow$  320 || SPR(n)

The SPR field denotes a Special Purpose Register, encoded as shown in the table below. If the SPR field contains 129, the instruction references the Transaction Failure Instruction Address Register (TFIAR)<TM> and the result is dependent on the privilege with which it is executed. See Book III-S. Otherwise, the contents of the designated Special Purpose Register are placed into register RT. For Special Purpose Registers that are 32 bits long, the low-order 32 bits of RT receive the contents of the Special Purpose Register and the high-order 32 bits of RT are set to zero.

| decimal | SPR <sup>1</sup>                      | Register             |

|---------|---------------------------------------|----------------------|

| decimal | spr <sub>5:9</sub> spr <sub>0:4</sub> | Name                 |

| 1       | 00000 00001                           | XER                  |

| 8       | 00000 01000                           | LR                   |

| 9       | 00000 01001                           | CTR                  |

| 13      | 00000 01101                           | AMR <sup>8</sup>     |

| 128     | 00100 00000                           | TFHAR <sup>8</sup>   |

| 129     | 00100 00001                           | TFIAR <sup>8</sup>   |

| 130     | 00100 00010                           | TEXASR <sup>8</sup>  |

| 131     | 00100 00011                           | TEXASRU <sup>8</sup> |

| 136     | 00100 01000                           | CTRL                 |

| 256     | 01000 00000                           | VRSAVE               |

| 259     | 01000 00011                           | SPRG3                |

| 260     | 01000 00100                           | SPRG4 <sup>2</sup>   |

- Note that the order of the two 5-bit halves of the SPR number is reversed.

- <sup>2</sup> Category: Embedded.

- <sup>3</sup> See Chapter 5 of Book II.

- 4 Category: SPE.

- Category: Alternate Time Base.

- <sup>6</sup> Category: Server; see Book III-S.

- Category: Phased-In. See Section 3.1 of Book II.

- 8 Category: Transactional Memory. See <crossref to Bk2 Ch 7+>.

|         | SPR <sup>1</sup>                      | Register             |

|---------|---------------------------------------|----------------------|

| decimal | spr <sub>5:9</sub> spr <sub>0:4</sub> | Name                 |

| 261     | 01000 00101                           | SPRG5 <sup>2</sup>   |

| 262     | 01000 00110                           | SPRG6 <sup>2</sup>   |

| 263     | 01000 00111                           | SPRG7 <sup>2</sup>   |

| 268     | 01000 01100                           | TB <sup>3</sup>      |

| 269     | 01000 01101                           | TBU <sup>3</sup>     |

| 512     | 10000 00000                           | SPEFSCR <sup>4</sup> |

| 526     | 10000 01110                           | ATB <sup>3,5</sup>   |

| 527     | 10000 01111                           | ATBU <sup>3,5</sup>  |

| 896     | 11100 00000                           | PPR <sup>6</sup>     |

| . 898   | 11100 00010                           | PPR32 <sup>7</sup>   |

Note that the order of the two 5-bit halves of the SPR number is reversed.

- <sup>2</sup> Category: Embedded.

- See Chapter 5 of Book II.

- Category: SPE.

- Category: Alternate Time Base.

- 6 Category: Server; see Book III-S.

- Oategory: Phased-In. See Section 3.1 of Book II.

- 8 Category: Transactional Memory. See <crossref to Bk2 Ch 7+>.

----- End text -----

### Book 2:

### **Section 1.1 Definitions**

Add transaction failure to the list of causes of deviation from the sequential execution model.

-----Begin text -----

### ■ program order

The execution of instructions in the order required by the sequential execution model. (See Section 2.2 of Book I.) A *dcbz* instruction that modifies storage which contains instructions has the same effect with respect to the sequential execution model as a *Store* instruction as described there. An additional exception to the sequential execution model beyond those described in Book I is caused by transaction failure (see <crossref to description of transaction failure handling>).

----- End text -----

Add the definition of aggregate store as a new bullet at the end of the section.

-----Begin text -----

### aggregate store

The set of stores caused by a successful transaction, which are performed as an atomic unit.

------ End text ------

Section 1.7.3.1 Reservations

Rather than continue to maintain the classification of the causes of reservation loss in the second sentence of the third paragraph, replace that sentence as follows.

------ Begin text ------

A processor has at most one reservation at any time. A reservation is established by executing a *Ibarx*, *Iharx*, *Iwarx*, or *Idarx* instruction, as described in item 1 below, and is lost or may be lost, depending on the item, if any of the following occur. Items 1-8 apply only if the relevant access is performed. (For example, an access that would ordinarily be caused by an instruction might not be performed if the instruction causes the system error handler to be invoked.)

----- End text -----

Add the following as a new third item in the list of causes of reservation loss.

----- Begin text

- 4. <TM> Any of the following occurs on the processor holding the reservation.

- a. The transaction state changes (from Non-transactional, Transactional, or Suspended state to one of the other two states; see Section 8.2, "Transactional Memory Facility States"), except in the following cases

- If the change is from Transactional state to Suspended state, the reservation is not lost.

- If the change is from Suspended state to Transactional state, the reservation is not lost if it was established in Transactional state.

- If the change is caused by a treclaim. or trechkpt. instruction, whether the reservation is lost is undefined.

- b. The transaction nesting depth (see Section 8.4, "Transactional Memory Facility Registers") changes; whether the reservation is lost is undefined. (This item applies only if the processor is in Transactional state both before and after the change.)

- c. The processor is in Suspended state and executes a Store Conditional instruction (stbcx., sthcx., stwcx., or stdcx.) or a waitrsv instruction; the reservation is lost if it was established in Transactional state. In this case the Store Conditional instruction's store is not performed, and the waitrsv does not wait. (For Store Conditional, the reservation is also lost if it was established in Suspended state; see item 2.)

----- End text -----

## Section 1.7+ Transactions [Category: Transactional Memory]

Add the following section before the section on instruction storage.

A transaction is a group of instructions that collectively have unique storage access behavior intended to facilitate parallel programming. (It is possible to nest transactions within one another. The description in this chapter will ignore nesting because it does not have a significant impact on the properties of the memory model. Nesting and its consequences will be described elsewhere.) Sequences of instructions that are part of the transaction may be interleaved with sequences of Suspended state instructions that are not part of the transaction. A transaction is said to succeed or to fail, and failure may happen before all of the instructions in the transaction have completed. If the transaction fails, it is as if the instructions that are part of the transaction were never executed. If the transaction succeeds, it appears to execute as an atomic unit as viewed by other processors and mechanisms. (Although the transaction appears to execute atomically, some knowledge of the inner workings will be necessary to avoid apparent paradoxes in the rest of the model. These details are described below.) The execution of Suspended state sequences have the same effect that the sequence would have in the absence of a transaction, independent of the success or failure of the transaction, including accessing storage according to the weakly consistent storage model or SAO, based on storage attributes. Upon failure, normal execution continues at the failure handler. Except for the rollback of the effects of transactional instructions upon transaction failure, as viewed by the executing thread, the interleaved sequences of Transactional and Suspended state instructions appear to execute according to the sequential execution model. See <cross ref to bk2 ch7+> for more details. The unique attributes of the storage model for transactions are described below.

Transaction processing does not support the rollback of operations on the reservation mechanism. To prevent this possibility, a reservation is lost as a result of a state change from Transactional to Non-transactional or Non-transactional to Transactional. It is possible to successfully complete an atomic update in Transactional state, though such a sequence would have no benefit. It is also possible to complete an atomic update in Suspended state, or straddling an interval in Suspended state if Suspended state is entered via an interrupt or *tsuspend*. and exited via *tresume*., , *rfid*, *hrfid*, or *mtmsrd*. However, an atomic update will not succeed if only one of the *Load and Reserve I Store Conditional* instruction pair is executed in Suspended state.

### - Programming Note

Note that if a *Store Conditional* instruction within a transaction does not store, it may still be possible for the transaction to succeed. Software must not depend on the two operations having the same outcome. For example, software must not use success of an enclosing transaction as a replacement for checking the condition code from a transactional *Store Conditional* instruction.

### Programming Note

Accessing storage locations in Suspended state that have been accessed transactionally has the potential to create apparent storage paradoxes. Consider, for example, a case where variable X has intial value zero, is updated transactionally to one, is read in Suspended state, subsequently the transaction fails, and variable X is read again. In the absence of external conflicts, the observed sequence of values will be zero, one, zero: old, new, old.

Performing an atomic update on X in Suspended state may be even more confusing. Suppose the atomic sequence increments X, but that the only way to have X=1 is via the transactional store that occurs before entering Suspended state. The store conditional, if it succeeds, will store X=2 and in so doing, kill the transaction. But with the transaction having failed, X was never equal to one.

The flexibility of the Suspended state programming model can create unintuitive results. It must be used with care.

Successful transactions are serialized in some order, and no processor or mechanism is able to observe the accesses caused by any subset of these transactions as occurring in an order that conflicts with this order. Specifically, let processor i execute transactions 0, 1,..., j, j+1, ..., where only successful transactions are numbered, and the numbering reflects program order. Let  $T_{ij}$  be transaction j on processor i. Then there is an ordering of the  $T_{ij}$  such that no processor or mechanism is able to observe the accesses caused by the transactions  $T_{ij}$  in an order that conflicts with this ordering. Note that Suspended state storage accesses are not included in the serialization property.

### **Programming Note**

The ordering of the  $T_{ij}$  for a given i is consistent with program order for processor i.

Because of the difference between a transaction's instantaneous appearance and the finite time required to execute it in an implementation, it is exposed to changes in memory management state in a way that is not true for individual accesses. A change to the translation or protection state that would prevent any access

from taking place at any time during its processing for the transaction compromises the integrity of the transaction. Any such change must either be prevented or must cause the transaction to fail. The architecture will automatically fail a transaction if the memory management state change is accomplished using *tlbie*. implementation may overdetect such conflicts between the tlbie and the transaction footprint. (Overdetection may result from the technique used to detect the conflict. A bloom filter may be used, as an example. Subsequent references to translation invalidation conflicts implicitly include any cases of spurious overdetection.) Changes made in some other manner must be managed by software, for example by explicitly aborting any affected transactions. Examples of instructions that require software management are tlbiel, slbie, slbia, and tlbia.

The atomic nature of a transaction, together with the cumulative memory barrier created by the transaction and the memory barriers created by tbegin. and tend. described below, has the potential to eliminate the need for explicit memory barriers within the transaction, and before and after the transaction as well. However, since there may be a desire to preserve existing algorithms while exploiting transactions, the interaction of memory barriers and transactions is defined. In the presence of transactions, storage access ordering is the same as if no transactions are present, with the following exceptions. Memory barriers that are created while the transaction is running (other than the integrated cumulative barrier of the transaction described below), data dependencies, and SAO do not order transactional stores. Instead, transactional stores are grouped together into an aggregate store, which is performed as an atomic unit with respect to other processors and mechanisms when the transaction succeeds, after all the transactional loads have been performed. With this store behavior, the appearance of transactional atomicity is created in a manner similarly to that for a Load and Reserve / Store Conditional pair. Success of the transaction is conditional on the storage locations specified by the loads not having been stored into by a more recent Suspended state store or by any store by another processor or mechanism since the load was performed. (There are additional conditions for the success of transactions.)

The *tbegin*. instruction creates a memory barrier that immediately precedes the transaction and orders storage accesses pairwise, as follows. Let A and B be sets of storage accesses as defined below. For each pair  $a_ib_j$  of storage accesses such that  $a_i$  is in A and  $b_j$  is in B, the memory barrier ensures that  $a_i$  will be performed with respect to any processor or mechanism, to the extent required by the associated Memory Coherence Required attributes, before  $b_j$  is performed with respect to that processor or mechanism. Set A contains all data accesses caused by instructions preceding the *tbegin*. that are neither Write Through Required nor Caching Inhibited. Set B contains all data accesses

caused by instructions following the *tbegin.*, including Suspended state accesses, that are neither Write Through Required nor Caching Inhibited.

A successful transaction has an integrated memory barrier behavior. When a processor (P1) executes a tend. instruction and tend. processing determines that the transaction will succeed, a memory barrier is created, which orders storage accesses pairwise, as follows. Let A and B be sets of storage accesses as defined below. For each pair aibi of storage accesses such that ai is in A and bi is in B, the memory barrier ensures that a will be performed with respect to any processor or mechanism, to the extent required by the associated Memory Coherence Required attributes, before b<sub>i</sub> is performed with respect to that processor or mechanism. Set A contains all non-transactional data accesses by other processors and mechanisms that have been performed with respect to P1 before the memory barrier is created and are neither Write Through Required nor Caching Inhibited. Set B contains the aggregate store and all non-transactional data accesses by other processors and mechanisms that are performed after a Load instruction executed by that processor or mechanism has returned the value stored by a store that is in set B. Note that the cumulative barrier does not order Suspended state storage accesses interleaved with the transaction.

A tend. instruction that ends a successful transaction creates a memory barrier that immediately follows the transaction and orders storage accesses pairwise, as follows. Let A and B be sets of storage accesses as defined below. For each pair aibi of storage accesses such that ai is in A and bi is in B, the memory barrier ensures that ai will be performed with respect to any processor or mechanism, to the extent required by the associated Memory Coherence Required attributes, before b<sub>i</sub> is performed with respect to that processor or mechanism. Set A contains all data accesses caused by instructions preceding the tend., including Suspended state accesses, that are neither Write Through Required nor Caching Inhibited. Set B contains all data accesses caused by instructions following the tend. that are neither Write Through Required nor Caching Inhibited.

#### Section 1.7+.1 Rollback-Only Transactions

A Rollback-Only Transaction (ROT) is a sequence of instructions that is executed, or not, as a unit. The purpose of the ROT is to enable bulk speculation of instructions with minimum overhead. It leverages the rollback mechanism that is invoked as part of transaction failure handling, but has reduced overhead in that it does not have the full atomic nature of the transaction and its synchronization and serialization properties. The absence of a (normal) transaction's atomic quality means that a ROT must not be used to manipulate shared data.

More specifically, a ROT differs from a normal transaction as follows.

- ROTs are not serialized.

- There are no barriers created by *tbegin*. and *tend*.

- A ROT has no integrated cumulative barrier.

- There is no monitoring of storage locations specified by loads for modification by other processors and mechanisms between the performing of the loads and the completion of the ROT.

- The stores that are included in the ROT need not appear to be performed as an aggregate store. (Implementations are likely to provide an aggregate store appearance, but the correctness of the program must not depend on the aggregate store appearance.)

| End text                                                                                          |

|---------------------------------------------------------------------------------------------------|

| Section 4.1 Parameters Useful to Application Programs                                             |

| Add item 13 to the list: "Maximum transaction level".                                             |

| Section 4.3.2 Data Cache Instructions                                                             |

| Add a programming note at the end of the dcbst description warning against treating it like dcbf. |

| Begin text                                                                                        |

| End text                                                                                          |

| Section 4.4.3 Memory Barrier Instructions                                                         |

| Add another pointer to the introductory material, point-                                          |

The *Memory Barrier* instructions can be used to control the order in which storage accesses are performed. See <crossref to new sec 1.7+, Bk2> for a description of how the *Memory Barrier* instructions interact with transactions. Additional information about these instructions and about related aspects of storage management can be found in Book III.

ing to the description of transaction behavior in

-- Begin text -

Bk2Ch1.

| End text |  |

|----------|--|

|          |  |

Chapter 7+ Transactional Memory Facility [Category: Transactional Memory]

Add a chapter describing TM at the end of Book 2.

| • |

|---|

# 8.1 Transactional Memory Facility Overview

This chapter describes the registers and instructions that make up the transactional memory (TM) facility.

Transactional memory is a shared-memory synchronization construct allowing an application to perform a sequence of storage accesses that appear to occur atomically with respect to other threads.

A set of instructions, special-purpose registers, and state bits in the MSR (see Book III) are used to control a transactional facility that is associated with each hardware thread. A tbegin. instruction is used to initiate transactional execution, and a tend, instruction is used to terminate transactional execution. Loads and stores that occur between the tbegin. and tend. instruction appear to occur atomically. An implementation may prematurely terminate transactional execution for a variety of reasons, rolling back all transactional storage updates that have been made by the thread since the tbegin. was executed, and rolling back the contents of a subset of the thread's book I registers to their contents before the tbegin. was executed. In the event of such premature termination, control is transferred to a software failure handler associated with the transaction, which may then retry the transaction or choose an alternate path depending on the cause of transaction failure. A transaction can be explicitly aborted via a set of conditional abort instructions and an unconditional abort instruction, tabort.. A tsr. instruction is used to suspend or resume transactional execution, while allowing the transaction to remain active.

### Programming Note

A *tbegin.* should always be followed immediately by a *beq* as the first instruction of the failure handler, that branches to the main body of the failure handler. The failure handler should always either retry the transaction or use non-transactional code to perform the same operation. (The number of retries should be limited to avoid the possibility of an infinite loop. The limit could be based on the perceived permanence / transience of the failure.) A failure handler policy which includes trying a different transaction before returning to the one that failed may fail to make forward progress.

### **Programming Note**

The architecture does not include a "fairness guarantee" or a "forward progress" guarantee for transactions. If two processors repeatedly conflict with one another in an attempt to complete a transaction, one of the two may always succeed while the other may always fail. If two processors repeatedly conflict with one another in an attempt to complete a transaction, both may always fail, depending on the details of the transaction. This is different from the behavior of a typical locking routine, in which one or the other of the competitors will generally get the lock.

Transactions performed using this facility are "strongly atomic", meaning that they appear atomic with respect to both transactional and non-transactional accesses performed by other threads. Transactions are isolated from reads and writes performed by other threads; i.e. transactional reads and writes will not appear to be interleaved with the reads and writes of other threads.

Nesting of transactions is supported using a form of nesting called *flattened nesting*, in which transactions that are initiated during transactional execution are subsumed by the pre-existing transaction. Consequently, the effects of a nested transaction do not become visible until the outer transaction commits, and if a nested transaction fails, the entire set of transactions (outer as well as nested) is rolled back, and control is transferred to the outer transaction's failure handler. The barriers created by *tbegin*. and *tend*. and the integrated cumulative barrier that are described in <crossref to ch1 transaction description> are only created for outer transactions and not any transactions nested within them.

References to *Store* instructions, and stores, include *dcbz* and the storage accesses that it causes.

### **Rollback-Only Transactions**

Rollback-Only Transactions (ROTs) differ from nornal transactions in that they are speculative but not atomic. They are initated by a unique variant of *tbegin*. They may be nested with other ROTs or with normal transactions. When a normal transaction is nested within a ROT, the behavior from the normal *tbegin*. until the end of the outer transaction is characteristic of a normal transaction. Although subject to failure from storage conflicts, the typical cause of ROT failure is via a *Tabort* variant that is executed after the program detects an error in its (software) speculation. Except where specifically differentiated or where differences follow from specific differentiation, the following description applies to ROTs as well as normal transactions.

### 8.1.1 Definitions

**Commit:** A transaction is said to *commit* when it successfully completes execution. When a transaction is committed, its transactional accesses become irrevocable, and are made visible to other threads. A transaction completes by either committing or failing.

**Speculative registers:** The set of registers that are saved when a transaction is initiated, and restored upon transaction failure, is a subset of the architected register state, consisting of the General Purpose Registers, Floating-Point Registers, Vector Registers, Vector-Scalar Registers, and the following Special Registers and fields: CR fields other than CR0, LR, CTR, FPSCR, AMR, PPR, VRSAVE, VSCR, DSCR, and TAR. This subset is referred to as the *speculative register state*. The speculative register state includes all

problem-state writable registers with the exception of CR0, , the performance monitor registers, and the Transactional Memory registers. With the exception updates of CR0 and the Transactional Memory registers, explicit updates of registers that are not included in the set of speculative registers are disallowed in Transactional state (i.e. will cause the transaction to fail), but are permitted in Suspended state. Suspended state modifications of these registers will not be rolled back in the event of transaction failure. (Modifications of Transactional Memory registers are only permitted in Non-transactional state. Attempts to modify Transactional Memory registers in other than Non-transactional state will cause a TM Bad Thing type Program interrupt.)

### Programming Note

CR0 and the Transactional Memory registers (TFHAR, TEXASR, TFIAR) are not saved, or restored when the transaction fails, because they are modified as a side effect of transaction failure (so restoring them would lose information needed by the failure handler). The performance monitor registers are not saved or restored because saving and restoring them would add significant implementation complexity and is not needed by software. Also, these registers can be modified asynchronously by the processor, so restoring them when the transaction fails could cause loss of information.

**Transactional accesses:** Data accesses that are caused by an instruction that is executed when the thread is in the Transactional state (see Section 8.2) are said to be *transactional*, or to have been *performed transactionally*. The set of accesses caused by a committed normal transaction is performed as if it were a single atomic access. That is, it is always performed in its entirety with no visible fragmentation. The sets performed by normal transactions are thus serialized: each happens in its entirety in some order, even when that order is not specified in the program or enforced between processors. Until a transaction commits, its set of transactional accesses is provisional, and will be discarded should the transaction fail.

**Non-transactional accesses:** Storage accesses performed in the existing Power® storage model are said to be *non-transactional*. In contrast to transactional storage accesses, there is no provision of atomicity across multiple non-transactional accesses. Non-transactional storage updates are not discarded in the event of a transaction failure.

**Outer transaction:** A transaction that is initiated from the Non-transactional state is said to be an *outer* transaction. A *tbegin.* instruction that initiates an outer transaction is sometimes referred to as an *outer tbegin.* Similarly, a *tend.* instruction with A=0 that ends

an outer transaction is sometimes referred to as an outer *tend*..

**Nested Transaction:** A transaction that is initiated while already executing a transaction is said to be *nested* within the pre-existing transaction. The set of active nested transactions forms a stack growing from the outer transaction.

**Failure**: A transaction failure is an exceptional condition causing the set of transactional storage updates to be discarded, and speculative registers to be reverted to their pre-transactional values.

**Failure handler**: A failure handler is a software component responsible for handling transaction failure. On transaction failure, hardware redirects control to the failure handler associated with the outer transaction.

**Conflict:** A transactional memory access is said to conflict with another transactional or non-transactional access if both accesses reference the same storage block, and at least one of them is a store. If two transactions make conflicting accesses, at least one of them will fail. If a transaction fails as a result of a conflict with a store, the store may have been executed by another processor or may have been executed in Suspended state by the processor with the failing transaction. For a ROT, no conflict is caused if the ROT performs a load and another program performs a non-transactional store to the same block.

A transactional memory access is said to conflict with a *tlbie* if the storage location being accessed is in the page the translation for which is being invalidated by the tlbie. For a ROT, no conflict is caused if the access is a load.

A Suspended state cache control instruction is said to cause a conflict if it would cause the destruction of a transactional update or if it would make a transactional update visible to another thread.

# 8.2 Transactional Memory Facility States

The transactional memory facility supports several modes of operation, referred to in this document as the *transaction state*. These states control the behavior of storage accesses made during the transaction and the handling of transaction failure. Changes to transaction state affect all transactions currently using the transactional facility on the affected thread: the outer transaction as well as any nested transactions, should they exist.

**Non-transactional**: The default, initial state of execution; no transaction is executing. The transactional facility is available for the initiation of a new transaction.

**Transactional**: This state is initiated by the execution of a *tbegin*. instruction in the Non-transactional state.

Storage accesses (data accesses) caused by instructions executed in the Transactional state are performed transactionally. Other storage accesses associated with instructions executed in the Transactional state (instruction fetches, implicit accesses) are performed non-transactionally. In the event of transaction failure, failure is recorded as defined in Section 8.3.2, and control is transferred to the failure handler as described in Section 8.3.3.

**Suspended**: The Suspended execution state is explicitly entered with the execution of a *tsuspend*. form of *tsr*. instruction during a transaction, the execution of a *trechkpt*. instruction from non-transactional state, or as a side-effect of interrupt while in the Transactional state. Storage accesses and accesses to SPRs that are not part of the speculative register state are performed non-transactionally; they will be performed independently of the outcome of the transaction. The initiation of a new transaction is prevented in this state. In the event of transaction failure, failure recording is performed as defined in Section 8.3.2, but failure handling is usually deferred until transactional execution is resumed (see Section 8.3.3 for details).

Until failure occurs, Load instructions that access storage locations that were transactionally written by the same thread will return the transactionally written data. After failure is detected, but before failure handling is performed, such loads may return either the transactionally written data, or the current non-transactional contents of the accessed location. The *tcheck* instruction can be used to determine whether any previous such loads may have returned non-transactional contents.

Suspended state Store instructions that access cache blocks that have been accessed transactionally (due to load or store) by the same thread may cause the transaction to fail.

### Programming Note —

The intent of the Suspended execution state is to temporarily escape from transactional handling when transactional semantics are undesirable. Examples of such cases include storage updates that should be retained in the event of transactional failure, which is useful for debugging, interthread communication, the access of Caching-Inhibited storage, and the handling of interrupts. In the event of transaction failure during the Suspended execution state, failure handling is deferred until transactional execution is resumed, allowing the block of Suspended state code to complete its activities.

### Programming Note

During Suspended state execution, accessing cache blocks that have been transactionally accessed by the same thread prior to entering Suspended state requires special care, because failure may occur due to uncontrollable events such as interactions with other threads or the operating system. Up until a transaction fails, loads from transactionally modified cache blocks will return the transactionally modified data. However once the transactionally updated version of storage, or the most recent non-transactional version. Stores to transactionally modified blocks may or may not cause the thread's transaction to fail.

Table 1 enumerates the set of Transactional Memory instructions and events that can cause changes to the transaction state. Transaction states are abbreviated N (Non-transactional), T (Transactional), and S (Suspended). (Interrupts, and the , *rfid*, *hrfid*, and *mtmsrd* instructions, can also cause changes to the transaction state; see Book III.)

### - Programming Note

**tbegin.** in Suspended state merely updates CR0. When **tbegin.** is followed by **beq**, this will result in a transfer to the failure handler. Nothing more severe (e.g. an interrupt) is required.

| Instr/<br>event<br>State | tbegin.        | tend.                                                    | Abort caused by <b>tabort</b> . and conditional <b>tabort</b> . variants | tsuspend.      | tresume.       | Failure             | treclaim.      | trechkpt.      |

|--------------------------|----------------|----------------------------------------------------------|--------------------------------------------------------------------------|----------------|----------------|---------------------|----------------|----------------|

| N <sup>7</sup>           | Т              | N <sup>3</sup>                                           | N <sup>3</sup>                                                           | N <sup>3</sup> | N <sup>3</sup> | Not appli-<br>cable | N <sup>8</sup> | S <sup>9</sup> |

| Т                        | Т              | N, if outer trans-<br>action or A=1<br>form; otherwise T | N <sup>4,5</sup>                                                         | S              | T              | N <sup>4,5</sup>    | N <sup>4</sup> | S <sup>8</sup> |

| s                        | s <sup>1</sup> | S <sup>8</sup>                                           | s <sup>4</sup>                                                           | s <sup>3</sup> | T <sup>6</sup> | s <sup>4</sup>      | N <sup>4</sup> | S <sup>8</sup> |

#### **Notes**

- 1. CR0 updated indicating transactional initiation was unsuccessful, due to a pre-existing transaction occupying the transactional facility.

- 3. Execution of these operations does not affect transaction state, allowing for the instructions to be used in software modules called from Non-transactional, Transactional, and Suspended paths.

- 4. If failure recording has not previously occurred, failure recording is performed as defined in Section 8.3.2.

- 5. Failure handling is performed as defined in Section 8.3.3.

- 6. If failure has occurred during Suspended execution, failure handling will be performed sometime after the execution of *tresume*, and no later than the set of events listed in Section 8.3.3.

- 7. Any attempt to execute a TM instruction when MSR<sub>TM</sub>=0 causes a Transactional Memory type of Facility Unavailable interrupt. Any attempt to execute a TM instruction in other than hypervisor state when HFSCR<sub>TM</sub>=0 causes a Transactional Memory type of Hypervisor Facility Unavailable interrupt. The contents of this row assumes that Transactional Memory is enabled.

- 8. Generate TM Bad Thing type Program interrupt.

- 9. If TEXASR<sub>FS</sub>=0, generate a TM Bad Thing type Program interrupt.

Table 1: Transaction state transitions caused by TM instructions and transaction failure

### 8.2.1 The TDOOMED bit

The status of an active transaction is summarized by a transaction doomed bit (TDOOMED) that resides in an implementation-dependent location. When 0, it indicates that the active transaction is valid, meaning that it remains possible for the transaction to commit successfully, if failure does not occur before committing. When 1 it indicates that transaction failure has already occurred for the transaction.

The TDOOMED bit is set to 0 upon the successful initiation of an outer transaction by *tbegin.*. It is set to 1 when failure occurs or as a result of executing *trech-kpt.*. When failure occurs, TDOOMED is set to 1 before any other effects of the transaction failure (recording the failure in TEXASR, rollback of transactional stores, over-writing of the transactionally accessed locations by a conflicting store, etc.) are visible to software executing on the processor that executed the transaction. In Non-transactional state, the value of TDOOMED is undefined.

### 8.3 Transaction Failure

# 8.3.1 Causes of Transaction Failure

A transaction failure is said to be "externally-induced" if the failure is caused by a thread other than the transactional thread. Likewise, a transaction failure is said to be "self-induced" if the failure is caused by the transactional thread itself.

For self-induced failure as a result of attempting to execute an instruction that is forbidden in the Transactional state, a Privileged Instruction type of Program Interrupt takes precedence over transaction failure. (For example, an attempt to execute **stdcix** in Transactional state and problem state will result in a Privileged Instruction type of Program interrupt.) Transaction failure takes precedence over all other interrupt types. The relevant instructions are listed in the third bullet of the second set of bullets below and the first bullet in the third set of bullets below.

In general, a ROT will not fail in the following scenarios when the failure is specified as a conflict on a transactional access and the access is a load.

Transactions will fail for the following externally-induced causes

- Conflict with transactional access by another thread

- Conflict with non-transactional access by another thread

- Conflict with a translation invalidation caused by a tlbie performed by another thread

Transactions will fail for the following self-induced causes

- Abort caused by the execution of tabort., tabortdc., tabortdci., tabortwc., tabortwci. or treclaim. instruction.

- Transaction level overflow, defined as an attempt to execute *tbegin*, when the transaction level is already at its maximum value

- Footprint overflow, defined as an attempt to perform a storage access in Transactional state which exceeds the capacity for tracking transactional accesses.

- Execution of the following instructions while in the Transactional state: doze, sleep, nap, rvwinkle, icbi, , dcbf, dcbi, dcbst, [h]rfid, , mtmsr[d], mtsle, mtsr, mtsrin, msgsnd, msgsndp, msgclr, msgclrp, slbie, slbia, slbmte, slbfee, and tlbie[l]. (These instructions are considered to be disallowed in Transactional state.) The disallowed instruction is not executed; failure handling occurs before it has been executed.

### Programming Note

Note that execution of a Power Saving instruction in Suspended state causes a TM Bad Thing type Program interrupt.

- Execution, while in Transactional state, of *mtspr* specifying an SPR that is not part of the speculative register state and is not a Transactional Memory SPR. The *mtspr* is not executed; failure handling occurs before it has been executed. (Modification of XER<sub>FXCC</sub> and CR<sub>CR0</sub> are allowed, but the changes will not be rolled back in the event of transaction failure.)

- Conflict caused by a Suspended state store to a block that was previously accessed transactionally.

- Conflict caused by a Suspended state *tlbie* that specifies a translation that was previously used transactionally. (This case will be recorded as a translation invalidation conflict because it may be hard to differentiate from a conflict caused by a *tlbie* performed by another thread and because it is highly likely to be a transient failure.)

For each of the following potential causes, the transaction will fail if the absence of failure would compromise transaction semantics; otherwise, whether the transaction fails is undefined.

- Execution of the following instructions while in the Transactional state: eciwx, ecowx, Ibzcix, Idcix, Ihzcix, Iwzcix, stbcix, stdcix, sthcix, stwci. The disallowed instruction is not executed; failure handling occurs before it has been executed. (These instructions are considered to be disallowed in Transactional state if they cause transaction failure in Transactional state.) Execution of these instructions in the Suspended state is allowed and does not cause transaction failure.

- Execution of the following instructions in the Transactional state: *wait*, *waitasec*. The disallowed instruction is not executed; failure handling occurs before it has been executed. (These instructions are considered to be disallowed in a transaction if they cause transaction failure.)

- Execution of the following instructions in the Suspended state: *wait*, *waitasec*. The disallowed instruction is treated as a no-op; failure recording occurs. (These instructions are considered to be disallowed in a transaction if they cause transaction failure.)

- Access of a disallowed type while in the Transactional state: Caching Inhibited, Write Through Required, and Memory Coherence not Required for data access; Caching-Inhibited for instruction fetch. The disallowed access is not performed; failure handling occurs such that the instruction that would cause (or be associated with, for instruction fetch) the disallowed access type appears not to have been executed. Accesses of this type in the Suspended state are allowed and do not cause transaction failure.

- Instruction fetch from a block that was previously written transactionally (reported as a unique cause that includes both self-induced and externallyinduced instances)

- dcbf, dcbi, or icbi specifying a block that was previously accessed transactionally, in either of the following cases.

### **Programming Note** -

Note that *dcbf* with L=3 should never compromise transactional semantics, but it is still permitted to cause transaction failure in Suspended state and it is disallowed in Transactional state.

- the instruction (dcbf, dcbi, or icbi) is executed in Suspended state on the processor executing the transaction (self-induced conflict)

- the instruction is executed by another processor (externally-induced conflict)

- dcbst specifying a block that was previously written transactionally, in either of the following cases.

- dcbst is executed in Suspended state on the processor executing the transaction (selfinduced conflict)

- dcbst is executed by another processor (externally-induced conflict)

- Cache eviction of a block that was previously accessed transactionally

### Programming Note

WARNING: Software should not depend for its correct execution on the behavior (whether or not the relevant transaction fails) of the cases described in the preceding set of bullets. The behavior is likely to vary from design to design. Such a dependence would impact the software's portability without any tangible advantage.

### Programming Note

Because the atomic nature of a transaction implies an apparent delay of its component accesses until they can be performed in unison, the use of cache control instructions to manage cache residency and/or the performing of storage accesses may have unexpected consequences. Although they may not cause transaction failure directly, their use in a transaction is strongly discouraged.

If an instruction or event does not cause transaction failure, it behaves as defined in the architecture.

The set of failure causes and events are further classified as *precise* and *imprecise* failure causes. All externally induced events are imprecise, and all self-induced

events are precise with the exception of the following cases:

- Self-induced conflicts caused by instruction fetch

- Self-induced conflicts caused by footprint overflow

- Self-induced conflicts in Suspended state, caused by a store to a block that was previously accessed transactionally, or a *dcbf*, *dcbi*, or *icbi* specifying a block that was previously accessed transactionally, or a *dcbst* specifying a block that was previously written transactionally, or a *tlbie* specifying a translation that was previously used transactionally.

When failure recording and handling occur (as defined in Section 8.3.2 and 8.3.3) for a precise failure, they will occur precisely according to the sequential execution model, adhering to the following rules:

- Effects of the failure occur such that all instructions preceding the instruction causing the failure appear to have completed with respect to the executing thread.

- The instruction causing the failure may appear not to have begun execution (except for causing the failure), or may have completed, depending on the failure cause.

- 3. Architecturally, no subsequent instruction has begun execution.

Failure handling for imprecise failure types is guaranteed to occur no later than the execution of *tend.* with A=1 or TEXASR<sub>TL</sub> =1. Failure recording for imprecise failure types is guaranteed to occur no later than failure handling. Any operation that can cause imprecise failure if performed in-order can also cause imprecise failure if performed out-of-order.

### **Programming Note**

Because instruction fetch from a transactionally written block may result in failure, it is recommended that transactionally accessed data and transactionally accessed instructions not be colocated within a single block.

### - Programming Note

The architecture does not detect and cause transaction failure for translation invalidations to transactionally accessed pages or segments, when the translation invalidation is caused by instructions other than *tlbie* (i.e. *slbie, slbia, tlbiel, tlbia*). Consequently, software is responsible for aborting transactions in circumstances where such local translation invalidations may affect a local transaction.

# 8.3.2 Recording of Transaction Failure

When transaction failure occurs, information about the cause and circumstances of failure are recorded in SPRs associated with the transactional facility. Failure recording is performed a single time per transaction that fails, controlled by the state of the TEXASR failure summary (FS) bit; when 0, FS indicates that failure recording has not already been performed, and is therefore permissible.

The following RTL function specifies the actions taken during the recording of transaction failure:

```

TMRecordFailure(FailureCause)

#FailureCause is 32-bit cause

code

if TEXASR_{ES} = 0

if failure IA known then

TFIAR <- CIA

TEXASR<sub>37</sub> <- 1

TFIAR <- approximate instruction address

TEXASR<sub>37</sub> <- 0

TEXASR<sub>0:31</sub> <- FailureCause

if \text{MSR}_{\text{TS}}\text{=}0\text{b01} then \text{TEXASR}_{\text{Suspended}} <- 1

TEXASR<sub>PR</sub> <- MSR<sub>PR</sub>

TEXASR<sub>HV</sub> <- MSR<sub>HV</sub>

TFIAR_{HV\ PR} <- MSR_{HV\ PR}

TEXASR<sub>FS</sub> <- 1

TDOOMED <- 1

```

When failure recording occurs, the TEXASR and TFIAR SPRs are set indicating the source of failure. When possible, TFIAR is set to the effective address of the instruction that caused the failure, and TEXASR $_{37}$  is set to 1 indicating that the contents of TFIAR are exact. When the instruction address is not known exactly, an approximate value is placed in TFIAR and TEXASR $_{37}$  is set to 0. TEXASR bits 0:31 are set indicating the cause of the failure, and the TEXASR $_{Suspended}$ , TEXASR $_{HV}$ , TEXASR $_{PR}$ , TFIAR $_{HV}$ , and TFIAR $_{PR}$  bits are set indicating the machine state in which the failure was recorded. TEXASR $_{TL}$  is unchanged. The TDOOMED bit is set to 1.

### **Programming Note**

TFIAR is intended for use in the debugging of transactional programs by identifying the source of transaction failure. Because TFIAR may not always be set exactly, software should test TEXASR $_{37}$  before use; if zero, the contents of TFIAR are an approximation.

# 8.3.3 Handling of Transaction Failure

After detection of failure, the timing of failure handling is dependent on the state of the transactional facility.

In Transactional state, failure handling may occur immediately, but an implementation is free to delay handling until one of the following failure handling synchronizing events occurs in Transactional state.

- An abort caused by the execution of a tabort., tabortdc., tabortdci., tabortwc., or tabortwci. instruction

- An attempt, in Transactional state, to execute a disallowed instruction, perform an access of a disallowed type, or execute an *mtspr* instruction that specifies an SPR that is not part of the speculative register state and is not a Transactional Memory SPR.

- An attempt to commit a transaction, caused by the execution of *tend*. with A = 1 or when TEXASR<sub>TL</sub> = 1.

- The execution of a *treclaim*. instruction.

If the failure is caused by an event in the preceding list, failure handling occurs immediately. (If the failure is caused by *treclaim.*, CR0 is not set to indicate failure and the transaction's failure handler is not invoked.)

When failure handling occurs, speculative registers are reverted to their pre-transactional values, all transactional updates to storage are discarded if they have not previously been discarded, and any resources occupied by the transaction are discarded. CR0 is set to 0b101 || 0. The transaction state is set to Non-transactional, and control flow is redirected to the instruction address stored in TFHAR.

The following RTL function specifies the actions taken during the handling of transaction failure:

Upon failure detected in Suspended state from causes other than the execution of a *treclaim.*, *tabort.*, *tabortdc.*, *tabortdc.*, or *tabortwci.* instruction, failure recording occurs as described in Section 8.3.2, but failure handling is deferred until the transaction is resumed. Once resumed, failure handling will occur no later than the set of failure handling synchronizing events listed above. However, speculative storage updates may be discarded at any time between

the time that failure is detected, up until the occurrence of one of the failure handling synchronizing events listed above. Upon failure in Suspended state caused by *treclaim.*, failure recording, discarding of speculative storage updates, and reverting of the speculative registers to pre-transactional values are immediate (but CR0 is not set to indicate failure and the transaction's failure handler is not invoked). Upon failure in Suspended state caused by a conditional or unconditional *Abort* instruction, failure recording and discarding of speculative storage updates are immediate. The remainder of failure handling occurs immediately after the transaction is resumed (e.g., the next instruction executed after the *tresume* (or *rfid*, etc.) is the instruction at the address contained in TFHAR).

### **Programming Note**

A *Load* instruction executed immediately after *tre-claim.* or a conditional or unconditional *Abort* instruction is guaranteed not to load a speculative storage update.

### - Engineering Note

In order to preserve the appearance of precise failures, failure handling should occur no later than the following events that would allow such delay in failure handling to be detected for the precise causes of failure

- An abort caused by the execution of tabort., tabortdc., tabortdci., tabortwc., tabortwci.

- The execution of *treclaim*.

- An execution of tsr., tend., rfid, hrfid, or mtmsrd, that change Transactional state

- Interrupts

# 8.4 Transactional Memory Facility Registers

The architecture is augmented with three Special Purpose Registers in support of transactional memory. TFHAR stores the effective address of the software failure handler used in the event of transaction failure. TFIAR is used to inform software of the exact location of the transaction failure, when possible. TEXASR contains a transaction level indicating the nesting depth of an active transaction, as well as an indicator of the cause of transaction failure and some machine state when the transaction failed. These registers can be accessed only when MSR $_{\rm TM}=1$  and either HFSCR $_{\rm TM}=1$  or the processor is in hypervisor state, (see Book III-S), and can be written only when also in Non-transactional state.

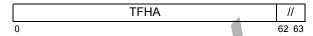

# 8.4.1 Transaction Failure Handler Address Register (TFHAR)

The Transaction Failure Handler Address Register is a 64-bit SPR that records the effective address of a software failure handler used in the event of transaction failure. Bits 62:63 are reserved.

This register is written with the NIA for the *tbegin.* as a side-effect of the execution of an outer *tbegin.* instruction (*tbegin.* executed in the Non-transactional state).

# 8.4.2 Transaction Exception And Summary Register (TEXASR)

The Transaction Exception And Summary Register is a 64-bit register, containing a transaction level (TEXAS- $R_{TL}$ ) and summary information for use by transaction failure handlers. Bits 0:31 are called the *failure cause* in the instruction descriptions.

TEXASR 63

### Bit(s Description

### 0:6 Failure Code

The Failure Code is copied from the *tabort*. or *treclaim*. source operand. When set, TFIAR is exact.

### 7 Failure Persistent

The failure is likely to recur on each execution of the transaction. This bit is a hint. It is set to 1 for causes in bits 8:11, copied from the *tabort.* or *treclaim.* source operand when RA is nonzero, and set to 0 for all other failure causes.

### Programming Note

The Failure Persistent bit may be viewed as an eighth bit in the failure code in that both fields are supplied by the least significant byte of RA and software may use all eight to differentiate among the cases for which it performs an abort or reclaim. However, software is expected to organize its cases so that bit 7 predicts the persistence of the case.

### 8 Disallowed

The instruction, SPR, or access type is not permitted. When set, TFIAR is exact. <cross-ref to 1.3.1 list of inst>

### Programming Note -

An instruction fetch to storage that is Caching Inhibited, while nominally disallowed, will be reported as Implementation-specific (bit 15). This choice was made because it seems like a relatively unlikely programming error, and there is a significant chance that data from an external conflict (store by another thread) could indirectly cause a wild branch to storage that is Caching Inhibited.

### 9 Nesting Overflow

The maximum transaction level was exceeded. When set, TFIAR is exact.

### 10 Footprint Overflow

The tracking limit for transactional storage accesses was exceeded. When set, TFIAR is an approximation.

### Programming Note

Note that transactional footprint tracking resources may be shared by multiple programs executing concurrently. Depending on the circumstances, this failure cause may or may not be persistent

### 11 Self-Induced Conflict

A self-induced conflict occurred in Suspended state, due to one of the following: a store to a block that was previously accessed transactionally; a *dcbf*, *dcbi*, or *icbi* specifying a block that was previously accessed transactionally; a *dcbst* specifying a block that was previously written transactionally; or a *tlbie* that specifies a translation that was previously used transactionally. When set, TFIAR may be exact.

### 12 Non-Transactional Conflict

A conflict occurred with a non-transactional access by another processor. When set, TFIAR is an approximation.

### 13 Transaction Conflict

A conflict occurred with another transaction. When set, TFIAR may be exact.

### 14 Translation Invalidation Conflict

A conflict occurred with a TLB invalidation. When set, TFIAR is an approximation.

### 15 Implementation-specific

An implementation-specific condition caused the transaction to fail. Such conditions are transient and the value in the TFIAR may be exact.

#### 16 Instruction Fetch Conflict

An instruction fetch (by this or another thread) was performed from a block that was previously written transactionally. Such conditions are transient and the value in the TFIAR may be exact.

17-30 Reserved for future failure causes

#### 31 Abort

An abort was caused by the execution of a *tabort.*, *tabortdc.*, *tabortdci.*, *tabortwc.*, *tabortwci.* or *treclaim.* instruction. When due to *tabort.* or *treclaim.*, bits in TEXASR<sub>0:7</sub> are user-supplied. When set, TFIAR is exact.

### 32 Suspended

When set to 1, the failure was recorded in Suspended state. When set to 0, the failure was recorded in Transactional state.

33 Reserved

### 34:35 **Privilege**

The thread was in this privilege state (HV||PR) when the failure was recorded.

### **Programming Note**

When looking at the state of the bits above, note that the transaction may fail in one state but the failure may be recorded in another if the failure cause is imprecise. An access that causes footprint overflow and is immediately followed by a *tsuspend*. is an example of when such a scenario is likely.

### 36 Failure Summary (FS)

Set to 1 when a failure has been detected and failure recording has been performed.

### 37 TFIAR Exact

Set to 1 when the value in the TFIAR is exact. Otherwise the value in the TFIAR is approximate.

### 38 **ROT**

Set to 1 when a ROT is initiated. Set to zero when a non-ROT *tbegin*. is executed.

39 Reserved

### 40:51 Reserved

### 52:63 Transaction Level (TL)

Transaction level (nesting depth + 1) for the active transaction, if any; otherwise 0 if the most recently executed transaction completed successfully, or the transaction level at which the most recently executed transaction failed if the most recently executed transaction did not complete successfully.

### Programming Note -

A value of 1 corresponds to an outer transaction. A value greater than 1 corresponds to a nested transaction.

The transaction level in TEXASR $_{TL}$  contains an unsigned integer indicating whether the current transaction is an outer transaction, or is nested, and if nested, its depth. The maximum transaction level supported by a given implementation is of the form  $2^t$  - 1. The value of t corresponding to the smallest maximum is 4; the value of t corresponding to the largest maximum is 12. This value is tied to the "Maximum transaction level" parameter useful for application programmers, as specified in Section 4.1. The high-order 12-t bits of TEXASR $_{TL}$  are treated as reserved.

Transaction failure information is contained in TEXASR $_{0:37}$ . The fields of TEXASR are initialized upon the successful initiation of a transaction from the Nontransactional state, by setting TEXASR $_{TL}$  to 1, indicating an outer transaction, and all other fields to 0.

When transaction failure is recorded, the failure summary bit TEXASR<sub>FS</sub> is set to 1, indicating that failure has been detected for the active transaction and that failure recording has been performed. TEXASR<sub>0:31</sub> are set indicating the source of the failure. Exactly one of bits 8 through 31 will be set indicating the instruction or event that caused failure. In the event of failure due to the execution of a tabort., tabortdc., tabortdci., tabortwc., tabortwci. or treclaim. instruction, TEXASR<sub>31</sub> is set to 1, and, for *tabort*. and *treclaim*., a software defined failure code is copied from a register operand to TEXASR<sub>0:7</sub>. TEXASR<sub>Suspended</sub> indicates whether the transaction was in the Suspended state at the time that failure occurred. The value of MSR<sub>HV</sub> and MSR<sub>PR</sub> at the time that failure occurs are copied to TEXASR<sub>34</sub> and TEXASR<sub>35</sub>, respectively. In some circumstances, the failure causing instruction address in TFIAR may not be exact. In such circumstances, TEXASR<sub>37</sub> is set to 0 indicating that the contents of TFIAR are not exact; otherwise TEXASR<sub>37</sub> is set to 1.

### **Programming Note**

The transaction level contained in  $\mathsf{TEXASR}_\mathsf{TL}$  should be interpreted by software as follows:

When in the Transactional or Suspended state, this field contains an unsigned integer representing the transaction level of the active transaction, with 1 indicating an outer transaction, and a number greater than 1 indicating a nested transaction. The nesting depth of the active transaction is TEXAS- $R_{TL} - 1. \label{eq:RTL}$

When in the Non-transactional state, TEXASR<sub>TL</sub> contains 0 if the last transaction committed successfully, otherwise it contains the transaction level at which the most recent transaction failed.

### Programming Note

The Privilege bits in TEXASR represent the state of the machine at the point when failure occurs. This information may be used by problem-state software to determine whether an unexpected hypervisor or operating system interaction was responsible for transaction failure. This information may be useful to operating systems or hypervisors when restoring register state for failure handling after the transactional facility was reclaimed, to determine which of the operating system or the hypervisor has retained the pre-transactional version of the speculative registers.

### - Engineering Note

If multiple failure causes occur at the same time, hardware must choose one cause to report. In general, it will be most beneficial to report a persistent cause when both types occur simultaneously.

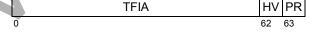

# 8.4.3 Transaction Failure Instruction Address Register (TFIAR)

The Transaction Failure Instruction Address Register is a 64-bit SPR that is set to the exact effective address of the instruction causing the failure, when possible. Bits 62:63 contain  $MSR_{HV\ PR}$  at the time of the failure..

In certain cases, the exact address may not be available, and therefore TFIAR will be an approximation. An approximate value will point to an instruction near the instruction that was executing at the time of the failure. TFIAR accuracy is recorded in an Exact bit residing in  $TEXASR_{37}$ .

# 8.5 Transactional Facility Instructions

The *Transactional Memory* instructions may only be executed when  $MSR_{TM}=1$  and either  $HFSCR_{TM}=1$  or the processor is in hypervisor state (see Book III-S).

Similar to the *Floating-Point Status* and *Control Register* instructions, modifications of transaction state caused by the execution of *Transactional Memory* instructions or by failure handling synchronize the effects of exception-causing floating-point instructions executed by a given processor. Executing a Transactinal Memory instruction, or invocation of the failure handler, ensures that all floating-point instructions previously initiated by the given processor have completed before the transaction state is modified, and that no subsequent floating-point instructions are initiated

by the given processor until the transaction state has been modified. In particular:

- All exceptions that will be caused by the previously initiated instructions are recorded in the FPSCR before the transaction state is modified.

- All invocations of the system floating-point enabled exception error handler that will be caused by the previously initiated instructions have occurred before the transaction state is modified.

- No subsequent floating-point instruction that alters the settings of any FPSCR bits is initiated until the transaction state has been modified.

(Floating-point Storage Access instructions are not affected.)

### Transaction Begin

X-form

tbegin. R

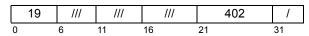

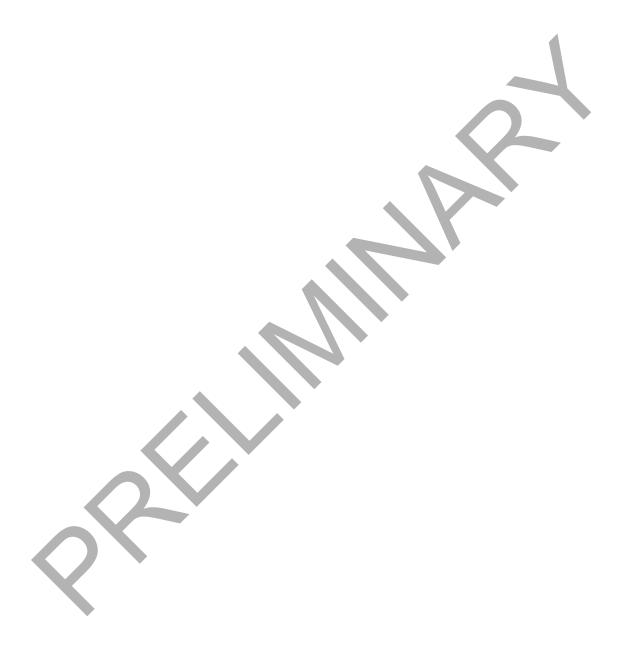

| 31 | Α   | // R | /// | /// | 654 | 1  |

|----|-----|------|-----|-----|-----|----|

| 0  | 6 7 | 10   | 11  | 16  | 21  | 31 |

```

ROT <- R

CRO <- 0 \mid MSR<sub>TS</sub> \mid 0

#Non-transactional

if MSR_{TS} = 0b00 then