# Intel<sup>®</sup> Virtualization Technology for Directed I/O Architecture Specification

February 2006

Order Number: D51397-001

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EX-PRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RE-LATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FIT-NESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Intel may make changes to specifications and product descriptions at any time, without notice.

Developers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Improper use of reserved or undefined features or instructions may cause unpredictable behavior or failure in developer's software code when running on an Intel processor. Intel reserves these features or instructions for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from their unauthorized use.

The Intel<sup>®</sup> IA-32 architecture processors (e.g., Pentium<sup>®</sup> 4 and Pentium III processors) may contain design defects or errors known as errata. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting Hyper-Threading Technology and an HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See <u>http://www.intel.com/technology/hyperthread/</u> for more information including details on which processors support HT Technology.

Intel<sup>®</sup> Virtualization Technology requires a computer system with an enabled Intel<sup>®</sup> processor, BIOS, virtual machine monitor (VMM) and for some uses, certain platform software enabled for it. Functionality, performance or other benefits will\_vary depending on hardware and software configurations. Intel<sup>®</sup> Virtualization Technology-enabled BIOS and VMM applications are currently in development.

Intel<sup>®</sup> Extended Memory 64 Technology (Intel<sup>®</sup> EM64T) requires a computer system with a processor, chipset, BIOS, OS, device drivers and applications enabled for Intel EM64T. **Processor will not operate (including 32-bit operation) without an Intel EM64T-enabled BIOS.** Performance will vary depending on your hardware and software configurations. **Intel EM64T-enabled OS, BIOS, device drivers and applications may not be available.** Check with your vendor for more information.

Intel, Pentium, Intel Xeon, Intel NetBurst, Intel Core Solo, Intel Core Duo, Intel Pentium D, Itanium, MMX, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937 Denver, CO 80217-9808

or call 1-800-548-4725 or visit Intel's website at http://www.intel.com

Copyright © 2006 Intel Corporation

Version 1.0

# **CONTENTS**

#### PAGE

#### **CHAPTER 1** INTRODUCTION 1.1 1.2 1.3 1.4

#### CUADTED 2

| CHAFIE        |                                                                        |     |

|---------------|------------------------------------------------------------------------|-----|

| <b>OVERVI</b> |                                                                        |     |

| 2.1           | INTEL <sup>®</sup> VIRTUALIZATION TECHNOLOGY OVERVIEW                  | 2-1 |

| 2.2           | VMM AND VIRTUAL MACHINES                                               | 2-1 |

| 2.3           | HARDWARE SUPPORT FOR PROCESSOR VIRTUALIZATION                          |     |

| 2.4           | I/O VIRTUALIZATION                                                     | 2-2 |

| 2.5           | INTEL <sup>®</sup> VIRTUALIZATION TECHNOLOGY FOR DIRECTED I/O OVERVIEW | 2-3 |

| 2.5.1         | Hardware Support for DMA Remapping                                     | 2-3 |

| 2.5.2         | OS Usages of DMA Remapping                                             | 2-4 |

| 2.5.3         | VMM Usages of DMA Remapping.                                           | 2-5 |

| 2.5.3.1       | DMA Remapping Usages by Guests                                         | 2-6 |

| 2.5.4         | Interaction with Processor Virtualization                              | 2-7 |

#### **CHAPTER 3**

| 3.1     | DOMAINS AND ADDRESS TRANSLATION            | 3-1  |

|---------|--------------------------------------------|------|

| 3.2     | MAPPING DEVICES TO DOMAINS                 | 3-2  |

| 3.2.1   | Source Identifier                          | 3-2  |

| 3.2.2   | Root-Entry                                 | .3-3 |

| 3.2.3   | Context-Entry                              | 3-4  |

| 3.2.3.1 | Context Caching                            | 3-5  |

| 3.3     | ADDRESS TRANSLATION                        | 3-6  |

| 3.3.1   | Multi-Level Page Table                     |      |

| 3.3.1.1 | Adjusted Guest Address Width (AGAW)        | .3-8 |

| 3.3.1.2 | Multi-level Page Table Translation         | 3-9  |

| 3.3.1.3 | I/O Translation Lookaside Buffer (IOTLB)   | 3-9  |

| 3.4     | DMA REMAPPING FAULTS                       | 3-10 |

| 3.4.1   | Fault Logging                              | 3-11 |

| 3.4.1.1 | Primary Fault Logging                      | 3-12 |

| 3.4.1.2 | Advanced Fault Logging                     | 3-12 |

| 3.4.1.3 | Fault Priority                             |      |

| 3.4.2   | Fault Reporting                            |      |

| 3.4.3   | Hardware Handling of Faulting DMA Requests | 3-13 |

#### **CHAPTER 4**

#### HARDWARE CONSIDERATIONS

| 4.1 | HANDLING INTERRUPT MESSAGES                               | 4-1 |

|-----|-----------------------------------------------------------|-----|

| 4.2 | ASSIGNING DEVICES BEHIND PCI EXPRESS TO PCI/PCI-X BRIDGES | 4-1 |

| 4.3 | ASSIGNING PCI EXPRESS DEVICES USING PHANTOM FUNCTIONS     | 4-2 |

| 4.4 | HANDLING DMA REQUESTS CROSSING PAGE BOUNDARY              | 4-2 |

| 4.5 | HANDLING OF ZERO-LENGTH DMA                               | 4-2 |

| 4.6 | DMA REMAPPING - SOFTWARE VIEW          | 4-3 |

|-----|----------------------------------------|-----|

| 4.7 | HANDLING DMA TO RESERVED SYSTEM MEMORY | 4-3 |

| 4.8 | PEER TO PEER CONSIDERATIONS            | 4-4 |

| 4.9 | HANDLING OF ISOCHRONOUS DMA            | 4-4 |

## CHAPTER 5 BIOS CONSIDERATIONS

| DIU3 C | UNSIDERATIONS                                    |       |

|--------|--------------------------------------------------|-------|

| 5.1    | DMA REMAPPING REPORTING STRUCTURE                | 5-1   |

| 5.2    | DMA REMAPPING STRUCTURE TYPES                    | 5-2   |

| 5.3    | DMA REMAPPING HARDWARE UNIT DEFINITION STRUCTURE | 5-3   |

| 5.3.1  | Device Scope Structure                           | . 5-4 |

| 5.3.2  | Device Scope Example                             | .5-5  |

| 5.4    | RESERVED MEMORY REGION REPORTING STRUCTURE       | 5-7   |

#### **CHAPTER 6**

#### TRANSLATION STRUCTURE FORMATS

| 6.1 | ROOT-ENTRY       | 6-1 |

|-----|------------------|-----|

| 6.2 | CONTEXT-ENTRY    | 6-3 |

| 6.3 | PAGE-TABLE ENTRY | 6-6 |

| 6.4 | FAULT RECORD     | 6-8 |

## CHAPTER 7

| CHAPT    | ER 7                                              |

|----------|---------------------------------------------------|

| DMA RE   | EMAPPING REGISTERS                                |

| 7.1      | REGISTER LOCATION                                 |

| 7.2      | SOFTWARE ACCESS TO HARDWARE REGISTERS             |

| 7.3      | REGISTER ATTRIBUTES                               |

| 7.4      | REGISTER DESCRIPTIONS                             |

| 7.4.1    | Version Register                                  |

| 7.4.2    | Capability Register                               |

| 7.4.3    | Extended Capability Register7-10                  |

| 7.4.4    | Global Command Register                           |

| 7.4.5    | Global Status Register                            |

| 7.4.6    | Root-Entry Table Address Register7-17             |

| 7.4.7    | Context Command Register7-18                      |

| 7.4.8    | IOTLB Invalidation Unit Registers7-21             |

| 7.4.8.1  | IOTLB Invalidate Register7-22                     |

| 7.4.8.2  | Invalidate Address Register7-25                   |

| 7.4.9    | Hardware Caching Details7-26                      |

| 7.4.9.1  | Caching Mode Behavior                             |

| 7.4.9.2  | Context Caching                                   |

| 7.4.9.3  | IOTLB                                             |

| 7.4.9.4  | Page Directory Entry (PDE) Caching7-28            |

| 7.4.9.5  | PDE Cache Invalidation7-28                        |

| 7.4.10   | Fault Status Register                             |

| 7.4.11   | Fault Event Control Register7-31                  |

| 7.4.12   | Hardware Handling of Fault Events7-32             |

| 7.4.12.1 | Fault Event Generation with Primary Fault Logging |

| 7.4.12.2 |                                                   |

| 7.4.13   | Fault Event Data Register                         |

| 7.4.14   | Fault Event Address Register                      |

| 7.4.15   | Fault Event Upper Address Register                |

| 7.4.16<br>7.4.17 | Fault Recording Registers [n]       Advanced Fault Log Register |      |

|------------------|-----------------------------------------------------------------|------|

| 7.4.18           | Hardware Handling of Fault Logging                              | 7-39 |

| 7.4.18.1         | Hardware Handling of Primary Fault Logging                      | 7-39 |

| 7.4.18.2         | Hardware Handling of Advanced Fault Logging                     | 7-40 |

| 7.4.19           | Protected Memory Enable Register                                | 7-41 |

| 7.4.20           | Protected Low-Memory Base Register                              | 7-43 |

| 7.4.21           | Protected Low-Memory Limit Register                             | 7-44 |

| 7.4.22           | Protected High-Memory Base Register                             | 7-45 |

| 7.4.23           | Protected High-Memory Limit Register                            | 7-46 |

#### **CHAPTER 8**

#### EXTENDED DMA REMAPPING FEATURES

| 8.1 | ON-DEVICE IOTLBS                  | 8-1 |

|-----|-----------------------------------|-----|

| 8.2 | DMA REMAPPING - EXTENDED FEATURES | 8-1 |

#### APPENDIX A

#### FAULT REASON ENCODINGS

#### FIGURES

| Figure 1-1. | General Platform Topology                             | 1-1 |

|-------------|-------------------------------------------------------|-----|

| Figure 2-1. | Example OS Usage of DMA Remapping                     |     |

| Figure 2-2. | Example Virtualization Usage of DMA Remapping.        | 2-5 |

| Figure 2-3. | Interaction Between I/O and Processor Virtualization  | 2-7 |

| Figure 3-1. | DMA Address Translation                               | 3-2 |

| Figure 3-2. | Requester Identifier Format                           | 3-3 |

| Figure 3-3. | Device to Domain Mapping Structures                   | 3-4 |

| Figure 3-4. | Example Multi-level Page Table                        | 3-7 |

| Figure 3-5. | Example Multi-level Page Table (with 2MB Super Pages) | 3-8 |

| Figure 5-1. | Hypothetical Platform Configuration                   | 5-6 |

| Figure 6-1. | Root-Entry Format                                     |     |

| Figure 6-2. | Context-Entry Format                                  | 6-3 |

| Figure 6-3. | Page-Table-Entry Format                               | 6-6 |

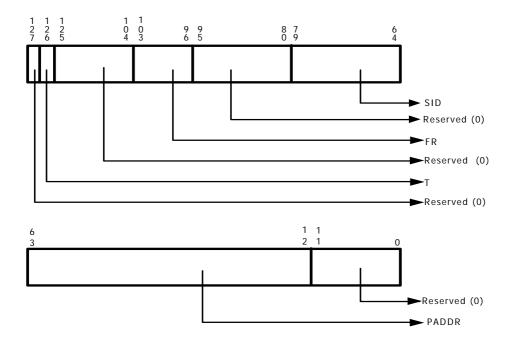

| Figure 6-4. | Fault-Record Format                                   |     |

|             |                                                       |     |

#### TABLES

| Table 1-1. | Document Organization 1-2                                   |

|------------|-------------------------------------------------------------|

| Table 1-2. | Glossary                                                    |

| Table 1-3. | References                                                  |

| Table 3-1. | DMA Remapping Fault Conditions 3-10                         |

| Table 5-1. | DMA Remapping Reporting (DMAR) Table                        |

|            | DMA Remapping Structure Types 5-2                           |

| Table 5-3. | DMA Remapping Hardware Unit Definition (DRHD) Structure 5-3 |

| Table 5-4. | Device Scope Entry Structure                                |

| Table 5-5. | Reserved Memory Region Reporting (RMRR) Structure 5-8       |

| Table 6-1. | Root-Entry Contents                                         |

| Table 6-2. | Context-Entry Contents                                      |

| Table 6-3. | Page-Table-Entry Contents                                   |

| Table 6-4.  | Fault-Record Entry Contents                        | 6-9  |

|-------------|----------------------------------------------------|------|

| Table 7-1.  | Attribute Definitions for DMA Remapping Registers. |      |

| Table 7-2.  | DMA Remapping Register                             |      |

| Table 7-3.  | Version Register                                   |      |

| Table 7-4.  | Capability Register                                |      |

| Table 7-5.  | Extended Capability Register                       |      |

| Table 7-6.  | Global Command Register                            |      |

| Table 7-7.  | Global Status Register                             |      |

| Table 7-8.  | Root-Entry Table Address Register                  |      |

| Table 7-9.  | Context Command Register                           |      |

| Table 7-10. | IOTLB Invalidation Unit Registers.                 | 7-21 |

| Table 7-11. | IOTLB Invalidate Register.                         | 7-22 |

| Table 7-12. | Invalidate Address Register                        | 7-25 |

| Table 7-13. | Fault Status Register                              | 7-29 |

| Table 7-14. | Fault Event Control Register.                      | 7-31 |

| Table 7-15. | Fault Event Data Register.                         | 7-34 |

| Table 7-16. | Fault Event Address Register                       | 7-34 |

| Table 7-17. | Fault Event Upper Address Register                 | 7-35 |

| Table 7-18. | Fault Recording Register                           | 7-36 |

| Table 7-19. | Advanced Fault Log Register                        | 7-38 |

| Table 7-20. | Protected Memory Enable Register                   | 7-41 |

| Table 7-21. | Protected Low-Memory Base Register                 | 7-43 |

| Table 7-22. | Protected Low-Memory Limit Register                | 7-44 |

| Table 7-23. | Protected High-Memory Base Register                | 7-45 |

| Table 7-24. | Protected High-Memory Limit Register               | 7-46 |

| Table A-1.  | Fault Reason Encodings.                            |      |

## CHAPTER 1 INTRODUCTION

This document describes the Intel<sup>®</sup> Virtualization Technology for Directed I/O (VT-d); specifically, it describes the components supporting I/O virtualization as it applies to platforms that use Intel<sup>®</sup> processors and core logic chipsets complying with Intel<sup>®</sup> platform specifications.

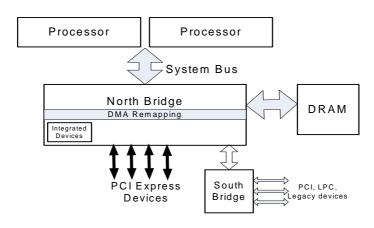

Figure 1-1 illustrates the general platform topology.

Figure 1-1. General Platform Topology

The document includes the following topics:

- An overview of I/O subsystem hardware functions for virtualization support

- A brief overview of expected usages of the generalized hardware functions

- The theory of operation of hardware, including the programming interface

The following topics are not covered (or are covered in a limited context):

- Intel<sup>®</sup> Virtualization Technology for IA-32 Intel<sup>®</sup> Architecture. For more information, refer to the "*IA-32 Intel<sup>®</sup> Architecture Software Developer's Manual*".

- Intel<sup>®</sup> Virtualization Technology for Intel<sup>®</sup> Itanium<sup>®</sup> Architecture. For more information, refer to the "Intel<sup>®</sup> Virtualization Technology Specification for the Intel<sup>®</sup> Itanium<sup>®</sup> Architecture".

• This specification is based on the PCI Express\* 1.1 base specification. Any additional features added to PCI Express that are relevant to I/O virtualization and DMA remapping will be accommodated in future versions of this specification.

### 1.1 AUDIENCE

This document is aimed at hardware designers developing Intel platforms or core-logic providing hardware support for virtualization. The document is also expected to be used by operating system and virtual machine monitor (VMM) developers utilizing the I/O virtualization hardware capabilities.

#### 1.2 ORGANIZATION

The document is organized as shown in the following table.

| Chapter/<br>Appendix | Description                     |

|----------------------|---------------------------------|

| 1                    | Introduction                    |

| 2                    | I/O Device Assignment           |

| 3                    | DMA Remapping                   |

| 4                    | Other Hardware Considerations   |

| 5                    | BIOS Considerations             |

| 6                    | Translation Structure Formats   |

| 7                    | DMA Remapping Registers         |

| 8                    | Extended DMA Remapping Features |

| A                    | Fault Reason Encodings          |

Table 1-1. Document Organization

## 1.3 GLOSSARY

VMM

The document uses the terms listed in the following table.

| Term                       | Definition                                                                                                                                                                                                                                          |  |  |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Chipset / Root-<br>Complex | Used in this specification to refer to one or more hardware components that connect processor complexes to the I/O and memory subsystems. The chipset may include a variety of integrated devices.                                                  |  |  |  |

| Context                    | A hardware representation of state that identifies a device and the domain to which the device is assigned.                                                                                                                                         |  |  |  |

| Device ID                  | A 16-bit device identification number consisting of the PCI Bus number, Device number and Function number. It is also referred to as Source-ID in this document.                                                                                    |  |  |  |

| DMA Remapping              | Translating the address in a DMA request (DVA) to a host physical address (HPA).                                                                                                                                                                    |  |  |  |

| Domain                     | A collection of physical, logical, or virtual resources that are allocated to work together. Domain is used as a generic term for virtual machines, partitions, etc.                                                                                |  |  |  |

| DVA                        | DMA Virtual Address: a virtual address in a DMA request. One example usage of DVA in virtualization is for it to be the same as the Guest physical address (GPA).                                                                                   |  |  |  |

| GAW                        | Guest Address Width. GAW refers to the DMA virtual addressability limit.                                                                                                                                                                            |  |  |  |

| GPA                        | Guest Physical Address is the view of physical memory from software running in a partition. GPA is also used in this document as an example usage for DMA virtual addresses (DVA).                                                                  |  |  |  |

| Guest                      | Software running within a virtual machine environment (partition).                                                                                                                                                                                  |  |  |  |

| HAW                        | Host Address Width. HAW refers to the DMA physical addressability limit for a platform.                                                                                                                                                             |  |  |  |

| HPA                        | Host Physical Address.                                                                                                                                                                                                                              |  |  |  |

| IOTLB                      | I/O Translation Lookaside Buffer. IOTLB refers to an address translation cache in a DMA remapping hardware unit that caches effective translations from DVA (GPA) to HPA.                                                                           |  |  |  |

| MGAW                       | Maximum Guest Address Width. MGAW refers to the maximum DMA virtual addressability supported by a DMA remapping hardware implementation.                                                                                                            |  |  |  |

| MSI                        | Message Signalled Interrupts.                                                                                                                                                                                                                       |  |  |  |

| PDE Cache                  | Page Directory Entry cache. This refers to address translation caches in a DMA remapping hardware unit that caches page directory entries at the various page-<br>directory levels. These are also referred to as non-leaf caches in this document. |  |  |  |

Virtual Machine Monitor - A software layer that controls virtualization.

#### Table 1-2. Glossary

### 1.4 REFERENCES

For related information, see the documents listed in the following table.

| Document | Description                                                       |

|----------|-------------------------------------------------------------------|

| IA32-SDM | IA-32 Intel <sup>®</sup> Architecture Software Developer's Manual |

| PCI-EXP  | PCI Express <sup>*</sup> Base Specification - Revision 1.1        |

| ACPI     | ACPI Specification - Rev 3.0                                      |

#### Table 1-3. References

## CHAPTER 2 OVERVIEW

This chapter provides an overview of Intel<sup>®</sup> Virtualization Technology for processor virtualization, and describes additional hardware support for I/O virtualization.

### 2.1 INTEL<sup>®</sup> VIRTUALIZATION TECHNOLOGY OVERVIEW

Intel<sup>®</sup> Virtualization Technology consists of technology components that support virtualization of platforms based on Intel processors, thereby enabling the running of multiple operating systems and applications in independent partitions. Each partition behaves like a virtual machine (VM) and provides isolation and protection across partitions. This hardware-based virtualization solution, along with the virtualization software, enables multiple usages such as server consolidation, activity partitioning, workload isolation, embedded IT management, legacy software migration, and disaster recovery.

### 2.2 VMM AND VIRTUAL MACHINES

Intel<sup>®</sup> Virtualization Technology supports virtual machine architectures comprised of two principal classes of software:

- Virtual-machine Monitor (VMM): A VMM acts as a host and has full control of the processor(s) and other platform hardware. VMM presents guest software (see below) with an abstraction of a virtual processor and allows it to execute directly on a logical processor. A VMM is able to retain selective control of processor resources, physical memory, interrupt management, and I/O.

- **Guest Software**: Each virtual machine is a guest software environment that supports a stack consisting of an operating system (OS) and application software. Each operates independently of other virtual machines and uses the same interface to processor(s), memory, storage, graphics, and I/O provided by a physical platform. The software stack acts as if it were running on a platform with no VMM. Software executing in a virtual machine must operate with reduced privilege so that the VMM can retain control of platform resources.

The VMM is a key component of the platform infrastructure in virtualization usages. Intel<sup>®</sup> Virtualization Technology can improve the reliability and supportability of virtualization infrastructure software with programming interfaces to virtualize processor hardware. It also provides a foundation for additional virtualization support for other hardware components in the platform.

### 2.3 HARDWARE SUPPORT FOR PROCESSOR VIRTUALIZATION

Hardware support for processor virtualization enables system vendors to provide simple, robust and reliable virtual machine monitor software. VMM relies on hardware support to set policy and operational details for the handling of events, exceptions, and resources allocated to virtual machines.

Intel<sup>®</sup> Virtualization Technology provides hardware support for processor virtualization. Intel<sup>®</sup> Virtualization Technology for IA-32 processors is referred to as VT-x. VT-x constitutes a set of virtual-machine extensions (VMX) that support virtualization of processor hardware for multiple software environments by using virtual machines. An equivalent architecture for processor virtualization of the Itanium architecture is defined and is referred to as VT-i.

### 2.4 I/O VIRTUALIZATION

A VMM must support virtualization of I/O requests from guest software. I/O virtualization may be supported by a VMM through any of the following models:

- <u>Emulation</u>: A VMM may expose a virtual device to guest software by emulating an existing (legacy) I/O device. This enables the same device drivers for the legacy device to be run within the guest, and the VMM emulates the functionality of the I/O device in software over whatever physical devices are available on the physical platform. I/O virtualization through emulation provides good compatibility (by allowing existing device drivers to run within a guest), but introduces limitations with respect to performance and functionality.

- <u>New Software Interfaces</u>: This model is similar to I/O emulation, except that instead of emulating legacy devices, VMM software exposes a synthetic (new) interface/device to guest software. The synthetic device interface is often defined to be virtualization-friendly to enable efficient virtualization compared to the overhead associated with I/O emulation. This model provides improved performance over emulation, but has reduced compatibility (due to the need for specialized guest software or drivers utilizing the new software interfaces).

- <u>Assignment</u>: As part of virtualizing the platform to guests, a VMM may directly assign the physical I/O devices to VMs. With direct assignment of devices, the driver for an assigned I/O device runs in the VM to which it is assigned and is allowed to interact directly with the device hardware without invoking the VMM. Robust I/O assignment requires additional hardware support to ensure the assigned device accesses are isolated and restricted to resources owned by the assigned partition. The I/O assignment model may also be used to create one or more I/O container partitions that support emulation or software interfaces for virtualizing I/O requests from other guests. The I/O-container based approach removes the need for running the physical device drivers as part of VMM privileged software.

- <u>Device-assisted I/O Sharing</u>: In this model, which is an extension to the I/O assignment model, an I/O device supports multiple functional interfaces, each of which may be independently assigned to a VM. The device hardware itself is capable of accepting

multiple I/O requests through any of these functional interfaces and processing them utilizing the device's hardware resources.

Depending on the usage requirements, a VMM may support any of the above models for I/O virtualization. For example, I/O emulation may be best suited for virtualizing legacy devices. I/O assignment may provide the best performance when hosting I/O-intensive workloads in a guest. I/O virtualization through new software interfaces makes a trade-off between compatibility and performance, and native I/O sharing provides more virtual devices than the number of physical devices in the platform.

#### 2.5 INTEL<sup>®</sup> VIRTUALIZATION TECHNOLOGY FOR DIRECTED I/O OVERVIEW

A general requirement for all of the above I/O virtualization models is the ability to isolate and contain device accesses only to resources owned by the domain managing the device. Intel<sup>®</sup> Virtualization Technology for Directed I/O provides VMM software with the following capabilities:

- Assign I/O devices across VMs: Flexibly assign I/O devices to VMs and extend the protection and isolation properties of VMs for I/O accesses.

- **DMA remapping**: Direct Memory Accesses (DMA) from devices can be independently address-translated.

- **Reliability**: Record and report DMA errors that may otherwise corrupt memory to system software.

For simplicity, the address translation functionality for I/O device DMA requests is referred to as *DMA remapping* in this document.

### 2.5.1 Hardware Support for DMA Remapping

To generalize I/O virtualization and make it applicable to different processor architectures and operating systems, this document refers to domains as abstract isolated environments in the plat-form to which a subset of host physical memory is allocated.

DMA remapping provides hardware support for isolation of device accesses to memory, and enables each device in the system to be assigned to a specific domain through a distinct set of I/O page tables. When the device attempts to access system memory, the DMA remapping hardware intercepts the access and utilizes the I/O page tables to determine whether the access can be permitted; it also determines the actual location to access. Frequently used I/O page table structures can be cached in hardware; the caches are referred to as I/O translation look-aside buffers (IOTLBs). The DMA remapping can be configured flexibly and independently for each device, or across multiple devices.

### 2.5.2 OS Usages of DMA Remapping

There are several ways in which operating systems can use DMA remapping:

- **OS Protection**: An OS may define a domain containing its critical code and data structures, and restrict access to that domain for all I/O devices in the system. This allows the OS to limit erroneous or unintended corruption of its data and code through incorrect programming of devices by device drivers, thereby improving its robustness and reliability.

- Feature Support: An OS may use domains to better manage DMA from legacy 32-bit PCI devices to high memory (above 4GB). This is achieved by allocating 32-bit devices to one or more domains and programming the platform's DMA remapping mechanism to remap DMA from these devices to high memory. Without such support, software must resort to data copying through OS "bounce buffers".

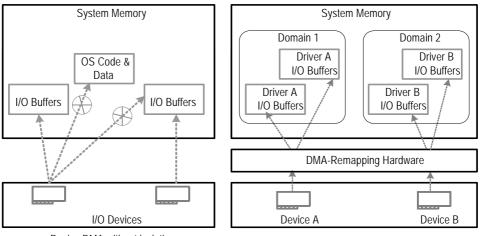

- **DMA Isolation**: An OS may manage I/O by creating multiple domains and assigning one or more I/O devices to each domain. Each device-driver explicitly registers its I/O buffers with the OS, and the OS assigns these I/O buffers to specific domains, using hardware to enforce DMA domain protection. See Figure 2-1.

Device DMA without isolation

Device DMA isolated using DMA remapping hardware

Figure 2-1. Example OS Usage of DMA Remapping

### 2.5.3 VMM Usages of DMA Remapping

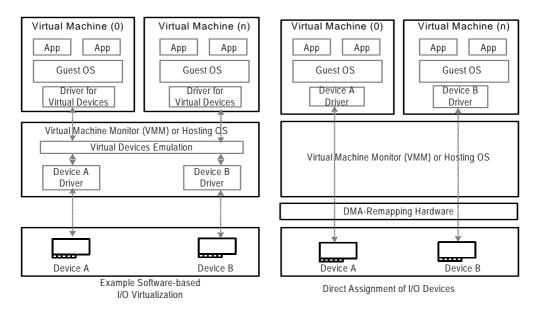

The limitations of software-only methods for I/O virtualization can be improved through direct assignment of I/O devices to partitions. With this approach, the driver for an assigned I/O device runs only in the partition to which it is assigned and is allowed to interact directly with the device hardware without invoking the VMM. The hardware support for DMA remapping enables this direct device assignment without device-specific knowledge in the VMM. See Figure 2-2.

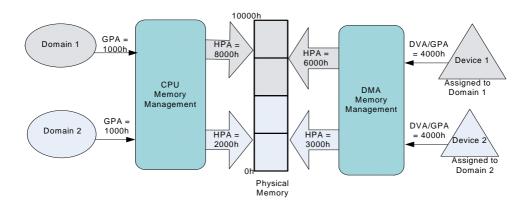

Figure 2-2. Example Virtualization Usage of DMA Remapping

In this model, the VMM restricts itself to a controlling function for enabling direct assignment of devices to its partitions. Rather than invoking the VMM for all (or most) I/O requests from a partition, the VMM is invoked only when guest software accesses protected resources (such as I/O configuration accesses, interrupt management, etc.) that impact system functionality and isolation.

To support direct assignment of I/O devices, a VMM must enforce isolation of DMA requests. I/O devices can be assigned to domains, and the DMA remapping hardware can be used to restrict DMA from an I/O device to the physical memory presently owned by its domain. For domains that may be relocated in physical memory (i.e., GPA not identical to HPA), the DMA remapping hardware can be programmed to perform the necessary translation.

I/O device assignment allows other I/O sharing usages — for example, assigning an I/O device to an I/O partition that provides I/O services to other user partitions. DMA remapping hardware enables virtualization software to choose the right combination of device assignment and software-based methods for I/O virtualization.

#### 2.5.3.1 DMA Remapping Usages by Guests

A guest OS running in a VM may benefit from the availability of DMA remapping hardware to support the usages described in Section 2.5.2. To support such usages, the VMM may virtualize the DMA remapping hardware to its guests. For example, the VMM may intercept guest accesses to the virtual DMA remapping hardware registers, and manage a shadow copy of the guest DMA remapping structures that is provided to the physical DMA remapping hardware. On updates to the guest I/O page tables, the guest software performs appropriate virtual IOTLB invalidation operations. The virtual IOTLB invalidations may be intercepted by the VMM, the respective shadow page tables updated, and the physical IOTLBs flushed. Due to the non-restartability of faulting DMA transactions (unlike CPU memory management virtualization), a VMM cannot perform lazy updates to its shadow DMA remapping structures. To keep the shadow structures consistent with the guest structures, the VMM may expose virtual IOTLB with eager pre-fetching behavior (including caching of not-present entries) or write-protect the guest DMA remapping structures.

### 2.5.4 Interaction with Processor Virtualization

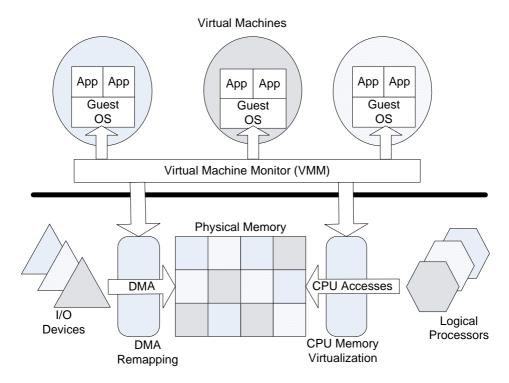

Figure 2-3 depicts the interaction between system software, and hardware support for processor level virtualization (VT-x) and Intel<sup>®</sup> Virtualization Technology for Directed I/O virtualization (VT-d).

Figure 2-3. Interaction Between I/O and Processor Virtualization

The VMM manages processor requests to access physical memory via the processor's memory management hardware. DMA requests to access physical memory use DMA remapping hardware. Both the processor memory management and DMA memory management are under the control of VMM.

#### OVERVIEW

## CHAPTER 3 DMA REMAPPING

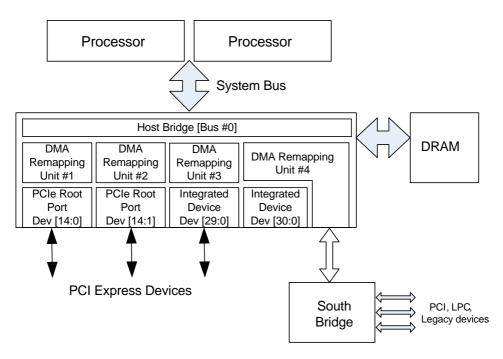

This chapter describes the hardware architecture for DMA remapping. The architecture envisions DMA remapping hardware to be implemented in core root-complex components, such as the memory controller hub (MCH) or the I/O (IOH) controller hub.

### 3.1 DOMAINS AND ADDRESS TRANSLATION

A domain is abstractly defined as an isolated environment in the platform, to which a subset of the host physical memory is allocated. I/O devices that are allowed to access physical memory directly are allocated to a domain and are referred to as the domain's assigned devices.

The isolation property of a domain is achieved by blocking access to its physical memory from resources not assigned to it. Multiple isolated domains are supported in a system by ensuring all I/O devices are assigned to some domain (possibly a null domain), and by restricting access from each assigned device only to the physical resources allocated to its domain.

The DMA remapping architecture facilitates flexible assignment of I/O devices to an arbitrary number of domains. As described in Section 2.5, each domain has a view of physical address space that may be different than the host physical address space. DMA remapping treats the address specified in a DMA request as a DMA virtual address (DVA). Depending on the software usage model, the DMA virtual address space may be the same as the guest-physical address (GPA) space of the domain to which the I/O device is assigned, or a purely virtual address space defined by software. In either case, DMA remapping transforms the address in a DMA request issued by an I/O device to its corresponding host-physical address (HPA).

For simplicity, this document refers to an address in a DMA request as a GPA and the translated address as an HPA.

Figure 3-1 illustrates DMA address translation. I/O devices 1 and 2 are assigned to domains 1 and 2, respectively. The software responsible for creating and managing the domains allocates system physical memory for both domains and sets up the DMA address translation function. GPAs in DMA requests initiated by devices 1 & 2 are translated to appropriate HPAs by the DMA remapping hardware.

Figure 3-1. DMA Address Translation

The host platform may support one or more DMA remapping hardware units. Each hardware unit supports remapping DMA requests originating within its hardware scope. For example, a desktop chipset implementation may expose a single DMA remapping hardware unit that translates all DMA transactions at the memory controller hub (MCH) component. A server platform with one or more core chipset components may support independent translation hardware units in each component, each translating DMA requests originating within its I/O hierarchy (such as a PCI Express root port). The architecture supports configurations in which these hardware units may either share the same translation data structures (in system memory) or use independent structures, depending on software programming.

The DMA remapping hardware applies the address translation function to the address in a DMA request to convert it to a host physical address (HPA) before further hardware processing (such as address decoding, snooping of processor caches, and/or forwarding to the memory controllers).

### 3.2 MAPPING DEVICES TO DOMAINS

The following sub-sections describe the DMA remapping architecture and data structures used to map I/O devices to domains.

### 3.2.1 Source Identifier

The identity of the originator of a DMA request appearing at the address-translation hardware (the "requestor identifier") is required to identify the device originating the DMA. The attribute identifying the originator of an I/O transaction is referred to as the "source-id" in this document. The DMA remapping hardware may determine the source-id of a transaction in implementation-

specific ways. For example, some I/O bus protocols may provide the originating device identity as part of each I/O transaction. In other cases (for root-complex integrated devices, for example), the source-id may be derived based on the root-complex internal implementation.

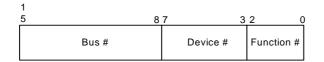

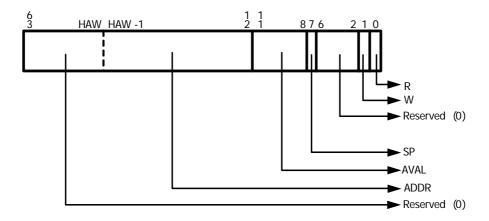

For PCI Express devices, the source-id is mapped to the requester identifier in the PCI express transaction layer header. The requester identifier of a device, which is composed of its PCI Bus/Device/Function number, is assigned by configuration software and uniquely identifies the hardware function that initiated the request. Figure 3-2 illustrates the requester-id as defined by the PCI Express Specification.

Figure 3-2. Requester Identifier Format

The following sections describe the data structures for mapping I/O devices to domains.

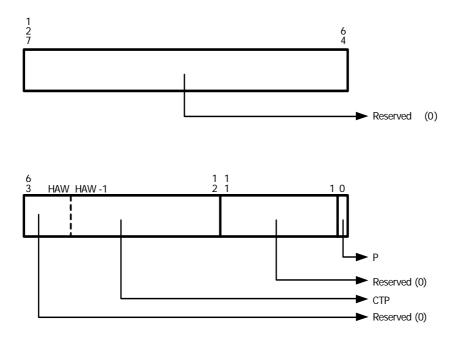

#### 3.2.2 Root-Entry

The root-entry functions as the top level structure to map devices on a specific PCI bus to their respective domains. Each root-entry structure contains the following fields:

- **Present flag**: The present field is used by software to indicate to hardware whether the root-entry is present and initialized. Software may clear the present field for root entries corresponding to bus numbers that are either not present in the platform, or don't yet have any downstream devices attached. If the present field of a root-entry used to process a DMA request is clear, the DMA request is blocked, resulting in a translation fault.

- **Context-entry table pointer**: The context-entry table pointer references the context-entry table for devices on the bus identified by the root-entry. Section 3.2.3 describes context entries in further detail.

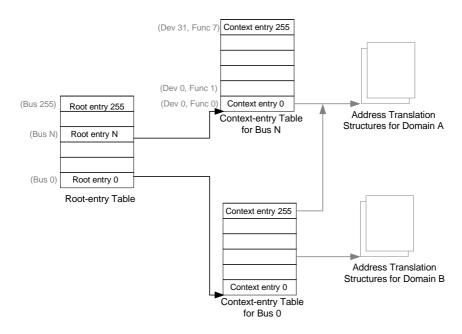

Figure 3-3 illustrates the root-entry format. The root entries are programmed through the rootentry table. The location of the root-entry table in system memory is programmed through the Root-entry Table Address register (described in Section 7.4.6). The root-entry table is 4KB in size and accommodates 256 root entries to cover the PCI bus number space (0-255). In the case of a PCI device, the bus number (upper 8-bits) encoded in a DMA transaction's source-id field is used to index into the root-entry structure. Figure 3-3 illustrates how these tables are used to map devices to domains.

Figure 3-3. Device to Domain Mapping Structures

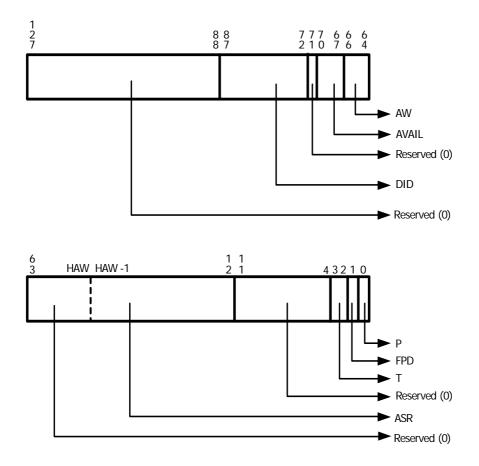

### 3.2.3 Context-Entry

A context-entry maps a specific I/O device on a bus to the domain to which it is assigned, and, in turn, to the address translation structures for the domain. The context entries are programmed through the memory-resident context-entry tables. Each root-entry in the root-entry table contains the pointer to the context-entry table for the corresponding bus number. Each context-entry table contains 256 entries, with each entry representing a unique PCI device function on the bus. For a PCI device, the device and function numbers (lower 8-bits) of a source-id are used to index into the context-entry table.

Each context-entry contains the following attributes:

- **Domain Identifier**: The domain identifier is a software-assigned field in a context entry that identifies the domain to which a device with the given source-id is assigned. Hardware may use this field to tag its caching structures. Context entries programmed with the same domain identifier must always reference the same address translation structure, and vice versa.

- **Present Flag**: The present field is used by software to indicate to hardware whether the context-entry is present and initialized. Software may clear the present field for context entries corresponding to device functions that are not present in the platform. If the present

field of a context-entry used to process a DMA request is clear, the DMA request is blocked, resulting in a translation fault.

- **Translation Type**: The translation-type field indicates the type of the address translation structure that must be used to address-translate a DMA request processed through the context-entry.

- Address Width: The address-width field indicates the address width of the domain to which the device corresponding to the context-entry is assigned.

- Address Space Root: The address-space-root field provides the host physical address of the address translation structure in memory to be used for address-translating DMA requests processed through the context-entry.

- Fault Processing Disable Flag: The fault-processing-disable field enables software to selectively disable recording and reporting of DMA remapping faults detected for DMA requests processed through the context-entry.

Section 6.2 illustrates the exact context-entry format. Multiple devices may be assigned to the same domain by programming the context entries for the devices to reference the same translation structures, and programming them with the same domain identifier.

#### 3.2.3.1 Context Caching

The DMA remapping architecture enables hardware to cache root-entries and context-entries to minimize the overhead incurred for fetching them from memory. Hardware manages the context-cache and supports context-cache invalidation requests by software.

When modifying device-to-domain mapping structures referenced by multiple DMA remapping hardware units in a platform, software is responsible for explicitly invalidating the caches at each of the hardware units. For more detailed information, see Section 7.4.9.

The architecture defines the following types of context-cache invalidation requests:

- 1. **Global Invalidation**: All context-cache entries cached at a DMA remapping hardware unit are invalidated through a global invalidate.

- 2. **Domain-Selective Invalidation**: Context-cache entries corresponding to a specific domain are invalidated through a domain-selective invalidate.

- 3. **Device-Selective Invalidation**: Context-cache entries corresponding to a specific device within a domain are invalidated through a device-selective invalidate.

Hardware implementations must allow software to specify any of the above three types of invalidation requests, but may perform the actual invalidation at a coarser granularity if the requested invalidation granularity cannot be supported. For example, hardware may perform a domainselective invalidation on a device-selective invalidation request. Hardware reports to software the granularity at which the actual invalidation was performed. Section 7.4.9 describes the hardware registers for context-cache invalidation.

### 3.3 ADDRESS TRANSLATION

The translation-type field in a context-entry specifies the translation structure type used to remap DMA requests from an I/O device. The architecture currently defines only a multi-level, page-table-based, address-translation structure type.

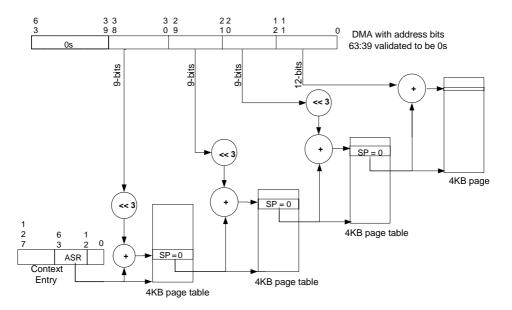

### 3.3.1 Multi-Level Page Table

The multi-level page tables allow software to manage host physical memory at page (4KB) granularity and set up a hierarchical structure with page directories and page tables. Hardware implements the page-walk logic and traverses these structures using the address from the DMA request. The maximum number of page-table levels that need to be traversed is a function of the address width of the domain (specified in the corresponding context entry).

The architecture defines the following features for the multi-level page table structure:

- Super Pages

- The super-page field in page-table entries enables larger page allocations. When a page-table entry with the super-page field set is encountered by hardware on a page-table walk, the translated address is formed immediately by combining the page base address in the page-table entry with the GPA bits not yet used for the page-walk.

- The architecture currently defines super-pages of size 2<sup>21</sup>, 2<sup>39</sup>, 2<sup>48</sup>, and 2<sup>57</sup>. Implementations indicate support for specific super-page sizes through the Capability register. Hardware implementations may optionally support these super-page sizes.

- DMA Access Controls

- DMA access controls make it possible to control DMA accesses to specific regions within a domain's address space. These controls are defined through the read and the write permission fields.

- If hardware encounters a page-table entry with the read field clear as part of address-translating a DMA read request, the request is blocked.

- If hardware encounters a page-table entry with the write field clear as part of address translating a DMA write request, the request is blocked.

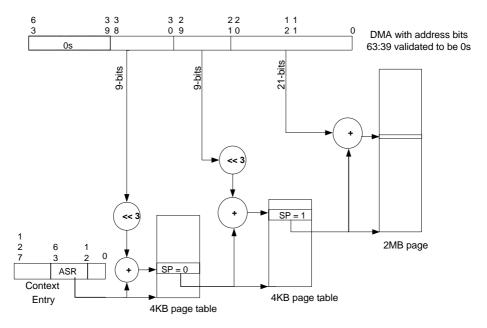

Figure 3-4 shows a multi-level (3-level) page-table structure with 4KB page mappings and 4KB page tables. Figure 3-5 shows the same thing with 2MB super pages.

Figure 3-4. Example Multi-level Page Table

Figure 3-5. Example Multi-level Page Table (with 2MB Super Pages)

#### 3.3.1.1 Adjusted Guest Address Width (AGAW)

To allow page-table walks with 9-bit stride, the Adjusted Guest Address Width (AGAW) value for a domain is defined as its Guest Address Width (GAW) value adjusted, such that (AGAW-12) is a multiple of 9. For example, a domain to which 2GB of memory is allocated has a GAW of 31, and an AGAW of 39. AGAW is calculated as follows:

```

R = (GAW - 12) MOD 9;

if (R == 0) {

AGAW = GAW;

} else {

AGAW = GAW + 9 - R;

}

if (AGAW > 64)

AGAW = 64;

```

The AGAW indicates the number of levels of page-walk. Hardware implementations report the supported AGAWs through the Capability register. Software must ensure that it uses an AGAW supported by the underlying hardware implementation when setting up page tables for a domain.

#### 3.3.1.2 Multi-level Page Table Translation

Address translation of DMA requests processed through a context-entry specifying use of multilevel page table is handled by DMA remapping hardware as follows:

- 1. If the GPA in the DMA request is to an address above the maximum guest address width supported by the remapping hardware (as reported through the MGAW field in the Capability register), the DMA request is blocked.

- 2. If the address-width (AW) field programmed in the context-entry is not one of the AGAWs supported by hardware (as reported through the SGAW field in the Capability register), the DMA request is blocked.

- 3. The address of the DMA request is validated to be within the adjusted address width of the domain to which the device is assigned. DMA requests attempting to access memory locations above address (2<sup>X</sup> 1) are blocked, where X is the AGAW corresponding to the address-width (AW) programmed in the context-entry used to process this DMA request.

- 4. If the above checks are successful, the address in the DMA request is adjusted (zeroextended) to X bits, where X is the address width (AW) programmed in the context-entry used to process this DMA request.

- 5. The adjusted address and length specified in the DMA request is used to address translate the DMA request through the multi-level page table referenced by the context entry. Based on the programming of the page-table entries (super-page, read, write attributes), either the adjusted address is successfully translated to a host physical address (HPA), or the DMA request is blocked.

- 6. For successful address translations, hardware performs the normal processing (address decoding, etc.) of the DMA request as if it was targeting the translated HPA.

#### 3.3.1.3 I/O Translation Lookaside Buffer (IOTLB)

The DMA remapping architecture defines support for caching effective translations<sup>1</sup> for improved address translation performance. The cache of effective translations is referred to as the I/O translation look-aside buffer (IOTLB). Similar to the context-cache, hardware manages the IOTLB, and supports IOTLB invalidation requests by software. Details of the hardware caching and invalidation behavior are described in Section 7.4.9.

When modifying page-table entries referenced by more than one DMA remapping hardware unit in a platform, software is responsible for explicitly invalidating the IOTLB at each of these DMA remapping hardware units.

<sup>1.</sup> When inserting a leaf page-table entry into the IOTLB, hardware caches the Read (R) and Write (W) attributes as the logical AND of all the respective R and W fields encountered in the page walk reaching up to this leaf entry.

The architecture defines the following types of IOTLB invalidation requests to support the various software usage models:

- 1. **Global Invalidation**: All address translations cached at a DMA remapping hardware unit are invalidated through a global invalidate.

- 2. **Domain-Selective Invalidation**: Cached translations belonging to a specific domain are invalidated through a domain-selective invalidate.

- 3. **Domain Page-Selective Invalidation**: Cached translations corresponding to the specified DMA address(es) of a domain are invalidated through a domain-page-selective invalidate.

Hardware implementations must allow software to specify any of the above types of IOTLB invalidation requests, but may perform the actual invalidation at a coarser granularity if the requested invalidation granularity cannot be supported. Hardware to reports to software the granularity at which the actual invalidation was performed.

### 3.4 DMA REMAPPING FAULTS

The following table enumerates the various conditions resulting in DMA remapping faults.

| DMA Remapping Fault Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| The present (P) field in the root-entry used to process the DMA request is clear.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |  |

| The present (P) field in the context-entry used to process the DMA request is clear.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |  |

| <ul> <li>Hardware detected invalid programming of a context-entry. For example:</li> <li>The address-width (AW) field was programmed with an SAGAW value not supported by the hardware implementation.</li> <li>The translation-type (T) field was programmed to indicate a translation type not supported by the hardware implementation. Currently, only the multi-level page-table translation type is defined.</li> <li>A hardware attempt to access the page-table base through the Address Space Root (ASR) field of the context-entry resulted in error.</li> </ul> | Yes |  |

| <ul> <li>The DMA request attempted to access an address beyond (2<sup>X</sup> - 1), where X is<sup>1</sup>:</li> <li>For multiple level page-table based translation, the minimum of the MGAW reported in the Capability register and the AGAW corresponding to the address-width field in the context-entry used to process the DMA request.</li> </ul>                                                                                                                                                                                                                   | Yes |  |

| The Write (W) field in a page-table entry used for address translation of the DMA write request is clear.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |  |

| The Read (R) field in a page-table entry used for address translation of the DMA read request is clear.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |  |

| A hardware attempt to access the next level page table through the Address (ADDR) field of the page-table entry resulted in error.                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |  |

#### Table 3-1. DMA Remapping Fault Conditions

| DMA Remapping Fault Conditions                                                                                                                                      | Qualified |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| A hardware attempt to access the root-entry table through the root-table address (RTA) field<br>in the Root-entry Table Address register resulted in error.         | No        |

| A hardware attempt to access context-entry table through context-entry table pointer (CTP) field resulted in error.                                                 | No        |

| Hardware detected reserved field(s) that are not initialized to zero in a root-entry with the present (P) field set. <sup>2</sup>                                   | No        |

| Hardware detected reserved field(s) that are not initialized to zero in a context-entry with the present (P) field set. <sup>2</sup>                                | Yes       |

| Hardware detected reserved field(s) that are not initialized to zero in a page-table entry with at least one of the read (R) and write (W) fields set. <sup>2</sup> | Yes       |

#### Table 3-1. DMA Remapping Fault Conditions (Contd.)

#### NOTES

- DMA requests to addresses beyond the maximum guest address width (MGAW) supported by hardware may be reported through other means such as through PCI Express Advanced error reporting (AER) at a PCI Express root port.

- 2. To ensure compatibility with future extensions of this architecture, software must zero reserved fields in all present structures. Hardware behavior is undefined on reserved field violation. Hardware implementations capable of reserved field checking reports reserved field violation as DMA remapping faults.

When a DMA remapping fault is detected:

- The faulting DMA request is always blocked.

- The unqualified fault conditions in Table 3-1 are always logged and reported.

- The qualifying fault conditions in Table 3-1, are logged and reported conditionally. Hardware checks the fault-processing-disable (FPD) field in the context-entry used to process the faulting DMA request to determine if a qualifying fault must be processed. If the FPD field is set, the qualifying fault is not reported. If the FPD field is clear, the qualifying fault is logged and reported.

The following sections provide detailed information about fault logging and reporting.

#### 3.4.1 Fault Logging

DMA remapping faults are processed by logging the fault information and reporting the faults to software through a fault event (interrupt). The architecture defines two types of fault logging facilities: (a) Primary Fault Logging, and (b) Advanced Fault Logging. The primary fault logging method must be supported by all implementations of this architecture. Support for advanced fault logging is optional. Software must not change the fault logging method while hardware is enabled.

#### 3.4.1.1 Primary Fault Logging

The primary method for logging DMA remapping faults is through Fault Recording registers. The number of fault recording registers supported by a DMA remapping hardware unit is reported through the Capability register. The following information is recorded in the Fault Recording registers:

- **Fault Reason**: The fault reason indicates the specific condition that caused the translation fault. Fault reason encodings are enumerated in Appendix A.

- Access Type: This field provides the type (write or read request) of the DMA request that faulted.

- Source ID: The source-id indicates the originator of the faulted DMA request.

- Faulting Address: The address field provides the page address in the faulted DMA request.

Hardware indicates a pending fault in a fault recording register by setting its Fault (F) field. Additional faults detected from the same requestor may be collapsed by hardware if there is already a pending fault from the same requester. Any fault overflow condition is handled by hardware by not recording the fault and indicating the overflow condition to software through the Primary Fault Overflow (PFO) field in the Fault Status register. Future faults are not recorded or reported until software handles the already reported faults in the fault recording registers, and clears the overflow condition. Section 7.4.18.1 describes the hardware handling of primary fault logging in detail.

#### 3.4.1.2 Advanced Fault Logging

Advanced fault logging is an optional hardware feature. Hardware implementations supporting advanced fault logging report the feature through the Capability register.

Advanced fault logging uses a memory-resident fault log to record fault information. The base and size of the memory-resident fault log region is programmed by software through the Advanced Fault Log register. Advanced fault logging must be enabled by software through the Global Command register before enabling the DMA remapping hardware. Each fault record contains the same information (fault reason, access type, source-id and faulting address fields) as with primary fault logging. Section 6.4 illustrates the format of the fault record.

When advanced fault logging is enabled, hardware manages a pointer to the next writable entry in the size-aligned fault log region. Whenever a new fault log region is programmed by software, the internal pointer is initialized to the base of the new fault log. The pointer is advanced whenever a fault record is written, for up to the maximum number of entries allowed by the fault log size. If hardware is not able to record a fault because the fault log is full, the fault is not recorded, and the overflow condition is indicated through the Advanced Fault Overflow (AFO) status field in the Advanced Fault Log register. Future faults are not recorded or reported until software clears the overflow condition and re-programs the fault log pointer in hardware. See Section 7.4.18.2 for more detailed information.

#### 3.4.1.3 Fault Priority

The priorities for hardware handling and reporting of fault conditions detected while remapping a DMA request are:

- 1. Fault conditions encountered on hardware attempt to access the various memory-resident DMA remapping structures.

- 2. Fault condition due to hardware detecting the target entry being not present.

- 3. Fault conditions due to erroneous programming of one or more fields in an entry.

- 4. For hardware implementations validating reserved fields, fault conditions due to one or more non-zero reserved fields.

### 3.4.2 Fault Reporting

Fault events are reported to software using a message signalled interrupt (MSI), and controlled through the Fault Event Control register. The fault event information (such as interrupt vector, delivery mode, address, etc.) is programmed through the Fault Event Data and Fault Event Address registers.

With both primary and advanced fault logging, hardware can be programmed to generate a fault event when the first fault is detected/recorded. Further fault events are auto-disabled in hardware until software explicitly re-arms fault-event generation. provides further details on hardware fault-event generation behavior with primary and advanced fault logging.

### 3.4.3 Hardware Handling of Faulting DMA Requests

A DMA request that results in a DMA remapping fault must be blocked by hardware. The exact method of DMA blocking is implementation-specific. For example:

- Faulting DMA write requests may be handled in much the same way as hardware handles write requests to non-existent memory. For example, the DMA request must be discarded in a manner convenient for implementations (such as by dropping the cycle, completing the write request to memory with all byte enables masked off, re-directed to a dummy memory location etc.).

- Faulting DMA read requests may be handled in much the same way as hardware handles read requests to non-existent memory. For example, the request may be redirected to a dummy memory location, returned as all 0's or 1's in a manner convenient to the implementation, or the request may be completed with an explicit error indication (preferred). For faulting DMA read requests from PCI Express devices, hardware must indicate either "Completer Abort" (CA) or "Unsupported Request" (UR) in the completion status field of the PCI Express read completion.<sup>1</sup>

<sup>1.</sup> For PCI Express, a DMA read completion with an error status may cause hardware to generate a PCI Express un-correctable, non-fatal (ERR\_NONFATAL) error message.

#### DMA REMAPPING

## CHAPTER 4 HARDWARE CONSIDERATIONS

This chapter discusses hardware considerations for DMA remapping that are not covered in other chapters.

### 4.1 HANDLING INTERRUPT MESSAGES

On Intel platforms, interrupt requests from IOAPICs and MSI-capable devices appear to the root-complex as upstream memory write requests to the address range 0xFEE0\_0000h to 0xFEEF\_FFFFh. Since this interrupt message address range is architectural and identical between the guest and the host, upstream DMA requests to addresses in the MSI address range are not subject to DMA remapping as described in Chapter 3. Hardware decodes the address in a DMA request to check if it falls in the interrupt address range and bypasses DMA remapping for such transactions. DMA write requests to this range are validated and interpreted as interrupt messages, and DMA requests to this range are treated as errors.

Software must ensure that the DMA remapping page tables are programmed not to remap regular DMA requests to the above interrupt address range. Hardware behavior is undefined for DMA requests remapped to the interrupt address range through the DMA remapping structures.

Future versions of this specification may define additional behavior for handling interrupt messages.

### 4.2 ASSIGNING DEVICES BEHIND PCI EXPRESS TO PCI/PCI-X BRIDGES

For PCI Express-to-PCI/PCI-X bridges, the bridge may generate a different requester-id and tag combination in some instances for transactions forwarded to the bridge's PCI Express interface. The action of replacing the original transaction's requester-id with one assigned by the bridge is generally referred to as taking "ownership" of the transaction. If the bridge generates a new requester-id for a transaction forwarded from the secondary interface to the primary interface, the bridge assigns the PCI Express requester-id using the secondary interface's bus number, and sets both the device number and function number fields to zero. Refer to the PCI Express-to-PCI/PCI-X bridge specifications for more details.

When assigning devices behind PCI Express-to-PCI/PCI-X bridges, software must consider the possibility of DMA requests arriving with the requester-id in the original PCI-X transaction or the requester-id provided by the bridge. Since devices behind these bridges can only be collectively assigned to a single domain, software must program multiple context entries, each corresponding to the possible set of requester-ids. Each of these context-entries must be programmed identically to ensure the DMA requests with any of these requester-ids are processed identically.

### 4.3 ASSIGNING PCI EXPRESS DEVICES USING PHANTOM FUNCTIONS

To increase the maximum possible number of outstanding requests requiring completion, PCI Express allows a device to use function numbers not assigned to implemented functions to logically extend the Tag identifier. Unclaimed function numbers are referred to as Phantom Function Numbers (PhFN). A device reports its support for phantom functions through the Device Capability configuration register, and requires software to explicitly enable use of phantom functions through the Device Control configuration register.

Since function number is part of the requester-id used to locate the context-entry for processing a DMA request, when assigning PCI Express devices with phantom functions enabled, software must program multiple context entries, each corresponding to the PhFN enabled for use by the device function. Each of these context-entries must be programmed identically to ensure the DMA requests with any of these requester-ids are processed identically.

### 4.4 HANDLING DMA REQUESTS CROSSING PAGE BOUNDARY

PCI Express memory requests are specified to disallow Address/Length combinations which cause a memory space access to cross a 4KB boundary. However, the PCI Express Specification defines checking for violations of this rule at the receivers as optional. If checked, violations are treated as malformed transaction layer packets and reported as PCI Express errors. Checking of DMA requests crossing 4KB boundary from root-complex integrated devices is typically platform-dependent.

Platforms supporting DMA remapping are expected to handle DMA requests that cross 4KB boundary in one of the following ways:

- The platform hardware checks for DMA requests that cross a 4KB boundary and explicitly blocks them. For PCI Express memory requests, this may be implemented by hardware strictly checking for the condition at the PCI Express receivers and handling it as PCI Express error. DMA requests from other devices (such as root-complex integrated devices) violating this rule (and hence blocked by hardware) may be handled in platform-specific ways. In this model, the DMA remapping hardware units never receive DMA requests that cross page boundaries.

- If the platform hardware cannot check for the 4KB crossing condition in DMA requests, the DMA remapping hardware units must detect this condition and re-map the requests as if they were multiple independent DMA requests.

### 4.5 HANDLING OF ZERO-LENGTH DMA

A memory read request of one double-word with no bytes enabled ("zero-length read") is typically used by devices as a type of flush request. For a requestor, the semantics of the flush request allow a device to ensure that previously issued posted writes in the same traffic class have been completed at their destination. When DMA remapping hardware is enabled, zero-length DMA requests are not processed differently than other DMA requests. Specifically, zero-length DMA requests are address-translated based on the programming of the DMA remapping structures. For successful translations, the transaction is completed in much the same way as it is completed without DMA remapping (for example, the transaction is completed in the coherency domain with all byte enables off). Unsuccessful translations result in DMA remapping faults.

### 4.6 DMA REMAPPING - SOFTWARE VIEW

The DMA remapping architecture allows hardware implementations supporting a single PCI segment group to expose (to software) the DMA remapping function either as a single hardware unit covering the entire PCI segment group, or as multiple hardware units, each supporting a mutually exclusive subset of devices in the PCI segment group hierarchy. For example, an implementation may expose a DMA remapping hardware unit that supports one or more integrated devices on the root bus, and additional DMA remapping hardware units for devices behind one or a set of PCI Express root ports. The platform firmware (BIOS) reports each DMA remapping hardware unit in the platform to software. Chapter 5 describes a proposed reporting structure through ACPI constructs.

For hardware implementations supporting multiple PCI segment groups, the DMA remapping architecture requires hardware to expose independent DMA remapping hardware units (at least one per PCI segment group) for processing DMA requests originating within the I/O hierarchy of each segment group.

### 4.7 HANDLING DMA TO RESERVED SYSTEM MEMORY

PC platforms commonly use reserved memory for platform-specific usages. These memory regions are typically marked as reserved by BIOS in the system memory map provided to software. Memory exposed to system software for operating system use through the system memory map is commonly referred to as "OS-visible memory". Usages of system reserved memory are platform-specific. Some common examples of private memory usages include: integrated UMA graphics controllers using reserved system memory to host the graphics translation table (GTT) and blitting, management controllers using reserved memory to store/run management firmware, and BIOS/SMM code utilizing reserved memory for USB legacy keyboard emulation.

Platform implementations supporting private memory must carefully consider the system software and security implications of its usages. These usages are beyond the scope of this specification. Platform hardware may use implementation-specific means to distinguish accesses to system reserved memory. These means must not depend on simple address-based decoding since DMA virtual addresses can indeed overlap with the host physical addresses of reserved system memory.

For platforms that cannot distinguish between DMA to OS-visible system memory and DMA to reserved system memory, the architecture defines a standard reporting method to inform system software about the reserved system memory address ranges and the specific devices that require DMA access to these ranges for proper operation. For legacy reasons, system software is expected to provide unity mapping for these address ranges, and to provide both read and write

access privileges to at least the identified devices. For these devices, the system software is also responsible for ensuring that the DMA virtual addresses generated by the system software do not overlap with the reserved system memory address ranges. Refer to Section 5.4 for details on the reporting of reserved memory regions.

### 4.8 PEER TO PEER CONSIDERATIONS

When DMA remapping hardware is enabled, peer-to-peer requests through the root complex must be handled as follows:

- The address in the DMA request must be treated as a DMA virtual address and addresstranslated to an HPA. The address decoding for peer addresses must be done only on the translated HPA. Hardware implementations are free to further limit peer-to-peer accesses to specific host physical address regions (or to completely disallow peer-forwarding of translated requests).

- Since address translation of PCI Express peer-to-peer requests changes the contents (address field) of the PCI Express transaction layer packet (TLP), for peer-to-peer requests with ECRC, the root-complex hardware must use the new ECRC (re-computed with the translated address) if it decides to forward the TLP as a peer request.