# IA-32 Intel<sup>®</sup> Architecture Software Developer's Manual

**Documentation Changes**

September 2005

**Notice:** The IA-32 Intel $^{\circledR}$  Architecture may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the specification updates.

Document Number: 252046-014

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

$I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $I^2C$  bus/protocol and was developed by Intel. Implementations of the  $I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel, Pentium, Celeron, Intel SpeedStep, Intel Xeon and the Intel logo, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2002–2005, Intel Corporation. All rights reserved.

| Revision History         | 4 |

|--------------------------|---|

| Preface                  | 5 |

| Summary Table of Changes | 6 |

| Documentation Changes    | 7 |

# **Revision History**

| Version | Description                                                                                                                                                                                                                   | Date           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001    | Initial Release                                                                                                                                                                                                               | November 2002  |

| -002    | <ul> <li>Added 1-10 Documentation Changes.</li> <li>Removed old Documentation Changes items that already have been incorporated in the published Software Developer's manual</li> </ul>                                       | December 2002  |

| -003    | <ul> <li>Added 9 -17 Documentation Changes.</li> <li>Removed Documentation Change #6 - References to bits Gen and Len Deleted.</li> <li>Removed Documentation Change #4 - VIF Information Added to CLI Discussion.</li> </ul> | February 2003  |

| -004    | <ul><li>Removed Documentation changes 1-17.</li><li>Added Documentation changes 1-24.</li></ul>                                                                                                                               | June 2003      |

| -005    | <ul><li>Removed Documentation Changes 1-24.</li><li>Added Documentation Changes 1-15.</li></ul>                                                                                                                               | September 2003 |

| -006    | Added Documentation Changes 16- 34.                                                                                                                                                                                           | November 2003  |

| -007    | <ul><li>Updated Documentation changes 14, 16, 17, and 28.</li><li>Added Documentation Changes 35-45.</li></ul>                                                                                                                | January 2004   |

| -008    | <ul><li>Removed Documentation Changes 1-45.</li><li>Added Documentation Changes 1-5.</li></ul>                                                                                                                                | March 2004     |

| -009    | Added Documentation Changes 7-27.                                                                                                                                                                                             | May 2004       |

| -010    | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1.</li></ul>                                                                                                                                  | August 2004    |

| -011    | Added Documentation Changes 2-28.                                                                                                                                                                                             | November 2004  |

| -012    | <ul><li>Removed Documentation Changes 1-28.</li><li>Added Documentation Changes 1-16.</li></ul>                                                                                                                               | March 2005     |

| -013    | <ul> <li>Updated title.</li> <li>There are no Documentation Changes for this revision of the document.</li> </ul>                                                                                                             | July 2005      |

| -014    | Added Documentation Changes 1-21.                                                                                                                                                                                             | September 2005 |

### Preface

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of documentation changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

### **Affected Documents/Related Documents**

| Document Title                                                                                          | Document<br>Number |

|---------------------------------------------------------------------------------------------------------|--------------------|

| IA-32 Intel® Architecture Software Developer's Manual: Volume 1, Basic Architecture                     | 253665             |

| IA-32 Intel <sup>®</sup> Architecture Software Developer's Manual: Volume 2A, Instruction Set Reference | 253666             |

| IA-32 Intel <sup>®</sup> Architecture Software Developer's Manual: Volume 2B, Instruction Set Reference | 253667             |

| IA-32 Intel <sup>®</sup> Architecture Software Developer's Manual: Volume 3, System Programming Guide   | 253668             |

### **Nomenclature**

**Documentation Changes** include errors or omissions from the current published specifications. These changes will be incorporated in the next release of the Software Development Manual.

# **Summary Table of Changes**

The following table indicates documentation changes which apply to the IA-32 Intel Architecture. This table uses the following notations:

### **Codes Used in Summary Table**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

### **Summary Table of Documentation Changes**

| Number | Documentation Changes                                                      |

|--------|----------------------------------------------------------------------------|

| 1      | Table addressing CPUID return values has been updated                      |

| 2      | Changes made to clarify the impact on TLBs when code modifies CR4.PGE      |

| 3      | More information provided on the handling override prefixes in 64-bit mode |

| 4      | IA32_MISC_ENABLE information updated for clarity                           |

| 5      | Opcode map updated                                                         |

| 6      | Count operand usage issue corrected                                        |

| 7      | Note on interrupt delivery added                                           |

| 8      | Error corrected in Table 9-1, Volume 3                                     |

| 9      | Updated CPUID operation description                                        |

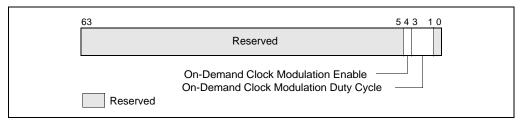

| 10     | Information on IA32_CLOCK_MODULATION MSR updated                           |

| 11     | MOVUPS/MOVUPD inconsistencies corrected                                    |

| 12     | Information on IRET treatment of EFLAGS.NT updated                         |

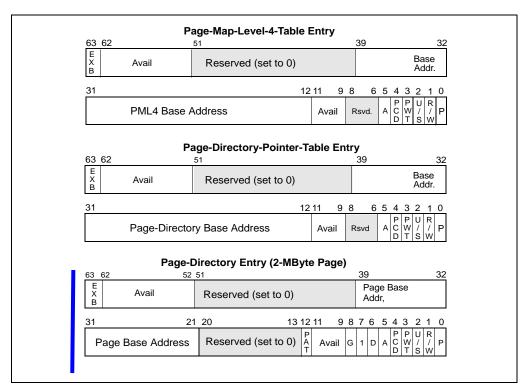

| 13     | Incorrect diagram of page directory entry corrected                        |

| 14     | MOV to/from control registers updated                                      |

| 15     | LGDT/LIDT exceptions updated                                               |

| 16     | Underflow description corrected                                            |

| 17     | IN/OUT virtual-8086 mode exceptions updated                                |

| 18     | SYSENTER and SYSEXIT sections updated                                      |

| 19     | LTR section updated                                                        |

| 20     | Table updated                                                              |

| 21     | Corrections to Jcc summary table                                           |

# **Documentation Changes**

#### 1. Table addressing CPUID return values has been updated

In Table 3-12, "CPUID—CPU Identification" section, *IA-32 Intel Architecture Software Developer's Manual, Volume 2A*; a number of issues have been addressed:

- Associativity field values have been corrected.

- The relationship between CPUID.EAX = 04H, ECX, and specific return values has been clarified using an extended note.

- Formatting issues have been addressed.

Table 3-12 has been reproduced below. See the change bars for the impacted area.

\_\_\_\_\_

Table 3-12. Information Returned by CPUID Instruction

| Initial EAX<br>Value |                          | Information Provided about the Processor                                                                                                                                                                                                                                                                                                      |

|----------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | Basic CF                 | PUID Information                                                                                                                                                                                                                                                                                                                              |

| OН                   | EAX<br>EBX<br>ECX<br>EDX | Maximum Input Value for Basic CPUID Information (see Table 3-13) "Genu" "ntel" "inel"                                                                                                                                                                                                                                                         |

| 01H                  | EAX                      | Version Information: Type, Family, Model, and Stepping ID (see Figure 3-5)                                                                                                                                                                                                                                                                    |

|                      | EBX                      | Bits 7-0: Brand Index Bits 15-8: CLFLUSH line size (Value * 8 = cache line size in bytes) Bits 23-16: Maximum number of logical processors in this physical package. Bits 31-24: Initial APIC ID                                                                                                                                              |

|                      | ECX<br>EDX               | Extended Feature Information (see Figure 3-6 and Table 3-15) Feature Information (see Figure 3-7 and Table 3-16)                                                                                                                                                                                                                              |

| 02H                  | EAX<br>EBX<br>ECX<br>EDX | Cache and TLB Information (see Table 3-17) Cache and TLB Information Cache and TLB Information Cache and TLB Information                                                                                                                                                                                                                      |

| 03H                  | EAX<br>EBX               | Reserved.                                                                                                                                                                                                                                                                                                                                     |

|                      | ECX                      | Bits 00-31 of 96 bit processor serial number. (Available in Pentium III processor only; otherwise, the value in this register is reserved.)                                                                                                                                                                                                   |

|                      | EDX                      | Bits 32-63 of 96 bit processor serial number. (Available in Pentium III processor only; otherwise, the value in this register is reserved.)                                                                                                                                                                                                   |

|                      |                          | <b>NOTE:</b> Processor serial number (PSN) is not supported in the Pentium 4 processor or later. On all models, use the PSN flag (returned using CPUID) to check for PSN support before accessing the feature. See AP-485, <i>Intel Processor Identification and the CPUID Instruction</i> (Order Number 241618) for more information on PSN. |

Table 3-12. Information Returned by CPUID Instruction (Continued)

| Initial EAX<br>Value |            | Information Provided about the Processor                                                                                                                                                                                                                                                                                                                    |

|----------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |            | ves > 3 < 80000000 are visible only when<br>C_ENABLES.BOOT_NT4[bit 22] = 0 (default).                                                                                                                                                                                                                                                                       |

|                      | Determinis | tic Cache Parameters Leaf                                                                                                                                                                                                                                                                                                                                   |

| 04H                  |            | NOTE: 04H output also depends on the inital value in ECX. See also: "INPUT EAX = 4: Returns Deterministic Cache Parameters for Each Level" on page 3-172.                                                                                                                                                                                                   |

|                      | EAX        | Bits 4-0: Cache Type* Bits 7-5: Cache Level (starts at 1) Bits 8: Self Initializing cache level (does not need SW initialization) Bits 9: Fully Associative cache Bits 13-10: Reserved Bits 25-14: Maximum number of threads sharing this cache in a physical package (see note)** Bits 31-26: Maximum number of processor cores in this physical package** |

|                      | EBX        | Bits 11-00: L = System Coherency Line Size** Bits 21-12: P = Physical Line partitions** Bits 31-22: W = Ways of associativity**                                                                                                                                                                                                                             |

|                      | ECX        | Bits 31-00: S = Number of Sets**                                                                                                                                                                                                                                                                                                                            |

|                      | EDX        | Reserved = 0                                                                                                                                                                                                                                                                                                                                                |

|                      |            | MORE NOTES:  * Cache Type fields: 0 = Null - No more caches 3 = Unified Cache 1 = Data Cache 4-31 = Reserved 2 = Instruction Cache  ** Add one to the value in the register to get the number. For example, the number of processor cores is EAX[31:26]+1.                                                                                                  |

|                      | MONITOR    | /MWAIT Leaf                                                                                                                                                                                                                                                                                                                                                 |

| 5H                   | EAX        | Bits 15-00: Smallest monitor-line size in bytes (default is processor's monitor granularity) Bits 31-16: Reserved = 0                                                                                                                                                                                                                                       |

|                      | EBX        | Bits 15-00: Largest monitor-line size in bytes (default is processor's monitor granularity) Bits 31-16: Reserved = 0                                                                                                                                                                                                                                        |

|                      | ECX<br>EDX | Reserved = 0<br>Reserved = 0                                                                                                                                                                                                                                                                                                                                |

Table 3-12. Information Returned by CPUID Instruction (Continued)

| Initial EAX |                          |                                                                                                                                                                                                                               |

|-------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Value       |                          | Information Provided about the Processor                                                                                                                                                                                      |

|             | Extended                 | d Function CPUID Information                                                                                                                                                                                                  |

| 80000000H   | EAX                      | Maximum Input Value for Extended Function CPUID Information (see Table 3-13).                                                                                                                                                 |

|             | EBX<br>ECX<br>EDX        | Reserved<br>Reserved<br>Reserved                                                                                                                                                                                              |

| 80000001H   | EAX                      | Extended Processor Signature and Extended Feature Bits.                                                                                                                                                                       |

|             | EBX                      | Reserved                                                                                                                                                                                                                      |

|             | ECX                      | Bit 0: LAHF/SAHF available in 64-bit mode<br>Bits 31-1 Reserved                                                                                                                                                               |

|             | EDX                      | Bits 10-0: Reserved Bit 11: SYSCALL/SYSRET available (when in 64-bit mode) Bits 19-12: Reserved = 0 Bit 20: Execute Disable Bit available Bits 28-21: Reserved = 0 Bit 29: Intel EM64T available = 1 Bits 31-30: Reserved = 0 |

| 80000002H   | EAX<br>EBX<br>ECX<br>EDX | Processor Brand String Processor Brand String Continued Processor Brand String Continued Processor Brand String Continued Processor Brand String Continued                                                                    |

| 80000003H   | EAX<br>EBX<br>ECX<br>EDX | Processor Brand String Continued Processor Brand String Continued Processor Brand String Continued Processor Brand String Continued                                                                                           |

| 80000004H   | EAX<br>EBX<br>ECX<br>EDX | Processor Brand String Continued Processor Brand String Continued Processor Brand String Continued Processor Brand String Continued                                                                                           |

Table 3-12. Information Returned by CPUID Instruction (Continued)

| Initial EAX<br>Value |                          | Information Provided about the Processor                                                                                                                |

|----------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80000005H            | EAX<br>EBX<br>ECX<br>EDX | Reserved = 0 Reserved = 0 Reserved = 0 Reserved = 0                                                                                                     |

| 80000006H            | EAX<br>EBX               | Reserved = 0<br>Reserved = 0                                                                                                                            |

|                      | ECX                      | Bits 7-0: Cache Line size Bits 15-12: L2 Associativity field * Bits 31-16: Cache size in 1K units                                                       |

|                      | EDX                      | Reserved = 0                                                                                                                                            |

|                      |                          | NOTES:  * L2 associativity field encodings: 00H - Disabled 01H - Direct mapped 02H - 2-way 04H - 4-way 06H - 8-way 08H - 16-way 0FH - Fully associative |

| 8000007H             | EAX<br>EBX<br>ECX<br>EDX | Reserved = 0 Reserved = 0 Reserved = 0 Reserved = 0                                                                                                     |

#### 2. Changes made to clarify the impact on TLBs when code modifies CR4.PGE

In Section 3.12, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*; updates that clarify the relationship between CR4.PGE and TLB have been made. The text has been reproduced below (with changes introduced in context). See the change bars for the impacted area.

... ...

(Introduced in the Pentium Pro processor.) The page global enable (PGE) flag in register CR4 and the global (G) flag of a page-directory or page-table entry (bit 8) can be used to prevent frequently used pages from being automatically invalidated in the TLBs on a task switch or a load of register CR3. (See Section 3.7.6, "Page-Directory and Page-Table Entries", for more information about the global flag.) When the processor loads a page-directory or page-table entry for a global page into a TLB, the entry will remain in the TLB indefinitely. The only ways to deterministically invalidate global page entries are as follows:

- Clear the PGE flag; this will invalidate the TLBs.

- Execute the INVLPG instruction to invalidate individual page-directory or page-table entries in the TLBs.

For additional information about invalidation of the TLBs, see Section 10.9, "Invalidating the Translation Lookaside Buffers (TLBs)".

·· ··· ···

Sections 10.11.7.2 and 10.11.8, *IA-32 Intel Architecture Software Developer's Manual, Volume 3;* changes have also been made to to address the same issue. The text has been reproduced below (with changes introduced in context). See the change bars for the impacted area.

\_\_\_\_\_

#### 10.11.7.2 MemTypeSet() Function

The MemTypeSet() function in Example 10-6 sets a MTRR for the physical memory range specified by the parameters base and size to the type specified by type. The base address and size are multiples of 4 KBytes and the size is not 0.

#### Example 10-6. MemTypeSet Pseudocode

```

IF CPU_FEATURES.MTRR (* processor supports MTRRs *)

THEN

IF BASE and SIZE are not 4-KByte aligned or size is 0

THEN return INVALID;

IF (BASE + SIZE) wrap 4-GByte address space

THEN return INVALID;

IF TYPE is invalid for Pentium 4, Intel Xeon, and P6 family processors

THEN return UNSUPPORTED;

FI;

IF TYPE is WC and not supported

THEN return UNSUPPORTED;

IF IA32_MTRRCAP.FIX is set AND range can be mapped using a fixed-range MTRR

pre_mtrr_change();

update affected MTRR;

post_mtrr_change();

FI;

ELSE (* try to map using a variable MTRR pair *)

IF IA32_MTRRCAP.VCNT = 0

THEN return UNSUPPORTED;

IF conflicts with current variable ranges

THEN return RANGE_OVERLAP;

FI;

IF no MTRRs available

THEN return VAR_NOT_AVAILABLE;

IF BASE and SIZE do not meet the power of 2 requirements for variable MTRRs

THEN return INVALID_VAR_REQUEST;

FI;

pre_mtrr_change();

Update affected MTRRs;

post_mtrr_change();

FI;

pre_mtrr_change()

BEGIN

```

```

disable interrupts:

Save current value of CR4:

disable and flush caches;

flush TLBs:

disable MTRRs:

IF multiprocessing

THEN maintain consistency through IPIs;

END

post_mtrr_change()

BEGIN

flush caches and TLBs:

enable MTRRs:

enable caches:

restore value of CR4;

enable interrupts:

END

```

The physical address to variable range mapping algorithm in the MemTypeSet function detects conflicts with current variable range registers by cycling through them and determining whether the physical address in question matches any of the current ranges. During this scan, the algorithm can detect whether any current variable ranges overlap and can be concatenated into a single range.

The pre\_mtrr\_change() function disables interrupts prior to changing the MTRRs, to avoid executing code with a partially valid MTRR setup. The algorithm disables caching by setting the CD flag and clearing the NW flag in control register CR0. The caches are invalidated using the WBINVD instruction. The algorithm flushes all TLB entries either by clearing the page-global enable (PGE) flag in control register CR4 (if PGE was already set) or by updating control register CR3 (if PGE was already clear). Finally, it disables MTRRs by clearing the E flag in the IA32\_MTRR\_DEF\_TYPE MSR.

After the memory type is updated, the post\_mtrr\_change() function re-enables the MTRRs and again invalidates the caches and TLBs. This second invalidation is required because of the processor's aggressive prefetch of both instructions and data. The algorithm restores interrupts and re-enables caching by setting the CD flag.

An operating system can batch multiple MTRR updates so that only a single pair of cache invalidations occur.

#### 10.11.8 MTRR Considerations in MP Systems

In MP (multiple-processor) systems, the operating systems must maintain MTRR consistency between all the processors in the system. The Pentium 4, Intel Xeon, and P6 family processors provide no hardware support to maintain this consistency. In general, all processors must have the same MTRR values.

This requirement implies that when the operating system initializes an MP system, it must load the MTRRs of the boot processor while the E flag in register MTRRdefType is 0. The operating system then directs other processors to load their MTRRs with the same memory map. After all the processors have loaded their MTRRs, the operating system signals them to enable their MTRRs. Barrier synchronization is used to prevent further memory accesses until all processors indicate that the MTRRs are enabled. This synchronization is likely to be a shoot-down style algorithm, with shared variables and interprocessor interrupts.

Any change to the value of the MTRRs in an MP system requires the operating system to repeat the loading and enabling process to maintain consistency, using the following procedure:

- 1. Broadcast to all processors to execute the following code sequence.

- 2. Disable interrupts.

- 3. Wait for all processors to reach this point.

- 4. Enter the no-fill cache mode. (Set the CD flag in control register CR0 to 1 and the NW flag to 0.)

- 5. Flush all caches using the WBINVD instructions. Note on a processor that supports self-snooping, CPUID feature flag bit 27, this step is unnecessary.

- 6. If the PGE flag is set in control register CR4, flush all TLBs by clearing that flag.

- 7. If the PGE flag is clear in control register CR4, flush all TLBs by executing a MOV from control register CR3 to another register and then a MOV from that register back to CR3.

- Disable all range registers (by clearing the E flag in register MTRRdefType). If only variable ranges are being modified, software may clear the valid bits for the affected register pairs instead.

- 9. Update the MTRRs.

- 10. Enable all range registers (by setting the E flag in register MTRRdefType). If only variable-range registers were modified and their individual valid bits were cleared, then set the valid bits for the affected ranges instead.

- 11. Flush all caches and all TLBs a second time. (The TLB flush is required for Pentium 4, Intel Xeon, and P6 family processors. Executing the WBINVD instruction is not needed when using Pentium 4, Intel Xeon, and P6 family processors, but it may be needed in future systems.)

- 12. Enter the normal cache mode to re-enable caching. (Set the CD and NW flags in control register CR0 to 0.)

- 13. Set PGE flag in control register CR4, if cleared in Step 6 (above).

- 14. Wait for all processors to reach this point.

- 15. Enable interrupts.

#### More information provided on the handling override prefixes in 64-bit mode

Section 3.3.7.1, *IA-32 Intel Architecture Software Developer's Manual, Volume 1;* information on the handling of override prefixes has been added. The added text has been reproduced below (with changes reproduced in context). See the change bars for the impacted area.

#### \_\_\_\_\_

#### 3.3.7.1 Canonical Addressing

In 64-bit mode, an address is considered to be in canonical form if address bits 63 through to the most-significant implemented bit by the microarchitecture are set to either all ones or all zeros.

Intel EM64T defines a 64-bit linear address. Implementations can support less. The first implementation of IA-32 processors with Intel EM64T supports a 48-bit linear address. This means a canonical address must have bits 63 through 48 set to zeros or ones (depending on whether bit 47 is a zero or one).

Although implementations may not use all 64 bits of the linear address, they should check bits 63 through the most-significant implemented bit to see if the address is in canonical form. If a linear-memory reference is not in canonical form, the implementation should generate an exception. In most cases, a general-protection exception (#GP) is generated. However, in the case of explicit or implied stack references, a stack fault (#SS) is generated.

Instructions that have implied stack references, by default, use the SS segment register. These include PUSH/POP-related instructions and instructions using RSP/RBP as base registers. In these cases, the canonical fault is #SF.

If an instruction uses base registers RSP/RBP and uses a segment override prefix to specify a non-SS segment, a canonical fault generates a #GP (instead of an #SF). In 64-bit mode, only FS and GS segment-overrides are applicable in this situation. Other segment override prefixes (CS, DS, ES and SS) are ignored. Note that this also means that an SS segment-override applied to a "non-stack" register reference is ignored. Such a sequence still produces a #GP for a canonical fault (and not an #SF).

#### 4. IA32\_MISC\_ENABLE information updated for clarity

In Table B-1, *IA-32 Intel Architecture Software Developer's Manual, Volume 3;* corrections have been made to IA32\_MISC\_ENABLE data. The applicable table cells are reproduced below (with the changes marked in context). See the change bars for the impacted area.

\_\_\_\_\_

Table B-1 MSRs in the Pentium 4 and Intel Xeon Processors

| Registe<br>Address | 6   | Register Name    | Model<br>Avail-  | Shared/ <sub>1</sub> |                                                                                                                                                                                                                                                          |

|--------------------|-----|------------------|------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hex                | Dec | Fields and Flags | ability          | Unique '             | Bit Description                                                                                                                                                                                                                                          |

| 1A0H               | 416 | IA32_MISC_ENABLE | 0, 1, 2,<br>3, 4 | Shared               | Enable Miscellaneous Processor<br>Features. (R/W)<br>Allows a variety of processor<br>functions to be enabled and disabled.                                                                                                                              |

|                    |     | 0                |                  |                      | Fast-Strings Enable. When set, the fast-strings feature on the Pentium 4 processor is enabled (default); when clear, fast-strings are disabled.                                                                                                          |

|                    |     | 1                |                  |                      | Reserved.                                                                                                                                                                                                                                                |

|                    |     | 2                |                  |                      | x87 FPU Fopcode Compatibility Mode Enable. When set, fopcode compatibility mode is enabled; when clear (default), mode is disabled. See "Fopcode Compatibility Mode" in Chapter 8 of the IA-32 Intel Architecture Software Developer's Manual. Volume 1. |

|                    |     | 3                |                  |                      | Thermal Monitor 1 Enable. When set, clock modulation controlled by the processor's internal thermal sensor is enabled; when clear (default), automatic clock modulation is disabled. See Section 13.16.2, "Thermal Monitor".                             |

Table B-1 MSRs in the Pentium 4 and Intel Xeon Processors

| <br>able b-1 Wisks III the i | ontium + unu mic | 7. 7.0011 1 100000010                                                                                                                                                                                           |

|------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                            |                  | Split-Lock Disable. This debug feature is specific to the Pentium 4 processor. When set, the bit causes an #AC exception to be issued instead of a split-lock cycle. Operating systems                          |

|                              |                  | that set this bit must align system structures to avoid split-lock scenarios.                                                                                                                                   |

|                              |                  | When the bit is clear (default), normal split-locks are issued to the bus.                                                                                                                                      |

| 5                            |                  | Reserved.                                                                                                                                                                                                       |

| 6                            |                  | Third-Level Cache Disable. (R/W) When set, the third-level cache is disabled; when clear (default) the third-level cache is enabled. This flag is reserved for processors that do not have a third-level cache. |

|                              |                  | Note that the bit controls only the third-level cache; and only if overall caching is enabled through the CD flag of control register CR0, the page-level cache controls, and/or the MTRRs.                     |

|                              |                  | See Section 10.5.4, "Disabling and Enabling the L3 Cache".                                                                                                                                                      |

| 7                            |                  | Performance Monitoring<br>Available. (R)<br>When set, performance monitoring is<br>enabled; when clear, performance<br>monitoring is disabled.                                                                  |

| 8                            |                  | Suppress Lock Enable. When set, assertion of LOCK on the bus is suppressed during a Split Lock access. When clear (default), LOCK is not suppressed.                                                            |

| 9                            |                  | Prefetch Queue Disable. When set, disables the prefetch queue. When clear (default), enables the prefetch queue.                                                                                                |

Table B-1 MSRs in the Pentium 4 and Intel Xeon Processors

|  |       | 1 | l |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--|-------|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | 10    |   |   | FERR# Interrupt Reporting Enable. (R/W) When set, interrupt reporting through the FERR# pin is enabled; when clear, this interrupt reporting function is disabled. When this flag is set and the processor is in the stop-clock state (STPCLK# is asserted), asserting the FERR# pin signals to the processor that an interrupt (such as, INIT#, BINIT#, INTR, NMI, SMI#, or RESET#) is pending and that the processor should return to normal operation to handle the interrupt. This flag does not affect the normal |

|  |       |   |   | operation of the FERR# pin (to indicate an unmasked floating-point error) when the STPCLK# pin is not asserted.                                                                                                                                                                                                                                                                                                                                                                                                        |

|  | 11    |   |   | Branch Trace Storage Unavailable (BTS_UNAVILABLE). (R) When set, the processor does not support branch trace storage (BTS); when clear, BTS is supported.                                                                                                                                                                                                                                                                                                                                                              |

|  | 12    |   |   | Precise Event Based Sampling Unavailable (PEBS_UNAVILABLE). (R) When set, the processor does not support precise event-based sampling (PEBS); when clear, PEBS is supported.                                                                                                                                                                                                                                                                                                                                           |

|  | 13    | 3 |   | TM2 Enable. (R/W) When this bit is set (1) and the thermal sensor indicates that the die temperature is at the pre-determined threshold, the Thermal Monitor 2 mechanism is engaged. TM2 will reduce the bus to core ratio and voltage according to the value last written to MSR_THERM2_CTL bits 15:0.                                                                                                                                                                                                                |

|  |       |   |   | When this bit is clear (0, default), the processor does not change the VID signals or the bus to core ratio when the processor enters a thermal managed state.                                                                                                                                                                                                                                                                                                                                                         |

|  |       |   |   | NOTE: If the TM2 feature flag (ECX[8]) is not set to 1 after executing CPUID with EAX = 1, then this feature is not supported and BIOS must not alter the contents of this bit location. The processor is operating out of spec if both this bit and the TM1 bit are set to disabled states.                                                                                                                                                                                                                           |

|  | 17:14 |   |   | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Table B-1 MSRs in the Pentium 4 and Intel Xeon Processors

|  |          |   | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--|----------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | 18       | 3 | ENABLE MONITOR FSM. (R/W) When set (default), the MONITOR and MWAIT instructions are enabled. When clear, these instructions are disabled and attempting to execute them results in an invalid opcode exception.  NOTE: CPUID.1:EAX.MONITOR[bit 3] indicates the setting of the Enable Monitor FSM bit. If CPUID.1:ECX.SSE3[bit 0] is not set, then the operating system must not attempt to alter the setting of the Enable Monitor FSM bit. BIOS should leave this bit in the default state. |

|  | 19       |   | Adjacent Cache Line Prefetch Disable. (R/W) When set to 1, the processor fetches the cache line of the 128-byte sector containing currently required data. When set to 0, the processor fetches both cache lines in the sector. Single processor platforms should not set this bit. Server platforms should set or clear this bit based on                                                                                                                                                     |

|  |          |   | platform performance observed in validation and testing. BIOS may contain a setup option that controls the setting of this bit.                                                                                                                                                                                                                                                                                                                                                                |

|  | 21:20    |   | validation and testing. BIOS may contain a setup option that                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|  | 21:20 22 | 3 | validation and testing. BIOS may contain a setup option that controls the setting of this bit.                                                                                                                                                                                                                                                                                                                                                                                                 |

Table B-1 MSRs in the Pentium 4 and Intel Xeon Processors

| 24 | L1 Data Cache Context Mode. (R/W)                                                                                                                                                                                                                                                                                      |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | When set, the L1 data cache is placed in shared mode; when clear (default), the cache is placed in adaptive mode. This bit is only enabled for IA-32 processors that support Intel Hyper-Threading Technology. See Section 10.5.6, "L1 Data Cache Context Mode" for additional information about the use of this flag. |

|    | When L1 is running in adaptive mode<br>and CR3s are identical, data in L1 is<br>shared across logical processors.<br>Otherwise, L1 is not shared and<br>cache use is competitive.                                                                                                                                      |

|    | NOTE: If the Context ID feature flag (ECX[10]) is set to 0 after executing CPUID with EAX = 1, the ability to switch modes is not supported. BIOS must not alter the contents of IA32_MISC_ENABLE[24].                                                                                                                 |

Changes to support IA32\_MISC\_ENABLE have also been made to Section 10.5.6 through 10.5.6.2, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*. The text has been reproduced below (with changes reproduced in context). See the change bars for the impacted area.

\_\_\_\_\_

#### 10.5.6 L1 Data Cache Context Mode

L1 data cache context mode is a feature of IA-32 processors that support Hyper-Threading Technology. When CPUID.1: $ECX[bit\ 10] = 1$ , the processor supports setting L1 data cache context mode using the L1 data cache context mode flag (IA32\_MISC\_ENABLE[bit\ 24]). Selectable modes are adaptive mode (default) and shared mode.

The BIOS is responsible for configuring the L1 data cache context mode.

#### 10.5.6.1 Adaptive Mode

Adaptive mode facilitates L1 data cache sharing between logical processors. When running in adaptive mode, the L1 data cache is shared across logical processors in the same core if:

- CR3 control registers for logical processors sharing the cache are identical.

- The same paging mode is used by logical processors sharing the cache.

In this situation, the entire L1 data cache is available to each logical processor (instead of being competitively shared).

If CR3 values are different for the logical processors sharing an L1 data cache or the logical processors use different paging modes, processors compete for cache resources. This reduces the effective size of the cache for each logical processor. Aliasing of the cache is not allowed (which prevents data thrashing).

#### 10.5.6.2 Shared Mode

In shared mode, the L1 data cache is competitively shared between logical processors. This is true even if the logical processors use identical CR3 registers and paging modes.

In shared mode, linear addresses in the L1 data cache can be aliased, meaning that one linear address in the cache can point to different physical locations. The mechanism for resolving aliasing can lead to thrashing. For this reason, IA32\_MISC\_ENABLE[bit 24] = 0 is the preferred configuration for IA-32 processors that support Hyper-Threading Technology.

#### 5. Opcode map updated

In Table A-4, *IA-32 Intel Architecture Software Developer's Manual, Volume 2B*; two table cells have been updated to reflect the operation of modern processors. The impacted rows and columns are reproduced below. See the shaded cells.

\_\_\_\_\_

Table A-4. Two-Byte Opcode Map for Non-64-Bit Mode (First Byte is 0FH)

|   | 8                                                 | 9                    | Α | В   | С | D      | E | F      |

|---|---------------------------------------------------|----------------------|---|-----|---|--------|---|--------|

| 0 | INVD <sup>1D</sup>                                | WBINVD <sup>1D</sup> |   | UD2 |   | NOP Ev |   |        |

| 1 | PREFETCH <sup>1C</sup><br>(Grp 16 <sup>1A</sup> ) |                      |   |     |   |        |   | NOP Ev |

#### 6. Count operand usage issue corrected

See the "PSLLW/PSLLD/PSLLQ—Shift Packed Data Left Logical," "PSRAW/PSRAD—Shift Packed Data Right Arithmetic," and "PSRLW/PSRLD/PSRLQ—Shift Packed Data Right Logical" sections of the *IA-32 Intel Architecture Software Developer's Manual, Volume 2B*.

The PRM did not explicitly state how much of the count operand is used to determine whether the count exceeds the datatype. One could have interpreted that the full 128-bit operand (for the SSE-2 integer xmm/m128 versions) is parsed for the count. Actually, only 64 bits of xmm/m128 are checked.

This problem has been corrected for all of the above sections. Only the "PSLLW/PSLLD/PSLLQ—Shift Packed Data Left Logical" section is reproduced below. See the change bars for the impacted area.

\_\_\_\_\_

#### PSLLW/PSLLD/PSLLQ—Shift Packed Data Left Logical

|                  |                          | 64-Bit | Compat/  |                                                                                 |

|------------------|--------------------------|--------|----------|---------------------------------------------------------------------------------|

| Opcode           | Instruction              | Mode   | Leg Mode | Description                                                                     |

| 0F F1 / <i>r</i> | PSLLW mm, mm/m64         | Valid  | Valid    | Shift words in <i>mm</i> left <i>mm/m64</i> while shifting in 0s.               |

| 66 0F F1 /r      | PSLLW xmm1,<br>xmm2/m128 | Valid  | Valid    | Shift words in <i>xmm1</i> left by <i>xmm2/m128</i> while shifting in 0s.       |

| 0F 71 /6 ib      | PSLLW xmm1, imm8         | Valid  | Valid    | Shift words in <i>mm</i> left by <i>imm8</i> while shifting in 0s.              |

| 66 0F 71 /6 ib   | PSLLW xmm1, imm8         | Valid  | Valid    | Shift words in <i>xmm1</i> left by <i>imm8</i> while shifting in 0s.            |

| 0F F2 /r         | PSLLD mm, mm/m64         | Valid  | Valid    | Shift doublewords in <i>mm</i> left by <i>mm/m64</i> while shifting in 0s.      |

| 66 0F F2 /r      | PSLLD xmm1,<br>xmm2/m128 | Valid  | Valid    | Shift doublewords in <i>xmm1</i> left by <i>xmm2/m128</i> while shifting in 0s. |

| 0F 72 /6 ib      | PSLLD mm, imm8           | Valid  | Valid    | Shift doublewords in <i>mm</i> left by <i>imm8</i> while shifting in 0s.        |

| 66 0F 72 /6 ib   | PSLLD xmm1, imm8         | Valid  | Valid    | Shift doublewords in <i>xmm1</i> left by <i>imm8</i> while shifting in 0s.      |

| 0F F3 /r         | PSLLQ mm, mm/m64         | Valid  | Valid    | Shift quadword in <i>mm</i> left by <i>mm/m64</i> while shifting in 0s.         |

| 66 0F F3 /r      | PSLLQ xmm1,<br>xmm2/m128 | Valid  | Valid    | Shift quadwords in <i>xmm1</i> left by <i>xmm2/m128</i> while shifting in 0s.   |

| 0F 73 /6 ib      | PSLLQ mm, imm8           | Valid  | Valid    | Shift quadword in <i>mm</i> left by <i>imm8</i> while shifting in 0s.           |

| 66 0F 73 /6 ib   | PSLLQ xmm1, imm8         | Valid  | Valid    | Shift quadwords in <i>xmm1</i> left by <i>imm8</i> while shifting in 0s.        |

#### **Description**

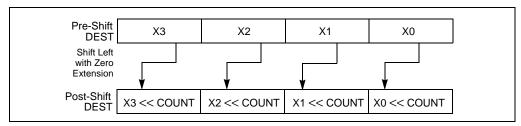

Shifts the bits in the individual data elements (words, doublewords, or quadword) in the destination operand (first operand) to the left by the number of bits specified in the count operand (second operand). As the bits in the data elements are shifted left, the empty low-order bits are cleared (set to 0). If the value specified by the count operand is greater than 15 (for words), 31 (for doublewords), or 63 (for a quadword), then the destination operand is set to all 0s. Figure 10-1 gives an example of shifting words in a 64-bit operand.

The destination operand may be an MMX technology register or an XMM register; the count operand can be either an MMX technology register or an 64-bit memory location, an XMM register or a 128-bit memory location, or an 8-bit immediate. Note that only the first 64-bits of a 128-bit count operand are checked to compute the count.

Figure 10-1. PSLLW, PSLLD, and PSLLQ Instruction Operation Using 64-bit Operand

The PSLLW instruction shifts each of the words in the destination operand to the left by the number of bits specified in the count operand; the PSLLD instruction shifts each of the doublewords in the destination operand; and the PSLLQ instruction shifts the quadword (or quadwords) in the destination operand.

In 64-bit mode, using an REX prefix in the form of REX.R permits this instruction to access additional registers (XMM8-XMM15).

#### Operation

```

PSLLW instruction with 64-bit operand:

IF (COUNT > 15)

THEN

DEST[64:0] \leftarrow0000000000000000H;

ELSE

DEST[15:0] ←ZeroExtend(DEST[15:0] << COUNT);

(* Repeat shift operation for 2nd and 3rd words *)

DEST[63:48] ←ZeroExtend(DEST[63:48] << COUNT);

FI:

PSLLD instruction with 64-bit operand:

IF (COUNT > 31)

THEN

DEST[64:0] \leftarrow0000000000000000H;

ELSE

DEST[31:0] ←ZeroExtend(DEST[31:0] << COUNT);

DEST[63:32] ←ZeroExtend(DEST[63:32] << COUNT);

FI;

PSLLQ instruction with 64-bit operand:

IF (COUNT > 63)

THEN

DEST[64:0] \leftarrow0000000000000000H;

ELSE

DEST ←ZeroExtend(DEST << COUNT);

PSLLW instruction with 128-bit operand:

COUNT ←COUNT_SOURCE[63:0];

IF (COUNT > 15)

THEN

ELSE

DEST[15:0] ←ZeroExtend(DEST[15:0] << COUNT);

(* Repeat shift operation for 2nd through 7th words *)

DEST[127:112] \leftarrow ZeroExtend(DEST[127:112] << COUNT);

FI;

PSLLD instruction with 128-bit operand:

COUNT ←COUNT_SOURCE[63:0];

IF (COUNT > 31)

THEN

ELSE

DEST[31:0] ←ZeroExtend(DEST[31:0] << COUNT);

(* Repeat shift operation for 2nd and 3rd doublewords *)

DEST[127:96] \leftarrow ZeroExtend(DEST[127:96] << COUNT);

FI;

```

#### Intel C/C#Compiler Intrinsic Equivalents

```

PSLLW

__m64 _mm_slli_pi16 (__m64 m, int count)

__m64 _mm_sll_pi16(__m64 m, __m64 count)

PSLLW

__m128i _mm_slli_pi16(__m64 m, int count)

PSLLW

PSLLW

__m128i _mm_slli_pi16(__m128i m, __m128i count)

PSLLD

__m64 _mm_slli_pi32(__m64 m, int_count)

__m64 _mm_sll_pi32(__m64 m, __m64 count)

PSLLD

PSLLD

__m128i _mm_slli_epi32(__m128i m, int count)

PSLLD

__m128i _mm_sll_epi32(__m128i m, __m128i count)

__m64 _mm_slli_si64(__m64 m, int_count)

PSLLQ

PSLLQ

__m64 _mm_sll_si64(__m64 m, __m64 count)

PSLLQ

__m128i _mm_slli_si64(__m128i m, int count)

PSLLQ

__m128i _mm_sll_si64(__m128i m, __m128i count)

```

#### Flags Affected

None.

#### **Numeric Exceptions**

None.

#### **Protected Mode Exceptions**

| #GP(0)  | If a memory operand | deffective address is   | s outside the CS. | DS, ES, FS, or GS    |

|---------|---------------------|-------------------------|-------------------|----------------------|

| πΟ1 (0) | II a memory operant | i ciiccii ve audicss is | o duiside die Co. | , DD, LD, I D, UI UD |

segment limit.

(128-bit operations only) If a memory operand is not aligned on a 16-byte

boundary, regardless of segment.

#SS(0) If a memory operand effective address is outside the SS segment limit.

#UD If CR0.EM[bit 2] = 1.

(128-bit operations only) If CR4.OSFXSR[bit 9] = 0.

(128-bit operations only) If CPUID.01H:EDX.SSE2[bit 26] = 0.

#NM If CR0.TS[bit 3] = 1.

#MF (64-bit operations only) If there is a pending x87 FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) (64-bit operations only) If alignment checking is enabled and an unaligned

memory reference is made while the current privilege level is 3.

#### **Real-Address Mode Exceptions**

#GP(0) (128-bit operations only) If a memory operand is not aligned on a 16-byte

boundary, regardless of segment.

If any part of the operand lies outside of the effective address space from 0 to

FFFFH.

#UD If CR0.EM[bit 2] = 1.

(128-bit operations only) If CR4.OSFXSR[bit 9] = 0.

(128-bit operations only) If CPUID.01H:EDX.SSE2[bit 26] = 0.

#NM If CR0.TS[bit 3] = 1.

#MF (64-bit operations only) If there is a pending x87 FPU exception.

#### Virtual-8086 Mode Exceptions

Same exceptions as in Real Address Mode

#PF(fault-code) For a page fault.

#AC(0) (64-bit operations only) If alignment checking is enabled and an unaligned

memory reference is made.

#### **Compatibility Mode Exceptions**

Same as for protected mode exceptions.

#### **64-Bit Mode Exceptions**

#SS(0) If a memory address referencing the SS segment is in a non-canonical form.

#GP(0) If the memory address is in a non-canonical form.

(128-bit operations only) If memory operand is not aligned on a 16-byte

boundary, regardless of segment.

#UD If CR0.EM[bit 2] = 1.

(128-bit operations only) If CR4.OSFXSR[bit 9] = 0.

(128-bit operations only) If CPUID.01H:EDX.SSE2[bit 26] = 0.

#NM If CR0.TS[bit 3] = 1.

#MF (64-bit operations only) If there is a pending x87 FPU exception.

#PF(fault-code) If a page fault occurs.

#AC(0) (64-bit operations only) If alignment checking is enabled and an unaligned

memory reference is made while the current privilege level is 3.

#### 7. Note on interrupt delivery added

In Section 5-10, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*; a note has been added. The note clarifies the relationship between interrupts and the IDT configuration task. Text from the applicable section has been reproduced below (with the note reproduced in context). See the change bars for the impacted area.

-----

#### 10.5 INTERRUPT DESCRIPTOR TABLE (IDT)

The interrupt descriptor table (IDT) associates each exception or interrupt vector with a gate descriptor for the procedure or task used to service the associated exception or interrupt. Like the GDT and LDTs, the IDT is an array of 8-byte descriptors (in protected mode). Unlike the GDT, the first entry of the IDT may contain a descriptor. To form an index into the IDT, the processor scales the exception or interrupt vector by eight (the number of bytes in a gate descriptor). Because there are only 256 interrupt or exception vectors, the IDT need not contain more than 256 descriptors. It can contain fewer than 256 descriptors, because descriptors are required only for the interrupt and exception vectors that may occur. All empty descriptor slots in the IDT should have the present flag for the descriptor set to 0.

The base addresses of the IDT should be aligned on an 8-byte boundary to maximize performance of cache line fills. The limit value is expressed in bytes and is added to the base address to get the address of the last valid byte. A limit value of 0 results in exactly 1 valid byte. Because IDT entries are always eight bytes long, the limit should always be one less than an integral multiple of eight (that is, 8N-1).

The IDT may reside anywhere in the linear address space. As shown in Figure 5-1, the processor locates the IDT using the IDTR register. This register holds both a 32-bit base address and 16-bit limit for the IDT.

The LIDT (load IDT register) and SIDT (store IDT register) instructions load and store the contents of the IDTR register, respectively. The LIDT instruction loads the IDTR register with the base address and limit held in a memory operand. This instruction can be executed only when the CPL is 0. It normally is used by the initialization code of an operating system when creating an IDT. An operating system also may use it to change from one IDT to another. The SIDT instruction copies the base and limit value stored in IDTR to memory. This instruction can be executed at any privilege level

If a vector references a descriptor beyond the limit of the IDT, a general-protection exception (#GP) is generated.

#### NOTE

Because interrupts are delivered to the processor core only once, an incorrectly configured IDT could result in incomplete interrupt handling and/or the blocking of interrupt delivery. IA-32 architecture rules need to be followed for setting up IDTR base/limit/access fields and each field in the gate descriptors. This includes the implicit referencing of the destination code segment through the GDT or LDT, and the accessing of the stack.

#### 8. Error corrected in Table 9-1, Volume 3

In Table 9-1, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*; a change has been made to correct an error. Cells from the table have been reproduced below (with the change

reproduced in context). There is a change to one cell and a change to notes that follow the table. See the change bars for the impacted area.

-----

Table 9-1. IA-32 Processor States Following Power-up, Reset, or INIT

|                                                               | Pentium 4 and Intel Xeon                                                                | <u> </u>                                                                                                                      |                                                                                                      |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Register                                                      | Processor                                                                               | P6 Family Processor                                                                                                           | Pentium Processor                                                                                    |

| EFLAGS <sup>1</sup>                                           | 00000002H                                                                               | 00000002H                                                                                                                     | 00000002H                                                                                            |

| EIP                                                           | 0000FFF0H                                                                               | 0000FFF0H                                                                                                                     | 0000FFF0H                                                                                            |

| CR0                                                           | 60000010H <sup>2</sup>                                                                  | 60000010H <sup>2</sup>                                                                                                        | 60000010H <sup>2</sup>                                                                               |

| CR2, CR3, CR4                                                 | 00000000H                                                                               | 00000000H                                                                                                                     | 00000000H                                                                                            |

| CS                                                            | Selector = F000H<br>Base = FFFF0000H<br>Limit = FFFFH<br>AR = Present, R/W,<br>Accessed | Selector = F000H<br>Base = FFFF0000H<br>Limit = FFFFH<br>AR = Present, R/W,<br>Accessed                                       | Selector = F000H<br>Base = FFFF0000H<br>Limit = FFFFH<br>AR = Present, R/W,<br>Accessed              |

| SS, DS, ES, FS,<br>GS                                         | Selector = 0000H<br>Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W,<br>Accessed | Selector = 0000H<br>Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W,<br>Accessed                                       | Selector = 0000H<br>Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W,<br>Accessed              |

| EDX                                                           | 00000FxxH                                                                               | 000n06xxH <sup>3</sup>                                                                                                        | 000005xxH                                                                                            |

| EAX                                                           | 04                                                                                      | 04                                                                                                                            | 04                                                                                                   |

| EBX, ECX, ESI,<br>EDI, EBP, ESP                               | 00000000H                                                                               | 00000000H                                                                                                                     | 00000000Н                                                                                            |

| ST0 through<br>ST7 <sup>5</sup>                               | Pwr up or Reset: +0.0<br>FINIT/FNINIT: Unchanged                                        | Pwr up or Reset: +0.0<br>FINIT/FNINIT: Unchanged                                                                              | Pwr up or Reset: +0.0<br>FINIT/FNINIT: Unchanged                                                     |

| x87 FPU Control<br>Word <sup>5</sup>                          | Pwr up or Reset: 0040H<br>FINIT/FNINIT: 037FH                                           | Pwr up or Reset: 0040H<br>FINIT/FNINIT: 037FH                                                                                 | Pwr up or Reset: 0040H<br>FINIT/FNINIT: 037FH                                                        |

| x87 FPU Status<br>Word <sup>5</sup>                           | Pwr up or Reset: 0000H<br>FINIT/FNINIT: 0000H                                           | Pwr up or Reset: 0000H<br>FINIT/FNINIT: 0000H                                                                                 | Pwr up or Reset: 0000H<br>FINIT/FNINIT: 0000H                                                        |

| x87 FPU Tag<br>Word <sup>5</sup>                              | Pwr up or Reset: 5555H<br>FINIT/FNINIT: FFFFH                                           | Pwr up or Reset: 5555H<br>FINIT/FNINIT: FFFFH                                                                                 | Pwr up or Reset: 5555H<br>FINIT/FNINIT: FFFFH                                                        |

| x87 FPU Data<br>Operand and CS<br>Seg. Selectors <sup>5</sup> | Pwr up or Reset: 0000H<br>FINIT/FNINIT: 0000H                                           | Pwr up or Reset: 0000H<br>FINIT/FNINIT: 0000H                                                                                 | Pwr up or Reset: 0000H<br>FINIT/FNINIT: 0000H                                                        |

| x87 FPU Data<br>Operand and<br>Inst. Pointers <sup>5</sup>    | Pwr up or Reset:<br>00000000H<br>FINIT/FNINIT: 00000000H                                | Pwr up or Reset:<br>00000000H<br>FINIT/FNINIT: 00000000H                                                                      | Pwr up or Reset:<br>00000000H<br>FINIT/FNINIT: 000000000H                                            |

| MM0 through<br>MM7 <sup>5</sup>                               | Pwr up or Reset:<br>0000000000000000H<br>INIT or FINIT/FNINIT:<br>Unchanged             | Pentium II and Pentium III<br>Processors Only—<br>Pwr up or Reset:<br>0000000000000000H<br>INIT or FINIT/FNINIT:<br>Unchanged | Pentium with MMX Technology Only— Pwr up or Reset: 0000000000000000H INIT or FINIT/FNINIT: Unchanged |

| XMM0 through<br>XMM7                                          | Pwr up or Reset:<br>0000000000000000H<br>INIT: Unchanged                                | Pentium III processor<br>Only—<br>Pwr up or Reset:<br>0000000000000000H<br>INIT: Unchanged                                    | NA                                                                                                   |

| MXCSR                                                         | Pwr up or Reset: 1F80H<br>INIT: Unchanged                                               | Pentium III processor only-<br>Pwr up or Reset: 1F80H<br>INIT: Unchanged                                                      | NA                                                                                                   |

Table 9-1. IA-32 Processor States Following Power-up, Reset, or INIT (Continued)

| Register                        | Pentium 4 and Intel Xeon Processor                                         | P6 Family Processor                                                        | Pentium Processor                                                          |

|---------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|

| GDTR, IDTR                      | Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W                     | Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W                     | Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W                     |

| LDTR, Task<br>Register          | Selector = 0000H<br>Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W | Selector = 0000H<br>Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W | Selector = 0000H<br>Base = 00000000H<br>Limit = FFFFH<br>AR = Present, R/W |