# INTEL® DATA STREAMING ACCELERATOR ARCHITECTURE SPECIFICATION

Order Number: 341204-002US Revision: 1.1 October 2020 You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

This document contains information on products in the design phase of development.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No product or component can be absolutely secure. Check with your system manufacturer or retailer or learn more at <a href="http://www.intel.com">http://www.intel.com</a>.

Intel® 64 architecture requires a system with a 64-bit enabled processor, chipset, BIOS and software. Performance will vary depending on the specific hardware and software you use. Consult your PC manufacturer for more information. For more information, visit <a href="http://www.intel.com/info/em64t">http://www.intel.com/info/em64t</a>.

Intel<sup>®</sup> Virtualization Technology requires a computer system with an enabled Intel<sup>®</sup> processor, BIOS, and virtual machine monitor (VMM). Functionality, performance or other benefits will vary depending on hardware and software configurations. Software applications may not be compatible with all operating systems. Consult your PC manufacturer. For more information, visit <a href="http://www.intel.com/go/virtualization">http://www.intel.com/go/virtualization</a>.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: <u>http://www.intel.com/design/literature.htm</u>.

Copyright © 2020, Intel Corporation. All Rights Reserved.

Intel, the Intel logo, Intel Data Streaming Accelerator, Intel DSA, Intel Virtualization Technology, Intel I/O Acceleration Technology, Intel IOAT, Intel Virtualization Technology for Directed I/O, Intel Scalable I/O Virtualization, and other Intel marks are trademarks of Intel Corporation or its subsidiaries.

\*Other names and brands may be claimed as the property of others.

### Table of Contents

| 1 | Intro      | ntroduction                                         |    |  |

|---|------------|-----------------------------------------------------|----|--|

|   | 1.1        | Audience                                            | 12 |  |

|   | 1.2        | References                                          | 12 |  |

| 2 | Ove        | rview                                               | 14 |  |

|   | 2.1        | High Level Usages                                   | 14 |  |

|   | 2.2        | Intel® DSA Features                                 | 14 |  |

|   | 2.2.1      | Infrastructure Features                             | 15 |  |

|   | 2.2.2      | Data Operations                                     |    |  |

|   | 2.2.3      | Control Operations                                  | 16 |  |

| 3 | Inte       | l® Data Streaming Accelerator Architecture          | 18 |  |

|   | 3.1        | Register and Software Programming Interface         | 18 |  |

|   | 3.2        | Descriptors                                         |    |  |

|   | 3.3        | Work Queues                                         | 19 |  |

|   | 3.3.1      | Shared Work Queue (SWQ)                             |    |  |

|   | 3.3.2      | Dedicated Work Queue (DWQ)                          | 21 |  |

|   | 3.4        | Engines and Groups                                  | 21 |  |

|   | 3.5        | Descriptor Processing                               |    |  |

|   | 3.6        | Descriptor Completion                               |    |  |

|   | 3.7        | Interrupts                                          |    |  |

|   | 3.8<br>3.9 | Batch Descriptor Processing<br>Ordering and Fencing |    |  |

|   | 3.10       | Drain Descriptor                                    |    |  |

|   | 3.11       | Address Translation                                 |    |  |

|   | 3.12       | Administrative Commands                             |    |  |

|   | 3.13       | Virtualization                                      | 32 |  |

| 4 | Qua        | lity of Service Control                             | 34 |  |

|   | 4.1        | Work Dispatch Priority                              | 34 |  |

|   | 4.2        | Traffic Classes                                     | 34 |  |

|   | 4.3        | Bandwidth Control                                   |    |  |

|   | 4.4        | Low Bandwidth Memory                                |    |  |

|   | 4.5        | Persistent Memory Support                           |    |  |

|   | 4.6        | Cache Control                                       |    |  |

| 5 | Errc       | r Handling                                          |    |  |

|   | 5.1        | Device Enable Checks                                |    |  |

|   | 5.2        | WQ Enable Checks                                    |    |  |

|   | 5.3        | Descriptor Submission Checks                        | 40 |  |

| 5.4   | Descriptor Checks                   |    |

|-------|-------------------------------------|----|

| 5.5   | Descriptor Reserved Field Checking  |    |

| 5.6   | Device Halt State                   |    |

| 5.7   | Error Codes                         |    |

| 5.7.1 | Operation Status Codes              |    |

| 5.7.2 | Other Software Error Codes          |    |

| 6 Pe  | rformance Monitoring                |    |

| 6.1   | Perfmon Discovery and Enumeration   |    |

| 6.2   | Perfmon Configuration Registers     |    |

| 6.3   | Event Counters                      |    |

| 6.3.1 | Counter Overflow                    |    |

| 6.3.2 | Counter Stop and Resume             |    |

| 6.4   | Filter Support                      |    |

| 6.5   | Event Programming Considerations    |    |

| 6.6   | Interrupt Generation                |    |

| 7 Re  | ference Software Architecture       |    |

| 7.1   | Kernel Mode Driver                  |    |

| 7.2   | User Mode Driver                    |    |

| 7.3   | Virtualization Software             |    |

| 7.3.1 | Virtual Intel® DSA Device           |    |

| 7.3.2 | Portal Virtualization               |    |

| 7.3.3 | SVM and PASID Virtualization        |    |

| 7.3.4 | Interrupt Virtualization            |    |

| 7.3.5 | Capability Virtualization           |    |

| 7.3.6 | State Migration During VM Migration |    |

| 8 De  | escriptor Formats                   |    |

| 8.1   | Common Descriptor Fields            |    |

| 8.1.1 | Trusted Fields                      |    |

| 8.1.2 | Operation                           | 61 |

| 8.1.3 | Flags                               | 61 |

| 8.1.4 | Completion Record Address           |    |

| 8.1.5 | Source Address                      |    |

| 8.1.6 |                                     |    |

| 8.1.7 |                                     |    |

| 8.1.8 | Completion Interrupt Handle         |    |

| 8.2   | Completion Record                   |    |

| 8.2.1 | Status                              |    |

| 8.2.2      | Result                                   | 67 |

|------------|------------------------------------------|----|

| 8.2.3      | Bytes Completed                          |    |

| 8.2.4      | Fault Address                            |    |

| 8.2.5      | Invalid Flags                            |    |

|            | criptor types                            |    |

| 8.3.1      | No-op                                    |    |

| 8.3.2      | Batch                                    |    |

| 8.3.3      | Drain                                    |    |

| 8.3.4      | Memory Move                              |    |

| 8.3.5      | Fill                                     |    |

| 8.3.6      | Compare                                  |    |

| 8.3.7      | Compare Pattern                          |    |

| 8.3.8      | Create Delta Record                      |    |

| 8.3.9      | Apply Delta Record                       |    |

| 8.3.10     | Memory Copy with Dualcast                |    |

| 8.3.11     | CRC Generation                           |    |

| 8.3.12     | Copy with CRC Generation                 |    |

| 8.3.13     | DIF Check                                |    |

| 8.3.14     | DIF Insert                               |    |

| 8.3.15     | DIF Strip                                |    |

| 8.3.16     | DIF Update                               |    |

| 8.3.17     | Cache Flush                              |    |

| 9 Register | Descriptions                             |    |

| 9.1 PCI    | Configuration Space Registers            | 93 |

| 9.1.1      | Base Address Registers (BAR)             |    |

| 9.1.2      | MSI-X Capability                         |    |

| 9.1.3      | Address Translation Capabilities         |    |

| 9.1.4      | Scalable I/O Virtualization Capability   |    |

| 9.1.5      | TPH Capability                           |    |

| 9.1.6      | VC Capability                            | 95 |

| 9.2 Con    | figuration and Control Registers (BAR0)  | 96 |

| 9.2.1      | Version Register (VERSION)               |    |

| 9.2.2      | General Capabilities Register (GENCAP)   |    |

| 9.2.3      | WQ Capabilities Register (WQCAP)         |    |

| 9.2.4      | Group Capabilities Register (GRPCAP)     |    |

| 9.2.5      | Engine Capabilities Register (ENGCAP)    |    |

| 9.2.6      | Operations Capabilities Register (OPCAP) |    |

| 9.2.7      | Table Offsets Register (OFFSETS)         |    |

| 9.2.8      | General Configuration Register (GENCFG)  |    |

| 9.2.9                            | General Control Register (GENCTRL)           |     |

|----------------------------------|----------------------------------------------|-----|

| 9.2.10                           | ) General Status Register (GENSTS)           |     |

| 9.2.11                           | I Interrupt Cause Register (INTCAUSE)        | 110 |

| 9.2.12                           | 2 Command Register (CMD)                     | 111 |

| 9.2.13                           | 3 Command Status Register (CMDSTATUS)        | 113 |

| 9.2.14                           | 4 Command Capabilities Register (CMDCAP)     | 116 |

| 9.2.15                           | 5 Software Error Register (SWERROR)          | 117 |

| 9.2.16                           |                                              |     |

| 9.2.17                           | 7 MSI-X Permissions Table (MSIXPERM)         |     |

| 9.2.18                           | 3 Group Configuration Table (GRPCFG)         | 121 |

| 9.2.19                           |                                              |     |

| 9.2.20                           | D Performance Monitoring Registers           |     |

| 9.2.21                           | I MSI-X Table                                | 137 |

| 9.2.22                           | 2 MSI-X Pending Bit Array                    | 137 |

| 9.2.23                           | 3 Interrupt Message Storage                  | 138 |

| 9.3                              | Portals (BAR2)                               | 139 |

| Append                           | lix A CRC Computation                        | 142 |

| Append                           | •                                            |     |

| B.1                              | DIF Check                                    | 146 |

| B.2                              | DIF Insert                                   |     |

| B.3                              | DIF Strip                                    |     |

| B.4 DIF Update                   |                                              | 147 |

| Append                           | ix C PCIe* Configuration Registers           |     |

| Append                           |                                              |     |

| D.1                              | Architectural Performance Monitoring Events  |     |

| D.2                              | Model-Specific Performance Monitoring Events |     |

| D.3 Event Configuration Examples |                                              |     |

## List of Figures

| Figure 3-1: Abstracted Internal Block Diagram of Intel® DSA | 19  |

|-------------------------------------------------------------|-----|

| Figure 3-2: Sample Group Configuration 1                    | 22  |

| Figure 3-3: Sample Group Configuration 2                    | 23  |

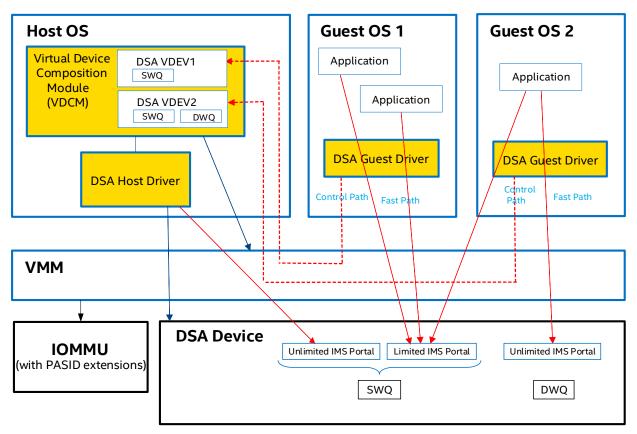

| Figure 7-1: Intel® Scalable IOV for Intel® DSA              | 55  |

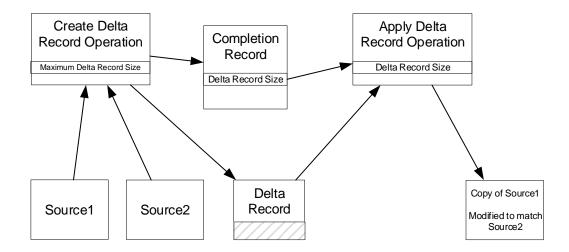

| Figure 8-1: Delta Record Usage                              | 79  |

| Figure 9-1: MMIO Register Map                               | 96  |

| Figure 9-2: Portals                                         | 140 |

#### List of tables

| Table 1-1: References                                         | 12  |

|---------------------------------------------------------------|-----|

| Table 2-1: Intel® DSA Data Operations                         |     |

| Table 2-2: Intel® DSA Control Operations                      |     |

| Table 3-1: Interrupt Delivery                                 | 25  |

| Table 5-1: Handling of Software Errors                        |     |

| Table 5-2: Completion Interrupt Handle Checks                 | 41  |

| Table 5-3: Supported Flags and Reserved Fields by Operations  |     |

| Table 5-4: Conditional Reserved Field Checking                |     |

| Table 5-5 : Operation Types with Required (must be 1) Flags   |     |

| Table 5-6: Operation Status Codes                             |     |

| Table 5-7: Other Software Error Codes                         |     |

| Table 6-1: Event Categories                                   |     |

| Table 6-2: Filter Types and Mask                              |     |

| Table 8-1: Descriptor Trusted Fields                          |     |

| Table 8-2: Operation Types                                    | 61  |

| Table 8-3: Descriptor Flags                                   | 64  |

| Table 8-4: Completion record Status field                     |     |

| Table 8-5: Drain Operation-specific Flags                     | 71  |

| Table 8-6: Completion Status for Compare Descriptor           | 74  |

| Table 8-7: Memory Copy with Dualcast Operation-specific Flags |     |

| Table 8-8: CRC Generation Operation-specific Flags            |     |

| Table 9-1: Register Attributes                                |     |

| Table 9-2: Address Translation Modes                          |     |

| Table 9-3: MMIO register initial values                       |     |

| Table 9-4: Read-only MMIO registers                           |     |

| Table 9-5: Administrative Commands                            |     |

| Table 9-6: Administrative Command Error Codes                 | 115 |

| Table 9-7: Default Commands Supported                         | 116 |

| Table 9-8: Work Queue Configuration Support                   |     |

| Table 9-9: Perfmon Register Read-only Status                  |     |

| Table 9-10: Filter Configuration Register Offsets             |     |

| Table 9-11: Supported Portal Operations                       |     |

### Revision History

| Date           | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November, 2019 | Rev 1.0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| October, 2020  | Rev 1.1  | <ul> <li>Addressed errata and omissions in Rev 1.0.</li> <li>Added guarantee of descriptor ordering under certain conditions.</li> <li>Added Command Capabilities register (CMDCAP).</li> <li>Added Dummy Portal.</li> <li>Added WQ ATS Disable.</li> <li>Added constraint on the value of Global Bandwidth Token Limit.</li> <li>Added Release Interrupt Handle command.</li> <li>Added details on Create Delta Record and Apply Delta Record.</li> <li>Added details on CRC and DIF operations.</li> <li>Removed Interrupt Handle Request capability. Instead, the<br/>Command Capabilities register is used to indicate support for the<br/>Request Interrupt Handle revocation.</li> <li>Clarified use of the Request Interrupt Handle command and<br/>described interrupt handle revocation.</li> <li>Changed description of Abort All command to require that no<br/>descriptors be submitted to the device while it is being processed.</li> <li>Changed Command register to write-only.</li> <li>Clarified intended use of unlimited portals for SWQs.</li> <li>Clarified behavior of IMS portals when IMS is not available.</li> <li>Clarified behavior of Ignore field in MSI-X Permissions and IMS.</li> </ul> |

## Glossary

| Acronym   | Term                             | Description                                                                                                                                                                           |

|-----------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATS       | Address Translation<br>Services  | A protocol defined by the PCI Express* specification to support address translations by a device and to issue ATC invalidations.                                                      |

| ATC       | Address Translation<br>Cache     | A structure in the device that stores translated addresses.<br>Also known as Device TLB.                                                                                              |

| BD        | Batch descriptor                 | A descriptor that refers to an array of descriptors in memory, to allow submitting multiple work descriptors at once.                                                                 |

|           | Completion Record                | A 32-byte data structure in memory that is written by the device when an operation completes.                                                                                         |

|           | Dedicated Mode                   | A mode that allows a single software client to submit work without unnecessary overhead.                                                                                              |

|           | Descriptor                       | A 64-byte data structure written to the device to specify work to be performed.                                                                                                       |

| DWQ       | Dedicated Work Queue             | A work queue used by a single software client to submit work.                                                                                                                         |

| DMWr      | Deferrable Memory<br>Write       | A type of PCI Express transaction that allows the device to defer (temporarily refuse) the write request.                                                                             |

|           | Engine                           | An independent operational unit within the Intel DSA device.                                                                                                                          |

| ENQCMD    | Enqueue Command                  | An Intel <sup>®</sup> 64 CPU instruction to enqueue a command to a shared work queue using Deferred Memory Write (DMWr).                                                              |

| ENQCMDS   | Enqueue Command<br>Supervisor    | An Intel <sup>®</sup> 64 CPU instruction to enqueue a command with<br>Supervisor permissions (from privileged software) to a<br>shared work queue using Deferred Memory Write (DMWr). |

| IMS       | Interrupt Message<br>Storage     | A Scalable I/O Virtualization feature used to store MSI messages in a device-specific manner.                                                                                         |

| IOMMU     | I/O Memory<br>Management Unit    | DMA Remapping Hardware Unit as defined by Intel <sup>®</sup><br>Virtualization Technology for Directed I/O.                                                                           |

|           | Group                            | A configurable set of work queues and engines.                                                                                                                                        |

| MMIO      | Memory-mapped I/O                |                                                                                                                                                                                       |

| MOVDIR64B | Move 64-Bytes as Direct<br>Store | An Intel <sup>®</sup> 64 CPU instruction used to enqueue a command to a dedicated work queue using a 64-byte memory write.                                                            |

| MSI       | Message Signaled<br>Interrupt    | A memory write operation to a pre-defined address to generate an interrupt.                                                                                                           |

| Acronym | Term                                 | Description                                                                                                                                                                                                                                                                                                                  |

|---------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSI-X   |                                      | A PCI Express feature used to configure Message Signaled<br>Interrupts.                                                                                                                                                                                                                                                      |

| PASID   | Process Address Space<br>Identifier  | A value used in memory transactions to convey the address<br>space on the host of an address used by the device.                                                                                                                                                                                                             |

| PM      | Persistent Memory                    | Memory that retains state when power is removed, such as battery-backed DRAM or Intel® Optane™ DC persistent memory.                                                                                                                                                                                                         |

| PRS     | Page Request Service                 | A protocol defined by the PCI Express specification for a device to report recoverable page-faults and receive page-fault responses.                                                                                                                                                                                         |

| RSVD    | Reserved                             | Any field that is described as reserved in this specification<br>must be written as 0 by software. Generally, hardware<br>reports an error if a reserved field is non-zero, but it may not<br>do so in all cases. If software sets a reserved field to a non-<br>zero value and no error is reported, behavior is undefined. |

| SoC     | System-on-chip                       | An integrated chip composed of host processors, accelerators, memory, and I/O agents.                                                                                                                                                                                                                                        |

| SR-IOV  | Single Root I/O<br>Virtualization    | A PCI Express standard for virtualizing PCI Express endpoint device interfaces.                                                                                                                                                                                                                                              |

| SVM     | Shared Virtual Memory                | Ability for an accelerator I/O device to operate in the same<br>virtual memory space of applications on host processors. It<br>also implies ability to operate from page-able memory,<br>avoiding functional requirements to pin memory for DMA<br>operations.                                                               |

|         | Shared Mode                          | A mode that allows multiple software clients to concurrently submit work.                                                                                                                                                                                                                                                    |

| SWQ     | Shared Work Queue                    | A work queue that allows multiple software clients to concurrently submit work.                                                                                                                                                                                                                                              |

| ТС      | Traffic Class                        | A PCI Express feature that allows differentiation of transactions to apply appropriate servicing policies.                                                                                                                                                                                                                   |

| VDCM    | Virtual Device<br>Composition Module | A software component that is part of a VMM, which composes a virtual device and makes it available to a VM.                                                                                                                                                                                                                  |

| VDEV    | Virtual Device                       | A virtual device implemented by VDCM.                                                                                                                                                                                                                                                                                        |

| WD      | Work Descriptor                      | A descriptor that specifies a DMA operation.                                                                                                                                                                                                                                                                                 |

| WQ      | Work Queue                           | A queue in the device used to store descriptors submitted by software until they can be dispatched.                                                                                                                                                                                                                          |

## 1 Introduction

This document describes the architecture of the Intel<sup>®</sup> Data Streaming Accelerator (Intel<sup>®</sup> DSA). Intel DSA is a high-performance data copy and transformation accelerator that will be integrated in future Intel<sup>®</sup> processors, targeted for optimizing streaming data movement and transformation operations common with applications for high-performance storage, networking, persistent memory, and various data processing applications.

Intel DSA replaces Intel<sup>®</sup> QuickData Technology, which is a part of Intel<sup>®</sup> I/O Acceleration Technology.

#### 1.1 Audience

The intended audience for this specification is hardware engineers and SoC architects building compliant hardware implementations, device driver software developers programming the device, virtualization software providers efficiently enabling sharing and virtualization of the device, and application or library developers utilizing Intel DSA operations.

#### 1.2 References

| Description                                                                                        |

|----------------------------------------------------------------------------------------------------|

| Intel® 64 and IA-32 Architectures Software Developer's Manuals                                     |

| https://software.intel.com/content/www/us/en/develop/articles/intel-sdm.html                       |

| Intel® Architecture Instruction Set Extensions Programming Reference                               |

| https://software.intel.com/content/www/us/en/develop/download/intel-architecture-instruction-set-  |

| extensions-programming-reference.html                                                              |

| PCI Express* Base Specification 4.0                                                                |

| http://www.pcisig.com/specifications/pciexpress                                                    |

| Intel® Virtualization Technology for Directed I/O Specification                                    |

| https://software.intel.com/content/www/us/en/develop/download/intel-virtualization-technology-for- |

| directed-io-architecture-specification.html                                                        |

| Intel® Scalable I/O Virtualization Technical Specification                                         |

| https://software.intel.com/content/www/us/en/develop/download/intel-scalable-io-virtualization-    |

| technical-specification.html                                                                       |

| Intel® I/O Acceleration Technology                                                                 |

| https://www.intel.com/content/www/us/en/wireless-network/accel-technology.html                     |

| RFC 3720, Internet Small Computer Systems Interface                                                |

| http://www.ietf.org/rfc/rfc3720.txt                                                                |

Table 1-1: References

§

## 2 Overview

The goal of Intel DSA is to provide higher overall system performance for data mover and transformation operations, while freeing up CPU cycles for higher level functions. Intel DSA hardware supports high-performance data mover capability to/from volatile memory, persistent memory, memory-mapped I/O, and through a Non-Transparent Bridge (NTB) in the SoC to/from remote volatile and persistent memory on another node in a cluster. It provides a PCI Express\* compatible programming interface to the Operating System and can be controlled through a device driver.

In addition to performing basic data mover operations, Intel DSA is designed to perform some number of higher-level transformation operations on memory. For example, it can generate and test CRC checksum or Data Integrity Field (DIF) on the memory region to support usages typical with storage and networking applications. It supports a memory compare operation for equality, generates a delta record, and applies a delta record to a buffer. These are compared and the delta generate/merge functions may be utilized by applications such as VM migration, VM fast check-pointing, and software managed memory deduplication usages.

#### 2.1 High Level Usages

This section summarizes some of the envisioned data movement and transformation usages for Intel DSA.

- **Datacenter**: As a data movement offload engine to reduce datacenter tax for memory copying, zeroing, etc., to free up CPU cycles from mundane infrastructure work.

- **Storage**: For data movement in storage appliances, both within the node and across nodes using Non-Transparent Bridge (NTB); and for CRC generation and Data Integrity Field (DIF) generation, with or without simultaneously moving data.

- **Networking**: For data copy in packet processing pipelines. An example usage is virtual switch offload for inter-VM packet switching.

- Deduplication: For comparing memory pages for equality to support memory deduplication.

- VM Migration and Fast Checkpointing: VM fast checkpointing and VM migration flows require the VMM to identify a VM's modified pages and send them efficiently to the destination machine, with minimal network traffic and latency. Intel DSA delta operations generate diffs of pages, enabling the VMM to send only the modified data to the destination, reducing network traffic.

### 2.2 Intel<sup>®</sup> DSA Features

Intel DSA features include 1) infrastructure features, which are basic features to help with programmability, performance, and efficiency; 2) data operations, which are the actual data DMA and other transformation operations; and 3) control operations. The following sections give an overview of these features.

#### 2.2.1 Infrastructure Features

The following infrastructure features are supported by Intel DSA.

- Shared Virtual Memory (SVM): SVM allows user level applications to submit commands to the device directly, with virtual addresses in the descriptors. It supports translating virtual addresses to physical addresses using IOMMU including handling page faults. The virtual address ranges referenced by a descriptor may span multiple pages. Intel DSA also supports the use of physical addresses, as long as each data buffer specified in the descriptor is contiguous in physical memory.

- Partial descriptor completion: With SVM, an operation may encounter a page fault during address translation. Software can control whether the device is to continue processing after waiting for resolution of a page fault or terminate processing of a descriptor that encounters a page fault and proceed to the next descriptor. If processing of a descriptor is terminated, the completion record indicates to software the amount of work completed and information about the page fault so that software can resolve the fault and restart the operation from the point where it stopped.

- Block on fault: As an alternative to partial descriptor completion, when the device encounters a page fault it can coordinate with system software to resolve the fault and continue the operation transparently to the software that submitted the descriptor.

- Batch processing: A Batch descriptor points to an array of work descriptors (i.e., descriptors with actual data operations). When processing a batch descriptor, the device fetches the work descriptors from the specified virtual memory address and processes them.

- Stateless device: Descriptors are designed so that all information required for processing the descriptor comes in the descriptor itself. This allows the device to store little client specific state which improves its scalability. The only exception is the completion interrupt message, when used, because it must be configured by trusted software.

- Cache allocation control: This allows applications to specify whether output data is allocated in the cache or is sent to memory without cache allocation. Completion records are always allocated in the cache.

- Shared Work Queue (SWQ) support: Shared Work Queues (SWQ) enable scalable work submission using Deferrable Memory Write transactions, which indicate whether the work was accepted into the WQ.

- **Dedicated Work Queue (DWQ) support:** Dedicated Work Queues (DWQ) enable high-throughput work submission using 64-byte Memory Write transactions.

- **QoS support:** Intel DSA supports several features that allow the kernel driver to separately control access to device resources by different guests and applications.

- Intel<sup>®</sup> Scalable IOV support: Intel Scalable IO Virtualization improves scalability of device assignment, allowing a VMM to share the device across many more VMs than would be possible using SR-IOV.

- Persistent Memory features: Configuration registers and descriptor flags allow software to indicate writes to durable memory (such as Intel® Optane™ DC persistent memory) and specify the durability and ordering semantics to the SoC.

#### 2.2.2 Data Operations

| Operation | Туре                   | Description                                                                                                                                                                                                  |

|-----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Move      | Memory<br>Move         | Transfer data from a source address to destination address. Source and destination ranges can be either in main memory or MMIO.                                                                              |

|           | CRC<br>Generation      | Generate CRC checksum on the transferred data.                                                                                                                                                               |

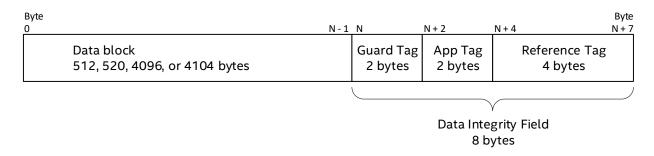

|           | DIF                    | Data Integrity Field (DIF) check.<br>DIF insert, strip, or update while transferring data.                                                                                                                   |

|           | Dualcast               | Copy data simultaneously to two destination locations.                                                                                                                                                       |

| Fill      | Memory Fill            | Fill memory range with a fixed pattern.                                                                                                                                                                      |

| Compare   | Memory<br>Compare      | Compare two source buffers and return whether the buffers are identical.                                                                                                                                     |

|           | Delta Record<br>Create | Create a delta record containing the differences between the original and modified buffers. The size of the delta record is bounded, and the device signals an overflow if the differences exceed the bound. |

|           | Delta Record<br>Merge  | Merge a delta record with the original source buffer to produce a copy of the modified buffer at the destination location.                                                                                   |

|           | Pattern/Zero<br>Detect | Special case of compare where instead of the second input buffer, an 8-<br>byte pattern is specified. Pattern may be zero.                                                                                   |

| Flush     | Cache Flush            | Evict all lines in a given address range from all levels of CPU caches.                                                                                                                                      |

The following data operations are supported by Intel DSA. See chapter 8 for details on these operations.

Table 2-1: Intel® DSA Data Operations

#### 2.2.3 Control Operations

The following control operations are supported by Intel DSA. Some of these commands are issued using descriptors and some are issued using the Command register. See sections 9.2.12 and 8.3 for details.

| Operation             | Туре             | Description                                                       |

|-----------------------|------------------|-------------------------------------------------------------------|

| Enable /<br>Disable / | Device           | Manage the device as a whole.                                     |

| Reset                 | WQ               | Manage individual WQs.                                            |

| Drain                 | Current client   | Drain all in-flight work requests from the current client.        |

| Drain /               | Specified client | Drain or abort in-flight work requests from the specified client. |

| Abort                 | Work Queue       | Drain or abort in-flight work requests in specified work queue.   |

|                       | All              | Drain all in-flight work requests in the device.                  |

| No-op                 | Null operation   | Performs no operation but can signal completion.                  |

#### Table 2-2: Intel® DSA Control Operations

§

## 3 Intel<sup>®</sup> Data Streaming Accelerator Architecture

This chapter describes the Intel DSA architecture in detail. Each SoC may support any number of Intel DSA device instances. A multi-socket server platform may support multiple such SoCs. From a software perspective, each instance is exposed as a single Root Complex Integrated Endpoint. Each instance is under the scope of a DMA Remapping hardware unit (also called an IOMMU). Each Intel DSA instance is behind a single DMA Remapping hardware unit, but depending on the SoC design, different device instances can be behind the same or different DMA Remapping hardware units.

Intel DSA supports an Address Translation Cache (ATC) and interacts with DMA Remapping hardware using the PCI-SIG-defined Address Translation Services (ATS), Process Address Space ID (PASID), and Page Request Services (PRS) capabilities. The PASID TLP prefix is added to upstream requests to support both Shared Virtual Memory (SVM) and Intel Scalable I/O Virtualization (Intel Scalable IOV). The device utilizes the DMA Remapping hardware to translate DMA addresses to host physical addresses. Depending on the usage, a DMA address can be a Host Virtual Address (HVA), Guest Virtual Address (GVA), Guest Physical Address (GPA), or I/O Virtual Address (IOVA). Intel DSA supports additional PCI Express capabilities, including Advanced Error Reporting (AER) and MSI-X.

The Intel DSA architecture is designed to support Intel Scalable I/O Virtualization. The device can be shared directly with multiple VMs in a secure and isolated manner to achieve high throughput. Sections 3.13 and 7.3 describe the virtualization features in more detail.

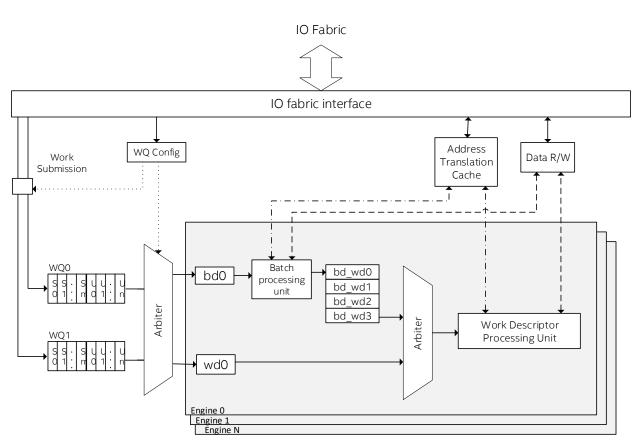

Figure 3-1 illustrates the high-level blocks within the Intel DSA device at a conceptual level. Downstream work requests from clients are received on the I/O fabric interface. Upstream read, write, and address translation operations are sent on that interface. The device includes configuration registers, Work Queues (WQ) to hold descriptors submitted by software, arbiters used to implement QoS and fairness policies, processing engines, an address translation and caching interface, and a memory read/write interface. The batch processing unit processes Batch descriptors by reading the array of descriptors from memory. The work descriptor processing unit has stages to read memory, perform the requested operation on the data, generate output data, and write output data, completion records, and interrupt messages.

The WQ configuration allows software to configure each WQ either as a Shared Work Queue (SWQ) that can be shared by multiple software components, or as a Dedicated Work Queue (DWQ) that is assigned to a single software component at a time. The configuration also allows software to control which WQs feed into which engines and the relative priorities of the WQs feeding each engine.

### 3.1 Register and Software Programming Interface

Intel DSA is software compatible with the standard PCI Express configuration mechanism and implements a PCI header and extended space in its configuration-mapped register set.

Memory-mapped I/O registers provide status and control of device operation. Capability, configuration, and work submission registers (portals) are accessible through the MMIO regions defined by the BARO and BAR2 registers described in section 9.1.1. Each portal is on a separate 4K page so that they may be independently mapped into different address spaces (clients) using CPU page tables.

Figure 3-1: Abstracted Internal Block Diagram of Intel® DSA

#### 3.2 Descriptors

Software specifies work for the device using descriptors. Descriptors specify the type of operation for the device to perform, addresses of data and status buffers, immediate operands, completion attributes, etc. See chapter 8 for descriptor formats and details. The completion attributes specify the address to write the completion record, and optionally, the information needed to generate a completion interrupt.

Intel DSA avoids maintaining client specific state on the device. All information to process a descriptor comes in the descriptor itself. This improves shareability of the device among user-mode applications, as well as among different virtual machines or machine containers in a virtualized system.

A descriptor may contain an operation and associated parameters (called a Work descriptor), or it can contain the address of an array of work descriptors (called a Batch descriptor). Software prepares the descriptor in memory and submits the descriptor to a Work Queue (WQ) of the device. The device dispatches descriptors from the work queues to the engines for processing. When an engine completes a descriptor or encounters certain faults or errors that result in an abort, it notifies the host software by either writing to a completion record in host memory, issuing an interrupt, or both.

### 3.3 Work Queues

Work queues (WQs) are on-device storage to contain descriptors that have been submitted to the device. The WQ Capability register indicates the number of work queues and the amount of work queue storage

available on the device. Software configures how many work queues are enabled and divides the available WQ space among the active WQs.

The WQ Configuration Table is used to configure the WQs. Prior to enabling the device, software configures the size of each WQ. Unused WQs have a size of 0. Other parameters of each WQ can be configured later, prior to enabling the WQ. In some configurations, the WQ size and other aspects of the WQ configuration are read-only. See section 9.2.19 for more details on configuring WQs.

Each work queue can be configured to run in one of two modes, Dedicated or Shared. The WQ Capability register indicates support for Dedicated and Shared modes. Controls in the WQ Configuration Table allow software to configure the mode of each WQ. The mode of a WQ can only be changed while the WQ is Disabled. See the specifications for the WQ Capability register, the WQ Configuration Table, and the Command register in section 9.2.19 for details on configuring and enabling Work Queues.

Descriptors are submitted to work queues via special registers called portals. Each portal is in a separate 4 KB page in device MMIO space. There are four portals per WQ:

- Unlimited MSI-X Portal

- Unlimited IMS Portal

- Limited MSI-X Portal

- Limited IMS Portal

The address of the portal used to submit a descriptor allows the device to determine which WQ to place the descriptor in, whether the portal is limited or unlimited, and which interrupt table to use for the completion interrupt.

See section 3.3.1, "Shared Work Queue", for the usage of limited and unlimited portals. For Dedicated WQs there is no difference between the limited and unlimited portals.

See section 3.7, "Interrupts", for the usage of MSI-X and IMS portals. For a descriptor that does not request an interrupt, it doesn't matter whether it is submitted to an MSI-X portal or an IMS portal. The IMS portals do not exist if IMS is not supported, so a descriptor written to an address that would normally correspond to an IMS portal is discarded without reporting an error. If the descriptor was submitted with a non-posted write, a Retry response is returned.

#### 3.3.1 Shared Work Queue (SWQ)

A Shared Work Queue accepts work submission using the PCIe\*-defined Deferrable Memory Write Request (DMWr). DMWr is a 64-byte non-posted write that waits for a response from the device before completing. The device returns Success if the descriptor is accepted into the work queue, or Retry if the descriptor is not accepted due to WQ capacity or QoS. This allows multiple clients to directly and simultaneously submit descriptors to the same work queue. Since the device provides this feedback, the clients can tell whether their descriptors were accepted. On Intel CPUs, DMWr is generated using the ENQCMD or ENQCMDS instructions. The ENQCMD and ENQCMDS instructions return the status of the command submission in EFLAGS.ZF flag; 0 indicates Success, and 1 indicates Retry.

A Shared WQ can be configured to reserve some of the WQ capacity by setting the WQ Threshold field in the WQCFG register. Work submission via a limited portal is accepted until the number of descriptors in the SWQ reaches the configured threshold. Work submission via an unlimited portal is accepted unless the SWQ is completely full. The unlimited portals are intended to be used only by privileged software when a work submission to the corresponding limited portal returns Retry. User-mode and guest software typically only have access to limited portals.

If DMWr returns Success, the descriptor has been accepted by the device and queued for processing. If DMWr returns Retry, software can try re-submitting the descriptor to the SWQ, or if it was a user-mode client using a limited portal, it can request that the kernel-mode driver submit the descriptor on its behalf using an unlimited portal. This helps avoid denial of service and provide forward progress guarantees. See chapter 7 for more information on software use of the limited and unlimited portals.

Clients are identified by the device using a 20-bit ID called process address space ID (PASID). The PASID capability must be enabled to use SWQs. The PASID is used by the device to look up addresses in the Address Translation Cache and to send address translation or page requests to the IOMMU. In Shared mode, the PASID to be used with each descriptor is contained in the PASID field of every descriptor. The ENQCMD instruction copies the PASID of the current thread from the IA32\_PASID MSR into the descriptor while ENQCMDS allows supervisor mode software to copy the PASID into the descriptor. For additional details on the use of PASID and the ENQCMD and ENQCMDS instructions, refer to the Intel® Architecture Instruction Set Extensions Programming Reference, listed in the References in section 1.2.

#### 3.3.2 Dedicated Work Queue (DWQ)

To submit work to a Dedicated Work Queue, software uses a 64-byte memory write transaction with write atomicity. This transaction may complete faster than DMWr due to the posted nature of the write operation. The device depends on software to provide flow control based on the number of slots in the work queue. Software is responsible for tracking the number of descriptors submitted and completed, to detect a work queue full condition. If software erroneously submits a descriptor to a dedicated WQ when there is no space in the work queue, the descriptor is dropped. (The error is reported in the Software Error Register.)

On Intel CPUs, work submission to a DWQ is performed using the MOVDIR64B instruction, which generates a non-torn 64-byte write. For information about the MOVDIR64B instruction, refer to the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manuals, listed in the References in section 1.2.

With dedicated WQs, the use of PASID is optional. If the PCI Express PASID capability is not enabled, PASID is not used. If the PASID capability is enabled, the WQ PASID Enable field of the WQ Configuration register controls whether PASID is used for each DWQ. Since the MOVDIR64B instruction does not fill in the PASID as the ENQCMD or ENQCMDS instructions do, the PASID field in the descriptor is ignored. When PASID is enabled for a DWQ, the device uses the WQ PASID field of the WQ Configuration register to do address translation. The WQ PASID field must be set by the driver before enabling a work queue in dedicated mode.

Although dedicated mode doesn't support the sharing of a single DWQ by multiple clients, Intel DSA can be configured to have multiple DWQs and each of the DWQs can be independently assigned to clients. DWQs can be configured to have the same or different QoS levels.

#### 3.4 Engines and Groups

An engine is an operational unit within an Intel DSA device. A group is a set of work queues and engines. Software configures WQs and engines into groups using the Group Configuration registers. Each group contains one or more WQs and one or more engines. Any engine in a group may be used to process a descriptor posted to any WQ in the group. Each WQ and each engine may be in only one group.

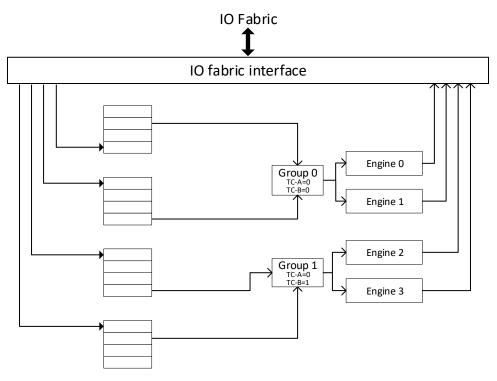

Although the Intel DSA architecture allows great flexibility in configuring work queues, groups, and engines, the hardware is designed with the intent to be used in specific configurations. Example configurations are shown in Figures 3-2 and 3-3. In the configuration shown in Figure 3-2, hardware uses either engine in a

group to process descriptors from any work queue in the group. If one engine has a stall due to a highlatency memory address translation or page fault, the other engine can continue to operate and maximize the throughput of the overall device.

Figure 3-2 shows example Traffic Class (TC) values for the two groups. In Group 0 both TC values are 0, while in Group 1, TC-B is 1. This example configuration might be used when Group 0 is used solely for operations that access DRAM, and Group 1 is used for operations that access both DRAM and persistent memory. The TC Selector flags in descriptors submitted to Group 1 indicate whether each address in the descriptor refers to DRAM or persistent memory. See chapter 4 for information on Traffic Classes and how they can be used to control QoS.

Figure 3-2 shows two work queues in each group, but there may be any number up to the maximum number of WQs supported. The WQs in a group may be shared WQs with different priorities, or one shared WQ and the others dedicated WQs, or multiple dedicated WQs with the same or different priorities.

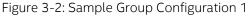

Figure 3-3 shows another example configuration, in which each engine is placed in a separate group. Software may choose this configuration when it wants to reduce the likelihood that latency-sensitive operations become blocked behind other operations. In this configuration, software submits latency-sensitive operations to the work queue connected to one engine, and other operations to the work queues connected to another engine. If the group used for latency sensitive operations is idle when a descriptor is submitted, the descriptor will be dispatched to an engine immediately.

Software can also mix these two, with some engines in a single group and the others in groups by themselves.

Figure 3-3: Sample Group Configuration 2

#### 3.5 Descriptor Processing

As each descriptor reaches the head of the work queue, it is available to be dispatched by the group arbiter to an available engine in the group. The arbiter for each group dispatches descriptors from the WQs in the group according to their priority, while ensuring that the higher priority WQs don't starve lower priority WQs. See section 4.1 for information about work dispatch priority.

For a Batch descriptor, which refers to work descriptors in memory, the engine fetches the array of work descriptors from memory. Each work descriptor is passed to the work descriptor processing unit. The work descriptor processing unit uses the Address Translation Cache and IOMMU for completion record, source, and destination address translations; reads source data; performs the specified operation; and writes the destination data back to memory. When the operation is complete, the engine writes the completion record to the pre-translated completion address and generates an interrupt, if requested by the work descriptor.

### 3.6 Descriptor Completion

Descriptors contain three flags and two other fields that allow software to control completion notifications. The three flags are: Completion Record Address Valid, Request Completion Record, and Request Completion Interrupt. The two fields are Completion Record Address and Completion Interrupt Handle.

The completion record is a 32-byte aligned structure in memory that the device writes when the operation is complete or encounters an error. The completion record contains completion status. If the operation completed successfully, the completion record may contain the result of the operation, if any, depending

on the type of operation. If the operation did not complete successfully, the completion record contains fault or error information.

Generally, all descriptors should have a valid Completion Record Address and the Completion Record Address Valid flag should be 1. (Exceptions to this rule are described later.)

The first byte of the completion record is the status byte. Status values written by the device are all nonzero. Software should initialize the status field of the completion record to 0 before submitting the descriptor to be able to tell when the device has written to the completion record. (Initializing the completion record also ensures that it is mapped, so the device is less likely to encounter a page fault when accessing it.)

The Request Completion Record flag indicates to the device that it should write the completion record even if the operation completed successfully. If this flag is not set, the device writes the completion record only if there is an error.

Descriptor completion can be detected by software using any of the following methods:

- 1. Poll the completion record, waiting for the status field to become non-zero.

- 2. Use the UMONITOR/UMWAIT instructions on the completion record address to block until it is written or until timeout. Software should then check whether the status field is non-zero to determine whether the operation has completed.

- 3. Request an interrupt when the operation is completed. For user-mode descriptors, this method requires the kernel to forward the notification to the application.

- 4. If the descriptor is in a batch, set the Fence flag in a subsequent descriptor in the same batch. Completion of the descriptor with the Fence or any subsequent descriptor in the same batch indicates completion of all descriptors that precede the Fence.

- 5. If the descriptor is in a batch, completion of the Batch descriptor that initiated the batch indicates completion of all descriptors in the batch.

- 6. Issue a Drain descriptor or a Drain command and wait for it to complete.

If the completion status indicates a partial completion due to a page fault, the completion record indicates how much processing was completed (if any) before the fault was encountered, and the virtual address where the fault was encountered. Software may choose to fix the fault (by touching the faulting address from the CPU) and resubmit the rest of the work in a new descriptor or complete the rest of the work in software. Faults on descriptor list and completion record addresses are handled differently and are described in more detail in section 3.11.

#### 3.7 Interrupts

Intel DSA supports only message signaled interrupts. It provides two types of interrupt message storage: (1) an MSI-X table, enumerated through the MSI-X capability, which stores interrupt messages used by the host driver; and (2) a device-specific Interrupt Message Storage (IMS) table, as described by the Intel Scalable IOV architecture specification, which stores interrupt messages used by guest drivers. For more information on IMS, refer to section 9.2.23, and to the Intel<sup>®</sup> Scalable I/O Virtualization Technical Specification, listed in the References in section 1.2.

Interrupts can be generated for five types of events: 1) completion of a descriptor; 2) WQ occupancy below programmed limit; 3) completion of an administrative command; 4) an error posted in the Software Error Register; and 5) performance monitoring counter overflow. For each type of event there is a separate

interrupt enable. Interrupts of types 3, 4 and 5 are generated using entry 0 in the MSI-X table. The Interrupt Cause Register may be read by software to determine the reason for the interrupt.

For completion of a descriptor that requests a completion interrupt, the interrupt message used is dependent on the portal the descriptor was submitted to and the Completion Interrupt Handle in the descriptor. As described in section 3.3, each WQ has both MSI-X portals and IMS portals. For a descriptor submitted via an MSI-X portal, the Completion Interrupt Handle field in the descriptor selects an entry in the MSI-X table. For a descriptor submitted via an IMS portal, the Completion Interrupt Handle field in the descriptor selects an entry in the Interrupt Message Storage. Descriptors in a batch are treated as if they had been submitted via the same portal as the Batch descriptor.

When the Request Interrupt Handle command is not supported (as indicated by the Command Capabilities register), the Completion Interrupt Handle is the index of the desired entry in the MSI-X table or the IMS. When the Request Interrupt Handle command is supported, software must use the command to obtain a handle to use for the interrupt. Software specifies in the Request Interrupt Handle command which interrupt table entry it wants a handle for. The response to the command contains the handle that software should place in the Completion Interrupt Handle field of the descriptor to request that interrupt.

An interrupt handle obtained using the Request Interrupt Handle command may be revoked. After an interrupt handle is revoked, any use of the handle will result in an Invalid Interrupt Handle error. If an Invalid Interrupt Handle error occurs, software should use the Request Interrupt Handle command again to obtain a new handle for the same interrupt table entry. It should then use the Release Interrupt Handle command to release the revoked handle. See section 7.3.4 for a description of interrupt virtualization.

The MSI-X table defined by the PCIe specification is augmented in Intel DSA by the MSI-X Permissions Table, detailed in section 9.2.17. Each MSI-X Permissions Table entry has several fields that control generation of interrupts using that table entry. Each IMS entry contains the same control fields. The PASID Enable and PASID fields of the selected interrupt table entry are checked before the descriptor is executed, as detailed in section 5.4. The Ignore and Mask fields are checked when the descriptor completes. If the Ignore field is 1, no interrupt is generated. If the Ignore field is 0, the Mask and Pending fields behave as specified by PCIe. If the Mask field is 1, the Pending field is set to 1 and no interrupt is generated. If Ignore and Mask are both 0, the interrupt is generated. For interrupts other than descriptor completions, the PASID Enable, PASID, and Ignore fields are not used.

| Event                                   | Submission register | Interrupt message used                                                                        |

|-----------------------------------------|---------------------|-----------------------------------------------------------------------------------------------|

| Error posted in SWERROR register        | N/A                 | MSI-X table entry 0.                                                                          |

| Completion of an administrative command | Command register    | MSI-X table entry 0.                                                                          |

| Perfmon counter<br>overflow             | N/A                 | MSI-X table entry 0.                                                                          |

| WQ Occupancy below                      | WQ Occupancy        | MSI-X or IMS entry programmed in WQ Occupancy                                                 |

| limit                                   | Interrupt register  | Interrupt register.                                                                           |

| Descriptor completion                   | MSI-X portal        | MSI-X table entry specified by Completion Interrupt Handle field in descriptor.               |

|                                         | IMS portal          | Interrupt Message Storage entry specified by Completion Interrupt Handle field in descriptor. |

#### Table 3-1: Interrupt Delivery

Interrupts generated by Intel DSA are processed through the Interrupt Remapping and Posting hardware as configured by the kernel or VMM software.

#### 3.8 Batch Descriptor Processing

Intel DSA supports submitting multiple descriptors at once. A Batch descriptor contains the address of an array of work descriptors in host memory and the number of elements in the array. The array of work descriptors is called the "batch". Use of Batch descriptors allows software to submit multiple work descriptors using a single work submission instruction and can potentially improve overall throughput, especially when using descriptors with small transfer sizes.

Intel DSA enforces a limit on the number of work descriptors in a batch. There is an overall limit, indicated by the Maximum Supported Batch Size field in the General Capabilities register, and also a separate limit for each work queue, set by the WQ Maximum Batch Size field for each WQ in the WQ Configuration Table. A batch must contain at least 2 work descriptors.

Batch descriptors are submitted to work queues in the same way as other work descriptors. When a Batch descriptor is processed by the device, the device reads the array of work descriptors from memory and then processes each of the work descriptors. The work descriptors are not necessarily processed in order. (See section 3.9 for information on how software can control ordering of descriptors in a batch.)

The PASID and the Priv fields of the Batch descriptor are used for all descriptors in the batch.<sup>1</sup> The PASID and Priv fields in the descriptors in the batch are ignored.

Each work descriptor in the batch can specify a completion record address and/or a completion interrupt, just as with directly submitted work descriptors. The completion record and completion interrupt for the Batch descriptor (if requested) are generated after completion of all the descriptors in the batch and generation of their completion records (if requested). No readback is performed before the Batch descriptor completion record is generated. To maintain ordering of the completion record for the Batch behind all writes from descriptors in the batch, either the Batch descriptor should use the same TC for its completion record as the prior writes, or the Destination Readback flag should be set in each of the descriptors in the batch.

The completion record for the Batch descriptor contains an indication of whether any of the descriptors in the batch completed with Status not equal to Success. This allows software to avoid examining all the completion records for the descriptors in the batch, in the usual case where all the descriptors in the batch completed successfully.

A Batch descriptor may not be included in a batch. Nested or chained descriptor arrays are not supported. See section 8.3.2 for details on the format of Batch descriptors.

<sup>&</sup>lt;sup>1</sup> For a Batch descriptor submitted to a dedicated work queue, the PASID and Priv fields of the Batch descriptor and all the work descriptors in the batch come from the WQ Configuration register.

#### 3.9 Ordering and Fencing

Descriptors may generally be processed by the device in any order. However, descriptors are guaranteed to be executed in the order that they are received by the device when all of the following conditions are met:

- Descriptors are submitted to a group with only one engine.

- Descriptors are all submitted to the same WQ using the same portal address.

- Descriptors are all Batch descriptors, or they are all not Batch descriptors.

Only write ordering is guaranteed. Reads by a subsequent descriptor can pass writes from a previous descriptor. If an error occurs in a descriptor, subsequent descriptors will continue to execute. Thus, software cannot necessarily rely on data transfers from earlier descriptors completing before those from later descriptors.

Even when these conditions are met, the order of descriptors within a batch is not guaranteed unless the Fence flag is set as described below.

If more control of the ordering of descriptors is required, software may use one of the following methods:

- Submit a descriptor, wait for the completion record or interrupt from the descriptor to ensure completion, and then submit the next descriptor.

- Use a Drain descriptor or Drain command to wait for preceding descriptors to complete, and then submit the following descriptors.

- Within a batch, use the Fence flag.

Enforcing ordering may increase both the CPU time used to submit a descriptor and the latency for the descriptor to begin execution within the device.

To control ordering for descriptors in a batch specified by a Batch descriptor, each work descriptor has a Fence flag. When set, Fence guarantees that processing of that descriptor will not start until all previous descriptors in the same batch are completed. This allows a descriptor with Fence to consume data produced by a previous descriptor in same batch. A descriptor consuming data from a previous descriptor in the batch should use the same Traffic Class as the descriptor producing the data. If software cannot ensure this, then software must set the Destination Readback flag in the descriptor that produces the data to ensure the required ordering.

If any descriptor in a batch completes with Status not equal to Success, for example if it is partially completed due to a page fault, a subsequent descriptor with the Fence flag equal to 1 and any following descriptors in the batch are abandoned. The completion record for the Batch descriptor that was used to submit the batch indicates how many descriptors were completed. Any descriptors that were partially completed and generated a completion record are counted as completed. Only the abandoned descriptors are considered not completed.

The completion record write for a descriptor is ordered after all data writes produced by the descriptor if:

- the descriptor is fully completed; or

- the completion record TC selector in the descriptor is the same as the destination TC selector(s).

Otherwise, the completion record may be observed by software before some of the data writes produced by the descriptor. Software may avoid partial completion by setting the Block on Fault flag in the descriptor. A completion interrupt (if requested) is ordered after the completion record write. The Destination Readback flag causes Intel DSA to perform a zero-length read, using the final destination address of the descriptor, prior to writing the completion record. If the destination target is different from the completion record target, then the Destination Readback flag may be set to ensure that writes have propagated to the destination before the completion record is written. For example, this flag may be used in descriptors that target NTB to ensure that data written by the descriptor has propagated across the NTB link. Destination readback is performed only if the descriptor is completed successfully. If the descriptor is partially completed, the readback is not performed. If a follow-up descriptor to complete the operation writes to the same destination using the same TC, sets the Destination Readback flag, and completes successfully, then the readback performed by the follow-up descriptor also ensures completion of memory writes performed by the prior descriptor(s). Software may avoid the need for a follow-up descriptor by setting the Block on Fault flag in the initial descriptor to prevent partial completion.

#### 3.10 Drain Descriptor