# INTEL® DATA STREAMING ACCELERATOR PRELIMINARY ARCHITECTURE SPECIFICATION

Order Number: 341204-001US Revision: 1.0 November 2019 You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

This document contains information on products in the design phase of development.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No product or component can be absolutely secure. Check with your system manufacturer or retailer or learn more at <a href="http://www.intel.com">http://www.intel.com</a>.

Intel<sup>®</sup> 64 architecture requires a system with a 64-bit enabled processor, chipset, BIOS and software. Performance will vary depending on the specific hardware and software you use. Consult your PC manufacturer for more information. For more information, visit <a href="http://www.intel.com/info/em64t">http://www.intel.com/info/em64t</a>.

Intel<sup>®</sup> Virtualization Technology requires a computer system with an enabled Intel<sup>®</sup> processor, BIOS, and virtual machine monitor (VMM). Functionality, performance or other benefits will vary depending on hardware and software configurations. Software applications may not be compatible with all operating systems. Consult your PC manufacturer. For more information, visit <u>http://www.intel.com/go/virtualization</u>.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: <u>http://www.intel.com/design/literature.htm</u>.

Copyright © 2019, Intel Corporation. All Rights Reserved.

Intel, the Intel logo, Intel Data Streaming Accelerator, Intel DSA, Intel Virtualization Technology, Intel I/O Acceleration Technology, Intel IOAT, Intel Virtualization Technology for Directed I/O, Intel Scalable I/O Virtualization, and other Intel marks are trademarks of Intel Corporation or its subsidiaries.

\*Other names and brands may be claimed as the property of others.

## Table of Contents

| 1 | Introduction |                                                        |    |

|---|--------------|--------------------------------------------------------|----|

|   | 1.1<br>1.2   | Audience<br>References                                 |    |

| 2 |              | rview                                                  |    |

| 2 |              |                                                        |    |

|   | 2.1<br>2.2   | High Level Usages<br>Intel® DSA Features               |    |

|   | 2.2.1        | Intel® DSA Infrastructure Features                     | 15 |

|   | 2.2.2        | Intel® DSA Data Operations                             | 17 |

|   | 2.2.3        | Intel® DSA Control Operations                          | 17 |

| 3 | Inte         | l® Data Streaming Accelerator Architecture             | 19 |

|   | 3.1          | Intel® DSA Register and Software Programming Interface | 20 |

|   | 3.2          | Descriptors                                            | 20 |

|   | 3.3          | Work Queues                                            | 21 |

|   | 3.3.1        | Shared Work Queue (SWQ)                                | 21 |

|   | 3.3.2        | Dedicated Work Queue (DWQ)                             |    |

|   | 3.4          | Engines and Groups                                     | 23 |

|   | 3.5          | Descriptor Processing                                  |    |

|   | 3.6          | Descriptor Completion                                  |    |

|   | 3.7          | Interrupts                                             |    |

|   | 3.8          | Batch Descriptor Processing                            | 27 |

|   | 3.9          | Ordering and Fencing                                   | 28 |

|   | 3.10         | Drain Descriptor                                       | 29 |

|   | 3.11         | Address Translation                                    |    |

|   | 3.12         | Administrative Commands                                |    |

|   | 3.13         | Virtualization                                         | 32 |

| 4 | Qua          | lity of Service Control                                | 35 |

|   | 4.1          | Work Dispatch Priority                                 | 35 |

|   | 4.2          | Traffic Classes                                        |    |

|   | 4.3          | Bandwidth Control                                      |    |

|   | 4.4          | Low Bandwidth Memory                                   |    |

|   | 4.5          | Persistent Memory Support                              |    |

|   | 4.6          | Cache Control                                          |    |

| 5 | Errc         | r Handling                                             | 39 |

|   | 5.1          | Device Enable Checks                                   | 40 |

|   | 5.2          | WQ Enable Checks                                       | 40 |

|   | 5.3          | Descriptor Submission Checks                           | 41 |

|        | 5.4<br>5.5<br>5.6<br>5.7<br>5.7.1 | Descriptor Checks<br>Descriptor Reserved Field Checking<br>Device Halt State<br>Error Codes<br>Operation Status Codes | 43<br>45<br>46<br>46 |

|--------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------|

|        | 5.7.2                             | Other Software Error Codes                                                                                            |                      |

| 6<br>7 |                                   | ormance Monitoring<br>erence Software Architecture                                                                    |                      |

|        | 7.1                               | Kernel Mode Driver                                                                                                    | 51                   |

|        | 7.2                               | User Mode Driver                                                                                                      | 51                   |

|        | 7.3                               | Virtualization Software                                                                                               | 51                   |

|        | 7.3.1                             | Virtual Intel® DSA Device                                                                                             | 52                   |

|        | 7.3.2                             | SVM and PASID Virtualization                                                                                          | 53                   |

|        | 7.3.3                             | Interrupt Virtualization                                                                                              |                      |

|        | 7.3.4                             | Capability Virtualization                                                                                             |                      |

|        | 7.3.5                             | Intel <sup>®</sup> DSA State Migration During VM Migration                                                            | 55                   |

| 8      | Des                               | criptor Formats                                                                                                       | 57                   |

|        | 8.1                               | Common Descriptor Fields                                                                                              | 57                   |

|        | 8.1.1                             | Trusted Fields                                                                                                        | 57                   |

|        | 8.1.2                             | Operation                                                                                                             |                      |

|        | 8.1.3                             | Flags                                                                                                                 | 58                   |

|        | 8.1.4                             | Completion Record Address                                                                                             | 62                   |

|        | 8.1.5                             | Source Address                                                                                                        |                      |

|        | 8.1.6                             | Destination Address                                                                                                   |                      |

|        | 8.1.7                             | Transfer Size                                                                                                         |                      |

|        | 8.1.8                             | Completion Interrupt Handle                                                                                           | 63                   |

|        | 8.2                               | Completion Record                                                                                                     | 63                   |

|        | 8.2.1                             | Status                                                                                                                |                      |

|        | 8.2.2                             | Result                                                                                                                |                      |

|        | 8.2.3                             | Bytes Completed                                                                                                       |                      |

|        | 8.2.4                             | Fault Address                                                                                                         |                      |

|        | 8.2.5                             | Invalid Flags                                                                                                         | 65                   |

|        | 8.3                               | Descriptor types                                                                                                      | 65                   |

|        | 8.3.1                             | No-op                                                                                                                 | 65                   |

|        | 8.3.2                             | Batch                                                                                                                 |                      |

|        | 8.3.3                             | Drain                                                                                                                 |                      |

|        | 8.3.4                             | Memory Move                                                                                                           |                      |

|        | 8.3.5                             | Fill                                                                                                                  | 70                   |

|   | 8.3.6      | Compare                                  | 71   |

|---|------------|------------------------------------------|------|

|   | 8.3.7      | Compare Pattern                          | 72   |

|   | 8.3.8      | Create Delta Record                      | 73   |

|   | 8.3.9      | Apply Delta Record                       | 74   |

|   | 8.3.10     | Memory Copy with Dualcast                | 75   |

|   | 8.3.11     | CRC Generation                           | 76   |

|   | 8.3.12     | Copy with CRC Generation                 | 78   |

|   | 8.3.13     | DIF Check                                | 79   |

|   | 8.3.14     | DIF Insert                               | 80   |

|   | 8.3.15     | DIF Strip                                | 81   |

|   | 8.3.16     | DIF Update                               | 82   |

|   | 8.3.17     | Cache Flush                              | 86   |

| 9 | Register D | Descriptions                             | 87   |

|   | 9.1 PCI C  | onfiguration Space Registers             | 88   |

|   | 9.1.1      | Base Address Registers (BAR)             |      |

|   | 9.1.2      | MSI-X Capability                         |      |

|   | 9.1.3      | Address Translation Capabilities         |      |

|   | 9.1.4      | Scalable I/O Virtualization Capability   |      |

|   | 9.1.5      | TPH Capability                           |      |

|   | 9.1.6      | VC Capability                            |      |

|   | 9.2 Conf   | iguration and Control Registers (BARO)   | 91   |

|   | 9.2.1      | Version Register (VERSION)               | 94   |

|   | 9.2.2      | General Capabilities Register (GENCAP)   |      |

|   | 9.2.3      | WQ Capabilities Register (WQCAP)         | 97   |

|   | 9.2.4      | Group Capabilities Register (GRPCAP)     | 98   |

|   | 9.2.5      | Engine Capabilities Register (ENGCAP)    | 99   |

|   | 9.2.6      | Operations Capabilities Register (OPCAP) | .100 |

|   | 9.2.7      | Table Offsets Register (OFFSETS)         | .101 |

|   | 9.2.8      | General Configuration Register (GENCFG)  | .102 |

|   | 9.2.9      | General Control Register (GENCTRL)       | .103 |

|   | 9.2.10     | General Status Register (GENSTS)         | .104 |

|   | 9.2.11     | Interrupt Cause Register (INTCAUSE)      | .105 |

|   | 9.2.12     | Command Register (CMD)                   | .106 |

|   | 9.2.13     | Command Status Register (CMDSTATUS)      | .108 |

|   | 9.2.14     | Software Error Register (SWERROR)        | .110 |

|   | 9.2.15     | MSI-X Permissions Table (MSIXPERM)       | .112 |

|   | 9.2.16     | Group Configuration Table (GRPCFG)       | .113 |

|   | 9.2.17     | WQ Configuration Table (WQCFG)           | .115 |

|   | 9.2.18     | Performance Monitoring Registers         | .121 |

|   | 9.2.19     | MSI-X Table                              | .122 |

| 9.2.20 | MSI-X Pending Bit Array12   | 2 |

|--------|-----------------------------|---|

| 9.2.21 | Interrupt Message Storage12 | 3 |

| 9.3    | Portals (BAR2)12            | 4 |

## List of Figures

| Figure 3-1: Abstracted Internal Block Diagram of Intel® DSA | 20 |

|-------------------------------------------------------------|----|

| Figure 3-2: Sample Group Configuration 1                    |    |

| Figure 3-3: Sample Group Configuration 2                    |    |

| Figure 7-1: Scalable IOV for Intel® DSA                     |    |

| Figure 9-1: MMIO Register Map                               |    |

| Figure 9-2: Portals                                         |    |

## List of tables

| Table 1-1: References                                         | 13  |

|---------------------------------------------------------------|-----|

| Table 2-1: Intel® DSA Data Operations                         | 17  |

| Table 2-2: Intel® DSA Control Operations                      | 17  |

| Table 3-1: Interrupt Delivery                                 | 26  |

| Table 5-1: Handling of Software Errors                        |     |

| Table 5-2: Completion Interrupt Handle Checks                 | 42  |

| Table 5-3: Supported Flags and Reserved Fields by Operations  | 44  |

| Table 5-4: Conditional Reserved Field Checking                | 45  |

| Table 5-5 : Operation Types with Required (must be 1) Flags   | 45  |

| Table 5-6: Operation Status Codes                             |     |

| Table 5-7: Other Software Error Codes                         |     |

| Table 8-1: Descriptor Trusted Fields                          | 58  |

| Table 8-2: Operation Types                                    | 58  |

| Table 8-3: Descriptor Flags                                   |     |

| Table 8-4: Completion record Status field                     |     |

| Table 8-5: Drain Operation-specific Flags                     | 68  |

| Table 8-6: Completion Status for Compare Descriptor           | 71  |

| Table 8-7: Memory Copy with Dualcast Operation-specific Flags | 75  |

| Table 8-8: CRC Generation Operation-specific Flags            | 77  |

| Table 9-1: Register Attributes                                | 88  |

| Table 9-3: Address Translation Modes                          |     |

| Table 9-4: MMIO register initial values                       | 93  |

| Table 9-5: Read-only MMIO registers                           |     |

| Table 9-6: Administrative Commands                            |     |

| Table 9-7: Administrative Command Error Codes                 | 109 |

| Table 9-8: Work Queue Configuration Support                   |     |

| Table 9-11: Supported Portal Operations                       | 124 |

## Revision History

| Date          | Revision | Description                |

|---------------|----------|----------------------------|

| November 2019 | Rev 1.0  | Preliminary draft release. |

|               |          |                            |

## Glossary

| Acronym      | Term                                  | Description                                                                                                                                   |

|--------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| ATS          | Address Translation<br>Services       | A protocol defined by the PCI Express* specification to<br>support address translations by a device and to issue ATC<br>invalidations.        |

| ATC          | Address Translation<br>Cache          | A structure in the device that stores translated addresses.<br>Also known as Device TLB.                                                      |

| BD           | Batch descriptor                      | A descriptor that refers to an array of descriptors in memory, to allow submitting multiple work descriptors at once.                         |

|              | Completion Record                     | A 32-byte data structure in memory that is written by the device when an operation completes.                                                 |

|              | Dedicated Mode                        | A mode that allows a single software client to submit work without unnecessary overhead.                                                      |

|              | Descriptor                            | A 64-byte data structure written to the device to specify work to be performed.                                                               |

| DWQ          | Dedicated Work Queue                  | A work queue used by a single software client to submit work.                                                                                 |

|              | Engine                                | An independent operational unit within the Intel DSA device.                                                                                  |

| ENQCMD       | Enqueue Command                       | A CPU instruction to enqueue a command to a shared work queue.                                                                                |

| ENQCMDS      | Enqueue Command as<br>Supervisor      | A CPU instruction to enqueue a command to a shared work<br>queue with Supervisor permissions (from privileged<br>software).                   |

| IMS          | Interrupt Message<br>Storage          | A Scalable I/O Virtualization feature used to store MSI messages in a device-specific manner.                                                 |

| Intel® I/OAT | Intel® I/O Acceleration<br>Technology | A component of Intel® Virtualization Technology for<br>Connectivity, improves data flow across the platform to<br>enhance system performance. |

| IOMMU        | I/O Memory<br>Management Unit         | DMA Remapping Hardware Unit as defined by Intel <sup>®</sup><br>Virtualization Technology for Directed I/O.                                   |

|              | Group                                 | A configurable set of work queues and engines.                                                                                                |

| MMIO         | Memory-mapped I/O                     |                                                                                                                                               |

| MOVDIR64B    | Move Direct 64-Byte                   | A CPU instruction used to enqueue a command to a dedicated work queue.                                                                        |

| MSI          | Message Signaled<br>Interrupt         | A memory write operation to a pre-defined address to generate an interrupt.                                                                   |

| Acronym       | Term                                 | Description                                                                                                                                                                                                                                                                                                                  |

|---------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSI-X         |                                      | A PCI Express feature used to configure Message Signaled Interrupts.                                                                                                                                                                                                                                                         |

| PASID         | Process Address Space<br>Identifier  | A value used in memory transactions to convey the address<br>space on the host of an address used by the device.                                                                                                                                                                                                             |

| PM            | Persistent Memory                    | Memory that retains state when power is removed, such as battery-backed DRAM or Intel® Optane™ DC persistent memory.                                                                                                                                                                                                         |

| PRS           | Page Request Service                 | A protocol defined by the PCI Express specification for a device to report recoverable page-faults and receive page-fault responses.                                                                                                                                                                                         |

| RSVD          | Reserved                             | Any field that is described as reserved in this specification<br>must be written as 0 by software. Generally, hardware<br>reports an error if a reserved field is non-zero, but it may not<br>do so in all cases. If software sets a reserved field to a non-<br>zero value and no error is reported, behavior is undefined. |

| SoC           | System-on-chip                       | An integrated chip composed of host processors, accelerators, memory, and I/O agents.                                                                                                                                                                                                                                        |

| SR-IOV        | Single Root I/O<br>Virtualization    | A PCI Express standard for virtualizing PCI Express endpoint device interfaces.                                                                                                                                                                                                                                              |

| SVM           | Shared Virtual Memory                | Ability for an accelerator I/O device to operate in the same<br>virtual memory space of applications on host processors. It<br>also implies ability to operate from page-able memory,<br>avoiding functional requirements to pin memory for DMA<br>operations.                                                               |

|               | Shared Mode                          | A mode that allows multiple software clients to concurrently submit work.                                                                                                                                                                                                                                                    |

| SWQ           | Shared Work Queue                    | A work queue that allows multiple software clients to concurrently submit work.                                                                                                                                                                                                                                              |

| ТС            | Traffic Class                        | A PCI Express feature that allows differentiation of transactions to apply appropriate servicing policies.                                                                                                                                                                                                                   |

| VDCM          | Virtual Device<br>Composition Module | A software component that is part of a VMM, which composes a virtual device and makes it available to a VM.                                                                                                                                                                                                                  |

| VDEV          | Virtual Device                       | A virtual device implemented by VDCM.                                                                                                                                                                                                                                                                                        |

| WD            | Work Descriptor                      | A descriptor that specifies a DMA operation.                                                                                                                                                                                                                                                                                 |

| WQ Work Queue |                                      | A queue in the device used to store descriptors submitted by software until they can be dispatched.                                                                                                                                                                                                                          |

## 1 Introduction

This document describes the architecture of the Intel<sup>®</sup> Data Streaming Accelerator (Intel<sup>®</sup> DSA). Intel DSA is a high-performance data copy and transformation accelerator that will be integrated in future Intel<sup>®</sup> processors, targeted for optimizing streaming data movement and transformation operations common with applications for high-performance storage, networking, persistent memory, and various data processing applications.

Intel DSA replaces the Intel® QuickData Technology, which is a part of Intel® I/O Acceleration Technology.

## 1.1 Audience

The intended audience for this specification is hardware engineers and SoC architects to build compliant hardware implementations, device driver software developers to program the device, virtualization software providers to efficiently enable sharing and virtualization of the device, and application or library developers utilizing Intel DSA operations.

## 1.2 References

| Description                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------|

| Intel® 64 and IA-32 Architectures Software Developer's Manuals                                                           |

| https://software.intel.com/en-us/articles/intel-sdm                                                                      |

| Intel® Architecture Instruction Set Extensions Programming Reference                                                     |

| https://software.intel.com/en-us/download/intel-architecture-instruction-set-extensions-programming-                     |

| reference<br>PCI Express* Base Specification 4.0                                                                         |

| http://www.pcisig.com/specifications/pciexpress                                                                          |

|                                                                                                                          |

| Intel® Virtualization Technology for Directed I/O Specification                                                          |

| https://software.intel.com/en-us/download/intel-virtualization-technology-for-directed-io-architecture-<br>specification |

|                                                                                                                          |

| Intel <sup>®</sup> Scalable I/O Virtualization Technical Specification                                                   |

| https://software.intel.com/en-us/download/intel-scalable-io-virtualization-technical-specification                       |

| Intel® I/O Acceleration Technology                                                                                       |

| https://www.intel.com/content/www/us/en/wireless-network/accel-technology.html                                           |

| RFC 3720, Internet Small Computer Systems Interface                                                                      |

| http://www.ietf.org/rfc/rfc3720.txt                                                                                      |

Table 1-1: References

§

## 2 Overview

The goal of Intel DSA is to provide higher overall system performance for data mover and transformation operations, while freeing up CPU cycles for higher level functions. Intel DSA hardware supports high-performance data mover capability to/from volatile memory, persistent memory, memory-mapped I/O, and through a Non-Transparent Bridge (NTB) in the SoC to/from remote volatile and persistent memory on another node in a cluster. Intel DSA hardware provides a PCI Express\* compatible programming interface to the Operating System and can be controlled through a device driver.

Besides doing basic data mover operations, Intel DSA is designed to perform some number of higher-level transformation operations on memory. For example, Intel DSA can generate and test CRC checksum or Data Integrity Field (DIF) on the memory region, to support usages typical with storage and networking applications. Intel DSA supports a memory compare operation for equality, generates a delta record, and applies a delta record to a buffer. These compare and the delta generate/merge functions may be utilized by applications such as VM migration, VM fast check-pointing, and software managed memory deduplication usages.

## 2.1 High Level Usages

This section summarizes some of the envisioned data movement and transformation usages for Intel DSA.

- **Datacenter**: As a data movement offload engine to reduce datacenter tax for memory copying, zeroing, etc. to free up CPU cycles from mundane infrastructure work.

- **Storage**: Storage appliances use data movement (including CRC generation and Data Integrity Field (DIF) generation) within the node and across nodes using Non-Transparent Bridge (NTB).

- **Networking**: Packet processing pipelines use Intel DSA for data copy. An example usage is virtual switch (vSwitch) offload for inter-VM packet switching.

- **Deduplication**: Memory deduplication requires comparing memory pages for equality, which can be done using Intel DSA memory compare operations.

- VM Migration and Fast Checkpointing: VM fast checkpointing and VM migration flows require the VMM to identify a VM's dirty pages and send them efficiently to the destination machine (with minimal network traffic and latency). Intel DSA delta operations generate diffs of pages, enabling the VMM to send only the delta record to the destination, reducing network bandwidth.

## 2.2 Intel<sup>®</sup> DSA Features

Intel DSA features include 1) infrastructure features, which are basic features to help with programmability, performance, and efficiency; 2) data operations, which are the actual data DMA and other transformation operations; and 3) control operations. The following sections give an overview of these features.

#### 2.2.1 Intel<sup>®</sup> DSA Infrastructure Features

The following infrastructure features are supported by Intel DSA.

- Shared Virtual Memory (SVM): Intel DSA supports SVM which allows user level applications to submit commands to Intel DSA directly with virtual addresses in the descriptors. Intel DSA supports translating virtual addresses to physical addresses using IOMMU including handling page faults. The virtual address ranges referenced by a descriptor may span multiple pages. Intel DSA also supports the use of physical addresses, as long as each data buffer specified in the descriptor is contiguous in physical memory.

- Partial descriptor completion: With SVM support in Intel DSA, it is possible for an operation to encounter a page fault during address translation. Software can control whether the device is to continue processing after waiting for resolution of a page fault or terminate processing of a descriptor that encounters a page fault and proceed to the next descriptor. If processing of a descriptor is terminated, the completion record indicates to software the amount of work completed and information about the page fault, so that software can resolve the fault and restart the operation from the point where it stopped.

- Block on fault: As an alternative to partial descriptor completion, when Intel DSA encounters a page fault, it can coordinate with system software to resolve the fault and continue the operation transparently to the software that submitted the descriptor.

- **Batch processing:** Intel DSA supports submitting descriptors in a batch. A Batch descriptor points to a set of virtually contiguous work descriptors (i.e., descriptors with actual data operations). When processing a batch descriptor, Intel DSA fetches the work descriptors from the specified memory and processes them.

- Stateless device: Intel DSA descriptors are designed so that all information required for processing the descriptor comes in the descriptor itself. This allows the device to store little client specific state which improves its scalability. The only exception is the completion interrupt message, when used, because it must be configured by trusted software.

- Cache allocation control: This allows applications to specify whether output data is allocated in the cache or is sent to memory without cache allocation. Completion records are always allocated in the cache.

- Shared Work Queue (SWQ) support: Intel DSA supports scalable work submission through Shared Work Queues (SWQ) using the ENQCMD and ENQCMDS instructions.

- Dedicated Work Queue (DWQ) support: Intel DSA supports high-throughput work submission through Dedicated Work queues (DWQ) using MOVDIR64B instruction.

- **QoS support:** Intel DSA has several features that allow the kernel driver to separately control access to Intel DSA resources by different guests and applications.

- Scalable IOV support: Intel Scalable IO Virtualization improves scalability of device assignment, allowing a VMM to share Intel DSA across many more VMs than would be possible using SR-IOV.

- Persistent Memory features: Configuration registers and descriptor flags allow software to indicate writes to durable memory (such as Intel<sup>®</sup> Optane<sup>™</sup> DC persistent memory) and specify the durability and ordering semantics to the SoC.

### 2.2.2 Intel<sup>®</sup> DSA Data Operations

The following data operations are supported by Intel DSA. See chapter 8 for details on these operations.

| Operation | Туре                   | Description                                                                                                                                                                                                |

|-----------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Move      | Memory<br>Move         | Transfer data from a source address to destination address. Source and destination ranges can be either in main memory or MMIO.                                                                            |

|           | CRC<br>Generation      | Generate CRC checksum on the transferred data.                                                                                                                                                             |

|           | DIF                    | Data Integrity Field (DIF) check.<br>DIF insert, strip, or update while transferring data.                                                                                                                 |

|           | Dualcast               | Copy data simultaneously to two destination locations.                                                                                                                                                     |

| Fill      | Memory Fill            | Fill memory range with a fixed pattern.                                                                                                                                                                    |

| Compare   | Memory<br>Compare      | Compare two source buffers and return whether the buffers are identical.                                                                                                                                   |

|           | Delta Record<br>Create | Create a delta record containing the differences between the original and modified buffers. The size of the delta record is bounded and Intel DSA signals an overflow if the differences exceed the bound. |

|           | Delta Record<br>Merge  | Merge a delta record with the original source buffer to produce a copy of the modified buffer at the destination location.                                                                                 |

|           | Pattern/Zero<br>Detect | Special case of compare where instead of the second input buffer, an 8-<br>byte pattern is specified. Pattern may be zero.                                                                                 |

| Flush     | Cache Flush            | Evict all lines in given address range from all levels of CPU caches.                                                                                                                                      |

Table 2-1: Intel® DSA Data Operations

### 2.2.3 Intel® DSA Control Operations

The following control operations are supported by Intel DSA. Some of these commands are issued using descriptors and some are issued using the Command register. See sections 9.2.12 and 8.3 for details.

| Operation             | Туре             | Description                                                       |

|-----------------------|------------------|-------------------------------------------------------------------|

| Enable /<br>Disable / | Device           | Manage the device as a whole.                                     |

| Reset                 | WQ               | Manage individual WQs.                                            |

| Drain                 | Current client   | Drain all in-flight work requests from the current client.        |

| Drain /               | Specified client | Drain or abort in-flight work requests from the specified client. |

| Abort                 | Work Queue       | Drain or abort in-flight work requests in specified work queue.   |

|                       | All              | Drain all in-flight work requests in the device.                  |

| No-op                 | Null operation   | Performs no operation but can signal completion.                  |

#### Table 2-2: Intel® DSA Control Operations

§

## 3 Intel<sup>®</sup> Data Streaming Accelerator Architecture

This chapter describes the Intel DSA architecture in detail. Each SoC may support any number of Intel DSA device instances. A multi-socket server platform may support multiple such SoCs. From a software perspective, each Intel DSA instance is exposed as a single Root Complex Integrated Endpoint. Each Intel DSA instance is under the scope of a DMA Remapping hardware unit (also called an IOMMU). Each Intel DSA instance is behind a single DMA Remapping hardware unit, but depending on the SoC design, different Intel DSA instances can be behind the same or different DMA Remapping hardware units.

Intel DSA supports an Address Translation Cache (ATC) and interacts with DMA Remapping hardware using the PCI-SIG-defined Address Translation Services (ATS), Process Address Space ID (PASID), and Page Request Services (PRS) capabilities. Intel DSA uses the PASID TLP prefix in upstream requests to support both Shared Virtual Memory (SVM) and Scalable I/O Virtualization (Scalable IOV). Intel DSA utilizes the DMA Remapping hardware to translate DMA addresses to host physical addresses. Depending on the usage, a DMA address can be a Host Virtual Address (HVA), Guest Virtual Address (GVA), Guest Physical Address (GPA), or I/O Virtual Address (IOVA). Intel DSA supports additional PCI Express capabilities, including Advanced Error Reporting (AER), and MSI-X.

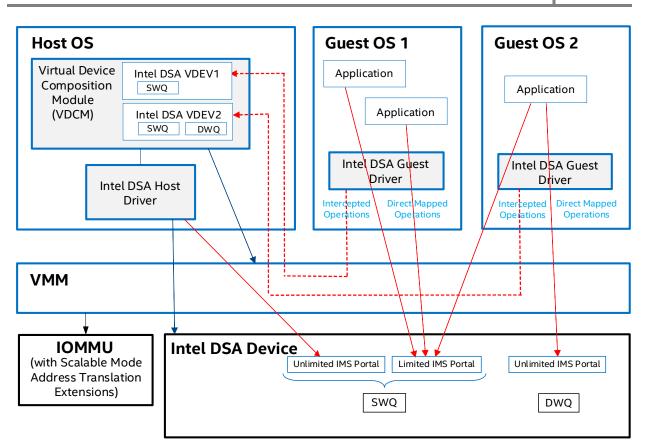

The Intel DSA architecture is designed to support Scalable I/O virtualization. The device can be shared directly to multiple VMs in a secure and isolated manner to achieve high throughput. Sections 3.13 and 7.3 describe the virtualization features in more detail.

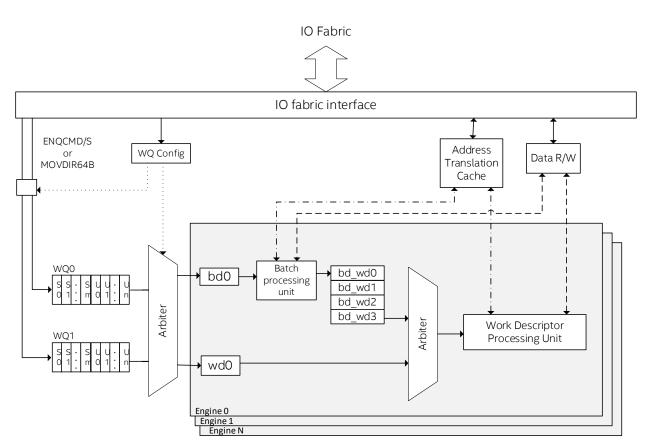

Figure 3-1 illustrates the high-level blocks within the Intel DSA device at a conceptual level. Intel DSA uses the I/O fabric interface for receiving downstream work requests from clients and for upstream read, write, and address translation operations. Intel DSA includes configuration registers, Work Queues (WQ) to hold descriptors submitted by software, arbiters used to implement QoS and fairness policies, processing engines, an address translation and caching interface, and a memory read/write interface. The batch processing unit processes Batch descriptors by reading the array of descriptors from memory. The work descriptor processing unit has stages to read memory, perform the requested operation on the data, generate output data, and write output data, completion records, and interrupt messages.

The WQ configuration allows software to configure each WQ either as a Shared Work Queue (SWQ) that receives descriptors using non-posted ENQCMD/S instructions or as a Dedicated Work Queue (DWQ) that receives descriptors using posted MOVDIR64B instructions. The configuration also allows software to control which WQs feed into which engines and the relative priorities of the WQs feeding each engine.

Figure 3-1: Abstracted Internal Block Diagram of Intel® DSA

## 3.1 Intel® DSA Register and Software Programming Interface

Intel DSA is software compatible with the standard PCI Express configuration mechanism and implements a PCI header and extended space in its configuration-mapped register set.

The Intel DSA device uses memory-mapped registers for controlling its operation. Capability, configuration, and work submission registers (portals) are accessible through the MMIO regions defined by the BARO and BAR2 registers described in section 9.1.1. Each portal is on a separate 4K page so that they may be independently mapped into different address spaces (clients) using CPU page tables.

## 3.2 Descriptors

Software specifies work for Intel DSA using descriptors. Descriptors specify the type of operation for Intel DSA to perform, addresses of data and status buffers, immediate operands, completion attributes, etc. See chapter 8 for descriptor formats and details. The completion attributes specify the address to write the completion record and optionally the information needed to generate a completion interrupt.

Intel DSA avoids maintaining client specific state on the device. All information to process a descriptor comes in the descriptor itself. This improves its shareability among user-mode applications as well as among different virtual machines (or machine containers) in a virtualized system.

A descriptor may contain an operation and associated parameters (called a Work descriptor), or it can contain the address of an array of work descriptors (called a Batch descriptor). Software prepares the descriptor in memory and submits the descriptor to a Work Queue (WQ) of the device. The device dispatches descriptors from the work queues to the engines for processing. When an engine completes a descriptor or encounters certain faults or errors that result in an abort, it notifies the host software by either writing to a completion record in host memory, issuing an interrupt, or both.

## 3.3 Work Queues

Work queues (WQs) are on-device storage to contain descriptors that have been submitted to the device. The WQ Capability register indicates the number of work queues and the amount of work queue storage available on the device. Software configures how many work queues are enabled and divides the available WQ space among the active WQs.

The WQ Configuration Table is used to configure the WQs. Prior to enabling the device, software configures the size of each WQ. Unused WQs have a size of 0. Other parameters of each WQ can be configured later, prior to enabling the WQ. In some configurations, the WQ size and other aspects of the WQ configuration are read-only. See section 9.2.17 for more details on configuring WQs.

Each work queue can be configured to run in one of two modes, Dedicated or Shared. The WQ Capability register indicates support for Dedicated and Shared modes. Controls in the WQ Configuration Table allow software to configure the mode of each WQ. The mode of a WQ can only be changed while the WQ is Disabled. See the specifications for the WQ Capability register, the WQ Configuration Table, and the Command register in section 9.2.17 below for details on configuring and enabling Work Queues.

Descriptors are submitted to work queues via special registers called portals. Each portal is in a separate 4 KB page in device MMIO space. There are four portals per WQ:

- Unlimited MSI-X Portal

- Unlimited IMS Portal

- Limited MSI-X Portal

- Limited IMS Portal

The unlimited portals are intended to be used by kernel-mode software, and the limited portals are intended to be used by user-mode and guest software. The address of the portal used to submit a descriptor allows the device to determine which WQ to place the descriptor in, whether the portal is limited or unlimited, and which interrupt table to use for the completion interrupt. See section 3.7, "Interrupts", for the usage of MSI-X and IMS portals. For a descriptor that does not request an interrupt, it doesn't matter whether it is submitted to an MSI-X portal or an IMS portal.

Descriptor submissions to a Shared WQ using a limited portal are subject to the occupancy threshold of the WQ, as configured using the WQCFG register. Descriptor submissions using an unlimited portal are not subject to the threshold. Dedicated WQs do not use the threshold, so there is no difference between the limited and unlimited portals for a DWQ.

### 3.3.1 Shared Work Queue (SWQ)

In Shared mode, an Intel DSA client uses the ENQCMD or ENQCMDS instruction to submit descriptors to the work queue. ENQCMD and ENQCMDS use a 64-byte non-posted write and wait for a response from the device before completing. Intel DSA returns Success if the descriptor is accepted into the work queue, or Retry if the descriptor is not accepted, due to WQ capacity or QoS. The ENQCMD and ENQCMDS instructions

return the status of the command submission in EFLAGS.ZF flag (0 indicates Success, and 1 indicates Retry). Using the ENQCMD and ENQCMDS instructions, multiple clients can directly and simultaneously submit descriptors to the same work queue. Since the device provides this feedback, the clients can tell whether their descriptors were accepted.

In Shared mode, Intel DSA can be configured to reserve some SWQ capacity for submissions via the unlimited portals for kernel-mode clients. Work submission via the limited portals is accepted until the number of descriptors in the SWQ reaches the threshold configured for the SWQ. Work submission via the unlimited portals is accepted until the SWQ is full.

If the ENQCMD or ENQCMDS instruction returns Success, the descriptor has been accepted by the device and queued for processing. If the instruction returns Retry, software can try re-submitting the descriptor to the SWQ, or if it was a user-mode client using a limited portal, it can request the kernel-mode driver to submit the descriptor on its behalf using an unlimited portal. This helps avoid denial of service and provide forward progress guarantees.

Clients are identified by the device using a 20-bit ID called process address space ID (PASID). The PASID capability must be enabled to use SWQs. The PASID is used by the device to look up addresses in the Address Translation Cache and to send address translation or page requests to the IOMMU. In Shared mode, the PASID to be used with each descriptor is contained in the PASID field of every descriptor. ENQCMD copies the PASID of current thread from IA32\_PASID MSR into the descriptor while ENQCMDS allows supervisor mode software to copy the PASID into the descriptor. For additional details on the use of PASID and the ENQCMD and ENQCMDS instructions, refer to the Intel<sup>®</sup> Architecture Instruction Set Extensions Programming Reference (see Table 1-1: References).

#### 3.3.2 Dedicated Work Queue (DWQ)

In Dedicated mode, an Intel DSA client uses the MOVDIR64B instruction to submit descriptors to the device work queue. MOVDIR64B uses a 64-byte posted write and the instruction completes faster due to the posted nature of the write operation. For dedicated work queues, Intel DSA exposes the total number of slots in the work queue and depends on software to provide flow control. Software is responsible for tracking the number of descriptors submitted and completed, to detect a work queue full condition. If software erroneously submits a descriptor to a dedicated WQ when there is no space in the work queue, the descriptor is dropped. (The error is reported in the Software Error Register.)

With dedicated WQs, the use of PASID is optional. If the PCI Express PASID capability is not enabled, PASID is not used. If the PASID capability is enabled, the WQ PASID Enable field of the WQ Configuration register controls whether PASID is used for each DWQ. Since the MOVDIR64B instruction does not fill in the PASID as the ENQCMD or ENQCMDS instructions do, the PASID field in the descriptor is ignored. When PASID is enabled for a DWQ, Intel DSA uses the WQ PASID field of the WQ Configuration register to do address translation. The WQ PASID field must be set by the Intel DSA driver before enabling a work queue in dedicated mode.

Although dedicated mode doesn't support sharing a single DWQ by multiple clients, Intel DSA can be configured to have multiple DWQs and each of the DWQs can be independently assigned to clients. DWQs can be configured to have the same or different QoS levels.

## 3.4 Engines and Groups

An Intel DSA engine is an operational unit within an Intel DSA device. A group is a set of work queues and engines. Software configures WQs and engines into groups using the Group Configuration registers. Each group contains one or more WQs and one or more engines. Intel DSA may use any engine in a group to process a descriptor posted to any WQ in the group. Each WQ and each engine may be in only one group.

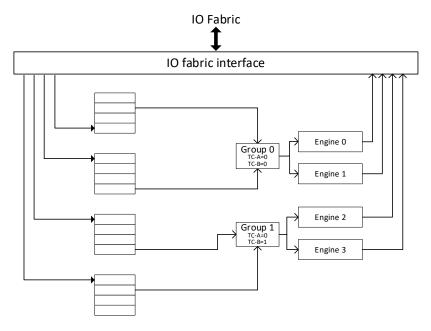

Figure 3-2: Sample Group Configuration 1

Although the Intel DSA architecture allows great flexibility in configuring work queues, groups, and engines, the hardware is designed with the intent to be used in specific configurations. An example configuration is shown in Figure 3-2 with two groups, each provisioned with two engines. Hardware uses either engine in a group to process descriptors from any work queue in the group. In this configuration, if one engine has a stall due to a high-latency memory address translation or page fault, the other engine can continue to operate and maximize the throughput of the overall device.

Figure 3-2 shows example Traffic Class (TC) values for the two groups. In Group 0 both TC values are 0, while in Group 1, TC-B is 1. This example configuration might be used when Group 0 is used solely for operations that access DRAM and Group 1 is used for operations that access both DRAM and persistent memory. The TC Selector flags in descriptors submitted to Group 1 indicate whether each address in the descriptor refers to DRAM or persistent memory. See chapter 4 for information on Traffic Classes and how they can be used to control QoS.

Figure 3-2 shows two work queues in each group, but there may be any number up to the maximum number of WQs supported. The WQs in a group may be shared WQs with different priorities, or one shared WQ and the others dedicated WQs, or multiple dedicated WQs with the same or different priorities.

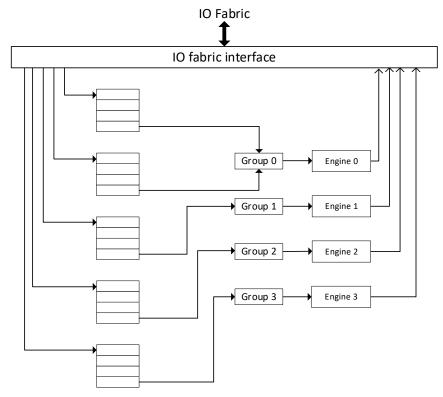

Another example configuration illustrated in Figure 3-3 places each engine in a separate group. Software may choose this configuration when it wants to reduce the likelihood that latency-sensitive operations become blocked behind other operations. In this configuration, software submits latency-sensitive

operations to the work queue connected to one engine, and other operations to the work queues connected to another engine.

If the group used for latency sensitive operations is idle when a descriptor is submitted, the descriptor will be dispatched to an engine immediately

Software can also mix these two, with some engines in a single group and the others in groups by themselves.

Figure 3-3: Sample Group Configuration 2

## 3.5 Descriptor Processing

As each descriptor reaches the head of the work queue, it is available to be dispatched by the group arbiter to an available engine in the group. The arbiter for each group dispatches descriptors from the WQs in the group according to their priority, while ensuring that the higher priority WQs don't starve lower priority WQs. See section 4.1 for information about work dispatch priority.

For a Batch descriptor, which refers to work descriptors in memory, the engine fetches the array of work descriptors from memory. Each work descriptor is passed to the work descriptor processing unit. The work descriptor processing unit uses the Address Translation Cache and IOMMU for completion record, source, and destination address translations; reads source data; performs the specified operation; and writes the destination data back to memory. When the operation is complete, the engine writes the completion record to the pre-translated completion address and generates an interrupt, if requested by the work descriptor.

## 3.6 Descriptor Completion

Descriptors contain three flags and two other fields that allow software to control completion notifications. The three flags are: Completion Record Address Valid, Request Completion Record, and Request Completion Interrupt. The two fields are Completion Record Address and Completion Interrupt Handle.

The completion record is a 32-byte aligned structure in memory that the device writes when the operation is complete or encounters an error. The completion record contains completion status. If the operation completed successfully, the completion record may contain the result of the operation, if any, depending on the type of operation. If the operation did not complete successfully, the completion record contains fault or error information.

Generally, all descriptors should have a valid Completion Record Address and the Completion Record Address Valid flag should be 1. (Exceptions to this rule are described later.)

The first byte of the completion record is the status byte. Status values written by the device are all nonzero. Software should initialize the status field of the completion record to 0 before submitting the descriptor to be able to tell when the device has written to the completion record. (Initializing the completion record also ensures that it is mapped, so the device is less likely to encounter a page fault when accessing it.)

The Request Completion Record flag indicates to the device that it should write the completion record even if the operation completed successfully. If this flag is not set, the device writes the completion record only if there is an error.

Descriptor completion can be detected by software using any of the following methods:

- 1. Poll the completion record, waiting for the status field to become non-zero.

- 2. Use the UMONITOR/UMWAIT instructions on the completion record address, to block until it is written or until timeout. Software should then check whether the status field is non-zero to determine whether the operation has completed.

- 3. Request an interrupt when the operation is completed. For user-mode descriptors, this method requires the kernel to forward the notification to the application.

- 4. If the descriptor is in a batch, set the Fence flag in a subsequent descriptor in the same batch. Completion of the descriptor with the Fence or any subsequent descriptor in the same batch indicates completion of all descriptors that precede the Fence.

- 5. If the descriptor is in a batch, completion of the Batch descriptor that initiated the batch indicates completion of all descriptors in the batch.

- 6. Issue a Drain descriptor or a Drain command and wait for it to complete.

If the completion status indicates a partial completion due to a page fault, the completion record indicates how much processing was completed (if any) before the fault was encountered, and the virtual address where the fault was encountered. Software may choose to fix the fault (by touching the faulting address from the CPU) and resubmit the rest of the work in a new descriptor or complete the rest of the work in software. Faults on descriptor list and completion record addresses are handled differently and are described in more detail in section 3.11.

## 3.7 Interrupts

Intel DSA supports only message signaled interrupts. Intel DSA provides two types of interrupt message storage: (a) an MSI-X table, enumerated through the MSI-X capability, which stores interrupt messages used

by the host driver; and (b) a device-specific Interrupt Message Storage (IMS) table, as described by the Scalable IOV architecture specification, which stores interrupt messages used by guest drivers. Refer to the Scalable I/O Virtualization Architecture Specification (see Table 1-1: References) and section 9.2.21 for more details on IMS.

Interrupts can be generated for five types of events: 1) completion of a descriptor; 2) WQ occupancy below programmed limit; 3) completion of an administrative command; 4) an error posted in the Software Error Register; and 5) performance monitoring counter overflow. For each type of event there is a separate interrupt enable. Interrupts of types 3, 4 and 5 are generated using entry 0 in the MSI-X table. The Interrupt Cause Register may be read by software to determine the reason for the interrupt.

For completion of a descriptor that requests a completion interrupt, the interrupt message used is dependent on the portal the descriptor was submitted to and the Completion Interrupt Handle in the descriptor. As described in section 3.3, each WQ has both MSI-X portals and IMS portals. For a descriptor submitted via an MSI-X portal, the Completion Interrupt Handle field in the descriptor selects an entry in the MSI-X table. For a descriptor submitted via an IMS portal, the Completion Interrupt Message Storage. Descriptors in a batch are treated as if they had been submitted via the same portal as the Batch descriptor.

When the Interrupt Handle Request capability is 0, the Completion Interrupt Handle is the index of the desired entry in the MSI-X table or the IMS. When the Interrupt Handle Request capability is 1, software uses the Request Interrupt Handle command to obtain the handle to use for the interrupt. Software specifies in the Request Interrupt Handle command which interrupt table entry it wants a handle for, and the response to the command contains the handle that software should place in the Completion Interrupt Handle field of the descriptor to request that interrupt. See section 7.3.3 for a description of interrupt virtualization.

| Event                                   | Submission register | Interrupt message used                                                                        |

|-----------------------------------------|---------------------|-----------------------------------------------------------------------------------------------|

| Error posted in SWERROR register        | N/A                 | MSI-X table entry 0.                                                                          |

| Completion of an administrative command | Command register    | MSI-X table entry 0.                                                                          |

| Perfmon counter<br>overflow             | N/A                 | MSI-X table entry 0.                                                                          |

| WQ Occupancy below                      | WQ Occupancy        | MSI-X or IMS entry programmed in WQ Occupancy                                                 |

| limit                                   | Interrupt register  | Interrupt register.                                                                           |

| Descriptor completion                   | MSI-X portal        | MSI-X table entry specified by Completion Interrupt Handle field in descriptor.               |

|                                         | IMS portal          | Interrupt Message Storage entry specified by Completion Interrupt Handle field in descriptor. |

#### Table 3-1: Interrupt Delivery

The MSI-X table defined by the PCIe\* specification is augmented in Intel DSA by the MSI-X Permissions Table, detailed in section 9.2.15. Each MSI-X Permissions Table entry has several fields that control generation of interrupts using that table entry. Each IMS entry contains the same control fields. The PASID Enable and PASID fields of the selected interrupt table entry are checked before the descriptor is executed, as detailed in section 5.4. The Ignore and Mask fields are checked when the descriptor completes. If the Ignore field is 1, no interrupt is generated. If the Ignore field is 0, the Mask and Pending fields behave as

specified by PCIe. If the Mask field is 1, the Pending field is set to 1 and no interrupt is generated. If Ignore and Mask are both 0, the interrupt is generated.

Interrupts generated by Intel DSA are processed through the Interrupt Remapping and Posting hardware as configured by the kernel or VMM software.

## 3.8 Batch Descriptor Processing

Intel DSA supports submitting multiple descriptors at once. A Batch descriptor contains the address of an array of work descriptors in host memory and the number of elements in the array. The array of work descriptors is called the "batch". Use of Batch descriptors allows Intel DSA clients to submit multiple work descriptors using a single ENQCMD, ENQCMDS, or MOVDIR64B instruction and can potentially improve overall throughput, especially when using descriptors with small transfer sizes.

Intel DSA enforces a limit on the number of work descriptors in a batch. There is an overall limit, indicated by the Maximum Supported Batch Size field in the General Capabilities register, and also a separate limit for each work queue, set by the WQ Maximum Batch Size field for each WQ in the WQ Configuration Table. A batch must contain at least 2 work descriptors.

Batch descriptors are submitted to work queues in the same way as other work descriptors. When a Batch descriptor is processed by the device, the device reads the array of work descriptors from memory and then processes each of the work descriptors. The work descriptors are not necessarily processed in order. (See section 3.9 for information on how software can control ordering of descriptors in a batch.)

The PASID and the Priv fields of the Batch descriptor are used for all descriptors in the batch.<sup>1</sup> The PASID and Priv fields in the descriptors in the batch are ignored.

Each work descriptor in the batch can specify a completion record address and/or a completion interrupt, just as with directly submitted work descriptors. The completion record and completion interrupt for the Batch descriptor (if requested) are generated after completion of all the descriptors in the batch and generation of their completion records (if requested). No readback is performed before the Batch descriptor completion record is generated. To maintain ordering of the completion record for the Batch behind all writes from descriptors in the batch, either the Batch descriptor should use the same TC for its completion record as the prior writes, or the Destination Readback flag should be set in each of the descriptors in the batch.

The completion record for the Batch descriptor contains an indication of whether any of the descriptors in the batch completed with Status not equal to Success. This allows software to avoid examining all the completion records for the descriptors in the batch, in the usual case where all the descriptors in the batch completed successfully.

A Batch descriptor may not be included in a batch. Nested or chained descriptor arrays are not supported. See section 8.3.2 for details on the format of Batch descriptors.

<sup>&</sup>lt;sup>1</sup> For a Batch descriptor submitted to a dedicated work queue, the PASID and Priv fields of the Batch descriptor and all the work descriptors in the batch come from the WQ Configuration register.

## 3.9 Ordering and Fencing

By default, Intel DSA doesn't guarantee any ordering while executing work descriptors. Descriptors can be dispatched and completed in any order the device sees fit to maximize throughput. If ordering is required, there are several ways for software to enforce it:

- Submit a descriptor, wait for the completion record or interrupt from the descriptor to ensure completion, and then submit the next descriptor.

- Use a Drain descriptor or Drain command to wait for preceding descriptors to complete and then submit the following descriptors.

- Within a batch, use the Fence flag.

Enforcing ordering may increase both the CPU time used to submit a descriptor and the latency for the descriptor to begin execution within Intel DSA.

To control ordering for descriptors in a batch specified by a Batch descriptor, each work descriptor has a Fence flag. When set, Fence guarantees that processing of that descriptor will not start until all previous descriptors in the same batch are completed. This allows a descriptor with Fence to consume data produced by a previous descriptor in same batch. A descriptor consuming data from a previous descriptor in the batch should use the same Traffic Class as the descriptor producing the data. If software cannot ensure this, then software must set the Destination Readback flag in the descriptor that produces the data, to ensure the required ordering.

If any descriptor in a batch completes with Status not equal to Success, for example if it is partially completed due to a page fault, a subsequent descriptor with the Fence flag equal to 1 and any following descriptors in the batch are abandoned. The completion record for the Batch descriptor that was used to submit the batch indicates how many descriptors were completed. Any descriptors that were partially completed and generated a completion record are counted as completed. Only the abandoned descriptors are considered not completed.

The completion record write for a descriptor is ordered after all data writes produced by the descriptor if:

- the descriptor is fully completed; or

- the completion record TC selector in the descriptor is the same as the destination TC selector(s).

Otherwise, the completion record may be observed by software before some of the data writes produced by the descriptor. Software may avoid partial completion by setting the Block on Fault flag in the descriptor. A completion interrupt (if requested) is ordered after the completion record write.

The Destination Readback flag causes Intel DSA to perform a zero-length read, using the final destination address of the descriptor, prior to writing the completion record. If the destination target is different from the completion record target, then the Destination Readback flag may be set to ensure that writes have propagated to the destination before the completion record is written. For example, this flag may be used in descriptors that target NTB to ensure that data written by the descriptor has propagated across the NTB link. Destination readback is performed only if the descriptor is completed successfully. If the descriptor is partially completed, the readback is not performed. If a follow-up descriptor submitted to Intel DSA to complete the operation writes to the same destination using the same TC, sets the Destination Readback flag, and completes successfully, then the readback performed by the follow-up descriptor also ensures

completion of memory writes performed by the prior descriptor(s). Software may avoid the need for a follow-up descriptor by setting the Block on Fault flag in the initial descriptor to prevent partial completion.

## 3.10 Drain Descriptor

Drain is a normal descriptor that is submitted to a work queue and allows a client to wait for completion of preceding descriptors in the WQ that the Drain descriptor is submitted to. For the purpose of Drain, a descriptor is completed after all writes generated by the operation are globally observable; after destination readback, if requested; after the write to the completion record is globally observable, if needed; and after generation of the completion interrupt, if requested.

If a Drain descriptor is submitted to a dedicated WQ, it waits for completion of all descriptors in the WQ. If Drain is submitted to a shared WQ, it waits for descriptors in the WQ that have the same PASID as the Drain descriptor. Drain can be used like a Fence operation for the entire PASID. A Drain descriptor can be used by software to request a single completion record and/or interrupt for the completion of multiple descriptors. A Drain descriptor may not be included in a batch. (A Fence flag may be used in a batch to wait for prior descriptors in the batch to complete.) Software should execute a fencing instruction such as SFENCE or MFENCE before submitting the Drain descriptor to ensure that the Drain descriptor is received by Intel DSA after the descriptors it is intended to drain.

To ensure completion of descriptors in the WQ, prior to Drain descriptor completion, hardware normally issues an implicit readback for each supported Traffic Class, using an address determined by hardware. Software can control this default behavior by setting one or both of the Suppress flags in the Drain descriptor. If unsuppressed through flags, the Drain descriptor implicit readbacks ensure that all previous writes to the Root Complex, on the respective TCs, have completed. Previous writes to a peer device (i.e. non-Root Complex) may not get flushed by a Drain descriptor implicit readback but can be flushed using explicit readbacks. The Drain descriptor allows software to specify up to 2 explicit readback addresses in the descriptor. If specified, hardware will issue readbacks to each explicit readback address using the Traffic Class specified by the corresponding TC selector flag in the descriptor. See section 8.3.3 for details of the Drain descriptor.

## 3.11 Address Translation

Intel DSA supports the use of either physical or virtual addresses. The use of virtual addresses that are shared with processes running on the CPU is called shared virtual memory (SVM). To support SVM the device provides a PASID when performing address translations, and it handles page faults that occur when no translation is present for an address. However, the device itself doesn't distinguish between virtual and physical addresses; this distinction is controlled by the programming of the IOMMU.

Intel DSA supports the PCI Express Address Translation Service (ATS) and Page Request Service (PRS) capabilities. ATS describes the device behavior during address translation. When a descriptor enters a descriptor processing unit, the device requests translations for the addresses in the descriptor. If there is a hit in the Address Translation Cache, the device uses the corresponding HPA. If there is a miss or permission fault, Intel DSA sends an address translation request to IOMMU for the translation. The IOMMU finds the translation by walking the appropriate page tables and returns an address translation response that contains the translated address and the effective permissions. The device stores the translation in the Address Translation Cache and uses the corresponding HPA for the operation. If IOMMU can't find the translation in the page tables, it returns an address translation response that indicates no translation is available. When the IOMMU response indicates no translation or indicates effective permissions that don't include the permission required by the operation, it is considered a page fault. Page fault handling is described below.

The Intel DSA device may encounter a page fault on one of: 1) a Completion Record Address; 2) the Descriptor List Address in a Batch descriptor; 3) Readback address in a Drain descriptor (See sections 3.10 and 8.3.3 for more details); or 4) a source buffer or destination buffer address. For the first three cases, the Intel DSA device blocks until the page fault is resolved, if PRS is enabled; otherwise it is reported as an error. For the fourth case, the Intel DSA device can either block until the page fault is resolved or prematurely complete the descriptor and return a partial completion to the client, as specified by software.

When Intel DSA blocks on a page fault it reports the fault as a PRS request to the IOMMU for servicing by the OS page fault handler. The IOMMU notifies the OS through an interrupt. The OS validates the address and upon successful checks creates a mapping in the page table and returns a PRS response through the IOMMU. If the OS was not able to create a mapping, it returns an error response and Intel DSA completes the descriptor with an error.