# Control-flow Enforcement Technology Preview

June 2017 Revision 2.0

Document Number: 334525-002

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

The products and services described may contain defects or errors known as errata which may cause deviations from published specifications. Current characterized errata are available on request.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at http://intel.com/

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting www.intel.com/design/literature.htm.

Intel, the Intel logo, and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2016-2017, Intel Corporation. All Rights Reserved.

## **Contents**

| 1 | Intr | roduc  | tion                                                                      | 7  |

|---|------|--------|---------------------------------------------------------------------------|----|

|   | 1.1  | Sha    | adow Stack                                                                | 7  |

|   | 1.2  | Ind    | rect branch tracking                                                      | 8  |

| 2 | Sh   | adow   | Stacks                                                                    | 9  |

|   | 2.1  | Sha    | adow Stack Pointer and its Operand and Address Size Attributes            | 9  |

|   | 2.2  | Ter    | minology                                                                  | 9  |

|   | 2.3  | Nea    | ar CALL and RET Behavior with Shadow Stacks Enabled                       | 10 |

|   | 2.4  | Far    | CALL and RET                                                              | 10 |

|   | 2.5  | Sta    | ck Switching on Call to Interrupt/Exception Handlers in 64-bit Mode       | 11 |

|   | 2.6  | Sha    | adow Stack Usage on Task Switch                                           | 12 |

|   | 2.7  | Sw     | itching Shadow Stacks                                                     | 13 |

| 3 | Ind  | lirect | Branch Tracking                                                           | 15 |

|   | 3.1  | No-    | track Prefix for Near Indirect Call/Jmp                                   | 16 |

|   | 3.2  | Ter    | minology                                                                  | 16 |

|   | 3.3  | Cor    | ntrol Transfer Tracking                                                   | 17 |

|   | 3.3  | 3.1    | Control Transfers between CPL 3 and CPL < 3                               | 18 |

|   | 3.3  | 3.2    | Control Transfers within CPL 3 or CPL < 3                                 | 18 |

|   | 3.4  | ΕN     | DBRANCH State Machine                                                     | 19 |

|   | 3.5  | INT    | 3 Treatment                                                               | 20 |

|   | 3.6  | Leg    | acy Compatibility Treatment                                               | 20 |

|   | 3.6  | 5.1    | Legacy Code Page Bitmap Format                                            | 21 |

|   | 3.7  | Oth    | er Considerations                                                         | 21 |

|   | 3.7  | '.1    | Intel® Transactional Synchronization Extensions (Intel® TSX) Interactions | 21 |

|   | 3.7  | '.2    | #CP(ENDBRANCH) Priority w.r.t #NM and #UD                                 | 21 |

|   | 3.7  | '.3    | #CP(ENDBRANCH) Priority w.r.t #BP                                         | 22 |

| 4 | Ch   | ange   | s to Control Transfer Instructions Reference                              | 23 |

|   | 4.1  | CA     | LL— Call Procedure                                                        | 23 |

|   | 4.2  | INT    | n/INTO/INT3 – Call to Interrupt Procedure                                 | 42 |

|   | 4.3  | JMI    | P — Jump                                                                  | 58 |

|   | 4.4  | RE     | T—Return from Procedure                                                   | 68 |

|   | 4.5  | SY     | SCALL—Fast System Call                                                    | 82 |

|   | 4.6  | SY     | SENTER—Fast System Call                                                   | 85 |

|   | 4.7  | SY     | SEXIT—Fast Return from Fast System Call                                   | 89 |

#### CONTROL-FLOW ENFORCEMENT TECHNOLOGY PREVIEW

|    | 4.8  | SYSRET—Return From Fast System Call                                            | 92    |

|----|------|--------------------------------------------------------------------------------|-------|

|    | 4.9  | IRET/IRETD—Interrupt Return                                                    | 95    |

| 5  | Tas  | k Management Interactions with CET105                                          |       |

|    | 5.1  | 32-bit Task-State Segment (TSS)                                                | . 105 |

|    | 5.2  | Task Switching                                                                 | . 105 |

| 6  | Sha  | dow Stack Management Instructions111                                           |       |

|    | 6.1  | INCSSP—Increment Shadow Stack Pointer                                          | . 112 |

|    | 6.2  | RDSSP—Read Shadow Stack Pointer                                                | . 114 |

|    | 6.3  | SAVEPREVSSP —Save Previous Shadow Stack Pointer                                | . 116 |

|    | 6.4  | RSTORSSP — Restore saved Shadow Stack Pointer                                  | . 119 |

|    | 6.5  | WRSS — Write to shadow stack                                                   | . 122 |

|    | 6.6  | WRUSS — Write to User Shadow Stack                                             | . 124 |

|    | 6.7  | SETSSBSY — Mark Shadow Stack Busy                                              | . 126 |

|    | 6.8  | CLRSSBSY — Clear Shadow Stack Busy Flag                                        | . 128 |

| 7  | Cor  | ntrol Transfer Terminating Instructions130                                     |       |

|    | 7.1  | ENDBR64 — Terminate an Indirect Branch in 64-bit Mode                          | . 130 |

|    | 7.2  | ENDBR32 — Terminate an Indirect Branch in 32-bit and Compatibility Mode        | . 131 |

| 8  | Cor  | ntrol Protection Exception, Enumeration, Enables and Extended State Management |       |

|    | 8.1  | Control Protection Exception                                                   | . 132 |

|    | 8.2  | Feature Enumeration                                                            | . 132 |

|    | 8.3  | Master Enable                                                                  | . 132 |

|    | 8.4  | CET MSRs                                                                       | . 132 |

|    | 8.5  | CET Extended State Management                                                  | . 133 |

| 9  | IA F | Paging and EPT Extensions135                                                   |       |

|    | 9.1  | Shadow Stack Marking in IA Page Tables                                         | . 135 |

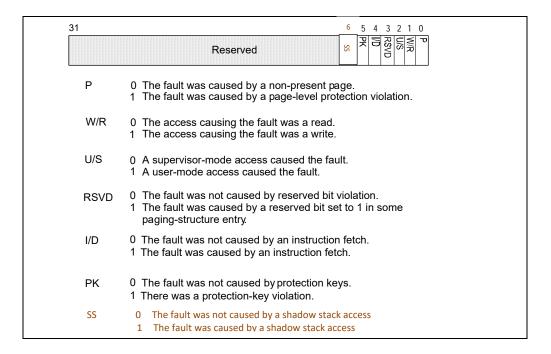

|    | 9.1. | 1 Page Faulting Behavior                                                       | . 135 |

|    | 9.1. | 2 Page-Fault Exceptions                                                        | . 135 |

|    | 9.1. | 3 CR0.WP interaction                                                           | . 137 |

|    | 9.1  | EPT Extensions                                                                 | . 138 |

|    | 9.1. | 1 EPT violations                                                               | . 139 |

|    | 9.1. | 2 EPT Violations Exit Qualification                                            | . 139 |

|    | 9.2  | Paging Disabled Behavior                                                       | . 139 |

| 10 | ) VM | X Interactions                                                                 |       |

|    | 10.1 | VMCS Guest State Area Extensions                                               | . 140 |

|    | 10.2 | VMCS Host State Area Extensions                                                | . 140 |

|    | 10.3 | VMCS VM-Exit Controls Extensions.                                              | . 141 |

#### CONTROL-FLOW ENFORCEMENT TECHNOLOGY PREVIEW

| 1  | 0.4 | VMCS VM-Entry Controls Extensions | 141 |

|----|-----|-----------------------------------|-----|

| 1  | 0.5 | EPTP                              | 141 |

| 1  | 0.6 | VM Exit                           | 141 |

| 1  | 0.7 | VM Entry                          | 142 |

| 1  | 8.0 | IA32_VMX_EPT_VPID_CAP             | 142 |

|    |     | M Interactions                    |     |

| 1  | 1.1 | SMRAM State Save Map              | 143 |

|    |     | SMI Handler Execution Environment |     |

|    |     | RSM                               |     |

| 12 | TX  | Γ Interactions                    |     |

| 13 | SG  | X Interactions                    |     |

## **Revision History**

| Document<br>Number | Revision<br>Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Date      |

|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 334525-001         | 1.0                | Initial release of the document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | June 2016 |

| 334525-002         | 2.0                | <ul> <li>Numerous updates across chapters include:</li> <li>Added CR0.WP and CR4.CET interaction, CET state save area description, and separate CPUID bits for SS and IBT.</li> <li>Clarified that WRUSS makes the shadow stack store with user-access intent.</li> <li>Updated the definition of the SSS bit in EPT and corresponding fault check.</li> <li>Updated SYSCALL/SYSENTER to clear SSP instead of setting it to IA32_PL0_SSP.</li> <li>Updated SAVESSP/RSTORSSP to close a timing window and renamed SAVESSP to SAVEPREVSSP.</li> <li>Clarified that SETSSBSY causes a #CP exception on token check failure, and uses IA32_PL0_SSP as an implicit operand.</li> <li>Clarified that CLRSSBSY clears SSP on completion and sets CF to indicate invalid token.</li> <li>Updated INCSSP to accept a register source operand.</li> <li>Updated CET MSR description to clarify that writes are always checked for machine canonicality on parts that support 64-bit mode and that bits 1:0 are reserved.</li> </ul> | June 2017 |

## 1 Introduction

Return-oriented Programming (ROP), and similarly call/jmp-oriented programming (COP/JOP), have been the prevalent attack methodology for stealth exploit writers targeting vulnerabilities in programs. These attack methodology have the common elements:

- A code module with execution privilege and contain small snippets of code sequence with the characteristic: at least one instruction in the sequence being a control transfer instruction that depends on data either in the return stack or in a register for the target address,

- Diverting the control flow instruction (e.g. RET, CALL, JMP) from its original target address to a new target (via modification in the data stack or in the register).

Control-flow Enforcement Technology (CET) provides the following capabilities to defend against ROP/JOP style control-flow subversion attacks:

- Shadow Stack return address protection to defend against Return Oriented Programming,

- Indirect branch tracking free branch protection to defend against Jump/Call Oriented Programming.

The rest of this document is organized as follows:

After an overview of Shadow Stack and Indirect Branch Tracking in the rest of this section. Sections 2 and 3 describe the programming environment of Shadow Stack and Indirect Branch Tracking. Sections 4 and 5 describe changes to traditional control flow instructions and task switching behaviors when these new capabilities are enabled. Both Shadow Stack and Indirect Branch Tracking introduce new instruction set extensions, and are described in Sections 6 and 7.

Control-flow Enforcement Technology introduces a new exception class (#CP) with interrupt vector 21. Section 8 covers enumeration, configuration and new exception class. Sections 9 through 13 cover interactions between CET and other IA system enhancement technology, including paging, VMX, SMX, SGX.

#### NOTE

In sections 4 and 5, text in this color is used to illustrate the extensions to the control transfer instructions and flows for CET.

### 1.1 Shadow Stack

A shadow stack is a second stack for the program that is used exclusively for control transfer operations. This stack is separate from the data stack and can be enabled for operation individually in user mode or supervisor mode. When shadow stacks are enabled, the CALL instruction pushes the return address on both the data and shadow stack. The RET instruction pops the return address from both stacks and compares them. If the return addresses from the two stacks do not match, the processor signals a control protection exception (#CP). Note that the shadow stack only holds the return addresses and not parameters passed to the call instruction. See Figure 1 for an illustration of shadow stack operations on near call and ret instruction.

The shadow stack is protected from tamper through the page table protections such that regular store instructions cannot modify the contents of the shadow stack. To provide this protection the page table protections are extended to support an additional attribute for pages to mark them as "Shadow Stack" pages. When shadow stacks are enabled, control transfer instructions/flows like near call, far call, call to interrupt/exception handlers, etc. are allowed to store return addresses to the shadow stack. However stores from instructions like MOV, XSAVE, etc. will not be allowed. Likewise control transfer instructions like near ret, far ret, iret, etc. when they attempt to read from the shadow stack the access will fault if the underlying page is not marked as a "Shadow Stack" page. This paging protection detects and prevents conditions that cause an overflow or underflow of the shadow stack or any malicious attempts to redirect the processor to consume data from addresses that are not shadow stack addresses.

8

## 1.2 Indirect branch tracking

The ENDBRANCH (see Section 7 for details) is a new instruction that is used to mark valid indirect call/jmp targets in the program. This instruction opcode is selected to be one that is a NOP on legacy machines such that programs compiled with ENDBRANCH new instruction continue to function on old machines without the CET enforcement. On processors that support CET the ENDBRANCH is still a NOP and is primarily used as a marker instruction by the in-order part of the processor pipeline to detect control flow violations. The CPU implements a state machine that tracks indirect jmp and call instructions. When one of these instructions is seen, the state machine moves from IDLE to WAIT\_FOR\_ENDBRANCH state. In WAIT\_FOR\_ENDBRANCH state the next instruction in the program stream must be an ENDBRANCH. If an ENDBRANCH is not seen the processor causes a control protection fault else the state machine moves back to IDLE state.

## 2 Shadow Stacks

A shadow stack is a second stack used exclusively for control transfer operations. This stack is separate from the data stack. The shadow stack is not used to store data and hence is not explicitly writeable by software. Writes to the shadow stack are restricted to control transfer instructions and shadow stack management instructions. The shadow stack feature can be enabled separately in user mode (CPL == 3) or supervisor mode (CPL < 3).

Shadow stacks operate only in protected mode with paging enabled. Shadow stacks cannot be enabled in virtual 8086 mode.

# 2.1 Shadow Stack Pointer and its Operand and Address Size Attributes

When CET is enabled the processor supports a new architectural register, shadow stack pointer (SSP), when the processor supports the shadow stack feature. The SSP cannot be directly encoded as a source, destination or memory operand in instructions. The SSP points to the current top of the shadow stack.

The SSP holds a linear address and is loaded into the register by FAR RET, IRET, SETSSBSY and RSTORSSP instructions. The SSP must be loaded with a 32-bit aligned linear address.

The width of the shadow stack is 32-bit in 32-bit/compatibility mode and is 64-bit in 64-bit mode. The address-size attribute of the shadow stack is likewise 32-bit in 32-bit/compatibility mode and 64-bit in 64-bit mode.

## 2.2 Terminology

When shadow stacks are enabled, control transfer instructions/flows and shadow stack management instructions do loads/stores to the shadow stack. Such load/stores from control transfer instructions and shadow stack management instructions are termed as shadow\_stack\_load and shadow\_stack\_store to distinguish them from a load/store performed by other instructions like MOV, XSAVES, etc.

The pseudocode for the instruction operations use a notation ShadowStackEnabled(CPL) as a test of whether shadow stacks are enabled at the CPL. This term returns a TRUE or FALSE indication as follows:

#### ShadowStackEnabled(CPL):

```

IF CR4.CET = 1 AND CR0.PE = 1 AND EFLAGS.VM = 0

IF CPL = 3

THEN

(* Obtain the shadow stack enable from MSR used to enable feature for CPL = 3 *)

SHADOW STACK ENABLED = IA32 U CET.SH STK EN;

ELSE

(* Obtain the shadow stack enable from MSR used to enable feature for CPL < 3 *)

SHADOW_STACK_ENABLED = IA32_S_CET.SH_STK_EN;

IF SHADOW_STACK_ENABLED = 1

THEN

return TRUE;

ELSE

return FALSE;

FI;

ELSE

(* Shadow stacks not enabled in real mode and virtual-8086 mode or if the master CET feature

```

,

enable in CR4 is disabled \*)

return FALSE;

ENDIF

# 2.3 Near CALL and RET Behavior with Shadow Stacks Enabled

Near CALL, when shadow stack is enabled, pushes the return address on both the data stack and the shadow stack. Near RET, when shadow stack is enabled, pops the return address from both the shadow stack and data stack. The data stack pointer (ESP/RSP) is further incremented optionally by 'n' bytes if an optional 'n' operand was specified however the shadow stack pointer (SSP) does not increment. If the return address popped from the two stacks are not the same then the processor causes a #CP(near-ret) exception.

#### 2.4 Far CALL and RET

The CALL instruction can be used to call a procedure located in a different segment than the current code segment or to a segment at a different privilege level.

On a far CALL, the processor pushes the CS, LIP (linear address of the return address) and the SSP on the shadow stack and on a far RET pops the SSP, LIP and the CS from the shadow stack. If the CS and LIP do not match the return address as determined by popping the CS and EIP from the data stack, the processor causes a #CP(FAR-RET/IRET) exception.

The shadow stack behavior on a far CALL to higher privilege level is as follows.

- When the far CALL originates at CPL3, the return addresses are not pushed onto the supervisor shadow stack. Likewise, a far RET to CPL3 from supervisor privilege level (CPL < 3) does not do any verification of the return addresses. On a CPL3 -> CPL<3 transition, the user space SSP is saved to an MSR - IA32\_PL3\_SSP and on a CPL<3 -> CPL3 transition is restored from this MSR.

- On an inter-privilege-level call, the call instruction performs a stack switch. The data stack for the supervisor program is located from the current TSS. Likewise, the shadow stack is switched on such transfers. The SSP for the supervisor program is obtained from one of following MSRs depending on the target privilege level.

- o IA32\_PL2\_SSP if transitioning to ring 2.

- o IA32 PL1 SSP if transitioning to ring 1.

- o IA32\_PL0\_SSP if transitioning to ring 0.

- A far call from ring 2 to ring 1, ring 2 to ring 0, or from ring 1 to ring 0 is considered a "same privilege class" transfer for shadow stacks. Thus such far calls subsequent to locating the SSP for the new privilege level push the CS, LIP and SSP of the calling procedure onto the shadow stack of the called procedure. Likewise, the far RET will verify the CS and LIP from the shadow stack matches the return address as determined by the CS and EIP obtained from the data stack.

On an inter-privilege far CALL, CET verifies a "supervisor shadow stack token" that is setup by the supervisor when creating shadow stacks intended to be used on these transfers. The supervisor shadow stack token is a 64-bit value formulated as follows.

- Bit 63:3 linear address of the "supervisor shadow stack token".

- Bit 2 reserved. Must be zero.

- Bit 1 -reserved. Must be zero.

- Bit 0 Busy bit. If 0 indicates this shadow stack is not active on any logical processor.

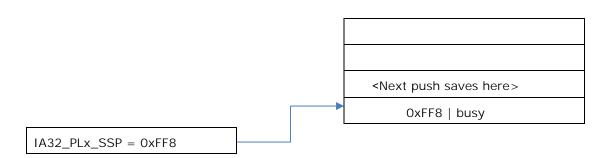

The following figure illustrates a supervisor shadow stack with a "supervisor shadow stack token" located at its base.

Figure 1 Supervisor Shadow Stack with a Supervisor Shadow Stack Token

The address specified in the IA32\_PLx\_SSP is required to be 8 byte aligned. The processor does the following checks prior to switching to a supervisor shadow stack programmed into IA32\_PLx\_SSP. These steps are performed atomically.

- 1. Load the "supervisor shadow stack" token from the address specified in IA32\_PLx\_SSP using a shadow\_stack\_load.

- 2. The busy bit in the token must be 0.

- 3. The address programmed in the MSR must match the address in the "supervisor shadow stack token".

- 4. If the checks 2 and 3 are successful, then set the busy bit in the token using a shadow\_stack\_store and switch the SSP to the value specified in the IA32\_PLx\_SSP.

- 5. If the checks 2 or 3 fail, then the busy bit is not set and a #GP(0) exception is raised.

On a far RET, the instruction clears the busy bit in the shadow stack token as follows. These steps are also performed atomically.

- 1. Load the "supervisor shadow stack" token from the SSP using a shadow\_stack\_load.

- 2. Check if the busy bit is 1.

- 3. Check if the address programmed in "supervisor shadow stack" token matches SSP.

- 4. If the checks 2 and 3 are successful, then clear the busy bit in the token using a shadow\_stack\_store, else continue without modifying the contents of the shadow stack pointed to by SSP.

The operations described here are also applicable to a far transfer performed when calling an interrupt or exception handler through an interrupt/trap gate in the IDT. Likewise, the IRET instruction behaves similar to the Far RET instruction.

# 2.5 Stack Switching on Call to Interrupt/Exception Handlers in 64-bit Mode

The 64-bit mode operation provides a stack-switching mechanism called Interrupt Stack Table (IST) wherein the 64-bit IDT descriptor can be used to specify one of seven data stack pointers in the 64-bit TSS when there is no privilege change involved as part of the call. If the IST index specified is 0 and there is no privilege change involved then a stack switch occurs to the same stack.

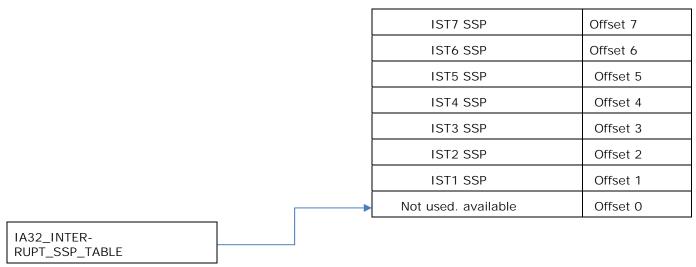

To support this stack-switching mechanism, the shadow stack feature provides an MSR, IA32\_INTER-RUPT\_SSP\_TABLE, to program the linear address of a table of seven shadow stack pointers. When a non-

zero IST value is specified and there is no privilege change involved as part of the call, the MSR points to a 64 byte table in memory that is indexed using the IST index.

Figure 2 Interrupt Shadow Stack Table

## 2.6 Shadow Stack Usage on Task Switch

A task switch may be invoked by:

- JMP or CALL instruction to a TSS descriptor in the GDT.

- JMP or CALL instruction to a task-gate descriptor in the GDT or the current LDT.

- An interrupt or exception vector points to a task-gate descriptor in the IDT.

With shadow stack enabled, the new task must be associated with a 32-bit TSS and must not be in virtual-8086 mode. The 32-bit SSP for the new task is located at offset 104 in the 32-bit TSS. Thus the TSS of the new task must be at least 108 bytes. This SSP is required to be 8 byte aligned, and required to point to a "supervisor shadow stack" token (though the task may be at CPL3).

On a nested task switch initiated by a CALL instruction, the SSP of the old task is not saved to the old task TSS. Instead, the SSP of the old task is pushed onto the shadow stack of the new task along with the CS and LIP of the old task. Likewise on a non-nested task switch initiated by IRET, the SSP of the new task is restored from the shadow stack of old task. The CS and LIP on the shadow stack of the old task are matched against the return address determined by the CS and EIP of the new task. If the match fails, a #CP(FAR-RET/IRET) exception is reported.

## 2.7 Switching Shadow Stacks

The architecture provides a mechanism to switch shadow stacks using a pair of instructions; RSTORSSP and SAVEPREVSSP. The RSTORSSP instruction verifies a "shadow stack restore" token located at the top of the new shadow stack and referenced by the memory operand of this instruction. The RSTORSSP instruction verifies this "shadow stack restore" token to determine if it is a valid restore point on the new shadow stack. This "shadow stack restore" token is a 64-bit value formatted as follows.

- Bit 63:2 shadow stack pointer when this restore point was created.

- Bit 1 -reserved. Must be zero.

- Bit 0 Mode bit. If 0, then this shadow stack restore token can be used with a RSTORSSP instruction in compatibility/legacy mode. If 1, then this shadow stack restore token can be used with a RSTORSSP instruction in 64-bit mode.

The "shadow stack restore" token is created by the SAVEPREVSSP instruction. The operating system may also create a restore point on a shadow stack by creating a "shadow stack restore" token.

The shadow stack switching sequence involves first switching to the new shadow stack using the RSTORSSP instruction. Subsequent to switching to the new shadow stack, if a restore point should be created on the old shadow stack then the SAVEPREVSSP instruction may be used. In order to allow the SAVEPREVSSP instruction to determine the address where to save the "shadow stack restore" token, the RSTORSSP instruction replaces the "shadow stack restore" token with a "previous ssp" token that holds the SSP at the time the RSTORSSP instruction was invoked and is formatted as follows.

- Bit 63:2 shadow stack pointer when the RSTORSSP instruction was invoked i.e. the SSP of the old shadow stack.

- Bit 1 set to 1.

- Bit 0 Mode bit. If 0 then this "previous ssp" token can be used with a SAVEPREVSSP instruction in compatibility/legacy mode. If 1 then this "previous ssp" token can be used with a SAVEPREVSSP instruction in 64-bit mode.

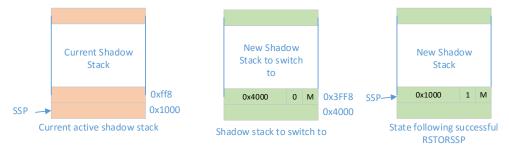

The following figure illustrates the RSTORSSP instruction operation during a shadow stack switching sequence.

Figure 3 RSTORSSP to switch to new shadow stack

In this example, the initial SSP is 0x1000 and the "shadow stack restore" token is on a new shadow stack at address 0x3FF8. The token at address 0x3FF8 holds the SSP when this restore point was created; in this example it is 0x4000.

In order to switch to the new shadow stack, the RSTORSSP instruction is invoked with the memory operand pointing set to 0x3FF8. When the RSTORSSP instruction completes, the SSP is set to 0x3FF8 and the "shadow stack restore" token at 0x3FF8 is replaced by a "previous ssp" token that holds the address 0x1000, i.e., old SSP.

The following figure illustrates the SAVEPREVSSP instruction operation during a shadow satck switching sequence.

Figure 4 SAVEPREVSSP to save a restore point

To allow switching back to this old shadow stack, a SAVEPREVSSP instruction is now invoked. The SAVE-PREVSSP instruction does not take any memory operand and expects to find a "previous ssp" token at the top of the shadow stack, i.e., at address 0x3FF8. The SAVEPREVSSP instruction then saves a "shadow stack restore" token on the old shadow stack at address 0xFF8, and the token itself holds the address 0x1000 which is the address recorded in the "previous ssp" token. The SAVEPREVSSP instruction also pops the "previous ssp" token off the current shadow stack and thus the SSP following SAVEPREVSSP is 0x4000.

Subsequently to switch back to the old shadow stack, a RSTORSSP instruction may be invoked with memory operand set to 0xFF8.

If following switch to a new shadow stack it is not required to create a restore point on the old shadow stack, then the "previous ssp" token created by the RSTORSSP instruction can be popped using the INCSSP instruction.

See the SAVEPREVSSP and RSTORSSP instruction operations for the detailed algorithm.

## 3 Indirect Branch Tracking

When the indirect branch tracking feature is active the indirect jmp/call instruction behavior changes as below.

- JMP If the next instruction retired after an indirect JMP is not an ENDBR32 instruction in legacy and compatibility mode or ENDBR64 instruction in 64-bit mode, then #CP fault. Below JMP instructions are tracked to enforce an endbranch. Note that jcc, RIP relative, and far direct jmp are not included as these have an offset encoded into the instruction and are not exploitable to create unintended control transfers.

- o jmp r/m16, r/m32, r/m64

- o jmp m16:16, m16:32, m16:64

- CALL If the next instruction retired after an indirect call is not an ENDBR32 instruction in legacy

and compatibility mode or ENDBR64 in 64-bit mode, then #CP fault. Below call instructions are

tracked to enforce an endbranch. Note that relative and zero displacement form of call instructions

are not included as these have an offset encoded into the instruction and are not exploitable to

create unintended control transfers.

- o call r/m16, r/m32, r/m64

- o call m16:16, m16:32, m16:64

The ENDBR32 and ENDBR64 instructions will have the same effect as the NOP instruction on Intel 64 processors that do not support CET. On processors supporting CET, these instructions still do not change register state (NOP-like). This allows CET instrumented programs to execute on processors that do not support CET. Even when CET is supported and enabled, these NOP-like instructions do not affect the execution state of the program, do not cause any additional register pressure, and are minimally intrusive from power and performance perspectives.

The processor implements a two-state state machine to track indirect call/jmp for terminations. One state machine is maintained for user mode and one for supervisor mode. At reset the user and supervisor mode state machines are in IDLE state.

When instructions other than indirect call/jmp retire the state machine stays in the IDLE state.

On an indirect call or jmp instruction retirement, the state machine transitions to WAIT\_FOR\_ENDBRANCH state.

In the WAIT\_FOR\_ENDBRANCH state, the indirect branch tracking stat machine will:

- Only allow the next instruction retirement to be an ENDBRANCH instruction (i.e. ENDBR64 if EFER.LMA=1 & CS.L=1, ENDBR32 if EFER.LMA=0 || (EFER.LMA=1 & CS.L=0) ), or

- Allow next instruction retirement to be compatible with non-CET code generation if legacy compatibility configuration allows (see section 3.6).

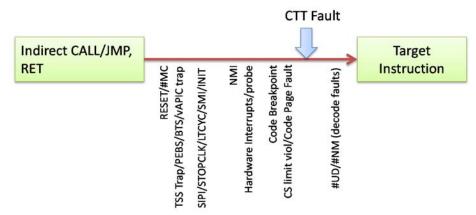

When a #CP(ENDBRANCH) exception is thrown, the priority of the exception is as follows.

Figure 5 Priority of Control Protection Exception on Missing Endbranch

Higher priority faults/traps/events that occur at the end of an indirect call/jmp or ret are delivered ahead of any #CP(ENDBRANCH) fault. The CET state machine at the privilege level where the higher priority fault/trap/event occurred retains its state when the control transfers to the fault/trap/event handler. The instruction pointer pushed on the stack for a CET fault is the address of the instruction at the target of the indirect call/jmp that caused the fault.

## 3.1 No-track Prefix for Near Indirect Call/Jmp

Near indirect call and jmp instructions when prefixed with 3EH are termed "non-tracked indirect control transfer instructions" and do not modify the CET indirect branch tracker. Far call and jmp are always tracked and ignore the 3EH prefix. The NO\_TRACK\_EN control in the IA32\_U\_CET/IA32\_S\_CET MSR enables this no-track prefix treatment. When this control is 0, the near indirect call and jmp are always tracked irrespective of the presence of the 3EH prefix.

In 64-bit mode, the 3EH prefix on an indirect call or jmp is recognized as a no-track prefix when the following conditions are satisfied.

- 3EH must be the last legacy prefix of any group (except any REX).

- There must not be a 64H/65H prefix on the instruction.

In legacy/compatibility mode, the 3EH prefix on an indirect call or jmp is recognized as a no-track prefix when it is the last group 2 prefix on the instruction.

## 3.2 Terminology

The pseudocode for the instruction operations use a notation EndbranchEnabled(CPL) as a test of whether endbranch tracking is enabled at the CPL. This term returns a TRUE or FALSE indication as follows.

#### EndbranchEnabled(CPL):

16

```

THEN

return TRUE;

ELSE

return FALSE;

FI;

ELSE

(* Endbranch tracking is not enabled in real mode and virtual-8086 mode or if the master CET feature

enable in CR4 is disabled *)

return FALSE;

ENDIF

Likewise the notation EndbranchEnabledAndNotSuppressed is defined as follows:

EndbranchEnabledAndNotSuppressed(CPL):

IF CR4.CET = 1 AND CR0.PE = 1 AND EFLAGS.VM = 0

IF CPL = 3

THFN

(* Obtain the endbranch enable from MSR used to enable feature for CPL = 3 *)

ENDBR ENABLED = IA32 U CET.ENDBR EN;

SUPPRESSED = IA32 U CET.SUPPRESS;

ELSE

(* Obtain the endbranch enable from MSR used to enable feature for CPL < 3 *)

ENDBR ENABLED = IA32 S CET.ENDBR EN;

SUPPRESSED = IA32 S CET.SUPPRESS;

FI;

IF ENDBR ENABLED = 1 AND SUPPRESSED = 0

THEN

return TRUE:

ELSE

return FALSE;

FI;

ELSE

(* Endbranch tracking is not enabled in real mode and virtual-8086 mode or if the master CET feature

enable in CR4 is disabled *)

return FALSE;

ENDIF

```

## 3.3 Control Transfer Tracking

The hardware implements two CET indirect branch tracker state machines, one for user mode (CPL == 3) and one for supervisor mode (CPL < 3). At any time, which of the CET indirect branch trackers is in the active state depends on the CPL of the machine. When a user space program is executing, the CPL 3 CET indirect branch tracker is active. When supervisor mode software is executing, the CPL < 3 tracker is active. This section describes the various control transfer conditions and the tracker state on those transfers.

#### 3.3.1 Control Transfers between CPL 3 and CPL < 3

Some events and instructions can cause control transfer to occur from CPL 3 to CPL < 3, and vice versa. As part of the CPL change the hardware also switches the active CET indirect branch tracker. For example, when an interrupt occurs during execution of a user mode (CPL == 3) program and it causes the CPL to switch to supervisor mode (CPL < 3) then, as part of the CPL change, the user mode CET indirect branch tracker becomes inactive and the supervisor mode CET indirect branch tracker becomes active. A subsequent iret is used by the interrupt handler to return to the interrupted user mode program. This iret causes the processor to switch the CPL to user mode (CPL == 3) and, as part of the CPL change, the supervisor mode CET indirect branch tracker becomes active.

The CPL where the event or instruction that caused the control transfer occurs is termed the source CPL, and the CET indirect branch tracker state at that CPL is referred here as the source CET indirect branch tracker state. The CPL reached at the end of the control transfer is termed the destination CPL, and the CET indirect branch tracker state at that CPL is referred to as the destination CET indirect branch tracker state.

This section describes various cases of control transfers that occur between user mode (CPL 3) and supervisor mode (CPL < 3).

In all these cases the source CET indirect branch tracker state becomes not active and retains its state (IDLE, WAIT\_FOR\_ENDBRANCH), and the target CET indirect branch tracker state becomes active if there was no fault during the transfer.

- Case 1: FAR call/jmp, SYSCALL/SYSENTER

- o If indirect branch tracking is enabled, the target indirect branch tracker state becomes active and is unsuppressed and goes to WAIT\_FOR\_ENDBRANCH. This enforces that the subroutine invoked by a far call/jmp must begin with an endbranch.

- Case 2: Hardware interrupt/trap/exception/NMI/Software interrupt/Machine Checks

- o If indirect branch tracking is enabled, the target indirect branch tracker state becomes active and is unsuppressed and goes to WAIT\_FOR\_ENDBRANCH.

- Case 3: iret

- o If indirect branch tracking enabled, the target indirect branch tracker becomes active and keeps its state. If the user mode was interrupted by a higher priority event, like an interrupt at the end of the indirect call/jmp, then when an iret is used to return to the interrupted user mode program, the user mode indirect branch tracker retains its state and a #CP fault will occur if the next instruction decoded is not an endbr32/64 according to mode of machine.

#### 3.3.2 Control Transfers within CPL 3 or CPL < 3

Some events and instructions can cause control transfer to occur within CPL 3 or CPL < 3. For such transfers since the CPL class does not change, the same indirect branch tracker is used at the beginning and end of the control transfer.

- Case 1: FAR CALL/JMP, Near indirect call/jmp

- o FAR CALL/JMP: If indirect branch tracking is enabled, active indirect branch tracker is unsuppressed and goes to WAIT\_FOR\_ENDBRANCH.

- Near indirect call/jmp: If indirect branch tracking is enabled and not suppressed, active indirect branch tracker goes to WAIT\_FOR\_ENDBRANCH.

- Case 2: Hardware interrupt/trap/exception/NMI/Software interrupt/Machine Checks

- If indirect branch tracking is enabled, the active indirect branch tracker is unsuppressed and goes to WAIT\_FOR\_ENDBRANCH.

- Case 3: iret

- o If indirect branch tracking is enabled, the active indirect branch tracker keeps its state.

## 3.4 ENDBRANCH State Machine

The state machine is described by following table.

| Current State                         | Trigger                    | Next state                                       |

|---------------------------------------|----------------------------|--------------------------------------------------|

|                                       | Instructions other than    |                                                  |

|                                       | indirect call/jmp or 3EH   | TRACKER=IDLE, SUPPRESS=0,                        |

| TRACKER=IDLE, SUPPRESS=0,             | prefixed near indirect     | ENDBR_EN=1                                       |

| ENDBR_EN=1                            | call/jmp and               |                                                  |

|                                       | NO_TRACK_EN=1              |                                                  |

|                                       | Indirect call/jmp without  | TRACKER=WAIT_FOR_ENDBRANCH,                      |

|                                       | 3EH prefix                 | SUPPRESS=0, ENDBR_EN=1                           |

|                                       | Indirect call/jmp with     |                                                  |

|                                       | 3EH prefix and             |                                                  |

|                                       | NO_TRACK_EN=0              |                                                  |

|                                       | Far call/jmp               | TDACKED- WAIT FOR ENDROANCH                      |

|                                       | INT3                       | TRACKER= WAIT_FOR_ENDBRANCH,                     |

|                                       | Endbranch instruction      | SUPPRESS=0, ENDBR_EN=1 TRACKER=IDLE, SUPPRESS=0, |

|                                       | Endbranch instruction      |                                                  |

| TRACKER= WAIT_FOR_ENDBRANCH,          | ENCLU[ERESUME]             | ENDBR_EN=1 TRACKER=IDLE, SUPPRESS=0,             |

| SUPPRESS=0, ENDBR EN=1                | LINCLO[ERESOME]            | ENDBR EN=1                                       |

| _                                     | Instructions other than    | If legacy compatibility treatment is             |

|                                       | endbranch, ENCLU[ERE-      | not enabled or if not allowed by leg-            |

|                                       | SUME] or int3              | acy code page bitmap:                            |

|                                       | -                          | No state change and deliver                      |

|                                       |                            | #CP (ENDBRANCH)                                  |

|                                       |                            | If legacy compatibility treatment is             |

|                                       |                            | enabled and transfer allowed by leg-             |

|                                       |                            | acy code page bitmap:                            |

|                                       |                            | TRACKER=IDLE, SU-                                |

|                                       |                            | PRESS=ISUPPRESS_DIS,                             |

|                                       |                            | ENDBR_EN=1                                       |

| TRACKER=x, SUPPRESS=x,                | All instructions           | TRACKER=x, SUPPRESS=x,                           |

| ENDBR_EN=0                            |                            | ENDBR_EN=0                                       |

| TRACKER=IDLE, SUPPRESS=1,             | FAR CALL/JMP               | TRACKER=WAIT_FOR_ENDBRANCH,                      |

| ENDBR_EN=1                            |                            | SUPPRESS=0, ENDBR_EN=1                           |

|                                       | Endbranch instruction      | TRACKER=IDLE, SUPPRESS=0,                        |

|                                       | ENCLU[ERESUME]             | ENDBR_EN=1                                       |

|                                       | All other instructions in- | TRACKER=IDLE, SUPPRESS=1,                        |

|                                       | cluding indirect call/jmp  | ENDBR_EN=1                                       |

| TRACKER=1, SUPPRESS=1,                | N/A                        | N/A                                              |

| ENDBR_EN=1                            |                            |                                                  |

| (This state cannot be reached by      |                            |                                                  |

| hardware and is disallowed as a valid |                            |                                                  |

| state by WRMSR/XRSTORS/VM en-         |                            |                                                  |

| try/VM exit)                          |                            |                                                  |

#### 3.5 INT3 Treatment

INT3 are treated special in the WAIT\_FOR\_ENDBRANCH state. Occurrence of INT3 do not move the tracker to IDLE, but instead the #BP trap from the INT3 instructions respectively is delivered as a higher priority event than the #CP exception due to missing endbranch.

## 3.6 Legacy Compatibility Treatment

Endbranch Legacy compatibility treatment allows a CET enabled program to be used with legacy software that was not compiled / instrumented with endbranch. A CET enabled program enters legacy compatibility treatment when all of the below conditions are met.

- 1. Legacy compatibility configuration is enabled in this CPL class by setting the LEG\_IW\_EN bit in IA32\_U\_CET/IA32\_S\_CET.

- 2. Control transfer is performed using an indirect call/jmp without no-track prefix to a non-end-branch instruction.

- 3. The legacy code page bitmap is setup to indicate that the target of the control transfer is a legacy code page.

The legacy code page bitmap is a data structure in program memory that is used by the hardware to determine if the code page to which a legacy transfer is being performed is allowed.

When a matching endbranch instruction is not decoded at the target of an indirect call/jmp when required, the processor performs the below actions.

#### **CET State machine violation event handler:**

```

If LEG IW EN == 1

LA = LIP;

IF ENCLAVE MODE == 1

LA = LA - SECS.BASEADDR;

IF (EFER.LMA & CS.L) == 0

BITMAP BYTE = load.Asize syslinaddr. Osize8(BITMAP BASE + LA[31:15]]

ELSE

IF CR4.LA57 == 1

BITMAP BYTE = load.Asize syslinaddr. Osize8(BITMAP BASE + LA[56:15]]

BITMAP BYTE = load.Asize syslinaddr. Osize8(BITMAP BASE + LA[47:15]]

IF BITMAP BYTE & (1 << LA[14:12]) == 0 then Deliver #CP(ENDBRANCH) fault

IF CPL = 3

IA32 U CET.TRACKER = IDLE

IA32 U CET.SUPPRESS = IA32 U CET.SUPPRESS DIS == 0 ? 1:0

ELSE

IA32 S CET.TRACKER = IDLE

IA32 S CET.SUPPRESS = IA32 S CET.SUPPRESS DIS == 0 ? 1 : 0

ENDIF

Restart the instruction (handle all arch. consistency around MOV SS state machines, STI etc.)

without opening up interrupt/trap window

ELSE

Deliver #CP(ENDBRANCH) Fault

ENDIF

```

20

Faults/traps in pseudocode are delivered normally (e.g. #PF, EPT violation). On fault, active tracker holds last value (WAIT\_FOR\_ENDBRANCH) and address saved on stack is current IP (instruction that wasn't the ENDBRANCH).

The CET endbranch state machine is suppressed in legacy compatibility mode if the SUPPRESS\_DIS control bit is 0.

Once the CET endbranch state machine has been suppressed, subsequent indirect call/jmp are not tracked for termination instruction.

Once CET has been suppressed, subsequent execution of endbranch instructions will do the following (see section 7 for details).

```

IF EndbranchEnabled(CPL)

NOP

ELSE

SUPPRESS = 0

TRACKER = IDLE

ENDIF

```

### 3.6.1 Legacy Code Page Bitmap Format

The legacy code page bitmap is a flat bitmap whose linear address is pointed to by the EB\_LEG\_BIT-MAP\_BASE. Each bit in the bitmap represents a 4K page in linear memory. If the bit is 1 it indicates that the corresponding code page is a legacy code page; else it is a CET-enabled code page.

The processor uses the linear address of the instruction to which legacy transfer was attempted to lookup the bitmap. Bits of the linear address used as index in the bitmap are as follows.

- In legacy and compatibility mode Bits 31:12

- In 64-bit mode (EFER.LMA=1 and CS.L=1)

- o If CR4.LA57 = 1, then Bits 56:12

- o If CR4.LA57 = 0, then Bits 47:12

### 3.7 Other Considerations

# 3.7.1 Intel® Transactional Synchronization Extensions (Intel® TSX) Interactions

The XBEGIN instruction encodes the relative offset to the abort handler and hence the fallback to the abort handler can be considered as a "direct" branch and the abort handler does not need to have an ENDBRANCH.

CET continues to enforce indirect call/jmp tracking within a transaction. Legacy compatibility treatment inside a transaction functions normally. If a transaction abort occurs then the processor sets the state of the indirect branch tracker to IDLE and not-suppressed.

## 3.7.2 #CP(ENDBRANCH) Priority w.r.t #NM and #UD

#NM, #UD and #CP(ENDBRANCH) are in the same priority class. Both #NM and #UD are opcode based faults. The #CP(endbranch) is prioritized higher than #NM and #UD as CET architecturally requires an ENDBRANCH at target of indirect call/jmp.

### 3.7.3 #CP(ENDBRANCH) Priority w.r.t #BP

Debug Exceptions priority is as follows.

- Traps delivered before any #CP(ENDBRANCH) fault: data breakpoint trap, IO breakpoint trap single step trap, task switch trap.

- Code Breakpoint fault detected before instruction decode and delivered before #CP(endbranch).

- GD condition fault lower priority than #CP(endbranch).

- On IRET back from #DB/#BP the source indirect branch tracker becomes active if enabled and not suppressed.

INT3 does not cause #CP(endbranch) to support debugger usage of replacing bytes of ENDBRANCH with INT3 to set breakpoints. INT3 at target of a CALL-JMP(indirect) cause #BP(INT3) instead of #CP(endbranch), #CP(endbranch) fault is delayed. #BP caused by INT3 treated like other events that are higher priority than CET fault. On IRET back from #BP the source indirect tracker becomes active if enabled and not suppressed.

## 4 Changes to Control Transfer Instructions Reference

When CET is enabled, the changes in operation of traditional control transfer instructions are described in this section

## 4.1 CALL— Call Procedure

| Opcode | Instruction   | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg<br>Mode | Description                                                                                                                                                                                        |

|--------|---------------|-----------|----------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E8 cw  | CALL rel16    | М         | N.S.           | Valid                  | Call near, relative, displacement relative to next instruction.                                                                                                                                    |

| E8 cd  | CALL rel32    | М         | Valid          | Valid                  | Call near, relative, displacement relative to next instruction. 32-bit displacement sign extended to 64-bits in 64-bit mode.                                                                       |

| FF /2  | CALL r/m16    | М         | N.E.           | Valid                  | Call near, absolute indirect, address given in r/m16.                                                                                                                                              |

| FF /2  | CALL r/m32    | М         | N.E.           | Valid                  | Call near, absolute indirect, address given in r/m32.                                                                                                                                              |

| FF /2  | CALL r/m64    | М         | Valid          | N.E.                   | Call near, absolute indirect, address given in r/m64.                                                                                                                                              |

| 9A cd  | CALL ptr16:16 | D         | Invalid        | Valid                  | Call far, absolute, address given in operand.                                                                                                                                                      |

| 9А ср  | CALL ptr16:32 | D         | Invalid        | Valid                  | Call far, absolute, address given in operand.                                                                                                                                                      |

| FF /3  | CALL m16:16   | М         | Valid          | Valid                  | Call far, absolute indirect address given in m16:16.                                                                                                                                               |

|        |               |           |                |                        | In 32-bit mode: if selector points to a gate, then RIP = 32-bit zero extended displacement taken from gate; else RIP = zero extended 16-bit offset from far pointer referenced in the instruction. |

| FF /3  | CALL m16:32   | М         | Valid          | Valid                  | In 64-bit mode: If selector points to a gate, then RIP = 64-bit displacement taken from gate; else RIP = zero extended 32-bit offset from far pointer referenced in the instruction.               |

| REX.W<br>+ FF /3 | CALL m16:64 | М | Valid | N.E. | In 64-bit mode: If selector points to a gate, then RIP = 64-bit displacement taken from gate; else RIP = 64-bit offset from far pointer referenced in the instruction. |  |

|------------------|-------------|---|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|------------------|-------------|---|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

#### Instruction Operand Encoding

| Op<br>/En | Operand 1     | Operand 2 | Operand 3 | Operand 4 |

|-----------|---------------|-----------|-----------|-----------|

| D         | Offset        | NA        | NA        | NA        |

| М         | ModRM:r/m (r) | NA        | NA        | NA        |

#### **Description**

Saves procedure linking information on the stack and branches to the called procedure specified using the target operand. The target operand specifies the address of the first instruction in the called procedure. The operand can be an immediate value, a general-purpose register, or a memory location.

This instruction can be used to execute four types of calls.

- Near Call A call to a procedure in the current code segment (the segment currently pointed to by the CS register), sometimes referred to as an intra-segment call.

- Far Call A call to a procedure located in a different segment than the current code segment, sometimes referred to as an inter-segment call.

- Inter-privilege-level far call A far call to a procedure in a segment at a different privilege level than that of the currently executing program or procedure.

- Task switch A call to a procedure located in a different task.

The latter two call types (inter-privilege-level call and task switch) can only be executed in protected mode. See "Calling Procedures Using Call and RET" in Chapter 6 of the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 1, for additional -information on near, far, and inter-privilege-level calls. See Chapter 7, "Task Management," in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A, for information on performing task switches with the CALL instruction.

**Near Call.** When executing a near call, the processor pushes the value of the EIP register (which contains the offset of the instruction following the CALL instruction) on the stack (for use later as a return-instruction pointer). The processor then branches to the address in the current code segment specified by the target operand. The target operand specifies either an absolute offset in the code segment (an offset from the base of the code segment) or a relative offset (a signed displacement relative to the current value of the instruction pointer in the EIP register; this value points to the instruction following the CALL instruction). The CS register is not changed on near calls.

For a near call absolute, an absolute offset is specified indirectly in a general-purpose register or a memory location (r/m16, r/m32, or r/m64). The operand-size attribute determines the size of the target operand (16, 32 or 64 bits). When in 64-bit mode, the operand size for near call (and all near branches) is forced to 64-bits. Absolute offsets are loaded directly into the EIP(RIP) register. If the operand size attribute is 16, the upper two bytes of the EIP register are cleared, resulting in a maximum instruction pointer size of 16 bits. When accessing an absolute offset indirectly using the stack pointer [ESP] as the base register, the base value used is the value of the ESP before the instruction executes.

25

A relative offset (*rel16* or *rel32*) is generally specified as a label in assembly code. But at the machine code level, it is encoded as a signed, 16- or 32-bit immediate value. This value is added to the value in the EIP(RIP) register. In 64-bit mode the relative offset is always a 32-bit immediate value which is sign extended to 64-bits before it is added to the value in the RIP register for the target calculation. As with absolute offsets, the operand-size attribute determines the size of the target operand (16, 32, or 64 bits). In 64-bit mode the target operand will always be 64-bits because the operand size is forced to 64-bits for near branches.

**Far Calls in Real-Address or Virtual-8086 Mode.** When executing a far call in real- address or virtual-8086 mode, the processor pushes the current value of both the CS and EIP registers on the stack for use as a return-instruction pointer. The processor then performs a "far branch" to the code segment and offset specified with the target operand for the called procedure. The target operand specifies an absolute far address either directly with a pointer (*ptr16:16* or *ptr16:32*) or indirectly with a memory location (*m16:16* or *m16:32*). With the pointer method, the segment and offset of the called procedure is encoded in the instruction using a 4-byte (16-bit operand size) or 6-byte (32-bit operand size) far address immediate. With the indirect method, the target operand specifies a memory location that contains a 4-byte (16-bit operand size) or 6-byte (32-bit operand size) far address. The operand-size attribute determines the size of the offset (16 or 32 bits) in the far address. The far address is loaded directly into the CS and EIP registers. If the operand-size attribute is 16, the upper two bytes of the EIP register are cleared.

**Far Calls in Protected Mode.** When the processor is operating in protected mode, the CALL instruction can be used to perform the following types of far calls.

- Far call to the same privilege level.

- Far call to a different privilege level (inter-privilege level call).

- Task switch (far call to another task).

In protected mode, the processor always uses the segment selector part of the far address to access the corresponding descriptor in the GDT or LDT. The descriptor type (code segment, call gate, task gate, or TSS) and access rights determine the type of call operation to be performed.

If the selected descriptor is for a code segment, a far call to a code segment at the same privilege level is performed. (If the selected code segment is at a different privilege level and the code segment is non-conforming, a general-protection exception is generated.) A far call to the same privilege level in protected mode is very similar to one carried out in real-address or virtual-8086 mode. The target operand specifies an absolute far address either directly with a pointer (ptr16:16 or ptr16:32) or indirectly with a memory location (m16:16 or m16:32). The operand- size attribute determines the size of the offset (16 or 32 bits) in the far address. The new code segment selector and its descriptor are loaded into CS register; the offset from the instruction is loaded into the EIP register.

A call gate (described in the next paragraph) can also be used to perform a far call to a code segment at the same privilege level. Using this mechanism provides an extra level of indirection and is the preferred method of making calls between 16-bit and 32-bit code segments.

When executing an inter-privilege-level far call, the code segment for the procedure being called must be accessed through a call gate. The segment selector specified by the target operand identifies the call gate. The target operand can specify the call gate segment selector either directly with a pointer (ptr16:16 or ptr16:32) or indirectly with a memory location (m16:16 or m16:32). The processor obtains the segment selector for the new code segment and the new instruction pointer (offset) from the call gate descriptor. (The offset from the target operand is ignored when a call gate is used.)

On inter-privilege-level calls, the processor switches to the stack for the privilege level of the called procedure. The segment selector for the new stack segment is specified in the TSS for the currently running task. The branch to the new code segment occurs after the stack switch. (Note that when using a call gate to perform a far call to a segment at the same privilege level, no stack switch occurs.) On the new stack, the processor pushes the segment selector and stack pointer for the calling procedure's stack, an optional set of parameters from the calling procedures stack, and the segment selector and instruction pointer for the calling procedure's code segment. (A value in the call gate descriptor determines how many parameters to copy to the new stack.) Finally, the processor branches to the address of the procedure being called within the new code segment.

Executing a task switch with the CALL instruction is similar to executing a call through a call gate. The target operand specifies the segment selector of the task gate for the new task activated by the switch (the offset in the target operand is ignored). The task gate in turn points to the TSS for the new task, which contains the segment selectors for the task's code and stack segments. Note that the TSS also contains the EIP value for the next instruction that was to be executed before the calling task was suspended. This instruction pointer value is loaded into the EIP register to re-start the calling task.

The CALL instruction can also specify the segment selector of the TSS directly, which eliminates the indirection of the task gate. See Chapter 7, "Task Management," in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A, for information on the mechanics of a task switch.

When you execute at task switch with a CALL instruction, the nested task flag (NT) is set in the EFLAGS register and the new TSS's previous task link field is loaded with the old task's TSS selector. Code is expected to suspend this nested task by executing an IRET instruction which, because the NT flag is set, automatically uses the previous task link to return to the calling task. (See "Task Linking" in Chapter 7 of the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A, for information on nested tasks.) Switching tasks with the CALL instruction differs in this regard from JMP instruction. JMP does not set the NT flag and therefore does not expect an IRET instruction to suspend the task.

**Mixing 16-Bit and 32-Bit Calls.** When making far calls between 16-bit and 32-bit code segments, use a call gate. If the far call is from a 32-bit code segment to a 16-bit code segment, the call should be made from the first 64 KBytes of the 32-bit code segment. This is because the operand-size attribute of the instruction is set to 16, so only a 16-bit return address offset can be saved. Also, the call should be made using a 16-bit call gate so that 16-bit values can be pushed on the stack. See Chapter 21, "Mixing 16-Bit and 32-Bit Code," in the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3B*, for more information.

**Far Calls in Compatibility Mode.** When the processor is operating in compatibility mode, the CALL instruction can be used to perform the following types of far calls.

- Far call to the same privilege level, remaining in compatibility mode.

- Far call to the same privilege level, transitioning to 64-bit mode.

- Far call to a different privilege level (inter-privilege level call), transitioning to 64-bit mode.

Note that a CALL instruction cannot be used to cause a task switch in compatibility mode since task switches are not supported in IA-32e mode.

In compatibility mode, the processor always uses the segment selector part of the far address to access the corresponding descriptor in the GDT or LDT. The descriptor type (code segment, call gate) and access rights determine the type of call operation to be performed.

If the selected descriptor is for a code segment, a far call to a code segment at the same privilege level is performed. (If the selected code segment is at a different privilege level and the code segment is non-conforming, a general-protection exception is generated.) A far call to the same privilege level in compatibility mode is very similar to one carried out in protected mode. The target operand specifies an absolute far address either directly with a pointer (ptr16:16 or ptr16:32) or indirectly with a memory location (m16:16 or m16:32). The operand-size attribute determines the size of the offset (16 or 32 bits) in the far address. The new code segment selector and its descriptor are loaded into CS register and the offset from the instruction is loaded into the EIP register. The difference is that 64-bit mode may be entered. This specified by the L bit in the new code segment descriptor.

Note that a 64-bit call gate (described in the next paragraph) can also be used to perform a far call to a code segment at the same privilege level. However, using this mechanism requires that the target code segment descriptor have the L bit set, causing an entry to 64-bit mode.

When executing an inter-privilege-level far call, the code segment for the procedure being called must be accessed through a 64-bit call gate. The segment selector specified by the target operand identifies the call gate. The target operand can specify the call gate segment selector either directly with a pointer (ptr16:16 or ptr16:32) or indirectly with a memory location (m16:16 or m16:32). The processor obtains the segment selector for the new code segment and the new instruction pointer (offset) from the 16-byte call gate descriptor. (The offset from the target operand is ignored when a call gate is used.)

27

On inter-privilege-level calls, the processor switches to the stack for the privilege level of the called procedure. The segment selector for the new stack segment is set to NULL. The new stack pointer is specified in the TSS for the currently running task. The branch to the new code segment occurs after the stack switch. (Note that when using a call gate to perform a far call to a segment at the same privilege level, an implicit stack switch occurs as a result of entering 64-bit mode. The SS selector is unchanged, but stack segment accesses use a segment base of 0x0, the limit is ignored, and the default stack size is 64-bits. The full value of RSP is used for the offset, of which the upper 32-bits are undefined.) On the new stack, the processor pushes the segment selector and stack pointer for the calling procedure's stack and the segment selector and instruction pointer for the calling procedure's code segment. (Parameter copy is not supported in IA-32e mode.) Finally, the processor branches to the address of the procedure being called within the new code segment.

**Near/(Far) Calls in 64-bit Mode.** When the processor is operating in 64-bit mode, the CALL instruction can be used to perform the following types of far calls

- Far call to the same privilege level, transitioning to compatibility mode.

- Far call to the same privilege level, remaining in 64-bit mode.

- Far call to a different privilege level (inter-privilege level call), remaining in 64-bit mode.

Note that in this mode the CALL instruction cannot be used to cause a task switch in 64-bit mode since task switches are not supported in IA-32e mode.

In 64-bit mode, the processor always uses the segment selector part of the far address to access the corresponding descriptor in the GDT or LDT. The descriptor type (code segment, call gate) and access rights determine the type of call operation to be performed.

If the selected descriptor is for a code segment, a far call to a code segment at the same privilege level is performed. (If the selected code segment is at a different privilege level and the code segment is non-conforming, a general-protection exception is generated.) A far call to the same privilege level in 64-bit mode is very similar to one carried out in compatibility mode. The target operand specifies an absolute far address indirectly with a memory location (m16:16, m16:32 or m16:64). The form of CALL with a direct specification of absolute far address is not defined in 64-bit mode. The operand-size attribute determines the size of the offset (16, 32, or 64 bits) in the far address. The new code segment selector and its descriptor are loaded into the CS register; the offset from the instruction is loaded into the EIP register. The new code segment may specify entry either into compatibility or 64-bit mode, based on the L bit value.

A 64-bit call gate (described in the next paragraph) can also be used to perform a far call to a code segment at the same privilege level. However, using this mechanism requires that the target code segment descriptor have the L bit set.

When executing an inter-privilege-level far call, the code segment for the procedure being called must be accessed through a 64-bit call gate. The segment selector specified by the target operand identifies the call gate. The target operand can only specify the call gate segment selector indirectly with a memory location (m16:16, m16:32 or m16:64). The processor obtains the segment selector for the new code segment and the new instruction pointer (offset) from the 16-byte call gate descriptor. (The offset from the target operand is ignored when a call gate is used.)

On inter-privilege-level calls, the processor switches to the stack for the privilege level of the called procedure. The segment selector for the new stack segment is set to NULL. The new stack pointer is specified in the TSS for the currently running task. The branch to the new code segment occurs after the stack switch.

Note that when using a call gate to perform a far call to a segment at the same privilege level, an implicit stack switch occurs as a result of entering 64-bit mode. The SS selector is unchanged, but stack segment accesses use a segment base of 0x0, the limit is ignored, and the default stack size is 64-bits. (The full value of RSP is used for the offset.) On the new stack, the processor pushes the segment selector and stack pointer for the calling procedure's stack and the segment selector and instruction pointer for the calling procedure's code segment. (Parameter copy is not supported in IA-32e mode.) Finally, the processor branches to the address of the procedure being called within the new code segment.

#### Operation

```

IF near call

THEN IF near relative call

THEN

IF OperandSize = 64

THEN

tempDEST <-SignExtend(DEST); (* DEST is rel32 *)

tempRIP <- RIP + tempDEST;

IF stack not large enough for a 8-byte return address

THEN #SS(0); FI;

Push(RIP);

IF ShadowStackEnabled(CPL)

ShadowStackPush8B(RIP);

FI;

RIP <- tempRIP;

FI:

IF OperandSize = 32

THEN

tempEIP <- EIP + DEST; (* DEST is rel32 *)

IF tempEIP is not within code segment limit THEN #GP(0); FI;

IF stack not large enough for a 4-byte return address

THEN #SS(0); FI;

Push(EIP);

IF ShadowStackEnabled(CPL)

ShadowStackPush4B(EIP);

FI;

EIP <- tempEIP;

FI;

IF OperandSize = 16

THEN

tempEIP <- (EIP + DEST) AND 0000FFFFH; (* DEST is rel16 *)

IF tempEIP is not within code segment limit THEN #GP(0); FI;

IF stack not large enough for a 2-byte return address

THEN #SS(0); FI;

Push(IP);

IF ShadowStackEnabled(CPL)

(* IP is zero extended and pushed as a 32 bit value on shadow stack *)

ShadowStackPush4B(IP);

FI;

EIP <- tempEIP;

FI:

ELSE (* Near absolute call *)

IF OperandSize = 64

THEN

tempRIP <- DEST; (* DEST is r/m64 *)

IF stack not large enough for a 8-byte return address

THEN #SS(0); FI;

Push(RIP);

IF ShadowStackEnabled(CPL)

```

```

ShadowStackPush8B(RIP);

FI;

RIP <- tempRIP;

FI;

IF OperandSize = 32

THEN

tempEIP <- DEST; (* DEST is r/m32 *)

IF tempEIP is not within code segment limit THEN #GP(0); FI;

IF stack not large enough for a 4-byte return address

THEN #SS(0); FI;

Push(EIP);

IF ShadowStackEnabled(CPL)

ShadowStackPush4B(EIP);

FI;

EIP <- tempEIP;

FI;

IF OperandSize = 16

THEN

tempEIP <- DEST AND 0000FFFFH; (* DEST is r/m16 *)

IF tempEIP is not within code segment limit THEN #GP(0); FI;

IF stack not large enough for a 2-byte return address

THEN #SS(0); FI;

Push(IP);

IF ShadowStackEnabled(CPL)

(* IP is zero extended and pushed as a 32 bit value on shadow stack *)

ShadowStackPush4B(IP);

FI;

EIP <- tempEIP;

FI;

FI;rel/abs

IF (Call near indirect, absolute indirect)

IF EndbranchEnabledAndNotSuppressed(CPL)

IF CPL = 3

THEN

IF ( no 3EH prefix OR IA32_U_CET.NO_TRACK_EN == 0 )

THEN

IA32 U CET.TRACKER = WAIT FOR ENDBRANCH

ELSE

IF (no 3EH prefix OR IA32 S CET.NO TRACK EN == 0)

THEN

IA32_S_CET.TRACKER = WAIT_FOR_ENDBRANCH

FΙ

FI;

FI;

FI;

FI; near

IF far call and (PE = 0 or (PE = 1 and VM = 1)) (* Real-address or virtual-8086 mode *)

THEN

```

30

```

IF OperandSize = 32

THEN

IF stack not large enough for a 6-byte return address

THEN #SS(0); FI;

IF DEST[31:16] is not zero

THEN #GP(0); FI;

Push(CS); (* Padded with 16 high-order bits *)