# Arm<sup>®</sup> Architecture Reference Manual Supplement Armv9, for Armv9-A architecture profile

Document number DDI0608

Document version A.a

Document confidentiality Non-confidential

Document build information Printed on: May 21, 2021.

Copyright © 2021 Arm Limited or its affiliates. All rights reserved.

# **Release information**

| Date       | Version | Changes                                                                                 |

|------------|---------|-----------------------------------------------------------------------------------------|

| 2021/May/2 | 20 EAC  | <ul><li>Initial EAC release.</li><li>BRBE, ETE, TME, and TRBE specifications.</li></ul> |

# **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks

Copyright © 2021 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349 version 21.0

# Arm® Architecture Reference Manual Supplement Armv9, for Armv9-A architecture profile

|                       | Release information                                                                |

|-----------------------|------------------------------------------------------------------------------------|

| Part A Preface        |                                                                                    |

| About this supplement |                                                                                    |

| Conventions           |                                                                                    |

|                       | Typographical conventions                                                          |

| Rules-based writing   |                                                                                    |

|                       | Content item identifiers                                                           |

| Additional reading    |                                                                                    |

| Feedback              | Feedback on this supplement                                                        |

| Part B Armv9-A A      | rchitecture Introduction and Overview                                              |

| Chapter B1 Int<br>B1. | roduction to the Armv9-A Architecture  1 Architectural extensions added by Armv9-A |

| Part C The Transa     | ctional Memory Extension                                                           |

|                       | ansactional Memory Extension                                                       |

| C1                    | .1 Transactions                                                                    |

| C1                    | C1.2.1       Failure causes                                                        |

|            |                                         | C1.3.2           | Atomicity                                              | 25   |

|------------|-----------------------------------------|------------------|--------------------------------------------------------|------|

|            |                                         |                  | Atomicity                                              |      |

|            | C1.4                                    |                  | actions and memory attributes                          |      |

|            | C1.5                                    |                  | ss translation                                         |      |

|            |                                         | C1.5.1           | Transactional translation table walks                  |      |

|            |                                         | C1.5.2           | Hardware management of the Access flag and dirty state |      |

|            |                                         | C1.5.3           | TLB shoot-down                                         |      |

|            |                                         | C1.5.4           | Translation table modifications inside transactions    |      |

|            | C1.6                                    |                  | cation of instructions in Transactional state          |      |

|            | C1.7                                    |                  | upt masking                                            |      |

|            | C1.8                                    | A64 ir           | nstruction behavior in Transactional state             | . 41 |

|            | (                                       | C1.8.1           | MRS                                                    | . 42 |

|            | (                                       | C1.8.2           | MSR (register)                                         | 43   |

|            | (                                       | C1.8.3           | MSR (immediate)                                        | 43   |

|            | (                                       | C1.8.4           | SYS and SYSL                                           | 43   |

|            | (                                       | C1.8.5           | Wait for Event                                         | 43   |

|            | (                                       | C1.8.6           | DMB                                                    | . 44 |

|            |                                         | C1.8.7           | ISB                                                    |      |

|            | (                                       | C1.8.8           | First-fault and Non-fault load instructions            | . 44 |

|            | C1.9                                    |                  |                                                        |      |

|            | C1.10                                   |                  | ication mechanism                                      | _    |

|            | • • • • • • • • • • • • • • • • • • • • |                  |                                                        |      |

| Chapter C2 | Debu                                    | g, PMU           | , Trace                                                |      |

| •          | C2.1                                    |                  | osted debug                                            | . 48 |

|            | (                                       | C2.1.1           | Breakpoint Instruction exceptions                      |      |

|            | (                                       | C2.1.2           | Breakpoint exceptions                                  |      |

|            |                                         | C2.1.3           | Watchpoint exceptions                                  |      |

|            |                                         | C2.1.4           | Software Step exceptions                               |      |

|            | C2.2                                    |                  | nal debug                                              |      |

|            | _                                       | C2.2.1           | Breakpoint and Watchpoint debug events                 |      |

|            |                                         | C2.2.2           | Halting Instruction debug event                        |      |

|            |                                         | C2.2.3           | Halting Step debug events                              |      |

|            |                                         | C2.2.4           | External Debug Request debug event                     |      |

|            |                                         | C2.2.5           | Reset Catch debug event                                |      |

|            |                                         | C2.2.6           | Other Halting debug events                             |      |

|            |                                         | C2.2.7           | Behavior in Debug state                                |      |

|            |                                         | C2.2.7           | The PC Sample-based Profiling Extension                |      |

|            | C2.3                                    |                  | tatistical Profiling Extension                         |      |

|            |                                         | C2.3.1           |                                                        |      |

|            |                                         | C2.3.1           | Memory accesses by profiling operations                |      |

|            |                                         | C2.3.2<br>C2.3.3 | Events packet payload                                  |      |

|            | C2.4                                    |                  | mbedded Trace Extension                                |      |

|            | C2.4                                    |                  | erformance Monitors Extension                          |      |

|            |                                         | C2.5.1           |                                                        |      |

|            |                                         |                  | Event filtering                                        |      |

|            |                                         | C2.5.2           | Accuracy of event filtering                            |      |

|            |                                         | C2.5.3           | TSTART_RETIRED                                         |      |

|            |                                         | C2.5.4           | TCOMMIT_RETIRED                                        |      |

|            |                                         | C2.5.5           | TME_TRANSACTION_FAILED                                 |      |

|            |                                         | C2.5.6           | TME_INST_RETIRED_COMMITTED                             |      |

|            |                                         | C2.5.7           | TME_CPU_CYCLES_COMMITTED                               |      |

|            |                                         | C2.5.8           | TME_FAILURE_CNCL                                       |      |

|            |                                         | C2.5.9           | TME_FAILURE_ERR                                        |      |

|            |                                         | C2.5.10          | TME_FAILURE_IMP                                        |      |

|            |                                         | C2.5.11          | TME_FAILURE_MEM                                        |      |

|            |                                         | C2.5.12          | TME FAILURE NEST                                       | . 57 |

|            |                                         | ·                | TME_FAILURE_SIZE                                       | . 58 |

|                          | C2.5.14 TME_FAILURE_TLBI                                                                                                                                                                                                                                                                                                                    |                                                                      |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Chapter C3               |                                                                                                                                                                                                                                                                                                                                             | 50                                                                   |

| Chapter C3               | C3.1.1 CTR_EL0  C3.1.2 ID_AA64ISAR0_EL1  C3.1.3 TCR_EL1  C3.1.4 TCR_EL2  C3.1.5 ISS encoding for an exception from a TSTART instruction  C3.1.6 SCTLR_EL1  C3.1.7 SCTLR_EL2  C3.1.8 SCTLR_EL3  C3.1.9 HCR_EL2  C3.1.10 SCR_EL3  C3.2 Performance Monitors registers  C3.2.1 PMEVTYPER <n>_EL0  C3.2.2 PMCCFILTR_EL0  C3.2.3 PMSEVFR_EL1</n> | 60<br>60<br>60<br>61<br>62<br>64<br>65<br>66<br>67<br>67<br>67<br>67 |

|                          | •                                                                                                                                                                                                                                                                                                                                           | 68                                                                   |

| Chapter C4               |                                                                                                                                                                                                                                                                                                                                             | 70<br>71                                                             |

| a a-                     | C4.3 TSTART                                                                                                                                                                                                                                                                                                                                 | 72<br>73                                                             |

| Chapter C5               | C4.3 TSTART                                                                                                                                                                                                                                                                                                                                 |                                                                      |

| Chapter C5<br>Chapter C6 | C4.3 TSTART                                                                                                                                                                                                                                                                                                                                 |                                                                      |

| Chapter C6               | C4.3 TSTART                                                                                                                                                                                                                                                                                                                                 |                                                                      |

| Chapter C6               | C4.4 TTEST  Interaction with Memory Tagging Extension  Transactional Memory Extension additional reading  Dedded Trace Extension  Embedded Trace Extension  D1.1 Introduction                                                                                                                                                               | 73                                                                   |

|            |        |             | om Element                        |       |

|------------|--------|-------------|-----------------------------------|-------|

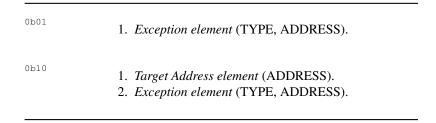

|            |        |             | ception Element                   |       |

|            |        | D2.2.3 Sc   | ource Address Element             |       |

|            |        | D2.2.4 Q    | Element                           |       |

|            |        | D2.2.5 Tra  | ansaction Start Element           | . 98  |

|            | D2.3   | Virtual A   | ddress Space Elements             |       |

|            |        | D2.3.1 Tra  | ace On Element                    | . 99  |

|            |        | D2.3.2 Ta   | rget Address Element              | . 99  |

|            |        | D2.3.3 Co   | ontext Element                    | . 99  |

|            | D2.4   | Temporal    | Elements                          | . 100 |

|            |        | D2.4.1 Cy   | cle Count Element                 | . 100 |

|            |        | D2.4.2 Tir  | mestamp Element                   | . 100 |

|            |        | D2.4.3 Tir  | mestamp Marker element            | . 101 |

|            | D2.5   | Speculati   | on Resolution Elements            | . 102 |

|            |        | D2.5.1 Co   | ommit Element                     | . 102 |

|            |        | D2.5.2 Ca   | ancel Element                     | . 103 |

|            |        |             | scard Element                     |       |

|            |        |             | spredict Element                  | . 103 |

|            | D2.6   |             |                                   |       |

|            | _      |             | vent Element                      |       |

|            |        | _           | verflow Element                   |       |

|            | D2.7   |             | onal Memory                       |       |

|            |        |             | ansaction Start element           |       |

|            |        |             | ansaction Commit element          |       |

|            |        |             | ansaction Commit element          |       |

|            |        | J2.7.3 II   | ansaction randre element          | . 105 |

| Chapter D3 | Instru | ction and   | Exception classifications         |       |

|            | D3.1   | AArch64     | •                                 | 107   |

|            | _      |             | rect P0 instructions              |       |

|            |        |             | direct P0 instructions            |       |

|            |        |             | anch with link instructions       |       |

|            |        |             | eaning of Atom elements           |       |

|            | D3.2   |             | A32                               |       |

|            |        |             | rect P0 instructions              |       |

|            |        |             | direct P0 instructions            |       |

|            |        |             |                                   |       |

|            |        |             | anch with link instructions       |       |

|            |        |             | eaning of Atom elements           |       |

|            | D3.3   |             | T32                               |       |

|            |        |             | rect P0 instructions              |       |

|            |        |             | direct P0 instructions            |       |

|            |        |             | anch with link instructions       |       |

|            |        |             | eaning of Atom elements           |       |

|            | D3.4   |             | WFE Instructions                  |       |

|            |        |             | FxT                               |       |

|            |        |             | eaning of Atom elements           |       |

|            | D3.5   | Exception   | ns to Exception element encodings | . 113 |

| 01 . D4    | _      |             |                                   |       |

| Chapter D4 |        |             | Configurations                    |       |

|            | D4.1   | Configura   | ations                            | . 116 |

| Chantar DE | Duete  | ool Doos    | intion                            |       |

| Chapter D5 |        | col Descr   | •                                 |       |

|            | D5.1   |             | on                                |       |

|            | D5.2   | -           | /                                 |       |

|            | D5.3   |             | Schemes                           |       |

|            |        | D5.3.1 Fie  | ald anaddings                     | 101   |

|            |        | ا ا ، ا ، ا | eld encodings                     | . 121 |

| [     | 05.3.2 Instruction set encoding                  |

|-------|--------------------------------------------------|

| D5.4  | Alignment Synchronization Packet                 |

| D5.5  | Discard Packet                                   |

| D5.6  | Overflow Packet                                  |

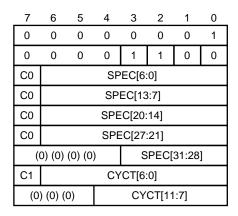

| D5.7  | Trace Info Packet                                |

| D5.8  | Trace On Packet                                  |

| D5.9  | Timestamp Packet                                 |

| D5.10 | Timestamp Marker Packet                          |

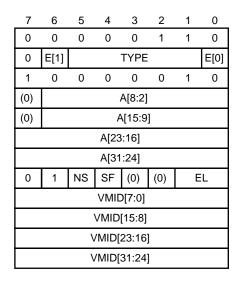

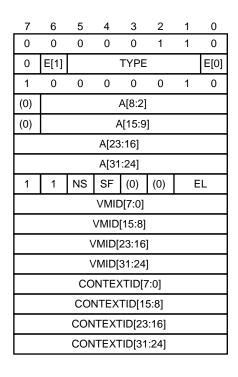

| D5.11 | Transaction Start Packet                         |

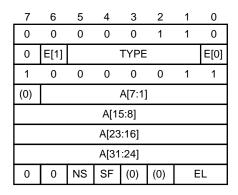

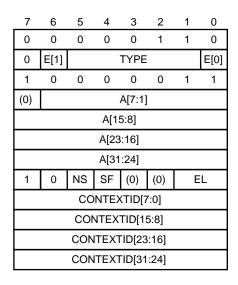

| D5.12 | Transaction Commit Packet                        |

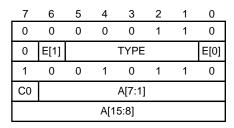

| D5.13 | Exception Exact Match Address Packet             |

| D5.14 | Exception Short Address ISO Packet               |

| D5.15 | Exception Short Address IS1 Packet               |

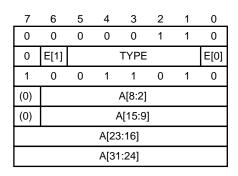

| D5.16 | Exception 32-bit Address ISO Packet              |

| D5.17 | Exception 32-bit Address IS1 Packet              |

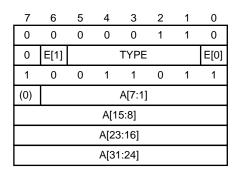

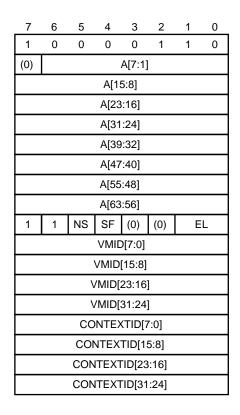

| D5.18 | Exception 64-bit Address ISO Packet              |

| D5.19 | Exception 64-bit Address IS1 Packet              |

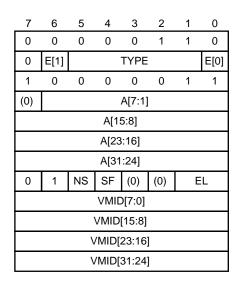

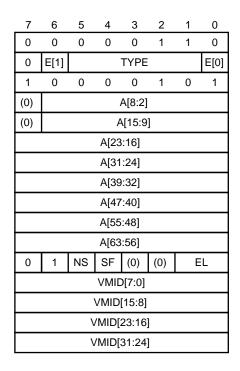

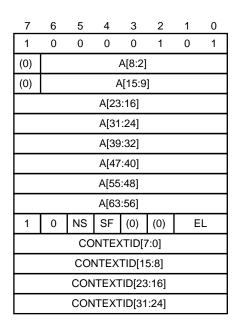

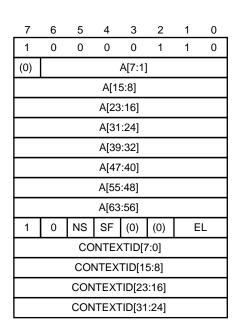

| D5.20 | Exception 32-bit Address IS0 with Context Packet |

| D5.21 | Exception 32-bit Address IS1 with Context Packet |

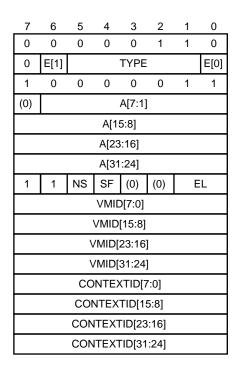

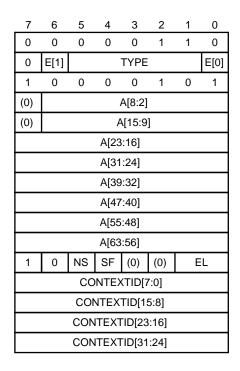

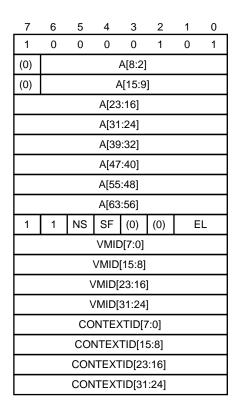

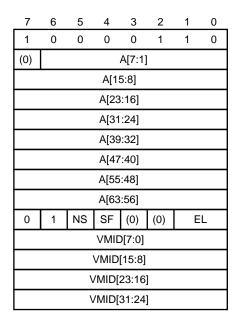

| D5.22 | Exception 64-bit Address IS0 with Context Packet |

| D5.23 | Exception 64-bit Address IS1 with Context Packet |

| D5.24 | Transaction Failure Packet                       |

| D5.25 | PE Reset Packet                                  |

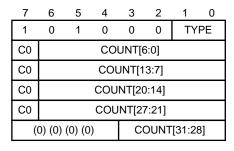

| D5.26 | Cycle Count Format 1_0 unknown count Packet      |

| D5.27 | Cycle Count Format 1_1 unknown count Packet      |

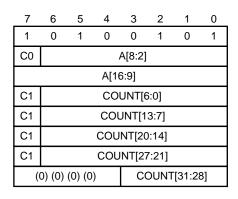

| D5.28 | Cycle Count Format 1_0 with count Packet         |

| D5.29 | Cycle Count Format 1_1 with count Packet         |

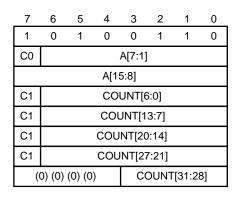

| D5.30 | Cycle Count Format 2_0 small commit Packet       |

| D5.31 | Cycle Count Format 2_0 large commit Packet       |

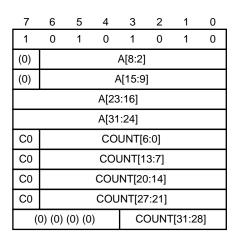

| D5.32 | Cycle Count Format 2_1 Packet                    |

| D5.33 | Cycle Count Format 3_0 Packet                    |

| D5.34 | Cycle Count Format 3_1 Packet                    |

| D5.35 | Commit Packet                                    |

| D5.36 | Cancel Format 1 Packet                           |

| D5.37 | Cancel Format 2 Packet                           |

| D5.38 | Cancel Format 3 Packet                           |

| D5.39 | Mispredict Packet                                |

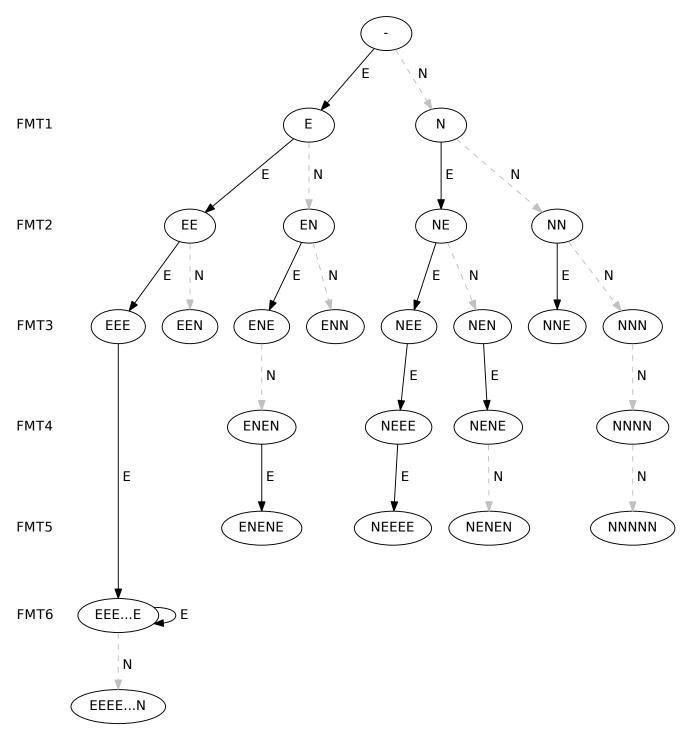

| D5.40 | Atom Format 1 Packet                             |

| D5.41 | Atom Format 2 Packet                             |

| D5.42 | Atom Format 3 Packet                             |

| D5.43 | Atom Format 4 Packet                             |

| D5.44 | Atom Format 5.1 Packet                           |

| D5.45 | Atom Format 5.2 Packet                           |

| D5.46 | Atom Format 6 Packet                             |

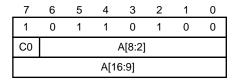

| D5.47 | Target Address Short ISO Packet                  |

| D5.48 | Target Address Short IS1 Packet                  |

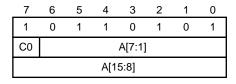

| D5.49 | Target Address 32-bit IS0 Packet                 |

| D5.50 | Target Address 32-bit IS1 Packet                 |

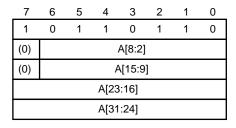

| D5.51 | Target Address 64-bit IS0 Packet                 |

| D5.52 | Target Address 64-bit IS1 Packet                 |

| D5.53 | Target Address Exact Match Packet                |

| D5.54 | Context Same Packet                              |

| D5.55 | Context Packet                                   |

| D5.56 | Target Address with Context 32-bit IS0 Packet    |

| D5.57 | Target Address with Context 32-bit IS1 Packet    |

|            | D5.58 | Target Address with Context 64-bit IS0 Packet                      |

|------------|-------|--------------------------------------------------------------------|

|            | D5.59 | Target Address with Context 64-bit IS1 Packet                      |

|            | D5.60 | Source Address Short IS0 Packet                                    |

|            | D5.61 | Source Address Short IS1 Packet                                    |

|            | D5.62 | Source Address 32-bit IS0 Packet                                   |

|            | D5.63 | Source Address 32-bit IS1 Packet                                   |

|            | D5.64 | Source Address 64-bit IS0 Packet                                   |

|            | D5.65 | Source Address 64-bit IS1 Packet                                   |

|            | D5.66 | Source Address Exact Match Packet                                  |

|            | D5.67 | Ignore Packet                                                      |

|            | D5.68 | Event Packet                                                       |

|            | D5.69 | Q Packet                                                           |

|            | D5.70 | Q with count Packet                                                |

|            | D5.71 | Q with Exact match address Packet                                  |

|            | D5.72 | Q short address IS0 Packet                                         |

|            | D5.73 | Q short address IS1 Packet                                         |

|            | D5.74 | Q 32-bit address IS0 Packet                                        |

|            | D5.75 | Q 32-bit address IS1 Packet                                        |

|            |       |                                                                    |

| Chapter D6 | Trace | Unit                                                               |

| -          | D6.1  | Resetting the trace unit                                           |

|            |       | 06.1.1 Trace unit reset                                            |

|            | D6.2  | System Behaviors                                                   |

|            |       | 06.2.1 Behavior on enabling                                        |

|            |       | 06.2.2 Behavior on disabling                                       |

|            | С     | 06.2.3 Behavior on flushing                                        |

|            | С     | 06.2.4 Low-power state                                             |

|            | С     | 06.2.5 Trace unit behavior when the PE is in a low-power state 253 |

|            | С     | 06.2.6 Trace unit behavior in the low-power state                  |

|            | D6.3  | Trace unit behavior while the PE is in Debug state                 |

|            | D6.4  | Trace unit behavior on a trace unit buffer overflow                |

|            | D6.5  | Trace unit power states                                            |

|            | D6.6  | Visibility of the PE operation                                     |

|            | С     | 06.6.1 ETE trace operation                                         |

|            | С     | 06.6.2 Impact on PE Behavior                                       |

|            | Г     | 06.6.3 Behavior on a PE Warm reset                                 |

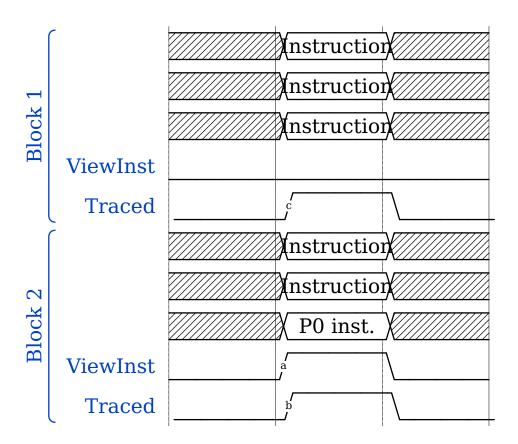

|            |       | 06.6.4 Instruction Block                                           |

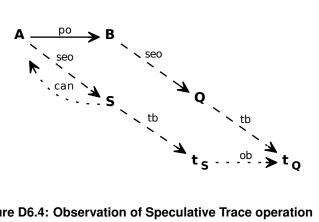

|            |       | 06.6.5 Exposing Speculation                                        |

|            |       | 06.6.6 Prohibited Regions                                          |

|            |       | 06.6.7 Multi-threaded processor                                    |

|            |       | 06.6.8 Sharing between multiple PEs                                |

|            | D6.7  | Speculation resolution                                             |

|            |       | 06.7.1 Initialization                                              |

|            |       | 06.7.2 New block operation                                         |

|            |       | 06.7.3 Resolved operation                                          |

|            |       | 06.7.4 Cancel operation                                            |

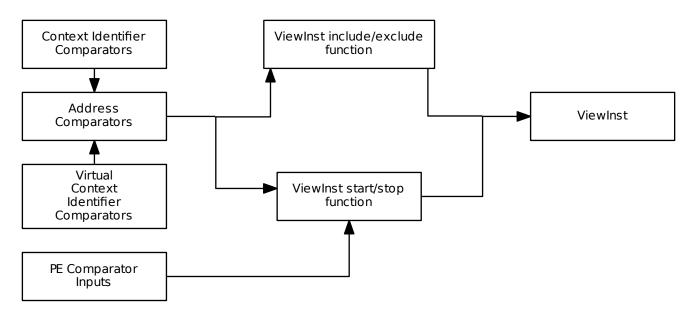

|            | D6.8  | Filtering trace generation                                         |

|            |       | 06.8.1 ViewInst function                                           |

|            |       |                                                                    |

|            |       | ·                                                                  |

|            |       | 06.8.3 ViewInst include/exclude function filtering                 |

|            |       | 26.8.4 Guidelines for interpreting the ViewInst function result    |

|            |       | 06.8.5 Rules for tracing Exceptional occurrences                   |

|            |       | 06.8.6 Forced tracing of Exceptional occurrences                   |

|            | D6.9  | Element Generation                                                 |

|            | Ľ     | 06.9.1 Trace Info Element Generation                               |

|            | ₽6.9.2           | Atom Element                                           |

|------------|------------------|--------------------------------------------------------|

|            | D6.9.3           | Exception Element                                      |

|            | D6.9.4           | Source Address Element                                 |

|            | D6.9.5           | Q Element                                              |

|            | D6.9.6           | Event Element                                          |

|            | D6.9.7           | Cancel Element Generation                              |

|            | D6.9.8           | Commit Element Generation                              |

|            | D6.9.9           | Transaction Start                                      |

|            | D6.9.10          | Transaction Commit                                     |

|            | D6.9.11          | Transaction Failure                                    |

|            | D6.9.12          |                                                        |

|            | D6.9.12          |                                                        |

|            | D6.9.14          |                                                        |

|            |                  |                                                        |

|            | D6.9.15          |                                                        |

|            | D6.9.16          | F                                                      |

|            | D6.9.17          |                                                        |

|            | D6.9.18          | •                                                      |

|            | D6.9.19          |                                                        |

|            | D6.10 Trace      | e unit features                                        |

|            | D6.10.1          | Branch broadcasting                                    |

|            | D6.10.2          | Q Regions                                              |

|            | D6.10.3          | Cycle Counting                                         |

|            | D6.10.4          | Timestamping                                           |

|            | D6.10.5          |                                                        |

|            | D6.10.6          | <u> </u>                                               |

|            | D6.10.7          | Event Trace                                            |

|            | D6.10.8          |                                                        |

|            | D6.10.9          | · · · · · · · · · · · · · · · · · · ·                  |

|            |                  | pression                                               |

|            | D6.11.1          |                                                        |

|            |                  | ·                                                      |

|            |                  | Atom packing                                           |

|            | D6.11.3          | <b>.</b>                                               |

|            |                  | Return Stack Address Matching                          |

|            | D6.11.5          | Timestamp Value Compression                            |

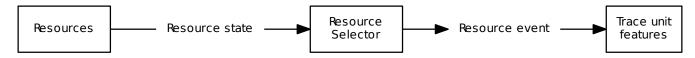

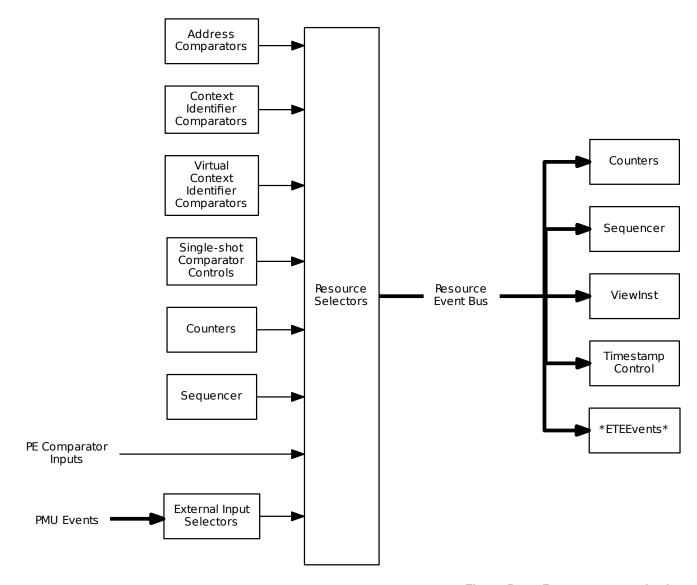

| Chapter D7 | Resources        |                                                        |

| Chapter D1 |                  | OO4                                                    |

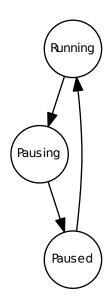

|            |                  | purce operation                                        |

|            | D7.1.1           | Behavior of the resources while in the Running state   |

|            | D7.1.2           | Behavior of the resources while in the Pausing state   |

|            | D7.1.3           | Behavior of the resources while in the Paused state    |

|            | D7.1.4           | Behavior of resources on a Trace synchronization event |

|            |                  | ource organization                                     |

|            | D7.2.1           | Precise Resources                                      |

|            | D7.2.2           | Imprecise Resources                                    |

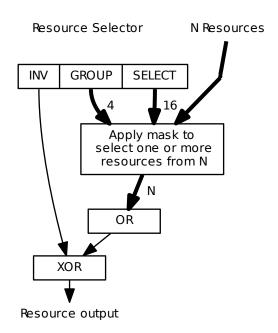

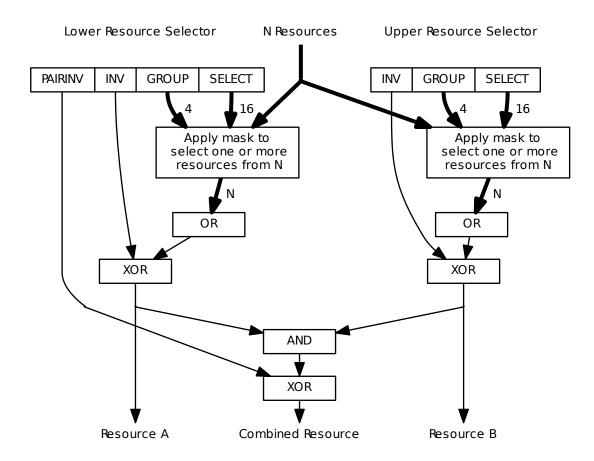

|            | D7.3 Sele        | cting a resource or a pair of resources                |

|            | D7.3.1           | A Resource Selector pair                               |

|            | D7.4 Addr        | ess comparators                                        |

|            | D7.4.1           | Single Address Comparators                             |

|            | D7.4.2           | Address Range Comparators                              |

|            |                  | ext Identifier Comparator                              |

|            |                  | al Context Identifier Comparators                      |

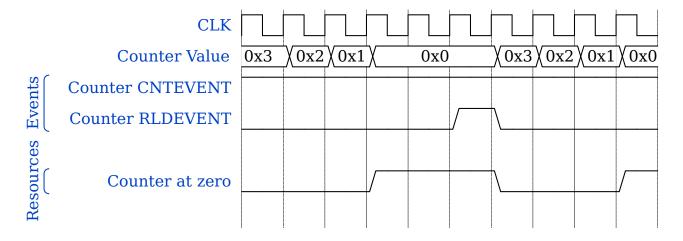

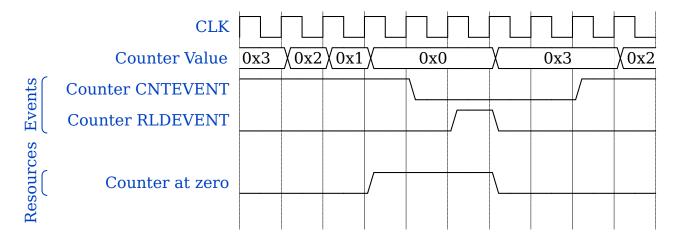

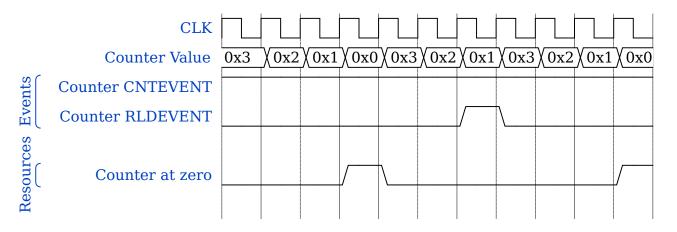

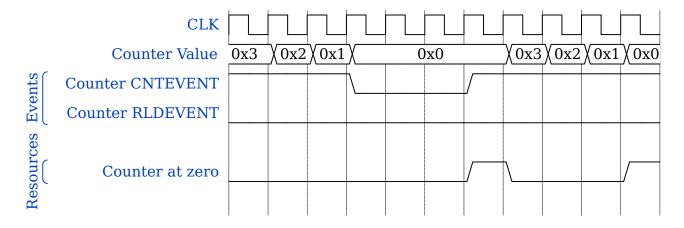

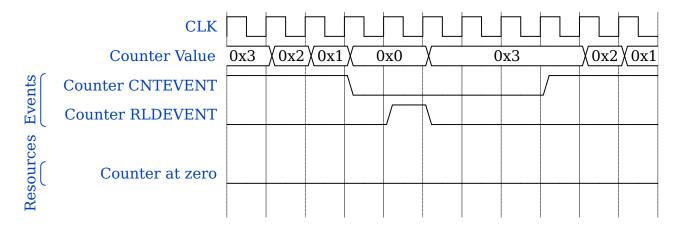

|            |                  | nters                                                  |

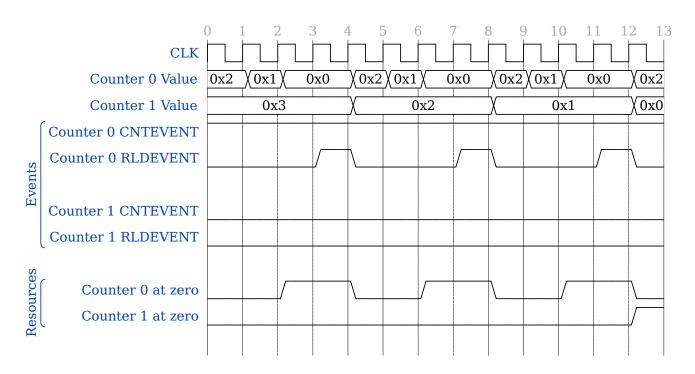

|            | D7.7 0001        | Forming a larger Counter from two separate Counters    |

|            | D7.7.1<br>D7.7.2 | Counter Operation in Self-reload mode                  |

|            |                  | ·                                                      |

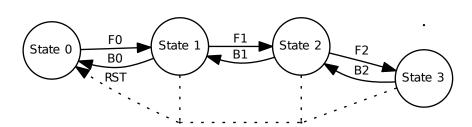

|            | o. seqt          | uencer                                                 |

|            |                  |                                                        |

|            | D7.8.1 Pseudocode                                                                 | 26 |

|------------|-----------------------------------------------------------------------------------|----|

|            | D7.9 Single-shot Comparator Controls                                              | 30 |

|            | D7.9.1 Single-shot Comparator Control modes                                       | 31 |

|            | D7.9.2 Operation while in Paused state                                            |    |

|            | D7.10 External Outputs                                                            | 33 |

|            | D7.10.1 Operation while in Paused state                                           |    |

|            | D7.11 External Inputs                                                             |    |

|            | D7.11.1 Operation while in Paused state                                           |    |

|            | D7.11.2 Operation while in the Low-power state                                    |    |

|            | D7.12 PE Comparator Inputs                                                        | 36 |

| Chapter D8 | Register Description                                                              |    |

|            | D8.1 Accessing ETE registers                                                      |    |

|            | D8.1.1 External debugger interface                                                |    |

|            | D8.1.2 System instructions                                                        |    |

|            | D8.2 Synchronization of register updates                                          |    |

|            | D8.2.1 AArch64 system registers                                                   |    |

|            | D8.2.2 External Debugger registers                                                |    |

|            | D8.2.3 Synchronization and the authentication interface                           |    |

|            | D8.3 Trace unit programming states                                                |    |

|            | D8.4 External debug registers                                                     |    |

|            | D8.4.1 Trace registers, external debug register map                               |    |

|            | D8.4.2 Management registers, external debug register map                          |    |

|            | D8.4.3 Integration registers                                                      | 48 |

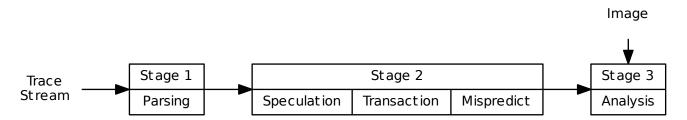

| Chapter D9 | Trace Analyzer                                                                    |    |

| <b>-</b>   | Rules-based writing                                                               | 49 |

|            | D9.1 Introduction                                                                 |    |

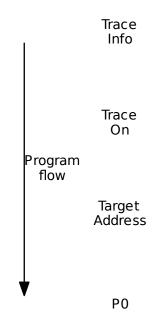

|            | D9.1.1 Using <i>Trace Info elements</i> to start trace analysis                   |    |

|            | D9.1.2 Encountering <i>Trace Info elements</i> after trace analysis has started 3 |    |

|            | D9.1.3 Decompression information                                                  |    |

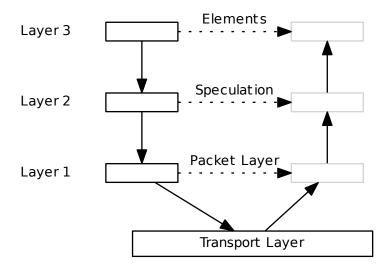

|            | D9.2 Stage 1 - Parsing the byte stream                                            |    |

|            | D9.2.1 Retained state                                                             |    |

|            | D9.2.2 Parsing                                                                    |    |

|            | D9.2.3 Alignment Sync packet                                                      |    |

|            | D9.2.4 Discard                                                                    |    |

|            | D9.2.5 Overflow                                                                   |    |

|            | D9.2.6 Trace Info                                                                 |    |

|            | D9.2.7 Trace On                                                                   |    |

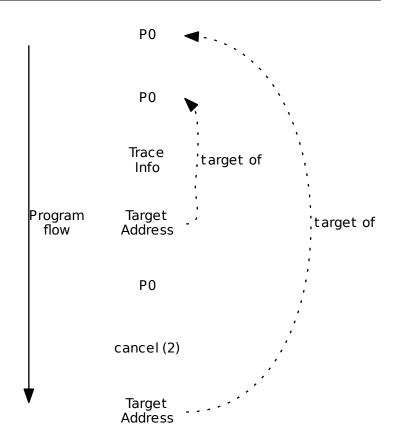

|            | D9.2.8 Speculation                                                                | 56 |

|            | ·                                                                                 | 59 |

|            | ·                                                                                 | 59 |

|            |                                                                                   | 63 |

|            | D9.2.12 Source Address Packets                                                    | 65 |

|            |                                                                                   | 66 |

|            | '                                                                                 | 68 |

|            |                                                                                   | 74 |

|            |                                                                                   | 75 |

|            | ·                                                                                 | 77 |

|            | · · · · · · · · · · · · · · · · · · ·                                             | 78 |

|            |                                                                                   | 80 |

|            | · · · · · · · · · · · · · · · · · · ·                                             | 80 |

|            | D9.3.2 Trace Info element                                                         |    |

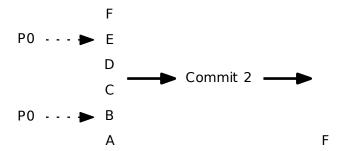

|            | D9.3.3 Commit element                                                             |    |

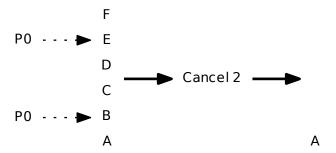

|            | D9.3.4 Cancel element                                                             |    |

|            |                                                                                   | -  |

|              | D9.3.5 Discard element                                                                                                                                                                                                                                                                                                                                         |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | D9.4 Stage 2 - Transaction Resolution                                                                                                                                                                                                                                                                                                                          |

|              | D9.4.1 ProcessTransaction()                                                                                                                                                                                                                                                                                                                                    |

|              | D9.4.2 Transaction Start element                                                                                                                                                                                                                                                                                                                               |

|              | D9.4.3 Transaction Commit element                                                                                                                                                                                                                                                                                                                              |

|              | D9.4.4 Transaction Failure element                                                                                                                                                                                                                                                                                                                             |

|              | D9.5 Stage 3 - Analysis                                                                                                                                                                                                                                                                                                                                        |

|              | D9.5.1 AnalyzeElement()                                                                                                                                                                                                                                                                                                                                        |

|              | D9.5.2 Retained state                                                                                                                                                                                                                                                                                                                                          |

|              | D9.5.3 Operation of the return stack                                                                                                                                                                                                                                                                                                                           |

|              | D9.5.4 Atom element                                                                                                                                                                                                                                                                                                                                            |

|              | D9.5.5 Context element                                                                                                                                                                                                                                                                                                                                         |

|              |                                                                                                                                                                                                                                                                                                                                                                |

|              | D9.5.6 Exception element                                                                                                                                                                                                                                                                                                                                       |

|              |                                                                                                                                                                                                                                                                                                                                                                |

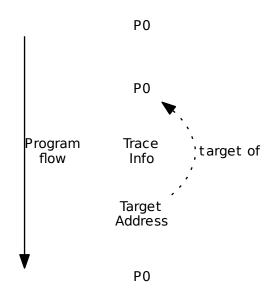

|              | D9.5.8 Target Address element                                                                                                                                                                                                                                                                                                                                  |

|              | D9.5.9 Trace Info element                                                                                                                                                                                                                                                                                                                                      |

|              | D9.5.10 Trace On element                                                                                                                                                                                                                                                                                                                                       |

|              | D9.5.11 Mispredict element                                                                                                                                                                                                                                                                                                                                     |

|              | D9.5.12 ETEEvent element                                                                                                                                                                                                                                                                                                                                       |

|              | D9.5.13 Discard element                                                                                                                                                                                                                                                                                                                                        |

|              | D9.5.14 Overflow element                                                                                                                                                                                                                                                                                                                                       |

|              | D9.5.15 Q element                                                                                                                                                                                                                                                                                                                                              |

|              | D9.5.16 Timestamp element                                                                                                                                                                                                                                                                                                                                      |

|              | D9.5.17 Cycle Count element                                                                                                                                                                                                                                                                                                                                    |

|              | D9.5.18 Functions                                                                                                                                                                                                                                                                                                                                              |

| Chapter D10  | Drogramming                                                                                                                                                                                                                                                                                                                                                    |

| Chapter DT0  | Programming D10.1 Everyple code coguences                                                                                                                                                                                                                                                                                                                      |

|              | D10.1 Example code sequences                                                                                                                                                                                                                                                                                                                                   |

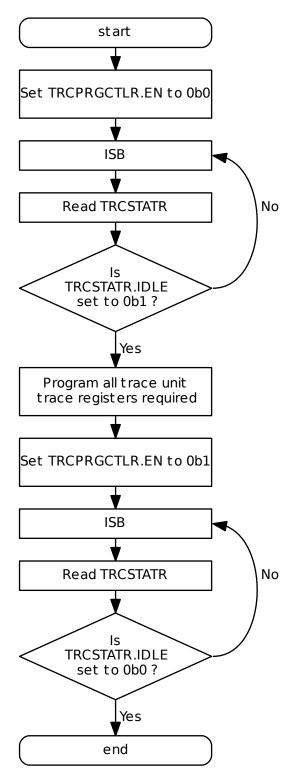

|              | D10.1.1 Enabling the trace unit                                                                                                                                                                                                                                                                                                                                |

|              | D10.1.2 Disabling the trace unit                                                                                                                                                                                                                                                                                                                               |

|              | D10.1.3 Example save restore routine                                                                                                                                                                                                                                                                                                                           |

|              | D10.2 Minimal programming                                                                                                                                                                                                                                                                                                                                      |

|              | D10.3 Filtering models                                                                                                                                                                                                                                                                                                                                         |

|              | D10.4 Filtering used the exclude function                                                                                                                                                                                                                                                                                                                      |

|              | D10.5 Filtering used the include function                                                                                                                                                                                                                                                                                                                      |

|              | D10.6 OS Save and Restore routines                                                                                                                                                                                                                                                                                                                             |

| Chapter D11  | Trace Examples                                                                                                                                                                                                                                                                                                                                                 |

| Chapter Diri | D11.1 Basic Examples                                                                                                                                                                                                                                                                                                                                           |

|              | D11.1.1 Simple example of basic program trace                                                                                                                                                                                                                                                                                                                  |

|              | D11.1.2 Simple example of basic program trace filtering applied 410                                                                                                                                                                                                                                                                                            |

|              | D11.1.2 Simple example of basic program trace filtering applied 410                                                                                                                                                                                                                                                                                            |

|              | D11.2.1 Simple successful transaction                                                                                                                                                                                                                                                                                                                          |

|              |                                                                                                                                                                                                                                                                                                                                                                |

|              | ·                                                                                                                                                                                                                                                                                                                                                              |

|              | D11.2.2 Simple Failed Transaction example                                                                                                                                                                                                                                                                                                                      |

|              | D11.2.2 Simple Failed Transaction example                                                                                                                                                                                                                                                                                                                      |

|              | D11.2.2 Simple Failed Transaction example                                                                                                                                                                                                                                                                                                                      |

| Chanter D12  | D11.2.2 Simple Failed Transaction example                                                                                                                                                                                                                                                                                                                      |

| Chapter D12  | D11.2.2 Simple Failed Transaction example                                                                                                                                                                                                                                                                                                                      |

| Chapter D12  | D11.2.2 Simple Failed Transaction example                                                                                                                                                                                                                                                                                                                      |

| Chapter D12  | D11.2.2 Simple Failed Transaction example       413         D11.2.3 Canceled Transaction failure example       414         D11.2.4 Speculated Transaction example       415         Pseudocode         D12.1 ETE element ASL       416         D12.1.1 Atom enumeration       416                                                                              |

| Chapter D12  | D11.2.2 Simple Failed Transaction example       413         D11.2.3 Canceled Transaction failure example       414         D11.2.4 Speculated Transaction example       415         Pseudocode         D12.1 ETE element ASL       416         D12.1.1 Atom enumeration       416         D12.1.2 AtomElement()       416                                      |

| Chapter D12  | D11.2.2 Simple Failed Transaction example       413         D11.2.3 Canceled Transaction failure example       414         D11.2.4 Speculated Transaction example       415         Pseudocode         D12.1 ETE element ASL       416         D12.1.1 Atom enumeration       416         D12.1.2 AtomElement()       416         D12.1.3 QElement()       417 |

| Chapter D12  | D11.2.2 Simple Failed Transaction example       413         D11.2.3 Canceled Transaction failure example       414         D11.2.4 Speculated Transaction example       415         Pseudocode         D12.1 ETE element ASL       416         D12.1.1 Atom enumeration       416         D12.1.2 AtomElement()       416                                      |

|                  | D12.1.6       ContextElement()       418         D12.1.7       CycleCountElement()       418         D12.1.8       DiscardElement()       419         D12.1.9       ExceptionElement()       419         D12.1.10       EventElement()       420         D12.1.11       DiscardElement()       420         D12.1.12       OverflowElement()       420         D12.1.13       TimestampElement()       420         D12.1.14       TraceOnElement()       421         D12.1.15       TraceOnElement()       421         D12.1.16       TargetAddressElement()       421         D12.1.17       SourceAddressElement()       422         D12.1.18       TransactionStartElement()       422         D12.1.19       TransactionStartElement()       422         D12.1.20       TransactionFailureElement()       422         D12.1.20       TransactionFailureElement()       423         D12.2.1       SubISA enumeration       424         D12.2.2       SubISA enumeration       424         D12.2.1       SubISA enumeration       424         D12.2.2       SynchronisationState enumeration       424         D12.3.1       EndOfStream()       426 |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Chapter D13      | D12.5.2 Zeros()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Part E The Trace | e Buffer Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

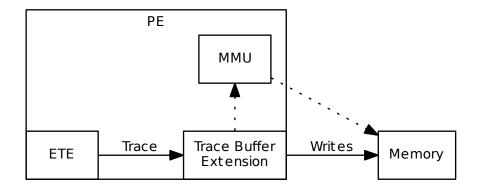

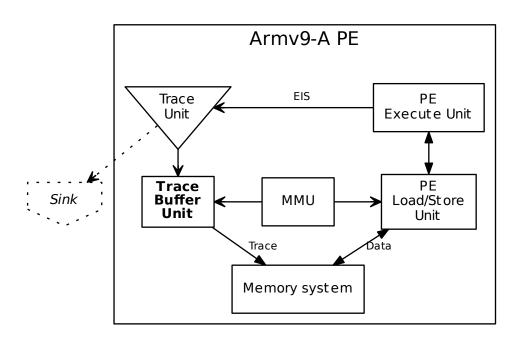

| Chapter E1       | Trace Buffer Extension           E1.1         Description         436           E1.1.1         About the Trace Buffer Extension         436           E1.1.2         System events         438           E1.1.3         Interrupts         438           E1.2         Specification         439           E1.2.1         The trace buffer         439           E1.2.2         Trace buffer management         452           E1.2.3         Synchronization and the Trace Buffer Unit         461           E1.3         Events         474                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                 | E1.3.1 Common microarchitectural events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part F The Bran | ch Record Buffer Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chapter F1      | Branch Record Buffer Extension           F1.1         Branch Record Buffer Extension specification         479           F1.1.1         Branch records         479           F1.1.2         Cycle counting         479           F1.1.3         Mispredicted branches         480           F1.1.4         Prohibited regions         481           F1.1.5         Branch records for exceptions         481           F1.1.6         Branch records for exception returns         482           F1.1.7         Transactional Memory Extension         482           F1.1.8         PE Speculation         483           F1.1.9         Branch record filtering         483           F1.1.10         Branch record buffer operation         487           F1.1.11         Branch record buffer         488           F1.1.12         Invalidating the Record Buffer         489           F1.1.13         Programmers Model         490           F1.2         Events         492           F1.2.1         Common architectural events         492 |

| Part G Appendi  | xes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Chapter G1      | Synchronization requirements for System registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

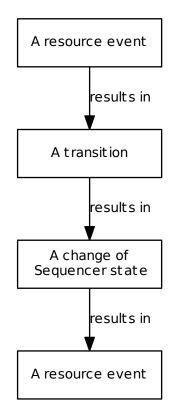

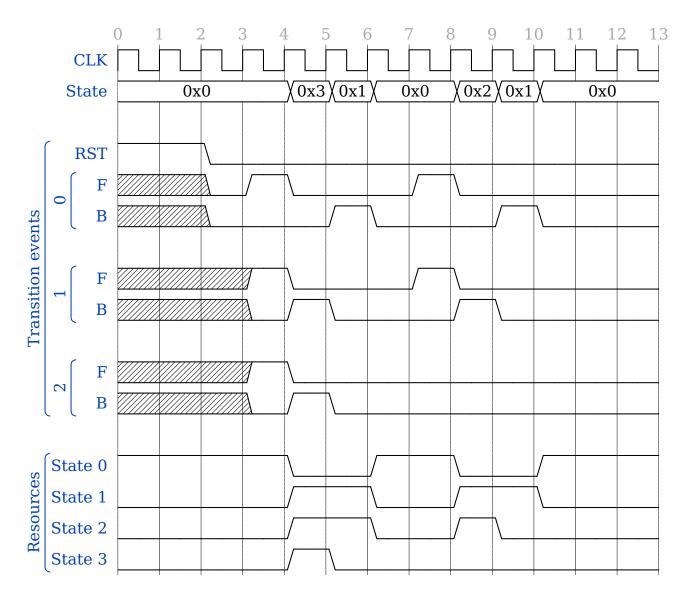

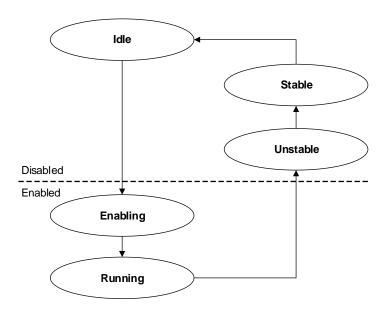

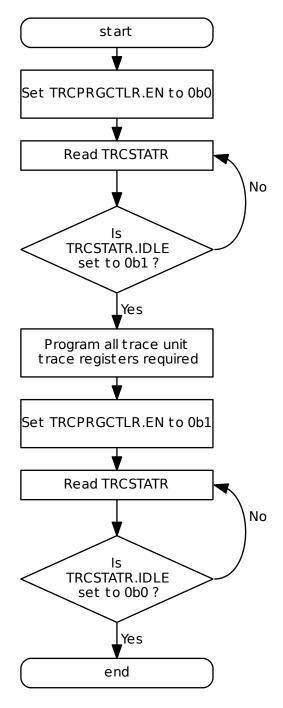

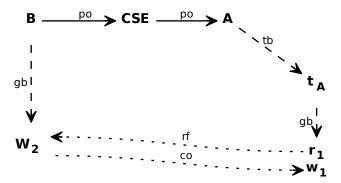

| Chapter G2      | Stages of executionG2.1Stages of execution without Transactional Memory Extension (TME) 499G2.2Stages of execution with TME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |