# Arm<sup>®</sup> Architecture Reference Manual Supplement, Custom Datapath Extension for Armv8-M

# **Release information**

| Date       | Version                           | Changes        |

|------------|-----------------------------------|----------------|

| 17/12/2019 | A.a Non-<br>confidential-<br>Beta | • Beta release |

## Armv8-M Architecture Reference Manual

Copyright © 2015 - 2019 Arm Limited or its affiliates. All rights reserved. The copyright statement reflects the fact that some draft issues of this document have been released, to a limited circulation.

# **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABIL-ITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUD-ING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>TM</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2015 - 2019 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

# **Confidentiality Status**

This document is Non-confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

# **Product Status**

The information in this document is for a Beta product, that is a product under development.

# Web Address

http://www.arm.com

# Contents

# Arm<sup>®</sup> Architecture Reference Manual Supplement, Custom Datapath Extension for Armv8-M

|         | Release information       ii         Armv8-M Architecture Reference Manual       iii |

|---------|--------------------------------------------------------------------------------------|

|         | Proprietary Notice                                                                   |

|         | Confidentiality Status                                                               |

|         | Product Status                                                                       |

|         |                                                                                      |

| Preface |                                                                                      |

|         | Additional reading       viii         Arm publications       viii                    |

# Part A Custom Datapath Extension for the Armv8-M Architecture Introduction and Overview

| Chapter A1 | Intro | duction |                                       |    |

|------------|-------|---------|---------------------------------------|----|

| •          | A1.1  | Docur   | ment layout and terminology           | 11 |

|            |       | A1.1.1  | Structure of the document             | 11 |

|            |       | A1.1.2  | Scope of the document                 | 12 |

|            |       | A1.1.3  | Intended audience                     | 12 |

|            |       | A1.1.4  | Terminology, phrases                  | 12 |

|            |       | A1.1.5  | Terminology, Armv8-M specific terms   | 12 |

|            | A1.2  | The C   | Custom Datapath Extension for Armv8-M | 13 |

|            | A1.3  | Overv   | iew of the Custom Datapath Extension  | 14 |

|            |       |         |                                       |    |

# Part B Custom Datapath Extension for the Armv8-M Architecture, Programmers' Model

| Chapter B1 | Progra | mmers' Model                  |    |

|------------|--------|-------------------------------|----|

| -          | B1.1   | Enabling CDE instructions     | 17 |

|            | B1.2   | Execution of CDE instructions | 18 |

# Part C Instruction Specification

| Chapter C1 | Alphabetica | l list of instructions |

|------------|-------------|------------------------|

| -          | C1.0.1      | CDP, CDP2              |

|            | C1.0.2      | CX1 23                 |

|            | C1.0.3      | CX1D 26                |

|            | C1.0.4      | CX2 28                 |

|            | C1.0.5      | CX2D 30                |

|            | C1.0.6      | CX3 32                 |

|            | C1.0.7      | CX3D 34                |

|            | C1.0.8      | LDC, LDC2 (immediate)  |

|            | C1.0.9      | LDC, LDC2 (literal)    |

|            | C1.0.10     | MCR, MCR2              |

|            | C1.0.11     | MCRR, MCRR2            |

Contents Contents

| C1.0.12 | MRC, MRC2     | 45 |

|---------|---------------|----|

| C1.0.13 | MRRC, MRRC2   | 47 |

| C1.0.14 | STC, STC2     | 49 |

| C1.0.15 | VCX1 (vector) | 52 |

| C1.0.16 | VCX1          | 54 |

| C1.0.17 | VCX2 (vector) | 56 |

| C1.0.18 | VCX2          | 58 |

| C1.0.19 | VCX3 (vector) | 60 |

| C1.0.20 | VCX3          | 62 |

# Part D Pseudocode Specification

| Chapter D1 | Pseudocode | Specification           |

|------------|------------|-------------------------|

| -          | D1.1 Alpha | betical Pseudocode List |

|            | D1.1.1     | CdeImpDefValue          |

|            | D1.1.2     | CoprocType              |

|            | D1.1.3     | CPDef                   |

|            | D1.1.4     | CX_op0 66               |

|            | D1.1.5     | CX_op1 66               |

|            | D1.1.6     | CX_op2 67               |

|            | D1.1.7     | CX_op3 67               |

|            | D1.1.8     | RF                      |

|            | D1.1.9     | RFD                     |

|            | D1.1.10    | VCX_op0 68              |

|            | D1.1.11    | VCX_op1 68              |

|            | D1.1.12    | VCX_op2 69              |

|            | D1.1.13    | VCX_op3 69              |

Glossary

# Preface

This preface introduces the Armv8-M Custom Datapath Extension. It contains the following sections: Introduction to CDE Custom Datapath Extension for the Armv8-M Architecture, Programmers' Model Alphabetical list of instructions Pseudocode Specification

# **Additional reading**

This section lists relevant publications from Arm and third parties. See https://developer.arm.com, for access to Arm documentation.

# **Arm publications**

• Arm<sup>®</sup>v8-M Architecture Reference Manual (ARM DDI 0553B.j)

Part A Custom Datapath Extension for the Armv8-M Architecture Introduction and Overview

# Chapter A1 Introduction

This chapter introduces the Custom Datapath Extension for the Armv8-M architecture. It contains the following sections:

A1.1 Document layout and terminology on page 11.

A1.2 The Custom Datapath Extension for Armv8-M on page 13.

A1.3 Overview of the Custom Datapath Extension on page 14.

# A1.1 Document layout and terminology

This section describes the structure and scope of this supplement. This section also describes the terminology that this supplement uses. It does not constitute part of the supplement, and must not be interpreted as implementation guidance.

## A1.1.1 Structure of the document

This supplement describes the behavior of the Custom Datapath Extension as a set of individual rules.

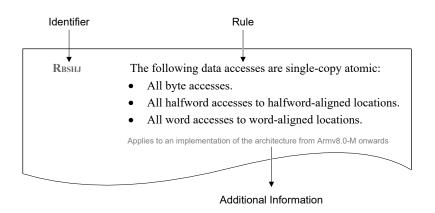

Each rule is clearly identified by the letter R, followed by a random group of subscript letters that do not reflect any intended order or priority, for example  $R_{BSHJ}$ . In the following example,  $R_{BSHJ}$  is simply a random rule identifier that has no significance apart from uniquely identifying a rule in this supplement.

Rules must not be read in isolation, and where more than one rule relating to a particular feature exists, individual rules are grouped into sections and subsections to provide the proper context. Where appropriate, these sections contain a short introduction to aid the reader.

An implementation that conforms to all the rules described in this supplement constitutes an Custom Datapath Extension for Armv8-M compliant implementation. An implementation whose behavior deviates from these rules is not compliant with the Custom Datapath Extension for Armv8-M architecture.

Some sections contain additional information and guidance that do not constitute rules. This information and guidance is provided purely as an aid to understanding the architecture. Information statements are clearly identified by the letter I, followed by a random group of subscript letters, for example I<sub>PRTD</sub>.

#### Note

Arm strongly recommends that implementers read *all* chapters and sections of this document to ensure that an implementation is compliant.

An implementation that conforms to all the rules described in this specification but chooses to ignore any additional information and guidance is compliant with the Armv8-M architecture.

In the following parts of this supplement, architectural rules are not identified by a specific prefix and a random group of subscript letters:

• Part C Custom Datapath Extension for Armv8-M Instruction Set.

## A1.1.2 Scope of the document

This supplement contains only rules and information that relate specifically to the Custom Datapath Extension for Armv8-M architecture. It does not include any information about other Arm architectures, nor does it describe the full details of the Armv8-M architecture.

#### A1.1.3 Intended audience

This supplement is written for users who want to design, implement, or program the Custom Datapath Extension for Armv8-M. This supplement is not a full description of the Armv8-M architecture.

The supplement provides a precise, accurate, and correct set of rules that must be followed in order for a Custom Datapath Extension for Armv8-M implementation to be architecturally compliant. It is an explicit reference supplement, and not a general introduction to, or user guide for, the Custom Datapath Extension for Armv8-M architecture.

## A1.1.4 Terminology, phrases

This subsection identifies some standard words and phrases that are used in the Arm architecture documentation. These words and phrases have an Arm-specific definition, which is described in this section.

#### Architecturally visible

Something that is visible to the controlling agent. The controlling agent might be software.

#### Arm recommends

A particular usage that ensures consistency and usability. Following all the rules listed in this supplement leads to a predictable outcome that is compliant with the architecture, but might produce an unexpected output. Adhering to a recommendation ensures that the output is as expected.

#### Arm strongly recommends

Something that is essentially mandatory, but that is outside the scope of the architecture described in this supplement. Failing to adhere to a strong recommendation can break the system, although the PE itself remains compliant with the architecture that is described in this supplement.

#### **Finite time**

An action will occur at some point in the future. Finite time does not make any statement about the time involved. However, delaying an action longer than is absolutely necessary might have an adverse impact on performance.

#### Permitted

Allowed behavior.

#### Required

Mandatory behavior.

#### Support

The implementation has implemented a particular feature.

## A1.1.5 Terminology, Armv8-M specific terms

For definitions of Custom Datapath Extension specific terms, see the Glossary.

# A1.2 The Custom Datapath Extension for Armv8-M

The Custom Datapath Extension is an OPTIONAL feature available from Armv8-M architecture. An implementation that includes the Custom Datapath Extension must implement the features that are provided by the Main Extension (M), and might implement the following OPTIONAL features:

- The features that are provided by the Floating-point Extension (FP). Instructions that operate on the S or D register file require FP or MVE.

- The features that are provided by the Armv8.1 M-Profile Vector Extension (MVE). Instructions that operate on the Q register file require MVE.

Applies to an implementation of the architecture from Armv8.0-M onwards.

Where applicable, a line below each rule or information statement indicates the extensions that are required for the rule or information statement to apply, and any other notes.

Applies to an implementation of the architecture from Armv8.0-M onwards.

A line below each rule or information statement indicates the architecture version, the extensions that are required for the rule or information statement to apply, and any other notes. Some extensions depend on the implementation of other extensions, for example FP.

Applies to an implementation of the architecture from Armv8.0-M onwards.

# A1.3 Overview of the Custom Datapath Extension

| $I_{QNBG}$        | The Custom Datapath Extension (CDE) for the Armv8-M architecture introduces three classes of two instructions in the co-processor instruction space:                                                                                                                                                                                            |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | <ul> <li>Three classes operate on the general-purpose register file, including the condition code flags APSR_nzcv.</li> <li>Three classes operate on the Floating-point or SIMD register file only.</li> </ul>                                                                                                                                  |

|                   | <i>Applies to an implementation of the architecture from</i> <b>Armv8.0-M</b> <i>onwards. The extension requirements are -</i> <b>CDE</b> <i>. Note, (FP    MVE) required for Floating-point register file. MVE is only available in an Armv8.1-M implementation.</i>                                                                           |

| I <sub>JWBF</sub> | A Custom Datapath instruction operating on the Floating-point or SIMD register files uses one of:                                                                                                                                                                                                                                               |

|                   | <ul> <li>32-bit S registers.</li> <li>64-bit D registers.</li> <li>128-bit Q registers.</li> </ul>                                                                                                                                                                                                                                              |

|                   | Applies to an implementation of the architecture from $Armv8.0-M$ onwards. The extension requirements are - $CDE$ && ( $FP \parallel MVE$ ). Note, $Q$ registers require MVE, MVE is only available in an Armv8.1-M implementation.                                                                                                             |

| $I_{RBLJ}$        | The three classes are defined by the following instruction patterns:                                                                                                                                                                                                                                                                            |

|                   | <ul> <li><operation code=""> <destination register="">.</destination></operation></li> <li><operation code=""> <destination register="">, <source register=""/>.</destination></operation></li> <li><operation code=""> <destination register="">, <source 1="" register=""/>, <source 2="" register=""/>.</destination></operation></li> </ul> |

|                   | Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.                                                                                                                                                                                                                                  |

| I <sub>FZRZ</sub> | The destination register of an instruction might be optionally read, as well as written.                                                                                                                                                                                                                                                        |

|                   | Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.                                                                                                                                                                                                                                  |

| $I_{\rm BXBG}$    | The operation code can be split between a true operation code in the custom datapath and an immediate value used in the custom datapath. The architecture does not prescribe any split.                                                                                                                                                         |

|                   | Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.                                                                                                                                                                                                                                  |

| $I_{\rm NFMB}$    | Immediate consequences of the above are:                                                                                                                                                                                                                                                                                                        |

|                   | <ul> <li>No operations on the Floating-point or SIMD registers can set condition codes.</li> <li>There are no instructions that support the use of all of, or any combination of, S registers, D registers, Q registers and, the general-purpose register file.</li> </ul>                                                                      |

|                   | Applies to an implementation of the architecture from <b>Armv8.0-M</b> onwards. The extension requirements are - <b>CDE</b> . Note, Q registers require MVE, MVE is only available in an Armv8.1-M implementation.                                                                                                                              |

| I <sub>TVRP</sub> | Operations on the general-purpose register file operate on 32-bit registers, or a dual-register consisting of a 64-bit value constructed from an even numbered general-purpose register and its immediately following odd numbered pair.                                                                                                        |

|                   | Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.                                                                                                                                                                                                                                  |

Part B Custom Datapath Extension for the Armv8-M Architecture, Programmers' Model

# Chapter B1 Programmers' Model

This chapter specifies the rules associated with the Custom Datapath Extension (CDE) for Armv8-M. It contains the following sections:

B1.1 Enabling CDE instructions on page 17

B1.2 Execution of CDE instructions on page 18

# **B1.1 Enabling CDE instructions**

**I**<sub>CXBC</sub> Custom Datapath instructions can be found within, and are associated with, the existing coprocessor encoding and numbering spaces.

Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.

**R**<sub>XLTS</sub> Custom Datapath instructions fall into encoding spaces associated with a *coprocessor* number in the range 0 to 7 inclusive.

Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.

**I**<sub>WWNQ</sub> Enabling the coprocessor space in which the Custom Datapath Extension is implemented is the same as other IMPLEMENTATION DEFINED coprocessors. The function IsCPEnabled() describes this.

Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE. Note, S required for Secure state.

- $\mathbb{R}_{VSVW}$  If a coprocessor is associated with the Custom Datapath Extension, that coprocessor cannot execute the following instructions:

- CDP, CDP2.

LDC, LDC2 (immediate).

LDC, LDC2 (literal).

MCR, MCR2.

- MCRR, MCRR2.

- MRC, MRC2.

- MRRC, MRRC2.

- STC, STC2.

Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.

$\mathbb{R}_{SKRX}$  Execution of a Custom Datapath instruction that accesses the Floating-point or SIMD register file causes *Lazy Floating-point stacking* as specified by the architecture.

Applies to an implementation of the architecture from *Armv8.0-M* onwards. The extension requirements are - *CDE* && (*FP* || *MVE*). Note, MVE is only available in an Armv8.1-M implementation.

ImvxwArmv8-M Double-precision Floating-point Extension implements 16 "D" registers, D0 to D15. The instructions<br/>defined by the Custom Datapath Extension are capable of indexing registers D0 to D31.

*Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE* **&&** (*FP* || *MVE*). *Note, MVE is only available in an Armv8.1-M implementation.*

ILPPYArmv8.1-M MVE implements eight "Q" registers, Q0 to Q7. The instructions defined by the Custom Datapath<br/>Extension are capable of indexing registers Q0 to Q15.

Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE && MVE. Note, MVE is only available in an Armv8.1-M implementation.

RLEENN

Execution of a Custom Datapath instruction that attempts to access an unimplemented Floating-point or SIMD register, is CONSTRAINED UNPREDICTABLE and either of the following behaviors can occur:

- The instruction is UNDEFINED.

- The instruction is treated as a NOP.

Applies to an implementation of the architecture from **Armv8.0-M** onwards. The extension requirements are - **CDE** && (**FP** || **MVE**). Note, MVE is only available in an Armv8.1-M implementation.

# **B1.2 Execution of CDE instructions**

| R <sub>QGNK</sub>        | The source and destination registers for any Custom Datapath instruction are restricted to those specified by the instruction pseudocode.                                                                                                                                                       |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.                                                                                                                                                                                  |

| R <sub>GPLC</sub>        | The operation of a Custom Datapath instruction cannot be stateful, and cannot operate directly on memory.                                                                                                                                                                                       |

|                          | Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.                                                                                                                                                                                  |

| R <sub>XFCV</sub>        | It is IMPLEMENTATION DEFINED which Custom Datapath instructions are implemented.                                                                                                                                                                                                                |

|                          | Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.                                                                                                                                                                                  |

| R <sub>SVBN</sub>        | An unimplemented Custom Datapath instruction whose associated coprocessor is not disabled is UNDEFINED.                                                                                                                                                                                         |

|                          | Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.                                                                                                                                                                                  |

| R <sub>SGPM</sub>        | Which coprocessors adhere to the Custom Datapath Extension or the Arm architecture coprocessor instruction set is IMPLEMENTATION DEFINED.                                                                                                                                                       |

|                          | Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.                                                                                                                                                                                  |

| <b>R</b> <sub>DVDG</sub> | If the Performance Monitors Extension is implemented only the instruction counter, Cycle counter and, IMPLE-<br>MENTATION DEFINED counters increment on execution of Custom Datapath Extension instructions. There are no<br>architected PMU events for Custom Datapath Extension instructions. |

|                          | Applies to an implementation of the architecture from <b>Armv8.0-M</b> onwards. The extension requirements are - <b>CDE &amp;&amp; PMU</b> .<br>Note, PMU is only available in an Armv8.1-M implementation.                                                                                     |

| $R_{VPLL}$               | When executing a CDE scalar dual instruction the CDE enabled coprocessor must process general-purpose register pairs according to the PE's current endianness.                                                                                                                                  |

|                          | Applies to an implementation of the architecture from Armv8.0-M onwards. The extension requirements are - CDE.                                                                                                                                                                                  |

| I <sub>RRTS</sub>        | All of the rules required for the M-Profile Vector Extension and the Low Overhead Loop and Branch Future Extension apply to all CDE beat-wise compatible instructions.                                                                                                                          |

|                          | This includes the following, but is not limited to:                                                                                                                                                                                                                                             |

|                          | <ul> <li>Exception continuable behavior.</li> <li>Overlapping of beat-wise instructions.</li> <li>VPT predication.</li> <li>Tail predicated low overhead loops.</li> </ul>                                                                                                                      |

|                          | The CDE instructions are as follows:                                                                                                                                                                                                                                                            |

|                          |                                                                                                                                                                                                                                                                                                 |

- VCX1 (vector)

- VCX2 (vector)

- VCX3 (vector)

*Applies to an implementation of the architecture from* **Armv8.0-M** *onwards. The extension requirements are -* **CDE && MVE && LOB**. *Note,* LOB && MVE *are only available in an* Armv8.1-M *implementation.*

Part C Instruction Specification

# Chapter C1 Alphabetical list of instructions

Instructions relevant to this Extension are listed in this section. For the full list of Armv8-M instruction see Armv8-M Architecture Reference Manual.

#### C1.0.1 CDP, CDP2

Coprocessor Data Processing. Coprocessor Data Processing tells a coprocessor to perform an operation.

If no coprocessor can execute the instruction, a UsageFault exception is generated.

Arm reserves coprocessors CP8 to CP15, and this manual defines the valid instructions when coproc is in this range.

#### **T1**

Armv8-M Main Extension only

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6  | 5  | 4 | 3 | 2  | 1  | 0 | 15 | 14 | 13 | 12 | 11 | 10  | 9   | 8 | 7 | 6    | 5 | 4 | 3 | 2  | 1  | 0 |

|----|----|----|----|----|----|---|---|---|----|----|---|---|----|----|---|----|----|----|----|----|-----|-----|---|---|------|---|---|---|----|----|---|

| 1  | 1  | 1  | 0  | 1  | 1  | 1 | 0 |   | ор | c1 |   |   | CI | Rn |   |    | CI | Rd |    |    | сор | roc |   | ( | opc2 | 2 | 0 |   | CF | ٦m |   |

#### T1 variant

```

CDP{<c>}{<q>} <coproc>, {#}<opc1>, <CRd>, <CRn>, <CRm> {, {#}<opc2>}

```

#### **Decode for this encoding**

```

1 if coproc IN {'100x', '101x', '111x'} then SEE "Floating-point and MVE";

2 if CoprocType(UInt(coproc)) == CP_CDEv1 then SEE "CDE instructions";

3 if !HaveMainExt() then UNDEFINED;

4 cp = UInt(coproc);

```

#### T2

Armv8-M Main Extension only

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5  | 4 | 3 | 2  | 1  | 0 | 15 | 14 | 13 | 12 | 11 | 10  | 9   | 8 | 7 | 6   | 5 | 4 | 3 | 2  | 1 | 0 |  |

|----|----|----|----|----|----|---|---|---|-----|----|---|---|----|----|---|----|----|----|----|----|-----|-----|---|---|-----|---|---|---|----|---|---|--|

| 1  | 1  | 1  | 1  | 1  | 1  | 1 | 0 |   | орс | :1 |   |   | CI | Rn |   |    | CF | ٦d |    |    | сор | roc |   | C | pc2 | 2 | 0 |   | CR | m |   |  |

#### T2 variant

CDP2{<c>}{<q>} <coproc>, {#}<opc1>, <CRd>, <CRn>, <CRm> {, {#}<opc2>}

#### **Decode for this encoding**

```

1 if coproc IN {'100x', '101x', '111x'} then SEE "Floating-point and MVE";

2 if CoprocType(UInt(coproc)) == CP_CDEv1 then SEE "CDE instructions";

3 if !HaveMainExt() then UNDEFINED;

4 cp = UInt(coproc);

```

#### Assembler symbols for all encodings

| <c></c>           | See Standard assembler syntax fields.                                                                       |

|-------------------|-------------------------------------------------------------------------------------------------------------|

| <q></q>           | See Standard assembler syntax fields.                                                                       |

| <coproc></coproc> | Is the name of the coprocessor, encoded in the "coproc" field. The generic coprocessor names are p0 to p15. |

| <opc1></opc1>     | Is a coprocessor-specific opcode, in the range 0 to 15, encoded in the "opc1" field.                        |

| <crd></crd>       | Is the destination coprocessor register, encoded in the "CRd" field.                                        |

| <crn></crn>       | Is the coprocessor register that contains the first operand, encoded in the "CRn" field.                    |

| <crm></crm>       | Is the coprocessor register that contains the second operand, encoded in the "CRm" field.                   |

| <opc2></opc2>     | Is a coprocessor-specific opcode in the range 0 to 7, defaulting to 0 and encoded in the "opc2"             |

|                   | field.                                                                                                      |

## **Operation for all encodings**

```

1 if ConditionPassed() then

2  EncodingSpecificOperations();

3  ExecuteCPCheck(cp);

4  if !Coproc_Accepted(cp, ThisInstr()) then

5      GenerateCoprocessorException();

6  else

7   Coproc_InternalOperation(cp, ThisInstr());

```

#### C1.0.2 CX1

Custom Instruction Class 1. Custom instruction class 1 computes a value based on an immediate, and optionally the destination value, and writes the result to the destination register.

The source and destination registers can be either general-purpose registers or the Condition flags, specified by use of APSR\_nzcv.

#### **T1**

Armv8-M Custom Datapath Extension

| 1! | 5 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4   3 | 2  | 1 | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8 | 7   | 6 | 5 | 4   3 | 3   | 2 | 1 | 0 |

|----|------|----|----|----|----|---|---|---|---|---|-------|----|---|---|----|----|----|----|----|----|------|---|-----|---|---|-------|-----|---|---|---|

| 1  | 1    | 1  | А  | 1  | 1  | 1 | 0 | 0 | 0 |   | 0     | 01 |   |   |    | F  | ۶d |    | 0  | С  | opro | C | op2 | 0 |   |       | орЗ | 3 |   |   |

#### Accumulator variant

Applies when A == 1

CX1A <coproc>, <Rd>, #<imm>

#### Non-accumulator variant

#### Applies when A == 0

CX1 <coproc>, <Rd>, #<imm>

#### **Decode for this encoding**

```

if CoprocType(UInt(coproc)) != CP_CDEv1 then SEE "Coprocessor instructions";

1

if !HaveMainExt()

2

then UNDEFINED;

3

cp = UInt(coproc);

4

d = UInt(Rd);

5

imm = op1:op2:op3;

6 \text{ acc} = (A == '1');

7

ExecuteCPCheck(cp);

8

if d == 13

then UNPREDICTABLE;

if !acc && InITBlock()

then UNPREDICTABLE;

```

#### **CONSTRAINED UNPREDICTABLE behavior**

If d = 13, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction returns an UNKNOWN value in SP.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 13, then one of the following behaviors must occur:

• It is UNKNOWN whether a stack limit check is performed.

#### **CONSTRAINED UNPREDICTABLE behavior**

If !acc && InITBlock (), then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction executes as if it passes the Condition code check.

#### Chapter C1. Alphabetical list of instructions

• The instruction executes as NOP.

# Assembler symbols for all encodings

| <a></a>           | Accumulate with existing register contents. This parameter must be one of the following values: |

|-------------------|-------------------------------------------------------------------------------------------------|

|                   | " Encoded as $A = 0$                                                                            |

|                   | A Encoded as $A = 1$                                                                            |

| <coproc></coproc> | Is the name of the coprocessor, encoding in the "coproc" field. Valid names are p0 to p7        |

|                   | inclusive.                                                                                      |

| <rd></rd>         | Is the general-purpose R0 - R14 or APSR_nzcv destination register, encoded in the "Rd"          |

|                   | field. For accumulator variants <rd> also specifies the source register. APSR_nzcv is</rd>      |

|                   | encoded by the "Rd" field value 0b1111.                                                         |

| <imm></imm>       | Is the immediate encoded in op1:op2:op3.                                                        |

## **Operation for all encodings**

```

1

if ConditionPassed() then

2

EncodingSpecificOperations();

3

if (!Coproc_Accepted(cp, ThisInstr())) then

4

GenerateCoprocessorException();

elsif acc then

5

RF[d] = CX_op1(ThisInstr(), RF[d], 32);

6

7

else

8

RF[d] = CX_op0(ThisInstr(), 32);

```

#### C1.0.3 CX1D

Custom Instruction Class 1. Custom instruction class 1 dual computes a value based on an immediate, and optionally the destination register pair value, and writes the result to a destination register pair.

The destination registers are a consecutive pair of general-purpose registers.

The significance of the words in each pair is consistent with the current data endianness.

#### **T1**

Armv8-M Custom Datapath Extension

|  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4   3 | 2         | 1 | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8 | 7   | 6 | 5 | 4 : | 3  | 2 | 1 | 0 |  |

|--|----|----|----|----|----|----|---|---|---|---|---|-------|-----------|---|---|----|----|----|----|----|----|------|---|-----|---|---|-----|----|---|---|---|--|

|  | 1  | 1  | 1  | А  | 1  | 1  | 1 | 0 | 0 | 0 |   | o     | <b>51</b> |   |   |    | F  | ٤d |    | 0  | С  | opro | с | op2 | 1 |   |     | ор | 3 |   |   |  |

#### Accumulator variant

```

Applies when A == 1

```

CX1DA <coproc>, <Rd>, <Rd+1>, #<imm>

#### Non-accumulator variant

#### Applies when A == 0

CX1D <coproc>, <Rd>, <Rd+1>, #<imm>

#### **Decode for this encoding**

```

if CoprocType(UInt(coproc)) != CP_CDEv1 then SEE "Coprocessor instructions";

1

2

if !HaveMainExt()

then UNDEFINED;

3 cp = UInt(coproc);

4

d

= UInt(Rd);

d2 = d + 1;

5

imm = op1:op2:op3;

6

7

acc = (A == '1');

8

ExecuteCPCheck(cp);

// Register pairs containing SP or PC are UNPREDICTABLE.

9

10 if d > 10

then UNPREDICTABLE;

if Rd[0] == '1'

11

then UNPREDICTABLE;

12 if !acc && InITBlock()

then UNPREDICTABLE;

```

#### **CONSTRAINED UNPREDICTABLE behavior**

If d is odd, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction returns and UNKNOWN value in Rd, Rd + 1 and Rd 1.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 12, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction returns and UNKNOWN value in R12 and SP.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 12 || d == 13, then one of the following behaviors must occur:

• It is UNKNOWN whether a stack limit check is performed.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 14, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If !acc && InITBlock (), then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction executes as if it passes the Condition code check.

- The instruction executes as NOP.

#### Assembler symbols for all encodings

| <a></a>           | Accumulate with existing register contents. This parameter must be one of the following values:<br>"Encoded as A = 0                                                                           |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | A Encoded as $A = 1$                                                                                                                                                                           |

| <coproc></coproc> | Is the name of the coprocessor, encoding in the "coproc" field. Valid names are $p0$ to $p7$ inclusive.                                                                                        |

| <rd></rd>         | Is the general-purpose register R0 – R11 specifying the first of destination register pair, encoded in the "Rd" field. For accumulator variants, <rd> also specifies the source register.</rd> |

| <imm></imm>       | Is the immediate encoded in op1:op2:op3.                                                                                                                                                       |

#### **Operation for all encodings**

```

if ConditionPassed() then

1

EncodingSpecificOperations();

2

3

if (!Coproc_Accepted(cp, ThisInstr())) then

4

GenerateCoprocessorException();

elsif acc then

5

6

RFD[d] = CX_op1(ThisInstr(), RFD[d], 64);

else

7

8

RFD[d] = CX_op0(ThisInstr(), 64);

```

#### C1.0.4 CX2

Custom Instruction Class 2. Custom instruction class 2 computes a value based on a source register, an immediate, and optionally the destination value, and writes the result to the destination register. The source and destination registers can be either general-purpose registers or the Condition flags, specified by use of APSR\_nzcv.

#### **T1**

Armv8-M Custom Datapath Extension

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 54  | 3 | 2 | 1  | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8 | 7   | 6 | 5 | 4 3 | 2  | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|-----|---|---|----|---|----|----|----|----|----|----|------|---|-----|---|---|-----|----|---|---|

| 1  | 1  | 1  | А  | 1  | 1  | 1 | 0 | 0 | 1 | op1 |   | F | Rn |   |    | F  | ۲d |    | 0  | С  | opro | C | op2 | 0 |   | C   | p3 |   |   |

#### Accumulator variant

#### Applies when A == 1

CX2A <coproc>, <Rd>, <Rn>, #<imm>

#### Non-accumulator variant

Applies when A == 0

CX2 <coproc>, <Rd>, <Rn>, #<imm>

#### Decode for this encoding

```

if CoprocType(UInt(coproc)) != CP_CDEv1 then SEE "Coprocessor instructions";

1

2

if !HaveMainExt()

then UNDEFINED:

3

cp = UInt(coproc);

4

= UInt(Rd);

d

= UInt(Rn);

5

n

6

imm = op1:op2:op3;

7

acc = (A == '1');

ExecuteCPCheck(cp);

8

if d == 13 || n == 13

then UNPREDICTABLE;

0

10

if !acc && InITBlock()

then UNPREDICTABLE;

```

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 13, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction returns an UNKNOWN value in SP.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 13, then one of the following behaviors must occur:

• It is UNKNOWN whether a stack limit check is performed.

#### **CONSTRAINED UNPREDICTABLE behavior**

If n = 13, then one of the following behaviors must occur:

- The instruction executes as NOP.

- The instruction returns an UNKNOWN value.

- The instruction is UNDEFINED.

#### **CONSTRAINED UNPREDICTABLE behavior**

If !acc && InITBlock (), then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction executes as if it passes the Condition code check.

- The instruction executes as NOP.

#### Assembler symbols for all encodings

| <a></a>           | Accumulate with existing register contents. This parameter must be one of the following values:                                                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | " Encoded as $A = 0$                                                                                                                                                                                                      |

|                   | A Encoded as $A = 1$                                                                                                                                                                                                      |

| <coproc></coproc> | Is the name of the coprocessor, encoding in the "coproc" field. Valid names are p0 to p7 inclusive.                                                                                                                       |

| <rd></rd>         | Is the general-purpose R0 - R14 or APSR_nzcv destination register, encoded in the "Rd" field. For accumulator variants <rd> also specifies the source register. APSR_nzcv is encoded by the "Rd" field value 0b1111.</rd> |

| <rn></rn>         | Is the general-purpose R0 - R14 or APSR_nzcv source register, encoded in the "Rn" field.<br>APSR_nzcv is encoded by the "Rn" field value 0b1111.                                                                          |

| <imm></imm>       | Is the immediate encoded in op1:op2:op3.                                                                                                                                                                                  |

#### **Operation for all encodings**

```

1

if ConditionPassed() then

EncodingSpecificOperations();

2

3

if (!Coproc_Accepted(cp, ThisInstr())) then

4

GenerateCoprocessorException();

elsif acc then

5

6

RF[d] = CX_op2(ThisInstr(), RF[d], RF[n], 32);

7

else

RF[d] = CX_op1(ThisInstr(), RF[n], 32);

8

```

#### C1.0.5 CX2D

Custom Instruction Class 2. Custom instruction class 2 dual computes a value based on a source register, an immediate, and optionally the destination register pair value, and writes the result to the destination register pair.

The destination registers are a consecutive pair of general-purpose registers.

The source registers can be either general-purpose registers or the Condition flags, specified by use of APSR\_nzcv. The significance of the words in each pair is consistent with the current data endianness.

#### **T1**

Armv8-M Custom Datapath Extension

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 4 | 1   3 | 2 | 1  | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8 | 7   | 6 | 5 | 4 3 | 2  | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|-----|-------|---|----|---|----|----|----|----|----|----|------|---|-----|---|---|-----|----|---|---|

| 1  | 1  | 1  | А  | 1  | 1  | 1 | 0 | 0 | 1 | op1 |       | F | Rn |   |    | F  | ۶d |    | 0  | С  | opro | С | op2 | 1 |   | 0   | 03 |   |   |

#### Accumulator variant

#### Applies when A == 1

CX2DA <coproc>, <Rd>, <Rd+1>, <Rn>, #<imm>

#### Non-accumulator variant

#### Applies when A == 0

CX2D <coproc>, <Rd>, <Rd+1>, <Rn>, #<imm>

#### Decode for this encoding

```

1

if CoprocType (UInt (coproc)) != CP_CDEv1 then SEE "Coprocessor instructions";

2

if !HaveMainExt()

then UNDEFINED;

3

cp = UInt(coproc);

4 d = UInt(Rd);

5

n = UInt(Rn);

imm = op1:op2:op3;

6

acc = (A == '1');

7

8

ExecuteCPCheck(cp);

9

// Register pairs containing SP or PC are UNPREDICTABLE.

10 if d > 10

then UNPREDICTABLE;

11 if n == 13

then UNPREDICTABLE;

if Rd[0] == '1'

12

then UNPREDICTABLE;

13 if !acc && InITBlock()

then UNPREDICTABLE;

```

#### **CONSTRAINED UNPREDICTABLE behavior**

If d is odd, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction returns and UNKNOWN value in Rd, Rd + 1 and Rd 1.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 12, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction returns and UNKNOWN value in R12 and SP.

• The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 12 || d == 13, then one of the following behaviors must occur:

• It is UNKNOWN whether a stack limit check is performed.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 14, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If n = 13, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The value in the destination register is UNKNOWN.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If !acc && InITBlock (), then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction executes as if it passes the Condition code check.

- The instruction executes as NOP.

#### Assembler symbols for all encodings

| <a></a>           | Accumulate with existing register contents. This parameter must be one of the following values:    |

|-------------------|----------------------------------------------------------------------------------------------------|

|                   | " Encoded as $A = 0$                                                                               |

|                   | A Encoded as $A = 1$                                                                               |

| <coproc></coproc> | Is the name of the coprocessor, encoding in the "coproc" field. Valid names are $p0$ to $p7$       |

|                   | inclusive.                                                                                         |

| <rd></rd>         | Is the general-purpose register $RO - R11$ specifying the first of destination register pair,      |

|                   | encoded in the "Rd" field. For accumulator variants, <rd> also specifies the source register.</rd> |

| <rn></rn>         | Is the general-purpose R0 - R14 or APSR_nzcv source register, encoded in the "Rn" field.           |

|                   | APSR_nzcv is encoded by the "Rn" field value 0b1110.                                               |

| <imm></imm>       | Is the immediate encoded in op1:op2:op3.                                                           |

#### **Operation for all encodings**

```

if ConditionPassed() then

1

2

EncodingSpecificOperations();

3

if (!Coproc_Accepted(cp, ThisInstr())) then

GenerateCoprocessorException();

4

elsif acc then

5

RFD[d] = CX_op2(ThisInstr(), RFD[d], RF[n], 64);

6

else

7

RFD[d] = CX_op1(ThisInstr(), RF[n], 64);

8

```

#### C1.0.6 CX3

Custom Instruction Class 3. Custom instruction class 3 computes a value based two source registers, an immediate and optionally the destination value, and writes the result to the destination register.

The source and destination registers can be either general-purpose registers or the Condition flags, specified by use of APSR\_nzcv.

#### **T1**

Armv8-M Custom Datapath Extension

| 1 | 5 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5   | 4 | 3 | 2 | 1  | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8 | 7   | 6 | 5  | 4  | 3 | 2 | 1 | 0 |

|---|---|----|----|----|----|----|---|---|---|---|-----|---|---|---|----|---|----|----|----|----|----|----|------|---|-----|---|----|----|---|---|---|---|

| 1 | L | 1  | 1  | А  | 1  | 1  | 1 | 0 | 1 |   | op1 |   |   | F | ۲n |   |    | R  | m  |    | 0  | С  | opro | C | op2 | 0 | ор | 03 |   | R | d |   |

#### Accumulator variant

Applies when A == 1

CX3A <coproc>, <Rd>, <Rn>, <Rm>, #<imm>

#### Non-accumulator variant

#### Applies when A == 0

CX3 <coproc>, <Rd>, <Rn>, <Rm>, #<imm>

#### **Decode for this encoding**

```

if CoprocType(UInt(coproc)) != CP_CDEv1 then SEE "Coprocessor instructions";

1

if !HaveMainExt()

2

then UNDEFINED;

3

cp = UInt(coproc);

4

= UInt(Rd);

d

5

n

= UInt(Rn);

= UInt(Rm);

6

m

7

imm = op1:op2:op3;

8

acc = (A == '1');

9 ExecuteCPCheck(cp);

10 if d == 13 || n == 13 || m == 13

then UNPREDICTABLE;

11 if !acc && InITBlock()

then UNPREDICTABLE;

```

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 13, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction returns an UNKNOWN value in SP.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 13, then one of the following behaviors must occur:

• It is UNKNOWN whether a stack limit check is performed.

#### **CONSTRAINED UNPREDICTABLE behavior**

If n = 13 or m = 13, then one of the following behaviors must occur:

• The instruction is UNDEFINED.

- The instruction returns and UNKNOWN value in SP.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If !acc && InITBlock (), then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction executes as if it passes the Condition code check.

- The instruction executes as NOP.

#### Assembler symbols for all encodings

| <a></a>           | Accumulate with existing register contents. This parameter must be one of the following values:<br>"Encoded as $A = 0$                                                                                                    |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | A Encoded as $A = 1$                                                                                                                                                                                                      |

| <coproc></coproc> | Is the name of the coprocessor, encoding in the "coproc" field. Valid names are $p0$ to $p7$ inclusive.                                                                                                                   |

| <rd></rd>         | Is the general-purpose R0 - R14 or APSR_nzcv destination register, encoded in the "Rd" field. For accumulator variants <rd> also specifies the source register. APSR_nzcv is encoded by the "Rd" field value 0b1111.</rd> |

| <rn></rn>         | Is the general-purpose R0 – R14 or APSR_nzcv destination register, encoded in the "Rn" field. APSR_nzcv is encoded by the "Rn" field value 0b1111.                                                                        |

| <rm></rm>         | Is the general-purpose R0 – R14 or APSR_nzcv destination register, encoded in the "Rm" field. APSR_nzcv is encoded by the "Rm" field value 0b1111.                                                                        |

| <imm></imm>       | Is the immediate encoded in op1:op2:op3.                                                                                                                                                                                  |

#### **Operation for all encodings**

```

if ConditionPassed() then

1

2

EncodingSpecificOperations();

3

if (!Coproc_Accepted(cp, ThisInstr())) then

4

GenerateCoprocessorException();

5

elsif acc then

RF[d] = CX_op3(ThisInstr(), RF[d], RF[n], RF[m], 32);

6

else

7

8

RF[d] = CX_op2(ThisInstr(), RF[n], RF[m], 32);

```

#### C1.0.7 CX3D

Custom Instruction Class 3. Custom instruction class 3 dual computes a value based on two source registers, an immediate, and optionally the destination register pair value, and writes the result to the destination register pair.

The source registers can be either general-purpose registers or the Condition flags, specified by use of APSR\_nzcv.

The destination registers are a consecutive pair of general-purpose registers.

The significance of the words in each pair is consistent with the current data endianness.

#### **T1**

Armv8-M Custom Datapath Extension

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5   | 4 | 3 | 2 | 1  | 0 | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8 | 7   | 6 | 5  | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|-----|---|---|---|----|---|----|----|----|----|----|----|------|---|-----|---|----|---|---|---|---|---|

| 1  | 1  | 1  | А  | 1  | 1  | 1 | 0 | 1 |   | op1 |   |   | F | ۲n |   |    | R  | m  |    | 0  | СС | opro | С | op2 | 1 | op | 3 |   | R | d |   |

#### Accumulator variant

#### Applies when A == 1

CX3DA <coproc>, <Rd>, <Rd+1>, <Rn>, <Rm>, #<imm>

#### Non-accumulator variant

#### Applies when A == 0

CX3D <coproc>, <Rd>, <Rd+1>, <Rn>, <Rm>, #<imm>

#### Decode for this encoding

```

1

if CoprocType (UInt (coproc)) != CP_CDEv1 then SEE "Coprocessor instructions";

2

if !HaveMainExt()

then UNDEFINED;

3

cp = UInt(coproc);

4 d = UInt(Rd);

= UInt(Rn);

5

n

= UInt(Rm);

6

m

7

imm = op1:op2:op3;

8

acc = (A == '1');

9

ExecuteCPCheck(cp);

10 // Register pairs containing SP or PC are UNPREDICTABLE.

11 if d > 10

then UNPREDICTABLE;

12

if n == 13 || m == 13

then UNPREDICTABLE;

13 if Rd[0] == '1'

then UNPREDICTABLE;

14 if !acc && InITBlock()

then UNPREDICTABLE:

```

#### **CONSTRAINED UNPREDICTABLE behavior**

If d is odd, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction returns and UNKNOWN value in Rd, Rd + 1 and Rd 1.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d = 12, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction returns and UNKNOWN value in SP.

• The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 12 || d == 13, then one of the following behaviors must occur:

• It is UNKNOWN whether a stack limit check is performed.

#### **CONSTRAINED UNPREDICTABLE behavior**

If d == 14, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If n == 13 || m == 12, then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The value in the destination register is UNKNOWN.

- The instruction executes as NOP.

#### **CONSTRAINED UNPREDICTABLE behavior**

If !acc && InITBlock (), then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction executes as if it passes the Condition code check.

- The instruction executes as NOP.

#### Assembler symbols for all encodings

| <a></a>           | Accumulate with existing register contents. This parameter must be one of the following values:<br>" Encoded as A = 0                                                                                       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | A Encoded as $A = 1$                                                                                                                                                                                        |

| <coproc></coproc> | Is the name of the coprocessor, encoding in the "coproc" field. Valid names are $p0$ to $p7$ inclusive.                                                                                                     |

| <rd></rd>         | Is the general-purpose register $RO - R11$ specifying the first of destination register pair, encoded in the "Rd" field. For accumulator variants, $\langle Rd \rangle$ also specifies the source register. |

| <rn></rn>         | Is the general-purpose R0 – R14 or APSR_nzcv source register, encoded in the "Rn" field.<br>APSR_nzcv is encoded by the "Rn" field value 0b1110.                                                            |

| <rm></rm>         | Is the general-purpose R0 - R14 or APSR_nzcv source register, encoded in the "Rm" field.<br>APSR_nzcv is encoded by the "Rm" field value 0b1110.                                                            |

| <imm></imm>       | Is the immediate encoded in op1:op2:op3.                                                                                                                                                                    |

#### **Operation for all encodings**

```

1

if ConditionPassed() then

2

EncodingSpecificOperations();

3

if (!Coproc_Accepted(cp, ThisInstr())) then

4

GenerateCoprocessorException();

5

elsif acc then

6

RFD[d] = CX_op3(ThisInstr(), RFD[d], RF[n], RF[m], 64);

7

else

8

RFD[d] = CX_op2(ThisInstr(), RFD[n], RF[m], 64);

```

#### C1.0.8 LDC, LDC2 (immediate)

Load Coprocessor (immediate). Load Coprocessor loads memory data from a sequence of consecutive memory addresses to a coprocessor. If no coprocessor can execute the instruction, a UsageFault exception is generated.

This is a generic coprocessor instruction. Some of the fields have no functionality defined by the architecture and are free for use by the coprocessor instruction set designer. These fields are the D bit, the CRd field, and in the Unindexed addressing mode only, the imm8 field.

Arm reserves coprocessors CP8 to CP15, and this manual defines the valid instructions when coproc is in this range.

#### **T1**

Armv8-M Main Extension only

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2          | 1 | 0 | 15 | 14 | 13 | 12 | 11     | 10 | 9 | 8 | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|------------|---|---|----|----|----|----|--------|----|---|---|------|---|---|---|---|---|---|---|

| 1  | 1  | 1  | 0  | 1  | 1  | 0 | Ρ | U | D | w | 1 | R | Rn != 1111 |   |   |    | C  | Rd |    | coproc |    |   |   | imm8 |   |   |   |   |   |   |   |

#### **Offset variant**

Applies when P == 1 && W == 0.

LDC{L}{<c>}{<q>} <coproc>, <CRd>, [<Rn>{, #{+/-}<imm>}]

Post-indexed variant

Applies when P == 0 && W == 1.

LDC{L}{<c>}{<q>} <coproc>, <CRd>, [<Rn>], #{+/-}<imm>

#### **Pre-indexed variant**

#### Applies when P == 1 & & W == 1.

LDC{L}{<c>}{<q>} <coproc>, <CRd>, [<Rn>, #{+/-}<imm>]!

#### Unindexed variant

Applies when P == 0 & & U == 1 & & W == 0.

LDC{L}{<c>}{<q>} <coproc>, <CRd>, [<Rn>], <option>

#### **Decode for this encoding**

```

if Rn == '1111' then SEE "LDC (literal)";

1

if coproc IN {'100x', '101x', '111x'}

then SEE "Floating-point and MVE";

2

if CoprocType(UInt(coproc)) == CP_CDEv1

then SEE "CDE instructions";

3

if P == '0' && U == '0' && D == '1' && W == '0' then SEE "MRRC, MRRC2";

4

if P == '0' && U == '0' && D == '0' && W == '0' then UNDEFINED;

5

6

if !HaveMainExt()

then UNDEFINED:

n = UInt(Rn); cp = UInt(coproc); imm32 = ZeroExtend(imm8:'00', 32);

index = (P == '1'); add = (U == '1'); wback = (W == '1');

7

```

#### T2

Armv8-M Main Extension only

| 15 | 14 | 1 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3  | 2    | 1   | 0 | 15 | 14 | 13 | 12 | 11 | 10  | 9   | 8 | 7 | 6 | 5 | 4   | 3  | 2 | 1 | 0 |

|----|----|---|----|----|----|----|---|---|---|---|---|---|----|------|-----|---|----|----|----|----|----|-----|-----|---|---|---|---|-----|----|---|---|---|

| 1  | 1  |   | 1  | 1  | 1  | 1  | 0 | Ρ | U | D | W | 1 | Rn | ı != | 111 | 1 |    | CI | ٦d |    |    | сор | roc |   |   |   |   | imn | 18 |   |   |   |

Chapter C1. Alphabetical list of instructions

**Offset variant**

Applies when P == 1 && W == 0.

$LDC2\{L\}\{<\!c\!>\}\{<\!q\!>\} <\!coproc\!>, <\!CRd\!>, [<\!Rn\!>\!\{, \#\{+/-\}<\!imm\!>\}]$

## Post-indexed variant

Applies when P == 0 & W == 1.

LDC2{L}{<c>}{<q>} <coproc>, <CRd>, [<Rn>], #{+/-}<imm>

**Pre-indexed variant**

## Applies when P == 1 & & W == 1.

LDC2{L}{<c>}{<q>} <coproc>, <CRd>, [<Rn>, #{+/-}<imm>]!

## Unindexed variant

#### Applies when P == 0 & U == 1 & W == 0.

LDC2{L}{<c>}{<q>} <coproc>, <CRd>, [<Rn>], <option>

# **Decode for this encoding**

```

1 if Rn == '1111' then SEE "LDC (literal)";

2 if coproc IN {'100x', '101x', '111x'} then SEE "Floating-point and MVE";

3 if CoprocType(UInt(coproc)) == CP_CDEv1 then SEE "CDE instructions";

4 if P == '0' && U == '0' && D == '1' && W == '0' then SEE "MRRC, MRRC2";

5 if P == '0' && U == '0' && D == '0' && W == '0' then UNDEFINED;

6 if !HaveMainExt() then UNDEFINED;

7 n = UInt(Rn); cp = UInt(coproc); imm32 = ZeroExtend(imm8:'00', 32);

8 index = (P == '1'); add = (U == '1'); wback = (W == '1');

```

# Assembler symbols for all encodings

| L                            | If specified, selects the $D == 1$ form of the encoding. If omitted, selects the $D == 0$ form.                                                                   |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <c></c>                      | See Standard assembler syntax fields.                                                                                                                             |

| <q></q>                      | See Standard assembler syntax fields.                                                                                                                             |

| <coproc></coproc>            | Is the name of the coprocessor, encoded in the "coproc" field. The generic coprocessor names are p0 to p15.                                                       |

| <crd></crd>                  | Is the coprocessor register to be transferred, encoded in the "CRd" field.                                                                                        |

| <rn></rn>                    | Is the general-purpose base register, encoded in the "Rn" field. If the PC is used, see LDC, LDC2 (literal).                                                      |

| <pre><option></option></pre> | Is a coprocessor option, in the range 0 to 255 enclosed in { }, encoded in the "imm8" field.                                                                      |

| +/-                          | Specifies the offset is added to or subtracted from the base register, defaulting to + if omitted and encoded in the "U" field. It can have the following values: |

|                              | - when U = 0                                                                                                                                                      |

|                              | + when $U = 1$                                                                                                                                                    |

| <imm></imm>                  | Is the immediate offset used for forming the address, a multiple of 4 in the range 0-1020, defaulting to 0 and encoded in the "imm8" field, as <imm>/4.</imm>     |

```

1 if ConditionPassed() then

2   EncodingSpecificOperations();

3   ExecuteCPCheck(cp);

4

5   thisInstr = ThisInstr();

6   if !Coproc_Accepted(cp, thisInstr) then

```

## Chapter C1. Alphabetical list of instructions

```

7

GenerateCoprocessorException();

8

else

9

offset_addr = if add then (R[n] + imm32) else (R[n] - imm32);

10

address = if index then offset_addr else R[n];

11

12

// Determine if the stack pointer limit check should be performed

if wback && n == 13 then

13

14

violatesLimit = ViolatesSPLim(LookUpSP(), offset_addr);

15

else

16

violatesLimit = FALSE;

17

18

// Memory operation only performed if limit not violated

19

\quad \text{if } ! \texttt{violatesLimit } \mathbf{then} \\

20

repeat

21

Coproc_SendLoadedWord(MemA[address,4], cp, thisInstr);

22

address = address + 4;

23

until Coproc_DoneLoading(cp, thisInstr);

24

25

// If the stack pointer is being updated a fault will be raised

// if the limit is violated

26

27

if wback then RSPCheck[n] = offset_addr;

```

# C1.0.9 LDC, LDC2 (literal)

Load Coprocessor (literal). Load Coprocessor loads memory data from a sequence of consecutive memory addresses to a coprocessor. If no coprocessor can execute the instruction, a UsageFault exception is generated.

This is a generic coprocessor instruction. The D bit and the CRd field have no functionality defined by the architecture and are free for use by the coprocessor instruction set designer.

Arm reserves coprocessors CP8 to CP15, and this manual defines the valid instructions when coproc is in this range.

# **T1**

Armv8-M Main Extension only

| 1 | 5 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 15 | 14 | 13 | 12 | 11 | 10  | 9   | 8 | 7 | 6 | 5 | 4   | 3  | 2 | 1 | 0 |

|---|------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|-----|-----|---|---|---|---|-----|----|---|---|---|

| 1 | 1    | 1  | 0  | 1  | 1  | 0 | Р | U | D | w | 1 | 1 | 1 | 1 | 1 |    | CF | ٦d |    |    | сор | roc |   |   |   |   | imr | m8 |   |   |   |

#### T1 variant

Applies when ! (P == 0 & U == 0 & W == 0).

LDC{L}{<c>}{<q>} <coproc>, <CRd>, <label> LDC{L}{<c>}{<q>} <coproc>, <CRd>, [PC, #{+/-}<imm>]

## **Decode for this encoding**

```

if coproc IN {'100x', '101x', '111x'}

then SEE "Floating-point and MVE";

if CoprocType(UInt(coproc)) == CP_CDEv1

2

then SEE "CDE instructions";

if P == '0' && U == '0' && D == '1' && W == '0' then SEE "MRRC, MRRC2";

3

if P == '0' && U == '0' && D == '0' && W == '0' then UNDEFINED;

4

5

if !HaveMainExt()

then UNDEFINED:

6

index = (P == '1'); // Always TRUE in the T32 instruction set

add = (U == '1'); cp = UInt(coproc); imm32 = ZeroExtend(imm8:'00', 32);

7

8 if W == '1' || P == '0'

then UNPREDICTABLE;

```

## **CONSTRAINED UNPREDICTABLE behavior**

If W == '1' || P == '0', then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction executes as NOP.

- The instruction executes without writeback of the base address.

- The instruction executes as LDC with writeback to the PC.

## **T2**

Armv8-M Main Extension only

|   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 15 | 14 | 13 | 12 | 11 | 10  | 9   | 8 | 7 | 6 | 5 | 4 3  | 2 | 1 | 0 |  |

|---|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|-----|-----|---|---|---|---|------|---|---|---|--|

| ſ | 1  | 1  | 1  | 1  | 1  | 1  | 0 | Р | U | D | W | 1 | 1 | 1 | 1 | 1 |    | CF | ٦d |    |    | сор | roc |   |   |   |   | imm8 |   |   |   |  |

#### T2 variant

#### Applies when ! (P == 0 && U == 0 && W == 0).

```

LDC2{L}{<c>}{<q>} <coproc>, <CRd>, <label>

LDC2{L}{<c>}{<q>} <coproc>, <CRd>, [PC, #{+/-}<imm>]

```

# Decode for this encoding

```

if coproc IN {'100x', '101x', '111x'} then SEE "Floating-point and MVE";

if CoprocType(UInt(coproc)) == CP_CDEv1 then SEE "CDE instructions";

1

2

if P == '0' && U == '0' && D == '1' && W == '0' then SEE "MRRC, MRRC2";

3

if P == '0' && U == '0' && D == '0' && W == '0' then UNDEFINED;

4

5

if !HaveMainExt()

then UNDEFINED;

index = (P == '1'); // Always TRUE in the T32 instruction set

6

add = (U == '1'); cp = UInt(coproc); imm32 = ZeroExtend(imm8:'00', 32);

7

8 if W == '1' || P == '0'

then UNPREDICTABLE;

```

## **CONSTRAINED UNPREDICTABLE behavior**

If W == 'l' || P == '0', then one of the following behaviors must occur:

- The instruction is UNDEFINED.

- The instruction executes as NOP.

- The instruction executes without writeback of the base address.

- The instruction executes as LDC with writeback to the PC.

## Assembler symbols for all encodings