# **AMD64 Technology**

# **AMD64 Architecture Programmer's Manual** Volume 4: **128-Bit Media Instructions**

Publication No. Revision Date 26568 3.06 February 2005

© 2002, 2003, 2004, 2005 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### **Trademarks**

AMD, the AMD arrow logo, AMD Athlon, AMD Duron, and combinations thereof, and 3DNow! are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

Windows NT is a registered trademark of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **Contents**

| Figur | es                                    |

|-------|---------------------------------------|

| Table | ·sxi                                  |

| Revis | ion History                           |

| Prefa | ce                                    |

|       | About This Book xv                    |

|       | Audience xv                           |

|       | Contact Information xv                |

|       | Organization xv                       |

|       | Definitionsxvi                        |

|       | Related Documents xxvii               |

| 1     | 128-Bit Media Instruction Reference 1 |

|       | ADDPD4                                |

|       | ADDPS                                 |

|       | ADDSD                                 |

|       | ADDSS                                 |

|       | ADDSUBPD                              |

|       | ADDSUBPS19                            |

|       | ANDNPD22                              |

|       | ANDNPS24                              |

|       | ANDPD                                 |

|       | ANDPS                                 |

|       | CMPPD30                               |

|       | CMPPS                                 |

|       | CMPSD                                 |

|       | CMPSS                                 |

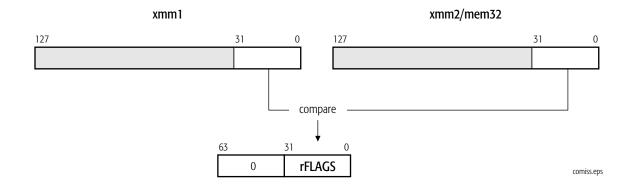

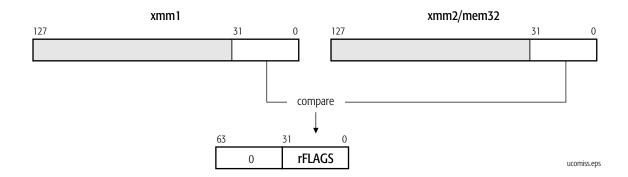

|       | COMISD                                |

|       | COMISS                                |

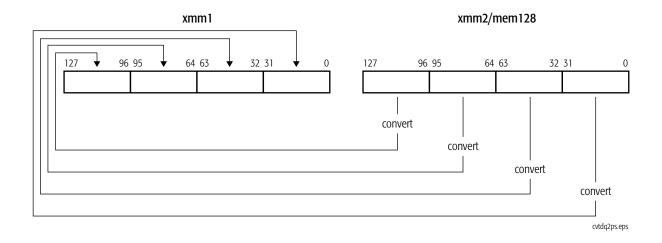

|       | CVTDQ2FD                              |

|       | CVTPD2D053                            |

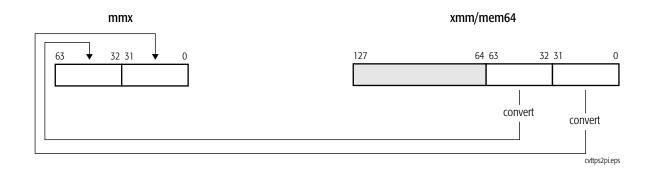

|       | CVTPD2PI                              |

|       | CVTPD2PS                              |

|       | CVTPI2PD                              |

|       | CVTPI2PS64                            |

|       | CVTPS2DQ                              |

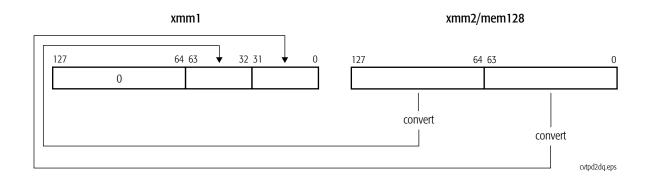

|       | CVTPS2PD69                            |

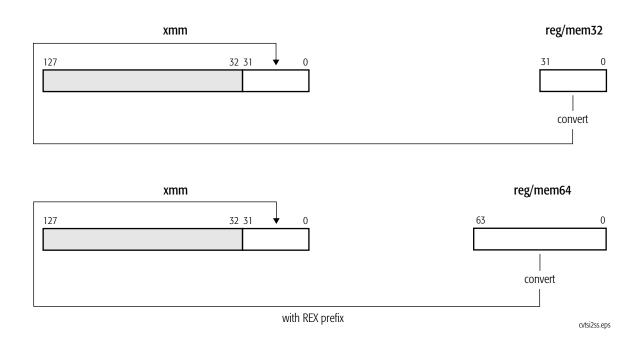

|       | CVTPS2PI71                            |

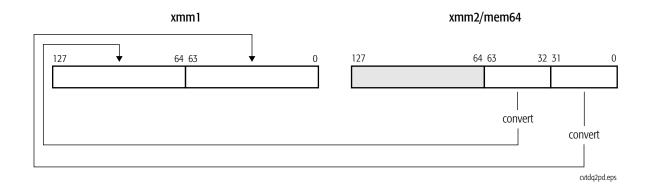

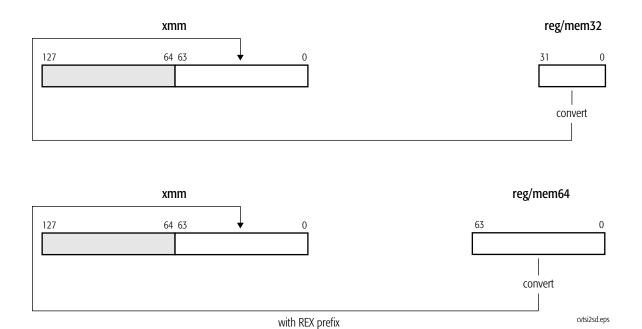

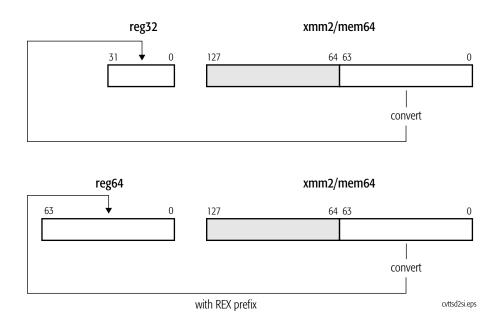

|       | CVTSD2SI                              |

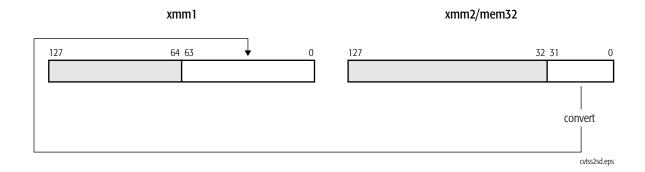

|       | CVTSD2SS                              |

|       | CVTSI2SD80                            |

# 26568–Rev. 3.06–February 2005

| CVTSI2SS   |      |

|------------|------|

| CVTSS2SD   |      |

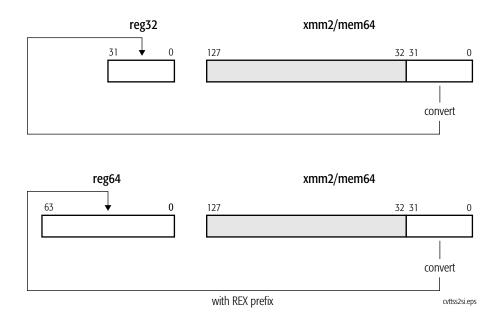

| CVTSS2SI   |      |

| CVTTPD2DQ  | . 91 |

| CVTTPD2PI  | . 94 |

| CVTTPS2DQ  | . 97 |

| CVTTPS2PI  | 100  |

| CVTTSD2SI  | 103  |

| CVTTSS2SI  | 106  |

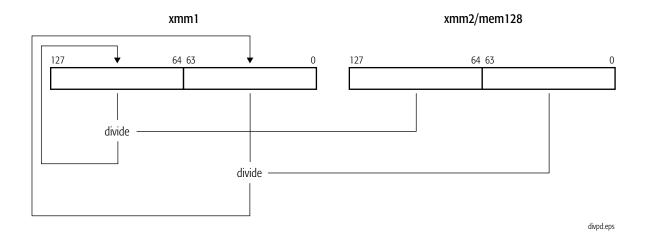

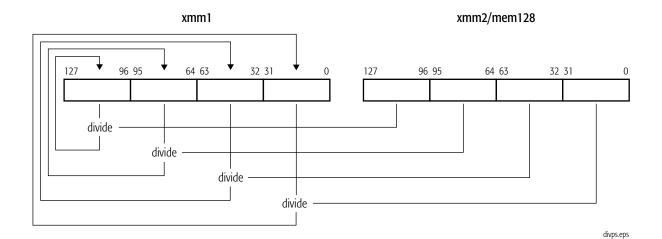

| DIVPD      | 109  |

| DIVPS      | 112  |

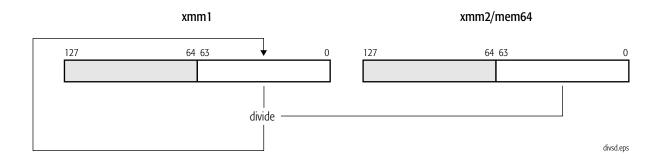

| DIVSD      | 115  |

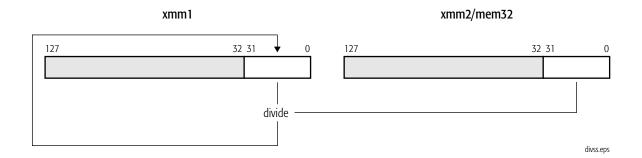

| DIVSS      | 118  |

| FXRSTOR    | 121  |

| FXSAVE     | 124  |

| HADDPD     | 126  |

| HADDPS     |      |

| HSUBPD     | 132  |

| HSUBPS     | 135  |

| LDDQU      | 138  |

| LDMXCSR    | 140  |

| MASKMOVDQU | 142  |

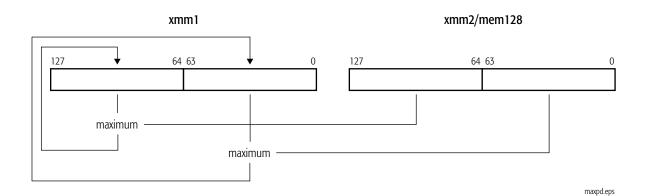

| MAXPD      |      |

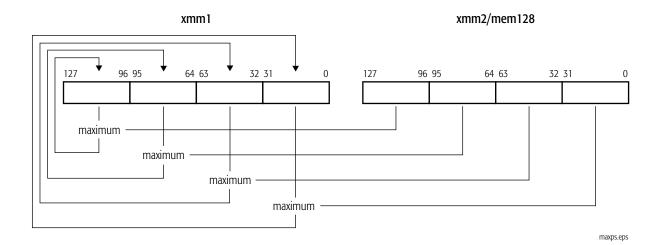

| MAXPS      | 148  |

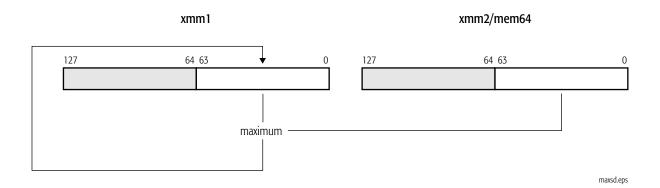

| MAXSD      | 151  |

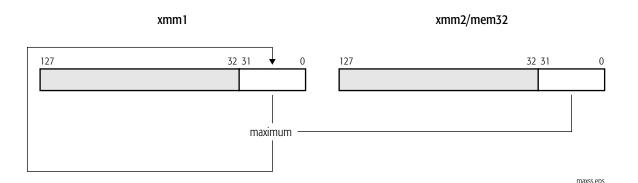

| MAXSS      | 154  |

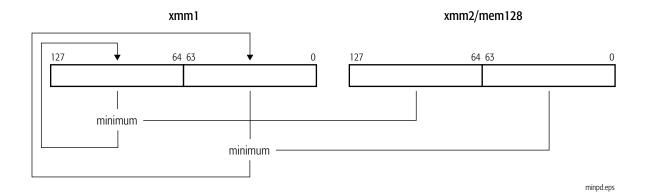

| MINPD      | 157  |

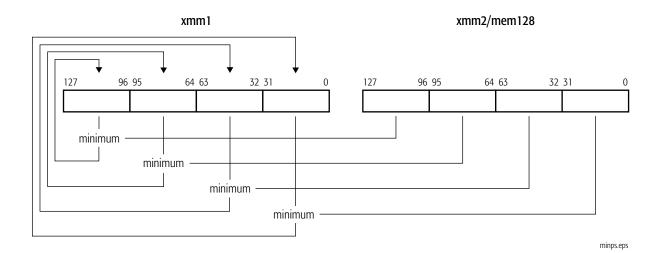

| MINPS      | 160  |

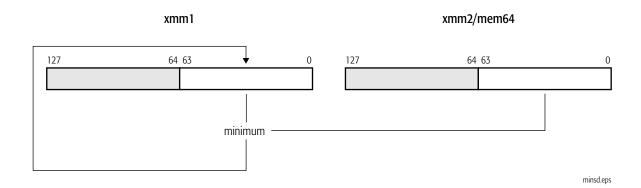

| MINSD      | 163  |

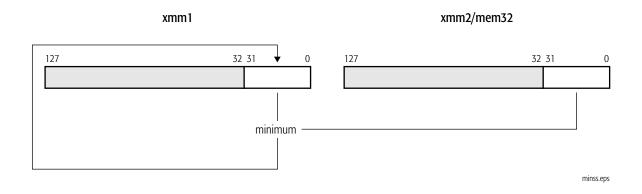

| MINSS      | 166  |

| MOVAPD     | 168  |

| MOVAPS     | 170  |

| MOVD       | 173  |

| MOVDDUP    | 176  |

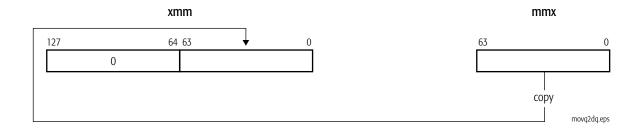

| MOVDQ2Q    | 178  |

| MOVDQA     |      |

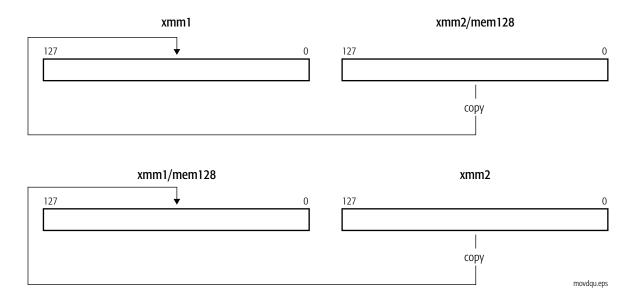

| MOVDQU     | 182  |

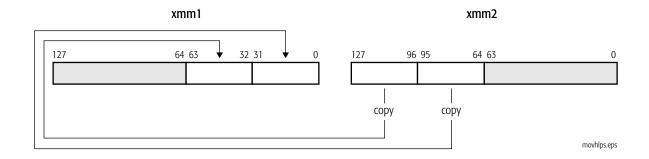

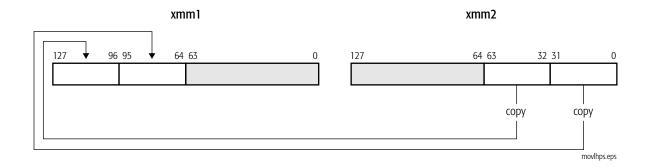

| MOVHLPS    | 184  |

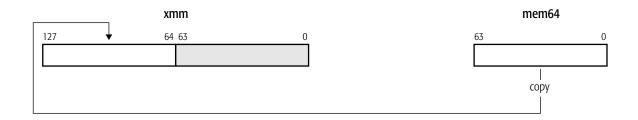

| MOVHPD     |      |

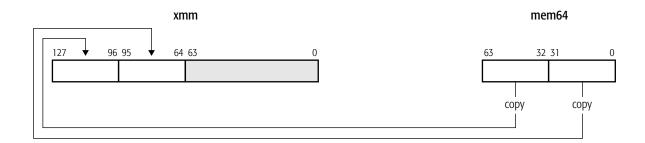

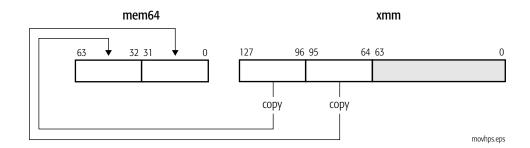

| MOVHPS     |      |

| MOVLHPS    |      |

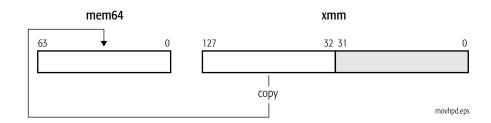

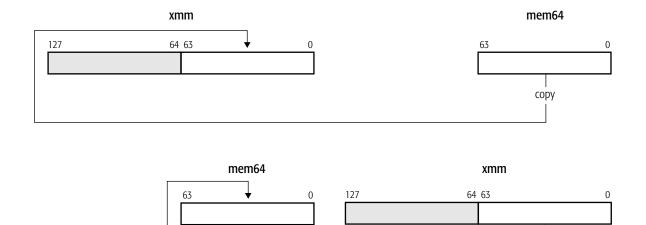

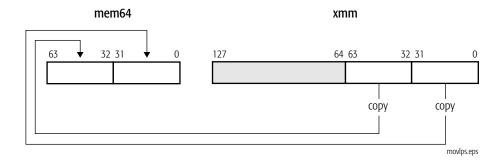

| MOVLPD     |      |

| MOVLPS     |      |

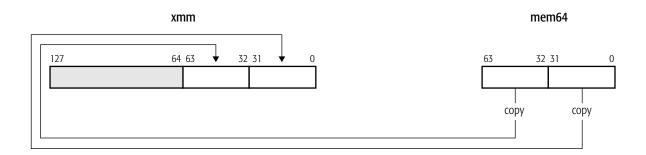

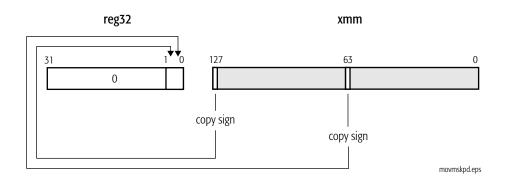

| MOVMSKPD   |      |

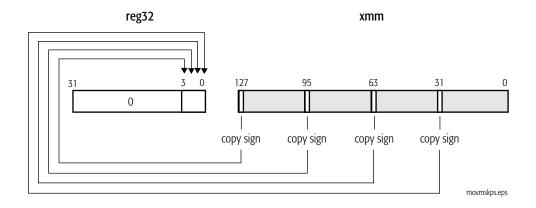

| MOVMSKPS   |      |

| MOVNTDQ    |      |

| MOVNTPD    | 202  |

# 26568-Rev. 3.06-February 2005

| MOVNTPS  |     |

|----------|-----|

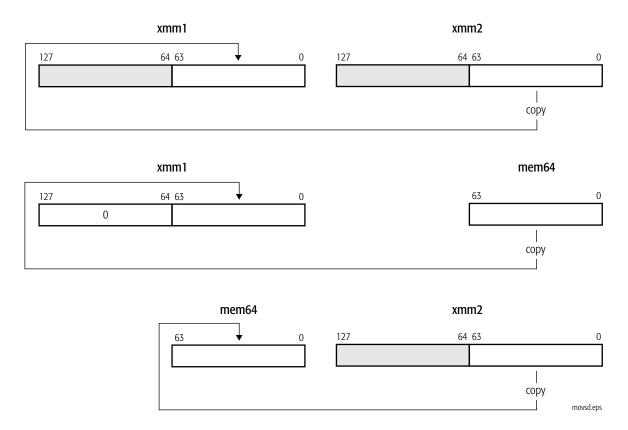

| MOVQ     |     |

| MOVQ2DQ  |     |

| MOVSD    | 210 |

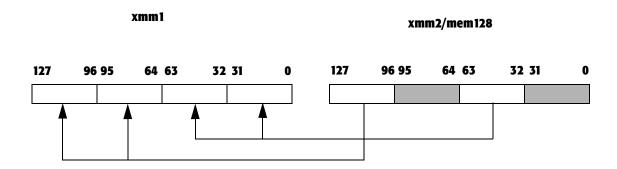

| MOVSHDUP |     |

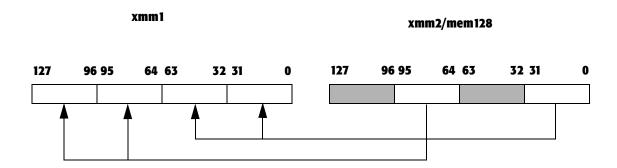

| MOVSLDUP |     |

| MOVSS    |     |

| MOVUPD   |     |

| MOVUPS   |     |

| MULPD    |     |

| MULPS    |     |

| MULSD    |     |

| MULSS    |     |

| ORPD     |     |

| ORPS     |     |

| PACKSSDW |     |

| PACKSSWB |     |

| PACKUSWB |     |

| PADDB    |     |

| PADDD    |     |

| PADDQ    |     |

| PADDSB   |     |

| PADDSW   |     |

| PADDUSB  |     |

| PADDUSW  |     |

| PADDW    |     |

| PAND     |     |

| PANDN    |     |

| PAVGB    |     |

| PAVGW    |     |

| PCMPEQB  |     |

| PCMPEQD  |     |

| PCMPEQW  | 276 |

| PCMPGTB  | 278 |

| PCMPGTD  | 280 |

| PCMPGTW  | 282 |

| PEXTRW   | 284 |

| PINSRW   | 286 |

| PMADDWD  | 289 |

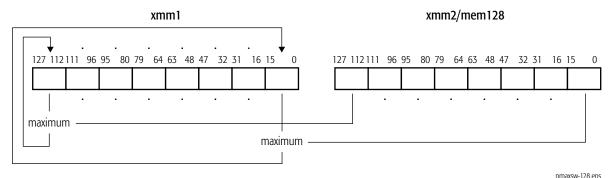

| PMAXSW   | 291 |

| PMAXUB   | 293 |

| PMINSW   | 295 |

| PMINUB   | 297 |

| PMOVMSKB |     |

| PMULHUW  | 301 |

| PMULHW   |     |

| PMULLW   |     |

# 26568–Rev. 3.06–February 2005

| PMULUDQ    |       |

|------------|-------|

| POR        |       |

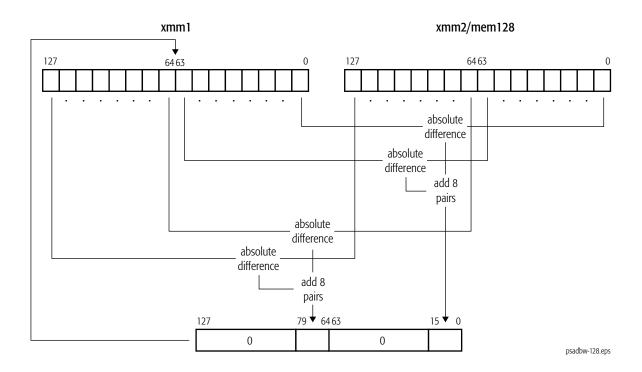

| PSADBW     | . 311 |

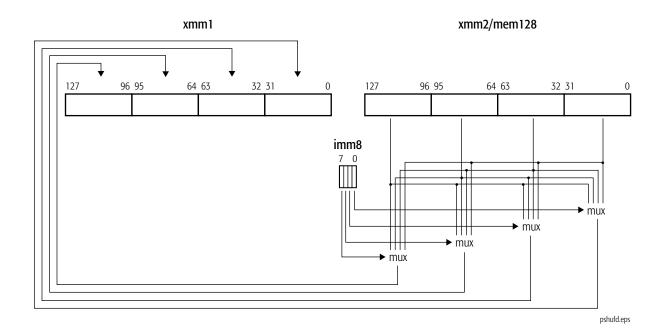

| PSHUFD     |       |

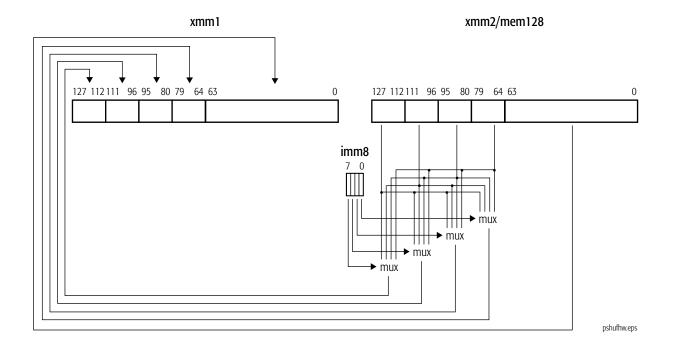

| PSHUFHW    | . 317 |

| PSHUFLW    | . 320 |

| PSLLD      | . 323 |

| PSLLDQ     | . 326 |

| PSLLQ      | . 328 |

| PSLLW      |       |

| PSRAD      | . 333 |

| PSRAW      | . 336 |

| PSRLD      | . 339 |

| PSRLDQ     | . 342 |

| PSRLQ      |       |

| PSRLW      |       |

| PSUBB      |       |

| PSUBD      |       |

| PSUBQ      |       |

| PSUBSB     |       |

| PSUBSW     |       |

| PSUBUSB    |       |

| PSUBUSW    |       |

| PSUBW      |       |

| PUNPCKHBW  |       |

| PUNPCKHDQ  |       |

| PUNPCKHQDQ |       |

| PUNPCKHWD  |       |

| PUNPCKLBW  |       |

| PUNPCKLDQ  |       |

| PUNPCKLQDQ |       |

| PUNPCKLWD  |       |

| PXOR       |       |

| RCPPS      |       |

| RCPSS      |       |

| RSQRTPS    | . 388 |

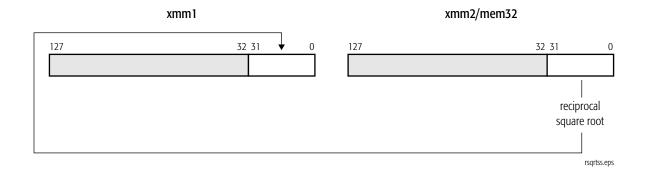

| RSORTSS    |       |

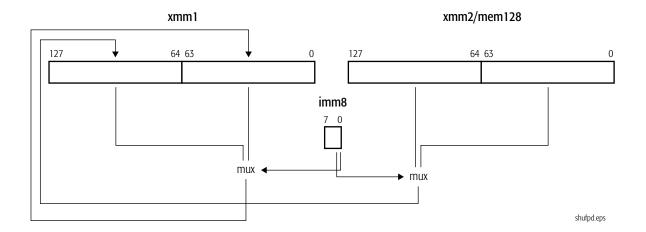

| SHUFPD     |       |

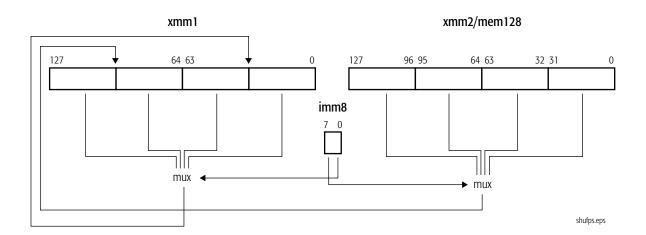

| SHUFPS     | . 395 |

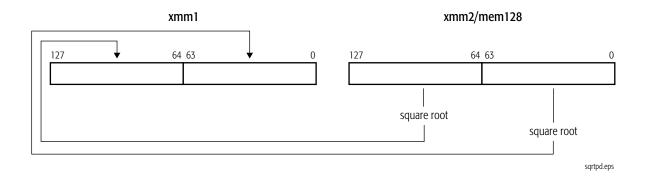

| SQRTPD     |       |

| SÕRTPS     |       |

| SQRTSD     | . 404 |

| SORTSS     |       |

| STMXCSR    |       |

| SUBPD      | . 412 |

| SUBPS      |       |

| CLIDCD     | 110   |

# 26568-Rev. 3.06-February 2005

# AMD 64-Bit Technology

|       | SUBSS    | 42 | <u> </u> |

|-------|----------|----|----------|

|       | UCOMISD  | 42 | 2        |

|       | UCOMISS  | 42 | 27       |

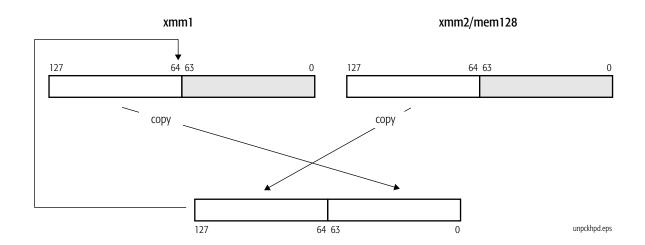

|       | UNPCKHPD | 43 | 3(       |

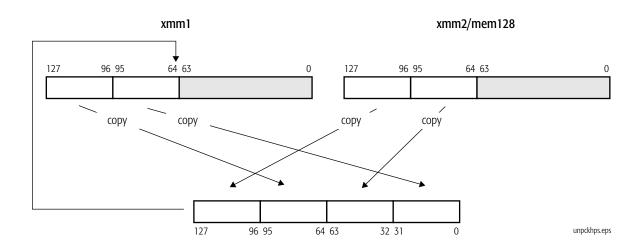

|       | UNPCKHPS | 43 | 32       |

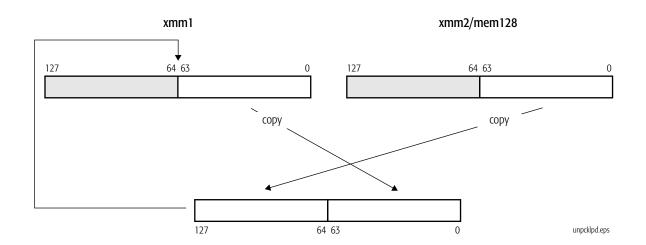

|       | UNPCKLPD | 43 | 34       |

|       | UNPCKLPS |    |          |

|       | XORPD    | 43 | 38       |

|       | XORPS    |    | ļ(       |

| Index |          | 44 | 13       |

AMD 64-Bit Technology

26568–Rev. 3.06–February 2005

viii Contents

| Fi | g  | Ш | re | S |

|----|----|---|----|---|

|    | ж. |   | _  | _ |

Figure 1-1. Diagram Conventions for 128-Bit Media Instructions . . . . . . . 2

Figures ix

26568–Rev. 3.06–February 2005

x Figures

# **Tables**

| Table 1-1. | Immediate Operand Values for Compare Operations        |

|------------|--------------------------------------------------------|

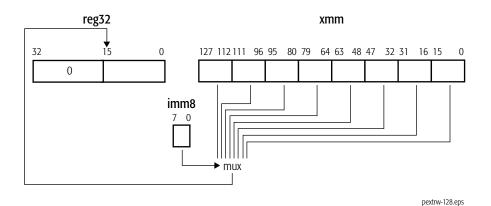

| Table 1-2. | Immediate-Byte Operand Encoding for 128-Bit PEXTRW285  |

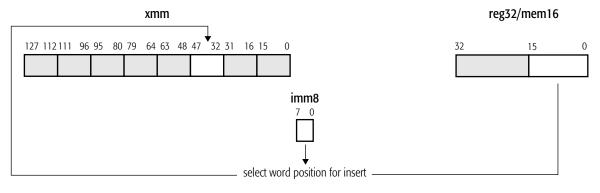

| Table 1-3. | Immediate-Byte Operand Encoding for 128-Bit PINSRW 287 |

| Table 1-4. | Immediate-Byte Operand Encoding for PSHUFD315          |

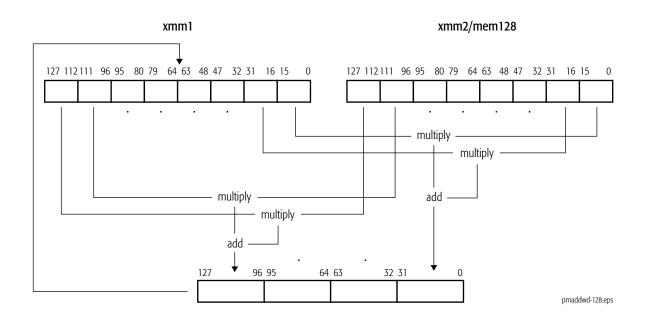

| Table 1-5. | Immediate-Byte Operand Encoding for PSHUFHW318         |

| Table 1-6. | Immediate-Byte Operand Encoding for PSHUFLW 321        |

| Table 1-7. | Immediate-Byte Operand Encoding for SHUFPD393          |

| Table 1-8. | Immediate-Byte Operand Encoding for SHUFPS396          |

Tables xi

AMD 64-Bit Technology

26568–Rev. 3.06–February 2005

xii Tables

# **Revision History**

| Date           | Revision | Description                                                                                  |

|----------------|----------|----------------------------------------------------------------------------------------------|

| January 2005   | 3.06     | Added documentation on SSE3 instructions. Corrected numerous minor factual errors and typos. |

| September 2003 | 3.05     | Made numerous small factual corrections.                                                     |

| April 2003     | 3.04     | Made minor corrections.                                                                      |

Chapter: xiii

26568–Rev. 3.06–February 2005

xiv Chapter:

# **Preface**

## **About This Book**

This book is part of a multivolume work entitled the *AMD64 Architecture Programmer's Manual*. This table lists each volume and its order number.

| Title                                                      | Order No. |

|------------------------------------------------------------|-----------|

| Volume 1, Application Programming                          | 24592     |

| Volume 2, System Programming                               | 24593     |

| Volume 3, General-Purpose and System Instructions          | 24594     |

| Volume 4, 128-Bit Media Instructions                       | 26568     |

| Volume 5, 64-Bit Media and x87 Floating-Point Instructions | 26569     |

# **Audience**

This volume (Volume 4) is intended for all programmers writing application or system software for processors that implement the AMD64 architecture.

# **Contact Information**

To submit questions or comments concerning this document, contact our technical documentation staff at AMD64.Feedback@amd.com.

# **Organization**

Volumes 3, 4, and 5 describe the AMD64 architecture's instruction set in detail. Together, they cover each instruction's mnemonic syntax, opcodes, functions, affected flags, and possible exceptions.

The AMD64 instruction set is divided into five subsets:

- General-purpose instructions

- System instructions

- 128-bit media instructions

Preface xv

- 64-bit media instructions

- x87 floating-point instructions

Several instructions belong to—and are described identically in—multiple instruction subsets.

This volume describes the 128-bit media instructions. The index at the end cross-references topics within this volume. For other topics relating to the AMD64 architecture, and for information on instructions in other subsets, see the tables of contents and indexes of the other volumes.

## **Definitions**

Many of the following definitions assume an in-depth knowledge of the legacy x86 architecture. See "Related Documents" on page xxvii for descriptions of the legacy x86 architecture.

#### **Terms and Notation**

In addition to the notation described below, "Opcode-Syntax Notation" in Volume 3 describes notation relating specifically to opcodes.

1011b

A binary value—in this example, a 4-bit value.

F0EAh

A hexadecimal value—in this example a 2-byte value.

[1,2)

A range that includes the left-most value (in this case, 1) but excludes the right-most value (in this case, 2).

7\_4

A bit range, from bit 7 to 4, inclusive. The high-order bit is shown first.

128-bit media instructions

Instructions that use the 128-bit XMM registers. These are a combination of the SSE, SSE2 and SSE3 instruction sets.

64-bit media instructions

Instructions that use the 64-bit MMX registers. These are primarily a combination of MMX<sup>TM</sup> and 3DNow!<sup>TM</sup>

**xvi** Preface

instruction sets, with some additional instructions from the SSE and SSE2 instruction sets.

#### 16-bit mode

Legacy mode or compatibility mode in which a 16-bit address size is active. See *legacy mode* and *compatibility mode*.

#### 32-bit mode

Legacy mode or compatibility mode in which a 32-bit address size is active. See *legacy mode* and *compatibility mode*.

#### 64-bit mode

A submode of *long mode*. In 64-bit mode, the default address size is 64 bits and new features, such as register extensions, are supported for system and application software.

#### #GP(0)

Notation indicating a general-protection exception (#GP) with error code of 0.

#### absolute

Said of a displacement that references the base of a code segment rather than an instruction pointer. Contrast with *relative*.

#### biased exponent

The sum of a floating-point value's exponent and a constant bias for a particular floating-point data type. The bias makes the range of the biased exponent always positive, which allows reciprocation without overflow.

#### byte

Eight bits.

#### clear

To write a bit value of 0. Compare set.

#### compatibility mode

A submode of *long mode*. In compatibility mode, the default address size is 32 bits, and legacy 16-bit and 32-bit applications run without modification.

Preface xvii

#### commit

To irreversibly write, in program order, an instruction's result to software-visible storage, such as a register (including flags), the data cache, an internal write buffer, or memory.

#### CPL

Current privilege level.

#### CR0-CR4

A register range, from register CR0 through CR4, inclusive, with the low-order register first.

#### CR0.PE = 1

Notation indicating that the PE bit of the CR0 register has a value of 1.

#### direct

Referencing a memory location whose address is included in the instruction's syntax as an immediate operand. The address may be an absolute or relative address. Compare indirect.

#### dirty data

Data held in the processor's caches or internal buffers that is more recent than the copy held in main memory.

#### displacement

A signed value that is added to the base of a segment (absolute addressing) or an instruction pointer (relative addressing). Same as *offset*.

#### doubleword

Two words, or four bytes, or 32 bits.

#### double quadword

Eight words, or 16 bytes, or 128 bits. Also called *octword*.

#### DS:rSI

The contents of a memory location whose segment address is in the DS register and whose offset relative to that segment is in the rSI register.

xviii Preface

#### EFER.LME = 0

Notation indicating that the LME bit of the EFER register has a value of 0.

#### effective address size

The address size for the current instruction after accounting for the default address size and any address-size override prefix.

#### effective operand size

The operand size for the current instruction after accounting for the default operand size and any operand-size override prefix.

#### element

See vector.

#### exception

An abnormal condition that occurs as the result of executing an instruction. The processor's response to an exception depends on the type of the exception. For all exceptions except 128-bit media SIMD floating-point exceptions and x87 floating-point exceptions, control is transferred to the handler (or service routine) for that exception, as defined by the exception's vector. For floating-point exceptions defined by the IEEE 754 standard, there are both masked and unmasked responses. When unmasked, the exception handler is called, and when masked, a default response is provided instead of calling the handler.

#### FF /0

Notation indicating that FF is the first byte of an opcode, and a subfield in the second byte has a value of 0.

#### flush

An often ambiguous term meaning (1) writeback, if modified, and invalidate, as in "flush the cache line," or (2) invalidate, as in "flush the pipeline," or (3) change a value, as in "flush to zero."

#### GDT

Global descriptor table.

#### IDT

Interrupt descriptor table.

Preface xix

#### IGN

Ignore. Field is ignored.

#### indirect

Referencing a memory location whose address is in a register or other memory location. The address may be an absolute or relative address. Compare *direct*.

#### IRB

The virtual-8086 mode interrupt-redirection bitmap.

#### IST

The long-mode interrupt-stack table.

#### IVT

The real-address mode interrupt-vector table.

#### LDT

Local descriptor table.

#### legacy x86

The legacy x86 architecture. See "Related Documents" on page xxvii for descriptions of the legacy x86 architecture.

#### legacy mode

An operating mode of the AMD64 architecture in which existing 16-bit and 32-bit applications and operating systems run without modification. A processor implementation of the AMD64 architecture can run in either *long mode* or *legacy mode*. Legacy mode has three submodes, *real mode*, *protected mode*, and *virtual-8086 mode*.

#### long mode

An operating mode unique to the AMD64 architecture. A processor implementation of the AMD64 architecture can run in either *long mode* or *legacy mode*. Long mode has two submodes, 64-bit mode and compatibility mode.

#### lsb

Least-significant bit.

#### LSB

Least-significant byte.

xx Preface

#### main memory

Physical memory, such as RAM and ROM (but not cache memory) that is installed in a particular computer system.

#### mask

(1) A control bit that prevents the occurrence of a floatingpoint exception from invoking an exception-handling routine. (2) A field of bits used for a control purpose.

#### MBZ

Must be zero. If software attempts to set an MBZ bit to 1, a general-protection exception (#GP) occurs.

#### memory

Unless otherwise specified, main memory.

#### **ModRM**

A byte following an instruction opcode that specifies address calculation based on mode (Mod), register (R), and memory (M) variables.

#### moffset

A 16, 32, or 64-bit offset that specifies a memory operand directly without using a ModRM or SIB byte.

#### msb

Most-significant bit.

#### MSB

Most-significant byte.

#### multimedia instructions

A combination of 128-bit media instructions and 64-bit media instructions.

#### octword

Same as double quadword.

#### offset

Same as displacement.

#### overflow

The condition in which a floating-point number is larger in magnitude than the largest, finite, positive or negative

Preface xxi

number that can be represented in the data-type format being used.

#### packed

See vector.

#### PAE

Physical-address extensions.

#### physical memory

Actual memory, consisting of *main memory* and cache.

#### probe

A check for an address in a processor's caches or internal buffers. *External probes* originate outside the processor, and *internal probes* originate within the processor.

#### protected mode

A submode of legacy mode.

#### quadword

Four words, or eight bytes, or 64 bits.

#### RAZ

Read as zero (0), regardless of what is written.

#### real-address mode

See real mode.

#### real mode

A short name for real-address mode, a submode of legacy mode.

#### relative

Referencing with a displacement (also called offset) from an instruction pointer rather than the base of a code segment. Contrast with *absolute*.

#### reserved

Fields marked as reserved may be used at some future time.

To preserve compatibility with future processors, reserved fields require special handling when read or written by software.

Reserved fields may be further qualified as MBZ, RAZ, SBZ or IGN (see definitions).

**xxii** Preface

Software must not depend on the state of a reserved field, nor upon the ability of such fields to return to a previously written state.

If a reserved field is not marked with one of the above qualifiers, software must not change the state of that field; it must reload that field with the same values returned from a prior read.

#### REX

An instruction prefix that specifies a 64-bit operand size and provides access to additional registers.

#### RIP-relative addressing

Addressing relative to the 64-bit RIP instruction pointer.

set

To write a bit value of 1. Compare clear.

#### SIB

A byte following an instruction opcode that specifies address calculation based on scale (S), index (I), and base (B).

#### **SIMD**

Single instruction, multiple data. See *vector*.

#### SSE

Streaming SIMD extensions instruction set. See 128-bit media instructions and 64-bit media instructions.

#### SSE2

Extensions to the SSE instruction set. See 128-bit media instructions and 64-bit media instructions.

#### SSE3

Further extensions to the SSE instruction set. See 128-bit media instructions.

#### sticky bit

A bit that is set or cleared by hardware and that remains in that state until explicitly changed by software.

#### TOP

The x87 top-of-stack pointer.

Preface xxiii

TPR

Task-priority register (CR8).

**TSS**

Task-state segment.

#### underflow

The condition in which a floating-point number is smaller in magnitude than the smallest nonzero, positive or negative number that can be represented in the data-type format being used.

#### vector

- (1) A set of integer or floating-point values, called *elements*, that are packed into a single operand. Most of the 128-bit and 64-bit media instructions use vectors as operands. Vectors are also called *packed* or *SIMD* (single-instruction multiple-data) operands.

- (2) An index into an interrupt descriptor table (IDT), used to access exception handlers. Compare *exception*.

virtual-8086 mode

A submode of legacy mode.

word

Two bytes, or 16 bits.

*x*86

See legacy x86.

#### Registers

In the following list of registers, the names are used to refer either to a given register or to the contents of that register:

AH-DH

The high 8-bit AH, BH, CH, and DH registers. Compare *AL-DL*.

AL-DL

The low 8-bit AL, BL, CL, and DL registers. Compare AH–DH.

*AL-r15B*

The low 8-bit AL, BL, CL, DL, SIL, DIL, BPL, SPL, and R8B-R15B registers, available in 64-bit mode.

**xxiv** Preface

BP

Base pointer register.

CRn

Control register number *n*.

CS

Code segment register.

#### eAX-eSP

The 16-bit AX, BX, CX, DX, DI, SI, BP, and SP registers or the 32-bit EAX, EBX, ECX, EDX, EDI, ESI, EBP, and ESP registers. Compare *rAX-rSP*.

#### EBP

Extended base pointer register.

#### **EFER**

Extended features enable register.

#### **eFLAGS**

16-bit or 32-bit flags register. Compare *rFLAGS*.

#### **EFLAGS**

32-bit (extended) flags register.

eIP

16-bit or 32-bit instruction-pointer register. Compare *rIP*.

**EIP**

32-bit (extended) instruction-pointer register.

#### **FLAGS**

16-bit flags register.

#### **GDTR**

Global descriptor table register.

#### **GPRs**

General-purpose registers. For the 16-bit data size, these are AX, BX, CX, DX, DI, SI, BP, and SP. For the 32-bit data size, these are EAX, EBX, ECX, EDX, EDI, ESI, EBP, and ESP. For the 64-bit data size, these include RAX, RBX, RCX, RDX, RDI, RSI, RBP, RSP, and R8–R15.

Preface xxv

#### **IDTR**

Interrupt descriptor table register.

#### IP

16-bit instruction-pointer register.

#### **LDTR**

Local descriptor table register.

#### MSR

Model-specific register.

#### r8-r15

The 8-bit R8B-R15B registers, or the 16-bit R8W-R15W registers, or the 32-bit R8D-R15D registers, or the 64-bit R8-R15 registers.

#### rAX-rSP

The 16-bit AX, BX, CX, DX, DI, SI, BP, and SP registers, or the 32-bit EAX, EBX, ECX, EDX, EDI, ESI, EBP, and ESP registers, or the 64-bit RAX, RBX, RCX, RDX, RDI, RSI, RBP, and RSP registers. Replace the placeholder r with nothing for 16-bit size, "E" for 32-bit size, or "R" for 64-bit size.

#### RAX

64-bit version of the EAX register.

#### RBP

64-bit version of the EBP register.

#### RBX

64-bit version of the EBX register.

#### RCX

64-bit version of the ECX register.

#### RDI

64-bit version of the EDI register.

#### RDX

64-bit version of the EDX register.

#### **rFLAGS**

16-bit, 32-bit, or 64-bit flags register. Compare *RFLAGS*.

**xxvi** Preface

**RFLAGS**

64-bit flags register. Compare *rFLAGS*.

rIP

16-bit, 32-bit, or 64-bit instruction-pointer register. Compare *RIP*.

RIP

64-bit instruction-pointer register.

RSI

64-bit version of the ESI register.

RSP

64-bit version of the ESP register.

SP

Stack pointer register.

SS

Stack segment register.

TPR

Task priority register, a new register introduced in the AMD64 architecture to speed interrupt management.

TR

Task register.

#### **Endian Order**

The x86 and AMD64 architectures address memory using littleendian byte-ordering. Multibyte values are stored with their least-significant byte at the lowest byte address, and they are illustrated with their least significant byte at the right side. Strings are illustrated in reverse order, because the addresses of their bytes increase from right to left.

## **Related Documents**

- Peter Abel, IBM PC Assembly Language and Programming, Prentice-Hall, Englewood Cliffs, NJ, 1995.

- Rakesh Agarwal, 80x86 Architecture & Programming: Volume II, Prentice-Hall, Englewood Cliffs, NJ, 1991.

- AMD, *AMD-K6*<sup>TM</sup> *MMX*<sup>TM</sup> *Enhanced Processor Multimedia Technology*, Sunnyvale, CA, 2000.

Preface xxvii

- AMD, 3DNow!™ Technology Manual, Sunnyvale, CA, 2000.

- AMD, *AMD Extensions to the 3DNow!*<sup>TM</sup> *and MMX*<sup>TM</sup> *Instruction Sets*, Sunnyvale, CA, 2000.

- Don Anderson and Tom Shanley, *Pentium Processor System Architecture*, Addison-Wesley, New York, 1995.

- Nabajyoti Barkakati and Randall Hyde, *Microsoft Macro Assembler Bible*, Sams, Carmel, Indiana, 1992.

- Barry B. Brey, 8086/8088, 80286, 80386, and 80486 Assembly Language Programming, Macmillan Publishing Co., New York, 1994.

- Barry B. Brey, *Programming the 80286*, 80386, 80486, and *Pentium Based Personal Computer*, Prentice-Hall, Englewood Cliffs, N.J., 1995.

- Ralf Brown and Jim Kyle, *PC Interrupts*, Addison-Wesley, New York, 1994.

- Penn Brumm and Don Brumm, 80386/80486 Assembly Language Programming, Windcrest McGraw-Hill, 1993.

- Geoff Chappell, *DOS Internals*, Addison-Wesley, New York, 1994.

- Chips and Technologies, Inc. *Super386 DX Programmer's Reference Manual*, Chips and Technologies, Inc., San Jose, 1992.

- John Crawford and Patrick Gelsinger, *Programming the* 80386, Sybex, San Francisco, 1987.

- Cyrix Corporation, 5x86 Processor BIOS Writer's Guide, Cyrix Corporation, Richardson, TX, 1995.

- Cyrix Corporation, M1 Processor Data Book, Cyrix Corporation, Richardson, TX, 1996.

- Cyrix Corporation, MX Processor MMX Extension Opcode Table, Cyrix Corporation, Richardson, TX, 1996.

- Cyrix Corporation, *MX Processor Data Book*, Cyrix Corporation, Richardson, TX, 1997.

- Ray Duncan, Extending DOS: A Programmer's Guide to Protected-Mode DOS, Addison Wesley, NY, 1991.

- William B. Giles, Assembly Language Programming for the Intel 80xxx Family, Macmillan, New York, 1991.

- Frank van Gilluwe, *The Undocumented PC*, Addison-Wesley, New York, 1994.

**xxviii** Preface

- John L. Hennessy and David A. Patterson, *Computer Architecture*, Morgan Kaufmann Publishers, San Mateo, CA, 1996.

- Thom Hogan, *The Programmer's PC Sourcebook*, Microsoft Press, Redmond, WA, 1991.

- Hal Katircioglu, *Inside the 486, Pentium, and Pentium Pro*, Peer-to-Peer Communications, Menlo Park, CA, 1997.

- IBM Corporation, 486SLC Microprocessor Data Sheet, IBM Corporation, Essex Junction, VT, 1993.

- IBM Corporation, 486SLC2 Microprocessor Data Sheet, IBM Corporation, Essex Junction, VT, 1993.

- IBM Corporation, 80486DX2 Processor Floating Point Instructions, IBM Corporation, Essex Junction, VT, 1995.

- IBM Corporation, 80486DX2 Processor BIOS Writer's Guide, IBM Corporation, Essex Junction, VT, 1995.

- IBM Corporation, *Blue Lightening 486DX2 Data Book*, IBM Corporation, Essex Junction, VT, 1994.

- Institute of Electrical and Electronics Engineers, *IEEE Standard for Binary Floating-Point Arithmetic*, ANSI/IEEE Std 754-1985.

- Institute of Electrical and Electronics Engineers, *IEEE Standard for Radix-Independent Floating-Point Arithmetic*, ANSI/IEEE Std 854-1987.

- Muhammad Ali Mazidi and Janice Gillispie Mazidi, 80X86 IBM PC and Compatible Computers, Prentice-Hall, Englewood Cliffs, NJ, 1997.

- Hans-Peter Messmer, *The Indispensable Pentium Book*, Addison-Wesley, New York, 1995.

- Karen Miller, An Assembly Language Introduction to Computer Architecture: Using the Intel Pentium, Oxford University Press, New York, 1999.

- Stephen Morse, Eric Isaacson, and Douglas Albert, *The* 80386/387 *Architecture*, John Wiley & Sons, New York, 1987.

- NexGen Inc., *Nx586 Processor Data Book*, NexGen Inc., Milpitas, CA, 1993.

- NexGen Inc., Nx686 Processor Data Book, NexGen Inc., Milpitas, CA, 1994.

Preface xxix

- Bipin Patwardhan, *Introduction to the Streaming SIMD Extensions in the Pentium III*, www.x86.org/articles/sse\_pt1/simd1.htm, June, 2000.

- Peter Norton, Peter Aitken, and Richard Wilton, *PC Programmer's Bible*, Microsoft Press, Redmond, WA, 1993.

- PharLap 386\ASM Reference Manual, Pharlap, Cambridge MA, 1993.

- PharLap TNT DOS-Extender Reference Manual, Pharlap, Cambridge MA, 1995.

- Sen-Cuo Ro and Sheau-Chuen Her, *i386/i486 Advanced Programming*, Van Nostrand Reinhold, New York, 1993.

- Jeffrey P. Royer, *Introduction to Protected Mode Programming*, course materials for an onsite class, 1992.

- Tom Shanley, *Protected Mode System Architecture*, Addison Wesley, NY, 1996.

- SGS-Thomson Corporation, 80486DX Processor SMM Programming Manual, SGS-Thomson Corporation, 1995.

- Walter A. Triebel, *The 80386DX Microprocessor*, Prentice-Hall, Englewood Cliffs, NJ, 1992.

- John Wharton, *The Complete x86*, MicroDesign Resources, Sebastopol, California, 1994.

- Web sites and newsgroups:

- www.amd.com

- news.comp.arch

- news.comp.lang.asm.x86

- news.intel.microprocessors

- news.microsoft

**XXX** Preface

# 1 128-Bit Media Instruction Reference

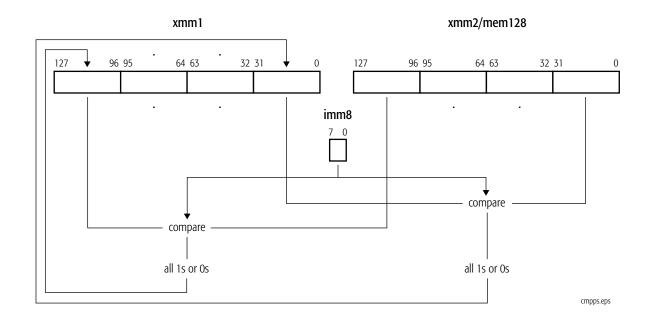

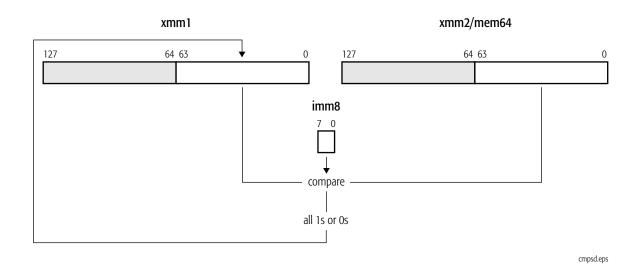

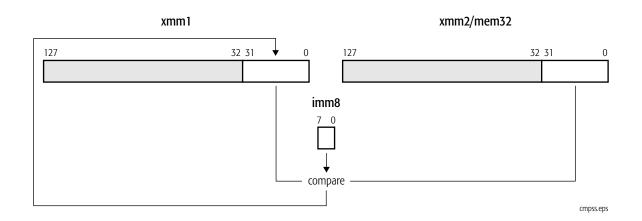

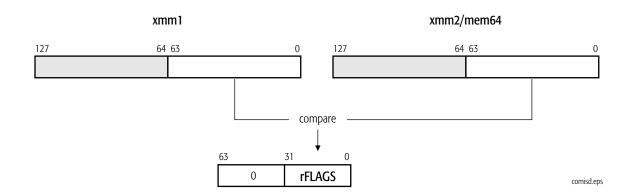

This chapter describes the function, mnemonic syntax, opcodes, affected flags of the 128-bit media instructions and the possible exceptions they generate. These instructions load, store, or operate on data located in 128-bit XMM registers. Most of the instructions operate in parallel on sets of packed elements called *vectors*, although a few operate on scalars. These instructions define both integer and floating-point operations. They include the SSE, SSE2 and SSE3 instructions.

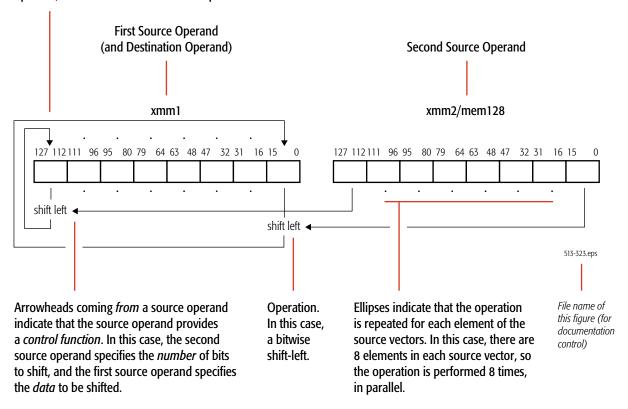

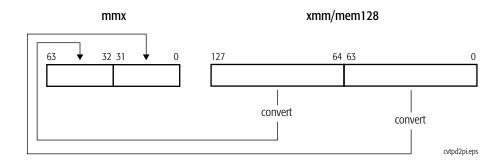

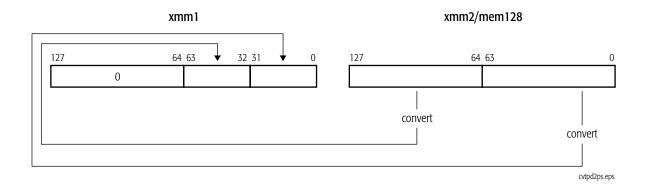

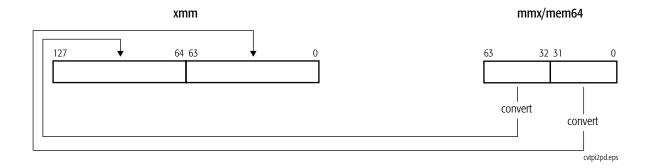

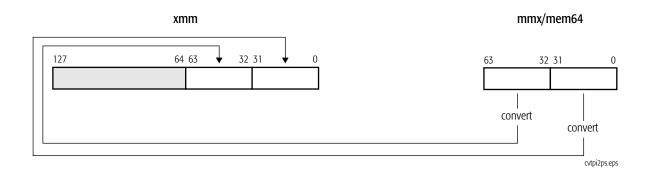

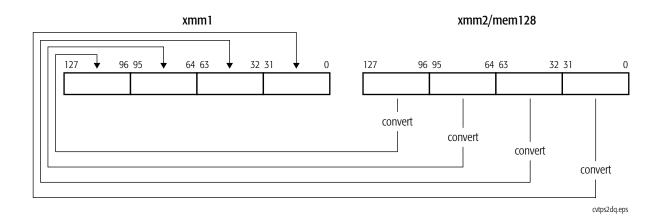

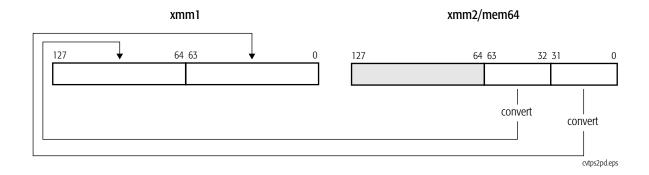

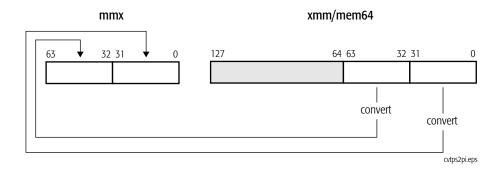

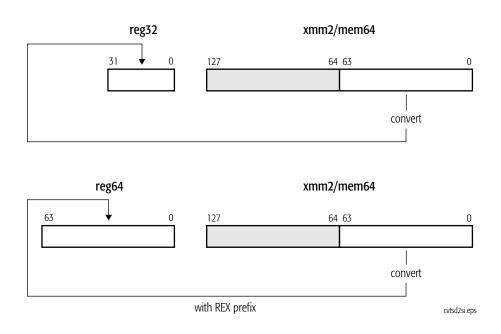

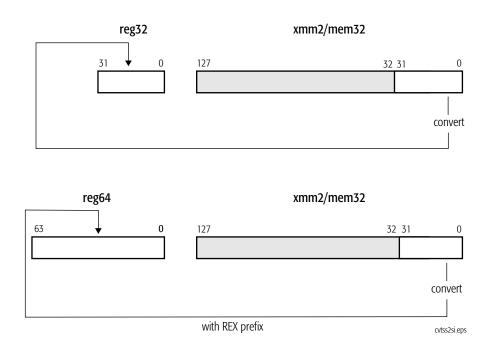

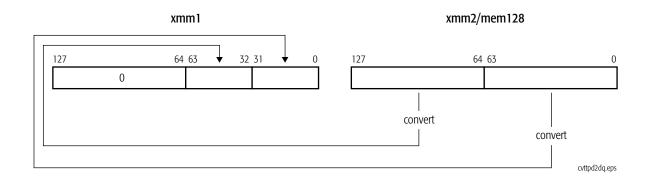

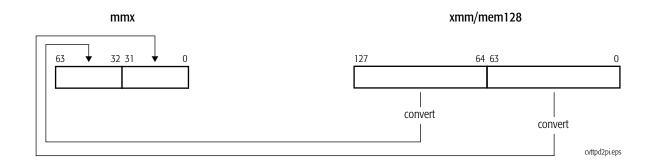

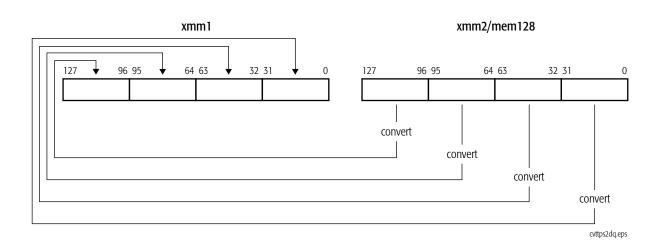

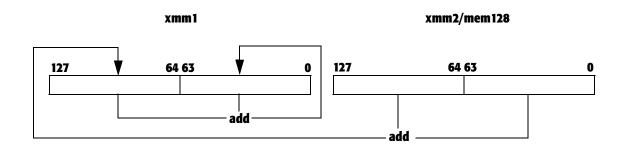

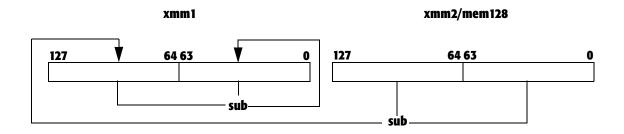

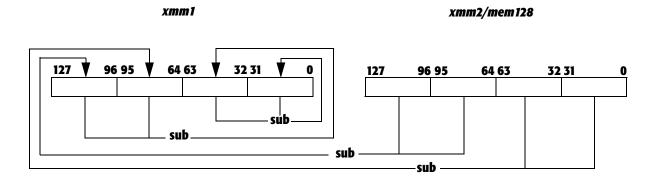

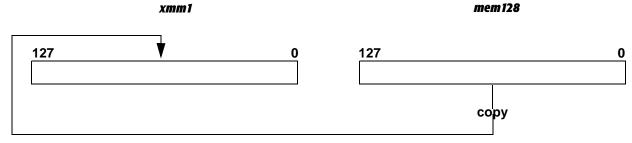

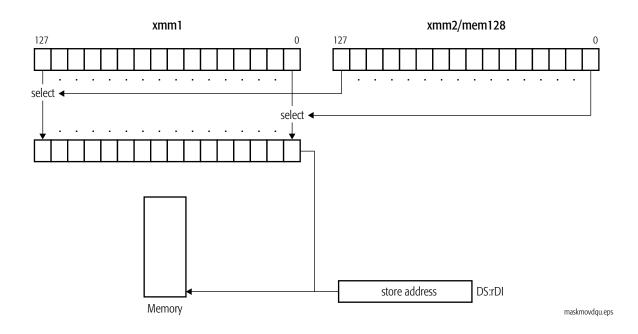

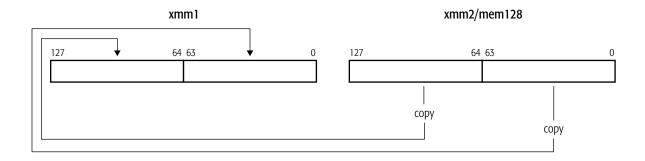

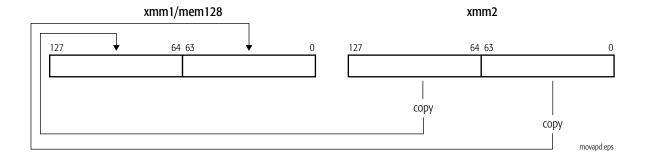

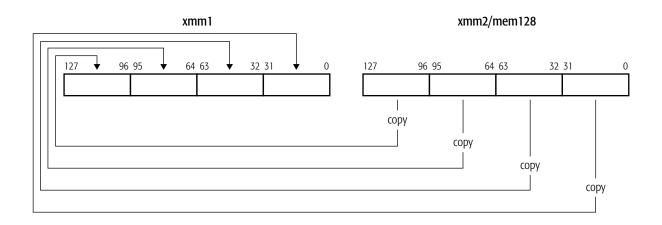

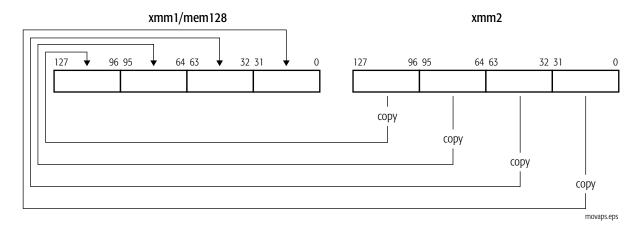

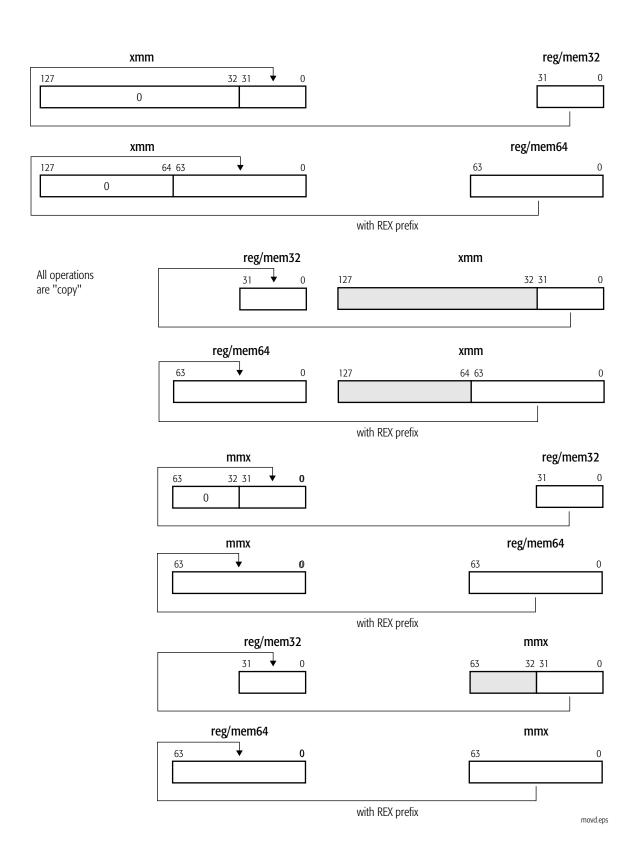

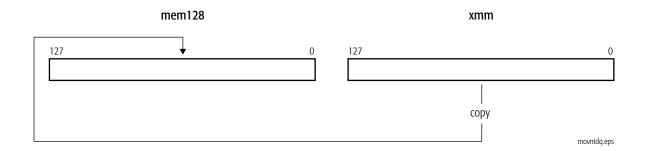

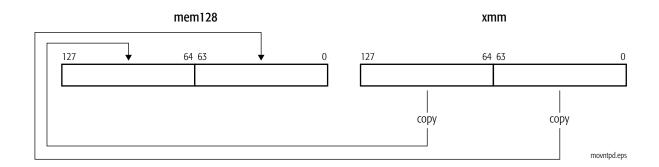

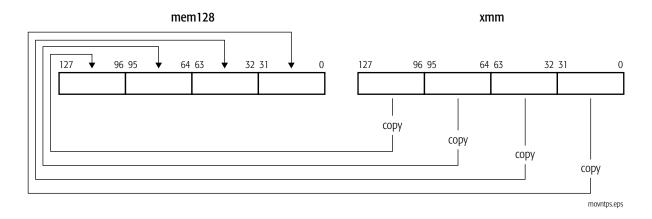

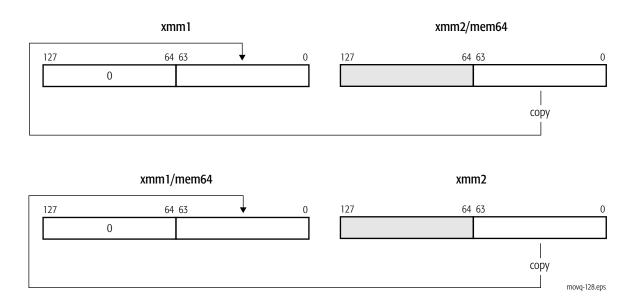

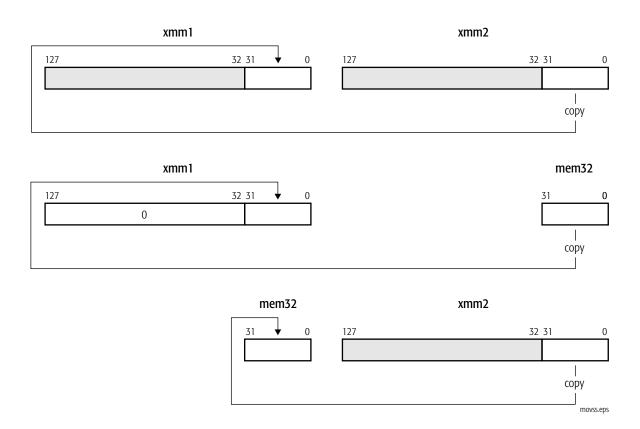

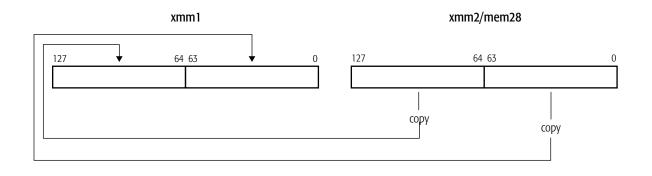

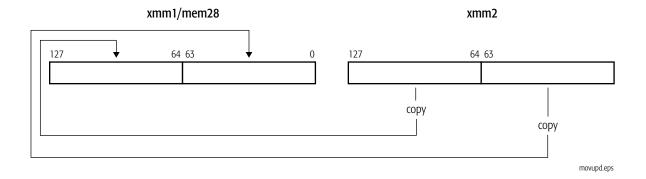

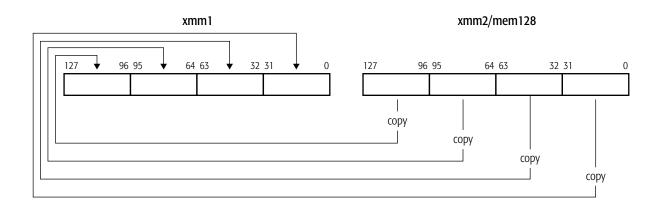

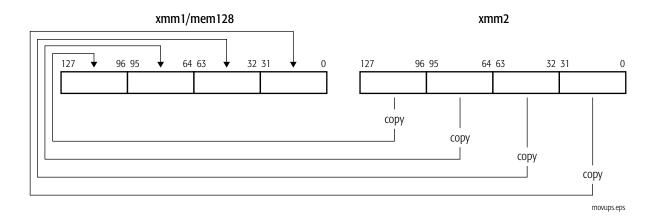

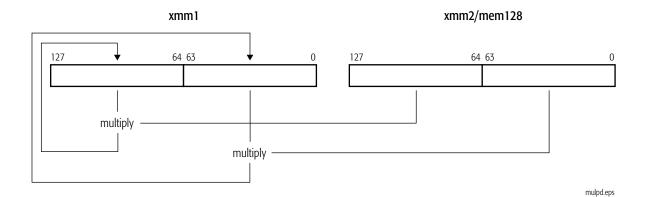

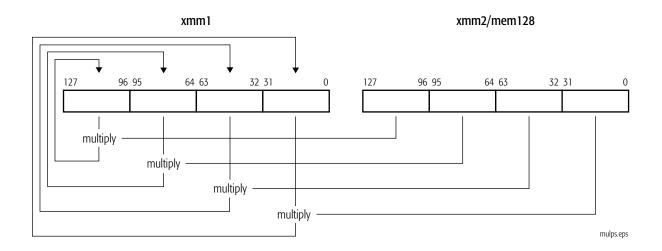

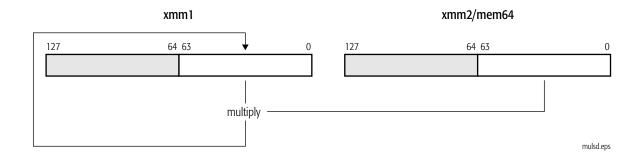

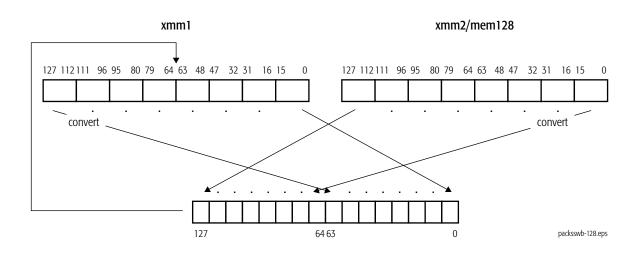

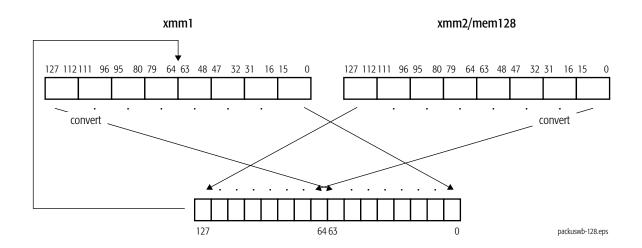

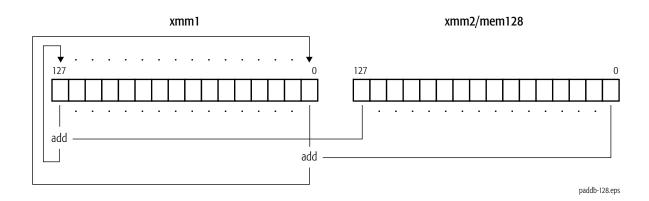

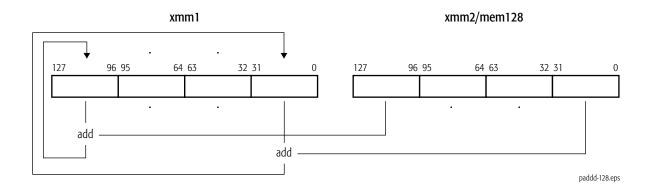

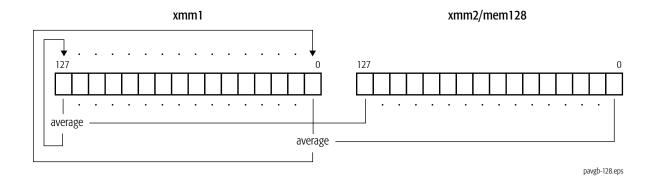

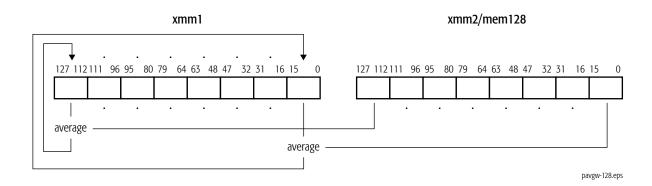

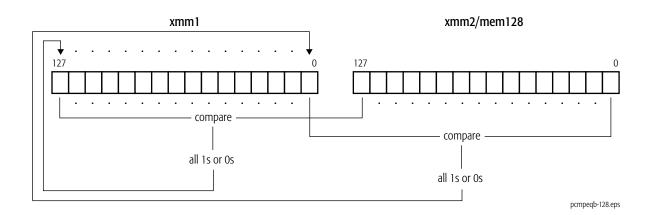

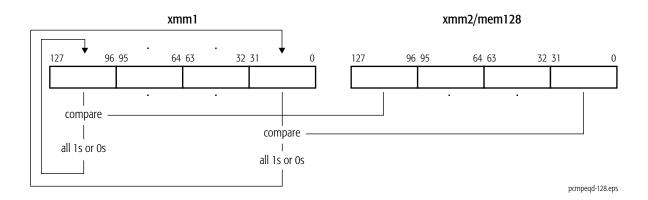

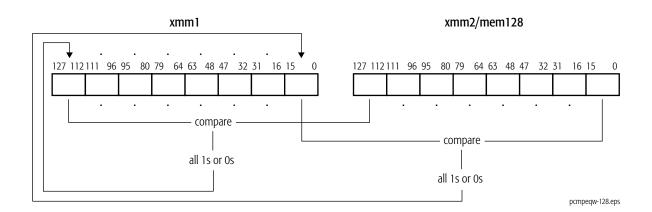

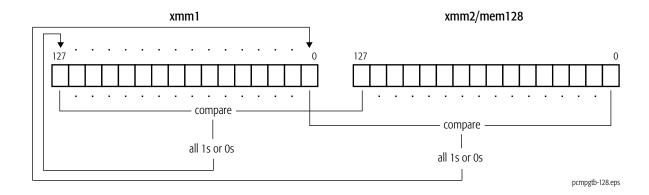

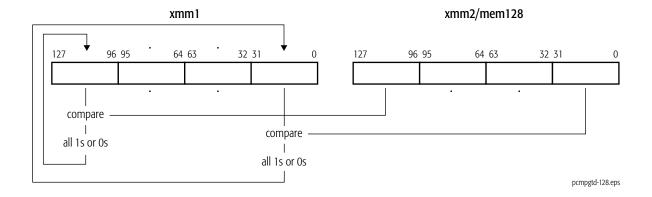

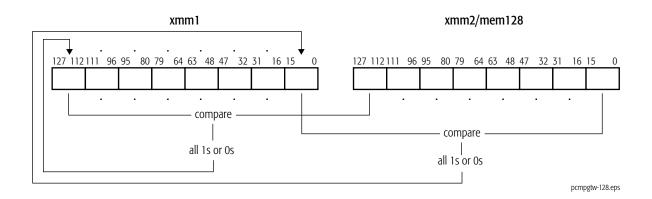

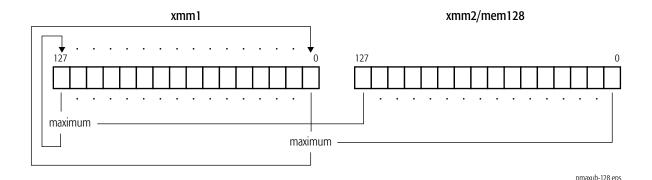

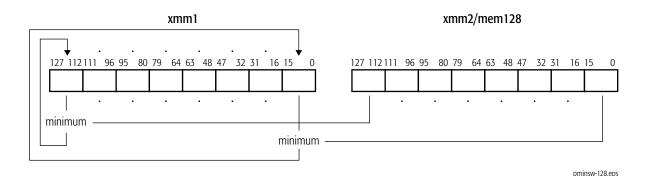

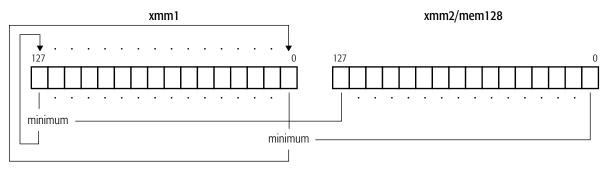

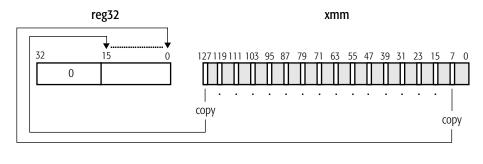

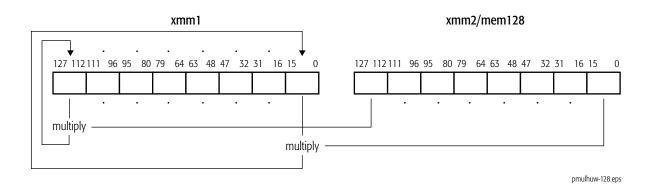

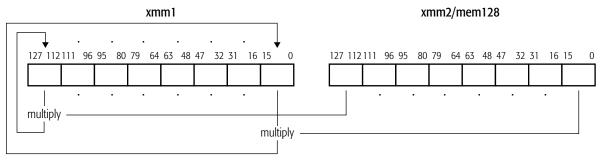

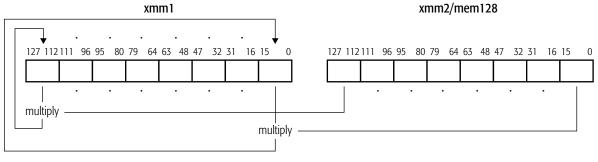

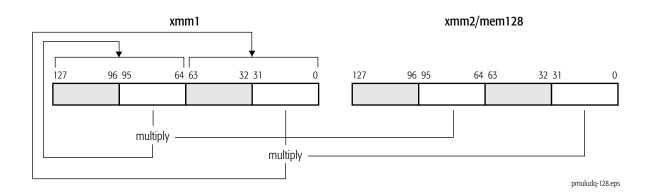

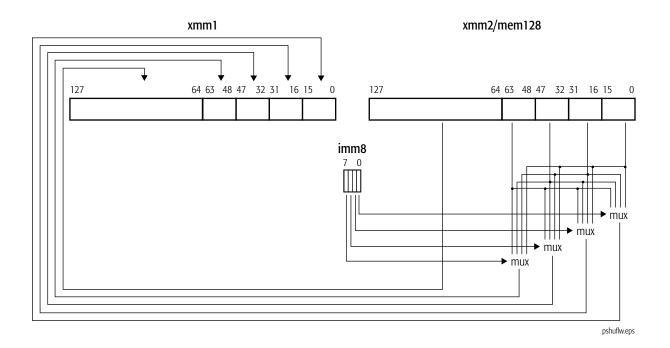

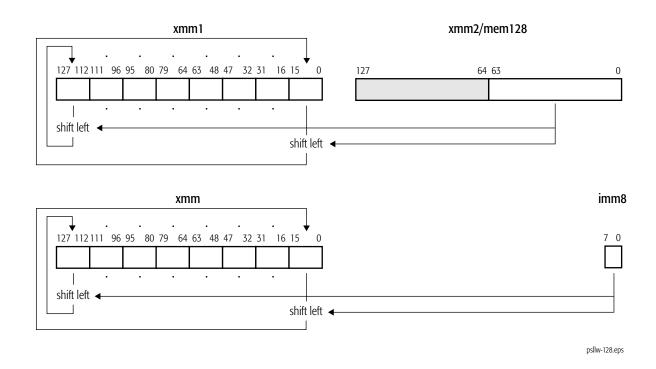

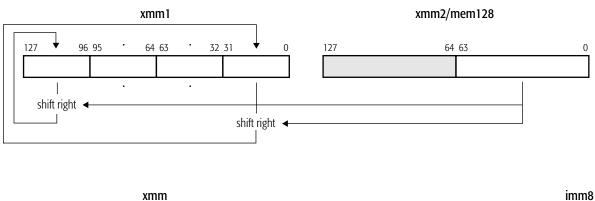

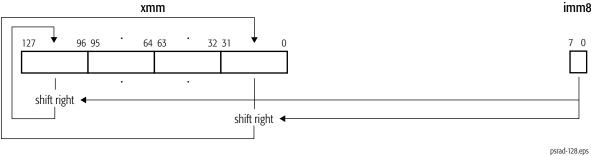

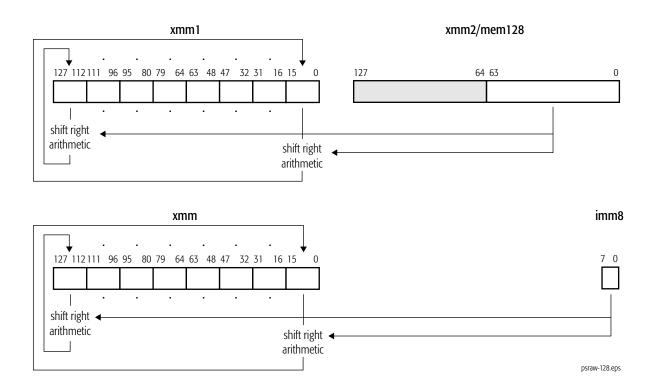

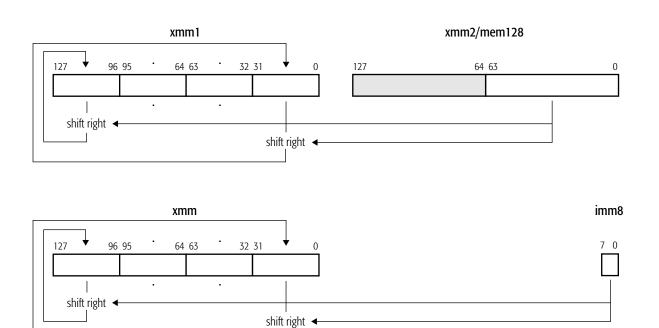

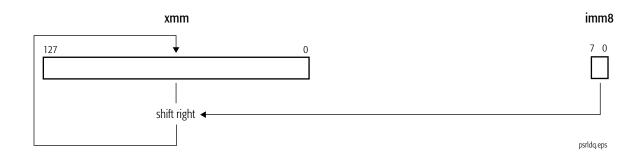

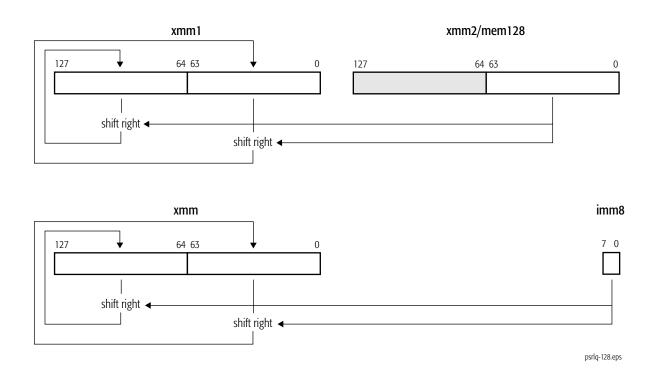

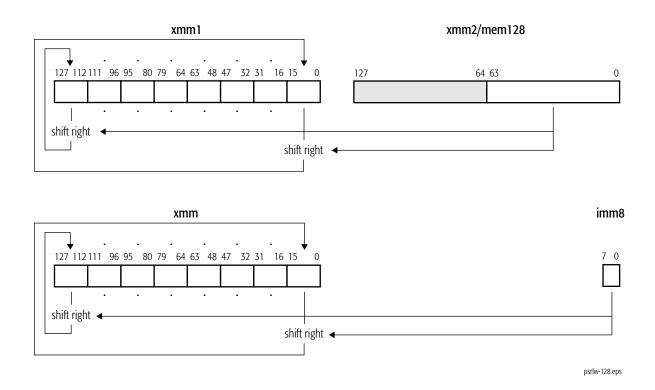

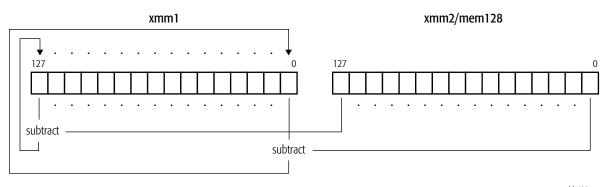

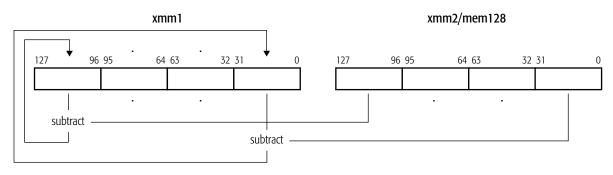

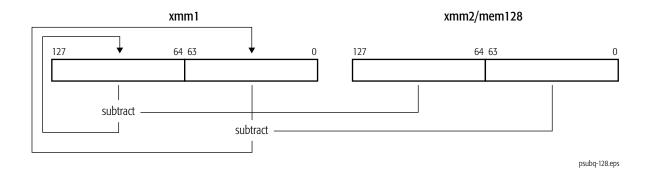

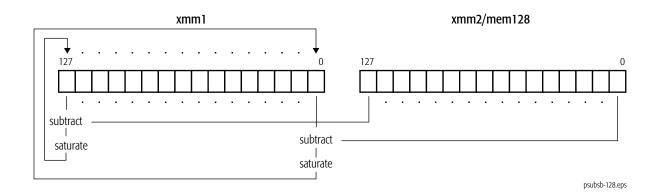

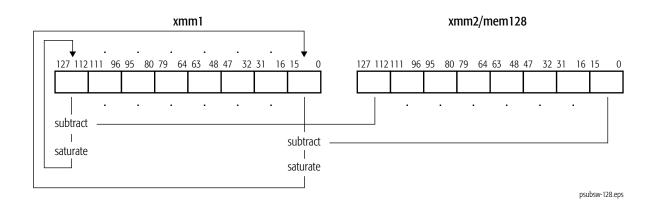

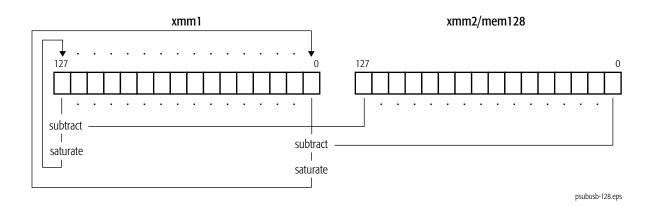

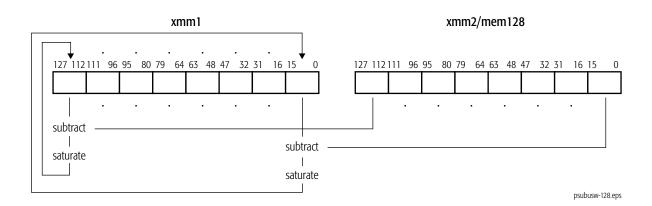

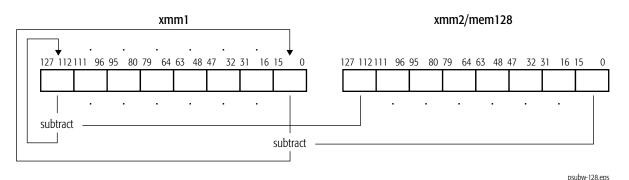

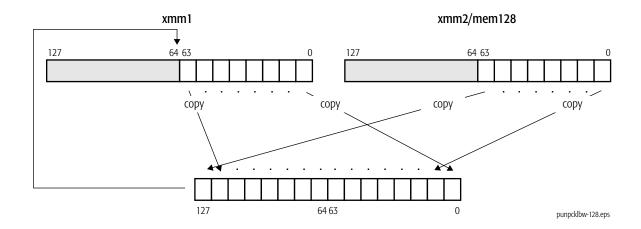

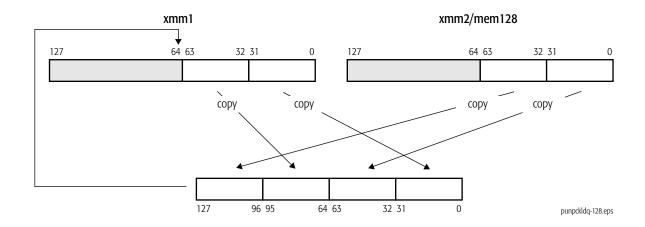

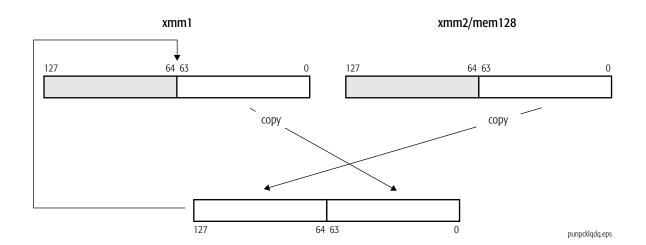

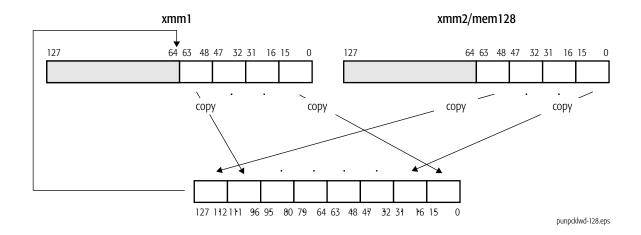

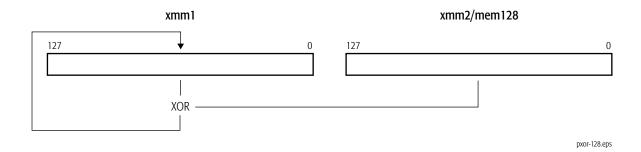

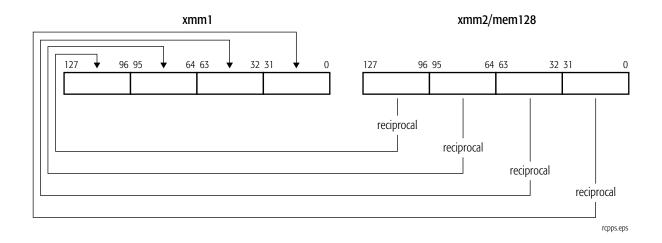

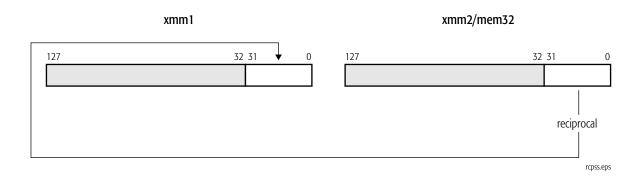

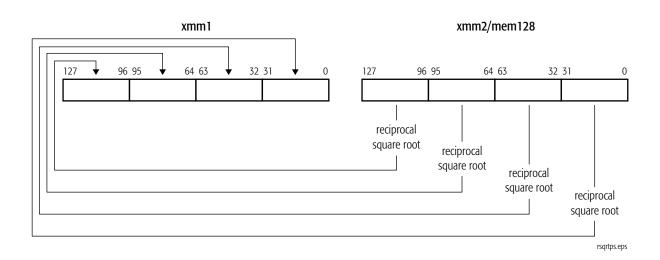

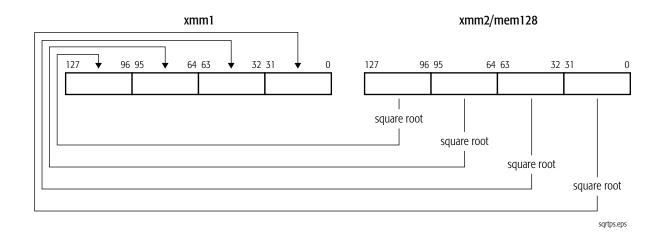

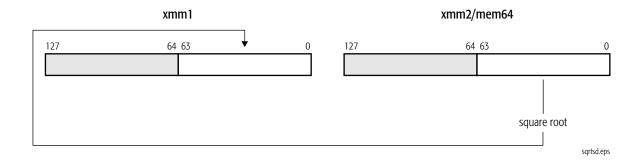

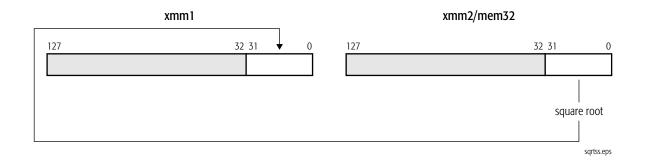

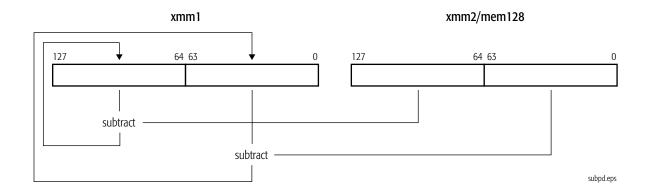

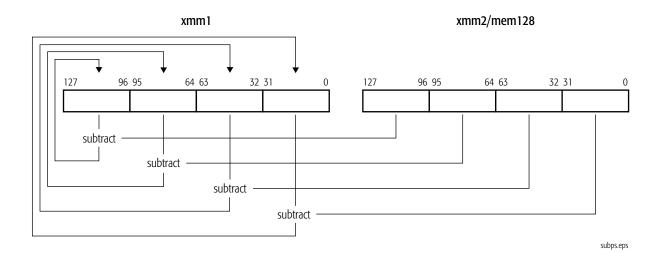

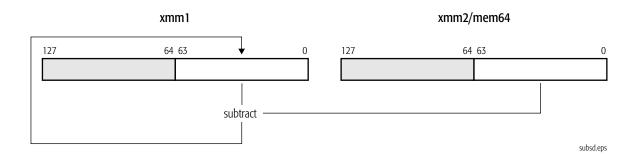

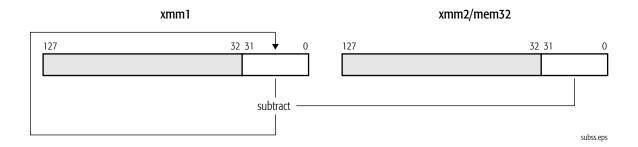

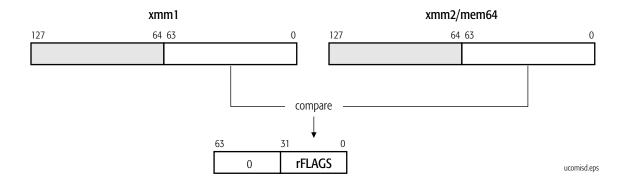

Each instruction that performs a vector (packed) operation is illustrated with a diagram. Figure 1-1 on page 2 shows the conventions used in these diagrams. The particular diagram shows the PSLLW (packed shift left logical words) instruction.

Arrowheads going *to* a source operand indicate the writing of the result. In this case, the result is written to the first source operand, which is also the destination operand.

Figure 1-1. Diagram Conventions for 128-Bit Media Instructions

*Gray* areas in diagrams indicate unmodified operand bits.

The 128-bit media instructions are useful in high-performance applications that operate on blocks of data. Because each instruction can independently and simultaneously perform a single operation on multiple elements of a vector, the instructions are classified as *single-instruction*, *multiple-data* (SIMD) instructions. A few 128-bit media instructions convert operands in XMM registers to operands in GPR, MMX<sup>TM</sup>, or x87 registers (or vice versa), or save or restore XMM state.

Hardware support for a specific 128-bit media instruction depends on the presence of at least one of the following CPUID functions:

- FXSAVE and FXRSTOR, indicated by EDX bit 24 returned by CPUID standard function 1 and extended function 8000\_0001h.

- SSE, indicated by EDX bit 25 returned by CPUID standard function 1.

- SSE2, indicated by EDX bit 26 returned by CPUID standard function 1.

- SSE3, indicated by ECX bit 0 returned by CPUID standard function 1.

The 128-bit media instructions can be used in legacy mode or long mode. Their use in long mode is available if the following CPUID function is set:

■ Long Mode, indicated by EDX bit 29 returned by CPUID extended function 8000\_0001h.

Compilation of 128-bit media programs for execution in 64-bit mode offers four primary advantages: access to the eight extended XMM registers (for a register set consisting of XMM0–XMM15), access to the eight extended, 64-bit general-purpose registers (for a register set consisting of GPR0–GPR15), access to the 64-bit virtual address space, and access to the RIP-relative addressing mode.

#### For further information, see:

- "128-Bit Media and Scientific Programming" in Volume 1.

- "Summary of Registers and Data Types" in Volume 3.

- "Notation" in Volume 3.

- "Instruction Prefixes" in Volume 3.

## **ADDPD**

# **Add Packed Double-Precision Floating-Point**

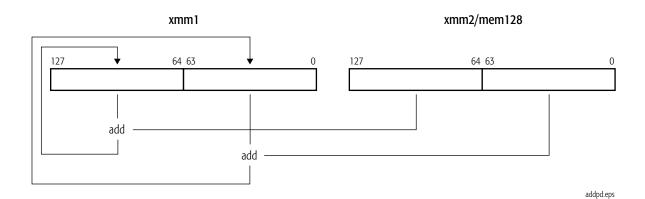

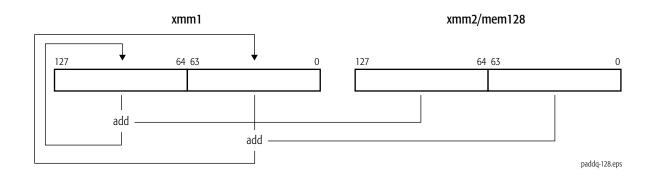

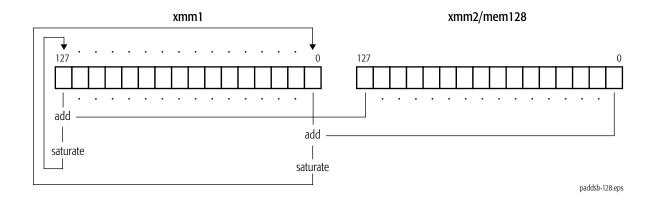

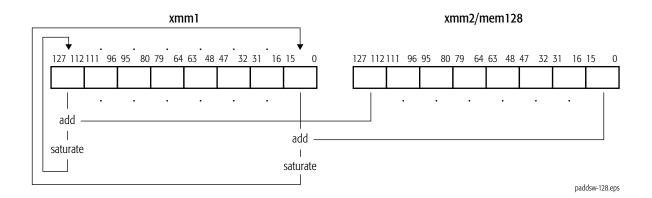

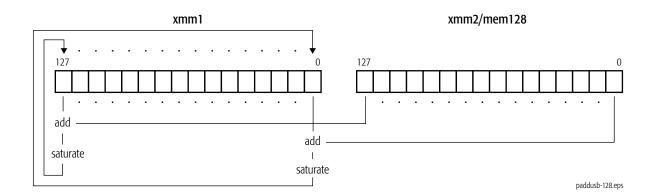

Adds each packed double-precision floating-point value in the first source operand to the corresponding packed double-precision floating-point value in the second source operand and writes the result of each addition in the corresponding quadword of the destination (first source). The first source/destination operand is an XMM register. The second source operand is another XMM register or 128-bit memory location.

The ADDPD instruction is an SSE2 instruction. The presence of this instruction set is indicated by a CPUID feature bit. (See "CPUID" in Volume 3.)

Mnemonic Opcode Description

ADDPD xmm1, xmm2/mem128

66 0F 58 /r

Adds two packed double-precision floating-point values in an XMM register and another XMM register or 128-bit memory location and writes the result in the destination XMM register.

#### **Related Instructions**

ADDPS, ADDSD, ADDSS

#### rFLAGS Affected

None

4 ADDPD

# **MXCSR Flags Affected**

| FZ | R  | C  | PM | UM | OM | ZM | DM | IM | DAZ | PE | UE | OE | ZE | DE | IE |

|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |    |     | М  | М  | M  |    | М  | М  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6   | 5  | 4  | 3  | 2  | 1  | 0  |

Note:

A flag that may be set to one or cleared to zero is M (modified). Unaffected flags are blank.

# **Exceptions**

|                                       |      | Virtual |           |                                                                                                                                       |  |  |  |

|---------------------------------------|------|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Exception                             | Real | 8086    | Protected | Cause of Exception                                                                                                                    |  |  |  |

| Invalid opcode, #UD                   | X    | Х       | Х         | The SSE2 instructions are not supported, as indicated by EDX bit 26 of CPUID standard function 1.                                     |  |  |  |

|                                       | X    | Х       | Х         | The emulate bit (EM) of CR0 was set to 1.                                                                                             |  |  |  |

|                                       | Х    | Х       | Х         | The operating-system FXSAVE/FXRSTOR support bit (OSFXSR) of CR4 was cleared to 0.                                                     |  |  |  |

|                                       | X    | Х       | Х         | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 0. See SIMD Floating-Point Exceptions, below, for details. |  |  |  |

| Device not available, #NM             | Χ    | Х       | Х         | The task-switch bit (TS) of CR0 was set to 1.                                                                                         |  |  |  |

| Stack, #SS                            | X    | Х       | Х         | A memory address exceeded the stack segment limit or was non-canonical.                                                               |  |  |  |

| General protection, #GP               | Х    | Х       | Х         | A memory address exceeded a data segment limit or was non-canonical.                                                                  |  |  |  |

|                                       |      |         | Х         | A null data segment was used to reference memory.                                                                                     |  |  |  |

|                                       | X    | Х       | х         | The memory operand was not aligned on a 16-byte boundary.                                                                             |  |  |  |

| Page fault, #PF                       |      | Х       | Х         | A page fault resulted from the execution of the instruction.                                                                          |  |  |  |

| SIMD Floating-Point<br>Exception, #XF | Х    | Х       | Х         | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 1. See SIMD Floating-Point Exceptions below for details.   |  |  |  |

| SIMD Floating-Point Exceptions        |      |         |           |                                                                                                                                       |  |  |  |

| Invalid-operation exception (IE)      | Х    | Х       | X         | A source operand was an SNaN value.                                                                                                   |  |  |  |

| . , ,                                 | Χ    | Х       | Х         | +infinity was added to -infinity.                                                                                                     |  |  |  |

| Denormalized-operand exception (DE)   | X    | Х       | Х         | A source operand was a denormal value.                                                                                                |  |  |  |

ADDPD 5

| Exception                | Real | Virtual<br>8086 | Protected | Cause of Exception                                                                |

|--------------------------|------|-----------------|-----------|-----------------------------------------------------------------------------------|

| Overflow exception (OE)  | Х    | Х               | Х         | A rounded result was too large to fit into the format of the destination operand. |

| Underflow exception (UE) | Х    | Х               | Х         | A rounded result was too small to fit into the format of the destination operand. |

| Precision exception (PE) | Х    | Х               | Х         | A result could not be represented exactly in the destination format.              |

6 ADDPD

### **ADDPS**

## **Add Packed Single-Precision Floating-Point**

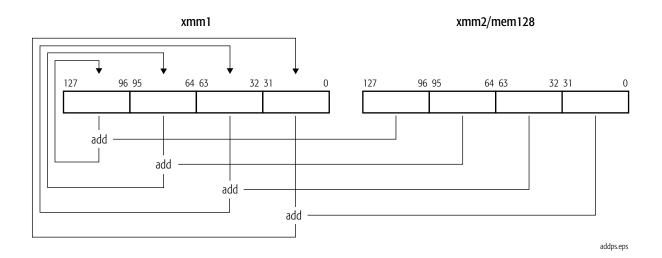

Adds each packed single-precision floating-point value in the first source operand to the corresponding packed single-precision floating-point value in the second source operand and writes the result of each addition in the corresponding quadword of the destination (first source). The first source/destination operand is an XMM register. The second source operand is another XMM register or 128-bit memory location.

The ADDPS instruction is an SSE instruction. The presence of this instruction set is indicated by a CPUID feature bit. (See "CPUID" in Volume 3.)

| Mnemonic | Opcode | Description |

|----------|--------|-------------|

|----------|--------|-------------|

ADDPS xmm1, xmm2/mem128

0F 58 /r

Adds four packed single-precision floating-point values in an XMM register and another XMM register or 128-bit memory location and writes the result in the destination XMM register.

### **Related Instructions**

ADDPD, ADDSD, ADDSS

### rFLAGS Affected

None

ADDPS 7

## **MXCSR Flags Affected**

| FZ | R  | C  | PM | UM | OM | ZM | DM | IM | DAZ | PE | UE | OE | ZE | DE | IE |

|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |    |     | М  | М  | M  |    | М  | M  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6   | 5  | 4  | 3  | 2  | 1  | 0  |

Note:

A flag that may be set to one or cleared to zero is M (modified). Unaffected flags are blank.

## **Exceptions**

| Exception                             | Real | Virtual<br>8086 | Protected    | Cause of Exception                                                                                                                    |

|---------------------------------------|------|-----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Invalid opcode, #UD                   | X    | X               | X            | The SSE instructions are not supported, as indicated by EDX bit 25 of CPUID standard function 1.                                      |

|                                       | Х    | Х               | Х            | The emulate bit (EM) of CR0 was set to 1.                                                                                             |

|                                       | Х    | Х               | Х            | The operating-system FXSAVE/FXRSTOR support bit (OSFXSR) of CR4 was cleared to 0.                                                     |

|                                       | X    | Х               | Х            | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 0. See SIMD Floating-Point Exceptions, below, for details. |

| Device not available, #NM             | Χ    | Χ               | Х            | The task-switch bit (TS) of CR0 was set to 1.                                                                                         |

| Stack, #SS                            | Х    | Х               | Х            | A memory address exceeded the stack segment limit or was non-canonical.                                                               |

| General protection, #GP               | Х    | Х               | Х            | A memory address exceeded a data segment limit or was non-canonical.                                                                  |

|                                       |      |                 | Х            | A null data segment was used to reference memory.                                                                                     |

|                                       | Х    | Х               | Х            | The memory operand was not aligned on a 16-byte boundary.                                                                             |

| Page fault, #PF                       |      | Х               | Х            | A page fault resulted from the execution of the instruction.                                                                          |

| SIMD Floating-Point<br>Exception, #XF | Х    | Х               | Х            | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 1. See SIMD Floating-Point Exceptions, below, for details. |

|                                       |      | SIN             | ИD Floating- | Point Exceptions                                                                                                                      |

| Invalid-operation exception (IE)      | Х    | Х               | Х            | A source operand was an SNaN value.                                                                                                   |

| 5seption (12)                         | Χ    | Х               | Х            | +infinity was added to -infinity.                                                                                                     |

| Denormalized-operand exception (DE)   | Х    | Х               | X            | A source operand was a denormal value.                                                                                                |

8 ADDPS

| Exception                | Real | Virtual<br>8086 | Protected | Cause of Exception                                                                |

|--------------------------|------|-----------------|-----------|-----------------------------------------------------------------------------------|

| Overflow exception (OE)  | Х    | Х               | Х         | A rounded result was too large to fit into the format of the destination operand. |

| Underflow exception (UE) | Х    | Х               | Х         | A rounded result was too small to fit into the format of the destination operand. |

| Precision exception (PE) | Х    | Х               | Х         | A result could not be represented exactly in the destination format.              |

### **ADDSD**

## **Add Scalar Double-Precision Floating-Point**

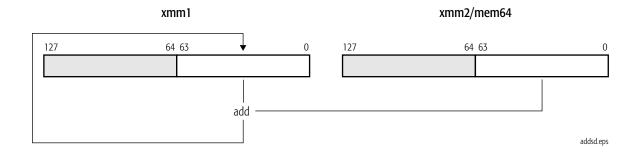

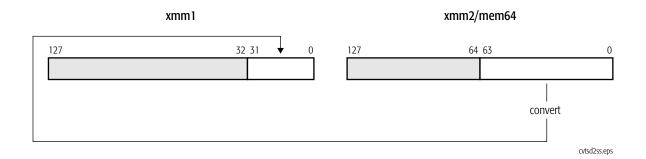

Adds the double-precision floating-point value in the low-order quadword of the first source operand to the double-precision floating-point value in the low-order quadword of the second source operand and writes the result in the low-order quadword of the destination (first source). The high-order quadword of the destination is not modified. The first source/destination operand is an XMM register. The second source operand is another XMM register or 64-bit memory location.

The ADDSD instruction is an SSE2 instruction. The presence of this instruction set is indicated by a CPUID feature bit. (See "CPUID" in Volume 3.)

Mnemonic Opcode Description

ADDSD xmm1, xmm2/mem64

F2 0F 58 /r

Adds low-order double-precision floating-point values in an XMM register and another XMM register or 64-bit memory location and writes the result in the destination XMM register.

### **Related Instructions**

ADDPD, ADDPS, ADDSS

### rFLAGS Affected

None

10 ADDSD

## **MXCSR Flags Affected**

| FZ | R  | C  | PM | UM | OM | ZM | DM | IM | DAZ | PE | UE | OE | ZE | DE | IE |

|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |    |     | М  | М  | M  |    | М  | M  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6   | 5  | 4  | 3  | 2  | 1  | 0  |

Note:

A flag that may be set to one or cleared to zero is M (modified). Unaffected flags are blank.

## **Exceptions**

|                                       |      | Virtual |              |                                                                                                                                       |

|---------------------------------------|------|---------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Exception                             | Real | 8086    | Protected    | Cause of Exception                                                                                                                    |

| Invalid opcode, #UD                   | X    | Х       | Х            | The SSE2 instructions are not supported, as indicated by EDX bit 26 of CPUID standard function 1.                                     |

|                                       | X    | Х       | Х            | The emulate bit (EM) of CR0 was set to 1.                                                                                             |

|                                       | Х    | Х       | Х            | The operating-system FXSAVE/FXRSTOR support bit (OSFXSR) of CR4 was cleared to 0.                                                     |

|                                       | X    | Х       | Х            | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 0. See SIMD Floating-Point Exceptions, below, for details. |

| Device not available, #NM             | Χ    | Х       | Х            | The task-switch bit (TS) of CR0 was set to 1.                                                                                         |

| Stack, #SS                            | Х    | Х       | Х            | A memory address exceeded the stack segment limit or was non-canonical.                                                               |

| General protection, #GP               | Х    | Х       | Х            | A memory address exceeded a data segment limit or was non-canonical.                                                                  |

|                                       |      |         | Х            | A null data segment was used to reference memory.                                                                                     |

| Page fault, #PF                       |      | Х       | Х            | A page fault resulted from the execution of the instruction.                                                                          |

| Alignment check, #AC                  |      | Х       | Х            | An unaligned memory reference was performed while alignment checking was enabled.                                                     |

| SIMD Floating-Point<br>Exception, #XF | Х    | Х       | Х            | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 1. See SIMD Floating-Point Exceptions, below, for details. |

|                                       |      | SIN     | MD Floating- | Point Exceptions                                                                                                                      |

| Invalid-operation exception (IE)      | Х    | Х       | Х            | A source operand was an SNaN value.                                                                                                   |

|                                       | Χ    | Χ       | X            | +infinity was added to -infinity.                                                                                                     |

| Denormalized-operand exception (DE)   | Х    | Х       | Х            | A source operand was a denormal value.                                                                                                |

ADDSD 11

| Exception                | Real | Virtual<br>8086 | Protected | Cause of Exception                                                                |

|--------------------------|------|-----------------|-----------|-----------------------------------------------------------------------------------|

| Overflow exception (OE)  | Х    | Х               | Х         | A rounded result was too large to fit into the format of the destination operand. |

| Underflow exception (UE) | Х    | Х               | Х         | A rounded result was too small to fit into the format of the destination operand. |

| Precision exception (PE) | Х    | Х               | Х         | A result could not be represented exactly in the destination format.              |

12 ADDSD

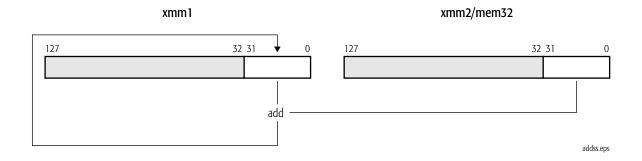

## **ADDSS**

## **Add Scalar Single-Precision Floating-Point**

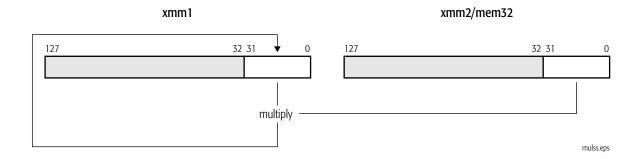

Adds the single-precision floating-point value in the low-order doubleword of the first source operand to the single-precision floating-point value in the low-order doubleword of the second source operand and writes the result in the low-order doubleword of the destination (first source). The three high-order doublewords of the destination are not modified. The first source/destination operand is an XMM register. The second source operand is another XMM register or 32-bit memory location.

The ADDSS instruction is an SSE instruction. The presence of this instruction set is indicated by a CPUID feature bit. (See "CPUID" in Volume 3.)

| Mnemonic               | Opcode     | Description                                                                                                                                                                        |

|------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDSS xmm1, xmm2/mem32 | F3 0F 58/r | Adds low-order single-precision floating-point values in an XMM register and another XMM register or 32-bit memory location and writes the result in the destination XMM register. |

### **Related Instructions**

ADDPD, ADDPS, ADDSD

#### rFLAGS Affected

None

## **MXCSR Flags Affected**

| FZ | R  | C  | PM | UM | OM | ZM | DM | IM | DAZ | PE | UE | OE | ZE | DE | IE |

|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |    |     | М  | М  | М  |    | M  | M  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6   | 5  | 4  | 3  | 2  | 1  | 0  |

Note:

A flag that may be set to one or cleared to zero is M (modified). Unaffected flags are blank.

## **Exceptions**

| Exception                             | Real | Virtual<br>8086 | Protected    | Cause of Exception                                                                                                                    |

|---------------------------------------|------|-----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Invalid opcode, #UD                   | Х    | Х               | Х            | The SSE instructions are not supported, as indicated by EDX bit 25 of CPUID standard function 1.                                      |

|                                       | X    | Х               | Х            | The emulate bit (EM) of CR0 was set to 1.                                                                                             |

|                                       | Х    | Х               | Х            | The operating-system FXSAVE/FXRSTOR support bit (OSFXSR) of CR4 was cleared to 0.                                                     |

|                                       | Х    | Х               | Х            | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 0. See SIMD Floating-Point Exceptions, below, for details. |

| Device not available, #NM             | Х    | Х               | Х            | The task-switch bit (TS) of CR0 was set to 1.                                                                                         |

| Stack, #SS                            | Х    | Х               | Х            | A memory address exceeded the stack segment limit or was non-canonical.                                                               |

| General protection, #GP               | Х    | Х               | Х            | A memory address exceeded a data segment limit or was non-canonical.                                                                  |

|                                       |      |                 | Х            | A null data segment was used to reference memory.                                                                                     |

| Page fault, #PF                       |      | Х               | Х            | A page fault resulted from the execution of the instruction.                                                                          |

| Alignment check, #AC                  |      | Х               | Х            | An unaligned memory reference was performed while alignment checking was enabled.                                                     |

| SIMD Floating-Point<br>Exception, #XF | Х    | Х               | Х            | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 1. See SIMD Floating-Point Exceptions, below, for details. |

|                                       |      | SIN             | ND Floating- | Point Exceptions                                                                                                                      |

| Invalid-operation exception (IE)      | Х    | Х               | Х            | A source operand was an SNaN value.                                                                                                   |

|                                       | Х    | Х               | X            | +infinity was added to -infinity.                                                                                                     |

| Denormalized-operand exception (DE)   | Х    | Х               | Х            | A source operand was a denormal value.                                                                                                |

14 ADDSS

| Exception                | Real | Virtual<br>8086 | Protected | Cause of Exception                                                                |

|--------------------------|------|-----------------|-----------|-----------------------------------------------------------------------------------|

| Overflow exception (OE)  | Х    | Х               | Х         | A rounded result was too large to fit into the format of the destination operand. |

| Underflow exception (UE) | Х    | Х               | Х         | A rounded result was too small to fit into the format of the destination operand. |

| Precision exception (PE) | Х    | Х               | Х         | A result could not be represented exactly in the destination format.              |

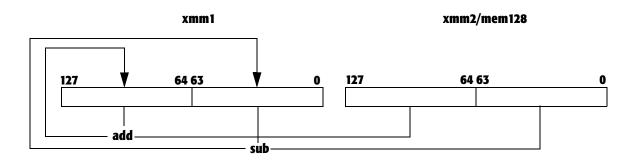

### **ADDSUBPD**

### **Add and Subtract Packed Double-Precision**

Adds the packed double-precision floating-point value in the high 64 bits of the source operand to the double-precision floating-point value in the high 64 bits of the destination operand and stores the sum in the high 64 bits of the destination operand; subtracts the packed double-precision floating-point value in the low 64 bits of the source operand from the low 64 bits of the destination operand and stores the difference in the low 64 bits of the destination operand.

The ADDSUBPD instruction is an SSE3 instruction. The presence of this instruction set is indicated by a CPUID feature bit. (See "CPUID" in Volume 3.)

Mnemonic Opcode Description

ADDSUBPD xmm1, xmm2/mem128 66 0F D0 /r

Adds the value in the upper 64 bits of the source operand to the value in the upper 64 bits of the destination operand and stores the result in the upper 64 bits of the destination operand; subtracts the value in the lower 64 bits of the source operand from the value in the lower 64 bits of the destination operand and stores the result in the lower 64 bits of the destination operand.

### **Related Instructions**

**ADDSUBPS**

### rFLAGS Affected

None

## **MXCSR Flags Affected**

| FZ | R  | C  | PM | UM | OM | ZM | DM | IM | DAZ | PE | UE | OE | ZE | DE | IE |

|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |    |     | М  | М  | M  |    | М  | M  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6   | 5  | 4  | 3  | 2  | 1  | 0  |

Note:

A flag that may be set to one or cleared to zero is M (modified). Unaffected flags are blank.

## **Exceptions**

|                                       |      | Virtual |           |                                                                                                                                       |

|---------------------------------------|------|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| Exception                             | Real | 8086    | Protected | Cause of Exception                                                                                                                    |

| Invalid opcode, #UD                   | Х    | Х       | Х         | The SSE3 instructions are not supported, as indicated by ECX bit 0 of CPUID standard function 1.                                      |

|                                       | X    | Х       | Х         | The emulate bit (EM) of CR0 was set to 1.                                                                                             |

|                                       | Х    | Х       | Х         | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 0. See SIMD Floating-Point Exceptions, below, for details. |

| Device not available, #NM             | Х    | Х       | Х         | The task-switch bit (TS) of CR0 was set to 1.                                                                                         |

| Stack, #SS                            | Х    | Х       | Х         | A memory address exceeded the stack segment limit or was non-canonical.                                                               |

| General protection, #GP               | Х    | Х       | Х         | A memory address exceeded a data segment limit or was non-canonical.                                                                  |

|                                       |      |         | Х         | A null data segment was used to reference memory.                                                                                     |

|                                       | Х    | Х       | Х         | The memory operand was not aligned on a 16-byte boundary.                                                                             |

| Page fault, #PF                       |      | Х       | Х         | A page fault resulted from the execution of the instruction.                                                                          |

| SIMD Floating-Point<br>Exception, #XF | Х    | Х       | Х         | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 1. See SIMD Floating-Point Exceptions below for details.   |

| Exception                           | Real | Virtual<br>8086 | Protected    | Cause of Exception                                                                |  |  |  |  |

|-------------------------------------|------|-----------------|--------------|-----------------------------------------------------------------------------------|--|--|--|--|

|                                     |      | SIN             | ND Floating- | Point Exceptions                                                                  |  |  |  |  |

| Invalid-operation exception (IE)    | Х    | Х               | Х            | A source operand was an SNaN value.                                               |  |  |  |  |

|                                     | Х    | Х               | Х            | +infinity was added to –infinity.                                                 |  |  |  |  |

|                                     | Х    | Х               | Х            | +infinity was subtracted from +infinity.                                          |  |  |  |  |

|                                     | Х    | Х               | Х            | -infinity was subtracted from -infinity.                                          |  |  |  |  |

| Denormalized-operand exception (DE) | Х    | Х               | Х            | A source operand was a denormal value.                                            |  |  |  |  |

| Overflow exception (OE)             | Х    | Х               | Х            | A rounded result was too large to fit into the format of the destination operand. |  |  |  |  |

| Underflow exception (UE)            | Х    | Х               | Х            | A rounded result was too small to fit into the format of the destination operand. |  |  |  |  |

| Precision exception (PE)            | Х    | Х               | Х            | A result could not be represented exactly in the destination format.              |  |  |  |  |

18 ADDSUBPD

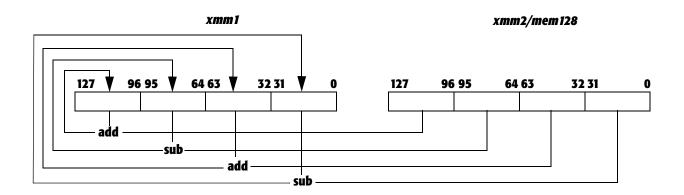

### **ADDSUBPS**

## **Add and Subtract Packed Single-Precision**

Subtracts the first and third single-precision floating-point values in the source operand from the first and third single-precision floating-point values of the destination operand and stores the result in the first and third values of the destination operand. Simultaneously, the instruction adds the second and fourth single-precision floating-point values in the source operand to the second and fourth single-precision floating-point values in the destination operand and stores the result in the second and fourth values of the destination operand.

The ADDSUBPS instruction is an SSE3 instruction. The presence of this instruction set is indicated by a CPUID feature bit. (See "CPUID" in Volume 3.)

### Mnemonic Opcode Description

ADDSUBPS xmm1, xmm2/mem128 F2 0F D0 /r

Subtracts the first and third packed single-precision values in the source XMM register or 128-bit memory operand from the corresponding values in the destination XMM register and stores the resulting values in the corresponding positions in the destination register; simultaneously, adds the second and fourth packed single-precision values in the source XMM register or 128-bit memory operand to the corresponding values in the destination register and stores the result in the corresponding positions in the destination register.

#### **Related Instructions**

ADDSUBPD

## rFLAGS Affected

None

## **MXCSR Flags Affected**

| FZ | R  | C  | PM | UM | OM | ZM | DM | IM | DAZ | PE | UE | OE | ZE | DE | IE |

|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |    |     | M  | М  | М  |    | M  | M  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6   | 5  | 4  | 3  | 2  | 1  | 0  |

Note:

A flag that may be set to one or cleared to zero is M (modified). Unaffected flags are blank.

## **Exceptions**

| Exception                             | Real | Virtual<br>8086 | Protected | Cause of Exception                                                                                                                    |

|---------------------------------------|------|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| Invalid opcode, #UD                   | Х    | Х               | Х         | The SSE3 instructions are not supported, as indicated by ECX bit 0 of CPUID standard function 1.                                      |

|                                       | X    | Х               | Х         | The emulate bit (EM) of CR0 was set to 1.                                                                                             |

|                                       | Х    | Х               | Х         | The operating-system FXSAVE/FXRSTOR support bit (OSFXSR) of CR4 was cleared to 0.                                                     |

|                                       | Х    | Х               | Х         | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 0. See SIMD Floating-Point Exceptions, below, for details. |

| Device not available, #NM             | Х    | Х               | Х         | The task-switch bit (TS) of CR0 was set to 1.                                                                                         |

| Stack, #SS                            |      |                 | Х         | A memory address exceeded the stack segment limit or was non-canonical.                                                               |

| General protection, #GP               | Х    | Х               | Х         | A memory address exceeded a data segment limit or was non-canonical.                                                                  |

|                                       |      |                 | Х         | Anull data segment was used to reference memory.                                                                                      |

|                                       | Х    | Х               | Х         | The memory operand was not aligned on a 16-byte boundary.                                                                             |

| Page fault, #PF                       |      | Х               | Х         | A page fault resulted from the execution of the instruction.                                                                          |

| SIMD Floating-Point<br>Exception, #XF | Х    | Х               | Х         | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 1. See SIMD Floating-Point Exceptions below for details.   |

20 ADDSUBPS

|                                     |      | Virtual |              |                                                                                   |

|-------------------------------------|------|---------|--------------|-----------------------------------------------------------------------------------|

| Exception                           | Real | 8086    | Protected    | Cause of Exception                                                                |

|                                     |      | SIN     | MD Floating- | Point Exceptions                                                                  |

| Invalid-operation exception (IE)    | Х    | Х       | Х            | A source operand was an SNaN value.                                               |

|                                     | Х    | Х       | Х            | +infinity was added to –infinity.                                                 |

|                                     | Х    | Х       | Х            | +infinity was subtracted from +infinity.                                          |

|                                     | Х    | Х       | Х            | -infinity was subtracted from -infinity.                                          |

| Denormalized-operand exception (DE) | Х    | Х       | Х            | A source operand was a denormal value.                                            |

| Overflow exception (OE)             | Х    | Х       | Х            | A rounded result was too large to fit into the format of the destination operand. |

| Underflow exception (UE)            | Х    | Х       | Х            | A rounded result was too small to fit into the format of the destination operand. |

| Precision exception (PE)            | Х    | Х       | Х            | A result could not be represented exactly in the destination format.              |

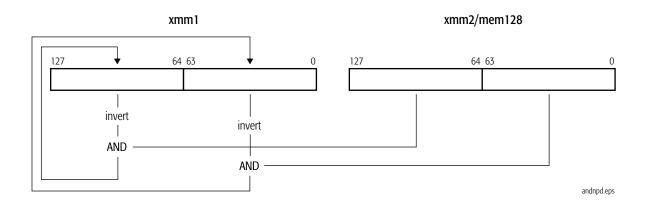

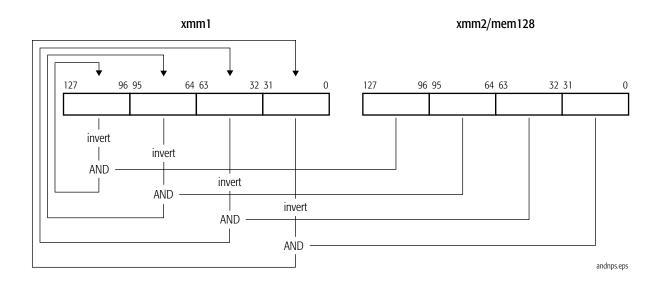

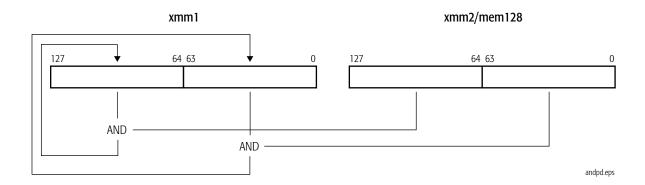

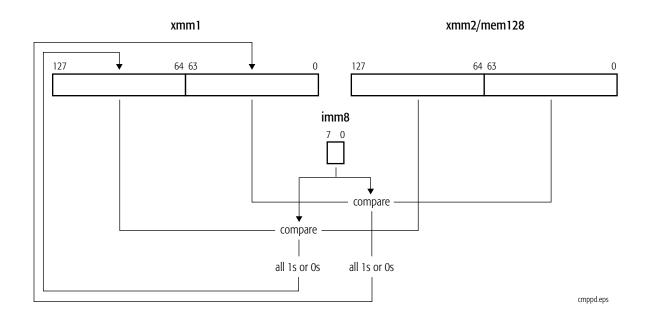

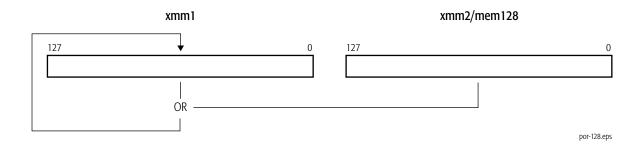

### **ANDNPD**

# **Logical Bitwise AND NOT Packed Double-Precision Floating-Point**

Performs a bitwise logical AND of the two packed double-precision floating-point values in the second source operand and the one's-complement of the corresponding two packed double-precision floating-point values in the first source operand and writes the result in the destination (first source). The first source/destination operand is an XMM register. The second source operand is another XMM register or 128-bit memory location.

The ADDNPD instruction is an SSE2 instruction. The presence of this instruction set is indicated by a CPUID feature bit. (See "CPUID" in Volume 3.)

Mnemonic Opcode Description

ANDNPD xmm1, xmm2/mem128

66 0F 55 /r

Performs bitwise logical AND NOT of two packed doubleprecision floating-point values in an XMM register and another XMM register or 128-bit memory location and writes the result in the destination XMM register.

### **Related Instructions**

ANDNPS, ANDPD, ANDPS, ORPD, ORPS, XORPD, XORPS

#### rFLAGS Affected

None

### **MXCSR Flags Affected**

22 ANDNPD

## None

# Exceptions

| Exception                    | Real | Virtual<br>8086 | Protected | Cause of Exception                                                                                                                    |

|------------------------------|------|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| Invalid opcode, #UD          | Х    | Х               | Х         | The SSE2 instructions are not supported, as indicated by EDX bit 26 of CPUID standard function 1.                                     |

|                              | X    | Х               | Х         | The emulate bit (EM) of CR0 was set to 1.                                                                                             |

|                              | Х    | Х               | Х         | The operating-system FXSAVE/FXRSTOR support bit (OSFXSR) of CR4 was cleared to 0.                                                     |

|                              | X    | Х               | Х         | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT = 0. See SIMD Floating-Point Exceptions, below, for details. |

| Device not available,<br>#NM | Х    | Х               | Х         | The task-switch bit (TS) of CR0 was set to 1.                                                                                         |

| Stack, #SS                   | Х    | Х               | Х         | A memory address exceeded the stack segment limit or was non-canonical.                                                               |

| General protection, #GP      | Х    | Х               | Х         | A memory address exceeded a data segment limit or was non-canonical.                                                                  |

|                              |      |                 | Х         | A null data segment was used to reference memory.                                                                                     |

|                              | Х    | Х               | Х         | The memory operand was not aligned on a 16-byte boundary.                                                                             |

| Page fault, #PF              |      | Х               | Х         | A page fault resulted from the execution of the instruction.                                                                          |

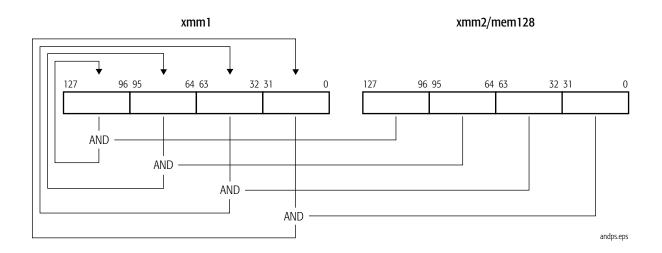

### **ANDNPS**

# **Logical Bitwise AND NOT Packed Single-Precision Floating-Point**

Performs a bitwise logical AND of the four packed single-precision floating-point values in the second source operand and the one's-complement of the corresponding four packed single-precision floating-point values in the first source operand and writes the result in the destination (first source). The first source/destination operand is an XMM register. The second source operand is another XMM register or 128-bit memory location.

The ADDNPS instruction is an SSE2 instruction. The presence of this instruction set is indicated by a CPUID feature bit. (See "CPUID" in Volume 3.)

### Mnemonic Opcode Description

ANDNPS xmm1, xmm2/mem128

0F 55 /r

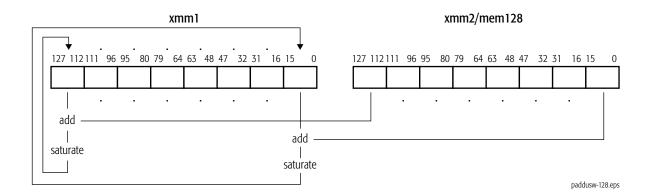

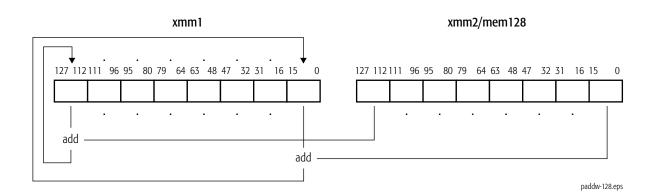

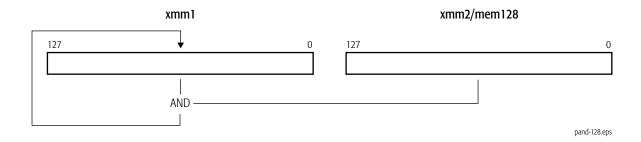

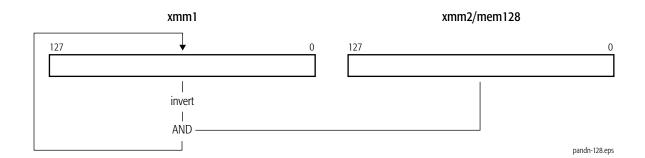

Performs bitwise logical AND NOT of four packed single-precision floating-point values in an XMM register and in another XMM register or 128-bit memory location and writes the result in the destination XMM register.