# **AMD64 Technology**

# AMD64 Architecture Programmer's Manual Volume 3: General-Purpose and System Instructions

| Publication No. | Revision | Date       |

|-----------------|----------|------------|

| 24594           | 3.04     | April 2003 |

© 2002, 2003 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

### **Trademarks**

AMD, the AMD arrow logo, AMD Athlon, AMD Duron, and combinations thereof, and 3DNow! are trademarks, and Am486,  $Am5_x86$ , and AMD-K6 are registered trademarks of Advanced Micro Devices, Inc.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

Windows NT is a registered trademark of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **Contents**

| Figure | S                                             |                                                                                                                                                                                                                                                                                                                                                                                                 | ix                                                   |

|--------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Tables | 5                                             |                                                                                                                                                                                                                                                                                                                                                                                                 | хi                                                   |

| Revisi | on Hist                                       | ory                                                                                                                                                                                                                                                                                                                                                                                             | xiii                                                 |

| Prefac | _                                             |                                                                                                                                                                                                                                                                                                                                                                                                 | χV                                                   |

|        | Audio<br>Conta<br>Organ<br>Defin              | t This Book ence cact Information nization at ions                                                                                                                                                                                                                                                                                                                                              | . xv<br>. xv<br>. xv<br>. xvi                        |

| 1      | Instru                                        | ction Formats                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                    |

|        | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7 | Instruction Byte Order Instruction Prefixes. Summary of Legacy Prefixes Operand-Size Override Prefix Address-Size Override Prefix Segment-Override Prefixes Lock Prefix. Repeat Prefixes REX Prefixes Opcode ModRM and SIB Bytes Displacement Bytes. Immediate Bytes RIP-Relative Addressing Encoding. REX Prefix and RIP-Relative Addressing. Address-Size Prefix and RIP-Relative Addressing. | 3<br>5<br>6<br>9<br>10<br>14<br>20<br>22<br>23<br>23 |

| 2      | Instru                                        | ction Overview                                                                                                                                                                                                                                                                                                                                                                                  | 27                                                   |

|        | 2.1<br>2.2<br>2.3<br>2.4<br>2.5               | Instruction Subsets                                                                                                                                                                                                                                                                                                                                                                             | 28<br>30<br>33<br>35<br>38<br>40                     |

|   | Mnemonic Syntax43                        |

|---|------------------------------------------|

|   | Opcode Syntax46                          |

|   | Pseudocode Definitions                   |

| 3 | General-Purpose Instruction Reference 59 |

|   | AAA                                      |

|   | AAD62                                    |

|   | AAM                                      |

|   | AAS64                                    |

|   | ADC65                                    |

|   | ADD67                                    |

|   | AND69                                    |

|   | BOUND72                                  |

|   | BSF74                                    |

|   | BSR                                      |

|   | BSWAP                                    |

|   | BT79                                     |

|   | BTC                                      |

|   | BTR83                                    |

|   | BTS                                      |

|   | CALL (Near)                              |

|   | CALL (Far)                               |

|   | CBW<br>CWDE                              |

|   | CDQE96                                   |

|   | CWD                                      |

|   | CDQ                                      |

|   | CQO97                                    |

|   | CLC98                                    |

|   | CLD99                                    |

|   | CLFLUSH                                  |

|   | CMC                                      |

|   | CMOV <i>cc</i>                           |

|   | CMP107                                   |

|   | CMPSx                                    |

|   | CMPXCHG113                               |

|   | CMPXCHG8B115                             |

|   | CPUID117                                 |

|   | DAA131                                   |

|   | DAS                                      |

|   | DEC133                                   |

|   | DIV                                      |

|   | ENTER                                    |

|   | IDIV                                     |

|   | IMUL141                                  |

|   | IN144                                    |

|   | INC                                      |

|   | INSx                                     |

## AMD64 Technology

### 24594 Rev. 3.04 April 2003

| INT                                                                                                                            |                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| INTO                                                                                                                           |                                                                                                |

| Jcc                                                                                                                            |                                                                                                |

| JCXZ                                                                                                                           |                                                                                                |

| JMP (Near)                                                                                                                     |                                                                                                |

| JMP (Far)                                                                                                                      |                                                                                                |

| LAHF                                                                                                                           | 173                                                                                            |

| LDS                                                                                                                            |                                                                                                |

| LES                                                                                                                            |                                                                                                |

| LFS                                                                                                                            |                                                                                                |

| LGS                                                                                                                            |                                                                                                |

| LSS                                                                                                                            |                                                                                                |

| LEA                                                                                                                            |                                                                                                |

| LEAVE                                                                                                                          |                                                                                                |

| LFENCE                                                                                                                         |                                                                                                |

| LODSx                                                                                                                          |                                                                                                |

| LOOPcc                                                                                                                         |                                                                                                |

| MFENCE                                                                                                                         |                                                                                                |

| MOV                                                                                                                            |                                                                                                |

| MOVD                                                                                                                           |                                                                                                |

| MOVMSKPD                                                                                                                       |                                                                                                |

| MOVMSKPS                                                                                                                       |                                                                                                |

| MOVNTI                                                                                                                         | 198                                                                                            |

|                                                                                                                                |                                                                                                |

| MOVS                                                                                                                           |                                                                                                |

| MOVSB                                                                                                                          |                                                                                                |

| MOVSB<br>MOVSW                                                                                                                 |                                                                                                |

| MOVSB<br>MOVSW<br>MOVSD                                                                                                        |                                                                                                |

| MOVSB<br>MOVSW<br>MOVSD<br>MOVSQ                                                                                               |                                                                                                |

| MOVSB MOVSW MOVSD MOVSQ                                                                                                        | 202                                                                                            |

| MOVSB MOVSW MOVSD MOVSQ                                                                                                        | 202<br>203                                                                                     |

| MOVSB MOVSW MOVSD MOVSQ                                                                                                        | 202<br>203<br>204                                                                              |

| MOVSB MOVSW MOVSD MOVSQ                                                                                                        | 202<br>203<br>204<br>205                                                                       |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG.                                                                         | 202<br>203<br>204<br>205                                                                       |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG.                                                                         | 202<br>203<br>204<br>205<br>207                                                                |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG.                                                                         | 202<br>203<br>204<br>205<br>207                                                                |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG.                                                                         | 202<br>203<br>204<br>205<br>207<br>210                                                         |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG. NOP. NOT.                                                               | 202<br>203<br>204<br>205<br>207<br>209<br>211<br>214                                           |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG. NOP. NOT. OR. OUT.                                                      | 202<br>203<br>204<br>205<br>207<br>209<br>210<br>214<br>214                                    |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG. NOP. NOT.                                                               | 202<br>203<br>204<br>205<br>207<br>209<br>210<br>214<br>214                                    |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG. NOP. NOT. OR. OUT.                                                      | 202<br>203<br>204<br>205<br>207<br>210<br>214<br>216<br>218                                    |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG. NOP. NOT. OR. OUT.                                                      | 202<br>203<br>204<br>205<br>207<br>210<br>211<br>214<br>218                                    |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG. NOP. NOT. OR. OUT. OUTSx POP POPAx.                                     | 202<br>203<br>204<br>205<br>207<br>210<br>211<br>214<br>218<br>221                             |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG. NOP. NOT. OR OUT. OUTSx POP POPAx. POPFx.                               | 202<br>203<br>204<br>205<br>207<br>210<br>211<br>214<br>216<br>221                             |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG. NOP. NOT. OR OUT. OUTSx POP POPAx. POPFx PREFETCHx                      | 202<br>203<br>204<br>205<br>207<br>210<br>214<br>214<br>218<br>221<br>222<br>225               |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG. NOP. NOT. OR OUT. OUTSx POP POPAx. POPFx. PREFETCHx PREFETCHlevel.      | 202<br>203<br>204<br>205<br>207<br>210<br>211<br>214<br>218<br>221<br>225<br>225               |

| MOVSB MOVSW MOVSD MOVSQ. MOVSX. MOVSXD MOVZX. MUL NEG. NOP. NOT. OR OUT. OUTSx POP POPAx. POPFx. PREFETCHx PREFETCHlevel. PUSH | 202<br>203<br>204<br>205<br>207<br>210<br>211<br>214<br>216<br>221<br>222<br>225<br>229<br>231 |

|   | RCR23                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3/                                                                                                                                                                                     |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | RET (Near)24                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>40</b>                                                                                                                                                                              |

|   | RET (Far)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12                                                                                                                                                                                     |

|   | ROL24                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        |

|   | ROR                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                        |

|   | SAHF                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |

|   | SAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ,0                                                                                                                                                                                     |

|   | SHL                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71                                                                                                                                                                                     |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                        |

|   | SAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                        |

|   | SBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                        |

|   | SCASx                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        |

|   | SET <i>cc</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                        |

|   | SFENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                        |

|   | SHL                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 66                                                                                                                                                                                     |

|   | SHLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67                                                                                                                                                                                     |

|   | SHR                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 69                                                                                                                                                                                     |

|   | SHRD                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71                                                                                                                                                                                     |

|   | STC                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73                                                                                                                                                                                     |

|   | STD27                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74                                                                                                                                                                                     |

|   | STOS <i>x</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                      |

|   | SUB                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                        |

|   | TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |

|   | XADD                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |

|   | XCHG                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                        |

|   | XLATx                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                      |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                        |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                        |

| _ | XOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38                                                                                                                                                                                     |

| 4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38                                                                                                                                                                                     |

| 4 | XOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38<br>91                                                                                                                                                                               |

| 4 | XOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38<br><b>91</b><br>92                                                                                                                                                                  |

| 4 | XOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38<br><b>91</b><br>92<br>94                                                                                                                                                            |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29                                                                                                                                                                                                                                                                                                                                                    | 38<br><b>91</b><br>92<br>94                                                                                                                                                            |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29                                                                                                                                                                                                                                                                                                                               | 38<br>91<br>92<br>94<br>96<br>97                                                                                                                                                       |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29                                                                                                                                                                                                                                                                                                        | 38<br>91<br>92<br>94<br>96<br>97                                                                                                                                                       |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30                                                                                                                                                                                                                                                                                  | 38<br>91<br>92<br>94<br>96<br>97<br>98                                                                                                                                                 |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30                                                                                                                                                                                                                                                          | 388<br>91<br>92<br>94<br>96<br>97<br>98<br>91                                                                                                                                          |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       30                                                                                                                                                                                                                                   | 38<br>91<br>92<br>94<br>96<br>97<br>98<br>91<br>92<br>93                                                                                                                               |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       30         LAR       30                                                                                                                                                                                                              | 38<br>91<br>92<br>94<br>96<br>97<br>98<br>91<br>92<br>93                                                                                                                               |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       30         LAR       30         LGDT       31                                                                                                                                                                                        | 38<br>91<br>92<br>94<br>96<br>97<br>98<br>91<br>93                                                                                                                                     |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       30         LAR       30         LGDT       31         LIDT       31                                                                                                                                                                  | 38<br>91<br>92<br>94<br>96<br>97<br>98<br>91<br>92<br>93<br>91<br>94                                                                                                                   |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       30         LAR       30         LGDT       31         LIDT       31         LLDT       31                                                                                                                                            | 38<br>91<br>92<br>94<br>96<br>97<br>98<br>91<br>93<br>91<br>91<br>14                                                                                                                   |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       30         LAR       30         LGDT       31         LIDT       31         LLDT       31         LMSW       31                                                                                                                      | 38<br>91<br>92<br>94<br>96<br>97<br>98<br>91<br>93<br>91<br>12<br>14<br>16<br>18                                                                                                       |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       30         LAR       30         LGDT       31         LIDT       31         LLDT       31                                                                                                                                            | 38<br>91<br>92<br>94<br>96<br>97<br>98<br>91<br>93<br>91<br>12<br>14<br>16<br>18                                                                                                       |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       30         LAR       30         LGDT       31         LIDT       31         LLDT       31         LMSW       31                                                                                                                      | 38<br>91<br>92<br>94<br>96<br>97<br>98<br>91<br>92<br>93<br>91<br>14<br>16<br>18                                                                                                       |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       30         LAR       30         LGDT       31         LIDT       31         LLDT       31         LMSW       31         LSL       31                                                                                                 | 92<br>94<br>96<br>97<br>98<br>91<br>92<br>14<br>16<br>18<br>19                                                                                                                         |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       30         LAR       30         LGDT       31         LIDT       31         LMSW       31         LSL       31         LTR       32                                                                                                  | 38<br>91<br>92<br>94<br>96<br>97<br>98<br>91<br>91<br>91<br>14<br>16<br>18<br>19<br>21<br>23                                                                                           |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       36         LAR       30         LGDT       31         LIDT       31         LMSW       31         LSL       31         LTR       32         MOV(CRn)       32                                                                        | 38<br>91<br>92<br>94<br>96<br>97<br>98<br>91<br>91<br>91<br>91<br>91<br>91<br>91<br>91<br>91<br>91                                                                                     |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INVD       30         INVLPG       30         IRETx       30         LAR       30         LGDT       31         LIDT       31         LLDT       31         LMSW       31         LSL       31         LTR       32         MOV(CRn)       32         MOV(DRn)       32                                               | 92<br>94<br>96<br>97<br>98<br>91<br>91<br>91<br>91<br>91<br>91<br>91<br>91<br>92<br>91<br>92<br>93<br>94<br>95<br>95<br>95<br>95<br>95<br>95<br>95<br>95<br>95<br>95<br>95<br>95<br>95 |

| 4 | XOR       28         ystem Instruction Reference       29         ARPL       29         CLI       29         CLTS       29         HLT       29         INT 3       29         INVD       30         INVLPG       30         IRETx       30         LAR       30         LGDT       31         LIDT       31         LLDT       31         LMSW       31         LSL       31         LTR       32         MOV(CRn)       32         MOV(DRn)       32         RDMSR       32 | 38<br>91<br>92<br>94<br>96<br>97<br>98<br>91<br>91<br>92<br>93<br>94<br>94<br>95<br>96<br>97<br>98<br>97<br>98<br>98<br>99<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90       |

|             |               | RSM                                                 |       |

|-------------|---------------|-----------------------------------------------------|-------|

|             |               | SGDT                                                |       |

|             |               | SIDT                                                |       |

|             |               | SLDT                                                |       |

|             |               | SMSW                                                |       |

|             |               | STI                                                 |       |

|             |               | STR                                                 |       |

|             |               | SYSCALL                                             |       |

|             |               | SYSENTER.                                           |       |

|             |               | SYSEXIT                                             |       |

|             |               | SYSRET                                              |       |

|             |               | UD2                                                 |       |

|             |               | VERR                                                |       |

|             |               | VERW                                                |       |

|             |               | WBINVD                                              |       |

|             |               | WRMSR                                               |       |

| Appendix A  | Opcode and    | Operand Encodings                                   | 367   |

| ippendix 71 | A.1           | Opcode-Syntax Notation                              |       |

|             | A.2           | Opcode Encodings                                    |       |

|             |               | One-Byte Opcodes                                    |       |

|             |               | Two-Byte Opcodes                                    |       |

|             |               | rFLAGS Condition Codes for Two-Byte Opcodes         | . 378 |

|             |               | ModRM Extensions to One-Byte and Two-Byte Opcodes   |       |

|             |               | ModRM Extensions to SWAPGS and CLFLUSH Opcodes      | . 382 |

|             |               | 3DNow! <sup>TM</sup> Opcodes                        |       |

|             |               | x87 Encodings                                       |       |

|             |               | rFLAGS Condition Codes for x87 Opcodes              |       |

|             | A.3           | Operand Encodings                                   |       |

|             |               | ModRM Operand References                            |       |

|             |               | SIB Operand References                              | . 399 |

| Appendix B  | General-Pur   | pose Instructions in 64-Bit Mode                    | 403   |

|             | B.1           | General Rules for 64-Bit Mode                       | . 403 |

|             | B.2           | Operation and Operand Size in 64-Bit Mode           |       |

|             | B.3           | Invalid and Reassigned Instructions in 64-Bit Mode  |       |

|             | B.4           | Instructions with 64-Bit Default Operand Size       |       |

|             | B.5           | Single-Byte INC and DEC Instructions in 64-Bit Mode |       |

|             | B.6           | NOP in 64-Bit Mode                                  |       |

|             | B.7           | Segment Override Prefixes in 64-Bit Mode            | . 438 |

| Appendix C  | Differences l | between Long Mode and Legacy Mode                   | 439   |

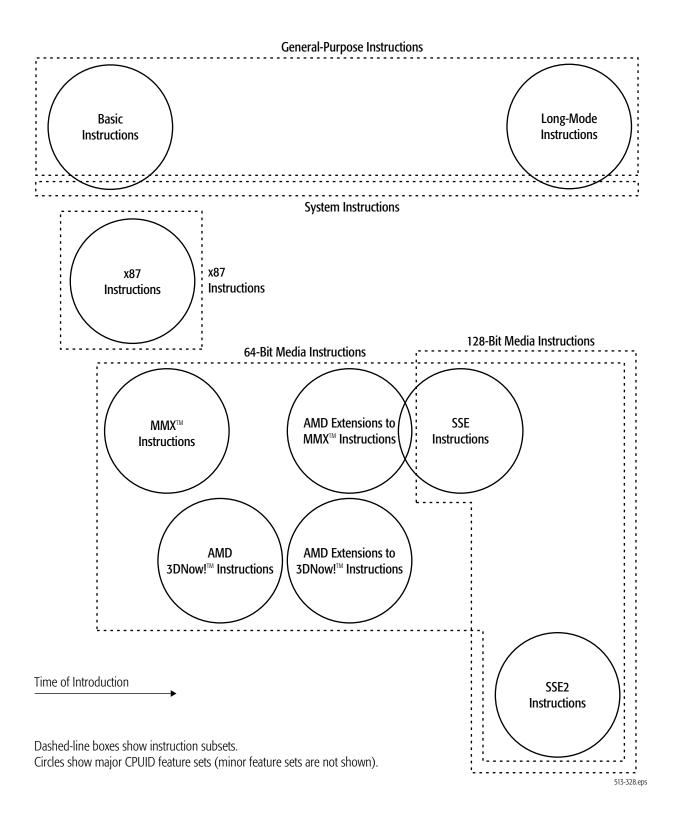

| Appendix D  | Instruction S | Subsets and CPUID Feature Sets                      | 441   |

|             | D.1           | Instruction Subsets                                 |       |

|             | D.2           | CPUID Feature Sets                                  |       |

|             | D.3           | Instruction List                                    | . 445 |

| Appendix E  | Instruction E | iffects on RFLAGS                                   | 479   |

24594 Rev. 3.04 April 2003

Index 485

viii Contents

# **Figures**

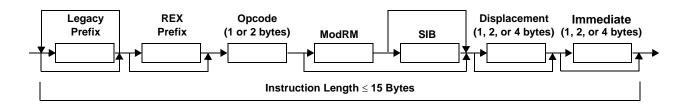

| Figure 1-1. Instruction Byte-Order                                    |

|-----------------------------------------------------------------------|

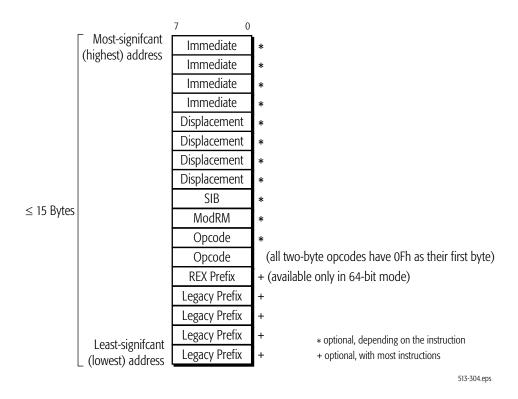

| Figure 1-2. Little-Endian Byte-Order of Instruction Stored in Memory2 |

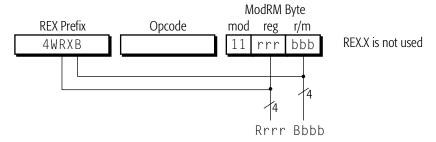

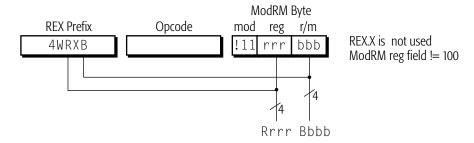

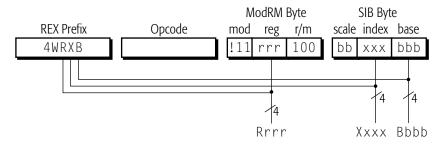

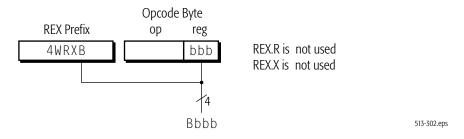

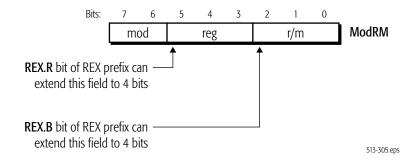

| Figure 1-3. Encoding Examples of REX-Prefix R, X, and B Bits          |

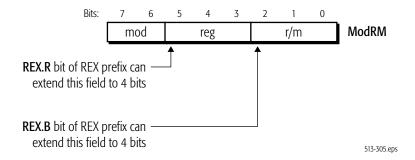

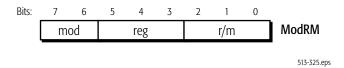

| Figure 1-4. ModRM-Byte Format                                         |

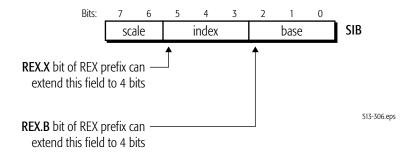

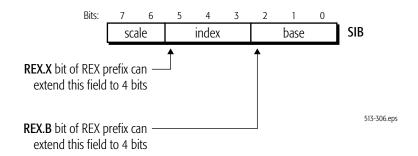

| Figure 1-5. SIB-Byte Format                                           |

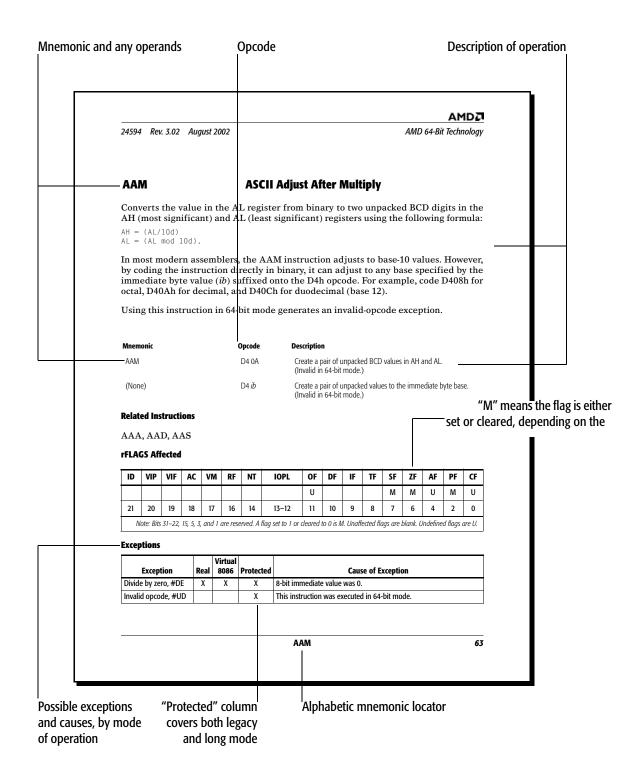

| Figure 2-1. Format of Instruction-Detail Pages                        |

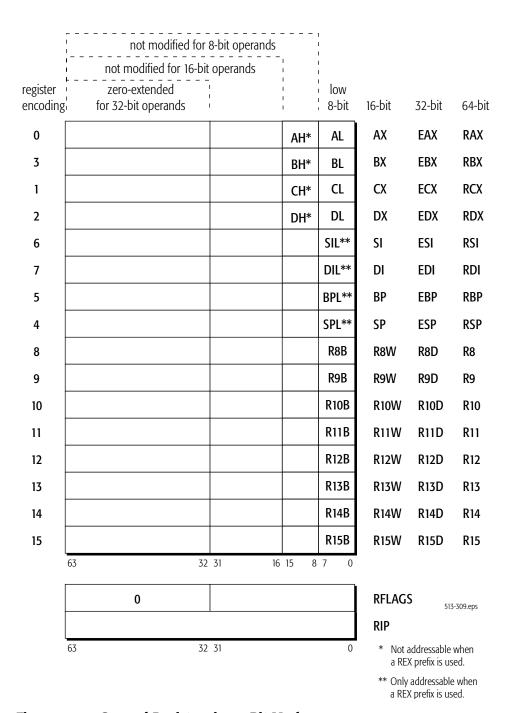

| Figure 2-2. General Registers in Legacy and Compatibility Modes30     |

| Figure 2-3. General Registers in 64-Bit Mode31                        |

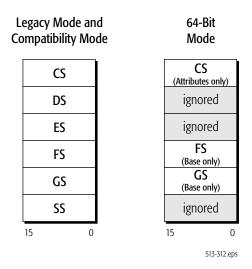

| Figure 2-4. Segment Registers                                         |

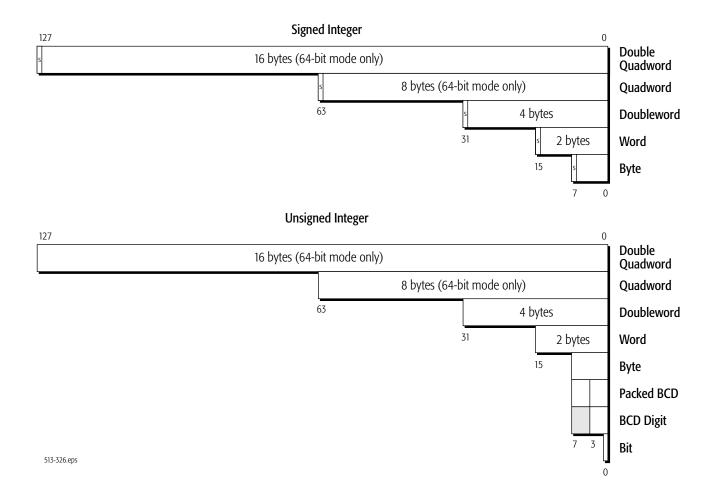

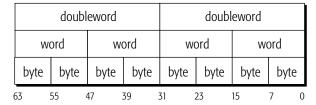

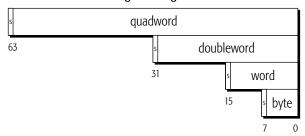

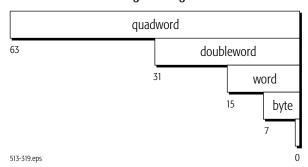

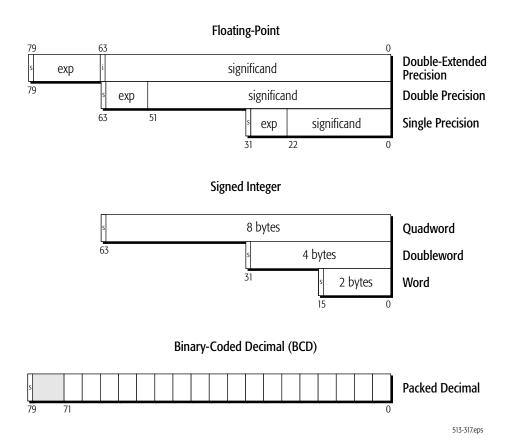

| Figure 2-5. General-Purpose Data Types                                |

| Figure 2-6. System Registers                                          |

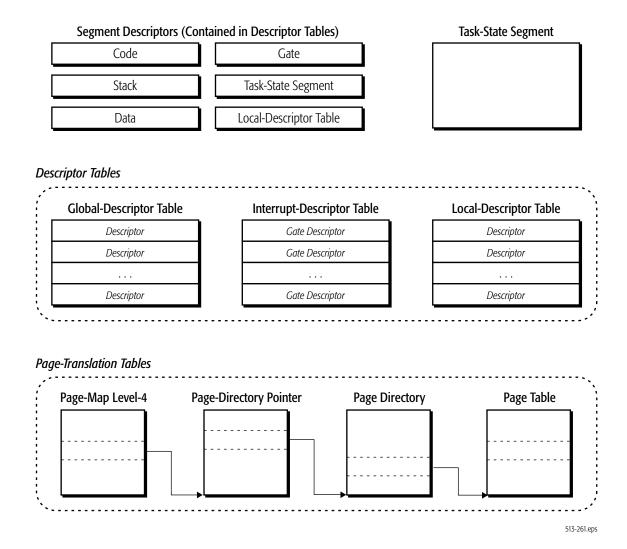

| Figure 2-7. System Data Structures                                    |

| Figure 2-8. 128-Bit Media Registers                                   |

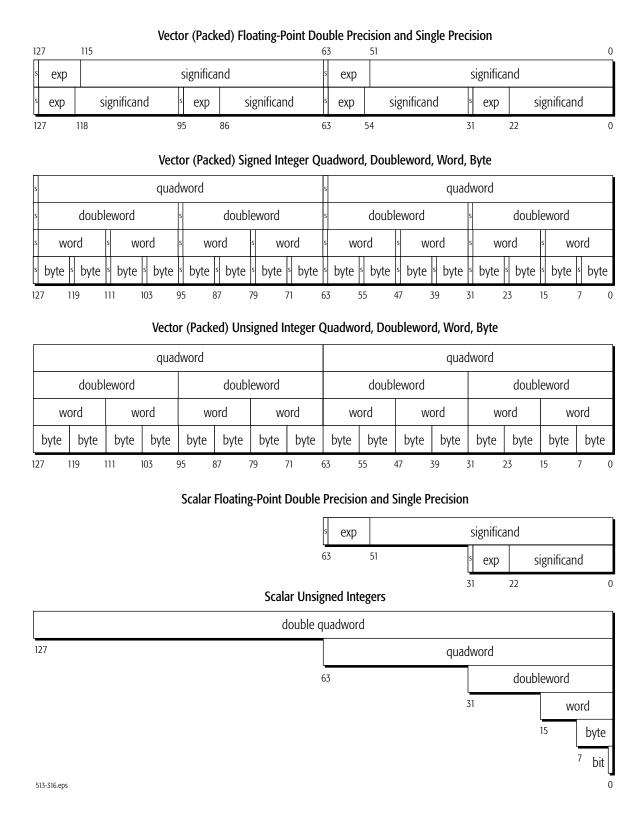

| Figure 2-9. 128-Bit Media Data Types                                  |

| Figure 2-10.64-Bit Media Registers                                    |

| Figure 2-11.64-Bit Media Data Types                                   |

| Figure 2-12.x87 Registers                                             |

| Figure 2-13.x87 Data Types                                            |

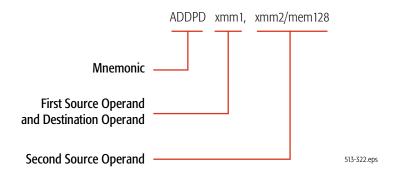

| Figure 2-14.Syntax for Typical Two-Operand Instruction                |

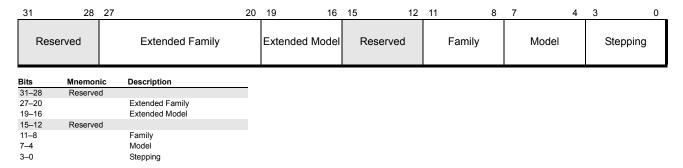

| Figure 3-1. Processor Signature (EAX Register)                        |

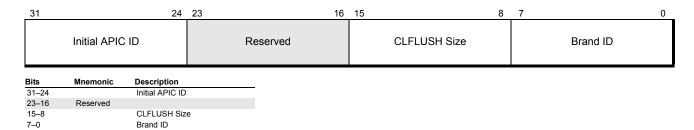

| Figure 3-2. Initial APIC ID, CLFLUSH Size, and                        |

| Brand ID (EBX Register)120                                            |

| Figure 3-3. Advanced Power Management Features (EDX Register) 129     |

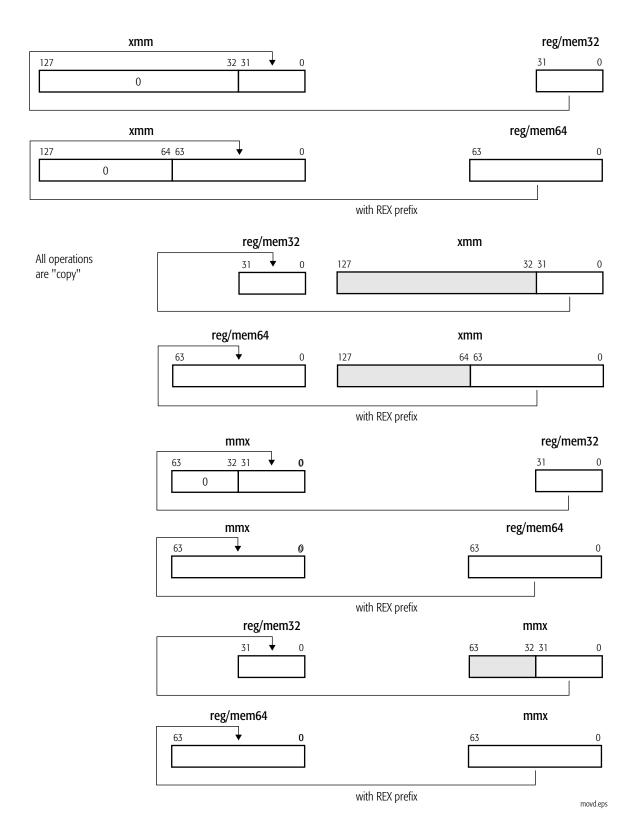

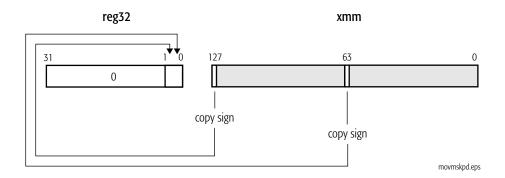

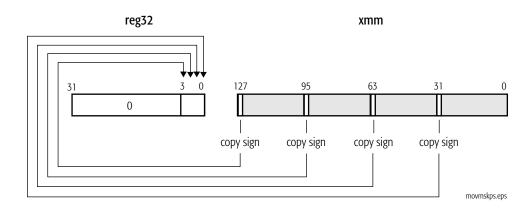

| Figure 3-4. MOVD Instruction Operation                                |

| Figure A-1. ModRM-Byte Fields                                         |

| Figure A-2. ModRM-Byte Format                                         |

| Figure A-3. SIB Byte Format                                           |

| Figure D.1 Instruction Subsets vs. CPIIID Feature Sets. 442           |

Figures ix

24594 Rev. 3.04 April 2003

x Figures

# **Tables**

| Table 1-1.  | Legacy Instruction Prefixes                                          | 4    |

|-------------|----------------------------------------------------------------------|------|

| Table 1-2.  | Operand-Size Overrides                                               | 5    |

| Table 1-3.  | Address-Size Overrides                                               | 7    |

| Table 1-4.  | Pointer and Count Registers and the Address-Size Prefix              | 8    |

| Table 1-5.  | Segment-Override Prefixes                                            | 9    |

| Table 1-6.  | REP Prefix Opcodes                                                   | . 11 |

| Table 1-7.  | REPE and REPZ Prefix Opcodes                                         | . 12 |

| Table 1-8.  | REPNE and REPNZ Prefix Opcodes                                       | . 13 |

| Table 1-9.  | REX Instruction Prefixes                                             | . 14 |

| Table 1-10. | Instructions Not Requiring REX Size Prefix in 64-Bit Mode.           | . 15 |

| Table 1-11. | REX Prefix-Byte Fields                                               | . 16 |

| Table 1-12. | Special REX Encodings for Registers                                  | . 19 |

| Table 1-13. | Encoding for RIP-Relative Addressing                                 | . 24 |

| Table 2-1.  | Interrupt-Vector Source and Cause                                    | . 42 |

| Table 2-2.  | +rb, +rw, +rd, and +rq Register Value                                | . 47 |

| Table 3-1.  | Processor Vendor Return Values                                       | 118  |

| Table 3-2.  | Effective Family Computation                                         | 119  |

| Table 3-3.  | Effective Model Computation                                          | 120  |

| Table 3-4.  | $CPUID\ Standard\ Feature\ Support\ (Standard\ Function\ 1)\ \ .\ .$ | 121  |

| Table 3-5.  | CPUID AMD Feature Support                                            | 124  |

| m 11 2.6    | (Extended Function 8000_0001h)                                       |      |

| Table 3-6.  | Processor Name String Example                                        |      |

| Table 3-7.  | CPUID TLB Bits for 2-Mbyte and 4-Mbyte Pages                         |      |

| Table 3-8.  | CPUID TLB Bits for 4-Kbyte Pages                                     |      |

| Table 3-9.  | CPUID L1 Data Cache Bits                                             |      |

|             | CPUID L1 Instruction Cache Bits                                      |      |

|             | CPUID L2 TLB Bits for 2-Mbyte and 4-Mbyte Pages                      |      |

|             | CPUID L2 TLB Bits for 4-Kbyte Pages                                  |      |

|             | CPUID L2 Cache Bits                                                  |      |

|             | CPUID Long-Mode Address Sizes                                        |      |

|             | Locality References for the Prefetch Instructions                    |      |

|             | One-Byte Opcodes, Low Nibble 0–7h                                    |      |

|             | One-Byte Opcodes, Low Nibble 8–Fh                                    |      |

| Table A-3.  | Second Byte of Two-Byte Opcodes, Low Nibble 0–7h                     | 372  |

Tables xi

| Table A-4.  | Second Byte of Two-Byte Opcodes, Low Nibble 8–Fh375                              |

|-------------|----------------------------------------------------------------------------------|

| Table A-5.  | rFLAGS Condition Codes for CMOVcc, Jcc, and SETcc 378                            |

| Table A-6.  | One-Byte and Two-Byte Opcode ModRM Extensions380                                 |

| Table A-7.  | SWAPGS and xFENCE ModRM Extensions                                               |

| Table A-8.  | Immediate Byte for 3DNow! $^{\text{TM}}$ Opcodes, Low Nibble 0–7h 383            |

| Table A-9.  | Immediate Byte for 3DNow! $^{\text{\tiny TM}}$ Opcodes, Low Nibble 8–Fh 384      |

| Table A-10. | x87 Opcodes and ModRM Extensions385                                              |

| Table A-11. | rFLAGS Condition Codes for FCMOVcc393                                            |

| Table A-12. | ModRM Register References, 16-Bit Addressing 394                                 |

| Table A-13. | ModRM Memory References, 16-Bit Addressing395                                    |

| Table A-14. | $ModRM\ Register\ References,32\text{-Bit}\ and\ 64\text{-Bit}\ Addressing}.397$ |

| Table A-15. | $ModRM\ Memory\ References, 32\text{-Bit}$ and 64-Bit Addressing . 398           |

| Table A-16. | SIB base Field References                                                        |

| Table A-17. | SIB Memory References401                                                         |

| Table B-1.  | Operations and Operands in 64-Bit Mode 405                                       |

| Table B-2.  | Invalid Instructions in 64-Bit Mode                                              |

| Table B-3.  | Reassigned Instructions in 64-Bit Mode435                                        |

| Table B-4.  | Invalid Instructions in Long Mode                                                |

| Table B-5.  | Instructions Defaulting to 64-Bit Operand Size436                                |

| Table C-1.  | Differences Between Long Mode and Legacy Mode 439                                |

| Table D-1.  | Instruction Subsets and CPUID Feature Sets                                       |

| Table E-1.  | Instruction Effects on RFLAGS                                                    |

xii Tables

# **Revision History**

| Date       | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| April 2003 | 3.08     | Corrected description of the operation of flags for RCL, RCR, ROL, and ROR instructions. Clarified description of the MOVSXD and IMUL instructions. Corrected operand specification for the STOS instruction. Corrected opcode of SET <i>cc</i> , <i>Jcc</i> , instructions. Added thermal control and thermal monitoring bits to CPUID instruction. Corrected exception tables for POPF, SFENCE, SUB, XLAT, IRET, LSL, MOV(CRn), SGDT/SIDT, SMSW, and STI instructions Corrected many small typos and incorporated branding terminology. |  |

Revision History xiii

24594–Rev. 3.04–April 2003

xiv Revision History

### **Preface**

### **About This Book**

This book is part of a multivolume work entitled the *AMD64 Architecture Programmer's Manual*. This table lists each volume and its order number.

| Title                                                      | Order No. |

|------------------------------------------------------------|-----------|

| Volume 1, Application Programming                          | 24592     |

| Volume 2, System Programming                               | 24593     |

| Volume 3, General-Purpose and System Instructions          | 24594     |

| Volume 4, 128-Bit Media Instructions                       | 26568     |

| Volume 5, 64-Bit Media and x87 Floating-Point Instructions | 26569     |

### **Audience**

This volume (Volume 3) is intended for all programmers writing application or system software for a processor that implements the AMD64 architecture. Descriptions of general-purpose instructions assume an understanding of the application-level programming topics described in Volume 1. Descriptions of system instructions assume an understanding of the system-level programming topics described in Volume 2.

### **Contact Information**

To submit questions or comments concerning this document, contact our technical documentation staff at AMD64.Feedback@amd.com.

### **Organization**

Volumes 3, 4, and 5 describe the AMD64 architecture's instruction set in detail. Together, they cover each instruction's mnemonic syntax, opcodes, functions, affected flags, and possible exceptions.

The AMD64 instruction set is divided into five subsets:

Preface xv

- General-purpose instructions

- System instructions

- 128-bit media instructions

- 64-bit media instructions

- x87 floating-point instructions

Several instructions belong to—and are described identically in—multiple instruction subsets.

This volume describes the general-purpose and system instructions. The index at the end cross-references topics within this volume. For other topics relating to the AMD64 architecture, and for information on instructions in other subsets, see the tables of contents and indexes of the other volumes.

### **Definitions**

Many of the following definitions assume an in-depth knowledge of the legacy x86 architecture. See "Related Documents" on page xxvii for descriptions of the legacy x86 architecture.

### **Terms and Notation**

In addition to the notation described below, "Opcode-Syntax Notation" on page 367 describes notation relating specifically to opcodes.

1011b

A binary value—in this example, a 4-bit value.

F0EAh

A hexadecimal value—in this example a 2-byte value.

[1,2)

A range that includes the left-most value (in this case, 1) but excludes the right-most value (in this case, 2).

7-4

A bit range, from bit 7 to 4, inclusive. The high-order bit is shown first.

128-bit media instructions

Instructions that use the 128-bit XMM registers. These are a combination of the SSE and SSE2 instruction sets.

**xvi** Preface

### 64-bit media instructions

Instructions that use the 64-bit MMX<sup>TM</sup> registers. These are primarily a combination of MMX and 3DNow!<sup>TM</sup> instruction sets, with some additional instructions from the SSE and SSE2 instruction sets.

### 16-bit mode

Legacy mode or compatibility mode in which a 16-bit address size is active. See *legacy mode* and *compatibility mode*.

### 32-bit mode

Legacy mode or compatibility mode in which a 32-bit address size is active. See *legacy mode* and *compatibility mode*.

### 64-bit mode

A submode of *long mode*. In 64-bit mode, the default address size is 64 bits and new features, such as register extensions, are supported for system and application software.

### #GP(0)

Notation indicating a general-protection exception (#GP) with error code of 0.

### absolute

Said of a displacement that references the base of a code segment rather than an instruction pointer. Contrast with relative.

### biased exponent

The sum of a floating-point value's exponent and a constant bias for a particular floating-point data type. The bias makes the range of the biased exponent always positive, which allows reciprocation without overflow.

### byte

Eight bits.

### clear

To write a bit value of 0. Compare *set*.

Preface xvii

### compatibility mode

A submode of *long mode*. In compatibility mode, the default address size is 32 bits, and legacy 16-bit and 32-bit applications run without modification.

### commit

To irreversibly write, in program order, an instruction's result to software-visible storage, such as a register (including flags), the data cache, an internal write buffer, or memory.

### CPL

Current privilege level.

### CR0-CR4

A register range, from register CR0 through CR4, inclusive, with the low-order register first.

### CR0.PE = 1

Notation indicating that the PE bit of the CR0 register has a value of 1.

### direct

Referencing a memory location whose address is included in the instruction's syntax as an immediate operand. The address may be an absolute or relative address. Compare indirect.

### dirty data

Data held in the processor's caches or internal buffers that is more recent than the copy held in main memory.

### displacement

A signed value that is added to the base of a segment (absolute addressing) or an instruction pointer (relative addressing). Same as *offset*.

### doubleword

Two words, or four bytes, or 32 bits.

### double quadword

Eight words, or 16 bytes, or 128 bits. Also called octword.

**xviii** Preface

### DS:rSI

The contents of a memory location whose segment address is in the DS register and whose offset relative to that segment is in the rSI register.

### EFER.LME = 0

Notation indicating that the LME bit of the EFER register has a value of 0.

### effective address size

The address size for the current instruction after accounting for the default address size and any address-size override prefix.

### effective operand size

The operand size for the current instruction after accounting for the default operand size and any operand-size override prefix.

### element

See vector.

### exception

An abnormal condition that occurs as the result of executing an instruction. The processor's response to an exception depends on the type of the exception. For all exceptions except 128-bit media SIMD floating-point exceptions and x87 floating-point exceptions, control is transferred to the handler (or service routine) for that exception, as defined by the exception's vector. For floating-point exceptions defined by the IEEE 754 standard, there are both masked and unmasked responses. When unmasked, the exception handler is called, and when masked, a default response is provided instead of calling the handler.

### FF /0

Notation indicating that FF is the first byte of an opcode, and a subopcode in the ModR/M byte has a value of 0.

### flush

An often ambiguous term meaning (1) writeback, if modified, and invalidate, as in "flush the cache line," or (2) invalidate, as in "flush the pipeline," or (3) change a value, as in "flush to zero."

Preface xix

GDT

Global descriptor table.

IDT

Interrupt descriptor table.

IGN

Ignore. Field is ignored.

indirect

Referencing a memory location whose address is in a register or other memory location. The address may be an absolute or relative address. Compare *direct*.

**IRB**

The virtual-8086 mode interrupt-redirection bitmap.

**IST**

The long-mode interrupt-stack table.

IVT

The real-address mode interrupt-vector table.

LDT

Local descriptor table.

legacy x86

The legacy x86 architecture. See "Related Documents" on page xxvii for descriptions of the legacy x86 architecture.

legacy mode

An operating mode of the AMD64 architecture in which existing 16-bit and 32-bit applications and operating systems run without modification. A processor implementation of the AMD64 architecture can run in either *long mode* or *legacy mode*. Legacy mode has three submodes, *real mode*, *protected mode*, and *virtual-8086 mode*.

long mode

An operating mode unique to the AMD64 architecture. A processor implementation of the AMD64 architecture can run in either *long mode* or *legacy mode*. Long mode has two submodes, *64-bit mode* and *compatibility mode*.

xx Preface

lsb

Least-significant bit.

### LSB

Least-significant byte.

### main memory

Physical memory, such as RAM and ROM (but not cache memory) that is installed in a particular computer system.

### mask

(1) A control bit that prevents the occurrence of a floatingpoint exception from invoking an exception-handling routine. (2) A field of bits used for a control purpose.

### MBZ

Must be zero. If software attempts to set an MBZ bit to 1, a general-protection exception (#GP) occurs.

### memory

Unless otherwise specified, main memory.

### ModRM

A byte following an instruction opcode that specifies address calculation based on mode (Mod), register (R), and memory (M) variables.

### moffset