# AMD64 Architecture Programmer's Manual Volume 2: System Programming

| Publication No. | Revision | Date      |

|-----------------|----------|-----------|

| 24593           | 3.13     | July 2007 |

Advanced Micro Devices 🛛 🛃

© 2002 - 2007 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. The information contained herein may be of a preliminary or advance nature and is subject to change without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD arrow logo, AMD Athlon, and AMD Opteron, and combinations thereof, AMD Virtualization and 3DNow! are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

Windows NT is a registered trademark of Microsoft Corporation.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

24593—Rev. 3.13—July 2007

## Contents

| Revisi | ion His | tory xx                                  | w   |

|--------|---------|------------------------------------------|-----|

| Prefa  | ce      | XXV                                      | ii  |

|        |         | This Bookxxv                             |     |

|        | Audier  | ncexxv                                   | /ii |

|        | Contac  | t Information                            | /ii |

|        |         | zation                                   |     |

|        | •       | tions xx                                 |     |

|        |         | Terms and Notation                       | ix  |

|        |         | Registers xxx                            |     |

|        |         | Endian Order xxx                         | ix  |

|        | Relate  | d Documents                              | ix  |

| 1      | System  | n-Programming Overview                   | .1  |

|        | 1.1     | Memory Model                             | 1   |

|        |         | Memory Addressing                        | 2   |

|        |         | Memory Organization                      | 3   |

|        |         | Canonical Address Form                   | 4   |

|        | 1.2     | Memory Management                        | 5   |

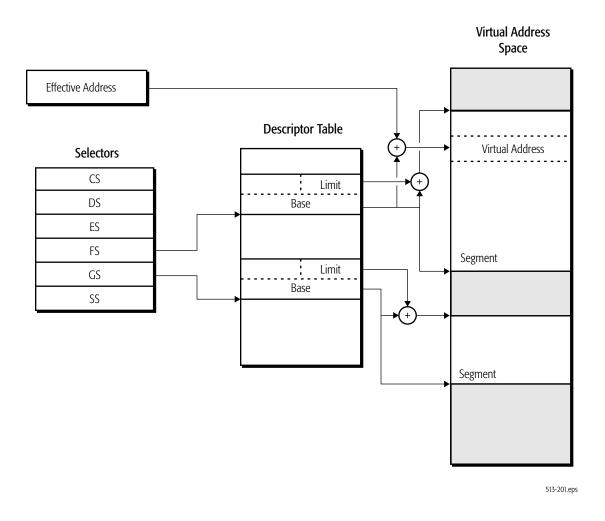

|        |         | Segmentation                             | 5   |

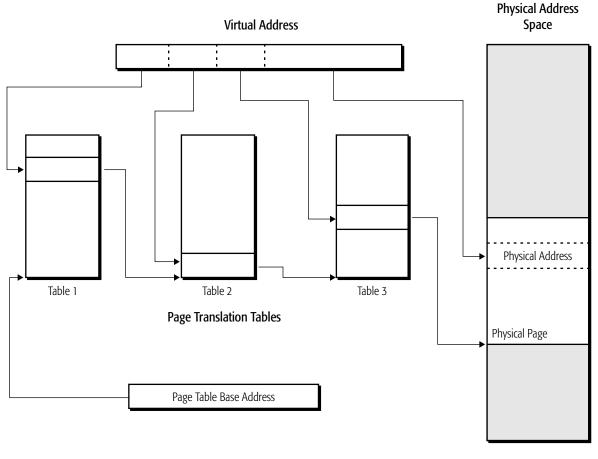

|        |         | Paging                                   | 7   |

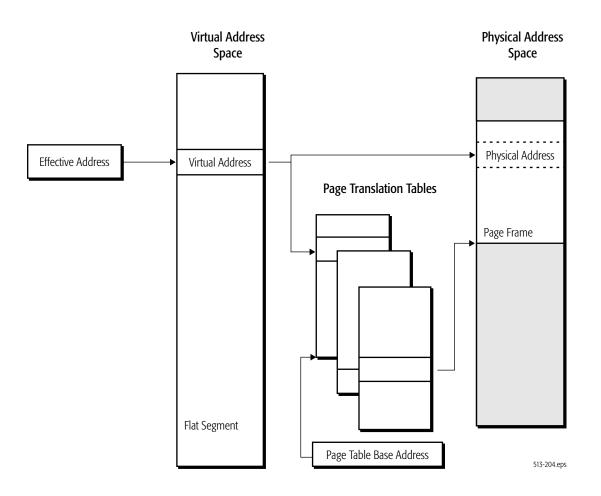

|        |         | Mixing Segmentation and Paging           | 8   |

|        |         | Real Addressing1                         | 0   |

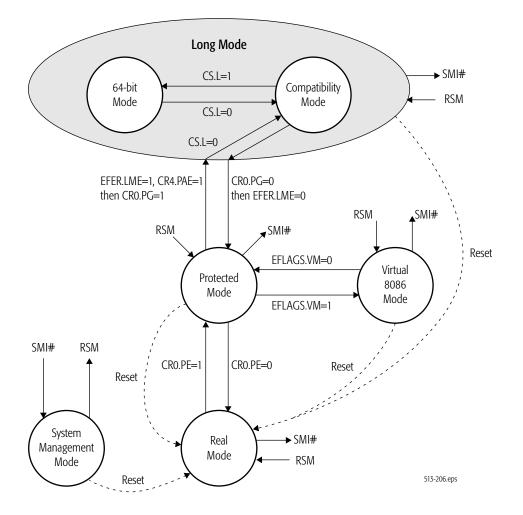

|        | 1.3     | Operating Modes 1                        |     |

|        |         | Long Mode                                |     |

|        |         | 64-Bit Mode1                             |     |

|        |         | Compatibility Mode                       |     |

|        |         | Legacy Modes 1                           |     |

|        |         | System Management Mode (SMM) 1           |     |

|        | 1.4     | System Registers 1                       |     |

|        | 1.5     | System-Data Structures                   |     |

|        | 1.6     | Interrupts                               |     |

|        | 1.7     | Additional System-Programming Facilities |     |

|        |         | Hardware Multitasking                    |     |

|        |         | Machine Check                            |     |

|        |         | Software Debugging                       |     |

|        |         | Performance Monitoring                   |     |

| 2      |         | nd AMD64 Architecture Differences2       |     |

|        | 2.1     | Operating Modes                          |     |

|        |         | Long Mode                                |     |

|        |         | Legacy Mode                              |     |

|        |         | System-Management Mode                   |     |

|        | 2.2     | Memory Model                             |     |

|        |         | Memory Addressing                        | 24  |

|       | Page Translation.                        | 25 |

|-------|------------------------------------------|----|

|       | Segmentation                             |    |

| 2.3   | Protection Checks                        |    |

| 2.4   | Registers                                | 28 |

|       | General-Purpose Registers.               |    |

|       | 128-Bit Media Registers                  |    |

|       | Flags Register                           |    |

|       | Instruction Pointer                      |    |

|       | Stack Pointer                            |    |

|       | Control Registers                        |    |

|       | Debug Registers.                         |    |

|       | Extended Feature Register (EFER)         |    |

|       | Memory Type Range Registers (MTRRs).     |    |

|       | Other Model-Specific Registers (MSRs).   |    |

| 2.5   | Instruction Set                          |    |

|       | REX Prefixes                             |    |

|       | Segment-Override Prefixes in 64-Bit Mode |    |

|       | Operands and Results                     |    |

|       | Address Calculations                     |    |

|       | Instructions that Reference RSP          |    |

|       | Branches                                 |    |

|       | NOP Instruction                          |    |

|       | Single-Byte INC and DEC Instructions.    |    |

|       | MOVSXD Instruction                       |    |

|       | Invalid Instructions                     |    |

|       | FXSAVE and FXRSTOR Instructions.         |    |

| 2.6   | Interrupts and Exceptions                |    |

| 2.0   | Interrupt Descriptor Table               |    |

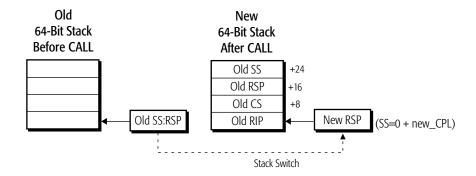

|       | Stack Frame Pushes                       |    |

|       | Stack Switching                          |    |

|       | IRET Instruction                         |    |

|       | Task-Priority Register (CR8).            |    |

|       | New Exception Conditions                 |    |

| 2.7   | Hardware Task Switching                  |    |

| 2.8   | Long-Mode vs. Legacy-Mode Differences    |    |

|       |                                          |    |

| Syste | em Resources                             |    |

| 3.1   | System-Control Registers                 |    |

|       | CR0 Register                             |    |

|       | CR2 and CR3 Registers                    | 45 |

|       | CR4 Register                             |    |

|       | CR1 and CR5–CR7 Registers                |    |

|       | 64-Bit-Mode Extended Control Registers   | 50 |

|       | CR8 (Task Priority Register, TPR)        | 50 |

|       | RFLAGS Register                          |    |

|       | Extended Feature Enable Register (EFER)  |    |

| 3.2   | Model-Specific Registers (MSRs)          |    |

|       | System Configuration Register (SYSCFG)   | 57 |

|   |       | System-Linkage Registers                   |      |

|---|-------|--------------------------------------------|------|

|   |       | Memory-Typing Registers                    |      |

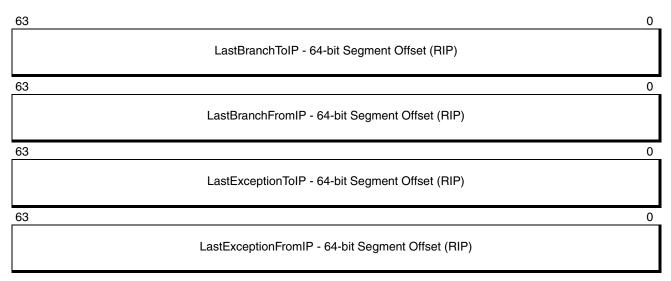

|   |       | Debug-Extension Registers                  |      |

|   |       | Performance-Monitoring Registers           |      |

|   |       | Machine-Check Registers                    |      |

|   | 3.3   | Processor Feature Identification           | . 61 |

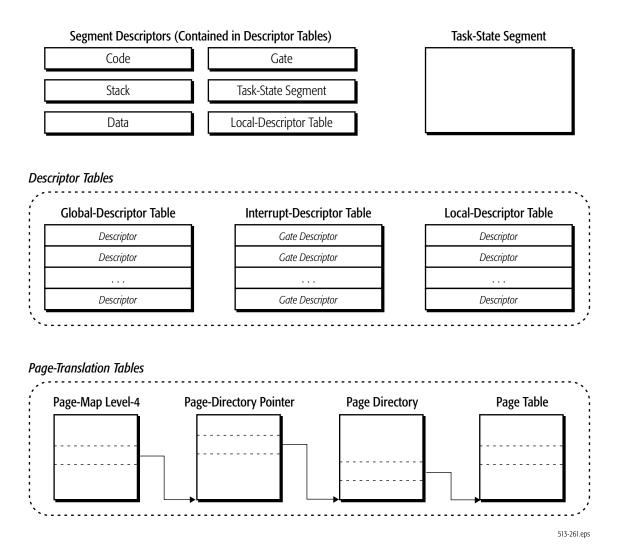

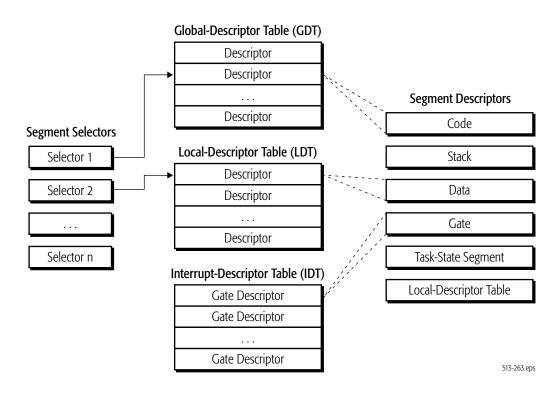

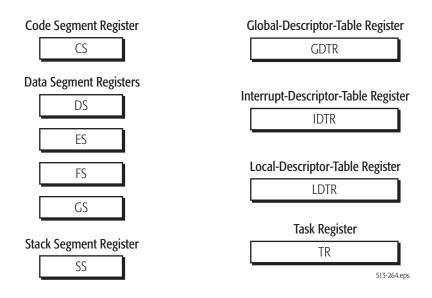

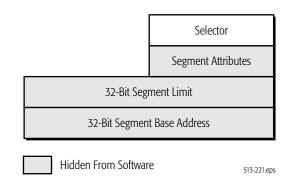

| 4 | Segm  | ented Virtual Memory                       | .63  |

|   | 4.1   | Real Mode Segmentation.                    | . 63 |

|   | 4.2   | Virtual-8086 Mode Segmentation             | . 64 |

|   | 4.3   | Protected Mode Segmented-Memory Models     | . 64 |

|   |       | Multi-Segmented Model                      | . 64 |

|   |       | Flat-Memory Model.                         | . 65 |

|   |       | Segmentation in 64-Bit Mode                |      |

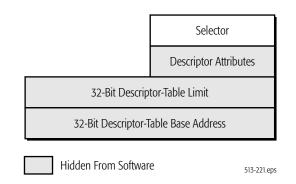

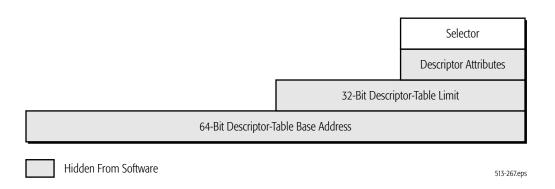

|   | 4.4   | Segmentation Data Structures and Registers |      |

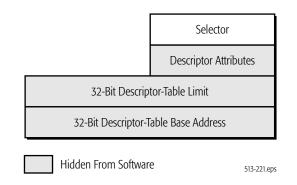

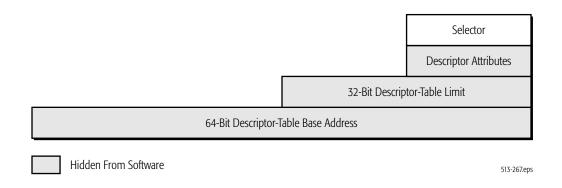

|   | 4.5   | Segment Selectors and Registers            |      |

|   |       | Segment Selectors                          |      |

|   |       | Segment Registers                          |      |

|   |       | Segment Registers in 64-Bit Mode           | . 70 |

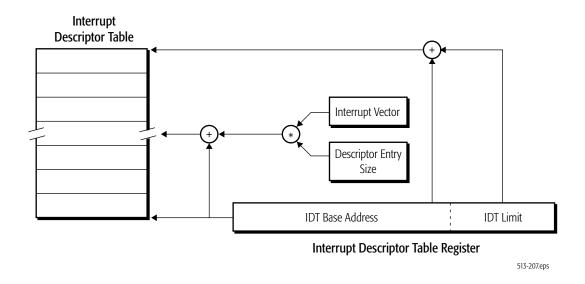

|   | 4.6   | Descriptor Tables                          |      |

|   |       | Global Descriptor Table.                   |      |

|   |       | Global Descriptor-Table Register           |      |

|   |       | Local Descriptor Table.                    |      |

|   |       | Local Descriptor-Table Register            |      |

|   |       | Interrupt Descriptor Table                 |      |

|   |       | Interrupt Descriptor-Table Register        |      |

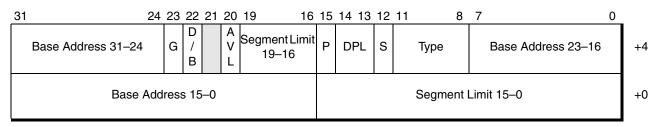

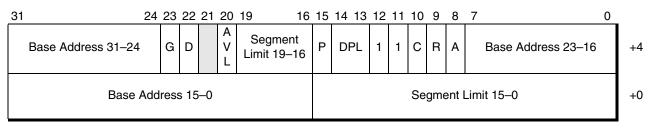

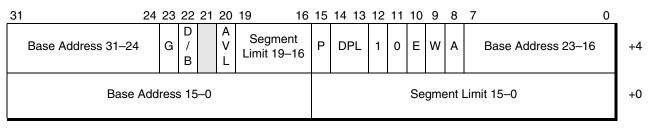

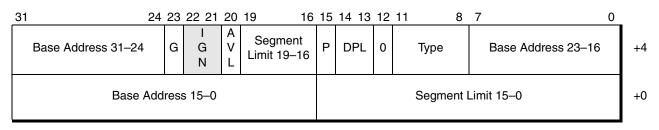

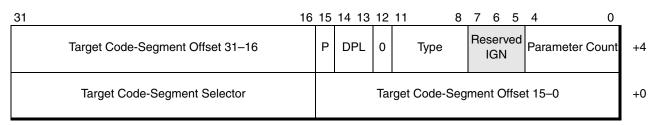

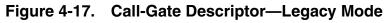

|   | 4.7   | Legacy Segment Descriptors                 |      |

|   |       | Descriptor Format                          |      |

|   |       | Code-Segment Descriptors                   |      |

|   |       | Data-Segment Descriptors                   |      |

|   |       | System Descriptors                         |      |

|   |       | Gate Descriptors                           |      |

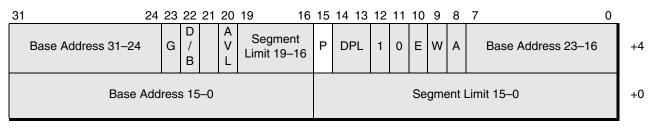

|   | 4.8   | Long-Mode Segment Descriptors              |      |

|   |       | Code-Segment Descriptors                   |      |

|   |       | Data-Segment Descriptors                   |      |

|   |       | System Descriptors                         |      |

|   |       | Gate Descriptors                           |      |

|   | 4.0   | Long Mode Descriptor Summary               |      |

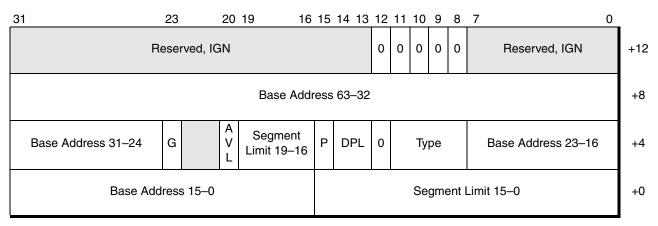

|   | 4.9   | Segment-Protection Overview                |      |

|   |       | Privilege-Level Concept                    |      |

|   | 4 10  | Privilege-Level Types                      |      |

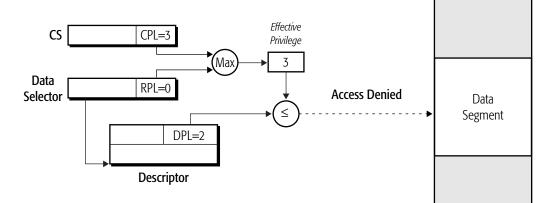

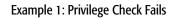

|   | 4.10  | Data-Access Privilege Checks               |      |

|   |       | Accessing Data Segments                    |      |

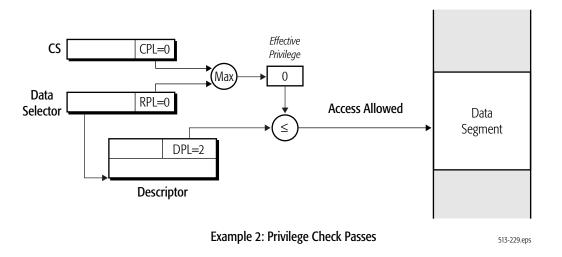

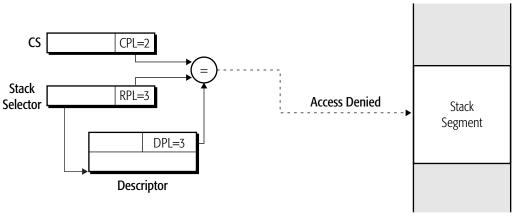

|   | 1 1 1 | Accessing Stack Segments.                  |      |

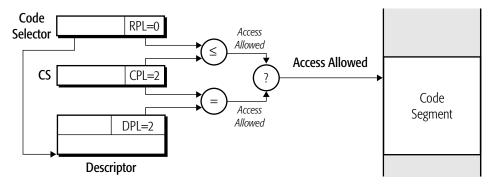

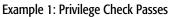

|   | 4.11  | Control-Transfer Privilege Checks          |      |

|   |       | Direct Control Transfers                   |      |

|   |       | Return Control Transfers                   |      |

|   |       |                                            | 109  |

|   | 4.12   | Limit Checks                                  |       |

|---|--------|-----------------------------------------------|-------|

|   | 4.10   | Determining Limit Violations                  |       |

|   | 4.13   | Type Checks                                   |       |

|   |        | Type Checks in Legacy and Compatibility Modes |       |

|   |        | Long Mode Type Check Differences              | . 113 |

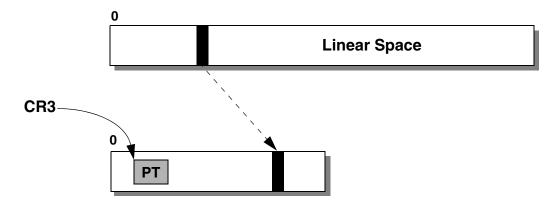

| 5 | Page 7 | Franslation and Protection                    |       |

|   | 5.1    | Page Translation Overview                     |       |

|   |        | Page-Translation Options.                     |       |

|   |        | Page-Translation Enable (PG) Bit              |       |

|   |        | Physical-Address Extensions (PAE) Bit         |       |

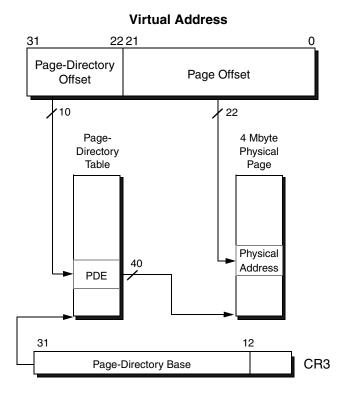

|   |        | Page-Size Extensions (PSE) Bit                | . 119 |

|   |        | Page-Directory Page Size (PS) Bit             | . 119 |

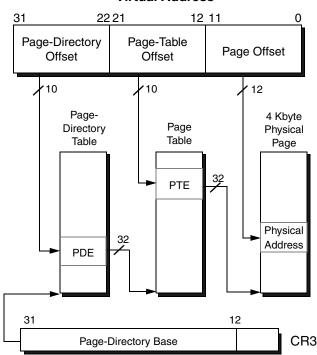

|   | 5.2    | Legacy-Mode Page Translation                  |       |

|   |        | CR3 Register                                  | . 120 |

|   |        | Normal (Non-PAE) Paging                       | . 121 |

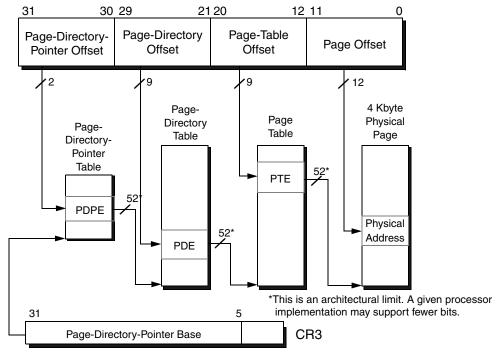

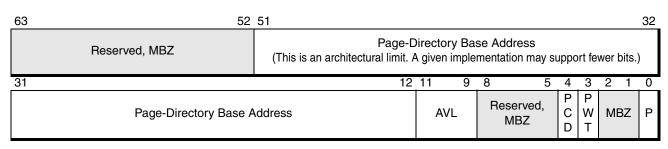

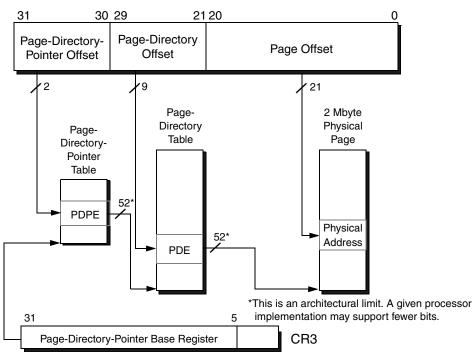

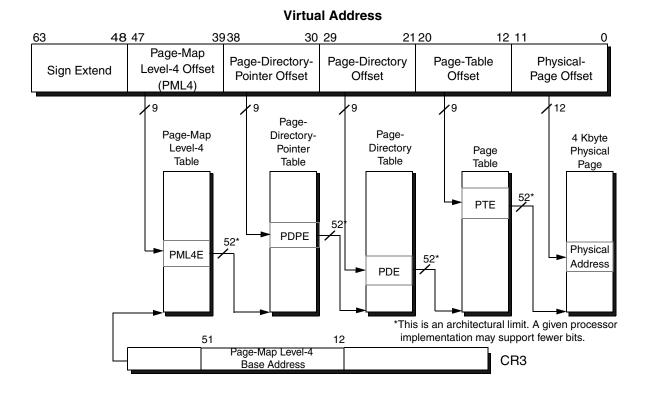

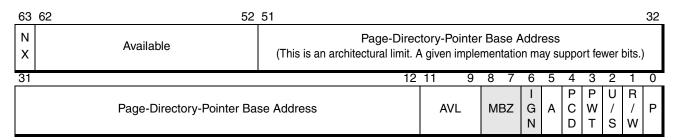

|   |        | PAE Paging                                    | . 124 |

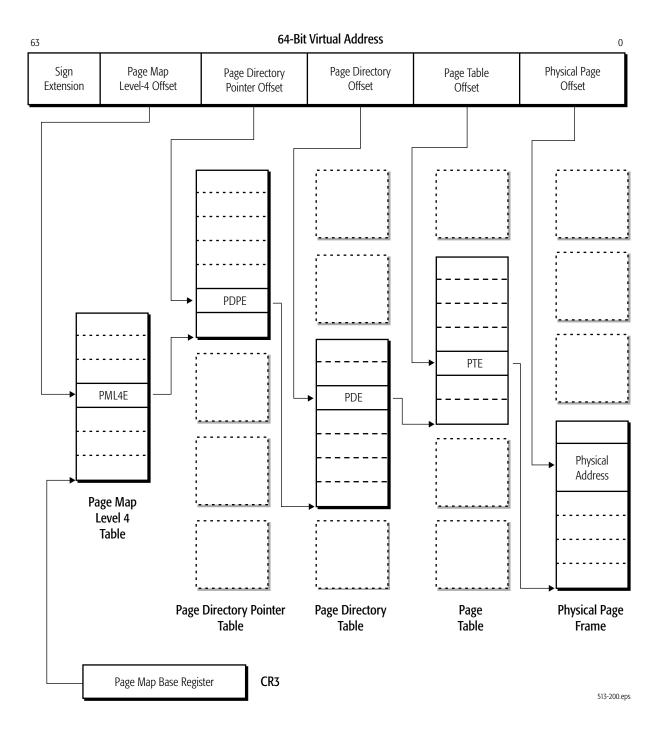

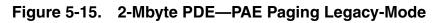

|   | 5.3    | Long-Mode Page Translation                    | . 128 |

|   |        | Canonical Address Form                        | . 128 |

|   |        | CR3                                           | . 128 |

|   |        | 4-Kbyte Page Translation                      | . 129 |

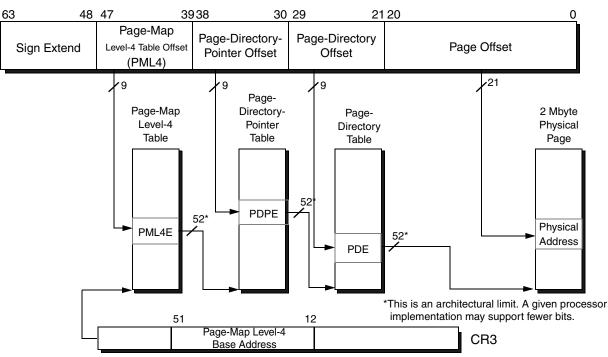

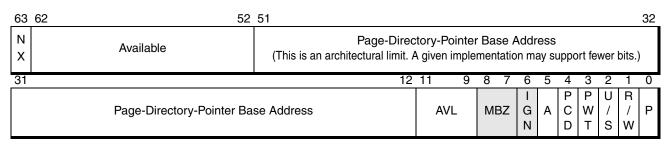

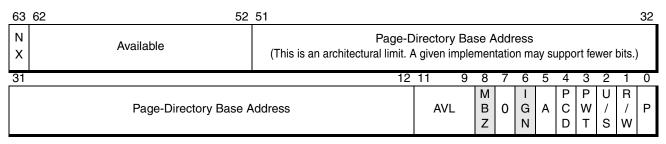

|   |        | 2-Mbyte Page Translation                      | . 132 |

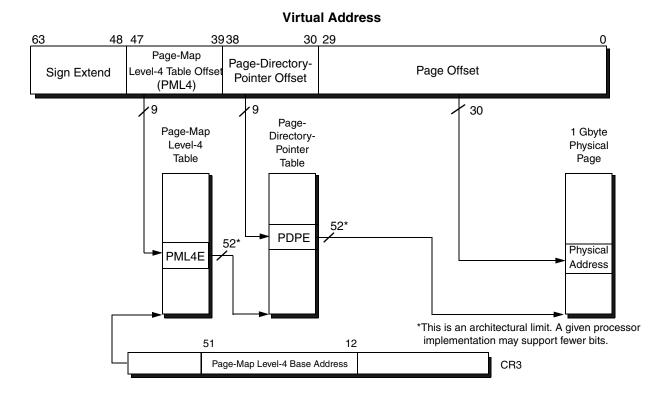

|   |        | 1-Gbyte Page Translation.                     | . 133 |

|   | 5.4    | Page-Translation-Table Entry Fields           | . 135 |

|   |        | Field Definitions                             | . 136 |

|   |        | Notes on Access and Dirty bits                | . 139 |

|   | 5.5    | Translation-Lookaside Buffer (TLB)            | . 139 |

|   |        | Global Pages                                  | . 140 |

|   |        | TLB Management                                | . 140 |

|   | 5.6    | Page-Protection Checks                        | . 141 |

|   |        | No Execute (NX) Bit                           | . 141 |

|   |        | User/Supervisor (U/S) Bit                     | . 142 |

|   |        | Read/Write (R/W) Bit                          | . 142 |

|   |        | Write Protect (CR0.WP) Bit                    | . 142 |

|   | 5.7    | Protection Across Paging Hierarchy            | . 143 |

|   |        | Access to User Pages when CR0.WP=1            | . 144 |

|   | 5.8    | Effects of Segment Protection                 | . 144 |

| 6 | Syster | n-Management Instructions                     | .145  |

|   | 6.1    | Fast System Call and Return                   | . 147 |

|   |        | SYSCALL and SYSRET                            | . 148 |

|   |        | SYSENTER and SYSEXIT (Legacy Mode Only)       | . 150 |

|   |        | SWAPGS Instruction                            |       |

|   | 6.2    | System Status and Control.                    |       |

|   |        | Processor Feature Identification (CPUID).     |       |

|   |        | Accessing Control Registers                   |       |

|   |        | Accessing the RFLAGs Register                 |       |

|   |        | Accessing Debug Registers                     |       |

|   |        |                                               |       |

|                   | Accessing Model-Specific Registers              |     |

|-------------------|-------------------------------------------------|-----|

| 6.3               | Segment Register and Descriptor Register Access |     |

|                   | Accessing Segment Registers                     |     |

| <i>с</i> <b>н</b> | Accessing Descriptor-Table Registers            |     |

| 6.4               | Protection Checking.                            |     |

|                   | Checking Access Rights                          |     |

|                   | Checking Segment Limits                         |     |

|                   | Checking Read/Write Rights                      |     |

|                   | Adjusting Access Rights                         |     |

| 6.5               | Processor Halt                                  |     |

| 6.6               | Cache and TLB Management                        |     |

|                   | Cache Management                                |     |

|                   | TLB Invalidation                                |     |

|                   | nory System                                     |     |

| 7.1               | Single-Processor Memory Access Ordering         |     |

|                   | Read Ordering                                   |     |

|                   | Write Ordering.                                 |     |

|                   | Read/Write Barriers                             |     |

| 7.2               | Multiprocessor Memory Access Ordering.          |     |

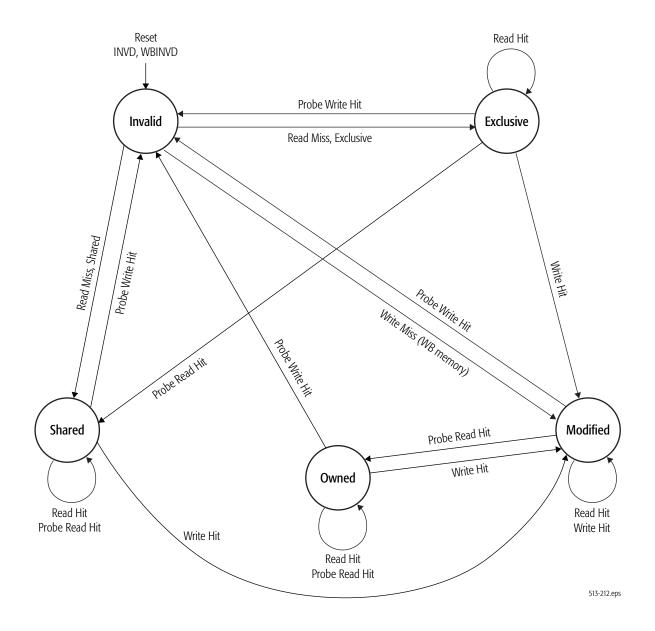

| 7.3               | Memory Coherency and Protocol                   |     |

|                   | Special Coherency Considerations                |     |

| 7.4               | Memory Types                                    | 168 |

|                   | Memory Barrier Interaction with Memory Types    | 170 |

| 7.5               | Buffering and Combining Memory Writes           |     |

|                   | Write Buffering                                 |     |

|                   | Write Combining                                 |     |

| 7.6               | Memory Caches                                   |     |

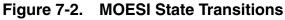

|                   | Cache Organization and Operation                |     |

|                   | Cache Control Mechanisms                        |     |

|                   | Cache and Memory Management Instructions        | 179 |

|                   | Serializing Instructions                        | 180 |

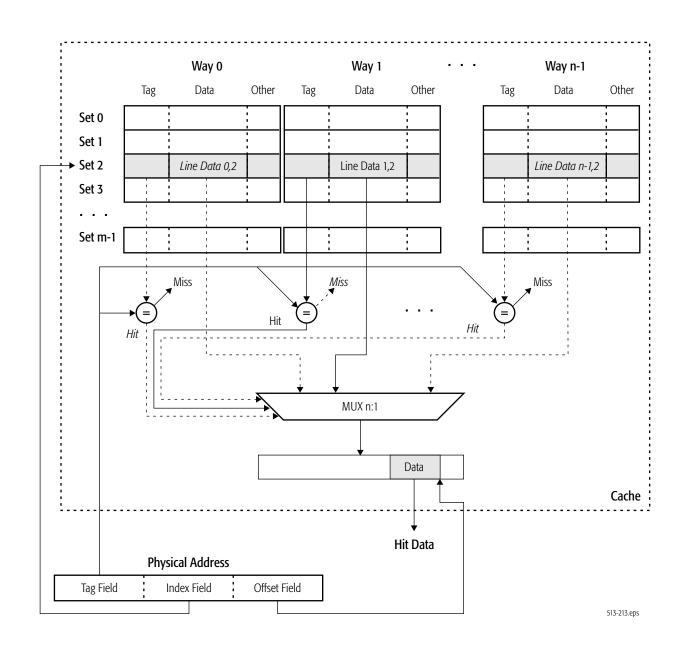

| 7.7               | Memory-Type Range Registers                     | 181 |

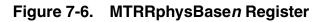

|                   | MTRR Type Fields                                | 181 |

|                   | MTRRs                                           | 182 |

|                   | Using MTRRs                                     | 188 |

|                   | MTRRs and Page Cache Controls                   | 189 |

|                   | MTRRs in Multi-Processing Environments.         | 191 |

| 7.8               | Page-Attribute Table Mechanism                  | 191 |

|                   | PAT Register                                    | 191 |

|                   | PAT Indexing                                    | 192 |

|                   | Identifying PAT Support                         | 193 |

|                   | PAT Accesses                                    | 193 |

|                   | Combined Effect of MTRRs and PAT                | 194 |

|                   | PATs in Multi-Processing Environments           |     |

| 7.9               | Memory-Mapped I/O.                              |     |

|                   | Extended Fixed-Range MTRR Type-Field Encodings  |     |

|                   | IORRs                                           |     |

|                   |                                                 |     |

|   |            | IORR Overlapping.                                    |     |

|---|------------|------------------------------------------------------|-----|

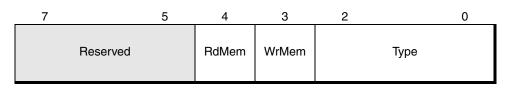

|   |            | Top of Memory                                        |     |

| 8 | Exce       | ptions and Interrupts                                | 203 |

|   | 8.1        | General Characteristics                              |     |

|   |            | Precision                                            |     |

|   |            | Instruction Restart                                  |     |

|   |            | Types of Exceptions                                  |     |

|   |            | Masking External Interrupts                          |     |

|   |            | Masking Floating-Point and Media Instructions        |     |

|   |            | Disabling Exceptions                                 |     |

|   | 8.2        | Vectors                                              |     |

|   |            | #DE—Divide-by-Zero-Error Exception (Vector 0)        |     |

|   |            | #DB—Debug Exception (Vector 1).                      |     |

|   |            | NMI—Non-Maskable-Interrupt Exception (Vector 2)      |     |

|   |            | #BP—Breakpoint Exception (Vector 3)                  |     |

|   |            | #OF—Overflow Exception (Vector 4).                   |     |

|   |            | #BR—Bound-Range Exception (Vector 5)                 |     |

|   |            | #UD—Invalid-Opcode Exception (Vector 6)              |     |

|   |            | #NM—Device-Not-Available Exception (Vector 7)        |     |

|   |            | #DF—Double-Fault Exception (Vector 8)                |     |

|   |            | Coprocessor-Segment-Overrun Exception (Vector 9)     |     |

|   |            | #TS—Invalid-TSS Exception (Vector 10).               |     |

|   |            | #NP—Segment-Not-Present Exception (Vector 11)        |     |

|   |            | #SS—Stack Exception (Vector 12)                      |     |

|   |            | #GP—General-Protection Exception (Vector 13)         |     |

|   |            | #PF—Page-Fault Exception (Vector 14)                 |     |

|   |            | #MF—x87 Floating-Point Exception-Pending (Vector 16) |     |

|   |            | #AC—Alignment-Check Exception (Vector 17)            |     |

|   |            | #XF—SIMD Floating-Point Exception (Vector 18)        |     |

|   |            | User-Defined Interrupts (Vectors 32–255).            |     |

|   | 8.3        | Exceptions During a Task Switch                      |     |

|   | 8.3<br>8.4 | Error Codes                                          |     |

|   | 0.4        | Selector-Error Code                                  |     |

|   |            | Page-Fault Error Code                                |     |

|   | 8.5        | Priorities.                                          |     |

|   | 0.0        | Floating-Point Exception Priorities                  |     |

|   |            | External Interrupt Priorities                        |     |

|   | 8.6        | Real-Mode Interrupt Control Transfers                |     |

|   | 8.7        | Legacy Protected-Mode Interrupt Control Transfers    |     |

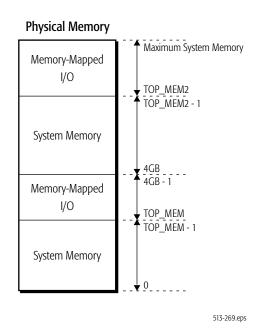

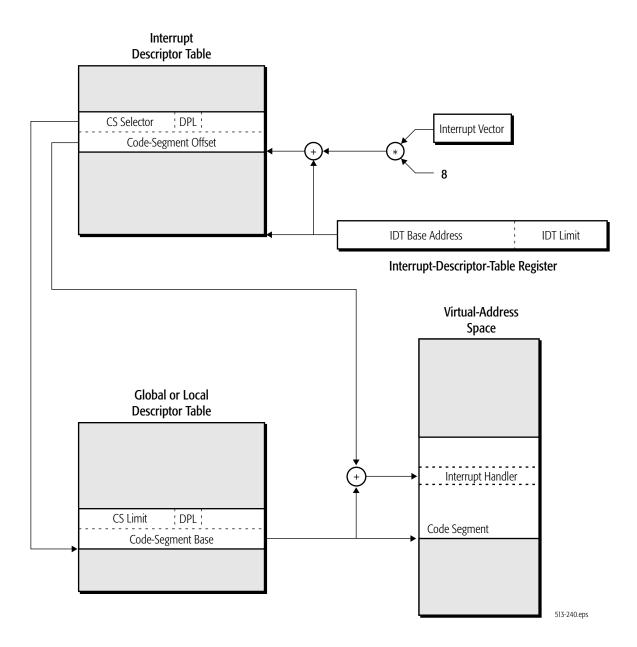

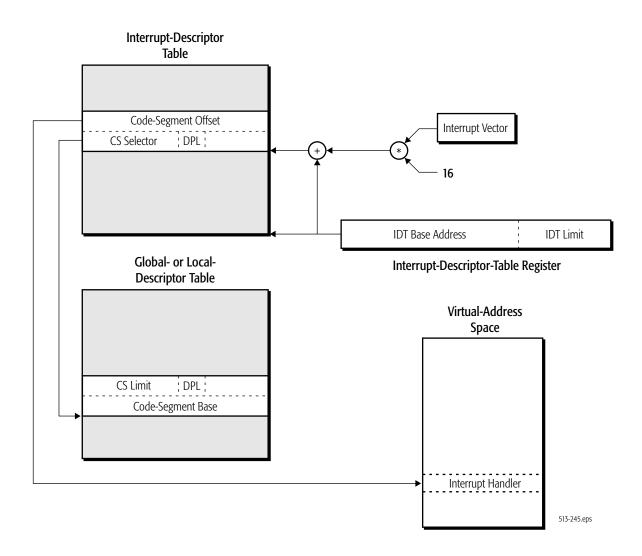

|   |            | Locating the Interrupt Handler                       |     |

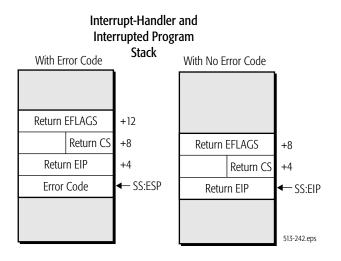

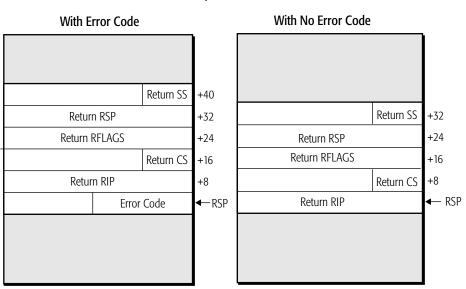

|   |            | Interrupt To Same Privilege                          |     |

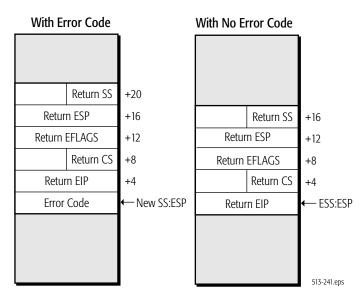

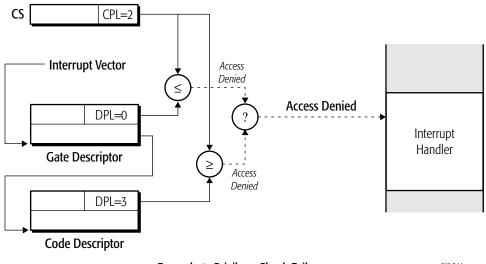

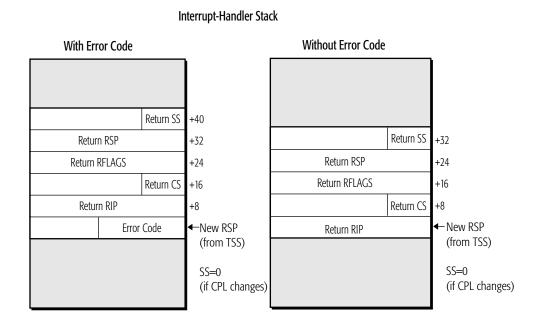

|   |            | Interrupt To Higher Privilege.                       |     |

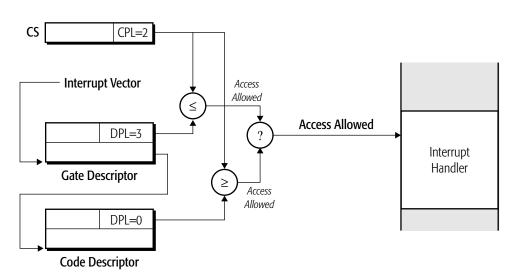

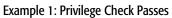

|   |            | Privilege Checks                                     |     |

|   |            | Returning From Interrupt Procedures                  |     |

|   | 8.8        | Virtual-8086 Mode Interrupt Control Transfers        |     |

|   |            | Protected-Mode Handler Control Transfer              |     |

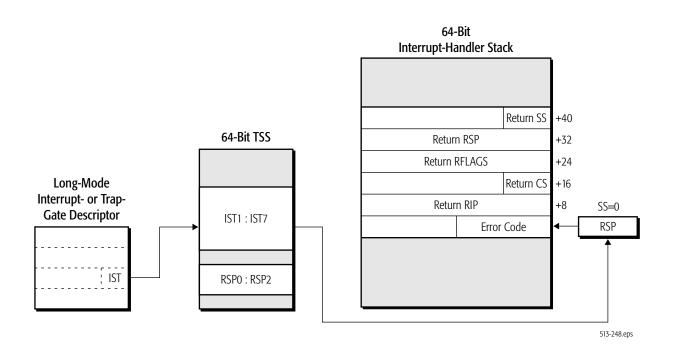

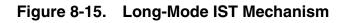

|    | 8.9                                            | Virtual-8086 Handler Control Transfer<br>Long-Mode Interrupt Control Transfers<br>Interrupt Gates and Trap Gates<br>Locating the Interrupt Handler<br>Interrupt Stack Frame                                                                                                                                                                                                                                                                                                                  | . 239<br>. 239<br>. 240                                                                                                                                                                      |

|----|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 8.10                                           | Interrupt-Stack Table       Returning From Interrupt Procedures         Virtual Interrupts       Virtual-8086 Mode Extensions         Protected Mode Virtual Interrupts       Effect of Instructions that Modify EFLAGS.IF                                                                                                                                                                                                                                                                   | . 244<br>. 245<br>. 246<br>. 249                                                                                                                                                             |

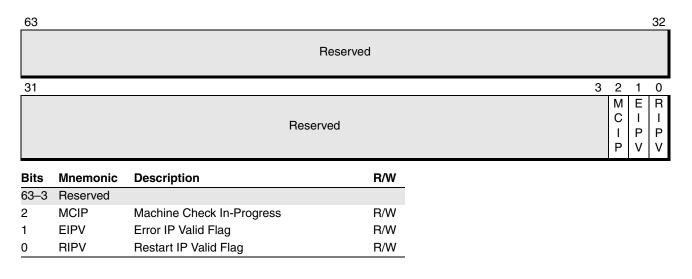

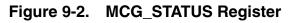

| 9  | Machi                                          | ine Check Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .253                                                                                                                                                                                         |

|    | 9.1                                            | Determining Machine-Check Support.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |

|    | 9.2                                            | Machine-Check Errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                              |

|    |                                                | Error Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                              |

|    | 9.3                                            | Machine Check MSRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |

|    |                                                | Global Status and Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                              |

|    |                                                | Error Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                              |

|    | 9.4                                            | Initializing the Machine-Check Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                              |

|    | 9.5                                            | Using Machine Check Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |

|    |                                                | Handling Machine Check Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                              |

|    |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                              |

| 10 | Gratar                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                              |

| 10 | •                                              | n-Management Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .269                                                                                                                                                                                         |

| 10 | 10.1                                           | n-Management Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>.269</b><br>. 269                                                                                                                                                                         |

| 10 | •                                              | n-Management Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 269<br>. 269<br>. 270                                                                                                                                                                      |

| 10 | 10.1                                           | n-Management Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 269<br>. 269<br>. 270<br>. 270                                                                                                                                                             |

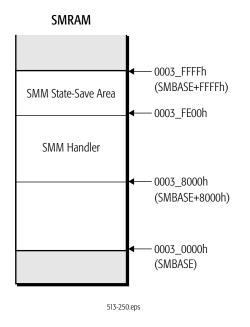

| 10 | 10.1                                           | n-Management Mode.<br>SMM Differences                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .269<br>.269<br>.270<br>.270<br>.271<br>.271                                                                                                                                                 |

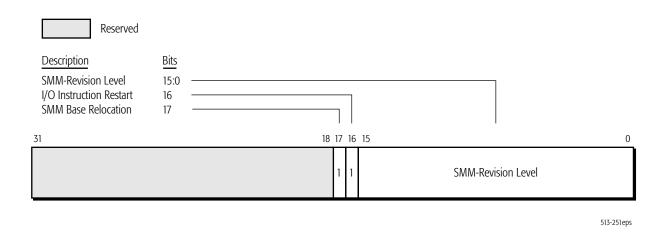

| 10 | 10.1                                           | n-Management Mode.<br>SMM Differences<br>SMM Resources.<br>SMRAM<br>SMBASE Register<br>SMRAM State-Save Area<br>SMM-Revision Identifier.                                                                                                                                                                                                                                                                                                                                                     | .269<br>.269<br>.270<br>.270<br>.271<br>.271<br>.272<br>.276                                                                                                                                 |

| 10 | 10.1<br>10.2                                   | n-Management Mode.<br>SMM Differences                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .269<br>.270<br>.270<br>.271<br>.271<br>.272<br>.276<br>.277                                                                                                                                 |

| 10 | 10.1                                           | n-Management Mode.<br>SMM Differences<br>SMM Resources.<br>SMRAM<br>SMRAM<br>SMBASE Register<br>SMRAM State-Save Area<br>SMM-Revision Identifier.<br>SMRAM Protected Area<br>Using SMM                                                                                                                                                                                                                                                                                                       | .269<br>.270<br>.270<br>.271<br>.272<br>.276<br>.277<br>.279                                                                                                                                 |

| 10 | 10.1<br>10.2                                   | n-Management Mode.<br>SMM Differences<br>SMM Resources.<br>SMRAM<br>SMRAM<br>SMBASE Register<br>SMRAM State-Save Area<br>SMR-Revision Identifier.<br>SMRAM Protected Area<br>Using SMM<br>System-Management Interrupt (SMI)                                                                                                                                                                                                                                                                  | .269<br>.269<br>.270<br>.270<br>.271<br>.272<br>.276<br>.277<br>.279<br>.279                                                                                                                 |

| 10 | 10.1<br>10.2                                   | n-Management Mode.<br>SMM Differences<br>SMM Resources.<br>SMRAM<br>SMRAM<br>SMBASE Register<br>SMRAM State-Save Area<br>SMM-Revision Identifier.<br>SMRAM Protected Area<br>Using SMM                                                                                                                                                                                                                                                                                                       | .269<br>.269<br>.270<br>.270<br>.271<br>.272<br>.276<br>.277<br>.279<br>.279<br>.279<br>.279                                                                                                 |

| 10 | 10.1<br>10.2                                   | n-Management Mode.<br>SMM Differences                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .269<br>.270<br>.270<br>.271<br>.272<br>.276<br>.277<br>.279<br>.279<br>.279<br>.279<br>.280<br>.281                                                                                         |

| 10 | 10.1<br>10.2                                   | n-Management Mode.<br>SMM Differences<br>SMM Resources.<br>SMRAM<br>SMRAM<br>SMBASE Register .<br>SMRAM State-Save Area<br>SMM-Revision Identifier.<br>SMRAM Protected Area<br>Using SMM .<br>System-Management Interrupt (SMI)<br>SMM Operating-Environment.<br>Exceptions and Interrupts<br>Invalidating the Caches<br>Saving Additional Processor State.                                                                                                                                  | .269<br>.269<br>.270<br>.271<br>.272<br>.272<br>.276<br>.277<br>.279<br>.279<br>.279<br>.280<br>.281<br>.281                                                                                 |

| 10 | 10.1<br>10.2                                   | n-Management Mode.<br>SMM Differences<br>SMM Resources.<br>SMRAM<br>SMBASE Register .<br>SMRAM State-Save Area<br>SMRAM State-Save Area<br>SMM-Revision Identifier.<br>SMRAM Protected Area<br>Using SMM.<br>System-Management Interrupt (SMI)<br>SMM Operating-Environment.<br>Exceptions and Interrupts<br>Invalidating the Caches<br>Saving Additional Processor State.<br>Operating in Protected Mode and Long Mode                                                                      | .269<br>.269<br>.270<br>.270<br>.271<br>.272<br>.276<br>.277<br>.279<br>.279<br>.279<br>.279<br>.280<br>.281<br>.281<br>.281                                                                 |

| 10 | 10.1<br>10.2                                   | n-Management Mode.<br>SMM Differences<br>SMM Resources.<br>SMRAM<br>SMBASE Register .<br>SMRAM State-Save Area .<br>SMRAM State-Save Area .<br>SMM-Revision Identifier.<br>SMRAM Protected Area .<br>Using SMM .<br>System-Management Interrupt (SMI) .<br>SMM Operating-Environment.<br>Exceptions and Interrupts .<br>Invalidating the Caches .<br>Saving Additional Processor State.<br>Operating in Protected Mode and Long Mode .<br>Auto-Halt Restart.                                 | .269<br>.269<br>.270<br>.270<br>.271<br>.272<br>.276<br>.277<br>.279<br>.279<br>.279<br>.279<br>.279<br>.280<br>.281<br>.281<br>.281<br>.282<br>.282                                         |

| 10 | 10.1<br>10.2                                   | n-Management Mode.<br>SMM Differences<br>SMM Resources.<br>SMRAM<br>SMBASE Register .<br>SMRAM State-Save Area<br>SMRAM State-Save Area<br>SMM-Revision Identifier.<br>SMRAM Protected Area<br>Using SMM.<br>System-Management Interrupt (SMI)<br>SMM Operating-Environment.<br>Exceptions and Interrupts<br>Invalidating the Caches<br>Saving Additional Processor State.<br>Operating in Protected Mode and Long Mode                                                                      | .269<br>.269<br>.270<br>.271<br>.272<br>.276<br>.277<br>.279<br>.279<br>.279<br>.279<br>.280<br>.281<br>.281<br>.281<br>.282<br>.282<br>.283                                                 |

| 10 | 10.1<br>10.2<br>10.3                           | n-Management Mode.<br>SMM Differences<br>SMM Resources.<br>SMRAM<br>SMBASE Register<br>SMRAM State-Save Area<br>SMM-Revision Identifier.<br>SMRAM Protected Area<br>Using SMM<br>System-Management Interrupt (SMI)<br>SMM Operating-Environment.<br>Exceptions and Interrupts<br>Invalidating the Caches<br>Saving Additional Processor State.<br>Operating in Protected Mode and Long Mode<br>Auto-Halt Restart.<br>I/O Instruction Restart<br>Leaving SMM                                  | .269<br>.269<br>.270<br>.270<br>.271<br>.272<br>.276<br>.277<br>.279<br>.279<br>.279<br>.279<br>.279<br>.280<br>.281<br>.281<br>.281<br>.282<br>.282<br>.283<br>.284                         |

|    | 10.1<br>10.2<br>10.3<br>10.4<br><b>128-B</b> i | n-Management Mode.<br>SMM Differences<br>SMM Resources.<br>SMRAM<br>SMBASE Register<br>SMRAM State-Save Area<br>SMRAM State-Save Area<br>SMRAM Protected Area<br>Using SMM.<br>System-Management Interrupt (SMI)<br>SMM Operating-Environment.<br>Exceptions and Interrupts<br>Invalidating the Caches<br>Saving Additional Processor State.<br>Operating in Protected Mode and Long Mode<br>Auto-Halt Restart.<br>I/O Instruction Restart<br>Leaving SMM<br>it, 64-Bit, and x87 Programming | .269<br>.269<br>.270<br>.271<br>.272<br>.276<br>.277<br>.279<br>.279<br>.279<br>.279<br>.279<br>.281<br>.281<br>.281<br>.281<br>.282<br>.283<br>.283<br>.284<br>.284<br>.287                 |

|    | 10.1<br>10.2<br>10.3                           | n-Management Mode.<br>SMM Differences<br>SMM Resources.<br>SMRAM<br>SMBASE Register<br>SMRAM State-Save Area<br>SMM-Revision Identifier.<br>SMRAM Protected Area<br>Using SMM<br>System-Management Interrupt (SMI)<br>SMM Operating-Environment.<br>Exceptions and Interrupts<br>Invalidating the Caches<br>Saving Additional Processor State.<br>Operating in Protected Mode and Long Mode<br>Auto-Halt Restart.<br>I/O Instruction Restart<br>Leaving SMM                                  | .269<br>.269<br>.270<br>.270<br>.271<br>.272<br>.276<br>.277<br>.279<br>.279<br>.279<br>.279<br>.279<br>.280<br>.281<br>.281<br>.281<br>.281<br>.282<br>.283<br>.283<br>.284<br>.287<br>.287 |

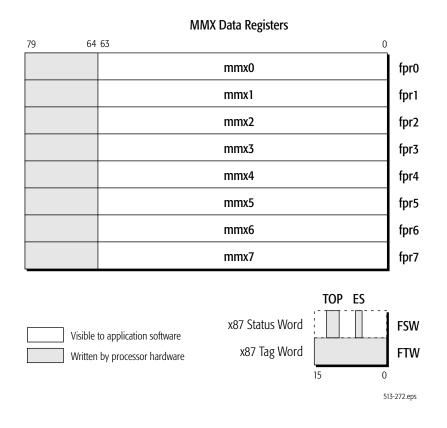

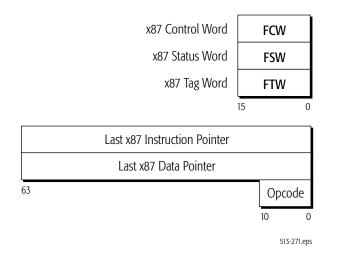

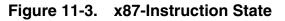

|    | 11.4  | Media and x87 Processor State                | 289 |

|----|-------|----------------------------------------------|-----|

|    |       | 128-Bit Media State                          | 289 |

|    |       | 64-Bit Media State                           | 290 |

|    |       | x87 State                                    | 292 |

|    |       | Saving Media and x87 Processor State         | 293 |

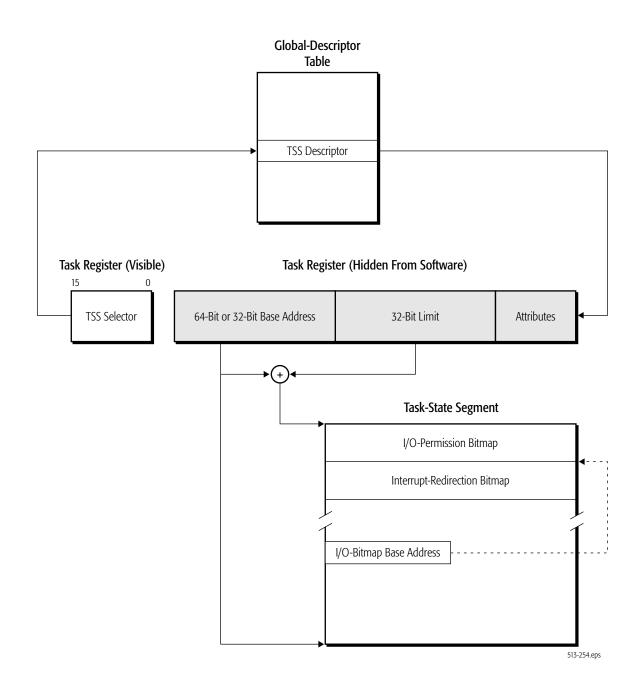

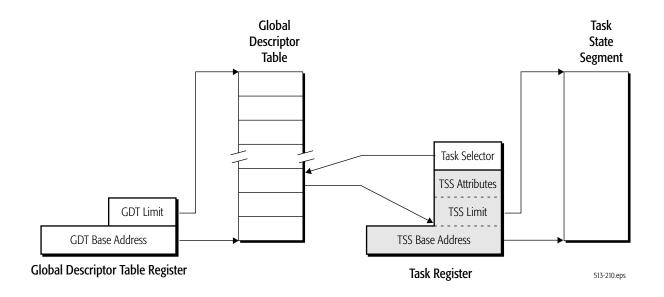

| 12 | Task  | Management                                   | 305 |

|    | 12.1  | Hardware Multitasking Overview               |     |

|    | 12.1  | Task-Management Resources                    |     |

|    | 12.2  | TSS Selector                                 |     |

|    |       | TSS Descriptor.                              |     |

|    |       | Task Register                                |     |

|    |       | Legacy Task-State Segment.                   |     |

|    |       | 64-Bit Task State Segment.                   |     |

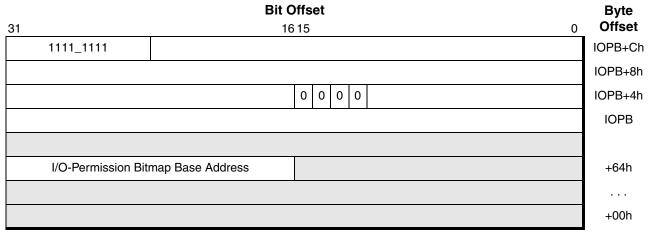

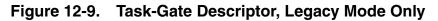

|    |       | Task Gate Descriptor (Legacy Mode Only).     |     |

|    | 12.3  | Hardware Task-Management in Legacy Mode      |     |

|    | 12.3  | Task Memory-Mapping                          |     |

|    |       | Switching Tasks                              |     |

|    |       | Task Switches Using Task Gates               |     |

|    |       | Nesting Tasks                                |     |

|    |       |                                              |     |

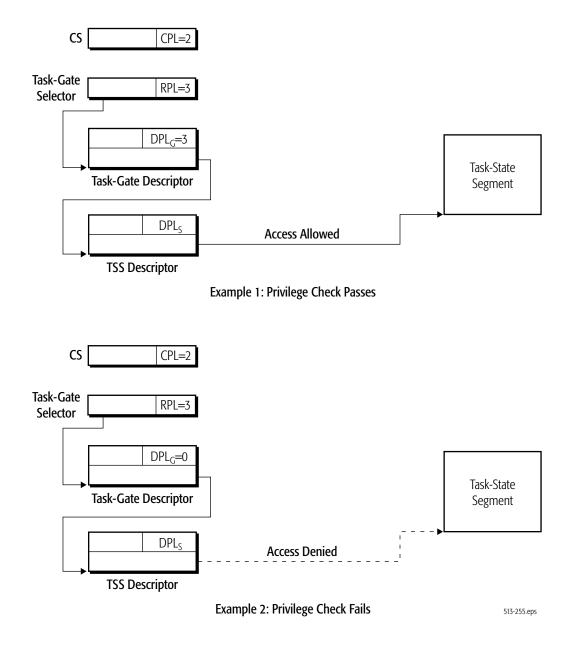

| 13 |       | g and Performance Resources                  |     |

|    | 13.1  | Software-Debug Resources                     |     |

|    |       | Debug Registers                              |     |

|    | 13.2  | Breakpoints                                  |     |

|    |       | Setting Breakpoints                          |     |

|    |       | Using Breakpoints                            |     |

|    |       | Single Stepping                              |     |

|    |       | Breakpoint Instruction (INT3).               |     |

|    |       | Control-Transfer Breakpoint Features         |     |

|    | 13.3  | Performance Optimization.                    |     |

|    |       | Performance Counters                         |     |

|    |       | Performance Event-Select Registers           |     |

|    |       | Using Performance Counters                   |     |

|    |       | Time-Stamp Counter                           | 344 |

| 14 | Proce | ssor Initialization and Long Mode Activation | 347 |

|    | 14.1  | Reset and Initialization                     | 347 |

|    |       | Built-In Self Test (BIST)                    | 347 |

|    |       | Clock Multiplier Selection.                  | 348 |

|    |       | Processor Initialization State               |     |

|    |       | Multiple Processor Initialization            | 350 |

|    |       | Fetching the First Instruction               |     |

|    | 14.2  | Hardware Configuration                       |     |

|    |       | Processor Implementation Information         |     |

|    |       | Enabling Internal Caches.                    |     |

|    |       | Initializing Media and x87 Processor State   |     |

|    |       | Model-Specific Initialization                |     |

|    |       |                                              |     |

|    | 14.3  | Initializing Real Mode                      |     |

|----|-------|---------------------------------------------|-----|

|    | 14.4  | Initializing Protected Mode                 |     |

|    | 14.5  | Initializing Long Mode                      |     |

|    | 14.6  | Enabling and Activating Long Mode           |     |

|    |       | Activating Long Mode                        |     |

|    |       | Consistency Checks                          |     |

|    |       | Updating System Descriptor Table References |     |

|    |       | Relocating Page-Translation Tables.         |     |

|    | 14.7  | Leaving Long Mode                           |     |

|    | 14.8  | Long-Mode Initialization Example            |     |

| 15 |       | e Virtual Machine                           |     |

|    | 15.1  | The Virtual Machine Monitor                 |     |

|    | 15.2  | SVM Hardware Overview                       |     |

|    |       | Virtualization Support                      |     |

|    |       | Guest Mode                                  |     |

|    |       | External Access Protection                  |     |

|    |       | Tagged TLB                                  |     |

|    |       | Interrupt Support                           |     |

|    |       | Restartable Instructions                    |     |

|    |       | Security Support                            |     |

|    | 15.3  | SVM Processor and Platform Extensions       |     |

|    | 15.4  | Enabling SVM                                |     |

|    | 15.5  | VMRUN Instruction                           |     |

|    |       | Basic Operation                             |     |

|    | 15.6  | #VMEXIT                                     |     |

|    | 15.7  | Intercept Operation                         |     |

|    |       | State Saved on Exit                         |     |

|    |       | Intercepts During IDT Interrupt Delivery    |     |

|    |       | EXITINTINFO Pseudo-Code                     |     |

|    | 15.8  | Instruction Intercepts                      |     |

|    | 15.9  | IOIO Intercepts                             |     |

|    | 15.10 | MSR Intercepts                              |     |

|    | 15.11 | Exception Intercepts                        |     |

|    |       | Vector 2 (Reserved)                         |     |

|    |       | #BP (Breakpoint)                            |     |

|    |       | #OF (Overflow)                              |     |

|    |       | #BR (Bound-Range)                           |     |

|    |       | #UD (Invalid Opcode)                        |     |

|    |       | #NM (Device-Not-Available)                  |     |

|    |       | #DF (Double Fault)                          |     |

|    |       | Vector 9 (Reserved)                         |     |

|    |       | #TS (Invalid TSS)                           |     |

|    |       | #NP (Segment Not Present).                  |     |

|    |       | #SS (Stack Fault)                           |     |

|    |       | #GP (General Protection)                    |     |

|    |       | #PF (Page Fault)                            |     |

|    |       | #MF (X87 Floating Point)                    | 383 |

|       | #AC (Alignment Check)                             | . 383 |

|-------|---------------------------------------------------|-------|

|       | #MC (Machine Check)                               | . 383 |

|       | #XF (SIMD Floating Point)                         | . 383 |

| 15.12 | Interrupt Intercepts.                             | . 384 |

|       | INTR Intercept.                                   | . 384 |

|       | NMI Intercept                                     | . 384 |

|       | SMI Intercept                                     | . 384 |

|       | INIT Intercept                                    |       |

|       | Virtual Interrupt Intercept                       | . 385 |

| 15.13 | Miscellaneous Intercepts                          | . 386 |

|       | Task Switch Intercept.                            | . 386 |

|       | Ferr_Freeze Intercept                             | . 386 |

|       | Shutdown Intercept                                | . 386 |

| 15.14 | VMSAVE and VMLOAD Instructions                    | . 386 |

| 15.15 | TLB Control.                                      | . 387 |

|       | TLB Flush                                         | . 388 |

|       | Invalidate Page, Alternate ASID                   | . 388 |

| 15.16 | Global Interrupt Flag, STGI and CLGI Instructions | . 388 |

| 15.17 | VMMCALL Instruction.                              | . 389 |

| 15.18 | Paged Real Mode                                   | . 389 |

| 15.19 | Event Injection                                   | . 389 |

| 15.20 | Interrupt and Local APIC Support.                 | . 391 |

|       | Physical (INTR) Interrupt Masking in EFLAGS.      | . 391 |

|       | Virtualizing APIC.TPR                             | . 391 |

|       | TPR Access in 32-Bit Mode                         | . 391 |

|       | Injecting Virtual (INTR) Interrupts               |       |

|       | Interrupt Shadows                                 | . 393 |

|       | Virtual Interrupt Intercept                       |       |

|       | INIT Support                                      |       |

|       | NMI Support                                       |       |

| 15.21 | SMM Support                                       |       |

|       | Sources of SMI                                    |       |

|       | Response to SMI                                   |       |

|       | Containerizing Platform SMM                       |       |

| 15.22 | Last Branch Record Virtualization                 |       |

|       | Enabling LBR Virualization                        |       |

|       | Host and Guest LBR Virtualization                 |       |

|       | LBR Virtualization CPUID Feature Detection        |       |

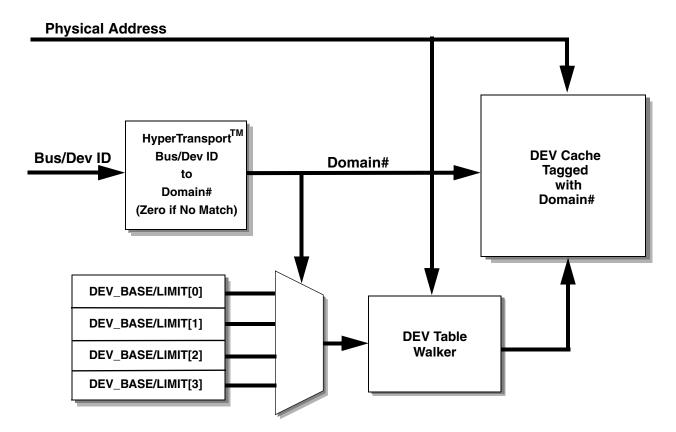

| 15.23 | External Access Protection                        |       |

|       | Device IDs and Protection Domains                 |       |

|       | Device Exclusion Vector (DEV)                     |       |

|       | Access Checking                                   |       |

|       | DEV Capability Block.                             |       |

|       | DEV Register Access Mechanism.                    |       |

|       | DEV Control and Status Registers.                 |       |

|       | Unauthorized Access Logging.                      |       |

|       | Secure Initialization Support                     | . 403 |

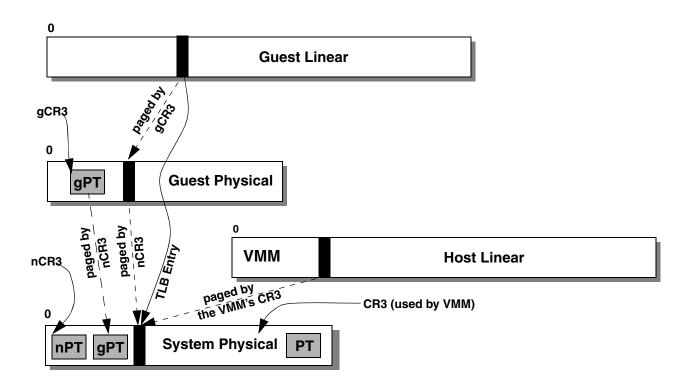

| 15.24 | Nested Paging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | Traditional Paging versus Nested Paging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|       | Replicated State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|       | Enabling Nested Paging.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 406 |

|       | Nested Paging and VMRUN/#VMEXIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|       | Nested Table Walk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|       | Nested versus Guest Page Faults, Fault Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|       | Combining Nested and Guest Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|       | Combining Memory Types, MTRRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |