Geode<sup>™</sup> SC2200 Thin Client on a Chip

National Semiconductor

# Geode<sup>™</sup> SC2200 Thin Client on a Chip

### **General Description**

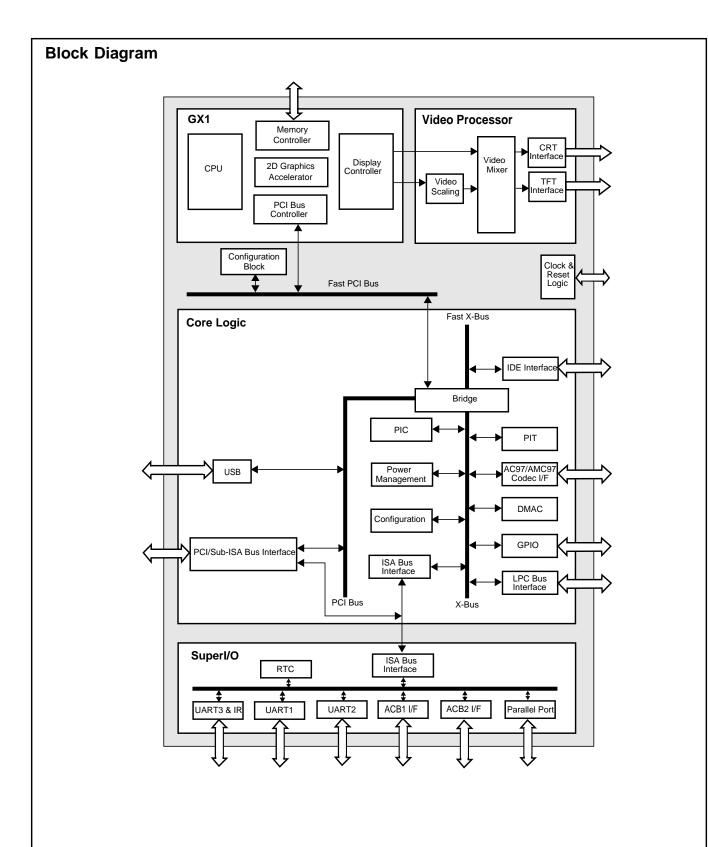

The Geode<sup>™</sup> SC2200 device is a member of the National IA on a Chip family of fully integrated x86 system chips. The Geode SC2200 includes a Geode GX1 32-bit x86 compatible processor, a CRT and TFT video processor, core logic and a SuperI/O block.

These features, combined with the device's small form factor and low power consumption, make it ideal as the core of a thin client. In particular, the SC2200 is an optimal solution for thin clients that are integrated into a flat panel display (FPD).

The Geode SC2200 integrated architecture simplifies system design by reducing the component count, the number of traces on the main system board, and the overall system power requirements. It can significantly lower overall system costs while improving time-tomarket.

### Primary Components of the GeedSC2200

The Geode GX1 combines advanced CPU performance with MMX<sup>™</sup> support, fully accelerated 2D graphics, a 64-bit synchronous DRAM (SDRAM) interface, a PCI bus controller, and a display controller.

**PRODUCT BRIEF**

September 2000

- The low-power CRT and TFT video processor has a hardware video accelerator for scaling, filtering, and color space conversion.

- Core Logic of the SC2200 device includes: PC AT functionality, a USB interface, an IDE interface, a PCI bus interface, an LPC bus interface, ACPI 1.0 compliant power managementand an audio codec interface.

- Other primary components include: three serial ports (UART1, UART2, UART3 with fast Infrared), a parallel port, two ACCESS.bus (ACB) interfaces, and a Real-Time Clock (RTC).

The block diagram on the following page shows the relationships between the functional blocks in the SC2200.

No part of this document may be reproduced in any form, or by any means, without the prior written consent of National Semiconductor Corporation.

National Semiconductor is a registered trademark, and Geode is a trademark of National Semiconductor Corporation. All other brand or product names are trademarks or registered trademarks of their respective holders.

### Features

### **Outstanding Features**

- 32-bit x86 processor, up to 266 MHz, with MMX instruction set support

- Memory controller with 64-bit SDRAM interface

- 2D graphics accelerator

- CRT and TFT controller with hardware video accelerator

- PC AT functionality

- PCI bus controller

- IDE interface

- USB, three ports, OpenHCI 1.0 compliant

- Audio, AC97/AMC97 2.0 compliant

- Virtual System Architecture (VSA<sup>™</sup>) support

- Power management, ACPI 1.0 compliant

- EBGA package

#### GX1

### CPU

- 32-bit x86, up to 266 MHz, with MMX compatible instruction set support

- 16 KB unified L1 cache

- Integrated Floating Point Unit (FPU)

- Re-entrant SMM enhanced for VSA

### **2D Graphics Accelerator**

- Accelerates BitBLTs, line draw and text

- Supports all 256 raster operations

- Supports transparent BLTs

- Runs at core clock frequency

### **Memory Controller**

- 64-bit SDRAM interface

- 66 MHz to 100 MHz frequency range

- Direct interface with CPU/cache, display controller and 2D graphic accelerator

- Supports clock suspend and power-down/selfrefresh

- Up to 8 SDRAM devices or one DIMM/SODIMM

### **Display Controller**

- Hardware graphics frame buffer compress/decompress

- Hardware cursor, 32 x 32 pixels

#### Video Processor

#### Video Accelerator

• Hardware video accelerator with video shaping and image enhancing

- Flexible video scaling support of up to 800% (horizontally and vertically)

- Bilinear interpolation filters (with two taps, and eight phases) to smooth output video

- Video/Graphics mixer using color key

- CRT interface

- 1280 x 1024 non-interlaced CRT @ 8 bpp, up to 75 Hz

- 1024 x 768 non-interlaced CRT @ 16 bpp, up to 85 Hz

- True color support up to 135 MHz (triple 8-bit DACs)

- TFT Interface

- 800 x 600 non-interlaced TFT @ 16 bpp Graphics, up to 75 Hz 18 bpp interface

- 1024 x 768 non-interlaced TFT @ 16 bpp Graphics, up to 75 Hz 18 bpp interface

### Core Logic

#### Audio

- AC97/AMC97 (Rev. 2.0) codec interface

- Legacy audio emulation using XpressAUDIO<sup>™</sup>

- 6 DMA channels

#### **PC AT Functionality**

- Programmable Interrupt Controller (PIC), 8259Aequivalent

- Programmable Interval Timer (PIT), 8254-equivalent

- DMA Controller (DMAC), 8237-equivalent

#### **Power Management**

- ACPI 1.0 compliant

- Sx state control of three power planes

- Cx/Sx state control of clocks and PLLs

- Thermal event input

- Wake-up event support:

- Three general-purpose events

- AC97 codec event

- UART2 RI signal

- Infrared (IR) event

### General Purpose I/O (GPIO) Ports

• 27 multiplexed GPIO signals

### Low Pin Count (LPC) Bus Interface

• Specification Rev. 1.0 compatible

#### **PCI Bus Interface**

- PCI 2.1 compliant with wake-up capability

- 32-bit data path, up to 33 MHz

- Glueless interface for an external PCI device

- Fixed priority

- 3.3V signal support only

### Features (Continued)

### Sub-ISA Bus Interface

- Up to 16 MB addressing

- Supports a chip select for ROM or Flash EPROM boot device

- Supports either:

- DiskOnChip<sup>®</sup> DOC2000 Flash file system

- NAND E<sup>2</sup>PROM

- Supports up to two chip selects for external I/O devices

- 8-bit (optional 16-bit) data bus width

- Shares balls with PCI signals

### **IDE Interface**

- IDE channel for up to two external IDE devices

- Supports ATA-33 synchronous DMA mode transfers, up to 33 MB/s

### **Universal Serial Bus (USB)**

- USB OpenHCI 1.0 compliant

- Three ports

### SuperI/O

### Real-Time Clock (RTC)

- DS1287, MC146818 and PC87911 compatible

- Multi-century calendar

### ACCESS.bus (ACB) Interface

Two ACB interface ports

### **Parallel Port**

- EPP 1.9 compliant

- IEEE1284 ECP compliant, including level 2

### Serial Port (UART)

- UART1, 16550A compatible (SIN, SOUT, BOUT pins), used for smart card interface

- UART2, 16550A compatible

- Enhanced UART with fast Infrared (IR)

#### **Other Features**

### **High Resolution Timer**

• 32-bit counter with 0.92593 μS count interval

### WATCHDOG

• Interfaces to INTR, SMI, Reset

## Clocks

- Input:

- 32.768 KHz (internal clock oscillator)

- 25 MHz (internal clock oscillator)

- Output:

- AC97 clock (24.576 MHz)

- Memory controller clock (66 MHz to 100 MHz)

- Ethernet clock (25 MHz)

- PCI clock (33 MHz)

### **JTAG Testability**

Bypass, Extest, Sample/Preload, IDcode, Clamp, Hiz

#### Voltages

- Internal logic:

- CPU frequency up to 266 MHz: 2.0VCPU frequency up to 200 MHz: 1.8V

- Battery: 3V

- I/O: 3.3V

- Standby: 3.3V

- Internal standby: 1.8V

### Package

- EBGA, 432 balls

- Footprint: 40 x 40 mm,1.27 mm pitch

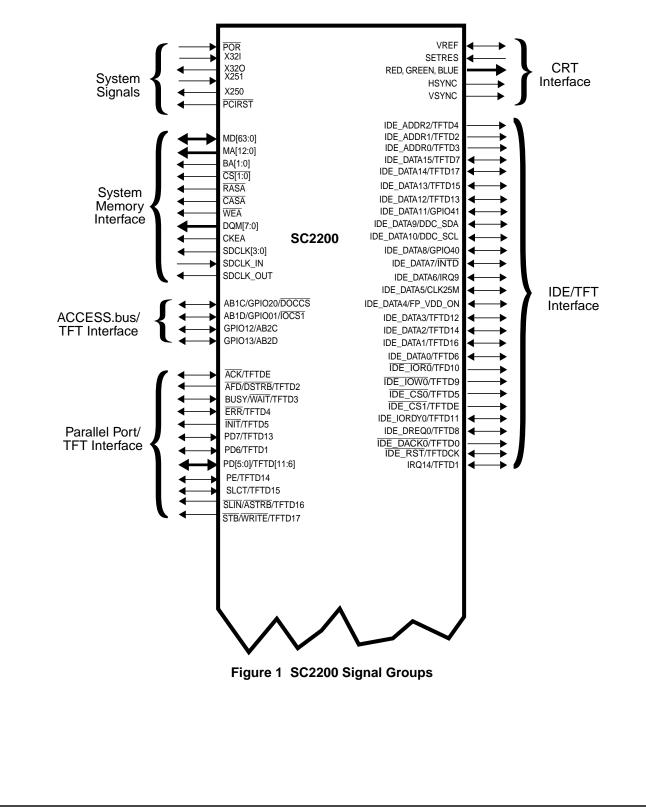

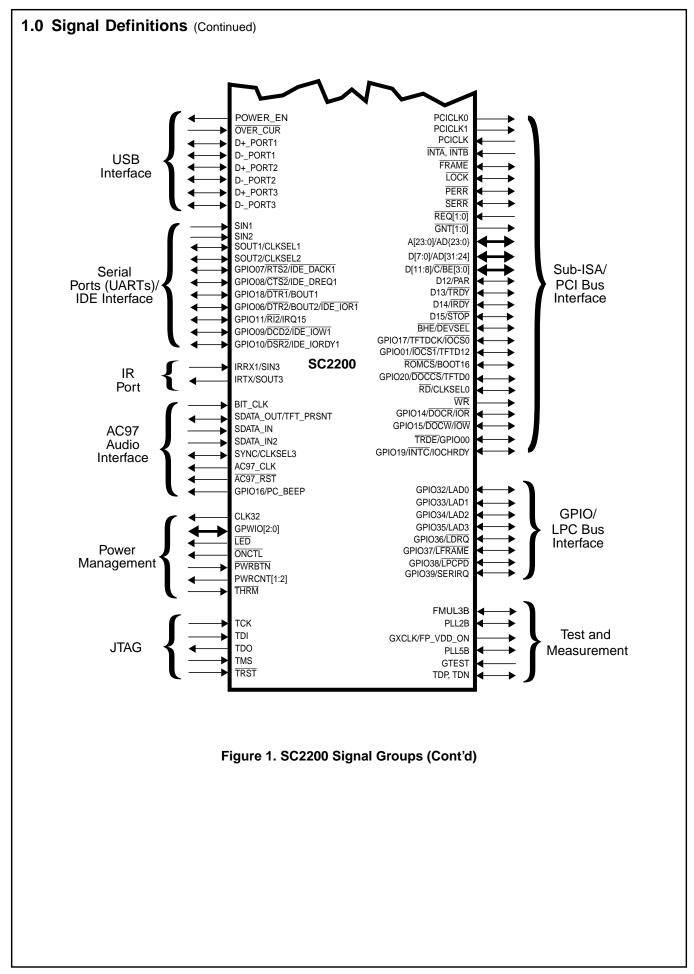

## 1.0 Signal Definitions

This section defines the signals and describes the external interface of the SC2200 device. Figure 2-1 shows the signals organized by their functional groups. Where signals are multiplexed, the default signal name is listed first and is separated by a slash (/) from other signal names.

The overline () symbol above a signal name indicates that the active or asserted state occurs when the signal is at a low voltage level. Otherwise, the signal is asserted when at a high voltage level.

### 1.1 Signal Groups

# 1.1.1 Functional Pin Summary

| Module                                                 | Pin Count |

|--------------------------------------------------------|-----------|

| System Signals                                         | 6         |

| System Memory Interface                                | 99        |

| CRT Interface                                          | 7         |

| IDE Interface (channel 1)                              | 28        |

| IDE Interface (channel 2, multiplexed))                | (6)       |

| TFT Interface (multiplexed)                            | (21)      |

| ACCESS.bus Interface                                   | 4         |

| PCI Bus Interface                                      | 54        |

| Sub-ISA Interface (including NAND E <sup>2</sup> PROM) | 10        |

| LPC Interface                                          | 8         |

| Universal Serial Bus (USB)                             | 8         |

| UART1 (for smart card)                                 | 3         |

| UART2                                                  | 8         |

| Parallel Port Interface (IEEE 1284)                    | 17        |

| Fast Infrared (IR) Port / UART3                        | 2         |

| AC97 Audio Interface                                   | 8         |

| Power Management                                       | 10        |

| Miscellaneous/Test/JTAG                                | 12        |

| GPIO Ports (multiplexed)                               | (27)      |

| Total                                                  | 284       |

### 1.1.2 Signal Descriptions

The following tables contain descriptions of each signal of the SC2200 device.

### 1.1.3 System Signals

| Name        | Туре | Description                                                                                                                                                                                                                                                                                                                                           | MUX |

|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| CLKSEL[1:0] | I    | <b>Fast PCI Clock Select.</b> These strap signals are used to set the internal fast PCI clock.                                                                                                                                                                                                                                                        |     |

|             |      | 00:       33.3 MHz         01:       48 MHz         10:       66.7 MHz         11:       33.3 MHz                                                                                                                                                                                                                                                     |     |

|             |      | During system reset, an internal pull-down resistor of 100 K $\Omega$ exists on these pins. If needed, an external pull-up resistor of 15 K $\Omega$ should be placed. <sup>1</sup>                                                                                                                                                                   |     |

| CLKSEL[3:2] | I    | <b>Maximum Core Clock Multiplier.</b> These strap signals are used to set the maximum allowed multiplier value for the core clock.                                                                                                                                                                                                                    |     |

|             |      | During system reset, an internal pull-down resistor of 100 K $\Omega$ exists on these pins. If needed, an external pull-up resistor of 15 K $\Omega$ should be placed. <sup>1</sup>                                                                                                                                                                   |     |

| BOOT16      | 1    | <b>16-Bit Wide Boot ROM.</b> This strap signal enables the optional 16-bit wide Sub-ISA bus.                                                                                                                                                                                                                                                          |     |

|             |      | During system reset, an internal pull-down resistor of 100 K $\Omega$ exists on this pin. If needed, an external pull-up resistor of 15 K $\Omega$ should be placed. <sup>1</sup>                                                                                                                                                                     |     |

| POR         | 1    | <b>Power On Reset.</b> POR is the system reset signal generated from the power supply to indicate that the system should be reset.                                                                                                                                                                                                                    |     |

| X32I, X32O  | I/O  | <b>Crystal.</b> Connected directly to a 32.768 KHz crystal. This clock input is required even if the internal RTC is not being used. Some of the internal clocks are derived from this clock. If an external clock is used, it should be connected to X32I, (X32O should remain unconnected), using a voltage level of 0 volts to V <sub>CORE</sub> . |     |

| X25I, X25O  | I/O  | <b>Crystal.</b> Connected directly to a 25 MHz crystal. This clock input is used for video circuits. Some of the internal clocks are derived from this clock. If an external clock is used, it should be connected to X25I, and X250, using a voltage level of 0 volts to $V_{IO}$ . X25O should remain unconnected.                                  |     |

| CLK25M      | 0    | 25 MHz Output Clock                                                                                                                                                                                                                                                                                                                                   |     |

| PCIRST      | 0    | <b>PCI and System Reset.</b> PCIRST is the reset signal for the PCI bus and system. It is asserted for approximately 100 $\mu$ S after POR is negated.                                                                                                                                                                                                |     |

1. An external pull-up or pull-down resistor may be needed for these pins if external components have an input DC current. This resistor should have a resistance of at least  $1K\Omega$ .

## 1.1.4 System Memory Interface

| Name           | Туре | Description                                                                                                                                                                                                                                                                                            |  |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MD[63:0]       | I/O  | Memory Data Bus. The data bus lines driven to/from system memory.                                                                                                                                                                                                                                      |  |

| MA[12:0]       | 0    | <b>Memory Address Bus.</b> The multiplexed row/column address lines driven to the system memory. Supports 256 Mbit SDRAM.                                                                                                                                                                              |  |

| BA[1:0]        | 0    | Bank Address Bits. These bits are used to select the component bank within the SDRAM.                                                                                                                                                                                                                  |  |

| <u>CS[1:0]</u> | 0    | <b>Chip Selects.</b> These bits are used to select the module bank within system memory. Each chip select corresponds to a specific module bank. If $\overline{CS}$ is high, the bank(s) do not respond to $\overline{RAS}$ , $\overline{CAS}$ , and $\overline{WE}$ until the bank is selected again. |  |

| RASA           | 0    | <b>Row Address Strobe.</b> $\overrightarrow{RAS}$ , $\overrightarrow{CAS}$ , $\overrightarrow{WE}$ and CKE are encoded to support the different SDRAM commands. $\overrightarrow{RASA}$ is used with $\overrightarrow{CS[1:0]}$ .                                                                      |  |

| CASA           | 0    | <b>Column Address Strobe.</b> $\overrightarrow{RAS}$ , $\overrightarrow{CAS}$ , $\overrightarrow{WE}$ and CKE are encoded to support the different SDRAM commands. $\overrightarrow{CASA}$ is used with $\overrightarrow{CS[1:0]}$ .                                                                   |  |

| WEA            | 0    | <b>Write Enable.</b> RAS, $\overline{CAS}$ , $\overline{WE}$ and CKE are encoded to support the different SDRAM commands. WEA is used with $\overline{CS[1:0]}$ .                                                                                                                                      |  |

| DQM[7:0]       | 0    | Data Mask Control Bits                                                                                                                                                                                                                                                                                 |  |

|                |      | During memory read cycles, these outputs control whether SDRAM out-<br>put buffers are driven on the MD bus or not. All DQM signals are asserted<br>during read cycles.                                                                                                                                |  |

|                |      | During memory write cycles, these outputs control whether or not MD data will be written into SDRAM.                                                                                                                                                                                                   |  |

|                |      | DQM[7:0] connect directly to the [DQM7:0] pins of each DIMM connector.                                                                                                                                                                                                                                 |  |

| CKEA           | 0    | Clock Enable. These signals are used to enter Suspend/power-down mode.                                                                                                                                                                                                                                 |  |

|                |      | If CKE goes low when no read or write cycle is in progress, the SDRAM<br>enters power-down mode. To ensure that SDRAM data remains valid, the<br>self-refresh command is executed. To exit this mode and return to normal<br>oepration, drive CKE high.                                                |  |

|                |      | These signals should have an external pull-down resistor of 33 K $\!\Omega$ .                                                                                                                                                                                                                          |  |

| SDCLK[3:0]     | 0    | <b>SDRAM Clocks.</b> SDRAM uses these clocks to sample all control, address, and data lines. To ensure that the Suspend mode functions correctly, SDCLK3 and SDCLK1 should be used with $\overline{CS1}$ . SDCLK2 and SDCLK0 should be used together with $\overline{CS0}$ .                           |  |

| SDCLK_IN       | I    | <b>SDRAM Clock Input.</b> The SC2200 samples the memory read data on this clock. Works in conjunction with the SDCLK_OUT signal.                                                                                                                                                                       |  |

| SDCLK_OUT      | 0    | <b>SDRAM Clock Output.</b> This output is routed back to SDCLK_IN. The board designer should vary the length of the board trace to control skew between SDCLK_IN and SDCLK.                                                                                                                            |  |

## 1.1.5 CRT/TFT Interface

| Name                | Туре        | Description                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DDC_SCL             | 0           | <b>DDC Serial Clock.</b> This is the serial clock for the VESA Display Data<br>Channel interface. It is used for monitor communications. The DDC2B<br>standard is supported by this interface.                                                                                                                                                                                                    |  |

| DDC_SDA             | I/O         | <b>DDC Serial Data.</b> This is the bidirectional serial data signal for the VESA Display Data Channel interface. It is used for monitor communications. The DDC2B standard is supported by this interface.                                                                                                                                                                                       |  |

| HSYNC               | 0           | Horizontal Sync                                                                                                                                                                                                                                                                                                                                                                                   |  |

| VSYNC               | 0           | Vertical Sync                                                                                                                                                                                                                                                                                                                                                                                     |  |

| VREF                | I/O         | <b>Voltage Reference.</b> Reference voltage for CRT PLL and DAC. This pin reflects the internal voltage reference. A 0.1 $\mu$ F capacitor connected from this signal to AV <sub>SSCRT</sub> may be used to reduce noise. If the capacitor is used, it should be verified that the signal does not oscillate. If an external voltage reference is used, this input is tied to a 1.235V reference. |  |

| SETRES              | I           | Set Resistor. This pin sets the current level for the RED/GREEN/BLUE analog outputs. Typically, a 464 $\Omega$ , 1% resistor is connected between this pin and AV_SS.                                                                                                                                                                                                                             |  |

| On-chip RAMDAC      |             |                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| RED, GREEN,<br>BLUE | 0           | Analog Red, Green and Blue                                                                                                                                                                                                                                                                                                                                                                        |  |

| TFT (External DAC   | C) Interfac | e                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| TFTDCK              | 0           | TFT Clock. Clock to external CRT DACs or TFT.                                                                                                                                                                                                                                                                                                                                                     |  |

| TFTDE               | 0           | TFT Data Enable. Can be used as blank signal to external CRT DACs.                                                                                                                                                                                                                                                                                                                                |  |

| FP_VDD_ON           | 0           | <b>TFT Power Control.</b> Used to enable power to the Flat Panel display, with power sequence timing.                                                                                                                                                                                                                                                                                             |  |

| TFTD[17:0]          | 0           | Digital RGB Data to TFT                                                                                                                                                                                                                                                                                                                                                                           |  |

|                     |             | TFTD[5:0] are connected to the Blue TFT inputs.<br>TFTD[11:6 are connected to the Green TFT inputs.<br>TFTD[17:12] are connected to the Red TFT inputs.                                                                                                                                                                                                                                           |  |

| TFT_PRSNT           | I           | <b>TFT Present.</b> A strap used to select Multiplexing of TFT signals at power-<br>up. Enables using TFT instead of Parallel Port, ACB1, and GPIO17.                                                                                                                                                                                                                                             |  |

|                     |             | During system reset, an internal pull-down resistor of 100 K $\Omega$ exists on this pin. If needed, an external pull-up resistor of 15 K $\Omega$ should be placed.                                                                                                                                                                                                                              |  |

## 1.1.6 ACCESS.bus Interface

| Name | Туре | Description                                                                                      |  |

|------|------|--------------------------------------------------------------------------------------------------|--|

| AB1C | I/O  | ACCESS.bus 1 Serial Clock. This is the serial clock for the interface.                           |  |

| AB1D | I/O  | <b>ACCESS.bus 1 Serial Data.</b> This is the bidirectional serial data signal for the interface. |  |

| AB2C | I/O  | ACCESS.bus 2 Serial Clock. This is the serial clock for the interface.                           |  |

| AB2D | I/O  | <b>ACCESS.bus 2 Serial Data.</b> This is the bidirectional serial data signal for the interface. |  |

## 1.1.7 PCI Bus Interface

| Name                      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCICLK                    | I    | <b>PCI Clock.</b> PCICLK provides timing for all transactions on the PCI Bus. All other PCI signals are sampled on the rising edge of PCICLK, and all timing parameters are defined with respect to this edge.                                                                                                                                                                                                                                                                                         |  |

| PCICLK0,<br>PCICLK1       | 0    | <b>PCI Clock Output.</b> PCICLK0 and PCICLK1 provide clock drives for the system at 33 MHz. These clocks are asynchronous to PCI signals. There is low skew between all outputs. One of these clock signals should be connected to PCICLK input. All PCI clock users in the system (including PCICLK) should receive the clock with as low a skew as possible.                                                                                                                                         |  |

| AD[31:0]                  | I/O  | <b>Multiplexed Address and Data.</b> A bus transaction consists of an address phase in the cycle in which FRAME is asserted followed by one or more data phases. During the address phase, AD[31:0] contain a physical 32-bit address. For I/O, this is a byte address. For configuration and memory, it is a DWORD address. During data phases, AD[7:0] contain the least significant byte (LSB) and AD[31:24] contain the most significant byte (MSB).                                               |  |

| C/BE[3:0]                 | I/O  | <b>Multiplexed Command and Byte Enables.</b> During the address phase of a transaction when FRAME is active, $\overline{C/BE[3:0]}$ define the bus command. During the data phase, $\overline{C/BE[3:0]}$ are used as byte enables. The byte enables are valid for the entire data phase and determine which byte lanes carry meaningful data. $\overline{C/BE0}$ applies to byte 0 (LSB) and $\overline{C/BE3}$ applies to byte 3 (MSB).                                                              |  |

| ÎNTĂ, ÎNTB,<br>ÎNTC, ÎNTD | I    | <b>PCI Interrupt.</b> The SC2200 provides inputs for the optional "level-sensi-<br>tive" PCI interrupts (also known in industry terms as PIRQx). These inter-<br>rupts can be mapped to IRQs of the internal 8259 interrupt controllers<br>using PCI Interrupt Steering Registers 1 and 2 (F0 Index 5Ch and 5Dh).                                                                                                                                                                                      |  |

| PAR                       | I/O  | <b>Parity.</b> Parity generation is required by all PCI agents. The master drives PAR for address- and write-data phases. The target drives PAR for read-data phases. Parity is even across AD[31:0] and C/BE[3:0].                                                                                                                                                                                                                                                                                    |  |

|                           |      | For address phases, PAR is stable and valid one PCI clock after the address phase. It has the same timing as AD[31:0] but is delayed by one PCI clock.                                                                                                                                                                                                                                                                                                                                                 |  |

|                           |      | For data phases, PAR is stable and valid one PCI clock after either IRDY is asserted on a write transaction or after TRDY is asserted on a read transaction.                                                                                                                                                                                                                                                                                                                                           |  |

|                           |      | Once PAR is valid, it remains valid until one PCI clock after the completion of the data phase. (Also see PERR.)                                                                                                                                                                                                                                                                                                                                                                                       |  |

| FRAME                     | I/O  | <b>Frame Cycle.</b> Frame is driven by the current master to indicate the beginning and duration of an access. FRAME is asserted to indicate the beginning of a bus transaction. While FRAME is asserted, data transfers continue. FRAME is deasserted when the transaction is in the final data phase.                                                                                                                                                                                                |  |

|                           |      | This pin is internally connected to a pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| ÎRDY                      | I/O  | <b>Initiator Ready.</b> IRDY is asserted to indicate that the bus master is able to complete the current data phase of the transaction. IRDY is used in conjunction with TRDY. A data phase is completed on any PCI clock in which both IRDY and TRDY are sampled as asserted. During a write, IRDY indicates that valid data is present on AD[31:0]. During a read, it indicates that the master is prepared to accept data. Wait cycles are inserted until both IRDY and TRDY are asserted together. |  |

|                           |      | This pin is internally connected to a pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TRDY   | I/O  | Target Ready.TRDYis asserted to indicate that the target agent is able to<br>complete the current data phase of the transaction.TRDYis used in con-<br>junction with IRDY. A data phase is complete on any PCI clock in which<br>both TRDY and IRDY are sampled as asserted. During a read, TRDY indi-<br>cates that valid data is present on AD[31:0]. During a write, it indicates<br>that the target is prepared to accept data. Wait cycles are inserted until<br>both IRDY and TRDY are asserted together.                                                                                |  |

|        |      | This pin is internally connected to a pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| STOP   | I/O  | <b>Target Stop.</b> STOP is asserted to indicate that the current target is requesting that the master stop the current transaction. This signal is used with DEVSEL to indicate retry, disconnect, or target abort. If STOP is sampled active by the master, FRAME is deasserted and the cycle is stopped within three PCI clock cycles. As an input, STOP can be asserted in the following cases:                                                                                                                                                                                            |  |

|        |      | <ol> <li>If a PCI master tries to access memory that has been locked by<br/>another master. This condition is detected if FRAME and LOCK are<br/>asserted during an address phase.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|        |      | 2) If the PCI write buffers are full or if a previously buffered cycle has not completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|        |      | <ol> <li>On read cycles that cross cache line boundaries. This is conditional<br/>based upon the programming of bit 1 in PCI Control Function 2 Regis-<br/>ter.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|        |      | This pin is internally connected to a pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| LOCK   | I/O  | <b>Lock Operation.</b> LOCK indicates an atomic operation that may require multiple transactions to complete. When LOCK is asserted, nonexclusive transactions may proceed to an address that is not currently locked (at least 16 bytes must be locked). A grant to start a transaction on PCI does not guarantee control of LOCK. Control of LOCK is obtained under its own protocol in conjunction with GNT.                                                                                                                                                                                |  |

|        |      | It is possible for different agents to use PCI while a single master retains ownership of $\overline{LOCK}$ . The arbiter can implement a complete system lock. In this mode, if $\overline{LOCK}$ is active, no other master can gain access to the system until the $\overline{LOCK}$ is deasserted.                                                                                                                                                                                                                                                                                         |  |

|        |      | This signal is internally connected to a pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| DEVSEL | 1/0  | <b>Device Select.</b> DEVSEL indicates that the driving device has decoded its address as the target of the current access. As an input, DEVSEL indicates whether any device on the bus has been selected. DEVSEL is also driven by any agent that has the ability to accept cycles on a subtractive decode basis. As a master, if no DEVSEL is detected within and up to the subtractive decode clock, a master abort cycle will be initiated (except for special cycles which do not expect a DEVSEL returned).                                                                              |  |

|        |      | This signal is internally connected to a pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| PERR   | I/O  | <b>Parity Error.</b> PERR is used for reporting data parity errors during all PCI transactions except a Special Cycle. The PERR line is driven two PCI clocks after the data in which the error was detected. This is one PCI clock after the PAR that is attached to the data. The minimum duration of PERR is one PCI clock for each data phase in which a data parity error is detected. PERR must be driven high for one PCI clock before being placed in TRISTATE. A target asserts PERR on write cycles if it has claimed the cycle with DEVSEL. The master asserts PERR on read cycles. |  |

| Name     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SERR     | I/O  | <b>System Error.</b> SERR can be asserted by any agent for reporting errors other than PCI parity, so that the PCI central agent notifies the processor. When the Parity Enable bit is set in the Memory Controller Configuration register, SERR is asserted upon detection of a parity error in read operations from DRAM.                                                                                                                          |  |

| REQ[1:0] | I    | <b>Request Lines.</b> REQ[1:0] indicate to the arbiter that an agent requires the bus. Each master has its own REQ line. REQ priorities are based on the specified arbitration scheme.<br>Each of these pins is internally connected to a pull-up resistor.                                                                                                                                                                                          |  |

| GNT[1:0] | 0    | <b>Grant Lines.</b> $\overline{\text{GNT}[1:0]}$ indicate to the requesting master that it has been granted access to the bus. Each master has its own $\overline{\text{GNT}}$ line. $\overline{\text{GNT}}$ can be retracted at any time a higher $\overline{\text{REQ}}$ is received or if the master does not begin a cycle within a minimum period of time (16 PCI clocks). These signals must be connected to a 15 K $\Omega$ pull-up resistor. |  |

## 1.1.8 Sub-ISA Interface

| Name      | Туре | Description                                                                     |  |

|-----------|------|---------------------------------------------------------------------------------|--|

| A[23:0]   | 0    | Address Lines                                                                   |  |

| D[15:0]   | I/O  | Data Bus                                                                        |  |

| BHE       | 0    | Byte High Enable. With A0, defines byte accessed for 16-bit wide bus cycles.    |  |

| IOCS[1:0] | 0    | I/O Chip Selects                                                                |  |

| ROMCS     | 0    | ROM or Flash ROM Chip Select                                                    |  |

| DOCCS     | 0    | DiskOnChip or NAND Flash Chip Select                                            |  |

| TRDE      | 0    | Transceiver Data Enable Control. Active low for Sub-ISA data transfers.         |  |

| RD        | 0    | Memory or I/O Read. Active on any read cycle.                                   |  |

| WR        | 0    | Memory or I/O Write. Active on any write cycle.                                 |  |

| IOR       | 0    | I/O Read. Active on any I/O read cycle.                                         |  |

| ĪOW       | 0    | I/O Write. Active on any I/O write cycle.                                       |  |

| DOCR      | 0    | DiskOnChip or NAND Flash Read. Active on any memory read cycle to DiskOnChip.   |  |

| DOCW      | 0    | DiskOnChip or NAND Flash Write. Active on any memory write cycle to DiskOnChip. |  |

| IRQ9      | 1    | Interrupt 9 Request Input. Active High.                                         |  |

| IOCHRDY   | I    | I/O Channel Ready                                                               |  |

## 1.1.9 Low Pin Count (LPC) Bus Interface

| Name     | Туре | Description                                                                                                                                  |  |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| LAD[3:0] | I/O  | LPC Address-Data. Multiplexed command, address, bidirectional data, and cycle status.                                                        |  |

| LDRQ     | I    | LPC DMA Request. Encoded DMA request for LPC I/F.                                                                                            |  |

| LFRAME   | 0    | <b>LPC Frame.</b> A low pulse indicates the beginning of a new LPC cycle or termination of a broken cycle.                                   |  |

| LPCPD    | 0    | <b>LPC Power-Down.</b> Signals the LPC device to prepare for power shut-<br>down on the LPC interface.                                       |  |

| SERIRQ   | I/O  | <b>Serial IRQ.</b> The interrupt requests are serialized over a single pin, where each IRQ level is delivered during a designated time slot. |  |

### 1.1.10 IDE Interface

| Name                      | Туре | Description                                                                                                                                                                                                      |  |

|---------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IDE_RST                   | 0    | <b>IDE Reset.</b> This signal resets all the devices that are attached to the IDE interface.                                                                                                                     |  |

| IDE_ADDR[2:0]             | 0    | <b>IDE Address Bits.</b> These address bits are used to access a register or data port in a device on the IDE bus.                                                                                               |  |

| IDE_DATA[15:0]            | I/O  | IDE Data Lines. IDE_DATA[15:0] transfers data to/from the IDE devices.                                                                                                                                           |  |

| IDE_IOR0,<br>IDE_IOR1     | 0    | <b>IDE I/O Read Channels 0 and 1.</b> IDE_IOR0 is the read signal for Channel 0 and IDE_IOR1 is the read signal for Channel 1. Each signal is asserted at read accesses to the corresponding IDE port addresses. |  |

| IDE_IOW0,<br>IDE_IOW1     | 0    | <b>IDE I/O Write Channels 0 and 1.</b> IDE_IOW0 is the write signal for Channel 0. IDE_IOW1 is the write signal for Channel 1. Each signal is asserted at write accesses to corresponding IDE port addresses.    |  |

| IDE_CS0,<br>IDE_CS1       | 0    | <b>IDE Chip Selects 0 and 1.</b> These signals are used to select the command block registers in an IDE device.                                                                                                  |  |

| IDE_IORDY0,<br>IDE_IORDY1 | I    | <b>I/O Ready Channels 0 and 1.</b> When deasserted, these signals extend the transfer cycle of any host register access if the required device is not ready to respond to the data transfer request.             |  |

| IDE_DREQ0,<br>IDE_DREQ1   | Ι    | <b>DMA Request Channels 0 and 1.</b> The IDE_DREQ signals are used to request a DMA transfer from the SC2200. The direction of transfer is determined by the IDE_IOR/IOW signals.                                |  |

| IDE_DACK0,<br>IDE_DACK1   | 0    | <b>DMA Acknowledge Channels 0 and 1.</b> The IDE_DACK signals acknowledge the DREQ request to initiate DMA transfers.                                                                                            |  |

| IRQ14, IRQ15              | I    | <b>Interrupt Request Channels 0 and 1.</b> These input signals are edge-sen-<br>sitive interrupts that indicate when the IDE device is requesting a CPU<br>interrupt service.                                    |  |

## 1.1.11 Universal Serial Bus (USB)

| Name     | Туре | Description                                                                                          |  |

|----------|------|------------------------------------------------------------------------------------------------------|--|

| POWER_EN | 0    | <b>Power Enable.</b> This pin enables the power to a self-powered USB hub.                           |  |

| OVER_CUR | I    | <b>Overcurrent.</b> This pin indicates that the USB hub has detected an over-<br>current on the USB. |  |

| D+_PORT1 | I/O  | <b>USB Port 1 Data Positive.</b> This pin is the Universal Serial Bus Data Positive for port 1.      |  |

| DPORT1   | I/O  | <b>USB Port 1 Data Negative.</b> This pin is the Universal Serial Bus Data Negative for port 1.      |  |

| D+_PORT2 | I/O  | <b>USB Port 2 Data Positive.</b> This pin is the Universal Serial Bus Data Positive for port 2.      |  |

| DPORT2   | I/O  | <b>USB Port 2 Data Negative.</b> This pin is the Universal Serial Bus Data Negative for port 2.      |  |

| D+_PORT3 | I/O  | <b>USB Port 3 Data Positive.</b> This pin is the Universal Serial Bus Data Positive for port 3.      |  |

| DPORT3   | I/O  | <b>USB Port 3 Data Negative.</b> This pin is the Universal Serial Bus Data Negative for port 3.      |  |

## 1.1.12 Serial Ports (UARTs)

| Name                             | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|----------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SIN1<br>SIN2<br>SIN3             | I    | Serial Input. Receive composite serial data from the communications link (peripheral device, modem or other data transfer device).                                                                                                                                                                                                                                                                                                                          |  |

| SOUT1<br>SOUT2<br>SOUT3          | 0    | <b>Serial Output.</b> Send composite serial data to the communications link (peripheral device, modem or other data transfer device). These signals are set active high after a system reset.                                                                                                                                                                                                                                                               |  |

| RTS2                             | 0    | <b>Request to Send.</b> When low, indicate to the modem or other data trans-<br>fer device that the corresponding UART is ready to exchange data. A sys-<br>tem reset sets these signals to inactive high, and loopback operation<br>holds them inactive.                                                                                                                                                                                                   |  |

| CTS2                             | I    | Clear to Send. When low, indicate that the modem or other data transfer device is ready to exchange data.                                                                                                                                                                                                                                                                                                                                                   |  |

| DTR1/<br>BOUT1<br>DTR2/<br>BOUT2 | 0    | Data Terminal Ready (DTRx). When low, indicate to the modem or other<br>data transfer device that the UART is ready to establish a communications<br>link. After a system reset, these pins provide the DTR function and set<br>these signals to inactive high. Loopback operation drives them inactive.Baud Output (BOUTx). Provides the associated serial channel baud rate<br>generator output signal if test mode is selected, i.e., bit 7 of the EXCR1 |  |

|                                  |      | Register is set.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| RI2                              | 1    | <b>Ring Indicator.</b> When low, indicates to the modem that a telephone ring signal has been received by the modem. They are monitored during power-off for wake-up event detection.                                                                                                                                                                                                                                                                       |  |

| DCD2                             | I    | <b>Data Carrier Detected.</b> When low, indicates that the data transfer device, e.g., modem, is ready to establish a communications link.                                                                                                                                                                                                                                                                                                                  |  |

| DSR2                             | I    | <b>Data SetReady.</b> When low, indicates that the data transfer device, e.g., modem, is ready to establish a communications link.                                                                                                                                                                                                                                                                                                                          |  |

## 1.1.13 Parallel Port

| Signal     | I/O | Description                                                                                                                                                                                                                                                                              | MUX |

|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| ĀCK        | I   | <b>Acknowledge.</b> Pulsed low by the printer to indicate that it has received data from the Parallel Port.                                                                                                                                                                              |     |

| AFD/DSTRB  | 0   | <b>AFD - Automatic Feed.</b> When low, instructs the printer to automatically feed a line after printing each line. This pin is in TRI-STATE after a 0 is loaded into the corresponding control register bit. An external 4.7 K $\Omega$ pullup resistor should be attached to this pin. |     |

|            |     | <b>DSTRB - Data Strobe (EPP).</b> Active low, used in EPP mode to denote a data cycle. When the cycle is aborted, DSTRB becomes inactive (high).                                                                                                                                         |     |

| BUSY/WAIT  | I   | BUSY. Set high by the printer when it cannot accept another character.                                                                                                                                                                                                                   |     |

|            |     | <b>WAIT.</b> In EPP mode, the Parallel Port device uses this active low signal to extend its access cycle.                                                                                                                                                                               |     |

| ERR        | I   | Error. Set active low by the printer when it detects an error.                                                                                                                                                                                                                           |     |

| INIT       | 0   | <b>Initialize.</b> When low, initializes the printer. This signal is in TRI-STATE after a 1 is loaded into the corresponding control register bit. Use an external $4.7 \text{ K}\Omega$ pull-up resistor.                                                                               |     |

| PD[7:0]    | I/O | <b>Parallel Port Data.</b> Transfer data to and from the peripheral data bus and the appropriate Parallel Port data register. These signals have a high current drive capability.                                                                                                        |     |

| PE         | I   | <b>Paper End.</b> Set high by the printer when it is out of paper. This pin has an internal weak pull-up or pull-down resistor.                                                                                                                                                          |     |

| SLCT       | I   | Select. Set active high by the printer when the printer is selected.                                                                                                                                                                                                                     |     |

| SLIN/ASTRB | 0   | <b>SLIN</b> - Select Input. When low, selects the printer. This signal is in TRI-STATE after a 0 is loaded into the corresponding control register bit. Uses an external 4.7 K $\Omega$ pull-up resistor.                                                                                |     |

|            |     | <b>ASTRB</b> - Address Strobe (EPP). Active low, used in EPP mode to denote an address or data cycle. When the cycle is aborted, ASTRB becomes inactive (high).                                                                                                                          |     |

| STB/WRITE  | 0   | <b>STB</b> - Data Strobe. When low, Indicates to the printer that valid data is available at the printer port. This signal is in TRI-STATE after a 0 is loaded into the corresponding control register bit. An external 4.7 K $\Omega$ pull-up resistor should be employed.              |     |

|            |     | <b>WRITE</b> - Write Strobe. Active low, used in EPP mode to denote an address or data cycle. When the cycle is aborted, WRITE becomes inactive (high).                                                                                                                                  |     |

## 1.1.14 Fast Infrared (IR) Port

| Name  | Туре | Description                                                                                                                                                                                                                                          |  |

|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IRRX1 | I    | <b>IR Receive.</b> Primary input to receive serial data from the IR transceiver.<br>Monitored during power-off for wake-up event detection.                                                                                                          |  |

| IRRX2 | I    | <b>IRRX2 - IR Receive 2.</b> Auxiliary IR receiver input to support a second transceiver. This input signal can be used when GPIO38 is selected using PMR[14], and when AUX_IRRX bit in register IRCR2 of the IR module in internal SuperI/O is set. |  |

| IRTX  | 0    | IR Transmit. IR serial output data.                                                                                                                                                                                                                  |  |

## 1.1.15 AC97 Audio Interface

| Name      | Туре | Description                                                                                                                 |  |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------|--|

| BIT_CLK   | I    | Audio Bit Clock. The serial bit clock from the codec.                                                                       |  |

| SDATA_OUT | 0    | Serial Data Output. This output transmits audio serial data to the codec.                                                   |  |

| SDATA_IN  | I    | Serial Data Input. This input receives serial data from the primary codec.                                                  |  |

| SDATA_IN2 | I    | Serial Data Input 2. This input receives serial data from the secondary codec. This pin has wake-up capability.             |  |

| SYNC      | 0    | Serial Bus Synchronization. This bit is asserted to synchronize the transfer of data between the SC2200 and the AC97 codec. |  |

| AC97_CLK  | 0    | Codec Clock. It is twice the frequency of the Audio Bit Clock.                                                              |  |

| AC97_RST  | 0    | Codec Reset                                                                                                                 |  |

| PC_BEEP   | 0    | PC Beep. Legacy PC/AT speaker output.                                                                                       |  |

## 1.1.16 Power Management

| Name        | Туре | Description                                                                                                                                                                                                                                                                              |  |

|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLK32       | 0    | 32.768 KHz Output Clock                                                                                                                                                                                                                                                                  |  |

| GPWIO[0:2]  | I/O  | General Purpose Wake-up I/O Signals                                                                                                                                                                                                                                                      |  |

| LED         | 0    | <b>LED Control.</b> Drives an externally connected LED (on, off or a 1 Hz blink). Sleeping / Working indicator. This signal is an open-drain output.                                                                                                                                     |  |

| ONCTL       | 0    | <b>On / Off Control.</b> This signal indicates to the main power supply that power should be turned on. This signal is an open-drain output.                                                                                                                                             |  |

| PWRBTN      | I    | <b>Power Button.</b> Input used by the power management logic to monitor external system events, most typically a system on/off button or switch. The pin has an internal pull-up of $100 \text{ K}\Omega$ , a schmitt-trigger input buffer and debounce protection of at least 16 msec. |  |

| PWRCNT[1:2] | 0    | <b>Suspend Power Plane Control 1 and 2.</b> Control signal asserted during power management suspend states. These signals are open-drain outputs.                                                                                                                                        |  |

| THRM        | I    | <b>Thermal Event.</b> Active low signal generated by external hardware indicating that the system temperature is too high.                                                                                                                                                               |  |

## 1.1.17 General Purpose (GPIO) Ports

| Name                     | Туре | Description                                                                                                                                                         |  |

|--------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GPIO[00:01], and [06:20] | I/O  | <b>GPIO Port 0</b> . Each signal is configured independently as input or I/O, with or without static pull-up, and with either open-drain or totem-pole output type. |  |

|                          |      | A debouncer and an interrupt can be enabled or masked for each of sig-<br>nals GPIO[00:01] and [06:15] independently.                                               |  |

| GPIO[32:41]              | I/O  | GPIO Port 1. Same as Port 0.                                                                                                                                        |  |

|                          |      | A debouncer and an interrupt can be enabled or masked for each of sig-<br>nals GPIO[32:41] independently.                                                           |  |

### 1.1.18 JTAG

| Name | Туре | Description                                                                                                                                                                                                                                  |  |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ТСК  | I    | Test Clock                                                                                                                                                                                                                                   |  |

| TDI  | I    | Test Data Input                                                                                                                                                                                                                              |  |

| TDO  | 0    | Test Data Output                                                                                                                                                                                                                             |  |

| TMS  | I    | Test Mode Select                                                                                                                                                                                                                             |  |

| TRST | I    | <ul> <li>Test Reset. This pin has an internal weak pull-up resistor.</li> <li>For normal JTAG operation, this signal should be active at power-up.</li> <li>If the JTAG interface is not being used, this signal can be tied low.</li> </ul> |  |

### 1.1.19 Test and Measurement

| Name     | Туре | Description                                     |  |

|----------|------|-------------------------------------------------|--|

| FMUL3B   | I/O  | For internal test only.                         |  |

| PLL2B    | I/O  | PLL2 bypass input. Graphics dot clock generator |  |

| GXCLK    | 0    | For internal test only.                         |  |

| PLL5B    | I/O  | PLL5 bypass input. For internal test only.      |  |

| GTEST    | I    | For internal test only.                         |  |

| TDP, TDN | I/O  | Thermal Diode. For test only.                   |  |

### 1.1.20 Power and Ground

Note: All power sources must be connected to the SC2200, even if the function is not used.

| Name                 | Туре | Description                                                                                                                                                                           |

|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AV <sub>SSPLL2</sub> | GND  | Analog PLL2 Ground Connection                                                                                                                                                         |

| AV <sub>SSPLL3</sub> | GND  | Analog PLL3 Ground Connection                                                                                                                                                         |

| AV <sub>CCUSB</sub>  | PWR  | 3.3V Analog USB Power Connection. Low noise power                                                                                                                                     |

| AV <sub>SSUSB</sub>  | GND  | Analog USB Ground Connection                                                                                                                                                          |

| AV <sub>CCCRT</sub>  | PWR  | 3.3V Analog CRT DAC Power Connection. Low noise power                                                                                                                                 |

| AV <sub>SSCRT</sub>  | GND  | Analog CRT DAC Ground Connection. Return current from DACs.                                                                                                                           |

| AV <sub>CC</sub>     | PWR  | 3.3V Analog Power Connection.                                                                                                                                                         |