# Transmeta's Second Generation Efficeon Microprocessor and Technology Roadmap

David R. Ditzel

Co-Founder, Vice-Chairman and CTO

Transmeta Corporation

October 2004

Fall Processor Forum

# Agenda

- Efficeon Processor Architecture

- Efficeon Generation 1 Implementation

- Efficeon Generation 2 Implementation

- Technology Roadmap

# **Transmeta Technology**

#### Efficeon is the sum of

**x86 Code Morphing Software**

- Provides Compatibility

- Translates the 1's and 0's of x86 instructions to equivalent 1's and 0's for a simple VLIW processor

- Learns and improves with time

**VLIW Hardware**

- Very Long Instruction Word processor

- Simple and fast

- Fewer transistors

Low Power

x86 PC Compatibility

High Performance

## **Efficeon Interfaces**

Transmeta

efficēon™

HyperTransport

#### AGP- 4X Graphics

- Supports 1X, 2X or 4X speeds

- AGP 2.0 compliant

- Full GART support

**Graphics**

AGP - 4x

**LPC** Low Pin Count Bus (Rev 1.0) Used for BIOS/CMS FLASH

Wireless, etc

**PCI HyperTransport** Southbridge

**FLASH**

#### DDR-400 Memory

- High performance 64-bit DDR

- Up to 200MHz/400 Megaxfers/sec

- Supports up to 4GB of memory

- Optional ECC support

**DDR - 400**

#### HyperTransport™ IO Bus

- Point to point LVDS Interface

- 8-bit interface each direction

- 200 or 400 MHz speeds

- 1.6 Gigabytes/s aggregate

- 12 times the bandwidth of PCI

# **High Instruction Level Parallelism**

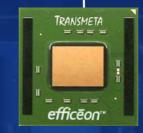

Each clock, Efficeon can issue from one to eight 32-bit instruction "atoms"...

... to any of the above eleven logical execution units.

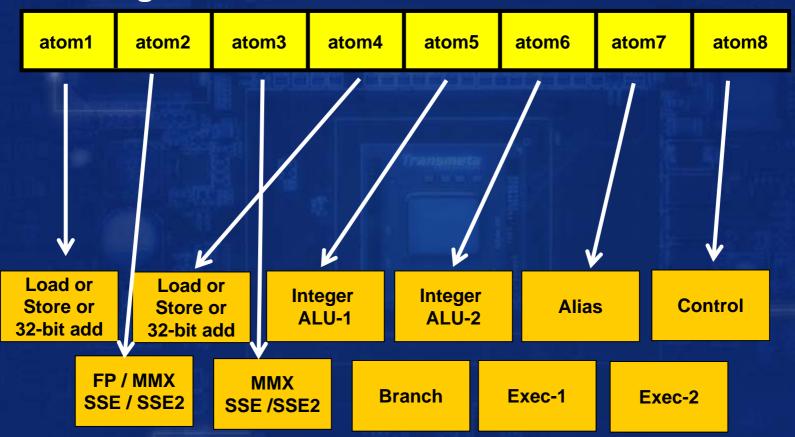

# **Transmeta Development Strategy**

# Efficeon

# **Generation 1**

# **Efficeon Roadmap**

TDP= Maximum Thermal Power

Efficeon Generation-1

TSMC 130 nm

TM8600 Standard Package

TM8620 Small Package

1 GHz 7 Watt TDP

Q4 2003

2004

2005

## First Efficeon Notebook: Jan 04

#### **Sharp Actius MM20**

2 pounds (990 grams)

1.0 GHz Efficeon Processor

0.62 inches at thinnest point

February 16, 2004:

"Efficeon is as well armed as the Pentium M with strong performance and cost efficiency, and has the potential to become part of the mainstream in the mobile notebook computer market."

#### **April 2004:**

"The MM20 has got the chops to go up against any Centrino machine running the low-voltage version of that processor."

### Efficeon in HP Blade PC: April 04

280 Efficeon Blades per 42U rack 20 Blades per 3U modular enclosure

# Efficeon

# **Generation 2**

# **Generation 2 Goals**

#### In less than 1 year:

- Double performance from 1 GHz to ~2 GHz

- Move into higher volume 12-25 Watt segment

- Cut power in half for 1 GHz operation

- Remain pin compatible with generation 1 parts

- Provide easily recognizable feature differentiation

- Virus Protection

- Advanced Video Processing

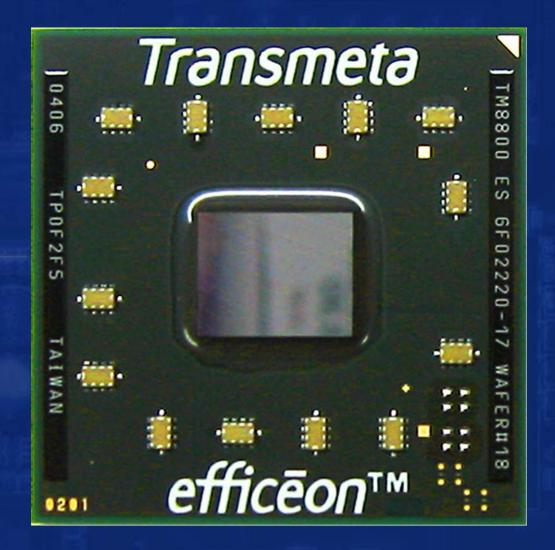

The new 90nm second generation Efficeon Processor from Transmeta

# **Second Generation Efficeon**

#### TM8800

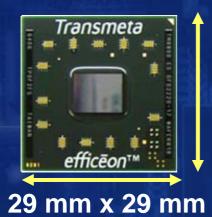

Same Die, two different packaging options

#### **TM8820**

- 90 nm CMOS Technology

- Pin compatible with TM8600 and TM8620 130nm parts

- Product goals:

- 1.0 1.1 GHz

- ~3 Watts max TDP

- 1.4 1.6 GHz

- ~7 watts max TDP

- 1.6 1.8 GHz ~12 watts max TDP

- 1.8 2.0+ GHz < 25 watts max TDP

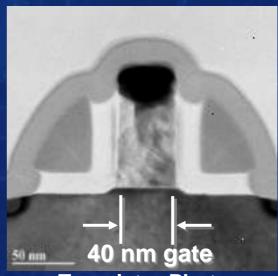

# **Technology Choice: Fujitsu 90nm**

- Fujitsu provided the best 90nm technology choice for speed

- Up to 10 layers interconnect (8 used in Efficeon)

- Low-K dielectric

- Industry leading 40nm transistor gate length

- Small ~1u<sup>2</sup> SRAM cell

**Transistor Photo**Fall Processor Forum October 5, 2004

## **Anti-Virus Protection**

- Efficeon 2 is the first low-power mobile processor to provide support for Antivirus protection

- New x86 memory management extension to protect against viruses exploiting buffer overflows – a common entry point for viruses and worms

- Allows Efficeon processor to mark memory locations as non-executable unless it explicitly contains executable code

- Works in conjunction with Microsoft's Data Execution Protection (DEP) feature in Windows XP Service Pack 2 (SP2)

# **New Multimedia "SSE-3" Instructions**

#### Graphics support:

haddpd, haddps, hsubpd, hsubps: Horizontal add/subtract

#### Complex arithmetic support:

- movddup, movshdup, movsldup: loads and duplicates data

- addsubpd, addsubps: adds and subtracts simultaneously

#### Video encoding support for MPEG-4

Iddqu: loads unaligned 128-bit data

#### General

fisttp: x87 floating point to integer conversion

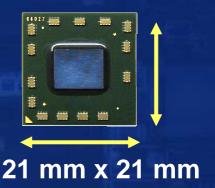

# **Space Efficiency Comparison**

±

Transmeta TM8820 CPU + Northbridge 21mm x 21mm

Intel Pentium-M

CPU

35mm x 35mm

Intel 855PM MCH

Northbridge

37.5mm x 37.5mm

TM8820 is 36% the size of Pentium-M alone

TM8820 is 17% the size of Pentium M + Northbridge

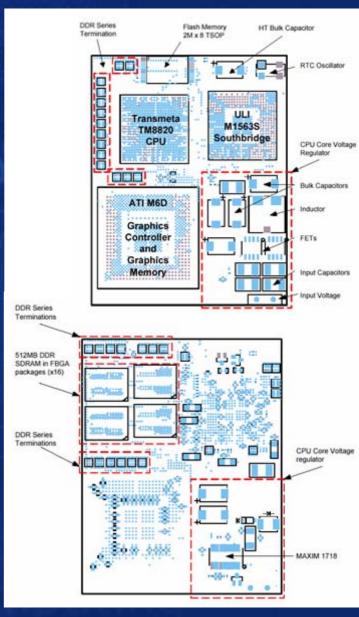

# **Small Form Factor Design Example**

- Entire core PC logic on a tiny board

- TM8620 CPU/NB(21mm x 21mm) and

- ULI1563S Southbridge (23mm x 23mm)

- Enables compact form factors

- Total Board Size 78mm x 62mm similar to PCMCIA card

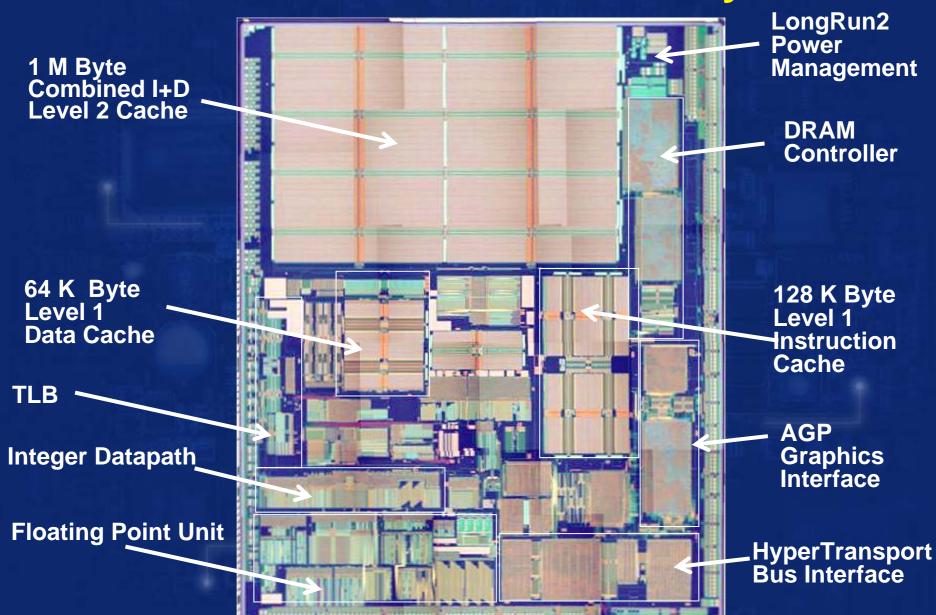

# **Efficeon 2 Die Photo and Layout**

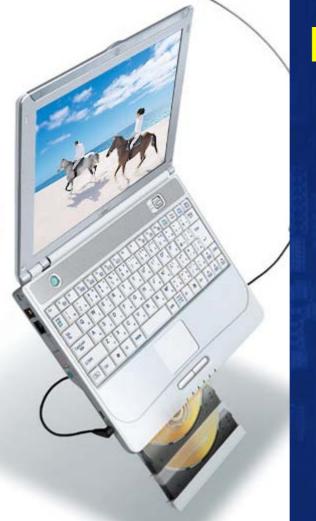

# First Efficeon-2 Notebook Sharp PC-MP70G

- Launched in Japan Sept 9<sup>th</sup>, 2004

- Uses 1.6 GHz Efficeon TM8800 Processor

- 2.8 pounds (1.26 kg)

- 10.4 inch LCD screen

- 2 spindle (Hard Disk and DVD)

Nearest competitive systems are new SONY T-Series 3 pounds, 10.6" LCD, 2 spindle

CPU: 1.1 GHz Pentium-M model 733 and

933 MHz Celeron-M model 353

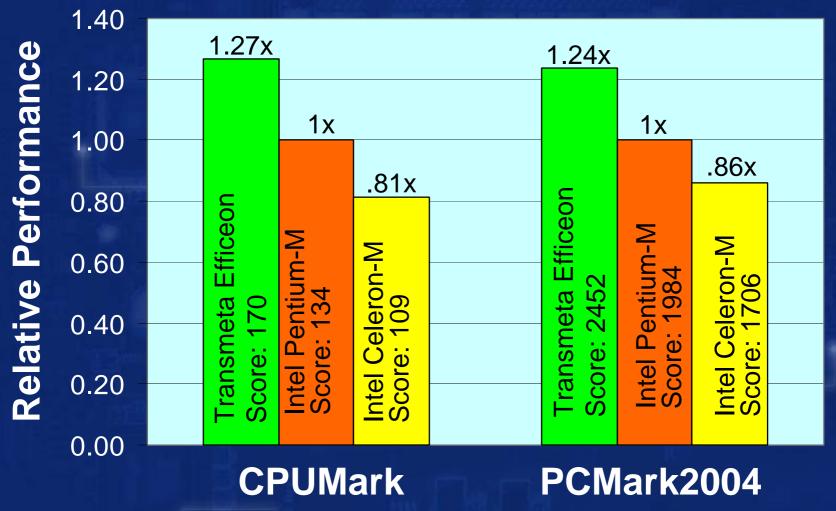

# Performance Comparison using best MHz of recent < 3 lb 10.6" notebooks

Benchmarks run at Transmeta on systems as similarly configured as possible Efficeon-2 data measured at 1.6 GHz with 512MB DDR333, 5400rpm 2.5" HDD, NV17 graphics Intel Pentium-M data measured at 1.1 GHz with 512MB DDR333, 5400rpm 2.5" HDD, i855GMCH Intel Celeron-M data estimated by measuring Celeron-M at 800 MHz (scores: 97/1517) and estimating 933 MHz score

#### First Clustered Workstation with TM8800

#### **Orion Multisystems DS-96**

- Deskside Personal Supercomputer

- 96 Efficeon TM8800 Processors

- 300 GigaFlops on DP Linpack

- Standard electrical wall outlet

| Efficeon excels at "Dense Computing"                      |           |           | ~Performance |             |

|-----------------------------------------------------------|-----------|-----------|--------------|-------------|

|                                                           | Frequency | Power     | SpecInt/Watt | SpecFP/Watt |

| Efficeon                                                  | 1.5 GHz   | 7 Watts   | 97.6         | 77.5        |

| AMD Opteron 148                                           | 2.2 GHz   | 86 Watts  | 16.3         | 17.5        |

| Intel Xeon                                                | 3.2 GHz   | 86 Watts  | 14.8         | 14.0        |

| IBM Power4                                                | 1.7 GHz   | 100 Watts | 10.8         | 16.0        |

| Intel Itanium 2                                           | 1.5 GHz   | 130 Watts | 10.2         | 16.3        |

| source: Microprocessor Report December 2003 and Transmeta |           |           |              |             |

# Technology Roadmap

# Efficeon Roadmap

Announced October 2003

Efficeon Generation-1

TSMC 130 nm

1 GHz / 7 Watt

Announced October 2004

Efficeon Generation-2

Fujitsu 90 nm

Efficeon Generation-3/4\* 90 nm / 65 nm

Product Goals

1.8 - 2.0 GHz / < 25 Watt

1.6 - 1.8 GHz / 12 Watt

1.4 - 1.6 GHz / 7 Watt

1.0 - 1.1 GHz / 3 Watt

Improved Microarchitecture

Higher Work/Clock

Fewer Gates/Clock

2x More Cache

3x Faster DRAM bus

4x Faster HT bus

2003

2004

2005

\* = Current plans, subject to change

## What's Next?

Here are a few things we're working on:

- More MHz moving up into mainstream notebooks

- Lower Power

- LongRun2 Power Management

- Virtualization

- Licensing of Transmeta Technology for SOC Cores

- 64-bit instruction extensions

- 65 nm CMOS Technology

# **Summary**

- Second generation 90 nm Efficeon-2 is a major leap forward

- Able to ship first all layer silicon, using only metal and CMS changes

- Subsequent tapeouts will improve MHz and reduce power further

- Efficeon-2 leads in performance when low power is a constraint

- Efficeon-2 leads in compact space solutions

- Efficeon-2 opens the door to higher volume platforms

- Mainstream notebooks

- Media center PC, STB's and PVR's

- Blade servers and Blade PC's

- UPC handheld devices

# Transmeta corporation