Crusoe

# TM5500/TM5800 System Design Guide

July 9, 2002

#### Crusoe™ Processor Model TM5500/TM5800 System Design Guide

Revision 1.3

Revision History:

- 1.0 July 2, 2001 first release

- 1.1 December 6, 2001 updated schematics, reorganized and added new information, misc corrections

- 1.2 June 17, 2002 changed DDR interface spec to one bank only, removed "Preliminary" mark

- 1.3 July 9, 2002 updated MAX1718 core power supply example, removed ISL6211 and FAN5250 examples

Property of:

Transmeta Corporation 3940 Freedom Circle Santa Clara, CA 95054 USA (408) 919-3000 http://www.transmeta.com

The information contained in this document is provided solely for use in connection with Transmeta products, and Transmeta reserves all rights in and to such information and the products discussed herein. This document should not be construed as transferring or granting a license to any intellectual property rights, whether express, implied, arising through estoppel or otherwise. Except as may be agreed in writing by Transmeta, all Transmeta products are provided "as is" and without a warranty of any kind, and Transmeta hereby disclaims all warranties, express or implied, relating to Transmeta's products, including, but not limited to, the implied warranties of merchantability, fitness for a particular purpose and non-infringement of third party intellectual property. Transmeta products may contain design defects or errors which may cause the products to deviate from published specifications, and Transmeta documents may contain inaccurate information. Transmeta makes no representations or warranties with respect to the accuracy or completeness of the information contained in this document, and Transmeta reserves the right to change product descriptions and product specifications at any time, without notice.

Transmeta products have not been designed, tested, or manufactured for use in any application where failure, malfunction, or inaccuracy carries a risk of death, bodily injury, or damage to tangible property, including, but not limited to, use in factory control systems, medical devices or facilities, nuclear facilities, aircraft, watercraft or automobile navigation or communication, emergency systems, or other applications with a similar degree of potential hazard.

Transmeta reserves the right to discontinue any product or product document at any time without notice, or to change any feature or function of any Transmeta product or product document at any time without notice.

Trademarks: Transmeta, the Transmeta logo, Crusoe, the Crusoe logo, Code Morphing, LongRun, and combinations thereof are trademarks of Transmeta Corporation in the USA and other countries. Other product names and brands used in this document are for identification purposes only, and are the property of their respective owners.

Copyright © 2001-2002 Transmeta Corporation. All rights reserved.

# Table of Contents

|           | List of Tables |                                                  |    |  |  |  |

|-----------|----------------|--------------------------------------------------|----|--|--|--|

|           | List c         | of Figures                                       | 7  |  |  |  |

| Chapter 1 | Intro          | duction and Naming Conventions                   | 9  |  |  |  |

|           | 1.1            | Overview                                         |    |  |  |  |

|           | 1.2            | Reference Documents                              |    |  |  |  |

|           | 1.3            | Naming Conventions                               |    |  |  |  |

|           |                | 1.3.1 Power Management Mode Terms                |    |  |  |  |

|           |                | 1.3.2 Power Network Names                        |    |  |  |  |

|           |                | 1.3.3 Signal Names                               |    |  |  |  |

| Chapter 2 | Exam           | nple System Block Diagram and Schematics         |    |  |  |  |

|           | 2.1            | System Block Diagram                             |    |  |  |  |

|           | 2.2            | Processor Schematics                             |    |  |  |  |

| Chapter 3 |                | essor Power Supplies and Power Management        |    |  |  |  |

|           | 3.1            | Power Supplies                                   |    |  |  |  |

|           |                | 3.1.1 Core Power Supply Requirements             |    |  |  |  |

|           |                | 3.1.2 VRM Core Power Supply Example              | 25 |  |  |  |

|           |                | 3.1.3 PLL Power Supply                           |    |  |  |  |

|           |                | 3.1.4 I/O Power Supplies                         |    |  |  |  |

|           |                | 3.1.5 Decoupling Capacitors                      |    |  |  |  |

|           | 3.2            | Power Supply Sequencing                          |    |  |  |  |

|           |                | 3.2.1 Power Sequencing Requirements              |    |  |  |  |

|           |                | 3.2.2 Power Sequencing Circuit Examples          |    |  |  |  |

|           | 3.3            | Power Supply Voltage Supervisor                  |    |  |  |  |

|           | 3.4            | POWERGOOD Block Diagram Example                  |    |  |  |  |

|           | 3.5            | State Transition Timing Requirements             |    |  |  |  |

| Chapter 4 | DDR            | Memory Design                                    |    |  |  |  |

|           | 4.1            | DDR Memory Interface                             | 51 |  |  |  |

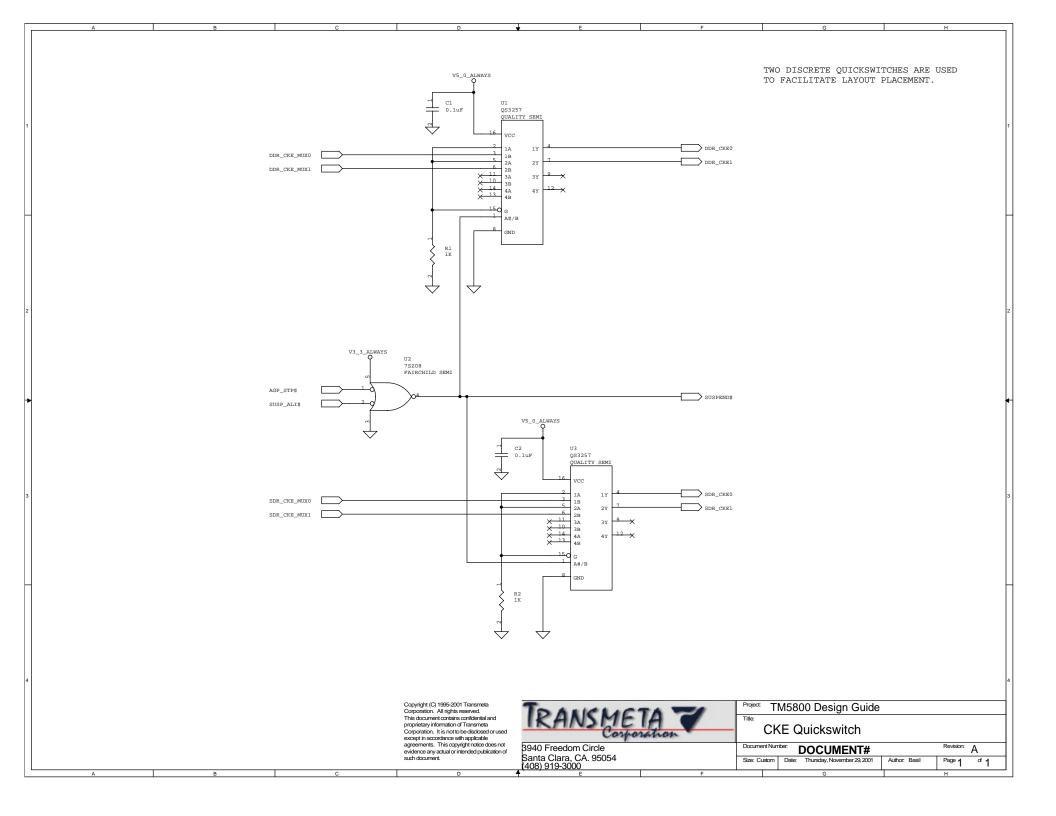

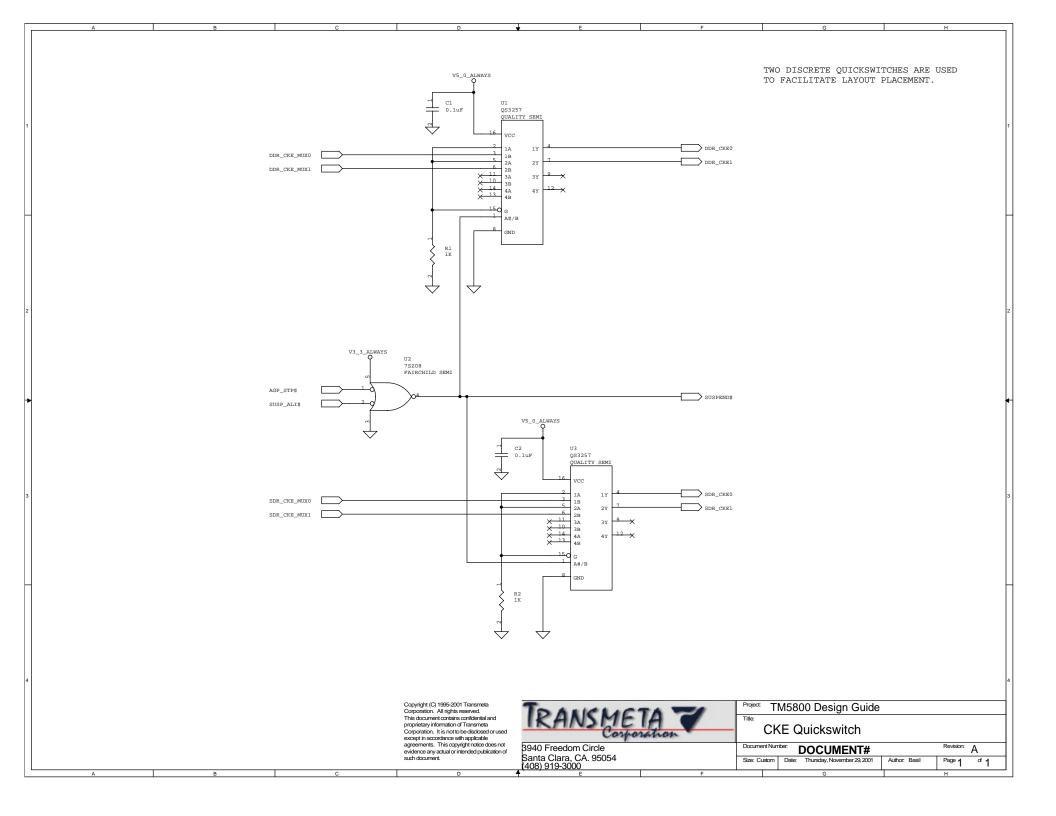

|           | 4.2            | Clock Enable Isolation                           |    |  |  |  |

|           | 4.3            | Signal Termination                               |    |  |  |  |

|           | 4.4            | DDR Reference Voltage                            |    |  |  |  |

|           |                | 4.4.1 DDR Reference Voltage Noise Filter Circuit |    |  |  |  |

|           | 4.5            | DDR Memory Interface Design Guidelines           |    |  |  |  |

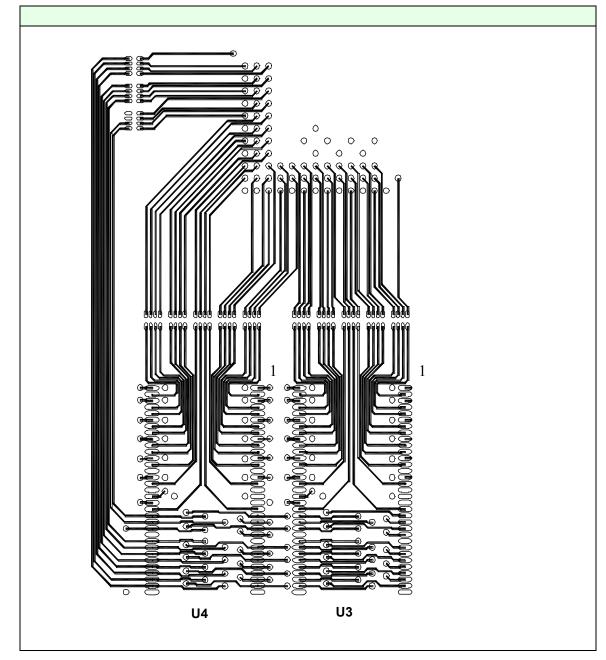

|           | 4.6            | PCB Placement and Routing Example                | 55 |  |  |  |

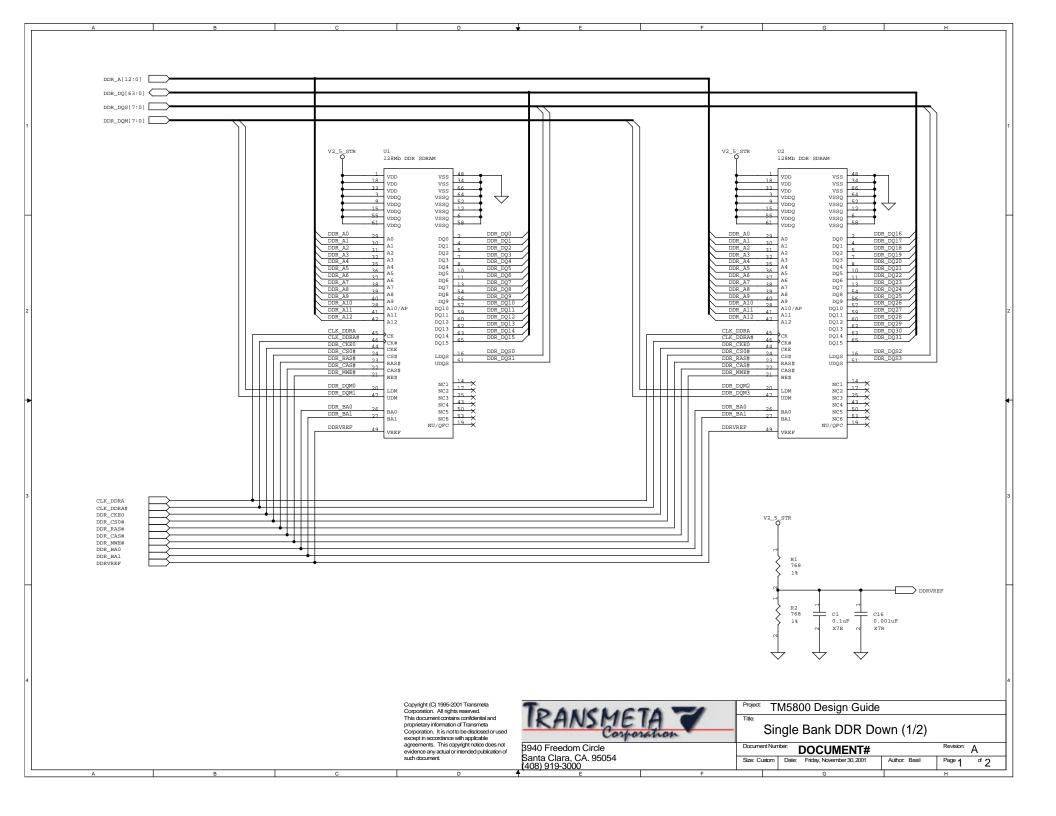

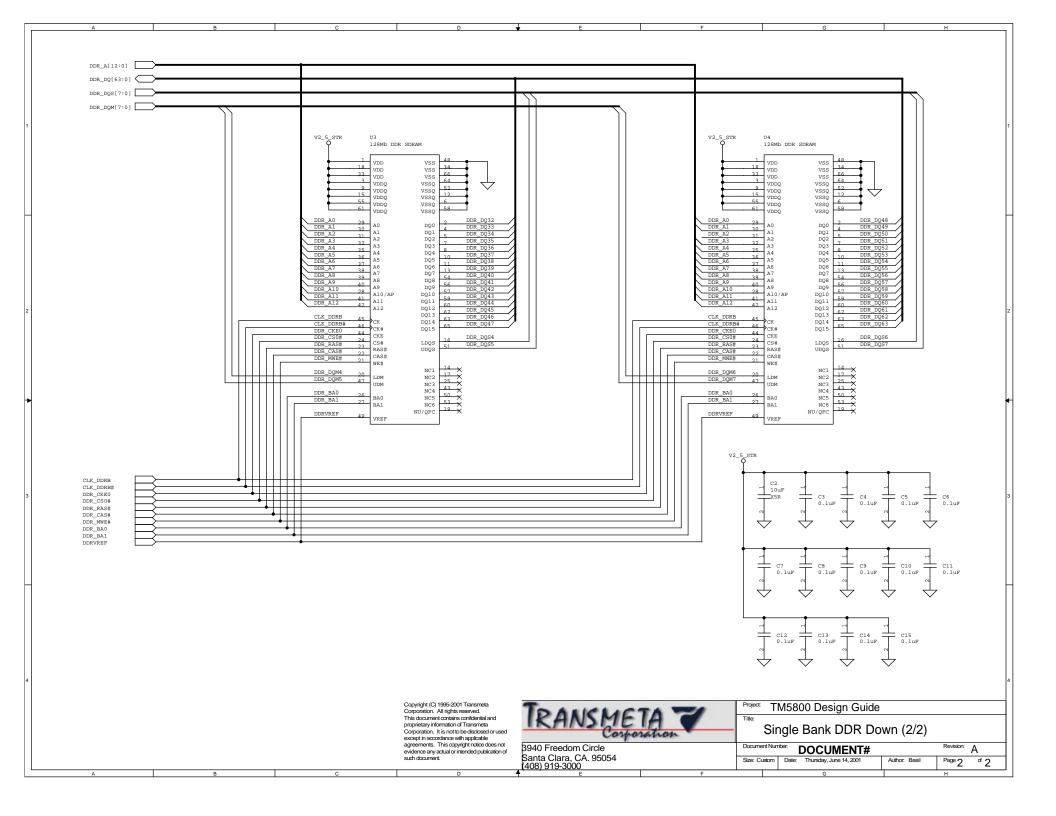

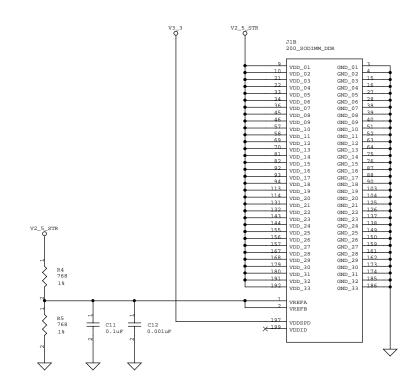

|           | 4.7            | DDR SDRAM Schematics                             | 59 |  |  |  |

| Chapter 5 |                | Memory Design                                    |    |  |  |  |

|           | 5.1            | SDR Memory Interface                             | 65 |  |  |  |

| 5.2 SDR Memory Interface Design Guidelines                 | 66  |

|------------------------------------------------------------|-----|

| 5.2.1 Bank Selection                                       | 66  |

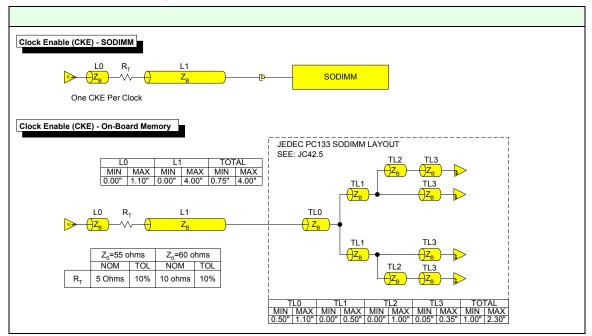

| 5.2.2 Clock Enable Isolation During Power-down States      | 67  |

| 5.2.3 Signal Termination                                   | 67  |

| 5.2.4 Miscellaneous Notes                                  | 67  |

| 5.3 SDR SDRAM Layout Notes                                 |     |

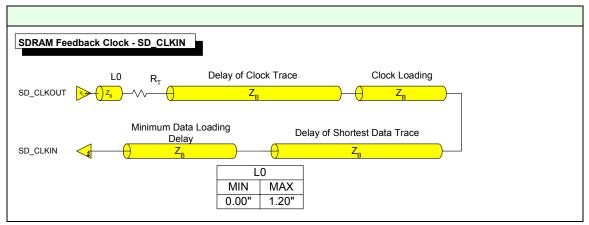

| 5.3.1 SDR SDRAM Memory Interface Timing                    |     |

| 5.3.2 Example Design Strategy                              |     |

| 5.3.3 Write Timing                                         |     |

| 5.3.4 Read Timing                                          |     |

| 5.3.5 Uncertainty in the Feedback Calculation              |     |

|                                                            |     |

| 5                                                          |     |

| 5.3.7 Recommended Design Procedure                         |     |

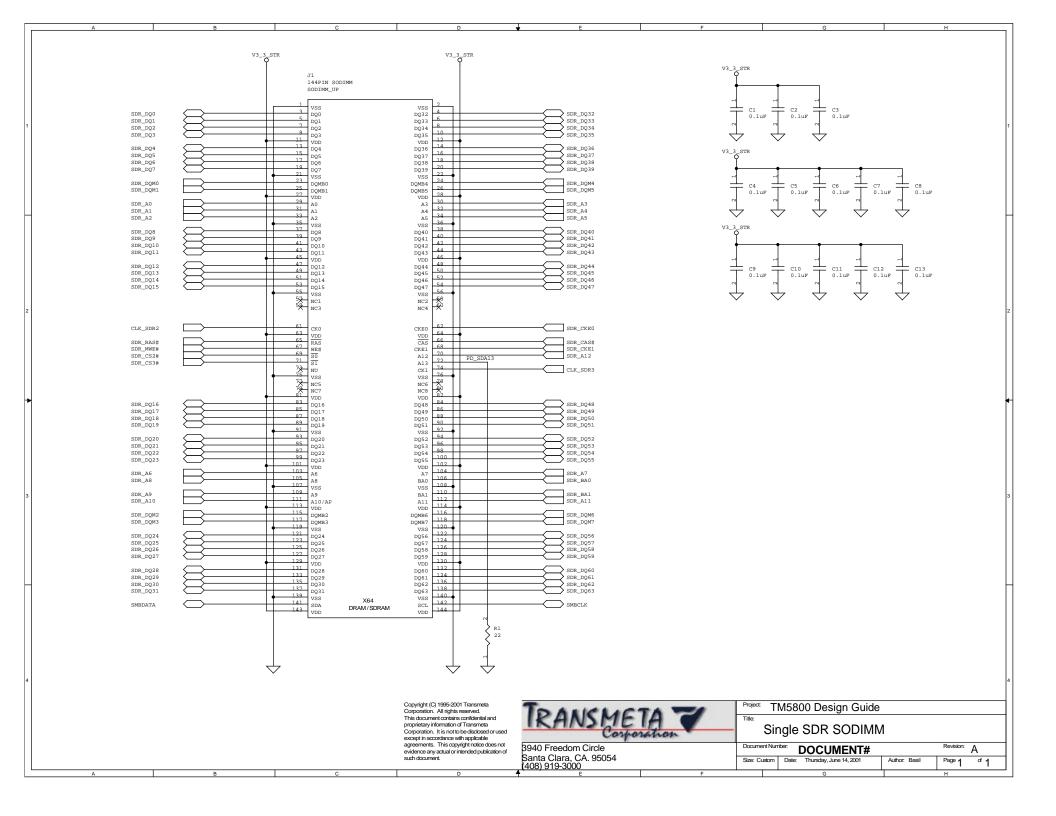

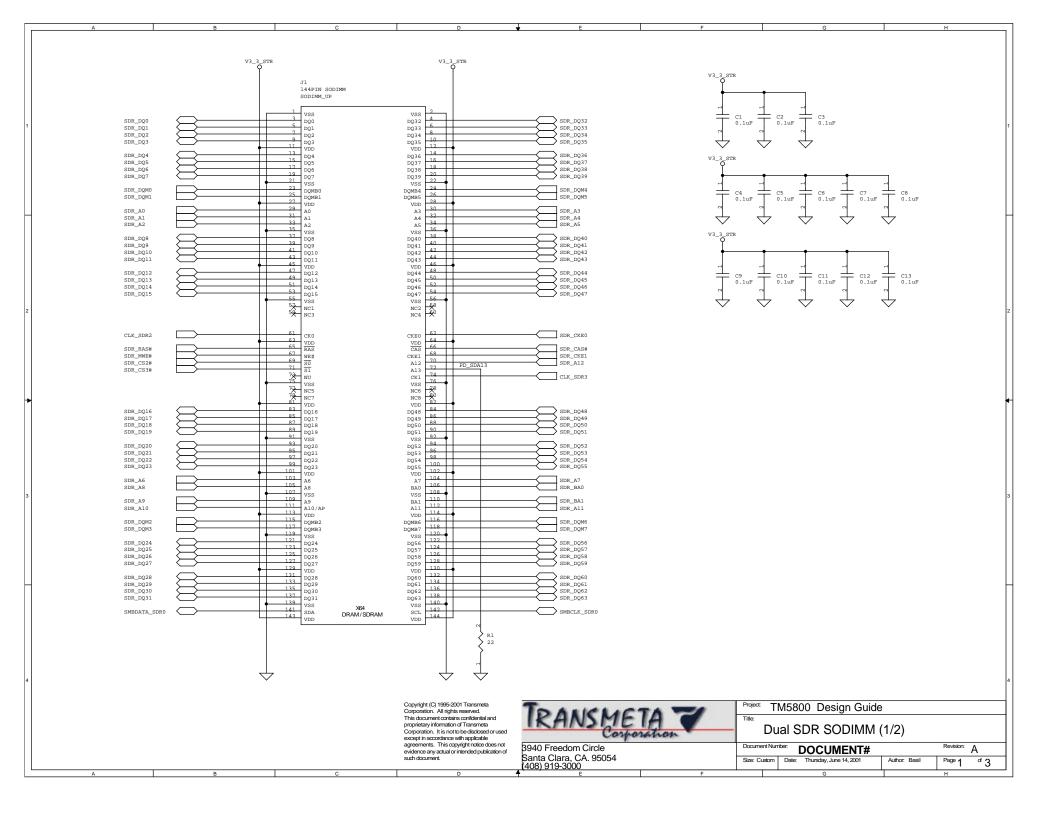

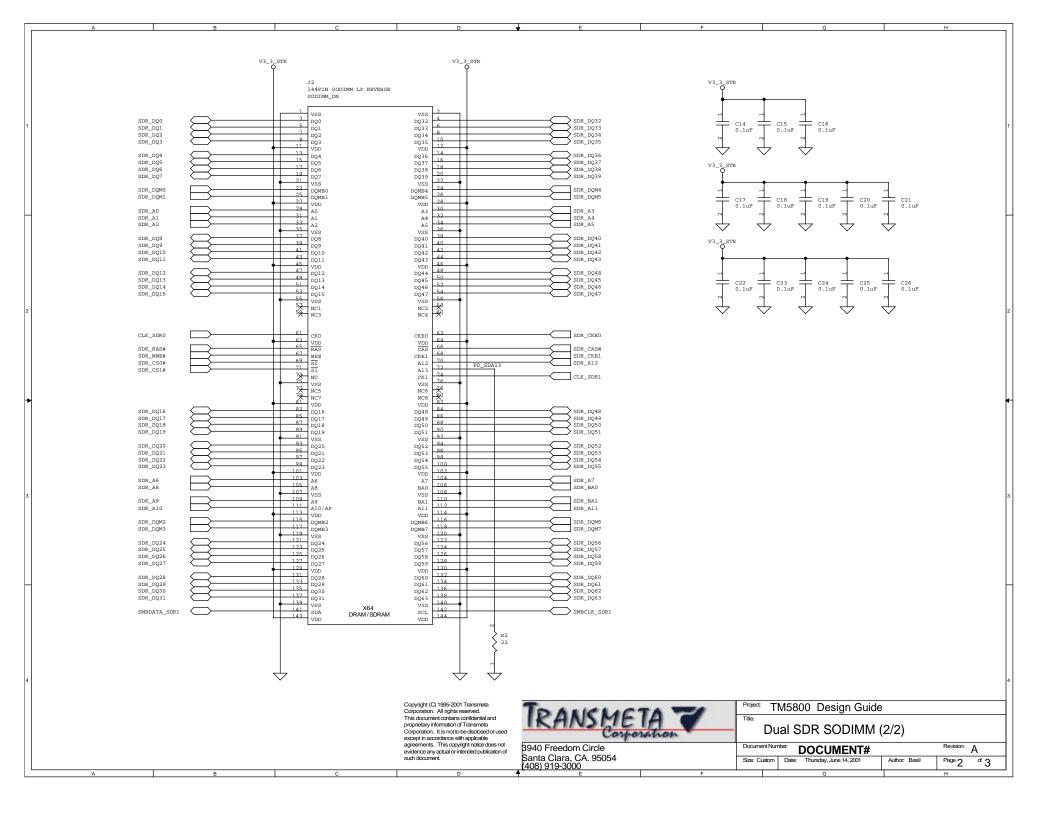

| 5.3.8 Design Example<br>5.4 SDR SDRAM Schematics           |     |

|                                                            |     |

| Chapter 6 System Design Considerations                     |     |

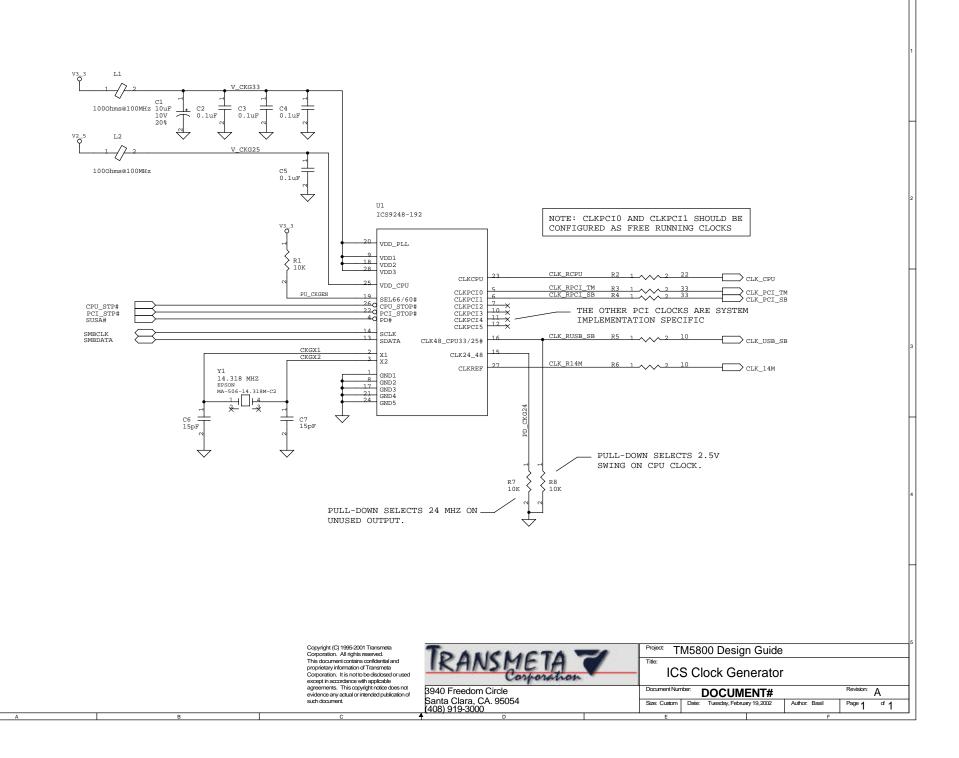

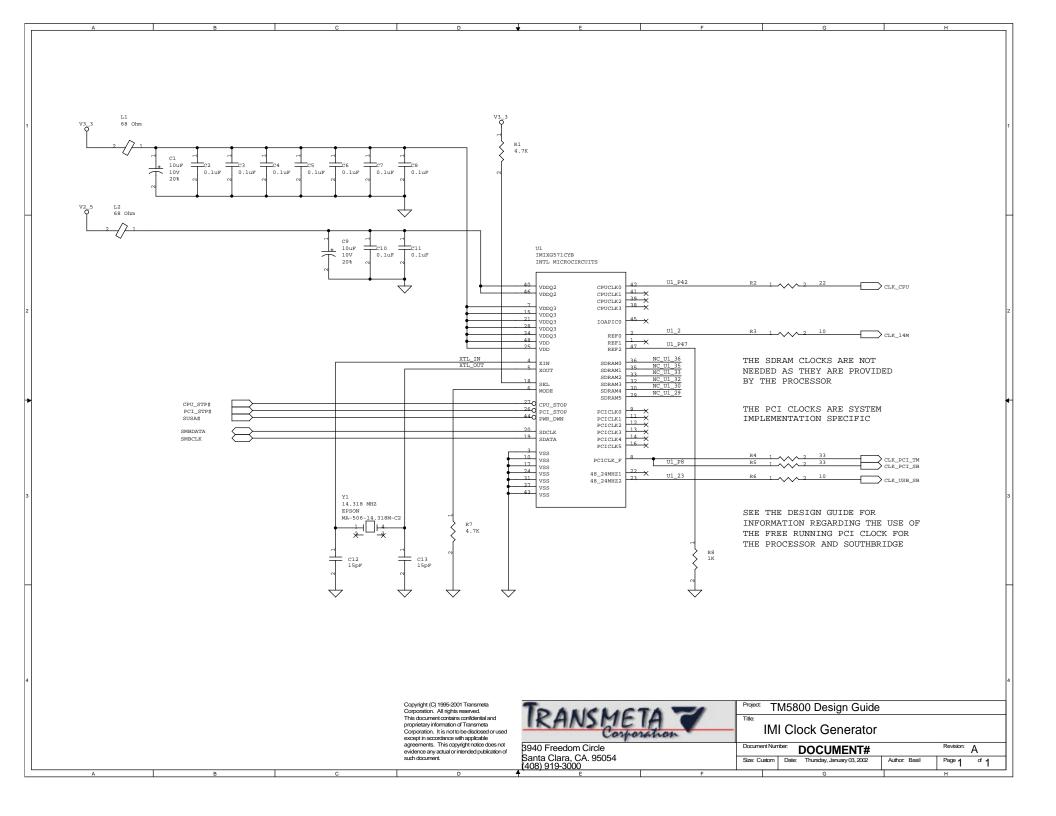

| 6.1 Clocking                                               |     |

| 6.2 System Reset                                           |     |

| 6.3 Signal Pull-ups and Pull-downs                         | 87  |

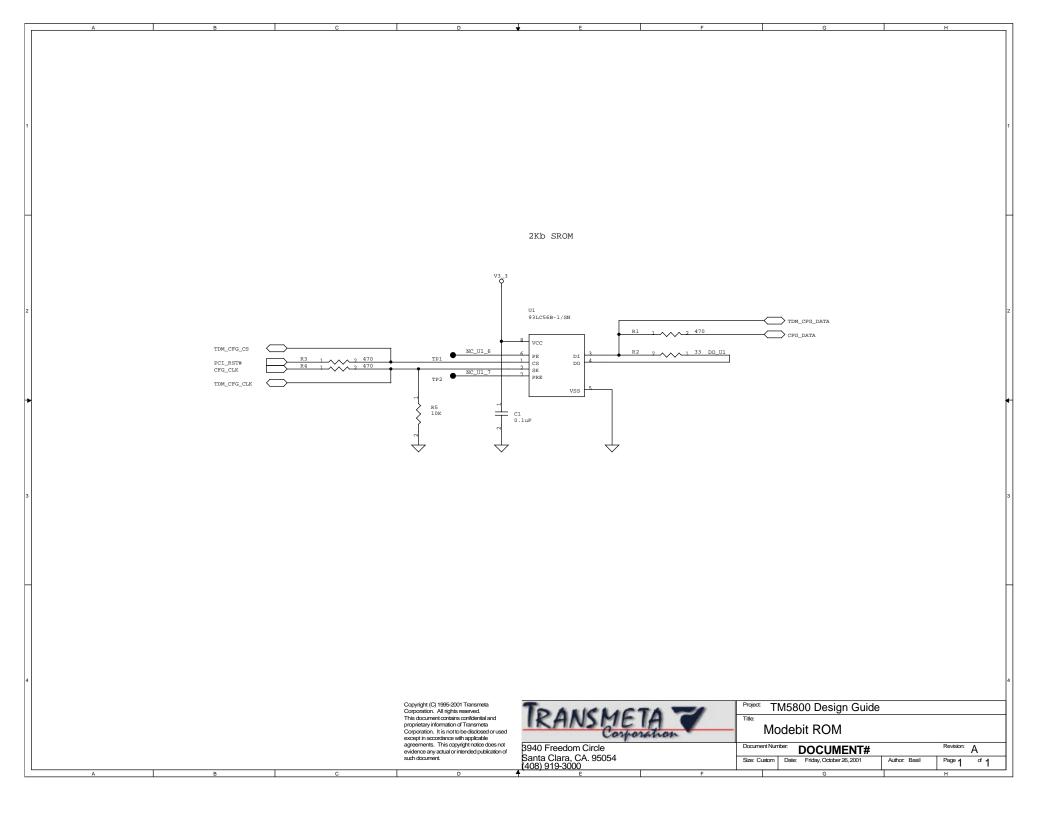

| 6.4 Mode-bit ROM                                           | 89  |

| 6.5 Code Morphing Software ROM                             | 91  |

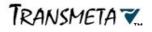

| 6.5.1 Serial Flash ROM Interface                           | 91  |

| 6.5.2 Serial Flash ROM Write Protection Circuit            | 93  |

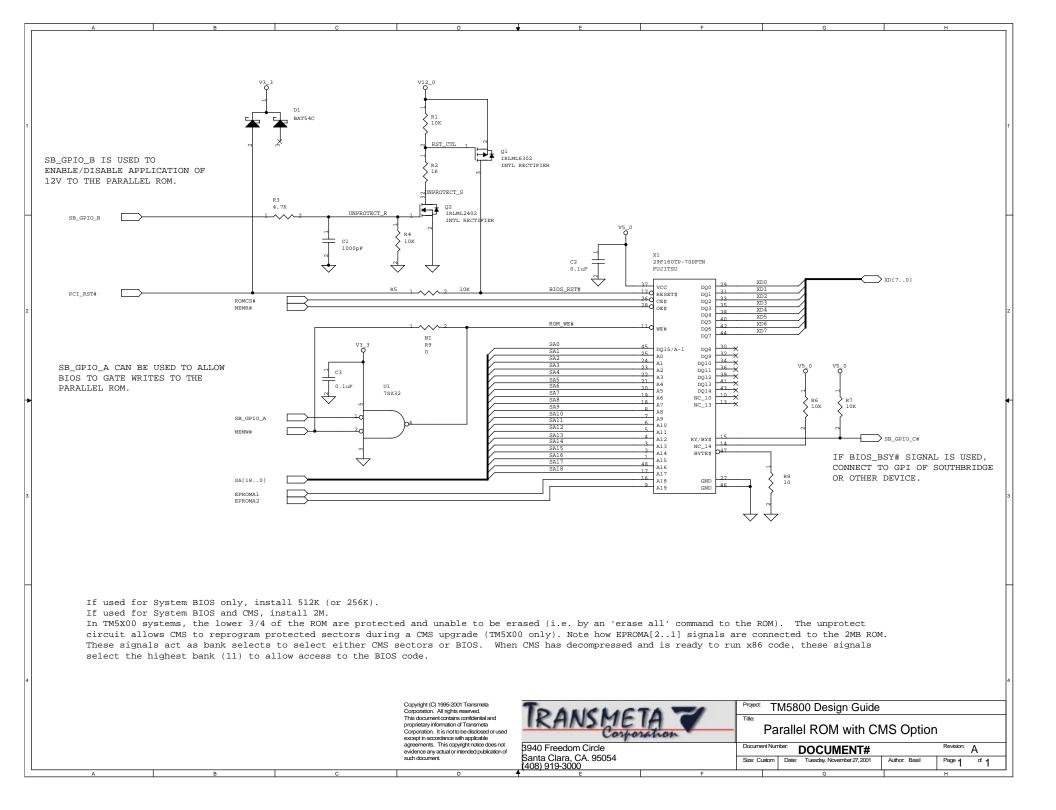

| 6.5.3 Combined BIOS/CMS Parallel ROM Interface             |     |

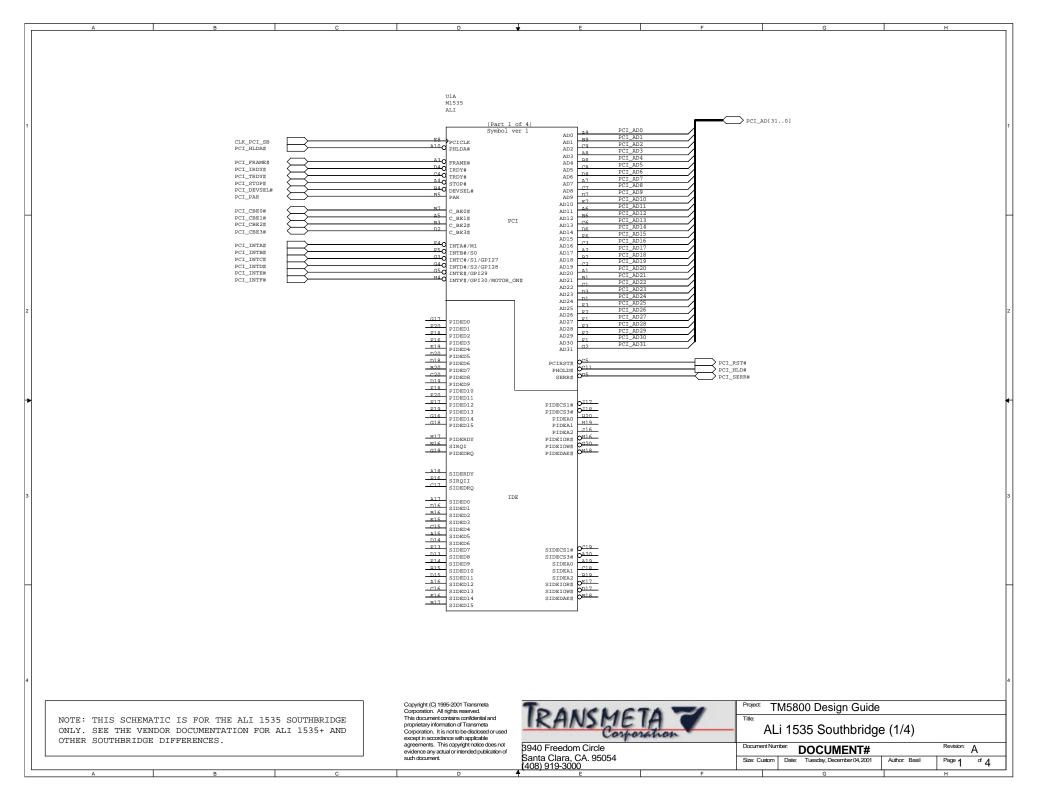

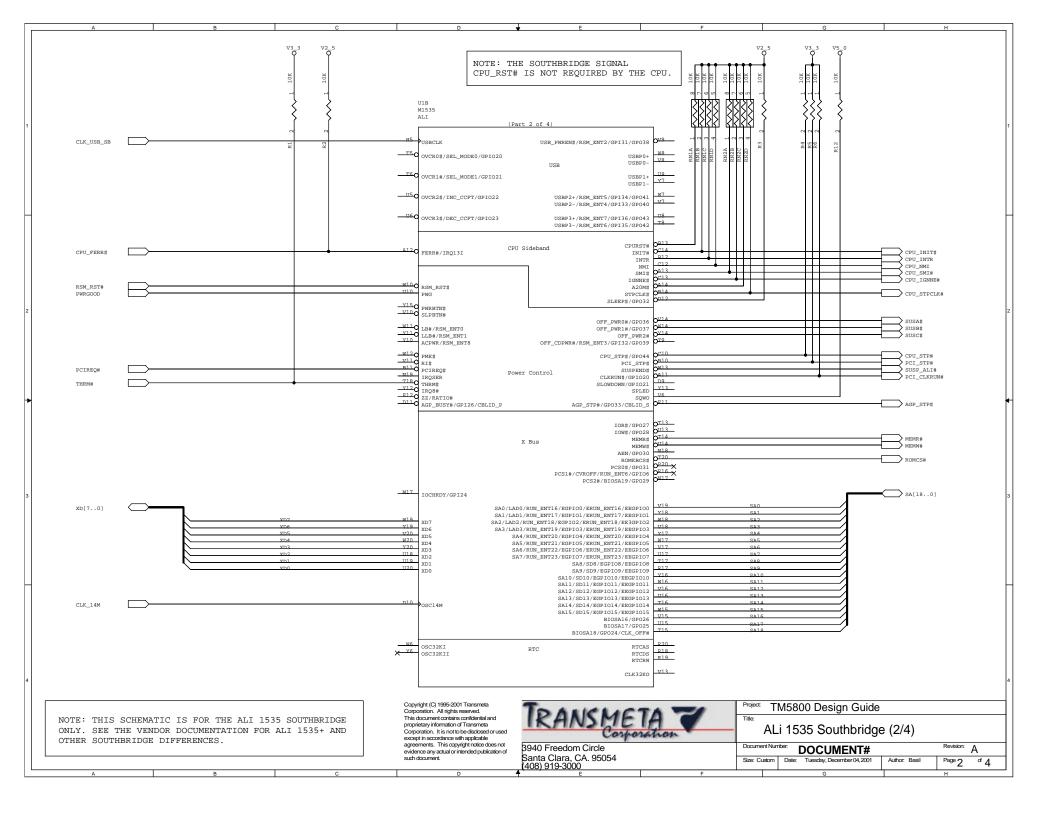

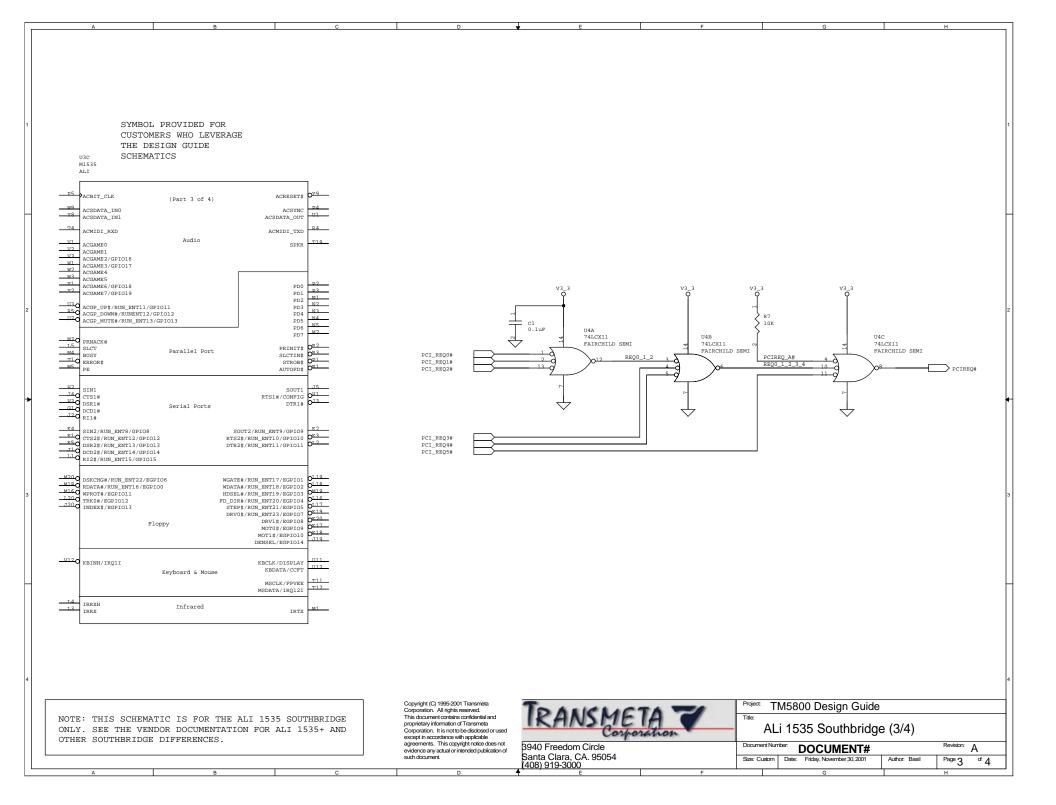

| 6.6 Southbridge                                            |     |

| 6.6.1 Qualified Southbridge Devices                        |     |

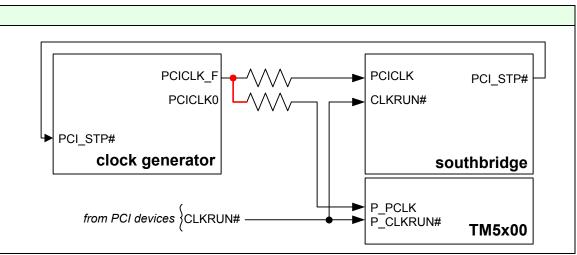

| 6.6.2 Using CLKRUN                                         |     |

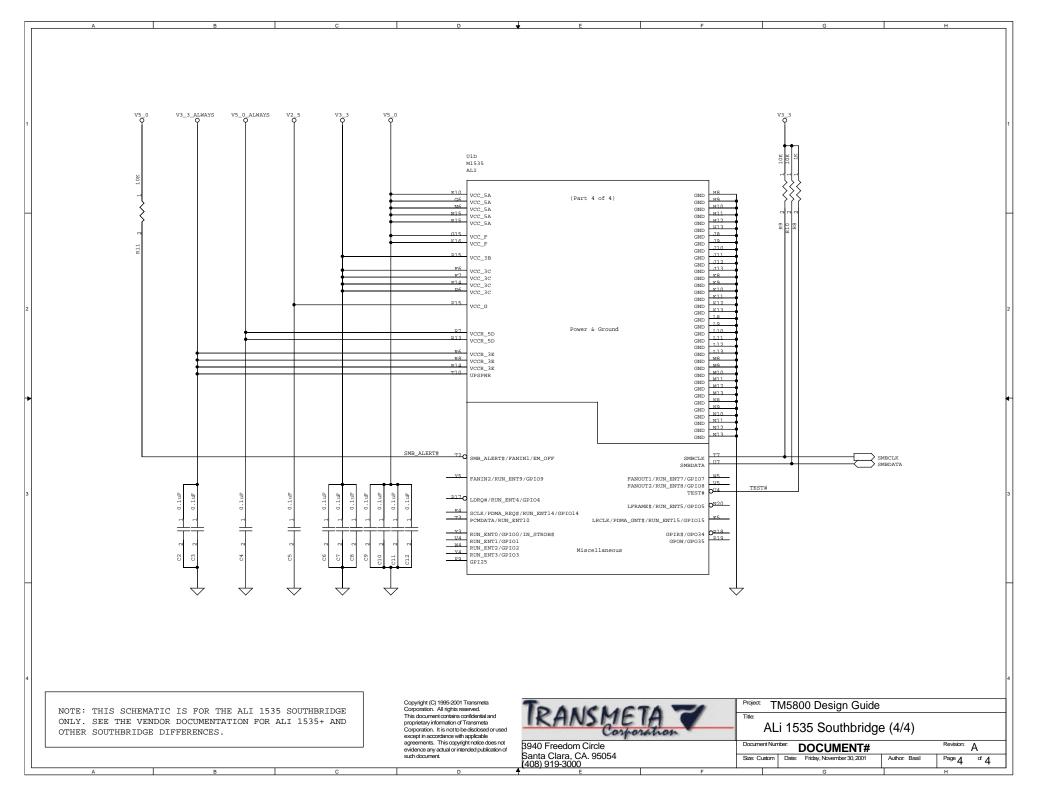

| 6.6.3 Southbridge Schematics                               |     |

| 6.7 Thermal Design                                         |     |

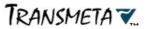

| 6.8 Thermal Diode and Thermal Sensor                       |     |

|                                                            |     |

|                                                            |     |

| 6.8.2 Thermal Sensor Issues                                |     |

| 6.8.3 Thermal Sensor Layout                                |     |

| 6.8.4 Thermal Sensor Example Schematic                     |     |

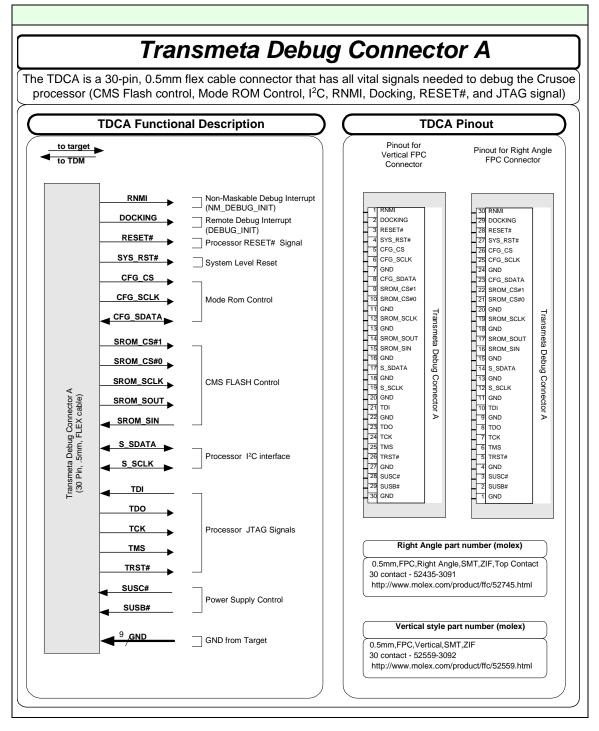

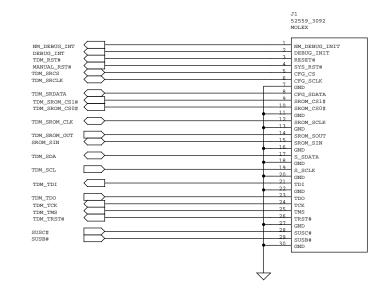

| 6.9 TDM Debug Interface Connection                         | 107 |

| Chapter 7 PCB Layout Guidelines                            | 111 |

| 7.1 PCB Design Layout                                      | 111 |

| 7.2 Example PCB Fabrication Notes                          |     |

| 7.3 Board Design Guidelines                                |     |

| 7.3.1 Printed Circuit Board Stackup                        |     |

| 7.3.2 Allegro Standard Spacing Constraints                 |     |

| 7.3.3 Allegro Extended Spacing Constraints                 |     |

| 7.3.4 Allegro Extended Physical (Lines/Vias) Constraints   |     |

| 7.3.5 Allegro Extended Electrical (Lines/Vias) Constraints |     |

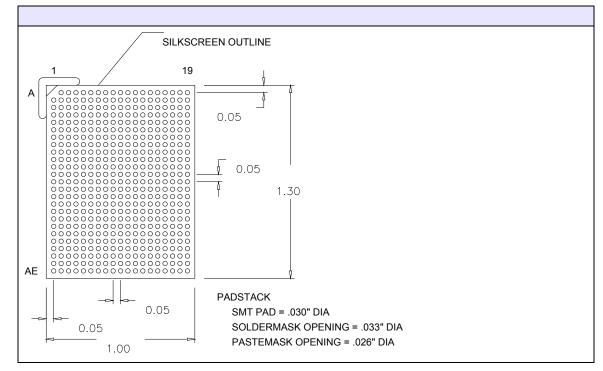

| 7.4 Footprint and Pin Escape Diagram                       |     |

|                                                            |     |

| Appendix A System Design Checklists                        | 117 |

| Appendix B Serial Write-protection PLD Data                | 123 |

|                                                            |     |

# List of Tables

| Table 1:  | Supported ACPI Processor States                             |     |

|-----------|-------------------------------------------------------------|-----|

| Table 2:  | Supported ACPI System States                                | 11  |

| Table 3:  | Power Net Naming Conventions                                | 12  |

| Table 4:  | Signal Naming Conventions                                   | 12  |

| Table 5:  | Core Power Supply Requirements for TM5500/TM5800 Processors | 22  |

| Table 6:  | Default Power-on Start Voltage VRDA (VID) Output Codes      | 23  |

| Table 7:  | VID/VRDA Values and Output Voltages for MAX1718 VRM         | 24  |

| Table 8:  | MAX1718 Core Power Supply Output Control Selector           | 25  |

| Table 9:  | MAX1718 DSX Voltage Configuration                           | 26  |

| Table 10: | Power Supply Sequencing Timing Specifications               | 35  |

| Table 11: | DDR SDRAM Memory Configurations                             | 51  |

| Table 12: | SDR SDRAM Memory Configurations                             | 65  |

| Table 13: | SDR SDRAM Interface Device Specifications                   | 68  |

| Table 14: | Write Timing Compensation                                   | 69  |

| Table 15: | Signal Pull-up/Pull-down Requirements                       | 87  |

| Table 16: | PLD Pinout                                                  | 94  |

| Table 17: | Recommended Eight Layer PCB Stackup                         | 113 |

| Table 18: | Standard Spacing/Line/Via Constraints                       | 113 |

| Table 19: | Extended Global Spacing/Line/Via Constraints                |     |

| Table 20: | Extended Physical Constraints                               | 115 |

| Table 21: | Extended Electrical Constraints                             |     |

List of Tables

# List of Figures

| Figure 1:  | Example Schematic Naming System                                            | .11  |

|------------|----------------------------------------------------------------------------|------|

| Figure 2:  | Example System Block Diagram                                               |      |

| Figure 3:  | PLL / Processor Core Voltage Tracking Requirement                          | . 30 |

| Figure 4:  | Power Supply Sequencing                                                    | . 35 |

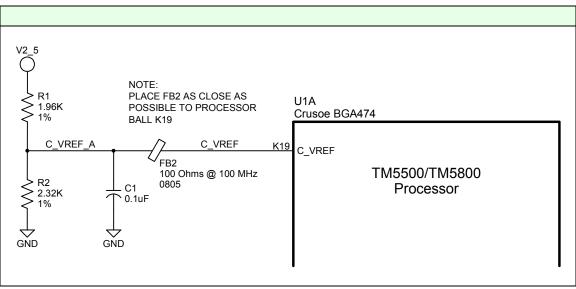

| Figure 5:  | Recommended DDR Reference Voltage Circuit with Ferrite Bead Noise Filter . | .53  |

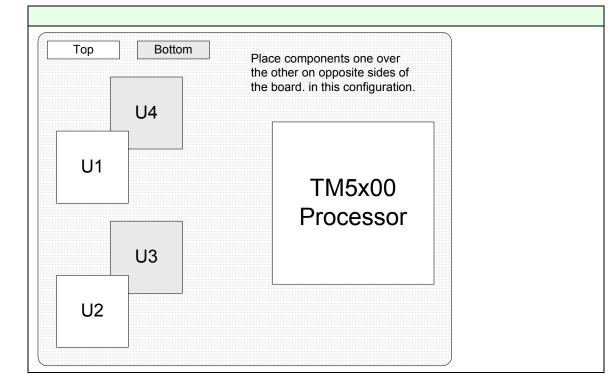

| Figure 6:  | Recommended 4-Device DDR Memory Chip Placement                             | .55  |

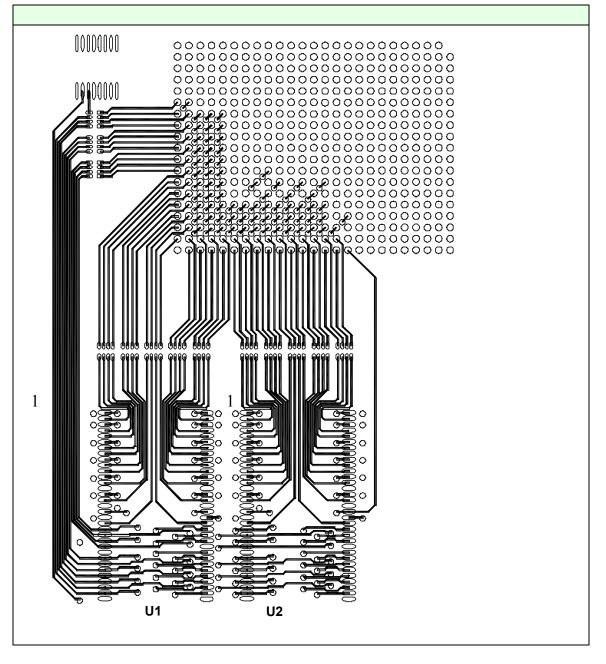

| Figure 7:  | Recommended 4-Device DDR Memory Signal Routing - Top Layer                 | .56  |

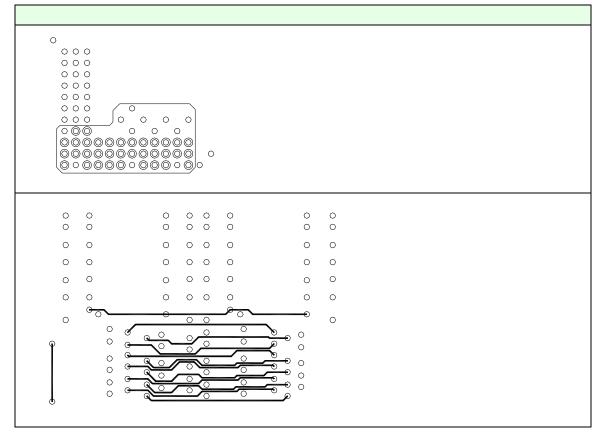

| Figure 8:  | Recommended 4-Device DDR Memory Signal Routing - Internal Layer            |      |

| Figure 9:  | Recommended 4-Device DDR Memory Signal Routing - Bottom Layer              | . 58 |

| Figure 10: | Physical SDRAM Configurations                                              | .68  |

| Figure 11: | Read Timing Compensation                                                   | .70  |

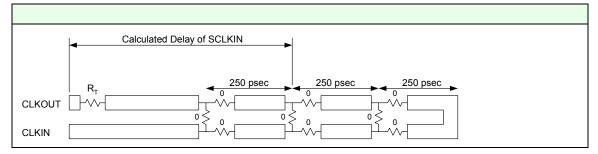

| Figure 12: | Adjustment of CLKIN Delay                                                  | .71  |

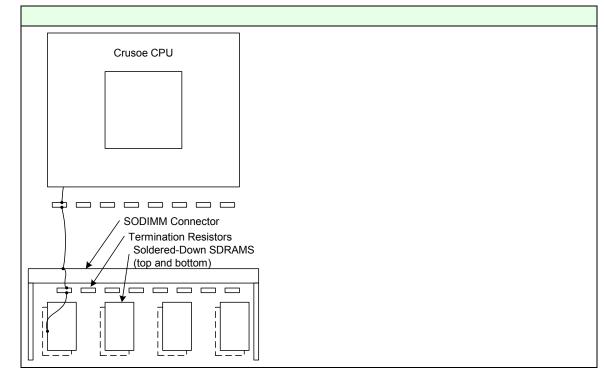

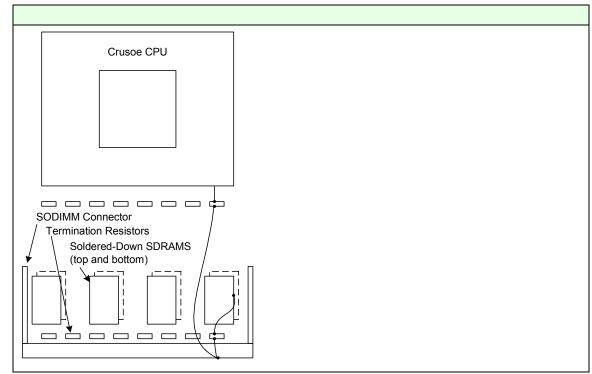

| Figure 13: | Optimum Placement and Routing                                              | .72  |

| Figure 14: | Sub-optimal Placement                                                      | .72  |

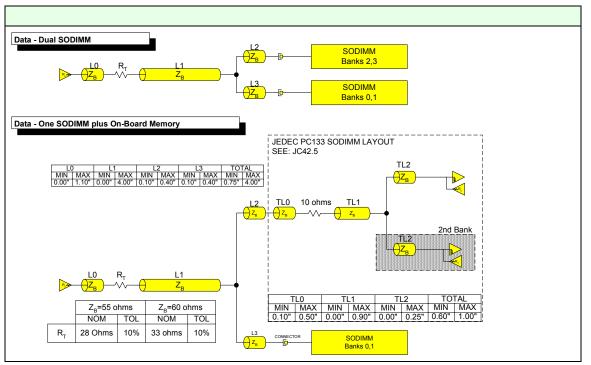

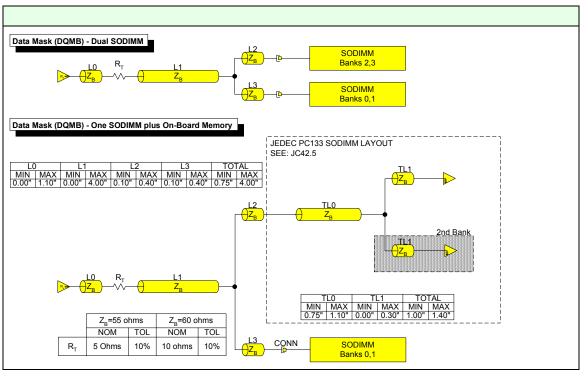

| Figure 15: | Data Structure Diagram                                                     |      |

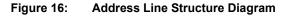

| Figure 16: | Address Line Structure Diagram                                             | .74  |

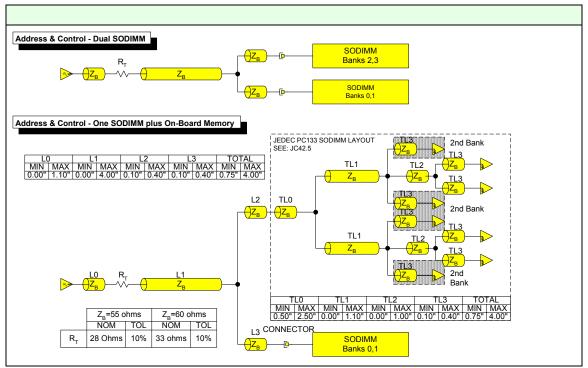

| Figure 17: | Clock Line Structure Diagram                                               | .74  |

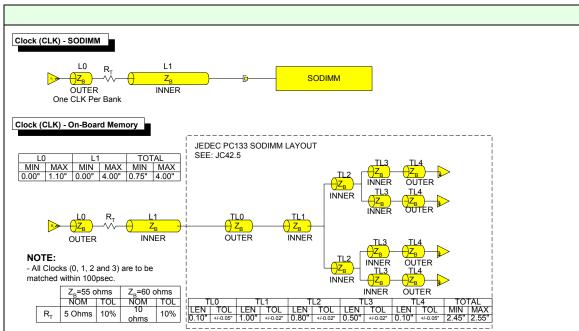

| Figure 18: | Data Mask Structure Diagram                                                | .75  |

| Figure 19: | Clock Enable Structure Diagram                                             | .75  |

| Figure 20: | System Reset Diagram                                                       | .86  |

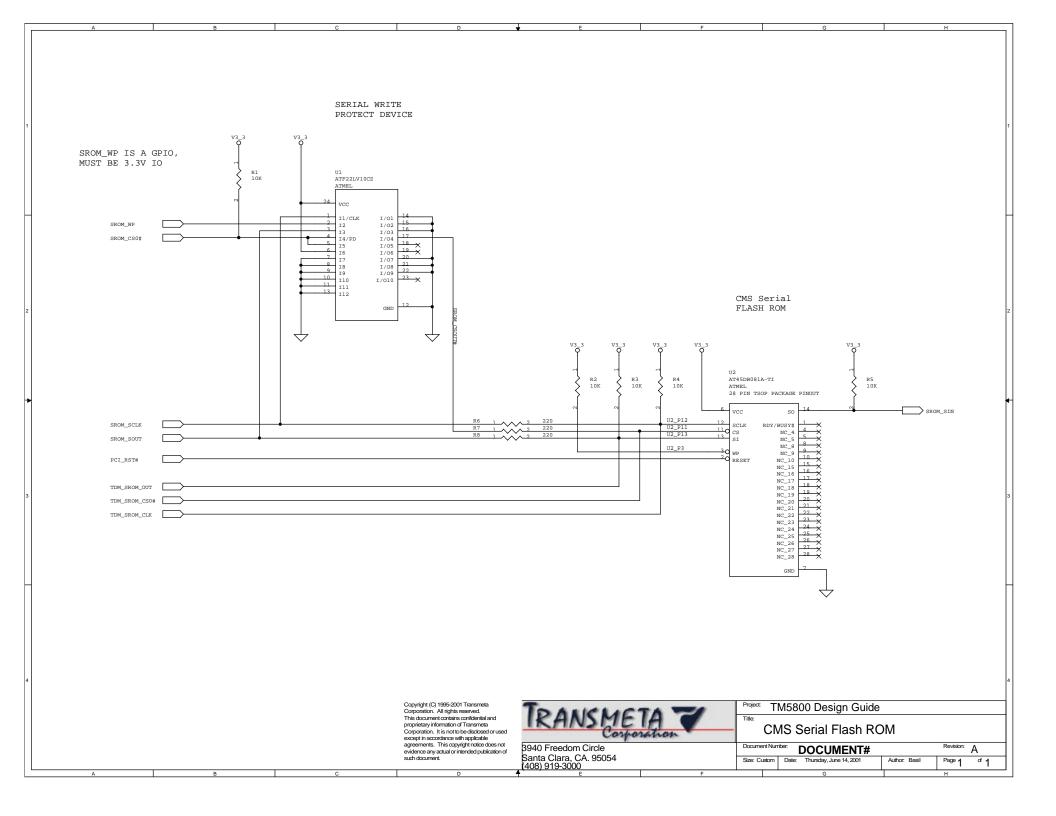

| Figure 21: | Schematic Diagram of Serial Flash Write-protection PLD in System           | .95  |

| Figure 22: | Recommended CLKRUN Circuit                                                 | .98  |

| Figure 23: | Transmeta Debug Connector (TDCA)                                           | 108  |

| Figure 24: | Mechanical Footprint                                                       |      |

| Figure 25: | Write Protection TSSOP-24 JEDEC Fuse Map                                   | 124  |

| Figure 26: | Write Protection TSSOP-24 CUPL Source Code                                 | 125  |

### Chapter 1

# Introduction and Naming Conventions

# 1.1 Overview

This design guide is organized into the following sections:

- Introduction and Naming Conventions (this chapter) introduces the conventions used in this document, including possible differences between hardware names for power supplies, pins, etc. and the reference schematics used throughout the document.

- Chapter 2, *Example System Block Diagram and Schematics* presents the Crusoe TM5500/TM5800 processor in the context of a block diagram that shows necessary components and their connections. The reference schematic for the processor itself is also provided.

- Chapter 3, *Processor Power Supplies and Power Management* describes the power supply network in detail.

- Chapter 4, *DDR Memory Design* provides design guidelines and layout requirements for incorporating DDR SDRAM memory into a design.

- Chapter 5, SDR Memory Design provides design guidelines and layout requirements for incorporating SDR SDRAM memory into a design.

- Chapter 6, *System Design Considerations* describes a variety of design issues, including clocking, reset, ROM interfaces, signal pull-up/pull-down requirements, thermal sensor, and southbridge interfaces.

- Chapter 7, *PCB Layout Guidelines* discusses physical issues related to memory and component interfaces, power supplies, signal integrity, mounting and spacing constraints, tolerances and fabrication guidelines, and footprint and pin escape diagrams.

- Appendix A, System Design Checklists includes cross-referenced checklists to follow while designing a system.

- Appendix B, Serial Write-protection PLD Data includes the JEDEC fuse map and CUPL source code for the write-protection PLD required for serial-ROM Code Morphing software placement. This issue is described in Serial Flash ROM Write Protection Circuit on page 93 in Chapter 6, System Design Considerations.

- An Index is also included.

#### Note

The block diagram and reference schematics included in this book offer general guidelines for integrating TM5500/TM5800 processors into product designs. For detailed processor-specific information, consult the reference documents listed below.

# **1.2 Reference Documents**

The following documents are available from Transmeta for use in conjunction with this design guide. Some of these documents are extensively referenced in the design guide, and should be consulted as specified in the text.

- TM5500/TM5800 Data Book

- TM5500/TM5800 Package Specifications and Manufacturing Guide

- TM5500/TM5800 Thermal Design Guide

- TM5500/TM5800 Development and Manufacturing Guide

- TM5500/TM5800 BIOS Programmer's Guide

- TM5500/TM5800 IBIS Models

- TM5500/TM5800 BSDL file

- TM5500/TM5800 Code Morphing Software Release Notes

- TM5500/TM5800 Technical Bulletins and Errata documents

# **1.3 Naming Conventions**

Power supply and signal names used in the *Data Book* and other hardware-specific materials can be different from those used on the reference schematics. This section shows the terms used in the *System Design Guide* and the reference schematics, and correlates them with the hardware-specific names used elsewhere.

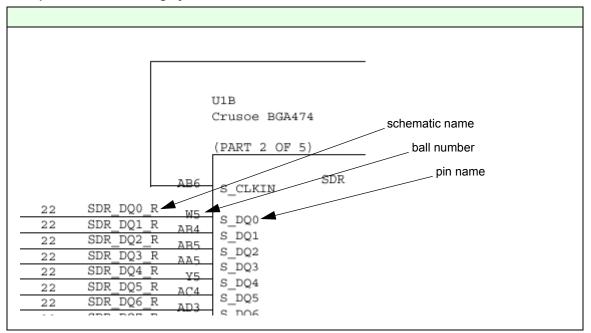

In general, the hardware symbols in the schematics show the hardware names for each item (signal or power line). The alphanumeric marker at the connection between symbol and line is the ball number, described in detail in the *Data Book*. The line itself shows the schematic net name, i.e. the name that is used throughout this document to refer to that net/signal/line.

The following diagram shows how to locate the various schematic names:

Figure 1: Example Schematic Naming System

# 1.3.1 Power Management Mode Terms

The power management modes supported by TM5500/TM5800 processors are discussed in detail in Chapter 1, *Functional Interface Description*, in the *Data Book*. The following tables show the ACPI power and sleep states supported by TM5500/TM5800 processors and referenced in this document.

| ACPI State | ACPI State Name | Description                                                                        |

|------------|-----------------|------------------------------------------------------------------------------------|

| C0         | Normal          | Active power state with processor executing instructions.                          |

| C1         | Auto Halt       | Sleep state entered by processor executing HALT instruction.                       |

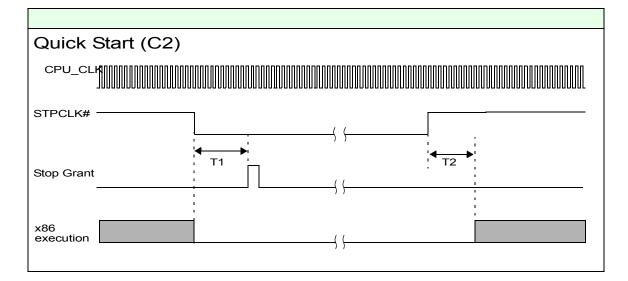

| C2         | Quick Start     | Sleep state requiring chipset/hardware support. This state is lower power than C1. |

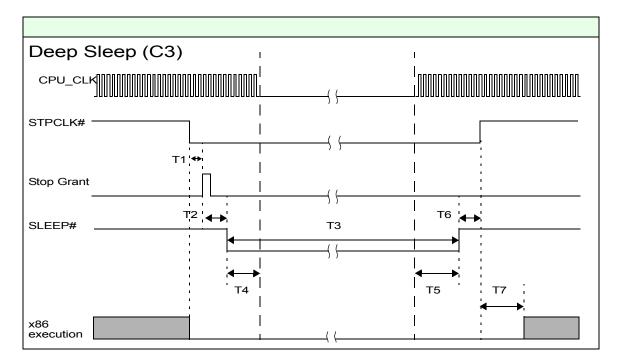

| C3         | Deep Sleep      | Sleep state requiring chipset/hardware support. This state is lower power than C2. |

#### Table 1: Supported ACPI Processor States

#### Table 2: Supported ACPI System States

| ACPI State | ACPI State Name         | Description                                                                                                                              |

|------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| S0         | Working                 | Normal active state (not sleeping).                                                                                                      |

| S1         | Power-on Suspend        | Processor not executing instructions. Processor state and RAM context maintained.                                                        |

| S3         | Suspend-to-RAM<br>(STR) | Current processor state is suspended and stored in volatile RAM (that is kept powered). Only _STR and _ALWAYS power supplies are active. |

| Table 2: | Supported ACPI System States (C | ontinued) |

|----------|---------------------------------|-----------|

|----------|---------------------------------|-----------|

| ACPI State | ACPI State Name          | Description                                                                                                        |

|------------|--------------------------|--------------------------------------------------------------------------------------------------------------------|

| S4         | Suspend-to-Disk<br>(STD) | Current processor state is suspended and saved to non-volatile disk.<br>All power supplies except _ALWAYS are off. |

| S5         | Soft Off                 | System is turned off. All power supplies except _ALWAYS are off.                                                   |

Note that some terms must be combined for a full description of system state (e.g. Working/Auto Halt vs. Working/Quick Start). For more details on ACPI states, see the ACPI specification.

For information on timing requirements between states, see *State Transition Timing Requirements* on page 42. Power specifications for each of the supported power management modes are provided in *Chapter 3, Electrical Specifications* in the *Data Book*.

# 1.3.2 Power Network Names

Transmeta's reference schematics use a standard naming convention for power supply nets, provided in the table below.

#### Table 3: Power Net Naming Conventions

| Convention  | Description                                                       |

|-------------|-------------------------------------------------------------------|

| V_name      | A switched voltage such as V_CPU_CORE, off during S3, S4, and S5  |

| Vn_d_STR    | A voltage present in S3 (STR), off during S4 and S5               |

| Vn_d        | A switched voltage at <i>n.d</i> volts, off during S3, S4, and S5 |

| V_Nn_d      | A negative voltage at <i>n.d</i> volts, off during S3, S4, and S5 |

| Vn_d_ALWAYS | An always-on voltage, i.e. present in all ACPI sleep states       |

# 1.3.3 Signal Names

Transmeta's reference schematics call out many signals which may be named slightly differently in hardwareoriented documents such as the *Data Book*. The following table illustrates the character conventions used in the schematics:

#### Table 4: Signal Naming Conventions

| Character | Description                                                                                | Example         |

|-----------|--------------------------------------------------------------------------------------------|-----------------|

| #         | Denotes asserted low signals. Signal names without this suffix are assumed to assert high. | LOWSIG#         |

| , :       | Used to separate elements in a list.                                                       | EIGHTBITBUS[70] |

|           |                                                                                            | D[7:0]          |

| 1         | Can be used to separate multiple uses of a pin.                                            | USEA/USEB       |

| []        | Delineates bus name from element list.                                                     | EIGHTBITBUS[70] |

## Chapter 2

# Example System Block Diagram and Schematics

# 2.1 System Block Diagram

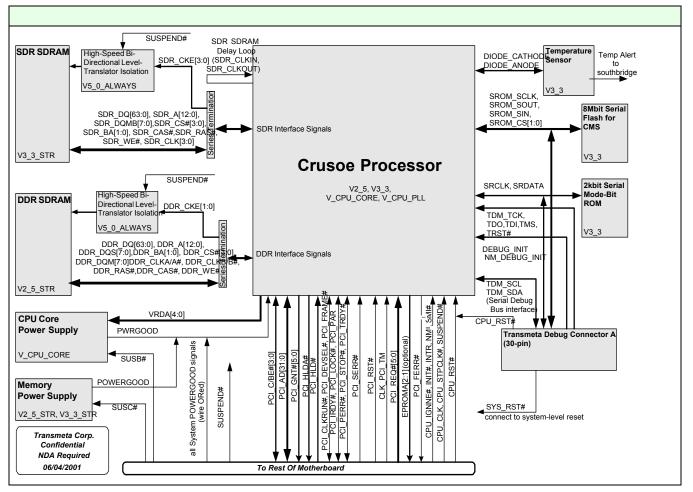

The block diagram below shows major elements of a TM5500/TM5800 processor-based system design. Signals and bus interconnections are also shown. For detailed circuit design information, see the reference schematics throughout this document (also available in OrCAD format from your Transmeta representative).

Figure 2: Example System Block Diagram

TRANSMETA 🟹

TM5500/TM5800 processors include both core processor and northbridge functionality. For a motherboard designer, this means the processor looks very much like a northbridge. TM5500/TM5800 processors support two DRAM interfaces, one for Double Data Rate (DDR) SDRAMs and the other for Single Data Rate (SDR) SDRAMs. Designers can choose to use either or both SDRAM interfaces, depending on their system cost and performance requirements.

In the block diagram, note that power signals that feed each component are listed in the component's block. This helps to identify suspend and switched power distribution to each component. Descriptions of each supply are described in Chapter 3, *Processor Power Supplies and Power Management*.

The major elements shown in the block diagram are outlined below:

- **Processor Core Power Supply**. The processor core high-efficiency switched-mode power supply. See Chapter 3, *Processor Power Supplies and Power Management*.

- **Memory Power Supplies**. The power supplies for SDR and DDR SDRAM memory. See Chapter 3, *Processor Power Supplies and Power Management*.

- DDR SDRAM Interface. The processor can support up to two identical banks of DDR SDRAMs in various configurations of 64-Mbit, 128-Mbit, 256-Mbit, and 512-Mbit devices. See Chapter 4, DDR Memory Design.

- SDR SDRAM Interface. The processor can support up to four banks of SDR SDRAMs in various configurations of 64-Mbit, 128-Mbit, 256-Mbit, and 512-Mbit devices. See Chapter 5, SDR Memory Design.

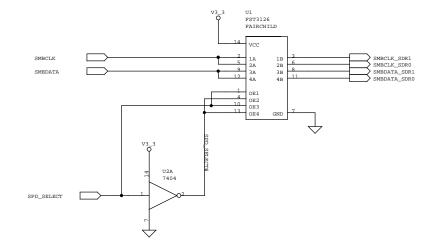

- SDRAM High-speed Bidirectional Level-translator Isolation. Signal isolation is used to ensure that CKE signals to the SDRAMs remain stable during processor power transitions. Since the processor does not have a suspend power well, output signals are undefined during power transitions and subject to glitching.

- PCI Interface and PCC Signals. The PCI interface is 33 MHz, 3.3 V. The arbiter supports five REQ/GNT pairs. CLKRUN is supported (see Using CLKRUN on page 98). PCC (PC compatibility) signals are used for communication with the southbridge. See Southbridge on page 98.

- Code Morphing Software Serial Flash ROM. Code Morphing software is stored in this optional (but recommended) 1 Mbyte device. See Serial Flash ROM Interface on page 91. Other options for Code Morphing software code storage (such as sharing the BIOS ROM) are also described. See Combined BIOS/CMS Parallel ROM Interface on page 96.

- Serial Flash Write-protection Circuit. If a serial flash ROM is used for Code Morphing software, a PLD (programmable logic device) write-protection device must be added to the serial flash ROM circuit. See Serial Flash ROM Write Protection Circuit on page 93.

- Mode-bit ROM (required). System-dependent configuration options vital to proper processor operation are stored in this required 2 Kbit device and read by the processor at boot time. See *Mode-bit ROM* on page 89.

- **Thermal Sensor**. An external thermal sensor is used in conjunction with a thermal sensing diode built into the processor. See *Thermal Diode and Thermal Sensor* on page 103.

- Transmeta Debug Module (TDM) Interface. This adds some low-level debug support to facilitate indesign bring-up, as well as connectivity to the Transmeta Virtual In-Circuit Emulator CE (TMVICE) for software development. See TDM Debug Interface Connection on page 107.

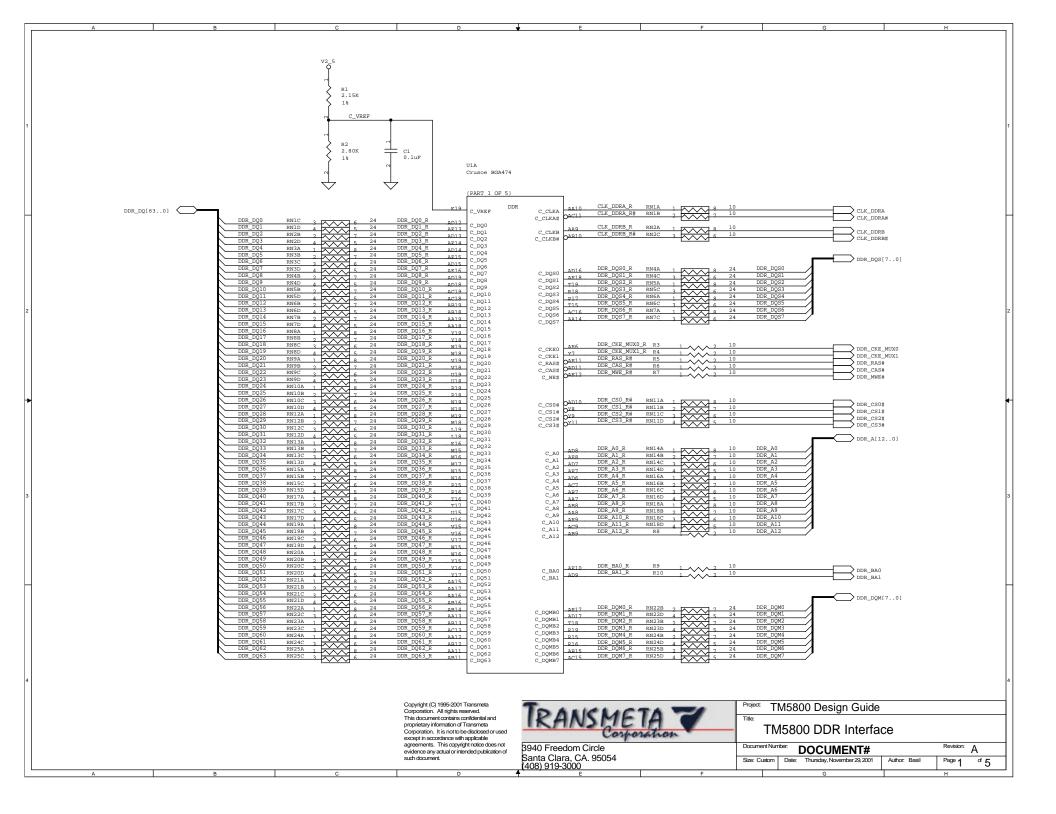

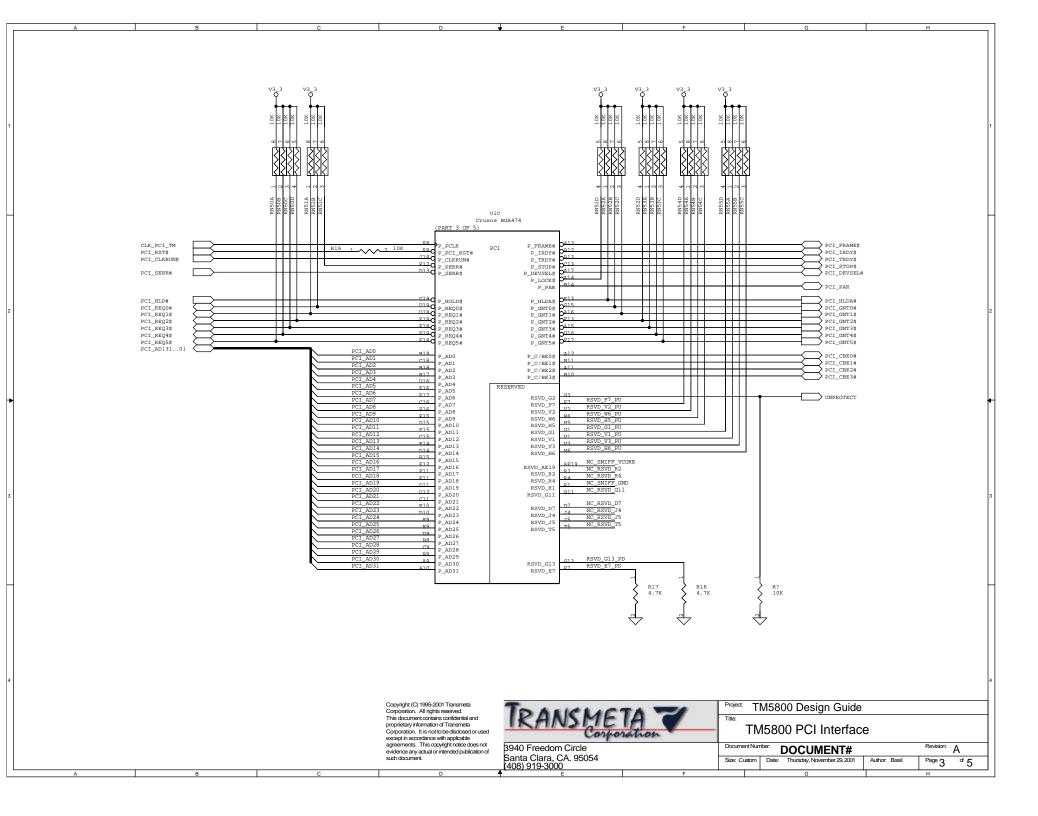

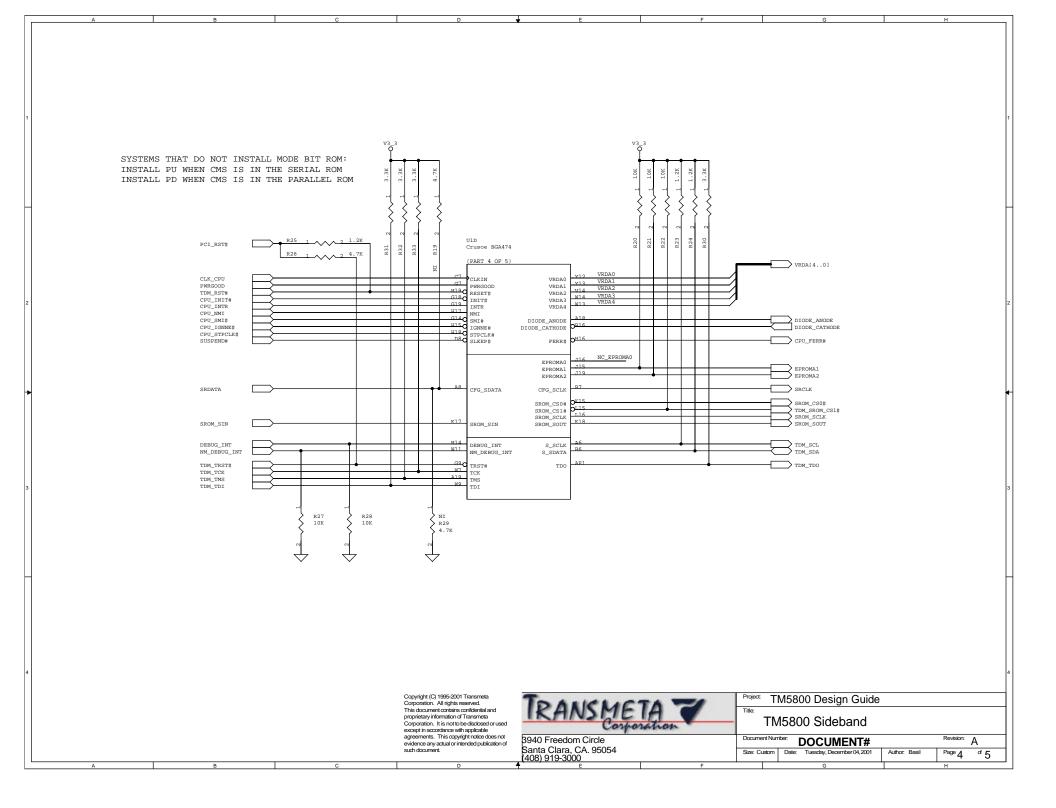

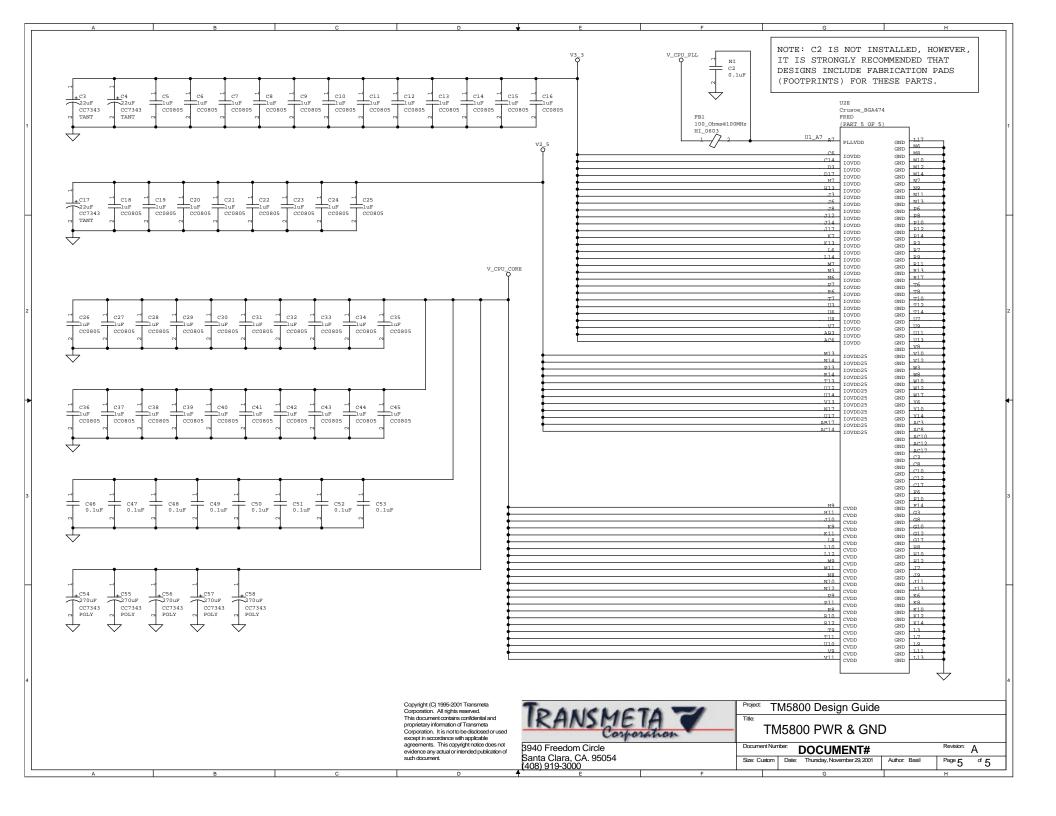

# **2.2** Processor Schematics

The following pages show TM5500/TM5800 processor reference schematics.

|              |               |                    |                            |                                          |              |                                                  | CDD OLVIN                         |                                                       |          |             |                              |        |

|--------------|---------------|--------------------|----------------------------|------------------------------------------|--------------|--------------------------------------------------|-----------------------------------|-------------------------------------------------------|----------|-------------|------------------------------|--------|

|              |               |                    |                            |                                          |              |                                                  | SDR_CLKIN                         |                                                       |          |             |                              |        |

|              |               |                    |                            | UlB                                      | oe BGA474    |                                                  |                                   |                                                       |          |             |                              |        |

|              |               |                    |                            |                                          |              |                                                  |                                   |                                                       |          |             |                              |        |

|              |               |                    |                            | (PAR                                     | 2T 2 OF 5)   |                                                  |                                   |                                                       |          |             |                              |        |

|              |               |                    |                            | -                                        | SDR SDR      | S_CLKOUT V6                                      | SDR_CLKOUT                        | 12                                                    | 33 PLAC  | E R11 CLOSE | TO SOURCE, PROCESSOR         | BALL V |

|              | →             | RN26A 8<br>RN26B 2 | 7 33                       | SDR_DQ0_R W5<br>SDR_DQ1_R AB4 S_D        |              |                                                  |                                   |                                                       |          |             |                              |        |

|              | ∠             | RN26C 3            | 6 33<br>5 33               | SDR_DQ2_R AB5 S_D<br>SDR_DQ3_R AB5 S_D   | Q2           | S_CLK0 M3                                        | CLK_SDR0_R<br>CLK_SDR1_R          | R12 1 2<br>R13 1 2                                    | 22       |             | CLK_SDR0                     |        |

| 2Q3          | ,             | RN27A 1<br>RN27B 2 | 8 33                       | SDR_DQ4_R v5 S_D                         |              | S_CLK1 M5<br>S_CLK2 M5                           | CLK_SDR2_R<br>CLK_SDR3_R          | R14 1 0 0 2                                           | 22       |             | CLK_SDR1<br>CLK_SDR2         |        |

|              | $\rightarrow$ | RN27C 3            | 6 33                       | SDR_DQ6_R AD3 S_D                        |              | S_CLK3 L4<br>S_CLK4 L5                           | NC_U1_L5<br>NC_U1_K3              |                                                       | 22       |             | CLK_SDR3                     |        |

|              | ⋧             | RN28A 1            | 8 33                       | SDR_DQ8_R AC2 S_D                        | Q7           | S_CLK5 K4                                        | NC_U1_K4                          | -                                                     |          |             |                              |        |

| 29 <b>(</b>  | ₹             | RN28C 3            | 7 33                       | SDR_DQ10_R AC1 S_D                       | Q9           | S_CLK7 K5                                        | NC_U1_K5                          | -                                                     |          |             |                              |        |

| bQ10         | ⋨             | RN28D 4            | 5 33                       |                                          | Q11          |                                                  |                                   |                                                       |          |             |                              |        |

| DQ12         | ∠             | RN29B 2<br>RN29C 3 | 7 33                       | SDR_DQ13_R V4 S_D<br>SDR_DQ14_R V2 S_D   | 0Q12<br>0Q13 |                                                  | SDR_CKE_MUX0_RRM                  | 29D 4 14 4 1 5                                        | 10       |             | _                            |        |

| 0Q14         | ,             | RN30A 1            | 8 33                       | SDR D015 R S_D                           | 0Q14<br>0Q15 | S_CKE0 J1<br>S_CKE1 J1                           | SDR_CKE_MUX1_RRM<br>SDR_RAS_R# RM | 30B 2 7                                               | 10       |             | SDR_CKE_MUX0<br>SDR_CKE_MUX1 |        |

| 0016<br>0017 | $\leftarrow$  | RN31A 8            | 1 33                       | SDR_DQ17_R G6 S D                        | Q16<br>0017  | S_RAS# OR5<br>S_CAS# OV4                         | SDR_CAS_R# RM                     | 31B 2 7                                               | 10       |             | SDR_RAS#                     |        |

| 0018         | →             | RN31C 3<br>RN32A 1 | 6 33<br>8 33               | SDR_DQ19_R SDR_DQ19_R R6 S_D             | Q18          | S_WE# 0P5                                        | SDR_MWE_R# RM                     | 31D 4 5                                               | 10       |             | SDR_MWE#                     |        |

| 0Q20 🧲       | ≍             | RN32B 2<br>RN32C 3 | 6 33                       | SDR_DQ21_R p5 S_D                        | Q20          |                                                  |                                   |                                                       |          |             |                              |        |

|              | ⇒             | RN32D 4            | 5 33                       | SDR_DQ22_R E5 S_D<br>SDR_DQ23_R D6 S_D   | 0Q21<br>0Q22 | -T/                                              | SDR_CS0_R# RM                     | 33B 2 6 6 6 7                                         | 10       |             | ~                            |        |

| 0023<br>0024 | ∠             | RN33C 3            | 6 33                       | SDR_DQ24_R S_D                           | 0Q23<br>0Q24 | s_cs0# 0 <del>14</del><br>s_cs1# 0 <del>13</del> | SDR_CS1_R# RM<br>SDR_CS2_R# RM    | 133D 4                                                | 10       |             | SDR_CS0#<br>SDR_CS1#         |        |

| 0Q25<br>0Q26 | ,             | RN34C 3            | 6 33                       | SDR_DQ26_R E3 S_D                        | Q25          | s_cs2# 0 <sup>T1</sup><br>s_cs3# 0 <sup>T2</sup> | SDR_CS3_R# RM                     | 134D 4 5                                              | 10       |             | SDR_CS2#<br>SDR_CS3#         |        |

|              | $\rightarrow$ | RN35A 8<br>RN35B 2 | 7 33                       | SDR_DQ28_R D4 S_D                        | Q27          |                                                  |                                   | <b>.</b>                                              |          | . <u></u>   |                              |        |

| 0029<br>0030 | ₹             | RN35C 3<br>RN35D 4 | 5 33                       | SDR_D029_R B5 S_D                        | Q29          |                                                  |                                   |                                                       |          |             |                              |        |

| DQ31 🧲       | ⇒             | DN260              |                            | SDR D032 R D06 S_D                       | Q31          | S_A0 P3                                          | SDR_A1_R RM                       | 36B 2 7                                               | 10       |             | SDR_A0                       |        |

|              | ≍=====        | RN37A 1            | 8 33                       | SDR_DQ33_R_AC5_S_D<br>SDR_D034_R_AC5_S_D |              | S_A1<br>S_A2 V5                                  | SDR_A2_R RM                       | (37B 2 7                                              | 10       |             | SDR_A1<br>SDR_A2             |        |

| DQ34         | ,             | RN38A 1            | 8 33                       | SDR DQ35 R AD4 S_D                       | Q34<br>Q35   | S_A3 N5                                          | SDR_A4_R RM                       | 138B 2 7                                              | 10       |             | SDR_A3<br>SDR_A4             |        |

| 0036         | $\leftarrow$  | RN39A 8            | 1 33                       | SDR DQ37 R ARE S_D                       | 0036<br>0037 | S_A5 P1                                          | SDR_A6_R RM                       | 139B 2 000 7                                          | 10       |             | SDR_A5<br>SDR_A6             |        |

|              |               | RN40A 1            | 8 33                       | SDR_DQ39_R AF2 S_D                       | Q38          | S_A7 N1                                          | SDR_A8_R RM                       | 140B 2 000 7                                          | 10       |             | SDR_A7<br>SDR_A8             |        |

| 0Q40 🗲       | ≍             | RN41A 8            | 1 33                       | SDR D041 R AB2 S_D                       | Q40          | S_A8 N2<br>S_A9 M2                               | SDR_A10_R RM                      | 41B 2 0 0 7                                           | 10       |             | SDR_A9                       |        |

| 0Q41         | ≠             | RN41C 3<br>RN42A 1 | 6 33                       | SDR_DQ42_R AA2 S_D<br>SDR_DQ43_R AA1 S_D | 0Q41<br>0Q42 | S_A10 K1<br>S_A11 K2                             | SDR_A11_R RM<br>SDR_A12_R RM      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 10       |             | SDR_A10<br>SDR_A11           |        |

| 0Q43         | ∠             | RN42C 3            | 6 33                       | SDR DQ44 R vo S_D                        | 0Q43<br>0Q44 | S_A12                                            |                                   |                                                       |          | L           | _> SDR_A12                   |        |

| 0Q45         | $\leftarrow$  | RN43A 1            | 8 33                       | SDR_DQ46_R w2 S D                        | 0Q45<br>0Q46 |                                                  |                                   |                                                       |          |             |                              |        |

| 0047<br>0048 | ₹             | RN43B 2<br>RN43C 3 | 7 33<br>6 33               | SDR_DQ48_R F1 S_D                        | Q47          |                                                  |                                   |                                                       |          |             |                              |        |

| 0Q49 🧲       | ≍             | RN43D 4            | 5 <u>33</u><br>7 <u>33</u> | SDR_DQ50_R F2 S_D                        | Q49          | S_BA0 I.1                                        | SDR_BA0_R RM<br>SDR_BA1_R RM      |                                                       | 10       |             | SDR_BA0                      |        |

| 0Q50         | ≍=====        | RN44D 4            | 5 33                       | SDR_DQ51_R D1 S_D<br>SDR DQ52 R P2 S_D   |              | S_BA1                                            |                                   |                                                       |          |             | _> SDR_BA1                   |        |

| 0Q52         | ,             | RN45B 2            | 7 33                       | SDR DQ53 R C1 S_D                        | 0Q52<br>0Q53 |                                                  |                                   |                                                       |          |             |                              |        |

| 0054<br>0055 | $\rightarrow$ | RN45D 4            | 5 33                       | SDR_DQ55_R C2 S_D                        | 0Q54<br>0Q55 |                                                  | CDD DOMO D                        | 460 -                                                 | 22       |             | _                            |        |

| 0056<br>0057 | ⋧             | RN46A 8<br>RN46C 3 | 6 33                       | SDR DQ57 R 32 S_D                        | Q56          | S_DQMB0 U1                                       | SDR_DQM0_R RM<br>SDR_DQM1_R RM    | 146D 4 6 6                                            | 33       |             | SDR_DQM0<br>SDR_DQM1         |        |

| Q58 🗲        | ₹             | RN47A 1<br>RN47C 3 | 8 33<br>6 33               | SDR DQ59 R 32 S_D                        |              | S_DQMB1 H4<br>S_DQMB2 H3                         | SDR_DQM2_R RM<br>SDR_DQM3_R RM    | 147D 4 4 4 4 5                                        | 33       |             | SDR_DQM2                     |        |

| 0Q59<br>0Q60 | ★             | RN48A 1            | 8 33                       | SDR_DQ60_R A4 S_D<br>SDR_DQ61_R P2 S_D   | Q60          | S_DQMB3<br>S_DQMB4                               | SDR_DQM4_R RM<br>SDR_DQM5_R RM    | 148B 2 7                                              | 33<br>33 |             | SDR_DQM3<br>SDR_DQM4         |        |

| Q61          | ,             | RN49A 1            | 8 33                       | SDR DQ62 R DO S_D                        | 0Q61<br>0Q62 | S_DQMB5 H2<br>S_DQMB6 H2                         | SDR_DQM6_R RM<br>SDR_DQM7_R RM    | 149B 2 7                                              | 33       |             | SDR_DQM5<br>SDR_DQM6         |        |

| 263 C        | →             | RN49C 3            |                            |                                          | Q63          | S_DQMB7 H1                                       | SDW_DÅW\_K BF                     | 490 4 5                                               | 33       |             | SDR_DQM7                     |        |

D

C

÷

F

Α

н

### Chapter 3

# Processor Power Supplies and Power Management

This section provides design guidelines for TM5500/TM5800 processor power supplies, power sequencing, and power management circuits. This section also describes processor power supply requirements that must be implemented.

See the *Data Book* for peak current and other power-related processor specifications. The current requirements of each supply should be calculated on a per-design basis.

#### Note

Follow the power supply sequencing requirements described in Power Supply Sequencing on page 35.

# 3.1 Power Supplies

The block diagram in Chapter 2, *System Block Diagram*, shows the power supplies for each of the major components. The power source for all notebook computers is either a battery (< 20 V) or a DC wall adapter of a comparable voltage. An intelligent switching mechanism is needed to create a stable V\_DC or V\_SOURCE that is used to supply the regulators that generate system voltages.

There are four power supplies required for TM5500/TM5800 processors:

- Core power supply (V\_CPU\_CORE)

- PLL power supply (V\_CPU\_PLL)

- 3.3 V I/O power supply (V3\_3)

- 2.5 V I/O power supply (V2\_5)

It is important to follow the design recommendations and meet the requirements provided below for TM5500/TM5800 power supply designs.

# **3.1.1** Core Power Supply Requirements

#### Note

See the Data Book for TM5500/TM5800 voltage and current requirements for this and all power supplies.

Information on low-range VRMs (voltage regulator modules), strongly recommended for new system designs, is available from qualified VRM vendors as indicated in this document.

#### Note

The only VRM qualified by Transmeta for TM5500/TM5800 processors is the Maxim MAX1718. Refer to the manufacturers VRM data sheet for detailed design information.

Care must be taken to assure the core power supply voltage, V\_CPU\_CORE, supplied to TM5500/TM5800 processors does not exceed the absolute maximum limit of 1.5 V when evaluating TM5500/TM5800 processor in systems designed for TM5400/TM5600 processors (designed to operate up to 1.6 V).

#### WARNING

CORE POWER SUPPLY VOLTAGE (V\_CPU\_CORE) TO TM5500/TM5800 PROCESSORS MUST NOT EXCEED 1.5 V OR PERMANENT DEVICE DAMAGE MAY RESULT.

The table below provides the most significant core power supply requirements for TM5500/TM5800 processors

#### Table 5: Core Power Supply Requirements for TM5500/TM5800 Processors

| Specification                                                       | Value                                                                                                    | Notes                                                                                                                                                           |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core voltage range                                                  | 0.95 - 1.30/1.35/1.40 V (nominal)                                                                        | See LongRun™ specifications                                                                                                                                     |

| Core voltage static regulation                                      | +/- 2% maximum at all voltage<br>settings, across all set points, line,<br>load and temperature          | Voltage tolerance for DC load<br>changes                                                                                                                        |

| Core voltage dynamic regulation                                     | +/- 5% maximum excursion;<br>return to within 1% of static<br>regulation band for a +/- 6 A load<br>step | Voltage tolerance for dynamic<br>current changes, i.e. short-term<br>voltage excursions that quickly<br>return to the static regulation band<br>described above |

| Core voltage recovery time                                          | 20 $\mu$ S maximum to return to within<br>1% of static regulation band for a<br>+/- 6 A load step        | Pulse width of voltage spikes                                                                                                                                   |

| Core voltage periodic and random deviation (PARD), including ripple | +/- 1% maximum                                                                                           | Includes other voltage changes<br>not included above                                                                                                            |

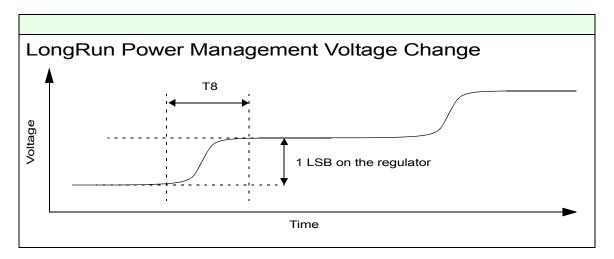

| Core voltage supply slew rate                                       | 4.0 mV/μS minimum                                                                                        | Minimum voltage change rate<br>required for LongRun™ power<br>management transitions                                                                            |

| Core supply current                                                 | 10.0 A maximum                                                                                           | For 1 GHz SKU                                                                                                                                                   |

| VRM voltage control mode                                            | Remote sense operation                                                                                   | Using processor core voltage<br>feedback signal (SNIFF_CVDD),<br>processor ball number AE19                                                                     |

| Specification                                             | Value                                                 | Notes                        |

|-----------------------------------------------------------|-------------------------------------------------------|------------------------------|

| Source voltage                                            | 10.0 V minimum                                        | Required for this particular |

| Combined ESR of bulk capacitors                           | 5 mΩ maximum                                          | reference design to meet     |

| Combined capacitance of bulk capacitors                   | 800 μF minimum (nominal)<br>1100 μF maximum (nominal) | specifications above         |

| Distribution resistance from bulk capacitors to processor | $2 \text{ m}\Omega$ maximum                           | -                            |

| Inductor inductance                                       | 1.8 μH nominal<br>2.2 μH maximum                      |                              |

| Inductor RMS current                                      | 14 A minimum                                          |                              |

| Inductor saturation current                               | 20 A minimum                                          | 1                            |

#### Table 5: Core Power Supply Requirements for TM5500/TM5800 Processors (Continued)

# 3.1.1.1 Default Power-on VRDA (VRM VID) Output Codes

TM5500/TM5800 processors have a default power-on VRDA code of 0x0E. This code corresponds to 1.050 V output for a Maxim MAX1718 VRM.

The table below shows the default power-on VRDA code values for TM5x00 processors.

Table 6: Default Power-on Start Voltage VRDA (VID) Output Codes

|                 | VID/VRDA Value |             |             |             |             | Default Startup Voltage |            |

|-----------------|----------------|-------------|-------------|-------------|-------------|-------------------------|------------|

| Processor Model | VRDA<br>[4]    | VRDA<br>[3] | VRDA<br>[2] | VRDA<br>[1] | VRDA<br>[0] | Hex                     | VRM Output |

| TM5500/TM5800   | 0              | 1           | 1           | 1           | 0           | 0x0E                    | 1.05 V     |

| TM5400/TM5600   | 0              | 1           | 0           | 1           | 0           | 0x0A                    | 1.25 V     |

# 3.1.1.2 VID/VRDA Code Table

The VID/VRDA codes for the Maxim MAX1718 VRM are shown in the table below.

#### Table 7: VID/VRDA Values and Output Voltages for MAX1718 VRM

| VID/VRDA Value |          |          |          |          |      |            |

|----------------|----------|----------|----------|----------|------|------------|

| VRDA [4]       | VRDA [3] | VRDA [2] | VRDA [1] | VRDA [0] | Hex  | VRM Output |

| 0              | 0        | 0        | 0        | 0        | 0x00 | 1.75 V     |

| 0              | 0        | 0        | 0        | 1        | 0x01 | 1.70 V     |

| 0              | 0        | 0        | 1        | 0        | 0x02 | 1.65 V     |

| 0              | 0        | 0        | 1        | 1        | 0x03 | 1.60 V     |

| 0              | 0        | 1        | 0        | 0        | 0x04 | 1.55 V     |

| 0              | 0        | 1        | 0        | 1        | 0x05 | 1.50 V     |

| 0              | 0        | 1        | 1        | 0        | 0x06 | 1.45 V     |

| 0              | 0        | 1        | 1        | 1        | 0x07 | 1.40 V     |

| 0              | 1        | 0        | 0        | 0        | 0x08 | 1.35 V     |

| 0              | 1        | 0        | 0        | 1        | 0x09 | 1.30 V     |

| 0              | 1        | 0        | 1        | 0        | 0x0A | 1.25 V     |

| 0              | 1        | 0        | 1        | 1        | 0x0B | 1.20 V     |

| 0              | 1        | 1        | 0        | 0        | 0x0C | 1.15 V     |

| 0              | 1        | 1        | 0        | 1        | 0x0D | 1.10 V     |

| 0              | 1        | 1        | 1        | 0        | 0x0E | 1.05 V     |

| 0              | 1        | 1        | 1        | 1        | 0x0F | 1.00 V     |

| 1              | 0        | 0        | 0        | 0        | 0x10 | 0.975 V    |

| 1              | 0        | 0        | 0        | 1        | 0x11 | 0.950 V    |

| 1              | 0        | 0        | 1        | 0        | 0x12 | 0.925 V    |

| 1              | 0        | 0        | 1        | 1        | 0x13 | 0.900 V    |

| 1              | 0        | 1        | 0        | 0        | 0x14 | 0.875 V    |

| 1              | 0        | 1        | 0        | 1        | 0x15 | 0.850 V    |

| 1              | 0        | 1        | 1        | 0        | 0x16 | 0.825 V    |

| 1              | 0        | 1        | 1        | 1        | 0x17 | 0.800 V    |

| 1              | 1        | 0        | 0        | 0        | 0x18 | 0.775 V    |

| 1              | 1        | 0        | 0        | 1        | 0x19 | 0.750 V    |

| 1              | 1        | 0        | 1        | 0        | 0x1A | 0.725 V    |

| 1              | 1        | 0        | 1        | 1        | 0x1B | 0.700 V    |

| 1              | 1        | 1        | 0        | 0        | 0x1C | 0.675 V    |

| 1              | 1        | 1        | 0        | 1        | 0x1D | 0.650 V    |

| 1              | 1        | 1        | 1        | 0        | 0x1E | 0.625 V    |

| 1              | 1        | 1        | 1        | 1        | 0x1F | 0.600 V    |

|                |          |          |          |          |      |            |

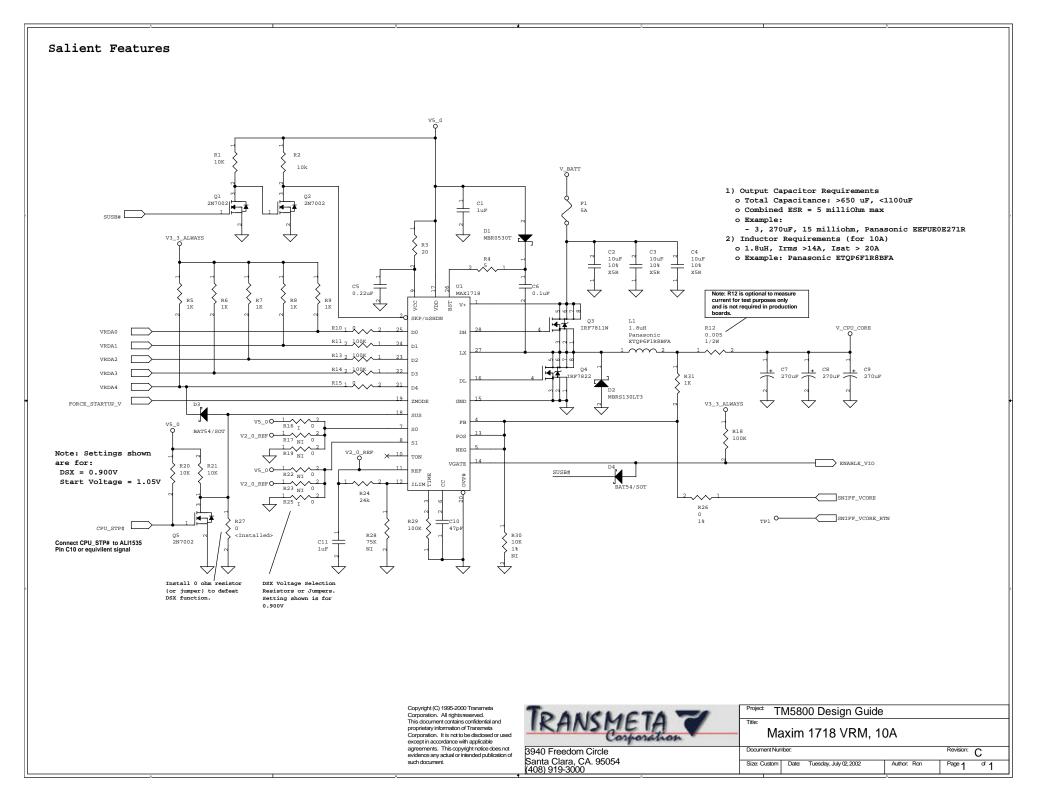

# 3.1.2 VRM Core Power Supply Example

The sections below provide an example core power supply design using the Maxim MAX1718 VRM. This reference design is recommended by Transmeta for TM5500/TM5800 processor-based system designs.

#### Note

Vendor part-specific information provided in this *System Design Guide* may be incorrect or out of date. Please consult with the manufacturer for the latest specifications and design information for the VRM and related components used in the design.

## 3.1.2.1 Maxim MAX1718 Regulator

Maxim provides a VRM that is well-suited for TM5500/TM5800 core power supply designs. This VRM is described below. A reference design, adapted from example circuits in the Maxim MAX1718 data sheet, is provided at the end of this section. Detailed design information for the MAX1718 low-range VRM is available from Maxim in the MAX1718 data sheet, and should be referenced whenever possible.

## 3.1.2.2 Output Voltage Control

The MAX1718 has three different methods that can be used to program the output voltage by means of three internal resisters:

- Normal Operating Mode voltage is determined by the logic levels of the VID inputs.

- Startup Mode voltage is determined by series resistors connected to the VID inputs.

- Deep Sleep Extension (DSX) Mode voltage is determined by the logic levels on the S0 and S1 inputs.

Which of the three methods is used to control the output voltage is determined by the ZMODE and SUS input signals. These inputs control internal multiplexers that select which register is presented to the DAC to set the output voltage. When high, the SUS input overrides the ZMODE input, forcing the output voltage to the DSX value. The table below describes this selection logic.

Table 8: MAX1718 Core Power Supply Output Control Selector

| Core Power Supply                  | Output Voltage           | Control Signal |      |          |  |

|------------------------------------|--------------------------|----------------|------|----------|--|

| Operating Mode                     | Determined By            | ZMODE          | SUS  | CPU_STP# |  |

| Normal Operating Mode <sup>1</sup> | Logic level of D0-D4     | Low            | Low  | High     |  |

| Startup Mode                       | Impedance of D0-D4       | High           | Low  | High     |  |

| DSX Mode                           | Logic level of S0 and S1 | Don't care     | High | Low      |  |

1. Used for LongRun power management.

### Normal Operating Mode

Normal operating mode output voltage is programmed directly by the five VID input signals according to Table 7. There are no internal VID pull-ups to 5 V in the MAX1718 (as there were in the MAX1711), so there is no need for a quickswitch to protect the processor VRDA outputs from the VRM VID inputs. However, because there are no internal pull-ups, external pull-up resistors are required.

## Startup Mode

Startup mode is selected when the ZMODE signal is high. In this mode the output voltage is determined by the internal impedance mode resister whose value is set on the rising edge of the ZMODE signal. The device looks at the impedance on the VID inputs. If it is > 90 K $\Omega$  it is considered a logic high, and if it is < 1.1 K $\Omega$  it is considered a logic low. This process is initiated by the rising edge of the ZMODE signal. During this time the device tries to move its VID inputs by alternately trying to pull the VID inputs high with a pull-up resistor to 5 V, and low through a pull-down resistor to ground. This happens over the period of a few  $\mu$ S. To make the VID input a logic 1 (high), insert a 100 K $\Omega$  resistor in series with the VID input. To make the VID input a logic 0 (low), make the series resistor zero  $\Omega$ . In addition to the series resistors, a pull-up resistor of 1 K $\Omega$  must be added to each VID input. If pull-up resistor to keep the AC impedance < 1 K $\Omega$ .

## Deep Sleep Extension (DSX) Mode

#### Note

Although this feature is incorporated in the MAX1718 VRM, it is not yet qualified for the TM5500/TM5800 processor.

The MAX1718 VRM supports a Deep Sleep extension (DSX) mode that can provide a very low output voltage to the TM5500/TM5800 processor core during extended Deep Sleep periods, significantly reducing processor leakage power during long intervals of sustained system inactivity. The reference design example provided at the end of this section shows the DSX mode configured for 0.9 V operation. This can be reconfigured to a lower TM5500/TM5800 DSX voltage specification when it becomes available. See Table 9 for DSX voltage programming information.

Driving the SUS signal high overrides the ZMODE control and sets the output voltage to one of thirteen preset values between 0.600 V and 0.900 V, depending on the state of the S0 and S1 inputs. The S0 and S1 inputs are each effectively quad-state / four-level logic, and can be set by connecting them to either the VRM VCC (+5 V), REF, or GND signals, or leaving the input open. Since each input has four states and there are two inputs, there are  $2^4 = 16$  possible combinations, of which only thirteen are used here.

The table below provides DSX mode output voltage configuration information for the full range of DSX voltages.

| DSX Voltage | SO   | S1   |

|-------------|------|------|

| 0.900 V     | VCC  | GND  |

| 0.875 V     | GND  | REF  |

| 0.850 V     | REF  | REF  |

| 0.825 V     | OPEN | REF  |

| 0.800 V     | VCC  | REF  |

| 0.775 V     | GND  | OPEN |

| 0.750 V     | REF  | OPEN |

| 0.725 V     | OPEN | OPEN |

| 0.700 V     | VCC  | OPEN |

| 0.675 V     | GND  | VCC  |

| 0.650 V     | REF  | VCC  |

| 0.625 V     | OPEN | VCC  |

| 0.600 V     | VCC  | VCC  |

#### Table 9: MAX1718 DSX Voltage Configuration

## 3.1.2.3 Current Limit Adjustment (ILIM)

Resistors in the example circuit are used to adjust the output current limit. The values are selected based on the maximum VRM current and the RDS<sub>on</sub> of the lower switching FET being used. See the MAX1718 data sheet for detailed information on adjusting the output current limit.

# 3.1.2.4 Output Voltage Offset Control (POS, NEG)

The MAX1718 has a provision to adjust the output voltage a little higher or lower than the programmed value. This is accomplished by means of a differential input amplifier that adds an offset voltage to the programmed value. Since voltage positioning is used in the reference design example, the output will droop below the set value by a negative tolerance. The output voltage offset control feature is used to shift the output voltage up to yield the required +5%, -2% output voltage tolerance.

The actual output offset voltage is the voltage applied between the POS and NEG inputs multiplied by a variable factor that depends on the output voltage, which in the reference design example is approximately 0.85. See the MAX1718 data sheet for detailed information on adjusting the output voltage offset.

# 3.1.2.5 Switching Frequency/On-time Selection Control (TON)

#### Note

The MAX1718 VRM has only been tested for TM5500/TM5800 designs at 300 KHz operation.

The VRM switching frequency is selected by means of the TON input. The reference design example shows the MAX1718 configured for 300 KHz operation. The MAX1718 has been tested to operate at 300 KHz only.

# 3.1.2.6 Output Voltage Slew-rate Adjustment (TIME)

The resistor connected to the TIME input on the device ( $R_{TIME}$ ) is used to set the slew-rate of the output voltage change when transitioning between programmed output values (see MAX1718 data sheet for details). The recommended range for  $R_{TIME}$  is 47 K $\Omega$  for a 380 KHz slew-rate clock to 470 K $\Omega$  for a 38 KHz slew-rate clock. Slew-rate clock frequency = 150 KHz x (120K /  $R_{TIME}$ ). The slew rate given by:

$$\frac{dV}{dT} = \frac{450}{R_{TIME}}$$

The slew rate is in mV per  $\mu S$  and the resistor,  $R_{TIME},$  is in K\Omega.

# 3.1.2.7 DH Pull-up Current/Turn-on Time Adjustment (BST)

A resistor connected to the BST input in the reference design example is used when necessary to slow down the turn-on time of the upper FET to minimize ringing.

# 3.1.2.8 VRM Shutdown Control (SKP/SDN#)

When the SKP/SDN# input is low, the VRM is shut down. When this signal is pulled high to VCC, the VRM operates in skip mode. When this signal is left floating, the VRM operates in PWM mode. The reference design example operates in skip mode to take advantage of the high efficiency of skip mode at low currents.

# 3.1.2.9 POWERGOOD Status (VGATE)

VGATE is an open-drain output which is high (floating) when the output voltage is in regulation. This output thus indicates a POWERGOOD status, and is used during power-up in the reference design example to enable the processor I/O power supplies (V3\_3\_STR and V2\_5\_STR) to begin ramping up, as required by TM5500/TM5800 power sequencing specifications. VGATE has an internal sense circuit to force it high during programmed transitions such as normal LongRun voltage step transitions, without the need for an external deglitching circuit.

# 3.1.2.10 Voltage Positioning

TM5500/TM5800 processors should not be used with voltage positioning core power supplies. The MAX1718 VRM in this reference design is configured for remote sense operation.

# 3.1.2.11 MAX1718 Core Supply Reference Design Schematic

A MAX1718 core power supply reference design schematic, recommended for TM5500/TM5800 processors, is provided on the following page.

Note that the output from this reference design power supply is labeled V\_CPU\_CORE. This output is connected to the processor core supply (CVDD) balls. The SNIFF\_VCORE voltage sense signal in the reference design is connected to the processor SNIFF\_CVDD signal (ball number AE19).

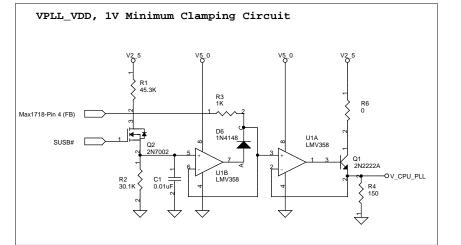

# 3.1.3 PLL Power Supply

#### Note

See the Data Book for the voltage and current requirements for this and all power supplies.

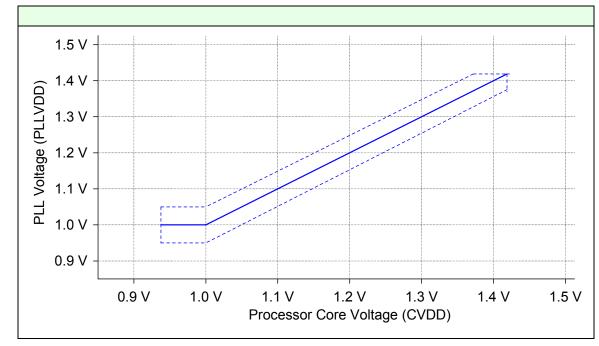

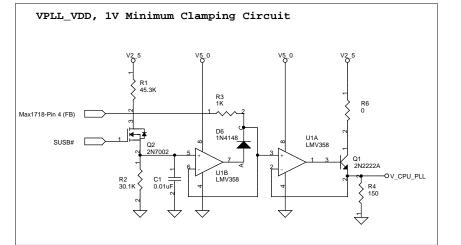

For new system designs, V\_CPU\_PLL for TM5500/TM5800 processors must track the core voltage from the maximum V\_CPU\_CORE value down to 1.0 V. The lower bound for V\_CPU\_PLL is 1.0 V. As the core voltage drops below 1.0 V, V\_CPU\_PLL must remain at 1.0 V.

V\_CPU\_PLL should be routed on the same side of the PCB that the processor is mounted on.

# 3.1.3.1 PLL Supply Core Voltage Tracking Requirement

V\_CPU\_PLL must track the core supply voltage, V\_CPU\_CORE, within  $\pm$  50 mV across a nominal core operating voltage range of 1.0 V to 1.3 V, while staying within the minimum/maximum voltage limits of each supply. V\_CPU\_PLL must remain at 1.0 V  $\pm$  50 mV across a nominal core operating voltage range of 0.9 V to 1.0 V.

For transitions in the core voltage (e.g. during LongRun power management voltage steps), V\_CPU\_PLL must settle to within the ± 50 mV V\_CPU\_CORE voltage tracking specification within ± 25  $\mu$ S.

The figure below graphically shows the TM5500/TM5800 processor PLL power supply tracking requirement.

#### Figure 3: PLL / Processor Core Voltage Tracking Requirement

## 3.1.3.2 PLL Power Supply Example

A PLL power supply design example is provided below that meets the requirements shown above, providing proper V\_CPU\_PLL vs. V\_CPU\_CORE tracking. The circuit includes an enable switch, output buffer, and a low-pass noise filter.

NOTE:

Use either Voltage Sequence, Option 1 or Option 2, to generate the "FORCE\_STARTUP\_V" signal. Do not use both.

such document.

## Example PLL Power Supply Circuit Description

R1/Q2 and R2 form a voltage divider to create a 1.0 V reference for the minimum V\_CPU\_PLL operating voltage. A high on START\_SEQ (typically connected to the POWERGOOD output of the V\_CPU\_CORE regulator) turns on the PLL supply via FET Q2. U1A and Q1 are connected as a unity-gain voltage follower so that V\_CPU\_PLL will equal the positive input of the opamp U1A at pin 3. U1A pin 3 is then connected to V\_CPU\_CORE through resistor R3. The purpose of R3 is to separate the U1A input node from V\_CPU\_CORE. The circuit described so far is an accurate voltage follower, where V\_CPU\_PLL tracks V\_CPU\_CORE. U1B is also connected as a voltage follower for the 1.0 V reference circuit, and D6 allows U1B to take control of the loop if V\_CPU\_PLL goes below 1.0 V. R4 provides a load for the U1A-Q1 follower and C2 provides a pole for the follower amp. The PLL power supply circuit should be located as close to the processor V\_CPU\_PLL pin as possible, and the V\_CPU\_PLL/GND loop length should be minimized.

## **Circuit Operation**

During operation, the V5\_0 (5.0 V) supply to the opamp and V2\_5 (2.5 V) supply to Q1 must be on whenever the processor core voltage (V\_CPU\_CORE) is on. Normal circuit operation is as follows:

**Operation above 1.0 V**: U1A regulates the V\_CPU\_PLL output to the voltage on its positive input (pin 3). If V\_CPU\_CORE is higher than 1.0 V, then V\_CPU\_PLL follows it. This makes the negative input of U1B (pin 6) greater than the 1.0 V reference on its positive input (pin 5), driving its output (pin 7) low. When pin 7 goes low it back-biases D6, disconnecting the U1B output from the U1A positive input and allowing V\_CPU\_PLL to track V\_CPU\_CORE.

**Operation below 1.0 V**: When V\_CPU\_CORE goes below 1.0 V, V\_CPU\_PLL attempts to track it, causing the negative input (pin 6) of U1B to fall below the 1.0 V reference on the U1B positive input (pin 5). This in turn causes the U1B output (pin 7) to increase, which forward biases D6 and allows it to take control of the loop. U1B now regulates V\_CPU\_PLL to its 1.0 V reference value as long as V\_CPU\_CORE is below the 1.0 V reference.

# 3.1.3.3 PLL Voltage Requirement in New and Existing Designs

### New System Designs

#### Note

Do not connect V\_CPU\_PLL to the processor core power supply (V\_CPU\_CORE), as was allowed for TM5400/TM5600 processors.

For new system designs, follow the new PLL voltage requirements specified above. Do not tie V\_CPU\_PLL to the processor core power supply (V\_CPU\_CORE), as was allowed with TM5400/TM5600 processors. Applications that violate the PLL voltage tracking specification are not guaranteed.

## Existing (TM5400/TM5600) System Designs

For existing TM5400/TM5600 processor-based system designs, V\_CPU\_PLL can be tied to V\_CPU\_CORE, but this will limit the low voltage range for the processor core power supply (V\_CPU\_CORE). Applications that violate the PLL voltage tracking specification are not guaranteed.

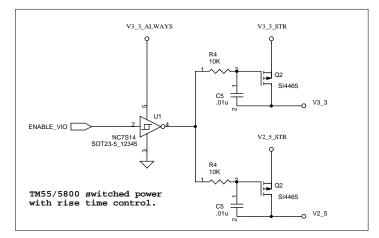

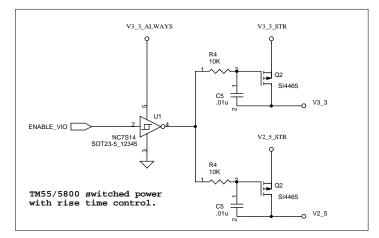

# 3.1.4 I/O Power Supplies

TM5500/TM5800 processors require a 3.3 V power supply (V3\_3) and a 2.5 V power supply (V2\_5) to power the I/O sections of the processor. If these supplies are derived from V3\_3\_STR and V2\_5\_STR, care must be taken to ensure the voltages are not glitched when these supplies are turned on. Glitching can be minimized by controlling the turn-on rise-time of the V3\_3 and V2\_5 supplies.

#### Note

See the Data Book for the voltage and current requirements for this and all power supplies.

#### Note

Power supply sequencing recommendations provided in *Power Supply Sequencing* on page 35 must be followed.

# 3.1.5 Decoupling Capacitors

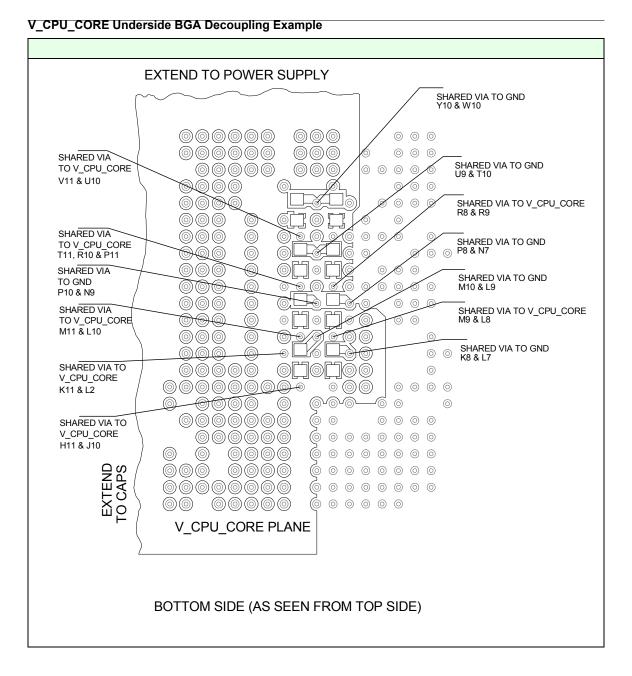

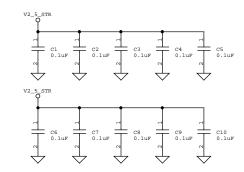

V\_CPU\_CORE decoupling capacitors (8 x 0.1  $\mu$ F X7R 0603) should be placed directly underneath the processor on the opposite PCB side (shown below). The V\_CPU\_CORE plane shown in the diagram below should extend significantly beyond the processor for connection to other peripheral decoupling capacitors.

# 3.2 Power Supply Sequencing

#### Note

See the *Data Book* for more information on power sequencing requirements for TM5500/TM5800 processors.

# **3.2.1** Power Sequencing Requirements

In order to prevent a high startup current condition on the processor I/O power supplies, it is required that the processor core power supply (V\_CPU\_CORE) be turned on first and reach a level of V\_CPU\_CORE\_MIN or greater, prior to applying the processor 2.5 V and 3.3 V I/O voltages (V2\_5 and V3\_3, respectively). After V\_CPU\_CORE has reached V\_CPU\_CORE\_MIN or greater, V3\_3 and V2\_5 can be supplied to the processor in any order.

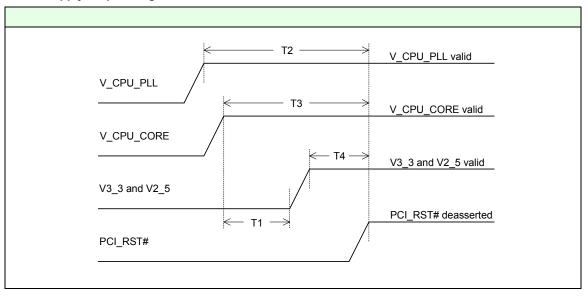

A diagram of the power supply sequencing required for TM5500/TM5800 processors is shown in the figure below. System designs for TM5500/TM5800 processors must also meet the power-on requirements specified in the *Data Book*.

Figure 4: Power Supply Sequencing

The table below provides timing specifications for the power supply sequencing figure above.

#### Table 10: Power Supply Sequencing Timing Specifications

| Timing<br>Value | Description                                                   | Min   | Max   |

|-----------------|---------------------------------------------------------------|-------|-------|

| T1              | Time from V_CPU_CORE valid to beginning ramp of V3_3 and V2_5 | 0 mS  | 50 mS |

| T2              | Time from V_CPU_PLL valid to PCI_RST# deassertion             | 20 mS | -     |

| Т3              | Time from V_CPU_CORE valid to PCI_RST# deassertion            | 20 mS | -     |

| T4              | Time from V3_3 and V2_5 valid to PCI_RST# deassertion         | 1 mS  | -     |

Under the above startup conditions the processor VDRA signals (that go to the VRM VID inputs) are not valid until the processor I/O voltages are present. Therefore, another method must be provided to supply valid VID signals to the VRM from the time the V\_CPU\_CORE core supply is enabled to the time the processor I/O voltages are within specifications. Once the processor I/O voltages are valid, the processor-suppled VDRA signals are valid and can be used to control the V\_CPU\_CORE core supply voltage.

When using TM5500/TM5800 processors with existing TM5400/TM5600 system designs, the existing power supply sequencing should not be used unless it meets the TM5500/TM5800 sequencing requirements described above, due to the likelihood for current surges on the I/O power supplies if the I/O voltages are applied to the processor prior to the V\_CPU\_CORE core supply reaching V\_CPU\_CORE<sub>MIN</sub>.

With the previously recommended TM5400/TM5600 power supply circuit, a high current on the I/O power supply circuits has been observed for about 3-10 ms, and its magnitude can be up to the current limit of the particular 3.3 V or 2.5 V regulator used (testing has shown up to 3.5 A). The excess current is not due to I/O contention, but rather current flow through the power supply pins of the processor.

This could possibly have the following negative effects for the system:

- DDR SDRAM data corruption when exiting STR (suspend-to-RAM).

- The 2.5 V or 3.3 V regulator may go into under-voltage shutdown or over-current protection, in which case system operation may only be recoverable if power-cycled.

- The 2.5 V or 3.3 V supply voltage may dip enough to cause memory corruption and power supply latchoff.

- The current spike may trigger other system-level protection circuits or result in I/O contention.

# 3.2.2 Power Sequencing Circuit Examples

As explained above in *Power Sequencing Requirements* on page 35, TM5500/TM5800 processors must have the core voltage (V\_CPU\_CORE) turned on prior to the I/O voltages (V3\_3 and V2\_5). However, the processor VRDA output code presented to the VRM VID inputs is not valid until the I/O voltages reach regulation. The processor core VRM must rely on another method for setting the VRM output voltage during processor power-up.

The fundamental requirement is to force the processor core VRM to a fixed startup supply voltage by a means other than the VID inputs, and then use the VRDA outputs from the processor to control the core VRM output only when these VRDA signals are valid.

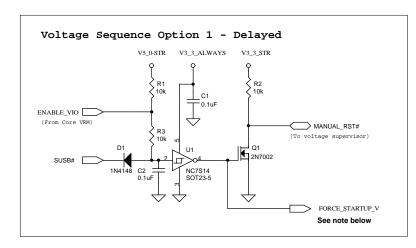

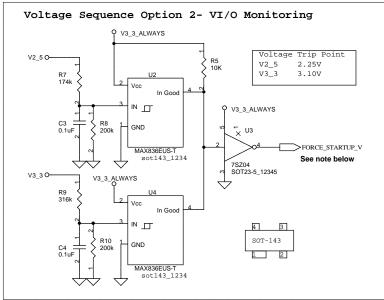

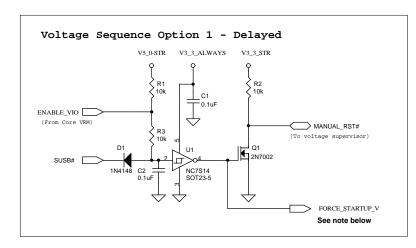

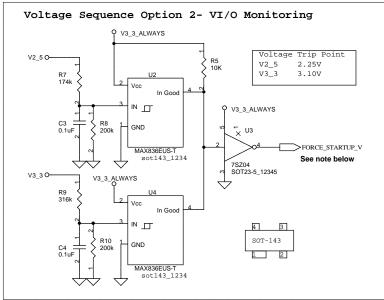

The processor core VRM designs shown in this document each have the ability to force the startup supply voltage (FORCE\_STARTUP\_V) without having a valid VID input code available from the processor. Two methods for using this capability are provided in the power supply sequencing reference design schematics below. Only one method is necessary for any system design, at the option of the designer. These two methods are described below:

**Method 1 (Delay):** This method uses a delay to drive the FORCE\_STARTUP\_V signal long enough for the I/O voltages to reach regulation. The advantage of this solution is lower cost and fewer components than Method 2.

**Method 2 (Monitor):** This method measures the I/O voltages to insure they are in regulation before releasing the FORCE\_STARTUP\_V signal. The advantage of this method over Method 1 is that it relies on actual voltage levels for control and is not susceptible to potential delay timing variability issues.

## Power Supply Sequencing Reference Design Schematic

Two possible power supply sequencing circuits, as described above, are shown in the reference design schematic on the following page.

NOTE:

Use either Voltage Sequence, Option 1 or Option 2, to generate the "FORCE\_STARTUP\_V" signal. Do not use both.

such document.

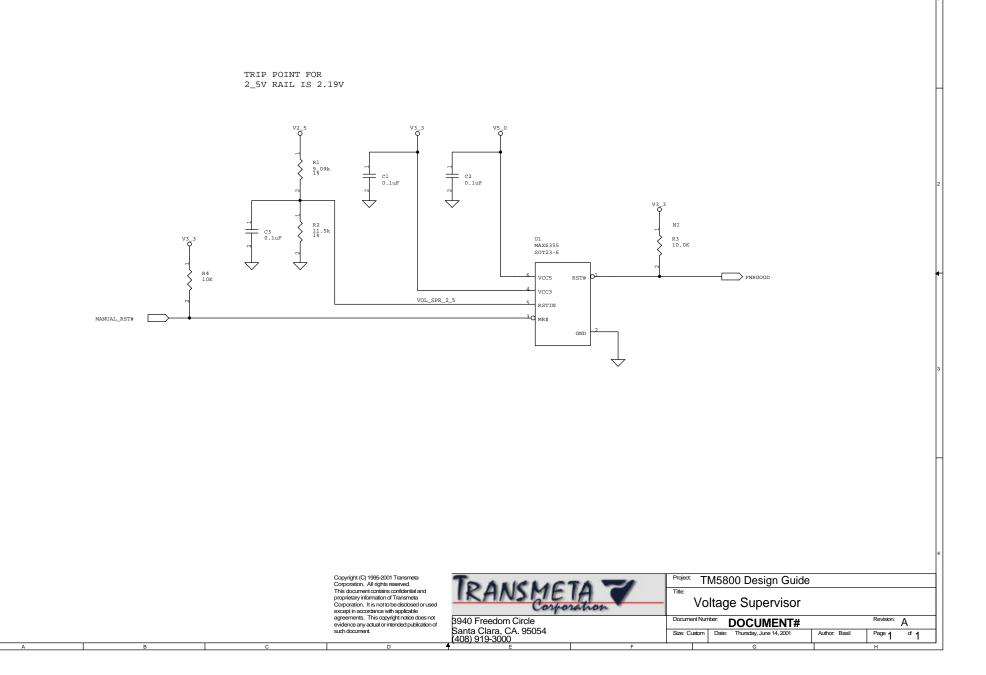

# 3.3 Power Supply Voltage Supervisor

The following page shows a power supply voltage supervisor reference design schematic.

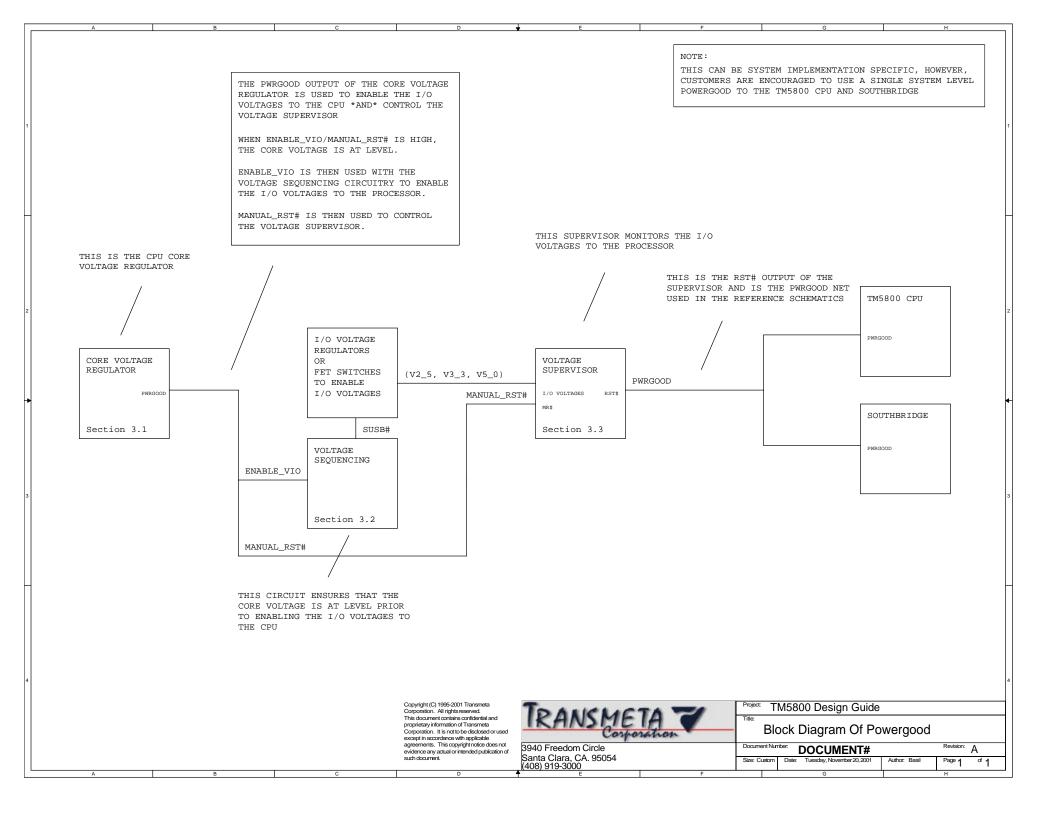

# 3.4 POWERGOOD Block Diagram Example

The following page shows an example block diagram for possible system POWERGOOD circuits.

# **3.5** State Transition Timing Requirements

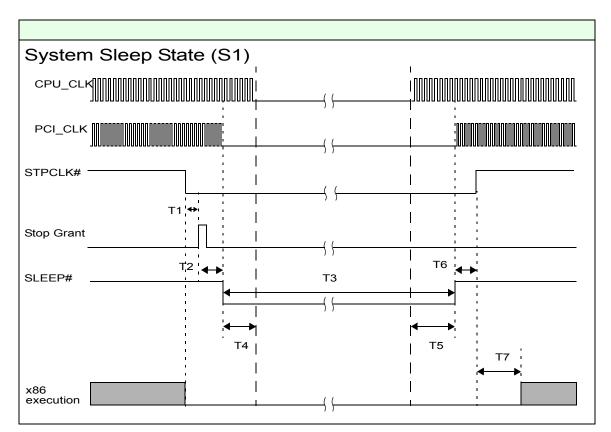

This section describes the state transition timing requirements for TM5500/TM5800 processors. Note that the various signal names used in this document are typically written from the perspective of the processor. For example, STPCLK# and SLEEP# refer to the processor input signals for Stop Clock and Sleep.

### ACPI Active State (CO)

The details of the TM5500/TM5800 processor power-on sequence are described in the *Data Book* and associated references. Only the timing diagram and critical latencies for the power-on sequence are provided here.

| Parameter              | Description                                                | Min       | Max    | Diagram Note |

|------------------------|------------------------------------------------------------|-----------|--------|--------------|

| t <sub>vdd_rise</sub>  | Supply delay and rise time <sup>1</sup>                    | -         | 250 mS | T1           |

| t <sub>vdd_pg</sub>    | POWERGOOD asserted after supplies reach 95% of final value | 0 S       | -      | T2           |

| t <sub>vdd_prst</sub>  | Supplies stable prior to PCI_RST# deasserted               | 1 mS      | -      | T3           |

| t <sub>pclk_prst</sub> | PCI_CLK stable prior to PCI_RST# deasserted                | 100 µS    | -      | T4           |

| t <sub>clk_prst</sub>  | CLKIN stable prior to PCI_RST#<br>deasserted               | 1 mS      | -      | T5           |

| t <sub>prst_rst</sub>  | PCI_RST# deasserted to RESET# deasserted                   | 0 S       | -      | T6           |

| t <sub>pg_rst</sub>    | POWERGOOD asserted to RESET#,<br>PCI_RST# deasserted       | 1 mS      | -      | T7           |

| t <sub>pg_low</sub>    | POWERGOOD inactive pulse width                             | 10 CLKINs | -      | not shown    |