TMS 9980A/ TMS 9981

#### 1. INTRODUCTION

#### 1.1 DESCRIPTION

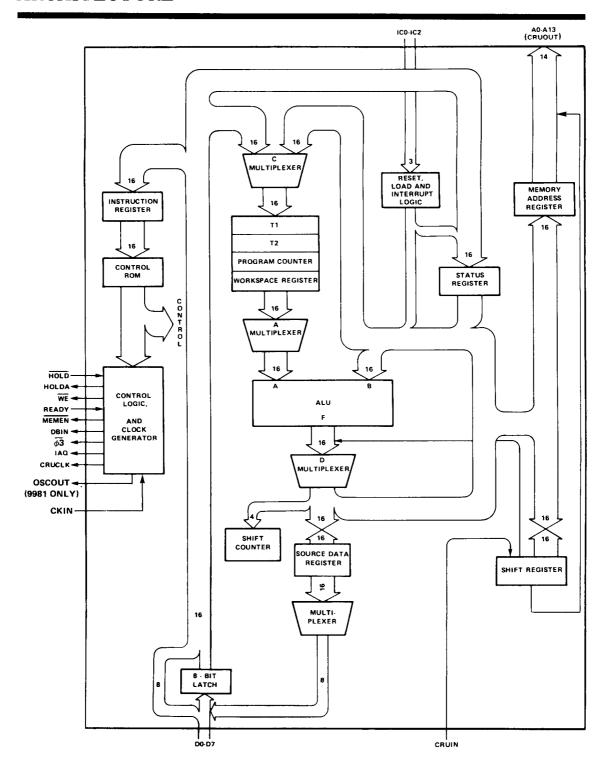

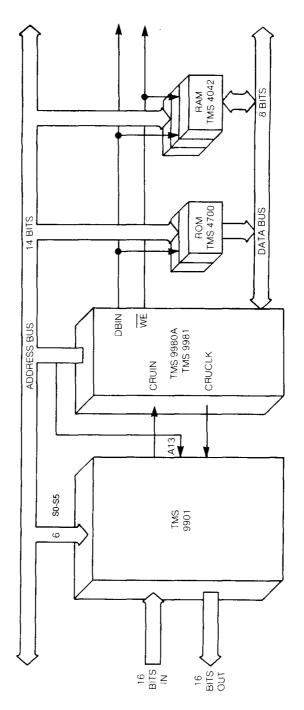

The TMS 9980A/TMS 9981 is a software-compatible member of TI's 9900 family of microprocessors. Designed to minimize the system cost for smaller systems, the TMS 9980A/TMS 9981 is a single-chip 16-bit central processing unit (CPU) which has an 8-bit data bus, on-chip clock, and is packaged in a 40-pin package (see Figure 1). The instruction set of the TMS 9980A/TMS 9981 includes the capabilities offered by full minicomputers and is exactly the same as the 9900's. The unique memory-to-memory architecture features multiple register files, resident in memory, which allow faster response to interrupts and increased programming flexibility. The separate bus structure simplifies the system design effort. Texas Instruments provides a compatible set of MOS and TTL memory and logic function circuits to be used with a TMS 9980A/TMS 9981 system.

#### 1.2 KEY FEATURES

- 16-Bit Instruction Word

- Full Minicomputer Instruction Set Capability Including Multiply and Divide

- Up to 16,384 Bytes of Memory

- 8-Bit Memory Data Bus

- Advanced Memory-to-Memory Architecture

- Separate Memory, I/O, and Interrupt-Bus Structures

- 16 General Registers

- 4 Prioritized Interrupts

- Programmed and DMA I/O Capability

- On-Chip 4-Phase Clock Generator

- 40-Pin Package

- N-Channel Silicon-Gate Technology

#### 1.3 TMS 9980A/TMS 9981 DIFFERENCES

The TMS 9980A and the TMS 9981 although very similar, have several differences which user should be aware.

- The TMS 9980A requires a VBB supply (pin 21) while the TMS 9981 has an internal charge pump to generate VBB from VCC and VDD.

- The TMS 9981 has an optional on-chip crystal oscillator in addition to the external clock mode of the TMS 9980A.

- 3. The pin-outs are not compatible for D0-D7, INT0-INT2, and  $\overline{\phi}3$ .

FIGURE 1 - ARCHITECTURE

## 2. ARCHITECTURE

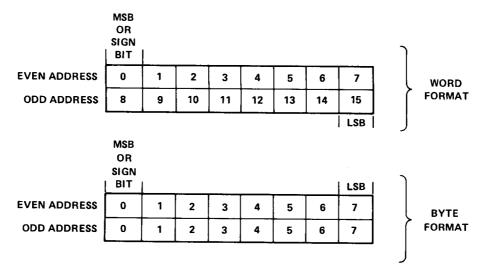

The memory for the TMS 9980A/TMS 9981 is addressable in 8-bit bytes. A word is defined as 16 bits or 2 consecutive bytes in memory. The words are restricted to be on even address boundaries, i.e., the most-significant half (8 bits) resides at even address and the least-significant half resides at the subsequent odd address. A byte can reside at even or odd address. The word and byte formats are shown below.

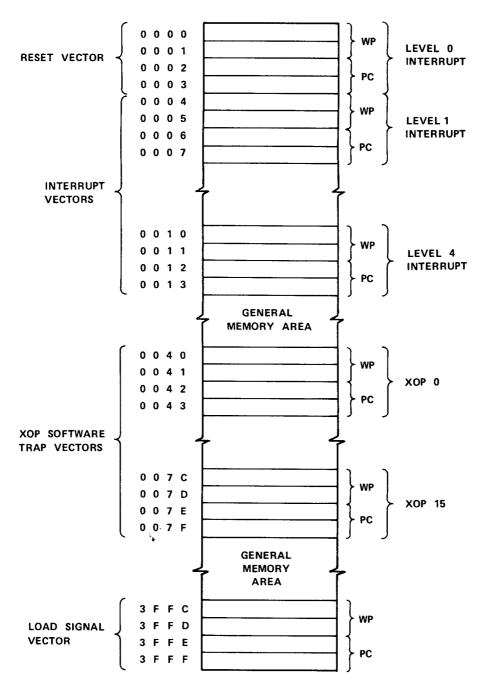

#### 21 REGISTERS AND MEMORY

The TMS 9980A/TMS 9981 employs an advanced memory-to-memory architecture. Blocks of memory designated as workspace replace internal hardware registers with program-data registers. The TMS 9980A/TMS 9981 memory map is shown in Figure 2. The first two words (4 bytes) are used for RESET trap vector. Addresses 000416 through 001316 are used for interrupt vectors. Addresses 0040 through 007F are used for the extended operation (XOP) instruction trap vectors. The last four bytes at address 3FFC16 to 3FFF are used for trap vector for the LOAD function.

The remaining memory is available for programs, data, and workspace registers. If desired, any of the special areas may also be used as general memory.

Three internal registers are accessible to the user. The program counter (PC) contains the address of the instruction following the current instruction being executed. This address is referenced by the processor to fetch the next instruction from memory and is then automatically incremented. The status register (ST) contains the present state of the processor and will be further defined in Section 3.4. The workspace pointer (WP) contains the address of the first word in the currently active set of workspace registers.

FIGURE 2 - MEMORY MAP

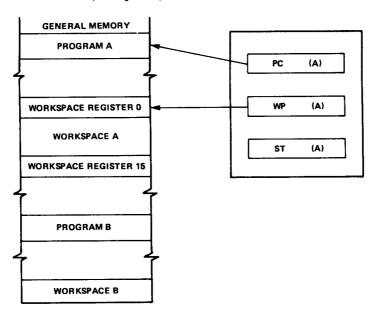

A workspace-register file occupies 16 contiguous memory words in the general memory area. Each workspace register may hold data or addresses and function as operand registers, accumulators, address registers, or index registers. During instruction execution, the processor addresses any register in the workspace by adding the register number to the contents of the workspace pointer and initiating a memory request for the word. The relationship between the workspace pointer and its corresponding workspace is shown below.

The workspace concept is particularly valuable during operations that require a context switch, which is a change from one program environment to another (as in the case of an interrupt or call to a subroutine). Such an operation, using a conventional multi-register arrangement, requires that at least part of the contents of the register file be stored and reloaded. A memory cycle is required to store or fetch each word. By exchanging the program counter, status register, and workspace pointer, the TMS 9980A/TMS 9981 accomplishes a complete context switch with only six store cycles and six fetch cycles. After the switch the workspace pointer contains the starting address of a new 16-word workspace in memory for use in the new routine. A corresponding time saving occurs when the original context is restored. Instructions in the TMS 9980A/TMS 9981 that result in a context switch include:

- 1. Branch and Load Workspace Pointer (BLWP)

- 2. Return from Subroutine (RTWP)

- 3. Extended Operation (XOP)

Device interrupts, RESET, and LOAD also cause a context switch by forcing the processor to trap to a service subroutine.

#### 2.2 INTERRUPTS

The architecture of the 9900 family allows vectoring of 16 interrupts. These interrupts are assigned levels from 0 to 15. The interrupt at level 0 has the highest priority and the interrupt at level 15 has the lowest priority. The TMS 9900 implements all 16 interrupt levels. The TMS 9980A/TMS 9981 implements only 5 levels (level 0 and levels 1 through 4). Level 0 is reserved for RESET function.

Levels 1 through 4 may be used for external devices. The external levels may also be shared by several device interrupts, depending upon system requirements. The TMS 9980A/TMS 9981 continuously compares the interrupt code (IC0 through IC2) with the interrupt mask contained in status-register bits 12 through 15. When the level of the pending interrupt is less than or equal to the enabling mask level (higher or equal priority interrupt), the processor recognizes the interrupt and initiates a context switch following completion of the currently executing instruction. The processor fetches the new context WP and PC from the interrupt vector locations. Then, the previous context WP, PC, and ST are stored in workspace registers 13, 14, and 15, respectively, of the new workspace. The TMS 9980A/TMS 9981 then forces the interrupt mask to a value that is one less than the level of the interrupt being serviced. This allows only interrupts of higher priority to interrupt a service routine. The processor also inhibits interrupts until the first instruction of the service routine has been executed to allow modification of interrupt mask if needed (to mask out certain interrupts). All interrupt requests should remain active until recognized by the processor in the device-service routine. The individual service routines must reset the interrupt requests before the routine is complete. The interrupt code (ICO-IC2) may change asynchronously within the constraints specified in Section 2.10.4.

If a higher priority interrupt occurs, a second context switch occurs to service the higher-priority interrupt. When that routine is complete, a return instruction (RTWP) restores the first service routine parameters to the processor to complete processing of the lower-priority interrupt. All interrupt subroutines should terminate with the return instruction to restore original program parameters. The interrupt-vector locations, device assignment, enabling mask value and the interrupt code are shown in Table 1.

TABLE 1

INTERRUPT LEVEL DATA

| INTERRUPT<br>CODE<br>(ICO-IC2) | FUNCTION | VECTOR LOCATION<br>(MEMORY ADDRESS<br>IN HEX) | DEVICE ASSIGNMENT | INTERRUPT MASK VALUES TO ENABLE (ST12 THROUGH ST15) |

|--------------------------------|----------|-----------------------------------------------|-------------------|-----------------------------------------------------|

| 1 1 0                          | Level 4  | 0 0 1 0                                       | External Device   | 4 Through F                                         |

| 1 0 1                          | Level 3  | 0 0 0 C                                       | External Device   | 3 Through F                                         |

| 100                            | Level 2  | 0008                                          | External Device   | 2 Through F                                         |

| 0 1 1                          | Level 1  | 0004                                          | External Device   | 1 Through F                                         |

| 001                            | Reset    | 0 0 0 0                                       | Reset Stimulus    | Don't Care                                          |

| 0 1 0                          | Load     | 3 F F C                                       | Load Stimulus     | Don't Care                                          |

| 000                            | Reset    | 0000                                          | Reset Stimulus    | Don't Care                                          |

| 1 1 1                          | No-Op    | ••••                                          |                   |                                                     |

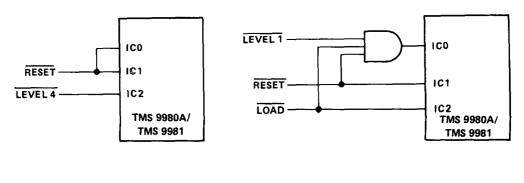

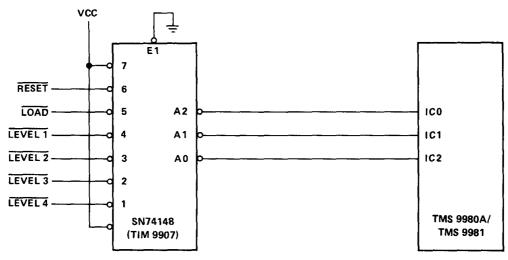

Note that RESET and LOAD functions are also encoded on the interrupt code input lines. Figure 3 illustrates some of the possible configurations. To realize RESET and one interrupt no external component is needed. If LOAD is also needed, a three input AND gate is wired as shown. If the system requires more than one interrupt, a single SN74148 (TIM 9907) is required.

FIGURE 3 - TMS 9980A/TMS 9981 INTERRUPT INTERFACE

# 2.3 INPUT/OUTPUT

The TMS 9980A/TMS 9981 utilizes a versatile direct command-driven I/O interface designated as the communications-register unit (CRU). The CRU provides up to 2,048 directly addressable output bits. Both input and output bits can be addressed individually or in fields of from 1 to 16 bits. The TMS 9980A/TMS 9981 employs CRUIN, CRUCLK, and A13 (for CRUOUT) and 11 bits (A2-A12) of the address bus to interface with the CRU system. The processor instructions that drive the CRU interface can set, reset, or test any bit in the CRU array or move between memory and CRU data fields.

## 2.4 SINGLE-BIT CRU OPERATIONS

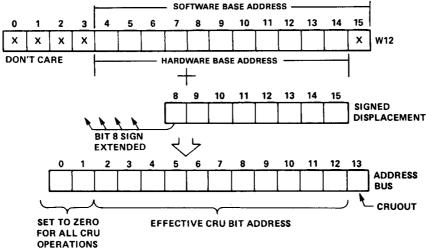

The TMS 9980A/TMS 9981 performs three single-bit CRU functions: test bit (TB), set bit to one (SBO), and set bit to zero (SBZ). To identify the bit to be operated upon, the TMS 9980A/TMS 9981 develops a CRU-bit address and places it on the address bus, A2 to A12.

For the two output operations (SBO and SBZ), the processor also generates a CRUCLK pulse, indicating an output operation to the CRU device and places bit 7 of the instruction word on the A13 line to accomplish the specified

operation (bit 7 is a one for SBO and a zero for SBZ). A test-bit instruction transfers the addressed CRU bit from the CRUIN input line to bit 2 of the status register (EQUAL).

The TMS 9980A/TMS 9981 develops a hardware base address for the single-bit operations from the software base address contained in workspace register 12 and the signed displacement count contained in bits 8 through 15 of the instruction. The displacement allows two's complement addressing from base minus 128 bits through base plus 127 bits. The hardware base address (bits 4 through 14 of WR12) is added to the signed displacement specified in the instruction and the result is loaded into the address bus. Figure 4 illustrates the development of a single-bit CRU address.

FIGURE 4 - TMS 9980A/TMS 9981 SINGLE-BIT CRU ADDRESS DEVELOPMENT

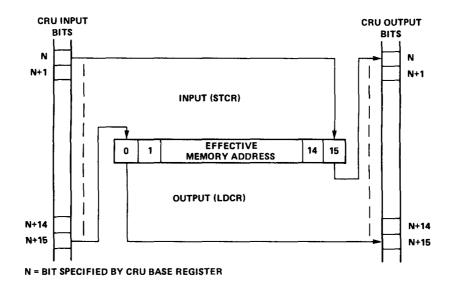

## 2.5 MULTIPLE-BIT CRU OPERATIONS

The TMS 9980A/TMS 9981 performs two multiple-bit CRU operations: store communications register (STCR) and load communications register (LDCR). Both operations perform a data transfer from the CRU-to-memory or from memory-to-CRU as illustrated in Figure 5. Although the figure illustrates a full 16-bit transfer operation, any number of bits from 1 through 16 may be involved. The LDCR instruction fetches a word from memory and right-shifts it to serially transfer it to CRU output bits. If the LDCR involves eight or fewer bits, those bits come from the right-justified field within the addressed byte of the memory word. If the LDCR involves nine or more bits, those bits come from the right-justified field within the whole memory word. When transferred to the CRU interface, each successive bit receives an address that is sequentially greater than the address for the previous bit. This addressing mechanism results in an order reversal of the bits; that is, bit 15 of the memory word (or bit 7) becomes the lowest addressed bit in the CRU and bit 0 becomes the highest addressed bit in the CRU field.

An STCR instruction transfers data from the CRU to memory. If the operation involves a byte or less transfer, the transferred data will be stored right-justified in the memory byte with leading bits set to zero. If the operation involves from nine to 16 bits, the transferred data is stored right-justified in the memory word with leading bits set to zero.

When the input from the CRU device is complete, the first bit from the CRU is the least-significant-bit position in the memory word or byte.

FIGURE 5 - TMS 9980A/TMS 9981 LDCR/STCR DATA TRANSFERS

Figure 6 illustrates how to implement a 16-bit input and a 16-bit output register in the CRU interface. CRU addresses are decoded as needed to implement up to 128 such 16-bit interface registers. In system application, however, only the exact number of interface bits needed to interface specific peripheral devices are implemented. It is not necessary to have a 16-bit interface register to interface an 8-bit device.

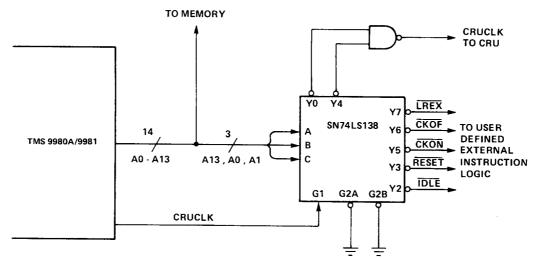

#### 2.6 EXTERNAL INSTRUCTIONS

The TMS 9980A/TMS 9981 has five external instructions that allow user-defined external functions to be initiated under program control. These instructions are CKON, CKOF, RSET, IDLE, and LREX. These mnemonics, except for IDLE, relate to functions implemented in the 990 minicomputer and do not restrict use of the instructions to initiate various user-defined functions. IDLE also causes the TMS 9980A/TMS 9981 to enter the idle state and remain until an interrupt, RESET, or LOAD occurs. When any of these five instructions are executed by the TMS 9980A/TMS 9981, a unique 3-bit code appears on the address bus, bits A13, A0, and A1, along with a CRUCLK pulse. When the TMS 9980A/TMS 9981 is in an idle state, the 3-bit code and CRUCLK pulses occur repeatedly until the idle state is terminated. The codes are:

| EXTERNAL INSTRUCTION | A13        | A0 | A1 |

|----------------------|------------|----|----|

| LREX                 | Н          | Н  | Н  |

| CKOF                 | н          | н  | L  |

| CKON                 | Н          | L  | н  |

| RSET                 | <u>ا</u> د | н  | н  |

| IDLE                 | L          | н  | L  |

| CRU INSTRUCTIONS     | H/L        | L  | L  |

FIGURE 6 - TMS 9980A/9981 16-BIT INPUT/OUTPUT INTERFACE

Note that during external instructions bits (A2-A12) of the address bus may have any of the possible binary patterns. Since these bits (A2-A12) are used as CRU addresses, CRUCLK to the CRU must be gated with a decode of 0 on A0 and A1 to avoid erroneous strobe to CRU bits during external instruction execution.

Figure 7 illustrates typical external decode logic to implement these instructions. Note CRUCLK to the CRU is inhibited during external instructions.

FIGURE 7 - EXTERNAL INSTRUCTION DECODE LOGIC

#### 2.7 NON-MASKABLE INTERRUPTS

#### 2.7.1 LOAD Function

The LOAD stimulus is an unmaskable interrupt that allows cold-start ROM loaders and front panels to be implemented for the TMS 9980A/TMS 9981. When the TMS 9980A/TMS 9981 decodes LOAD on ICO-IC2 lines, it initiates an interrupt sequence immediately following the instruction being executed. Memory location 3FFC is used to obtain the vector (WP and PC). The old PC, WP, and ST are loaded into the new workspace and the interrupt mask is set to 0000. Then the program execution resumes using the new PC and WP. Recognition of LOAD by the processor will also terminate the idle condition. External stimulus for LOAD must be held active (on ICO-IC2) for one instruction period by using IAQ signal.

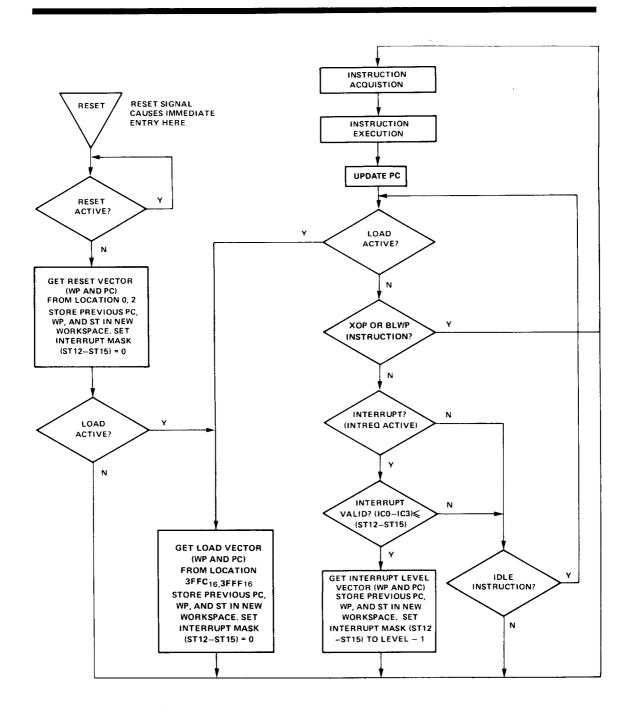

## 2.7.2 RESET

When the TMS 9980A/TMS 9981 recognizes a RESET on ICO-IC2, it resets and inhibits  $\overline{WE}$  and CRUCLK. Upon removal of the RESET code, the TMS 9980A/TMS 9981 initiates a level-zero interrupt sequence that acquires WP and PC from location 0000 and 0002, sets all status register bits to zero and starts execution. Recognition of RESET by the processor will also terminate an idle state. External stimulus for RESET must be held active for a minimum of three clock cycles.

FIGURE 8 - TMS 9980A/TMS 9981 CPU FLOW CHART

# 2.8 TMS 9980A PIN DESCRIPTION

Table 2 defines the TMS 9980A pin assignments and describes the function of each pin.

TABLE 2

TMS 9980A PIN ASSIGNMENTS AND FUNCTIONS

| SIGNATURE       | PIN | 1/0 | DESCRIPTION                                                                                                                                      | 7                    | TMS 9980A PI   | IN ASSIGNMENTS                                                   |

|-----------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|------------------------------------------------------------------|

| A0 (MSB)        | 17  | OUT | ADDRESS BUS                                                                                                                                      |                      |                |                                                                  |

| A1              | 16  | OUT | A0 through A13 comprise the address bus.                                                                                                         |                      | 4              |                                                                  |

| A2              | 15  | OUT | This 3-state bus provides the memory-                                                                                                            | HOLD                 | 1 🖺            | 40 MEMEN                                                         |

| A3              | 14  | OUT | address vector to the external-memory sys-                                                                                                       | HOLDA                | 2 🔲            | 39 READY                                                         |

| A4              | 13  | OUT | tem when MEMEN is active and I/O-bit                                                                                                             | IAQ                  | з 🗍            | 38 WE                                                            |

| A5              | 12  | OUT | addresses and external-instruction addresses                                                                                                     | A13/CRUOUT           | 4 1            | IE                                                               |

| A6              | 11  | OUT | to the I/O system when MEMEN is inactive.                                                                                                        |                      |                | 37 CRUCLK                                                        |

| A7<br>A8        | 10  | OUT | The address bus assumes the high-impedance                                                                                                       | A12                  | 5 📗            | 36 V <sub>DD</sub>                                               |

| A0<br>A9        | 9   | OUT | state when HOLDA is active.                                                                                                                      | A11                  | 6 ∐            | ☐35 V <sub>SS</sub>                                              |

| A10             | 7   | OUT |                                                                                                                                                  | A10                  | 7 🗍            | 34 CKIN                                                          |

| A11             | 6   | OUT |                                                                                                                                                  | А9                   | 8              | 33 D7                                                            |

| A12             | 5   | OUT |                                                                                                                                                  |                      | 긔              | 15                                                               |

| A13/CRUOUT      | 4   | OUT |                                                                                                                                                  | A8                   | 9 📙            | ∐ 32 D6                                                          |

| AI3/CHOOO!      | , , | 001 | CRUOUT                                                                                                                                           | A7                   | 10 🔲           | ☐ 31 D5                                                          |

|                 |     |     | Serial I/O data appears on A13 when an                                                                                                           | A6                   | 11 🛮           | 30 D4                                                            |

|                 |     |     | LDCR, SBZ and SBO instruction is execu-                                                                                                          | A5                   | 12             | 29 D3                                                            |

|                 | ĺ   |     | ted. This data should be sampled by the I/O interface logic when CRUCLK goes active                                                              |                      | - A            | IS                                                               |

|                 |     |     | (high). One bit of the external instruction                                                                                                      | A4                   | 13 📙           | <b>28</b> D2                                                     |

|                 |     | i   | code appears on A13 during external in-                                                                                                          | A3                   | 14 📙           | ∐27 D1                                                           |

|                 |     |     | struction execution.                                                                                                                             | A2                   | 15 📗           | 26 D0                                                            |

|                 |     |     | struction execution.                                                                                                                             | A1                   | 16             | 25 INT 0                                                         |

| DO (MSB)        | 26  | 1/0 | DATA BUS                                                                                                                                         | AO                   | 17             | IF                                                               |

| D1              | 27  | 1/0 | D0 through D7 comprise the bidirectional                                                                                                         |                      |                | 24 INT 1                                                         |

| D2              | 28  | 1/0 | 3-state data bus. This bus transfers memory                                                                                                      | DBIN                 | 18 📙           | 23 INT 2                                                         |

| D3              | 29  | 1/0 | data to (when writing) and from (when                                                                                                            | CRUIN                | 19 🔲           | $22 \overline{\phi}$ 3                                           |

| D4              | 30  | 1/0 | reading) the external-memory system when                                                                                                         | vcc                  | 20 🗌           | 21 VBB                                                           |

| D5              | 31  | 1/0 | MEMEN is active. The data bus assumes the                                                                                                        | •                    | l <u>i</u>     |                                                                  |

| D6              | 32  | 1/0 | high-impedance state when HOLDA is                                                                                                               |                      |                |                                                                  |

| D7 (LSB)        | 33  | 1/0 | active.                                                                                                                                          |                      |                |                                                                  |

|                 | ,   |     | POWER SUPPLIES                                                                                                                                   |                      |                |                                                                  |

| VBB             | 21  |     | Supply voltage (-5V NOM)                                                                                                                         |                      |                |                                                                  |

| Vcc             | 20  | -   | Supply voltage (5 V NOM)                                                                                                                         |                      |                |                                                                  |

| V <sub>DD</sub> | 36  |     | Supply voltage (12 V NOM)                                                                                                                        |                      |                |                                                                  |

| √ss             | 35  |     | Ground reference                                                                                                                                 |                      |                |                                                                  |

| CKIN            | 34  | IN  |                                                                                                                                                  |                      |                |                                                                  |

| OKIN            | 34  | IIV | Cleate to A TT                                                                                                                                   | CLOCKS               |                |                                                                  |

| 1               |     | 1   | Clock In. A TTL compatible input used to gene                                                                                                    | rate the internal 4- | phase clock. C | KIN frequency is 4 times the                                     |

|                 | ŀ   |     | desired system frequency.                                                                                                                        |                      |                |                                                                  |

| <u></u>         | 22  | ОПТ | Clock where 2 (do)                                                                                                                               |                      |                |                                                                  |

|                 |     | 55, | Clock phase 3 ( $\phi$ 3) inverted; used as a timing ref                                                                                         | erence.              |                |                                                                  |

| DBIN            | 18  | OUT |                                                                                                                                                  | IS CONTROL           |                |                                                                  |

|                 |     |     | Data bus in. When active (high), DBIN indicates<br>the memory to place memory-read data on the<br>except when HOLDA is active at which time it i | data bus during ME   | EMEN. DBIN     | ed its output buffers to allow<br>remains low in all other cases |

# TMS 9980A/9981 ARCHITECTURE

# TABLE 2 (CONTINUED)

| SIGNATURE            | PIN            | 1/0            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMEN                | 40             | OUT            | Memory enable. When active (low), MEMEN indicates that the address bus contains a memory address. When HOLDA is active, MEMEN is in the high Impedance state.                                                                                                                                                                                                                                                                                                                                                                                  |

| WE                   | 38             | оυт            | Write enable. When active (low), WE indicates that memory-write data is available from the TMS 9980 to be written into memory. When HOLDA is active, WE is in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                        |

| CRUCLK               | 37             | оит            | CRU clock. When active (high), CRUCLK indicates that external interface logic should sample the output data on CRUOUT or should decode external instructions on A0, A1, A13.                                                                                                                                                                                                                                                                                                                                                                   |

| CRUIN                | 19             | IN             | CRU data in. CRUIN, normally driven by 3-state or open-collector devices, receives input data from external interface logic. When the processor executes a STCR or TB instruction, it samples CRUIN for the level of the CRU input bit specified by the address bus (A2 through A12).                                                                                                                                                                                                                                                          |

| INT2<br>INT1<br>INT0 | 23<br>24<br>25 | 12<br>12<br>12 | Interrupt code. Refer to Section 2.2 for detailed description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                      |                |                | MEMORY CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| HOLD                 | 1              | IN             | Hold. When active (low), HOLD indicates to the processor that an external controller (e.g., DMA device) desires to utilize the address and data buses to transfer data to or from memory. The TMS 9980A enters the hold state following a hold signal when it has completed its present memory cycle.* The processor then places the address and data buses in the high-impedance state (along with WE, MEMEN, and DBIN) and responds with a hold-acknowledge signal (HOLDA). When HOLD is removed, the processor returns to normal operation. |

| HOLDA                | 2              | оит            | Hold acknowledge. When active (high), HOLDA indicates that the processor is in the hold state and the address and data buses and memory control outputs (WE, MEMEN, and DBIN) are in the high-impedance state.                                                                                                                                                                                                                                                                                                                                 |

| READY                | 39             | IN             | Ready. When active (high), READY indicates that memory will be ready to read or write during the next clock cycle. When not-ready is indicated during a memory operation, the TMS 9980A enters a wait state and suspends internal operation until the memory systems indicated ready.                                                                                                                                                                                                                                                          |

|                      |                |                | TIMING AND CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DAI                  | 3              | OUT            | Instruction acquisition. IAQ is active (high) during any memory cycle when the TMS 9980A is acquiring an instruction. IAQ can be used to detect illegal op codes. It may also be used to synchronize LOAD stimulus.                                                                                                                                                                                                                                                                                                                            |

<sup>\*</sup> If the cycle following the present memory cycle is also a memory cycle it, too, is completed before TMS 9980 enters hold state.

# 2.9 TMS 9981 PIN DESCRIPTION

Table 3 defines the TMS 9981 pin assignments and describes the function of each pin.

TABLE 3

TMS 9981 PIN ASSIGNMENTS AND FUNCTIONS

| SIGNATURE       | PIN      | 1/0          | DESCRIPTION                                                                            | 1                    | TMS 9981 PIN ASS    | SIGNMENTS                                   |

|-----------------|----------|--------------|----------------------------------------------------------------------------------------|----------------------|---------------------|---------------------------------------------|

| AO(MSB)         | 17       | OUT          | ADDRESS BUS                                                                            | HOLD                 |                     | ——————————————————————————————————————      |

| A1              | 16       | OUT          | A0 through A13 comprise the address bus.                                               |                      | <u> 1</u> 뷔 U       | 40 MEMEN                                    |

| A2              | 15       | OUT          | This 3-state bus provides the memory-                                                  | HOLDA                | 2 📙                 | 39 READY                                    |

| A3<br>A4        | 14       | OUT          | address vector to the external-memory sys-                                             | DAI                  | 3 🔲                 | 38 WE                                       |

| A4<br>A5        | 13<br>12 | OUT  <br>OUT | tem when MEMEN is active and I/O-bit                                                   | A13/CRUOUT           | 4 🛚                 | 37 CRUCLK                                   |

| A6              | 11       | OUT          | addresses and external-instruction addresses to the I/O system when MEMEN is inactive. | A12                  | 5                   | 36 Von                                      |

| A7              | 10       | OUT          | The address bus assumes the high-impedance                                             | A11                  | 6 🗍                 | F 00                                        |

| A8              | 9        | OUT          | state when HOLDA is active.                                                            |                      | · 🗇                 | ∐35 V <sub>SS</sub>                         |

| A9              | 8        | OUT          | Tate William House A 13 delive.                                                        | A10                  | 7 🗐                 | 24 CKIN                                     |

| A10             | 7        | OUT          |                                                                                        | A9                   | 8 ∐                 | 33 OSCOUT                                   |

| A11             | 6        | OUT          |                                                                                        | A8                   | 9 🔲                 | 32 D7                                       |

| A12             | 5        | OUT          |                                                                                        | A7                   | 10                  | 31 D6                                       |

| A13/CRUOUT      | 4        | OUT          | CRUOUT                                                                                 |                      | 11                  | lΗ                                          |

|                 |          |              | Serial I/O data appears on A13 when an                                                 | A6                   | ·                   | 30 D5                                       |

|                 |          |              | LDCR, SBZ and SBO instruction is execu-                                                | A5                   | 12 📙                | ∐29 D4                                      |

|                 |          |              | ted. This data should be sampled by the I/O                                            | A4                   | 13 🖳                | ⊒28 D3                                      |

|                 |          |              | interface logic when CRUCLK goes active                                                | A3                   | 14 🔲                | 27 D2                                       |

|                 |          | İ            | (high). One bit of the external instruction                                            | A2                   | 15                  | 26 D1                                       |

|                 |          |              | code appears on A13 during external in-<br>struction execution.                        | A1                   | 16                  | 25 D0 0                                     |

|                 | ĺĺ       |              | THE DESIGN EXECUTION.                                                                  | AO                   | 긤                   | 24 INT 0                                    |

| DO (MSB)        | 25       | 1/0          | DATA BUS                                                                               | DBIN                 | i (a)               | IE                                          |

| D1              | 26       | 1/0          | D0 through D7 comprise the bidirectional                                               |                      | a                   | IE                                          |

| D2              | 27       | 1/0          | 3-state data bus. This bus transfers memory                                            | CRUIN                | 19 🖺                | 22 INT 2                                    |

| D3              | 28       | 1/0          | data to (when writing) and from (when                                                  | Vcc                  | 20 🖺                | <b>⊒21</b> <i>φ</i> 3                       |

| D4              | 29       | 1/0          | reading) the external-memory system when                                               |                      |                     | J                                           |

| D5              | 30       | 1/0          | MEMEN is active. The data bus assumes the                                              |                      |                     |                                             |

| D6              | 31       | 1/0          | high-impedance state when HOLDA is                                                     |                      |                     |                                             |

| D7 (LSB)        | 32       | 1/0          | active.                                                                                |                      |                     |                                             |

|                 |          | 1            | POWER SUPPLIES                                                                         |                      |                     |                                             |

| vcc             | 20       |              | Supply voltage (5 V NOM)                                                               |                      |                     |                                             |

| V <sub>DD</sub> | 36       | 1            | Supply voltage (12 V NOM)                                                              |                      |                     |                                             |

| V <sub>SS</sub> | 35       |              | Ground reference                                                                       |                      |                     |                                             |

| CKIN            | 34       | IN           |                                                                                        | CLOCKS               |                     |                                             |

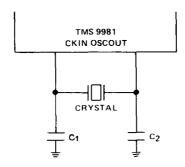

| OSCOUT          | 33       | OUT          | Clock in and Oscillator Out. These pins may b                                          |                      | two modes to gene   | rate the internal 4-phase                   |

|                 |          |              | clock. In mode 1 a crystal of 4 times the desire                                       |                      |                     |                                             |

| ļ               |          | į            | (see Figure 13). In mode 2 OSCOUT is left flo                                          |                      |                     |                                             |

|                 |          |              | frequency is 4 times the desired system frequen                                        |                      |                     | , s. , p. , . , . , . , . , . , . , . , . , |

| φ3              | 21       | ООТ          | Clock phase 3 ( $\phi$ 3) inverted; used as a timing re                                | ference.             |                     |                                             |

| DBIN            | 18       | оит          | F                                                                                      | US CONTROL           |                     |                                             |

| I               | -        |              | Data bus in. When active (high), DBIN indicate                                         |                      | 81 has disabled its | s output buffers to allow                   |

| •               |          | 1            | the memory to place memory-read data on the                                            |                      |                     |                                             |

|                 |          |              | •                                                                                      | is in the high-imped |                     |                                             |

# TMS 9980A/9981 ARCHITECTURE

#### TABLE 3 (CONTINUED)

| SIGNATURE            | PIN            | 1/0            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMEN                | 40             | оит            | Memory enable. When active (low), MEMEN indicates that the address bus contains a memory address. When HOLDA is active, MEMEN is in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                 |

| WE                   | 38             | ОПТ            | Write enable. When active (low), WE indicates that memory-write data is available from the TMS 9981 to be written into memory. When HOLDA is active, WE is in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                       |

| CRUCLK               | 37             | оит            | CRU clock. When active (high), CRUCLK indicates that external interface logic should sample the output data on CRUOUT or should decode external instructions on A0, A1, A13.                                                                                                                                                                                                                                                                                                                                                                                  |

| CRUIN                | 19             | IN             | CRU data in. CRUIN, normally driven by 3-state or open-collector devices, receives input data from external interface logic. When the processor executes a STCR or TB instruction, it samples CRUIN for the level of the CRU input bit specified by the address bus (A2 through A12).                                                                                                                                                                                                                                                                         |

| INT2<br>INT1<br>INT0 | 22<br>23<br>24 | IN<br>IN<br>IN | Interrupt code. Refer to Section 2.2 for detailed description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| HOLD                 | 1              | IZ             | MEMORY CONTROL  Hold. When active (low), HOLD indicates to the processor that an external controller (e.g., DMA device) desires to utilize the address and data buses to transfer data to or from memory. The TMS 9981 enters the hold state following a hold signal when it has completed its present memory cycle.* The processor then places the address and data buses in the high-impedance state (along with WE, MEMEN, and DBIN) and responds with a hold-acknowledge signal (HOLDA). When HOLD is removed, the processor returns to normal operation. |

| HOLDA                | 2              | оит            | Hold acknowledge. When active (high), HOLDA indicates that the processor is in the hold state and the address and data buses and memory control outputs (WE, MEMEN, and DBIN) are in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                |

| READY                | 39             | IN             | Ready. When active (high), READY indicates that memory will be ready to read or write during the next clock cycle. When not-ready is indicated during a memory operation, the TMS 9981 enters a wait state and suspends internal operation until the memory systems indicated ready.                                                                                                                                                                                                                                                                          |

| DAI                  | 3              | о∪т            | TIMING AND CONTROL  Instruction acquisition. IAQ is active (high) during any memory cycle when the TMS 9981 is acquiring an instruction. IAQ can be used to detect illegal op codes. It may also be used to synchronize LOAD stimulus.                                                                                                                                                                                                                                                                                                                        |

<sup>\*</sup>If the cycle following the present memory cycle is also a memory cycle it, too, is completed before TMS 9981 enters hold state.

# 2.10 TIMING

## 2.10.1 Memory

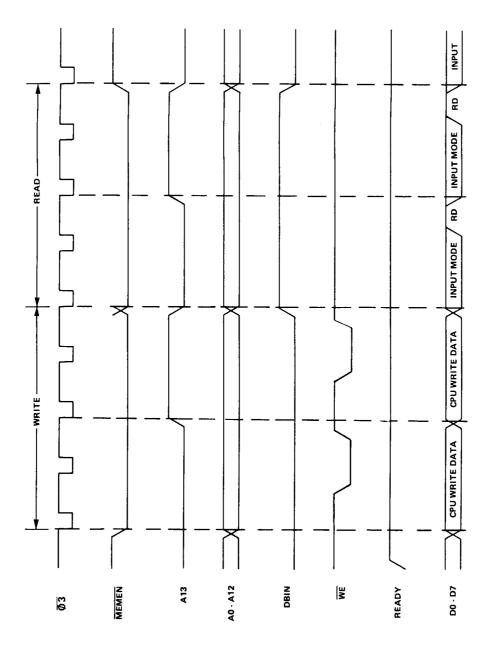

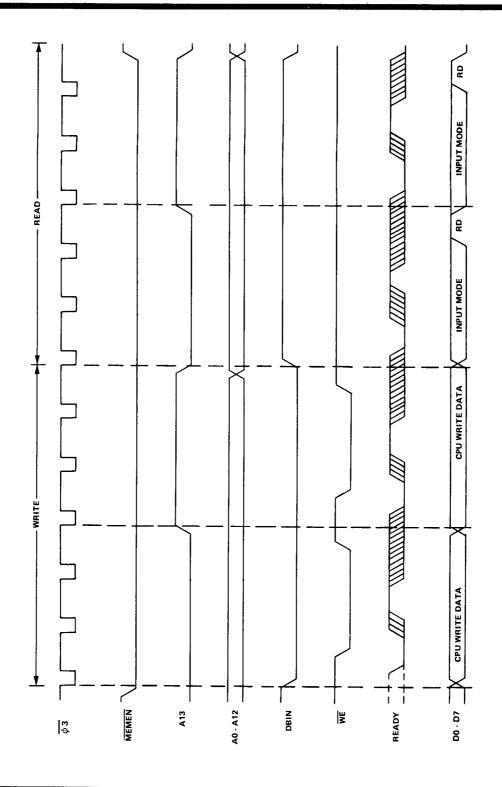

Basic memory read and write cycles are shown in Figures 9a and 9b. Figure 9a shows a read and a write cycle with no wait states while Figure 9b shows a read and a write cycle for a memory requiring one wait state.

MEMEN goes active (low) during each memory cycle. At the same time that MEMEN is active, the memory address appears on the address bits A0 through A13. Since the TMS 9980A/TMS 9981 has an 8-bit data bus, every memory operation consists of two consecutive memory cycles. Address bit A13 is 0 for the first of the two cycles and goes to 1 for the second. If the cycle is a memory-read cycle, DBIN will go active (high) at the same time MEMEN and A0 through A13 become valid. The memory-write (WE) signal remains inactive during a read cycle.

The READY signal allows extended memory cycle as shown in Figure 9b.

FIGURE 9a - TMS 9880A/TMS 9981 MEMORY BUS TIMING (NO WAIT STATES)

FIGURE 9b - TMS 9980A/TMS 9981 MEMORY BUS TIMING (ONE WAIT STATE)

At the end of the read cycle, MEMEN and DBIN go inactive (high and low respectively). The address bus also changes at this time, however, the data bus remains in the input mode for one clock cycle after the read cycle.

A write cycle is similar to read cycle except that  $\overline{\text{WE}}$  goes active (low) as shown and valid write data appears on the data bus at the same time the address appears.

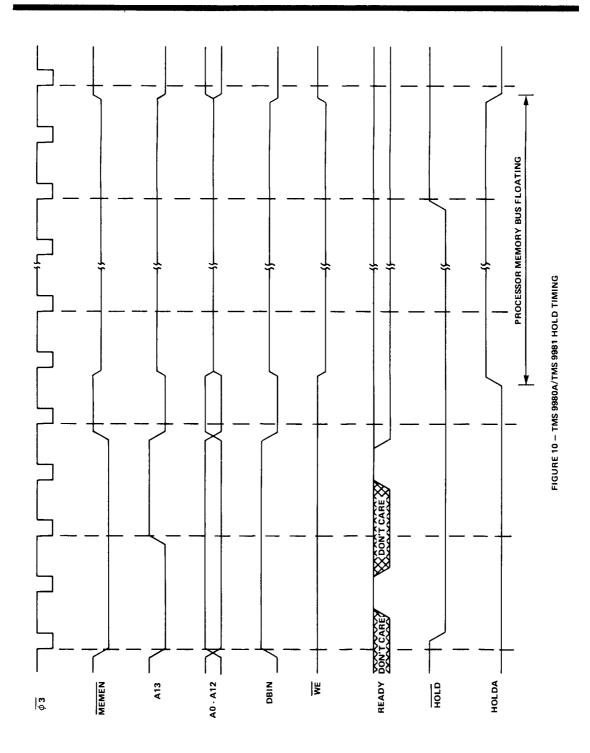

#### 2.10.2 HOLD

Other interfaces may utilize the TMS 9980A/TMS 9981 memory bus by using the hold operation (illustrated in Figure 10) of the TMS 9980A/TMS 9981. When  $\overline{\text{HOLD}}$  is active (low), the TMS 9980A/TMS 9981 enters the hold state at the next available non-memory cycle clock period. When the TMS 9980A/TMS 9981 has entered the hold state HOLDA goes active (high), A0 through A13, D0 through D7, DBIN,  $\overline{\text{MEMEN}}$ , and  $\overline{\text{WE}}$  go into high-impedance state to allow other devices to use the memory buses. When  $\overline{\text{HOLD}}$  goes inactive, TMS 9980A/TMS 9981 resumes processing as shown. Considering that there can be a maximum of 6 consecutive memory operations, the maximum delay between  $\overline{\text{HOLD}}$  going active to HOLDA going active (high) could be  $t_{\text{C}(\phi)}$  (for set up) + (12 + 6 W)  $t_{\text{C}(\phi)}$  (delay for HOLDA), where W is the number of wait states per memory cycle and  $t_{\text{C}(\phi)}$  is the clock cycle time. If hold occurs during a CRU operation, the TMS 9980A/TMS 9981 uses an extra clock cycle (after the removal of the  $\overline{\text{HOLD}}$  signal) to reassert the CRU address providing the normal setup times for the CRU bit transfer that was interrupted.

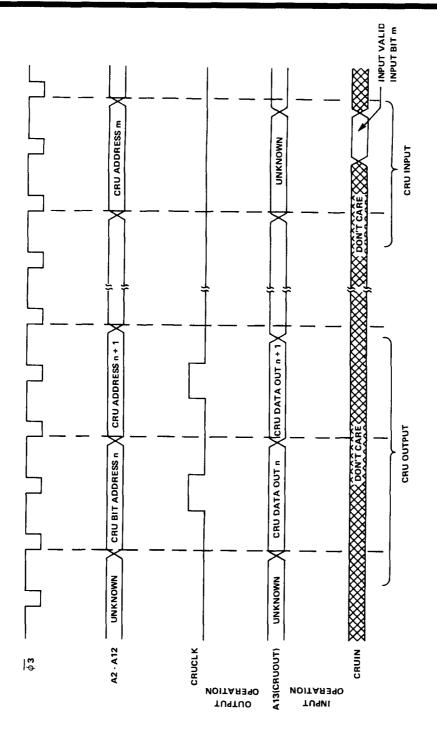

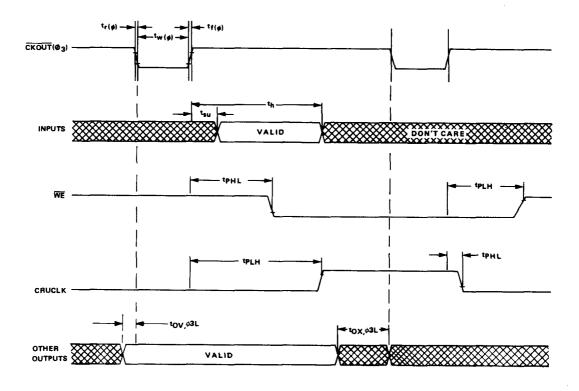

#### 2.10.3 CRU

CRU interface timing is shown in Figure 11. The timing for transferring two bits out and one bit in is shown. These transfers would occur during the execution of a CRU instruction. The other cycles of the instruction execution are not illustrated. To output a CRU bit, the CRU-bit address is placed on the address bus A2 through A12 and the actual bit data on A13. During the second clock cycle a CRU pulse is supplied by CRUCLK. This process is repeated until the number of bits specified by the instruction are completed.

The CRU input operation is similar in that the bit address appears on A2 through A12. During the subsequent cycle, the TMS 9980A/TMS 9981 accepts the bit input data as shown. No CRUCLK pulses occur during a CRU input operation.

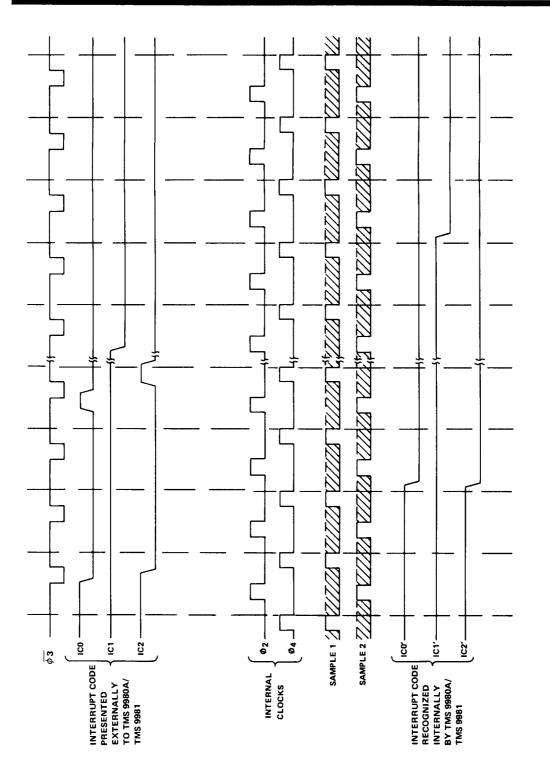

#### 2.10.4 Interrupt Code (ICO-IC2)

The TMS 9980A/TMS 9981 uses 4 phase clock ( $\phi$ 1,  $\phi$ 2,  $\phi$ 3, and  $\phi$ 4) for timing and control of the internal operations. ICO-IC2 are sampled during  $\phi$ 4 and then during  $\phi$ 2.

If these two successive samples are equal, the code is accepted and latched for internal use on the subsequent  $\phi 1$ . In systems with simple interrupt structures this allows the interrupt code to change asynchronously without the TMS 9980A/TMS 9981 accepting erroneous codes. Figure 3 shows systems with a single level of external interrupt implemented that would require no external timing. When implementing multiple external interrupts, as in the bottom diagram of Figure 3, external synchronization of interrupt requests is required. See Figure 12 for a timing diagram. In systems with more than one external interrupt, the interrupts should be synchronized with the  $\overline{\phi 3}$  output of the TMS 9980A/TMS 9981 to avoid code transitions on successive sample cycles. This synchronization ensures that the TMS 9980A/TMS 9981 will service only the proper active interrupt level.

FIGURE 11 - TMS 9980A/TMS 9981 CRU INTERFACE TIMING

FIGURE 12 - INTERRUPT CODE TIMING

# TMS 9980A/TMS 9981 INSTRUCTION EXECUTION TIMES

#### 3.6 TMS 9980A/TMS 9981 INSTRUCTION EXECUTION TIMES

Instruction execution times for the TMS 9980A/TMS 9981 are a function of:

- Clock cycle time, t<sub>C</sub>(φ)

- 2) Addressing mode used where operands have multiple addressing mode capability

- 3) Number of wait states required per memory access.

Table 4 lists the number of clock cycles and memory accesses required to execute each TMS 9980A/TMS 9981 instruction. For instructions with multiple addressing modes for either or both operands, Table 4 lists the number of clock cycles and memory accesses with all operands addressed in the workspace-register mode. To determine the additional number of clock cycles and memory accesses required for modified addressing, add the appropriate values from the referenced tables. The total instruction-execution time for an instruction is:

$T = t_{C}(\phi) (C+W \cdot M)$

where:

T = total instruction time;

$t_{C(\phi)} = clock cycle time;$

C = number of clock cycles for instruction execution plus address modification;

W = number of required wait states per memory access for instruction execution plus address modification;

M = number of memory accesses.

As an example, the instruction MOVB is used in a system with  $t_{C(\phi)}$ = 0.400 $\mu$ s and no wait states are required to access memory. Both operands are addressed in the workspace register mode:

T =

$$t_{C(\phi)}$$

(C+W•M) = 0.400 (22+0•8) = 8.8  $\mu$ s.

If two wait states per memory access were required, the execution time is:

$$T = 0.400 (22 + 2.8) \mu s = 15.2 \mu s.$$

If the source operand was addressed in the symbolic mode and two wait states were required:

$T = t_{C}(\phi) (C+W \cdot M)$

$$C = 22 + 10 = 32$$

$$M = 8 + 2 = 10$$

$T = 0.400 (32 + 2 \cdot 10) = 20.8 \,\mu s.$

TABLE 4

INSTRUCTION EXECUTION TIMES

| INSTRUCTION                                                            | CLOCK CYCLES      | MEMORY ACCESS | ADDRESS MODIFICATION*** |             |  |  |  |

|------------------------------------------------------------------------|-------------------|---------------|-------------------------|-------------|--|--|--|

|                                                                        | <u> </u>          | M             | SOURCE                  | DESTINATION |  |  |  |

| Α                                                                      | 22                | 8             | Α                       | Α           |  |  |  |

| AB                                                                     | 22                | 8             | В                       | В           |  |  |  |

| ABS (MSB = 0)                                                          | 16                | 4             | A                       | _           |  |  |  |

| (MSB = 1)                                                              | 20                | 6             | l A                     | _           |  |  |  |

| Al                                                                     | 22                | 8             | _                       | _           |  |  |  |

| ANDI                                                                   | 22                | 8             | _                       | _           |  |  |  |

| В                                                                      | 12                | 4             | A                       | _           |  |  |  |

|                                                                        |                   | ,             | 1                       |             |  |  |  |

| BL                                                                     | 18                | 6             | Α                       | -           |  |  |  |

| BLWP                                                                   | 38                | 12            | A                       | _           |  |  |  |

| C                                                                      | 20                | 6             | Α                       | A           |  |  |  |

| СВ                                                                     | 20                | 6             | В                       | В           |  |  |  |

| CI                                                                     | 20                | 6             |                         | _           |  |  |  |

| CKOF                                                                   | 14                | 2             | _                       | _           |  |  |  |

| CKON                                                                   | 14                | 2             | _                       | _           |  |  |  |

|                                                                        |                   | l .           | 1                       | 1           |  |  |  |

| CLR                                                                    | 16                | 6             | A                       | _           |  |  |  |

| coc                                                                    | 20                | 6             | A                       | -           |  |  |  |

| CZC                                                                    | 20                | 6             | Α                       | -           |  |  |  |

| DEC                                                                    | 16                | 6             | l A                     | _           |  |  |  |

| DECT                                                                   | 16                | 6             | l A                     |             |  |  |  |

| DIV (ST4 is set)                                                       | 22                | 6             | A                       | _           |  |  |  |

| DIV (ST4 is reset)*                                                    | 104-136           | 12            |                         | _           |  |  |  |

|                                                                        |                   |               | A                       |             |  |  |  |

| IDLE                                                                   | 14                | 2             | _                       | _           |  |  |  |

| INC                                                                    | 16                | 6             | A                       | _           |  |  |  |

| INCT                                                                   | 16                | 6             | A                       | -           |  |  |  |

| INV                                                                    | 16                | 6             | A                       | _           |  |  |  |

| Jump (PC is changed)                                                   | 12                | 2             | _                       | _           |  |  |  |

| (PC is not changed)                                                    | 10                | 2             | _                       | _           |  |  |  |

|                                                                        |                   |               | 1                       |             |  |  |  |

| LDCR (C = 0)                                                           | 58                | 6             | A                       | _           |  |  |  |

| (1 <c<8)< td=""><td>26+2C</td><td>6</td><td>В</td><td></td></c<8)<>    | 26+2C             | 6             | В                       |             |  |  |  |

| (9 <c<15)< td=""><td>26+2C</td><td>6</td><td>Α</td><td>_</td></c<15)<> | 26+2C             | 6             | Α                       | _           |  |  |  |

| Li                                                                     | 18                | 6             | -                       | _           |  |  |  |

| LIMI                                                                   | 22                | 6             | _                       | -           |  |  |  |

| LREX                                                                   | 14                | 2             | _                       | _           |  |  |  |

| LWPI                                                                   | 14                | 4             | _                       | _           |  |  |  |

| MOV                                                                    | 22                | 8             | A                       | A           |  |  |  |

|                                                                        |                   |               |                         |             |  |  |  |

| MOVB                                                                   | 22                | 8             | В                       | В           |  |  |  |

| MPY                                                                    | 62                | 10            | A                       |             |  |  |  |

| NEG                                                                    | 18                | 6             | Α                       | -           |  |  |  |

| ORI                                                                    | 22                | 8             | _                       | _           |  |  |  |

| RSET                                                                   | 14                | 2             | _                       | _           |  |  |  |

| RTWP                                                                   | 22                | 8             | _                       | _           |  |  |  |

| s                                                                      | 22                | 8             | A                       | A           |  |  |  |

| SB                                                                     | 22                | 8             | B                       | B           |  |  |  |

| 1                                                                      |                   |               | 1                       |             |  |  |  |

| SBO                                                                    | 16                | 4             | -                       | _           |  |  |  |

| SBZ                                                                    | 16                | 4             | -                       | _           |  |  |  |

| SETO                                                                   | 16                | 6             | Α                       | -           |  |  |  |

| Shift (C ≠ 0)                                                          | 18+2C             | 6             | _                       | -           |  |  |  |

| (C ≠0, Bits 12-15                                                      |                   |               |                         |             |  |  |  |

| of WRO = 0)                                                            | <b>6</b> 0        | 8             | _                       | _           |  |  |  |

|                                                                        | υ                 | 3             |                         | <u> </u>    |  |  |  |

| (C = 0, Bits 1215                                                      | <b>**</b> . = • · | _             |                         |             |  |  |  |

| of WRP = N ≠ 0)                                                        | 28+2N             | 8             | -                       | _           |  |  |  |

| soc                                                                    | 22                | 8             | A                       | A           |  |  |  |

| SOCB                                                                   | 22                | 8             | В                       | В           |  |  |  |

| STCR (C = 0)                                                           | 68                | 8             | A                       | _           |  |  |  |

| (1≤C≤7)                                                                | 50                | 8             | В                       | _           |  |  |  |

|                                                                        | 1                 |               |                         |             |  |  |  |

| (C = 8)                                                                | 52                | 8             | В                       | _           |  |  |  |

| (9≤C≤15)                                                               | 66 I              | 8             | Α                       | l –         |  |  |  |

$<sup>^{</sup>ullet}$ Execution time is dependent upon the partial quotient after each clock cycle during execution,

<sup>\*\*\*</sup> The letters A and B refer to the respective tables that follow.

# TMS 9980A/TMS 9981 INSTRUCTION EXECUTION TIMES

#### TABLE 4 (CONTINUED)

| INSTRUCTION                                      | CLOCK CYCLES | MEMORY ACCESS | ADDRESS N    | ODIFICATION*** |  |  |

|--------------------------------------------------|--------------|---------------|--------------|----------------|--|--|

| THO THOU TON                                     | С            | M             | SOURCE       | DESTINATION    |  |  |

| STST                                             | 12           | 4             | <del>-</del> | _              |  |  |

| STWP                                             | 12           | 4             | -            |                |  |  |

| SWPB                                             | 16           | 6             | A            | _              |  |  |

| SZC                                              | 22           | 8             | A            | A              |  |  |

| SZCB                                             | 22           | 8             | В            | В              |  |  |

| тв                                               | 16           | 4             | -            | -              |  |  |

| X**                                              | 12           | 4             | A            | _              |  |  |

| XOP                                              | 52           | 16            | Α            | _              |  |  |

| XOR                                              | 22           | 8             | A            | -              |  |  |

| RESET function                                   | 36           | 10            | _            | _              |  |  |

| LOAD function                                    | 32           | 10            | i –          | _              |  |  |

| Interrupt context switch                         | 32           | 10            | _            | _              |  |  |

| Undefined op codes:                              |              |               |              |                |  |  |

| 0000-01FF, 0320<br>033F, 0C00-0FFF,<br>0780-07FF | 8            | 2             | _            | _              |  |  |

<sup>\*\*\*</sup> Execution time is added to the execution time of the instruction located at the source address.

\*\*\* The letters A and B refer to the respective tables that follow.

# ADDRESS MODIFICATION - TABLE A

| ADDRESSING MODE                                                  | CLOCK CYCLES<br>C | MEMORY ACCESSES |

|------------------------------------------------------------------|-------------------|-----------------|

| WR (T <sub>S</sub> or T <sub>D</sub> = 00)                       | 0                 | 0               |

| WR indirect (T <sub>S</sub> or T <sub>D</sub> = 01)              | 6                 | 2               |

| WR indirect auto-increment ( $T_S$ or $T_D = 11$ )               | 12                | 4               |

| Symbolic (T <sub>S</sub> or $T_D = 10$ , S or $D = 0$ )          | 10                | 2               |

| Indexed (T <sub>S</sub> or T <sub>D</sub> = 10, S or D $\neq$ 0) | 12                | 4               |

# ADDRESS MODIFICATION - TABLE B

| ADDRESSING MODE                                                  | CLOCK CYCLES<br>C | MEMORY ACCESSES M |

|------------------------------------------------------------------|-------------------|-------------------|

| WR (T <sub>S</sub> or T <sub>D</sub> = 00)                       | 0                 | 0                 |

| WR indirect (T <sub>S</sub> or T <sub>D</sub> = 01)              | 6                 | 2                 |

| WR indirect auto-increment ( $T_S$ or $T_D = 11$ )               | 10                | 4                 |

| Symbolic ( $T_S$ or $T_D = 10$ , $S$ or $D = 0$ )                | 10                | 2                 |

| Indexed (T <sub>S</sub> or T <sub>D</sub> = 10, S or D $\neq$ 0) | 12                | 4                 |

## 4. TMS 9980A/TMS 9981 ELECTRICAL SPECIFICATIONS

# 4.1 ABSOLUTE MAXIMUM RATINGS OVER OPERATING FREE-AIR TEMPERATURE RANGE (UNLESS OTHERWISE NOTED)\*

| Supply voltage, VCC (see Note 1)             |    |     |    |     |   |  |  |  |  |  |  |  |  |   | -0.3 to 15 V  |

|----------------------------------------------|----|-----|----|-----|---|--|--|--|--|--|--|--|--|---|---------------|

| Supply voltage, V <sub>DD</sub> (see Note 1) |    |     |    |     |   |  |  |  |  |  |  |  |  |   |               |

| Supply voltage, VBB (see Note 1) (           | 99 | 804 | ٩o | nly | ) |  |  |  |  |  |  |  |  |   | -5.25 to 0 V  |

| All input voltages (see Note 1)              |    |     |    |     |   |  |  |  |  |  |  |  |  |   | −0.3 to 15 V  |

| Output voltage (see Note 1)                  |    |     |    |     |   |  |  |  |  |  |  |  |  |   | −2 V to 7 V   |

| Continuous power dissipation .               |    |     |    |     |   |  |  |  |  |  |  |  |  |   | 1.4 W         |

| Operating free-air temperature range         | је |     |    |     |   |  |  |  |  |  |  |  |  |   | 0°C to 70°C   |

| Storage temperature range                    |    |     |    |     |   |  |  |  |  |  |  |  |  | _ | 55°C to 150°C |

<sup>\*</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTE 1: Under absolute maximum ratings voltage values are with respect to VSS.

# 4.2 RECOMMENDED OPERATING CONDITIONS

|                                    | MiN   | NOM | MAX                | UNIT |