# iDRAGON™ mP6 IA PROCESSOR

A Key Innovation for Information Appliances

Doc#: MKTD6510.0 Version 3.1

## iDragon ™ mP6 IA Processor

The Rise<sup>™</sup> *iDragon*<sup>™</sup> mP6 IA processor is the first sixth generation x86-compatible processor optimized for low power consumption, high-performance information appliance applications such as set-top box, internet box, thin client, home gateway, iPVR and others. The innovative *iDragon*<sup>™</sup> mP6 IA processor is a superscalar and superpipelined IA processor featuring 3 integer units, 3–way MMX technology and a fully pipelined floating point unit giving the users the utmost JAVA\*, multimedia, video streaming and browsing experiences. The innovative circuitry of the *iDragon*<sup>™</sup> mP6 IA processor is optimized for low power consumption with the highest execution parallelism, which provides the excellent system thermal efficiency for enhanced system reliability.

- x86 Instruction Set Enhanced with MMX<sup>™</sup> Technology

- Superscaler & Superpipelined Integer and MMX Architecture

- Excellent JAVA\*, Multimedia and Browsing Performance

- Efficient MPEG4 video Streaming

- Advanced On-chip and System Power Management for Excellent Thermal Efficiency and Reliability

- Facility Gating

- Necessity Switching Only

- Required Selection Only

- SMM Compatible

- Clock Control

- ACPI Compliant

- Advanced Architecture Features

- Advanced Data Dependency Removal Technique

- Innovative Instruction Decode and Branch Prediction

- Dynamic Allocation of Resources

- Separate Code and Data Caches

- 8KB Code and 8KB Data

- Split Line Access Mechanism

- Filtered Tag Prefetching

- High Performance FPU

- IEEE 854 Compliant

- 80 Bit or 64 Bit Precision Results

- IEEE 1149.1 Boundary Scan

- ISO 9001 Wafer Fabrication, Assembly and Test

- Support for Bus Frequencies of 60, 66, 75, 83, 95, and 100 MHz

- CPU/Host Bus Ratio 2X, 2.5X, 3X, 3.5X

- 0.18um CMOS Technology with 3.3V I/O and 2.0V Core

- Low Profile 387-Terminal BGA Package

## All rights reserved. © 2001 Rise<sup>™</sup> Technology

Devices sold by Rise<sup>™</sup> Technology are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Rise<sup>™</sup> Technology makes no warranty, express or implied or by description regarding information set forth herein or regarding the freedom of the described devices from patent infringement. Rise<sup>™</sup> Technology Company reserves the right to discontinue production and change specifications and prices at any time and without notice.

Rise<sup>™</sup> Technology assumes no responsibility for the use of any circuitry other than circuitry embodied in a Rise<sup>™</sup> Technology product. No other circuits, patents or licensees are implied.

Rise<sup>™</sup> Technology products are not authorized for use as components in life systems or as part of life support devices.

Rise<sup>™</sup> and iDragon<sup>™</sup> are trademarks of Rise<sup>™</sup> Technology Company. All other trademarks are properties of respective owners.

Products, brand and corporate names used in this publication are for identification purposes only and may be trademarks of their respective companies.

This document contains information about a product under development at Rise<sup>™</sup> Technology Company and is intended to assist in evaluating this product. This is not a released product and specifications are subject to change without notice.

## **Table of Contents**

| 1 | PROCESSOR ARCHITECTURE OVERVIEW                                                                                                                                                              | 7                    |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|   | 1.1 <i>iDragon™</i> MP6 IA PROCESSOR ARCHITECTURE                                                                                                                                            | 10<br>11<br>11       |

| 2 | PIN REFERENCES                                                                                                                                                                               | 12                   |

|   | 2.1 BGA PACKAGE BALL ASSIGNMENT 2.2 BGA BALL REFERENCES BY TYPE 2.3 SIGNAL DESCRIPTION 2.4 PIN CONNECTIONS 2.4.1 RESERVED Pins 2.4.2 INC Pins 2.4.3 Processor and Host Bus Frequency Control | 14<br>17<br>22<br>22 |

| 3 | ELECTRICAL SPECIFICATIONS                                                                                                                                                                    | 23                   |

|   | 3.1 MAXIMUM RATINGS                                                                                                                                                                          | 24                   |

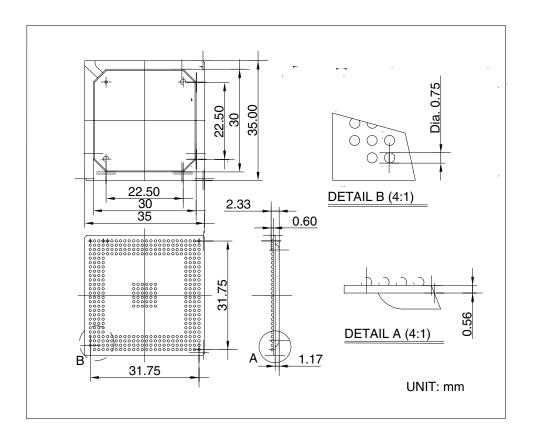

| 4 | MECHANICAL SPECIFICATIONS                                                                                                                                                                    | 37                   |

|   | 4.1 387 BALL BGA MECHANICAL DRAWING                                                                                                                                                          | 37                   |

| 5 | PART NUMBER                                                                                                                                                                                  | 40                   |

## **LIST OF FIGURES**

| FIGURE 1. <i>iDragon™</i> MP6 IA PROCESSOR BLOCK DIAGRAM | 8  |

|----------------------------------------------------------|----|

| FIGURE 2. FPU/MMX UNIT                                   |    |

| FIGURE 3. ARITHMETIC LOGIC UNITS                         | 10 |

| FIGURE 6. BGA PACKAGE TOP VIEW                           | 13 |

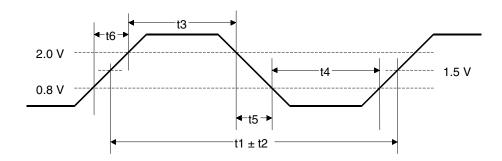

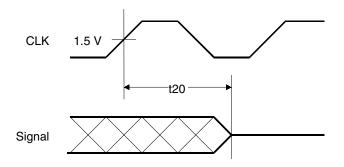

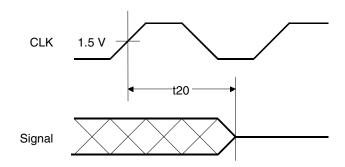

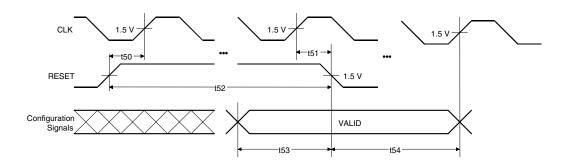

| FIGURE 7A. CLOCK INPUT WAVEFORM                          | 26 |

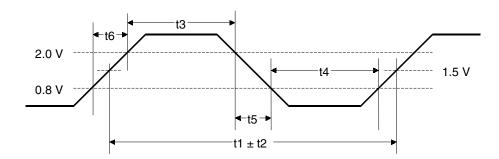

| FIGURE 7B. CLOCK INPUT WAVEFORM                          | 27 |

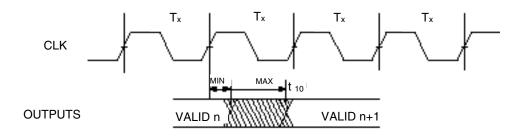

| FIGURE 8A. OUTPUT VALID DELAY WAVEFORM                   | 28 |

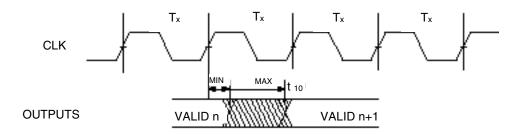

| FIGURE 8B. OUTPUT VALID DELAY WAVEFORM                   | 29 |

| FIGURE 9A. OUTPUT FLOAT DELAY WAVEFORM                   | 30 |

| FIGURE 9B. OUTPUT FLOAT DELAY WAVEFORM                   |    |

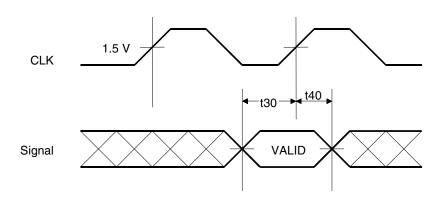

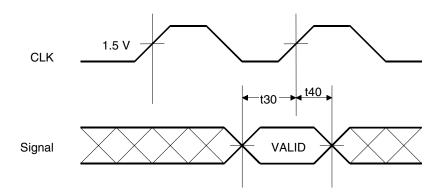

| FIGURE 10A. INPUT SETUP AND HOLD WAVEFORM                | 31 |

| FIGURE 10B. INPUT SETUP AND HOLD WAVEFORM                | 32 |

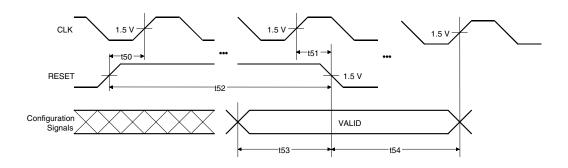

| FIGURE 11A. RESET-CONFIGURATION WAVEFORMS                | 33 |

| FIGURE 11B. RESET-CONFIGURATION WAVEFORMS                | 34 |

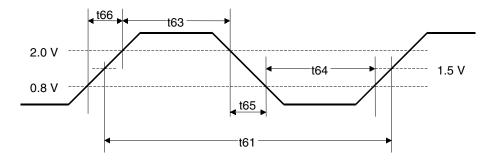

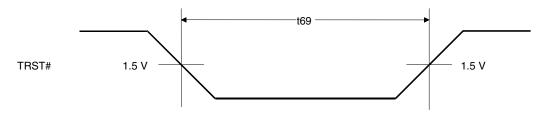

| FIGURE 12. TEST CLOCK INPUT WAVEFORM                     | 35 |

| FIGURE 13. TEST RESET WAVEFORM                           | 36 |

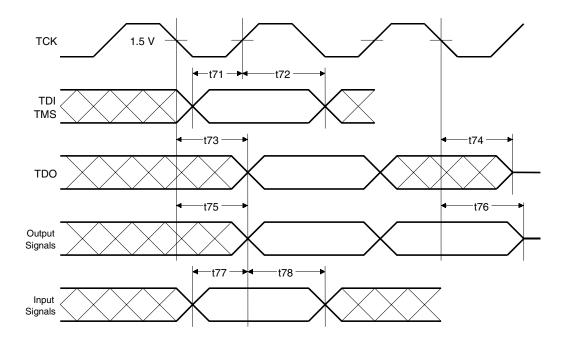

| FIGURE 14. JTAG TEST WAVEFORMS                           | 36 |

| FIGURE 16. BGA OUTLINE DRAWING                           | 37 |

| FIGURE 16. BGA OUTLINE DRAWING (CONTINUED)               | 38 |

| FIGURE 16. BGA OUTLINE DRAWING (CONTINUED)               | 39 |

## **List of Tables**

| Table 1. CPUID Return Values with EAX == 0                                      | 11           |

|---------------------------------------------------------------------------------|--------------|

| TABLE 2. CPUID EAX RETURN VALUES WITH EAX == 1                                  | 11           |

| TABLE 3. CPUID EDX RETURN VALUES WITH EAX == 1                                  | 12           |

| Table 4. BGA Address Ball Reference                                             | 14           |

| Table 5. BGA Data Ball Reference                                                | 14           |

| TABLE 6. BGA CONTROL BALL REFERENCE                                             | 15           |

| TABLE 7. BGA VCC <sub>10</sub> BALL REFERENCE                                   | 15           |

| TABLE 8. BGA VCC BALL REFERENCE                                                 | 16           |

| TABLE 9. BGA VSS BALL REFERENCE                                                 | 16           |

| Table 10. BGA PLL Ball Reference                                                | 16           |

| TABLE 11. BGA RESERVED BALL REFERENCE                                           | 17           |

| Table 12. BGA INC Ball Reference                                                | 17           |

| Table 13. BGA Clock Ball Reference                                              | 17           |

| Table 23. Rise <sup>™</sup> <i>iDragon™</i> мP6 IA Processor Signal Description | 17           |

| TABLE 24. CPU AND HOST BUS FREQUENCY CONTROL                                    | 22           |

| Table 25. Min/Max Ratings                                                       | 23           |

| Table 26. DC Specifications                                                     | 24           |

| Table 27. Power Dissipation Specifications                                      |              |

| Table 28A. AC Specifications26, 28                                              | , 30, 31, 33 |

| Table 28B. AC Specifications27, 29                                              | , 30, 32, 34 |

| Table 29. JTAG AC Specifications                                                | 35           |

## 1 Processor Architecture Overview

The Rise<sup>™</sup> *iDragon™* mP6 IA Processor provides a unique combination of exceptional performance and low power. Designed with the entire personal computing system in mind, the Rise iDragon™ mP6 IA Processor is the ideal choice for power-efficient embedded consumer information appliance, thin server and thin client. The Rise iDragon™ mP6 IA Processor provides software compatibility with Microsoft\* Windows\*, Windows CE\*, MS-DOS\*, QNX\* and UNIX\* along with the large installed base of x86 operating environments and applications. The Rise iDragon™ mP6 IA Processor is also hardware compatible with existent X86 platforms, it offers IA designers the time-to-market advantage by minimizing the application software porting efforts since most of the internet applications were developed based on X86 platforms.

## 1.1 *iDragon™* mP6 IA Processor Architecture

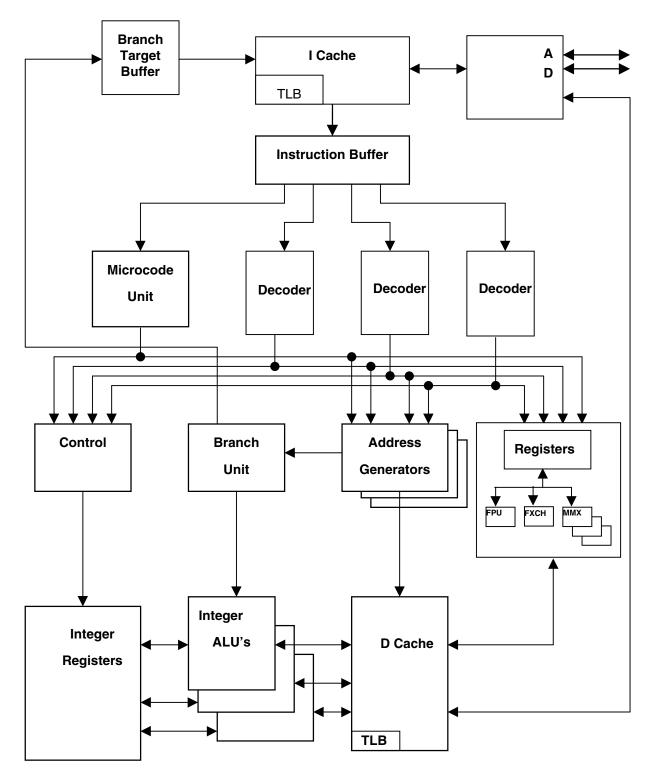

The 3-way superscalar architecture of the Rise  $^{\text{TM}}$   $iDragon^{\text{TM}}$  mP6 IA Processor, utilizing three integer and MMX\* superpipelines, enables instruction tripling. With instruction tripling, three instructions can be issued and completed in a single clock cycle, greatly increasing system throughput. Aggressive instruction pairing and tripling rules combined with advanced branch prediction algorithms ensure that three pipelines of the processor are utilized to their fullest. Figure 1 shows a block diagram of the Rise  $^{\text{TM}}$   $iDragon^{\text{TM}}$  mP6 IA Processor.

The Rise<sup>™</sup> *iDragon* ™ mP6 IA Processor has an eight-stage superpipelined architecture. Each integer pipeline contains six stages. Supporting the integer pipelines is a three–stage, non–interlocking instruction fetch pipeline and a two–stage non–interlocking data cache pipeline which is de-coupled from the decoder. The third stage of the instruction fetch is a buffer that is bypassed when the buffer is empty, resulting in a total of eight stages for the combined pipeline. These supporting pipelines and the eight–stage integer pipelines provide superpipelined efficiency that greatly reduces pipeline stalls, and increases the aggregate instruction completion rate.

To effectively manage its pipeline architecture, the Rise<sup>™</sup> *iDragon*<sup>™</sup> mP6 IA Processor uses innovative branch prediction and instruction decode techniques. A large 512 entry Branch Target Buffer (BTB), and an 8–entry call–return stack provide the base from which advanced branch prediction algorithms operate. By storing return addresses in its deep call–return stack, the Rise *iDragon* mP6 IA Processor is able to accurately predict return targets, even from nested subroutines.

Dual Instruction Stream Execution (DISE) is a unique feature that allows instructions to be decoded from three streams and issued from two different instruction streams simultaneously. Up to eight unresolved branches may simultaneously be operated upon by instruction fetch and integer pipelines. Pairing and tripling rules combined with the ability to decode from multiple streams tremendously increases the total instruction throughput.

To reduce pipeline stalls and to improve data movement efficiency, the Rise  $^{\text{TM}}$  *iDragon*  $^{\text{TM}}$  mP6 IA Processor resolves data dependency conflicts with the following features:

- Register Re–mapping

- Operand Forwarding

- Result Forwarding

- Zero Cycle Data Bypass

- Arithmetic Pairing

Each of these features reduces typical read after write, write after read, and write after write types of data dependencies. This allows the Rise  $^{\text{TM}}$   $iDragon^{\text{TM}}$  mP6 IA Processor to simultaneously execute pairs of instructions that other processors cannot.

FIGURE 1.  $iDragon^{TM}$  mP6 IA PROCESSOR BLOCK DIAGRAM

Doc#: MKTD6510.0 Version 3.1

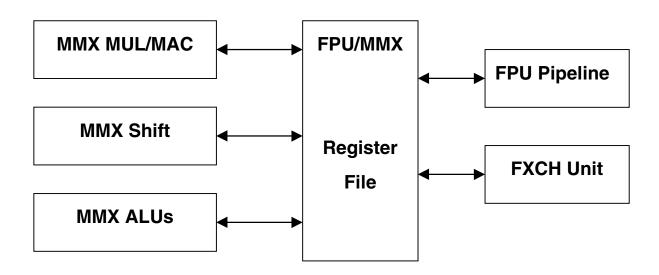

The integrated Floating Point Unit (FPU) of the processor has been designed as a four stage parallel operation pipeline. This high performance FPU produces 80 bit results and conforms to IEEE Standards 854 and 754. The Rise<sup>™</sup> *iDragon*<sup>™</sup> mP6 IA Processor can execute up to two floating point operations in the same cycle.

Three pipelines in the MMX<sup>\*</sup> Unit can execute up to three instructions per cycle in parallel and can resolve data dependency (twinning) to increase performance. The MMX Unit is geared for high performance multimedia such as image processing, video conferencing, soft DVD, and soft modem. Figure 2 depicts the multimedia features.

FIGURE 2. FPU/MMX UNIT

A 16 KByte L1 split cache design improves instruction and data handling, depending on the individual need. The instruction ("I") cache, uses a split–line access mechanism to ensure that up to 16 bytes of data can be accessed with each cycle, even if the data spans multiple lines.

The data ("D") cache utilizes eight interleaved banks to minimize conflicts between accesses. The "D" cache is dual ported (the tags are triple ported) to allow two read accesses, two write accesses, and a snoop access — all in the same cycle.

The "D" cache also contains a filtered tag prefetching mechanism to prefetch data while minimizing bus traffic and cache pollution. There is no misalignment penalty — an important factor for multimedia (e.g., MPEG playback).

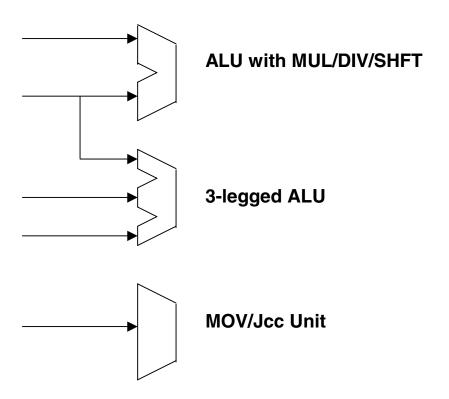

The Integer Arithmetic Logic Units (ALUs) implement features that eliminate data dependency. The three major units in the ALU include the MUL/DIV/Shift Units, the 3-legged inputs, and the MOV/Jcc Units, which are illustrated in Figure 3.

FIGURE 3. ARITHMETIC LOGIC UNITS

The following instruction stream can be accomplished in one cycle as the 3-legged ALU helps to collapse dependencies:

Dynamic Allocation of Resources (DAR) is a unique feature which provides an out–of–sequence–like execution technique utilized by the Rise  $^{\text{TM}}$  iDragon  $^{\text{TM}}$  mP6 IA Processor to improve instruction throughput. DAR breaks the typical resource–to–pipeline affinity found in most superscalar designs by allowing address generators, execution units, etc. of the processor to be allocated to various pipelines. Through DAR, resource utilization increases and instruction throughput is maximized.

## 1.2 Power Management

The Rise  $^{\text{TM}}$   $iDragon^{\text{TM}}$  mP6 IA Processor is instruction and pin compatible with the Pentium processor implementation of the System Management Mode (SMM), Stop Grant State, Auto Halt Power Down State and Stop Clock State. The Rise  $^{\text{TM}}$   $iDragon^{\text{TM}}$  mP6 IA Processor is also compliant with the Advanced Configuration and Power Interface (ACPI) Specification.

In addition to system level power saving facilities, the Rise  $^{\text{\tiny{TM}}}$   $iDragon^{\text{\tiny{TM}}}$  mP6 IA Processor has the following internal architectural mechanisms that minimize power dissipation:

that are not needed for the current operation.

Necessity Switching Only (NSO)

NSO reduces dynamic power dissipation by preventing

unnecessary circuit switching.

Required Selection Only (RSO)

RSO allows the processor to address and access only the

minimum required amount of data from its various cache and ROM structures. RSO minimizes dynamic power dissipation by

limiting the number of sense amplifiers driven per access.

No action is required by the system designer or the end user to realize the power saving benefits of these architectural features.

## 1.3 Testability

To assist in board level testing, the Rise  $^{\text{TM}}$  iDragon  $^{\text{TM}}$  mP6 IA Processor implements IEEE Standard 1149.1 Boundary Scan (JTAG). Electrical specifications for the JTAG interface are defined in Table 29.

## 1.4 Compatibility

In general, the Rise<sup>™</sup> *iDragon*<sup>™</sup> mP6 IA Processor is instruction and pin compatible with other advanced Socket 7– or Super Socket 7–based x86 processor such as the Pentium<sup>®</sup> processor with MMX<sup>\*</sup> Technology. However, certain features of the Pentium processor that are not needed or used in embedded IA applications are not supported. Such features include multiprocessor and server capabilities as well as certain extended model–specific features as defined by the CPUID instruction.

#### 1.4.1 Omitted Multiprocessing and Server Capabilities

The Rise  $^{\text{TM}}$   $iDragon^{\text{TM}}$  mP6 IA Processor is designed to specifically meet the needs of the power-efficient environments. The Rise  $^{\text{TM}}$   $iDragon^{\text{TM}}$  mP6 IA Processor does not provide the Pentium compatible server environment features of multiprocessing, APIC, and Master/Checker functional redundancy.

#### 1.4.2 CPUID Instruction

The CPUID instruction is supported on the Rise<sup>™</sup> *iDragon*<sup>™</sup> mP6 IA Processor, and return values for the CPUID instruction are shown in Tables 1 through 3. For comparison, the Intel P55C processor return values are included in the tables.

TABLE 1. CPUID RETURN VALUES WITH EAX == 0

| REGISTER    | iDragon™mP6  | P55C         |

|-------------|--------------|--------------|

| EAX         | 1            | 1            |

| EBX:ECX:EDX | RiseRiseRise | GenuineIntel |

TABLE 2. CPUID EAX RETURN VALUES WITH EAX == 1

| PROCESSOR    | [13:12]<br>Type ID | [11:8]<br>Family ID | [7:4]<br>Model ID | [3:0]<br>Stepping ID |

|--------------|--------------------|---------------------|-------------------|----------------------|

| iDragon™ mP6 | 0                  | 5                   | 2                 | Varies               |

| P55C         | 0                  | 5                   | 4                 | Varies               |

TABLE 3. CPUID EDX RETURN VALUES WITH EAX == 1

| EDX Bits – Meaning                        | iDRAGON™ mP6 | P55C | Notes |

|-------------------------------------------|--------------|------|-------|

| 0 - FP present                            | 1            | 1    |       |

| 1 - VM86 Extensions (VME)                 | 0            | 1    |       |

| 2 - Debugging Extensions                  | 0            | 1    |       |

| 3 - Page Size Extensions                  | 0            | 0    |       |

| 4 - Time Stand Counter (TSC) supported    | 1            | 1    |       |

| 5 - Model Specific Registers present      | 0            | 1    |       |

| 6 - PAE supported                         | 0            | 0    |       |

| 7 - Machine Check Exception               | 0            | 1    |       |

| 8 - CMPXCHG8B instruction                 | 0            | 1    | 1     |

| 9 - APIC supported                        | 0            | 1    |       |

| 10:11 - RESERVED                          | -            | -    |       |

| 12 - Memory Range Registers               | 0            | 0    |       |

| 13 - PTE global Bit supported             | 0            | 0    |       |

| 14 - Machine Check Architecture supported | 0            | 0    |       |

| 15 - Conditional Move supported           | 0            | 0    |       |

| 16:22 - RESERVED                          | -            | -    |       |

| 23 - MMX supported                        | 1            | 1    |       |

| 24:31 - RESERVED                          | -            | -    |       |

#### Notes:

1. The CMPXCHG8B instruction is supported and always enabled on the *iDragon™* mP6 IA Processor; however, the default CPUID function bit is set to 0 to circumvent a reported bug in Windows NT.

## 2 Pin References

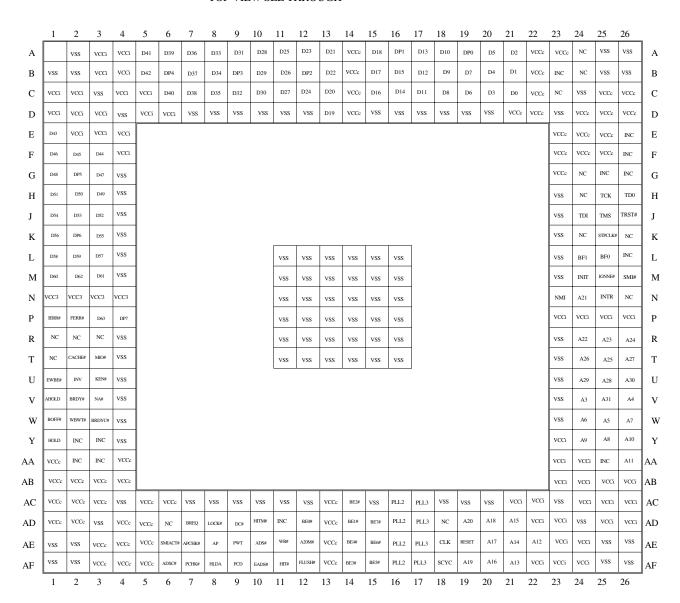

The Rise  $^{\text{TM}}$   $iDragon^{\text{TM}}$  mP6 IA Processor is available in ball grid array package. (BGA) to provide excellent solutions for reduced footprint, lower profile Information Appliances. This BGA package has 387 balls arranged as an array matrix placement. The BGA ball references are depicted in the following figures and listed in the following tables.

## 2.1 BGA Package Ball Assignment

#### TOP VIEW SEE THROUGH

FIGURE 6. BGA PACKAGE TOP VIEW

Doc#: MKTD6510.0 13

# 2.2 BGA Ball References by Type

**TABLE 4. BGA ADDRESS BALL REFERENCE**

|      | ADDRESS |      |      |      |      |      |     |      |     |  |  |  |  |  |

|------|---------|------|------|------|------|------|-----|------|-----|--|--|--|--|--|

| Addr | Loc     | Addr | Loc  | Addr | Loc  | Addr | Loc | Addr | Loc |  |  |  |  |  |

| А3   | V24     | A9   | Y24  | A15  | AD21 | A21  | N24 | A27  | T26 |  |  |  |  |  |

| A4   | V26     | A10  | Y26  | A16  | AF20 | A22  | R24 | A28  | U25 |  |  |  |  |  |

| A5   | W25     | A11  | AA26 | A17  | AE20 | A23  | R25 | A29  | U24 |  |  |  |  |  |

| A6   | W24     | A12  | AE22 | A18  | AD20 | A24  | R26 | A30  | U26 |  |  |  |  |  |

| A7   | W26     | A13  | AF21 | A19  | AF19 | A25  | T25 | A31  | V25 |  |  |  |  |  |

| A8   | Y25     | A14  | AE21 | A20  | AD19 | A26  | T24 |      |     |  |  |  |  |  |

TABLE 5. BGA DATA BALL REFERENCE

|      |     |      |     | DA   | TA  |      |     |      |     |

|------|-----|------|-----|------|-----|------|-----|------|-----|

| Data | Loc |

| D0   | C21 | D13  | A17 | D26  | B11 | D39  | A6  | D52  | J3  |

| D1   | B21 | D14  | C16 | D27  | C11 | D40  | C6  | D53  | J2  |

| D2   | A21 | D15  | B16 | D28  | A10 | D41  | A5  | D54  | J1  |

| D3   | C20 | D16  | C15 | D29  | B10 | D42  | B5  | D55  | K3  |

| D4   | B20 | D17  | B15 | D30  | C10 | D43  | E1  | D56  | K1  |

| D5   | A20 | D18  | A15 | D31  | A9  | D44  | F3  | D57  | L3  |

| D6   | C19 | D19  | D13 | D32  | C9  | D45  | F2  | D58  | L1  |

| D7   | B19 | D20  | C13 | D33  | A8  | D46  | F1  | D59  | L2  |

| D8   | C18 | D21  | A13 | D34  | B8  | D47  | G3  | D60  | M1  |

| D9   | B18 | D22  | B13 | D35  | C8  | D48  | G1  | D61  | M3  |

| D10  | A18 | D23  | A12 | D36  | A7  | D49  | НЗ  | D62  | M2  |

| D11  | C17 | D24  | C12 | D37  | B7  | D50  | H2  | D63  | P3  |

| D12  | B17 | D25  | A11 | D38  | C7  | D51  | H1  |      |     |

Doc#: MKTD6510.0 14

**TABLE 6. BGA CONTROL BALL REFERENCE**

|        | CONTROL |      |        |      |      |         |      |      |  |  |  |

|--------|---------|------|--------|------|------|---------|------|------|--|--|--|

| Signal | Loc     | Туре | Signal | Loc  | Туре | Signal  | Loc  | Туре |  |  |  |

| A20M#  | AE12    | I    | DP0    | A19  | I/O  | INV     | U2   | I    |  |  |  |

| ADS#   | AE10    | 0    | DP1    | A16  | I/O  | KEN#    | U3   | I    |  |  |  |

| ADSC#  | AF6     | 0    | DP2    | B12  | I/O  | LOCK#   | AD8  | 0    |  |  |  |

| AHOLD  | V1      | I    | DP3    | B9   | I/O  | M/IO#   | Т3   | 0    |  |  |  |

| AP     | AE8     | I/O  | DP4    | B6   | I/O  | NA#     | V3   | I    |  |  |  |

| APCHK# | AE7     | 0    | DP5    | G2   | I/O  | NMI     | N23  | Ι    |  |  |  |

| BE0#   | AD12    | 0    | DP6    | K2   | I/O  | PCD     | AF9  | 0    |  |  |  |

| BE1#   | AD14    | 0    | DP7    | P4   | I/O  | PCHK#   | AF7  | 0    |  |  |  |

| BE2#   | AC14    | 0    | EADS#  | AF10 | I    | PWT     | AE9  | 0    |  |  |  |

| BE3#   | AF14    | 0    | EWBE#  | U1   | I    | RESET   | AE19 | I    |  |  |  |

| BE4#   | AE14    | 0    | FERR#  | P2   | 0    | SCYC    | AF18 | 0    |  |  |  |

| BE5#   | AF15    | 0    | FLUSH# | AF12 | I    | SMI#    | M26  | I    |  |  |  |

| BE6#   | AE15    | 0    | HIT#   | AF11 | 0    | SMIACT# | AE6  | 0    |  |  |  |

| BE7#   | AD15    | 0    | HITM#  | AD10 | 0    | TCK     | H25  | I    |  |  |  |

| BOFF#  | W1      | I    | HLDA   | AF8  | 0    | TDI     | J24  | I    |  |  |  |

| BRDY#  | V2      | I    | HOLD   | Y1   | I    | TDO     | H26  | 0    |  |  |  |

| BRDYC# | W3      | I    | IERR#  | P1   | 0    | TMS     | J25  | I    |  |  |  |

| BREQ   | AD7     | 0    | IGNNE# | M25  | I    | TRST#   | J26  | I    |  |  |  |

| CACHE# | T2      | 0    | INIT   | M24  | I    | WR#     | AE11 | 0    |  |  |  |

| D/C#   | AD9     | 0    | INTR   | N25  | I    | WB/WT#  | W2   | I    |  |  |  |

TABLE 7. BGA  ${

m VCC}_{\rm lo}$  BALL REFERENCE

|      | VCCio |      |      |      |      |      |      |  |  |  |  |  |  |  |

|------|-------|------|------|------|------|------|------|--|--|--|--|--|--|--|

| А3   | A4    | В3   | B4   | C1   | C2   | C4   | C5   |  |  |  |  |  |  |  |

| D1   | D2    | D3   | D5   | D6   | E2   | E3   | E4   |  |  |  |  |  |  |  |

| F4   | N1    | N2   | N3   | N4   | P23  | P24  | P25  |  |  |  |  |  |  |  |

| P26  | Y23   | AA23 | AA24 | AB23 | AB24 | AB25 | AB26 |  |  |  |  |  |  |  |

| AC21 | AC22  | AC24 | AC25 | AC26 | AD22 | AD23 | AD25 |  |  |  |  |  |  |  |

| AD26 | AE23  | AE24 | AF22 | AF23 | AF24 |      |      |  |  |  |  |  |  |  |

## TABLE 8. BGA $VCC_{CORE}$ BALL REFERENCE

|     | VCCCORE |      |     |     |     |      |     |  |  |  |  |  |  |  |

|-----|---------|------|-----|-----|-----|------|-----|--|--|--|--|--|--|--|

| A14 | A22     | A23  | B14 | B22 | C14 | C22  | C25 |  |  |  |  |  |  |  |

| C26 | D14     | D21  | D22 | D24 | D25 | D26  | E23 |  |  |  |  |  |  |  |

| E24 | E25     | F23  | F24 | F25 | G23 | AA1  | AA4 |  |  |  |  |  |  |  |

| AB1 | AB2     | AB3  | AB4 | AC1 | AC2 | AC3  | AC5 |  |  |  |  |  |  |  |

| AC6 | AC13    | AD1  | AD2 | AD4 | AD5 | AD13 | AE3 |  |  |  |  |  |  |  |

| AE4 | AE5     | AE13 | AF3 | AF4 | AF5 | AF13 |     |  |  |  |  |  |  |  |

## **TABLE 9. BGAVSS BALL REFERENCE**

|      | VSS  |      |      |      |      |      |      |      |  |  |  |  |  |

|------|------|------|------|------|------|------|------|------|--|--|--|--|--|

| A2   | A25  | A26  | B1   | B2   | B25  | B26  | СЗ   | C24  |  |  |  |  |  |

| D4   | D7   | D8   | D9   | D10  | D11  | D12  | D15  | D16  |  |  |  |  |  |

| D17  | D18  | D19  | D20  | D23  | G4   | H4   | H23  | J4   |  |  |  |  |  |

| J23  | K4   | K23  | L4   | L11  | L12  | L13  | L14  | L15  |  |  |  |  |  |

| L16  | L23  | M4   | M11  | M12  | M13  | M14  | M15  | M16  |  |  |  |  |  |

| M23  | N11  | N12  | N13  | N14  | N15  | N16  | P11  | P12  |  |  |  |  |  |

| P13  | P14  | P15  | P16  | R4   | R11  | R12  | R13  | R14  |  |  |  |  |  |

| R15  | R16  | R23  | T4   | T11  | T12  | T13  | T14  | T15  |  |  |  |  |  |

| T16  | T23  | U4   | U23  | V4   | V23  | W4   | W23  | Y4   |  |  |  |  |  |

| AC4  | AC7  | AC8  | AC9  | AC10 | AC11 | AC12 | AC15 | AC18 |  |  |  |  |  |

| AC19 | AC20 | AC23 | AD3  | AD24 | AE1  | AE2  | AE25 | AE26 |  |  |  |  |  |

| AF1  | AF2  | AF25 | AF26 |      |      |      |      |      |  |  |  |  |  |

#### **TABLE 10. BGA PLL BALL REFERENCE**

| PLL3 - VCC10        |  |  |  |  |  |  |

|---------------------|--|--|--|--|--|--|

| AC17 AD17 AE17 AF17 |  |  |  |  |  |  |

| PLL2 - VCCcore      |  |  |  |  |  |  |

| AC16 AD16 AE16 AF16 |  |  |  |  |  |  |

**TABLE 11. BGA RESERVED BALL REFERENCE**

| RESERVED (NC) |          |     |     |     |     |  |  |

|---------------|----------|-----|-----|-----|-----|--|--|

| T1            | R2       | R3  | R1  | C23 | A24 |  |  |

| B24           | G24      | H24 | K24 | K26 | N26 |  |  |

| AD18          | AD18 AD6 |     |     |     |     |  |  |

#### **TABLE 12. BGA INC BALL REFERENCE**

| INC                           |  |  |  |  |  |  |  |

|-------------------------------|--|--|--|--|--|--|--|

| AD11 E26 G26 AA25 L26 G25 F26 |  |  |  |  |  |  |  |

| AA3 AA2 Y2 Y3 B23             |  |  |  |  |  |  |  |

## TABLE 13. BGA CLOCK BALL REFERENCE

| CLOCK                                |                                  |  |  |  |  |  |     |

|--------------------------------------|----------------------------------|--|--|--|--|--|-----|

| Signal                               | Signal Loc Signal Loc Signal Loc |  |  |  |  |  |     |

| BF0 L25 BF1 L24 CLK AE18 STPCLK# K25 |                                  |  |  |  |  |  | K25 |

# 2.3 Signal Description

The following table lists all signals supported by the. Rise  $^{\text{TM}}$   $iDragon^{\text{TM}}$  mP6 IA Processor. Since multiprocessor and server–related features are not supported by the Rise  $^{\text{TM}}$   $iDragon^{\text{TM}}$  mP6 IA Processor, signals are not listed for them.

TABLE 23. RISE™ *iDragon™* mP6 IA PROCESSOR SIGNAL DESCRIPTION

| SIGNAL | I/O<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A20M#  | I           | The <b>address bit 20 mask</b> causes the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor to emulate the address wraparound at 1 Mbyte which occurs on the 8086 by masking physical address bit 20 (A20) before performing an internal cache access or driving a memory cycle. A20M# is asserted when the Rise <i>iDragon</i> <sup>™</sup> mP6 IA Processor is in real mode and is undefined when it is in protected mode. |

| A31-A3 | I/O         | Address lines and byte enables (BE#7–BE#0) define memory or I/O access. The external system drives A31–A5 for cache inquiry cycles.                                                                                                                                                                                                                                                                                                       |

| ADS#   | 0           | The <b>address strobe</b> indicates that a new valid memory or I/O bus cycle is currently being driven by the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor.                                                                                                                                                                                                                                                             |

| ADSC#  | 0           | The address strobe copy is functionally identical to ADS#.                                                                                                                                                                                                                                                                                                                                                                                |

| SIGNAL    | I/O<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AHOLD     | I           | The <b>address hold</b> input allows another bus master access to the address of the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor. The Rise <i>iDragon</i> <sup>™</sup> mP6 IA Processor stops driving the address lines (A31–A3) and AP in the next clock, while the rest of the bus remains active so data can be returned or driven for previously issued bus cycles.                    |  |

| AP        | I/O         | Address parity is driven with even parity information on Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor –generated cycles in the same clock that the address is driven. During cache inquire cycles, this pin is sampled in the same clock as EADS# to ensure that correct parity check status is indicated by APACHK# of the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor. |  |

| APCHK#    | 0           | If the Rise <sup>™</sup> <i>iDragon™</i> mP6 IA Processor detects a parity error on the address bus during inquire cycles, the <b>address parity check</b> status pin is asserted two clocks after EADS# is sampled active and it remains active for one clock cycle.                                                                                                                                         |  |

| BE7#-BE0# | 0           | Byte enables determine which data bytes are transferred for the current cycle. Byte enables and address lines A31–A3 are driven in the same clock.                                                                                                                                                                                                                                                            |  |

| BF[1:0]   | I           | The <b>bus frequency</b> inputs are sampled at <b>RESET</b> to determine the CPU-to-bus frequency ratio. See Table 24 for Host Bus Frequency Selections.                                                                                                                                                                                                                                                      |  |

| BOFF#     | I           | The <b>backoff</b> input forces the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor to abort all outstanding bus. The Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor floats all pins to enter the bus hold state in the next clock. When BOFF# is negated, the Rise <i>iDragon</i> <sup>™</sup> mP6 IA Processor restarts the aborted bus cycles.                              |  |

| BRDY#     | I           | Burst ready input indicates that the external system has presented valid data on the data pins in response to a read, or that the external system has accepted Rise <sup>™</sup> iDragon <sup>™</sup> mP6 IA Processor data in response to a write request. The processor samples BRDY# in the second and subsequent clocks of a bus cycle.                                                                   |  |

| BRDYC#    | I           | The <b>burst ready (copy)</b> is functionally identical to BRDY#.                                                                                                                                                                                                                                                                                                                                             |  |

| BREQ      | 0           | The <b>bus request</b> output indicates to the external system that the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor has a bus cycle pending internally.                                                                                                                                                                                                                                    |  |

| CACHE#    | 0           | The <b>cache</b> pin indicates internal "cache–ability" of a read cycle or a burst write–back cycle. If this pin is driven inactive during a read cycle, the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor does not cache the returned data, regardless of the state of the KEN# pin. The <b>cache</b> pin is also used to determine the cycle length.                                       |  |

| CLK       | I           | <b>Clock</b> input provides the fundamental timing for the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor. External timing parameters are specified with reference to the rising edge of CLK.                                                                                                                                                                                                 |  |

| SIGNAL  | I/O<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D63-D0  | I/O         | <b>Data lines</b> are three–state, bi-directional signals. Lines D7–D0 define the least significant byte of the data bus, and lines D63–D56 define the most significant. The data bus is driven only while a write cycle is active. During reads, the CPU samples the data bus when BRDY# is returned.                                                                                                                                                                                                                                                                                            |  |  |  |

| D/C#    | 0           | The <b>data/code</b> is driven valid in the same clock that the ADS# signal is asserted. D/C# distinguishes between data and code or special cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| DP7-DP0 | I/O         | The <b>data parity</b> signals provide parity for the data bus — one for each byte of the data bus. These signals are driven by the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor with even parity information on writes in the same clock as the data. Even parity information must be driven back to the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor on these pins in the same clock as the data to ensure that the correct parity check status is indicated by the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor. DP7 applies to D63-D56. |  |  |  |

| EADS#   | I           | The <b>external address strobe</b> indicates a valid cache inquiry address is being driven onto the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor address bus in an inquire cycle.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| EWBE#   | I           | The <b>external write buffer empty</b> indicates that there are no pending write cycles in the external system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| FEER#   | 0           | The <b>floating-point error</b> pin is driven active when an unmasked floating point error occurs during the execution of the FPU instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| FLUSH#  | I           | The <b>flush</b> input forces the Rise <sup>™</sup> <i>iDragon</i> ™ mP6 IA Processor to flush the cache by writing back all modified lines in the data cache and invalidating its internal caches.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| HIT#    | 0           | <b>Hit</b> indicates that a current cache inquiry address has been found on a valid line in either the data or instruction cache. This pin is valid two clocks after EADS# is sampled as asserted, and remains valid until the next cache inquiry cycle.                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| HITM#   | 0           | The <b>hit modified line</b> indicates that a current cache inquiry address has been found in the cache and dirty data exists in the cache line. It inhibits another bus master from accessing the data until the line is completely written back.                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| HLDA    | 0           | The <b>bus hold acknowledge</b> indicates that a hold request being driven to the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor on the <b>HOLD</b> pin. When leaving bus hold, the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor resumes driving the bus and HLDA is driven inactive. If a bus cycle pending, the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor is driven one clock cycle after HLDA is de-asserted.                                                                                                                           |  |  |  |

| HOLD    | I           | The <b>bus hold request</b> indicates that another bus master has requested the control of the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor host bus. After completing all outstanding bus cycles, the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor enters a bus hold state until HOLD is de-asserted. The Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor recognizes HOLD during RESET but not in LOCK cycles.                                                                                                                                |  |  |  |

| SIGNAL | I/O<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IERR#  | 0           | The internal error pin indicates internal parity errors.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| IGNNE# | I           | The <b>ignore numeric error</b> forces the Rise <sup><math>^{\text{TM}}</math></sup> <i>iDragon</i> $^{\text{TM}}$ mP6 IA Processor to ignore any pending unmasked numeric exception and to continue executing floating-point instructions as long as this pin is asserted.                                                                                                                                                                      |  |  |  |

| INIT   | I           | The <b>initialization</b> input forces the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor to begin execution in a known state which is the same as the state after RESET except that the internal caches, write buffers, and floating-point registers retain their values. If INIT is sampled high when RESET transitions from high to low, the processor performs the build–in self test prior to initiating program execution. |  |  |  |

| INTR   | I           | The <b>maskable interrupt</b> input indicates that an external interrupt has been generated. When the IF bit of the EFLAGS register is set, the Rise $^{\text{IM}}$ $iDragon^{\text{TM}}$ mP6 IA Processor generates two locked interrupt acknowledge bus cycles and begins execution of an interrupt service routine after executing the current instruction.                                                                                   |  |  |  |

| INV    | I           | The <b>invalidation</b> input ascertains the final cache line state to be invalid or shared in a cache inquiry hit. It is sampled in the same clock with the cache inquiry address and the <b>EADS#</b> .                                                                                                                                                                                                                                        |  |  |  |

| KEN#   | I           | The <b>cache enable</b> input allows the data being returned from the current cycle to be cacheable. When the Rise $^{\text{TM}}$ $iDragon^{\text{TM}}$ mP6 IA Processor generates a cycle that can be cached (CACHE# asserted) and KEN# is active, the cycle is transformed into a 32–byte cache line fill cycle.                                                                                                                               |  |  |  |

| LOCK#  | 0           | The <b>lock</b> pin indicates that the current bus cycle is locked. The Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor does not accept a bus hold request from another bus master while LOCK# is asserted                                                                                                                                                                                                                        |  |  |  |

| M/IO#  | 0           | The <b>memory/input-output</b> is driven valid in the same clock as the <b>ADS#</b> . M/IO# distinguishes between memory and I/O cycles.                                                                                                                                                                                                                                                                                                         |  |  |  |

| NA#    | I           | The <b>next address</b> input indicates that the external memory system is ready to accept a new bus cycle, even though all data transfers for the current cycle are not yet complete. The Rise iDragon™ mP6 IA Processor issues ADS# for a pending cycle two clocks after NA# is asserted.                                                                                                                                                      |  |  |  |

| NMI    | I           | The <b>non–maskable interrupt</b> request signal indicates that an external non–maskable interrupt has been generated. The Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor suspends execution of the current instruction stream and begins execution of a NMI interrupt service routine.                                                                                                                                          |  |  |  |

| PCD    | 0           | The <b>page cache disable</b> pin reflects the state of the PCD bit in CR3, the Page Directory Entry, or the Page Table Entry. The PCD provides an external cache–ability indication on a page–by–page basis.                                                                                                                                                                                                                                    |  |  |  |

| SIGNAL   | I/O<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PCHK#    | 0           | The <b>parity check</b> output indicates a data bus parity error in a data read cycle It is driven with parity status two clocks after BRDY# is returned. Parity is checked only for the bytes on which valid data are returned.                                                                                                                                                                                                                                                                 |  |  |  |  |

| PWT      | 0           | The <b>page write through</b> pin reflects the state of the PWT bit in CR3, the page Directory Entry, or the Page Table Entry. The PWT pin is used to provide an external write back indication on a page—by—page basis. <b>PWT</b> has higher priority than <b>WB/WT#</b> .                                                                                                                                                                                                                     |  |  |  |  |

| RESET    | I           | <b>RESET</b> forces the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor to begin execution at a known state. All data in the internal caches is invalidated.                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| SCYC     | 0           | The <b>split cycle</b> is asserted during misaligned LOCKed transfers to indicate that more than two cycles are locked together. This signal is defined for locked cycles only.                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| SMI#     | I           | The <b>system management interrupt</b> causes the Rise <sup>™</sup> <i>iDragon</i> mP6 IA Processor to System Management Mode. <b>SMI</b> has higher priority than <b>NMI</b> .                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| SMIACT#  | 0           | The <b>system management interrupt active</b> indicates that the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor is in System Management Mode.                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| STPCLK#  | I           | The <b>stop clock</b> input is a request from the system to stop the internal clock of the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor. When the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor recognizes STPCLK#, it stops execution on the next instruction boundary and generates a stop grant acknowledge cycle. When STPCLK# is asserted, the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor still responds to external snoop requests. |  |  |  |  |

| TCK      | I           | The <b>testability clock (JTAG)</b> provides the clocking function for the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor boundary scan in accordance with the IEEE1149.1 Boundary Scan interface. It is used to clock state information and data into and out of the Rise iDragon mP6 IA Processor during boundary scan.                                                                                                                                                        |  |  |  |  |

| TDI      | I           | The <b>test data input (JTAG)</b> is a serial data input for the test logic. Data and instructions are shifted into the Rise <sup>™</sup> <i>iDragon</i> <sup>™</sup> mP6 IA Processor on this pin on the rising edge of TCK for testing.                                                                                                                                                                                                                                                        |  |  |  |  |

| TDO      | 0           | The <b>test data output (JTAG)</b> is a serial data output of the test logic. Data and instructions are shifted out of the Rise <sup>TM</sup> $iDragon^{TM}$ mP6 IA Processor on this pin on the falling edge of TCK for testing.                                                                                                                                                                                                                                                                |  |  |  |  |

| TMS      | I           | The <b>test mode select (JTAG)</b> signal sampled on the rising edge of TCK controls the sequence of state changes of the boundary scan test logic.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| TRST#    | I           | Test reset (JTAG) input asynchronously initializes boundary scan test logic.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| VCC2DET# | 0           | <b>VCC2 detect</b> is always driven low by the Rise <sup>™</sup> <i>iDragon™</i> mP6 IA Processor. It is not available in regular package, only available in OEM BPGA package.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| SIGNAL | I/O<br>TYPE | DESCRIPTION                                                                                                                                                                           |

|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W/R#   | 0           | <b>Write/read</b> is driven valid in the same clock period that the ADS# signal is asserted. It distinguishes between write and read cycles for the current memory or I/O bus access. |

| WB/WT# | I           | The write back/write through input defines the cache write policy to a data cache line as either write back or write through on a line-by-line basis.                                 |

## 2.4 Pin Connections

For reliable operation, any unused active high input must be tied to GND (VSS) and any unused active low input must be tied to VCC<sub>IO</sub>; however, if an unused input has an internal pull–up or pull–down resistor, then no external connection is required. Signals with internal pull–up or pull–down resistors are listed below (all internal pull–up and pull–down resistors are 33 K $\Omega$  ± 50%). If an external connection is made to an input with an internal resistor, it must be a direct connection (< 1 k $\Omega$  resistance). Unused inputs that do not have internal resistors should be connected to GND or VCC<sub>IO</sub> using a 20 k $\Omega$  resistor.

Signals with internal pull-down resistors include: BF0, CLK

Signals with internal pull-up resistors include: BF1, BRDY#, BRDYC#, SMI#, STPCLK#, TCK#, TDI#, TMS#, TRST#

#### 2.4.1 RESERVED Pins

Pins labeled RESERVED must not be connected; if they are connected, they can cause the processor to produce unexpected results or to otherwise malfunction.

#### 2.4.2 INC Pins

Pins labeled INC have no connection to the processor die and it is recommended (though not required) that these pins be left unconnected.

#### 2.4.3 Processor and Host Bus Frequency Control

The Rise<sup>™</sup> *iDragon*<sup>™</sup> mP6 IA Processor operates at a multiple of the host bus frequency. Table 24 lists the relationship between BF1–BF0 values and the consequent CPU–to–host bus ratios. Both BF0 and BF1 are active high signals so the corresponding pins should be tied to VCC<sub>10</sub> or VSS to obtain the desired CPU–to–host bus ratio. The processor uses internal pull–up/pull–down resistors to force a default CPU–to–host bus ratio of 2:1.

Table 24. CPU and Host Bus Frequency Control

|     |     |                       | EXAM                  | PLES                  |

|-----|-----|-----------------------|-----------------------|-----------------------|

| BFI | BFO | CPU:HOST BUS<br>RATIO | PERFORMANCE<br>RATING | HOST BUS<br>FREQUENCY |

| 1   | 0   | 2:1                   | 500 MIPS              | 100 MHz               |

| 0   | 0   | 2.5:1                 | 600 MIPS              | 100 MHz               |

## 3 Electrical Specifications

## 3.1 Maximum Ratings

The values in Table 25 are worst-case stress ratings. CPU operation and reliability can be impaired and failure can occur if maximum ratings are exceeded. The CPU is not warranted, expressed or implied, to perform beyond these parameters. For best results, adhere to the operating conditions defined in the DC and AC specification tables listed below. The Rise  $iDragon^{TM}$  mP6 IA Processor resists latch-up or circuit damage caused by electrostatic discharge (ESD). However, it is not possible to prevent all failures that can result from excessive ESD, and precautions to avoid E/M fields and static shocks should always be taken when handling, storing, or operating the Rise  $iDragon^{TM}$  mP6 IA Processor.

**TABLE 25. MIN/MAX RATINGS**

| SYMBOL              | PARAMETER                                      | MIN  | MAX              | UNITS |

|---------------------|------------------------------------------------|------|------------------|-------|

| Ts                  | Storage temperature                            | -65  | 150              | °C    |

| TCASE               | Case temperature under bias or voltage applied | -65  | 110              | °C    |

| VCCio               | 3.3 V supply voltage relative to VSS           | -0.5 | 3.9              | ٧     |

| VCCcore             | 2.0 V supply voltage relative to VSS           | -0.5 | 2.1 <sup>1</sup> | V     |

| VIN <sub>IO</sub> 1 | DC input voltage at any pin                    | -0.5 | VCC10 + 0.5      | V     |

#### Notes:

1. To avoid CPU damage, do not exceed the MAX voltage under any circumstances.

## 3.2 DC Specifications

#### **TABLE 26. DC SPECIFICATIONS**

| SYMBOL                | PARAMETER                  | MIN   | TYP | MAX                     | UNITS | NOTES                                             |

|-----------------------|----------------------------|-------|-----|-------------------------|-------|---------------------------------------------------|

| T <sub>CASE</sub>     | Operating case temperature | 0     |     | 70                      | °C    | 1                                                 |

| VCC <sub>CORE</sub>   | Core voltage               | 1.95  | 2.0 | 2.05                    | V     |                                                   |

| VCC <sub>IO</sub>     | I/O voltage                | 3.135 | 3.3 | 3.465                   | V     | $3.3V \pm 5\%^2$                                  |

| ICC <sub>CORE</sub>   | Power supply current       |       |     | 2                       | Α     | 600 MIPS <sup>3</sup>                             |

| ICC <sub>IO</sub>     | Power supply current       |       |     | 1                       | Α     | 500 MIPS <sup>3</sup>                             |

| VIL_IO                | Input low voltage          | -0.3  |     | 0.8                     | V     | 4                                                 |

| VIH_IO                | Input high voltage         | 2.0   |     | VCC <sub>IO</sub> + 0.3 | V     | 4                                                 |

| Vol_io                | Output low voltage         |       |     | 0.4                     | V     | 4,5                                               |

| <b>V</b> он_іо        | Output high voltage        | 2.4   | _   | _                       | V     | 4, 6                                              |

| ILI                   | Input leakage current      | _     | -   | ± 15                    | μΑ    | 0≤V <sub>IN</sub> ≤VCC <sub>IO</sub> <sup>7</sup> |

| I <sub>LO</sub>       | Output leakage current     | _     | _   | ± 15                    | μΑ    | 0≤V <sub>IN</sub> ≤VCC <sub>IO</sub> <sup>8</sup> |

| I <sub>IH</sub>       | Input Leakage Current      | _     | _   | 200                     | μΑ    | V <sub>IN</sub> =2.4 V <sup>9</sup>               |

| I <sub>IL</sub>       | Input leakage current      | _     | _   | - 400                   | μΑ    | 10                                                |

| C <sub>IN</sub>       | Input Capacitance          | _     | _   | 15                      | pF    | 11                                                |

| C <sub>OUT</sub>      | Output Capacitance         | _     | _   | 20                      | pF    | 11                                                |

| C <sub>I/Output</sub> | I/Output Capacitance       | _     | _   | 25                      | pF    | 11                                                |

| C <sub>CLK</sub>      | CLK Input Capacitance      | _     | _   | 15                      | pF    | 11                                                |

| C <sub>TIN</sub>      | Test Input Capacitance     | _     | _   | 15                      | pF    | 11                                                |

| C <sub>TOUT</sub>     | Test Output Capacitance    | _     | _   | 20                      | pF    | 11                                                |

| C <sub>TCK</sub>      | Test Clock Capacitance     | _     | _   | 15                      | pF    | 9                                                 |

#### Notes:

- 1. Assuming case was setup in average room temp.

- 2. Unit not guaranteed to work beyond the MAX operating voltage in the MAX temperature.

- 3. These values should be used for power supply design.

- 4. All signals are 3.3 V TTL levels.

- 5. Measured with a 4 mA load.

- 6. Measured with a -3 mA load.

- 7. For signals without an internal pull up or pull down resistor.

- 8. For signals with an internal pull up or pull down resistor.

- 9. For inputs with an internal pull down resistor.

- 10. For inputs with an internal pull up resistor.

- 11. Not 100% tested, guaranteed by design.

#### **TABLE 27. POWER DISSIPATION SPECIFICATIONS**

| PARAMETER                                                | TYP <sup>1</sup> | MAX          | UNITS  | PERFORMANCE<br>RATING |

|----------------------------------------------------------|------------------|--------------|--------|-----------------------|

| Active power dissipation                                 | 1.34<br>1.07     | 4.05<br>3.24 | W<br>W | 600 MIPS<br>500 MIPS  |

| Stop Grant and Auto Halt<br>Power Down power dissipation | _                | _            | W<br>W | 600 MIPS<br>500 MIPS  |

| Stop Clock power dissipation                             | _                | _            | W      | All                   |

#### Notes

<sup>1.</sup> Typical system power dissipation running a typical sequence of instructions with 20% of active time. Power dissipation varies across applications. System thermal solutions should be designed to dissipate the maximum power dissipation.

## 3.3 AC Specifications

The AC specifications are listed in two tables (28A and 28B). Table 28A lists the AC specifications of processors for host buses that run at 60MHz, 66MHz, and 75MHz, while Table 28B lists the AC specifications of processors for host buses that run at 83MHz, 95MHz, and 100MHz. The two tables are divided into several parts, each of which is followed by a related timing diagram in the following pages.

#### **TABLE 28A. AC SPECIFICATIONS**

See Table 26 for recommended operating range,  $C_L = 50 \text{ pF}$

|                |                      | 60 MHz |      | 66 1 | ИНz  | 75 I  | ИНz  |      |       |

|----------------|----------------------|--------|------|------|------|-------|------|------|-------|

| SYMBOL         | PARAMETER            | MIN    | MAX  | MIN  | MAX  | MIN   | MAX  | UNIT | NOTES |

| f              | CLK Frequency        | 30.0   | 60.0 | 33.3 | 66.7 | 37.5  | 75   | MHz  |       |

| t <sub>1</sub> | CLK Period           | 16.7   | 33.3 | 15.0 | 30.0 | 13.33 | 26.7 | nS   |       |

| t <sub>2</sub> | CLK Period Stability | -      | ±250 | -    | ±250 | -     | ±250 | pS   |       |

| t <sub>3</sub> | CLK High Time        | 4.0    | -    | 4.0  | -    | 4.0   | -    | nS   |       |

| t 4            | CLK Low Time         | 4.0    | _    | 4.0  | _    | 4.0   | -    | nS   |       |

| t 5            | CLK Fall Time        | 0.15   | 1.5  | 0.15 | 1.5  | 0.15  | 1.5  | nS   |       |

| t <sub>6</sub> | CLK Rise Time        | 0.15   | 1.5  | 0.15 | 1.5  | 0.15  | 1.5  | nS   |       |

FIGURE 7A. CLOCK INPUT WAVEFORM

## **TABLE 28B. AC SPECIFICATIONS**

See Table 26 for recommended operating range,  $C_L = 0 pF$

|                |                      | 83 MHZ |      | 95 MHZ |      | 100 MHz |      |      |       |

|----------------|----------------------|--------|------|--------|------|---------|------|------|-------|

| Symbol         | Parameter            | MIN    | MAX  | Min    | Max  | Min     | Max  | UNIT | NOTES |

| f              | CLK Frequency        | 41.5   | 83   | 47.5   | 95   | 50      | 100  | MHz  |       |

| t <sub>1</sub> | CLK Period           | 12.1   | 24.1 | 10.5   | 21.1 | 10      | 20   | ns   |       |

| t <sub>2</sub> | CLK Period Stability | _      | ±250 | _      | ±250 | _       | ±250 | ps   |       |

| t <sub>3</sub> | CLK High Time        | 3.0    | -    | 3.0    | -    | 3.0     | _    | ns   |       |

| t <sub>4</sub> | CLK Low Time         | 3.0    | -    | 3.0    | -    | 3.0     | _    | ns   |       |

| t <sub>5</sub> | CLK Fall Time        | 0.15   | 1.5  | 0.15   | 1.5  | 0.15    | 1.5  | ns   |       |

| t <sub>6</sub> | CLK Rise Time        | 0.15   | 1.5  | 0.15   | 1.5  | 0.15    | 1.5  | ns   |       |

FIGURE 7B. CLOCK INPUT WAVEFORM

## TABLE 28A. AC SPECIFICATIONS (CONTINUED)

See Table 26 for recommended operating range,  $C_L = 50 \text{ pF}$

|                 |                                                                                     | 60 MHZ |     | 66 1 | ИНZ | 75 I | ИНz |      |       |

|-----------------|-------------------------------------------------------------------------------------|--------|-----|------|-----|------|-----|------|-------|

| Symbol          | Parameter                                                                           | MIN    | MAX | Min  | Max | Min  | Max | UNIT | NOTES |

| t <sub>10</sub> | A31-3, ADSC#, BE7-BE0#,<br>CACHE#, D/C#, LOCK3, PCD,<br>PWT, SCYC, W/R# Valid Delay | 1.0    | 7.0 | 1.0  | 7.0 | 1.0  | 6.0 | nS   |       |

| t 10            | AP Valid Delay                                                                      | 1.0    | 8.5 | 1.0  | 8.5 | 1.0  | 7.5 | nS   |       |

| t 10            | ADS#, M/IO# Valid Delay                                                             | 1.0    | 7.0 | 1.0  | 6.0 | 1.0  | 6.0 |      |       |

| t <sub>10</sub> | APCHK#, FERR#, IERR# Valid<br>Delay                                                 | 1.0    | 8.0 | 1.0  | 8.0 | 1.0  | 7.0 | nS   |       |

| t 10            | PCHK# Valid Delay                                                                   | 1.0    | 7.0 | 1.0  | 7.0 | 1.0  | 6.0 | nS   |       |

| t <sub>10</sub> | BREQ, HLDA, SMIACT# Valid<br>Delay                                                  | 1.0    | 8.0 | 1.0  | 8.0 | 1.0  | 6.0 | nS   |       |

| t 10            | HIT# Valid Delay                                                                    | 1.0    | 8.0 | 1.0  | 8.0 | 1.0  | 6.0 | nS   |       |

| t <sub>10</sub> | HITM# Valid Delay                                                                   | 1.0    | 6.0 | 1.0  | 6.0 | 1.0  | 6.0 | nS   |       |

| t <sub>10</sub> | D63-D0, DP7-DP0 Write Data<br>Valid Delay                                           | 1.0    | 8.0 | 1.0  | 8.0 | 1.0  | 7.0 | nS   |       |

FIGURE 8A. OUTPUT VALID DELAY WAVEFORM

Doc#: MKTD6510.0 28

## TABLE 28B. AC SPECIFICATIONS (CONTINUED)

See Table 26 for recommended operating range,  $C_L = 0 pF$

|                 |                                                 | 83 1 | ИНZ | 95 I | ИНZ | 100 | MHz |      |       |

|-----------------|-------------------------------------------------|------|-----|------|-----|-----|-----|------|-------|

| Symbol          | Parameter                                       | MIN  | MAX | Min  | Max | Min | Max | UNIT | NOTES |

| t <sub>10</sub> | A31-A3 Valid Delay                              | 1.1  | 4.0 | 1.1  | 4.0 | 1.1 | 4.0 | ns   |       |

| t <sub>10</sub> | AP Valid Delay                                  | 1.0  | 5.5 | 1.0  | 5.5 | 1.0 | 5.5 | ns   |       |

| t <sub>10</sub> | ADS#, ADSC#, D/C#, M/IO#,<br>W/R# Valid Delay   | 1.0  | 4.0 | 1.0  | 4.0 | 1.0 | 4.0 | ns   |       |

| t <sub>10</sub> | APCHK#, FERR#, IERR# Valid<br>Delay             | 1.0  | 4.5 | 1.0  | 4.5 | 1.0 | 4.5 | ns   |       |

| t <sub>10</sub> | PCHK# Valid Delay                               | 1.0  | 4.5 | 1.0  | 4.5 | 1.0 | 4.5 | ns   |       |

| t <sub>10</sub> | BREQ, HLDA, SMIACT# Valid<br>Delay              | 1.0  | 4.0 | 1.0  | 4.0 | 1.0 | 4.0 | ns   |       |

| t <sub>10</sub> | HIT# Valid Delay                                | 1.0  | 4.0 | 1.0  | 4.0 | 1.0 | 4.0 | ns   |       |

| t <sub>10</sub> | BE7-BE0#, CACHE#, PCD,<br>PWT, SCYC Valid Delay | 1.0  | 4.0 | 1.0  | 4.0 | 1.0 | 4.0 | ns   |       |

| t <sub>10</sub> | D63-D0, DP7-DP0 Write Data<br>Valid Delay       | 1.3  | 4.5 | 1.3  | 4.5 | 1.3 | 4.5 | ns   |       |

| t <sub>10</sub> | HITM# Valid Delay                               | 1.0  | 5.5 | 1.1  | 4.0 | 1.1 | 4.0 | ns   |       |

| t <sub>10</sub> | LOCK# Valid Delay                               | 1.0  | 6.0 | 1.1  | 4.0 | 1.1 | 4.0 | ns   |       |

FIGURE 8B. OUTPUT VALID DELAY WAVEFORM

Doc#: MKTD6510.0 29

**TABLE 28A.** AC SPECIFICATIONS (CONTINUED) SEE TABLE 26 FOR RECOMMENDED OPERATING RANGE,  $C_L = 50 \text{ PF}$

|                 |                                                                                                                                         | 60 MHZ |     | 66 MHZ |     | 75 MHz |     |      |       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------|-----|--------|-----|--------|-----|------|-------|

| Symbol          | Parameter                                                                                                                               | MIN    | MAX | Min    | Max | Min    | Max | UNIT | NOTES |

| t <sub>20</sub> | A31-A3, ADS#, ADSC#, AP,<br>BE7-BE0#, CACHE#, D/C#,<br>LOCK#, M/IO#, PCD, PWT,<br>SCYC, W/R# D63-D0, DP7-<br>DP0 Write Data Float Delay |        | 7.0 |        | 7.0 |        | 7.0 | ns   | 1     |

FIGURE 9A. OUTPUT FLOAT DELAY WAVEFORM

**TABLE 28B. AC SPECIFICATIONS (CONTINUED)** SEE TABLE 26 FOR RECOMMENDED OPERATING RANGE,  $C_L = 50 \text{ PF}$