# Embedded Pentium<sup>®</sup> Processor with MMX<sup>™</sup> Technology Flexible Motherboard Design Guidelines

**Application Note**

October 1998

Order Number: 273206-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium<sup>®</sup> processors with MMX<sup>™</sup> technology may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Intro | oduction                                                                                                         | 7  |

|-----|-------|------------------------------------------------------------------------------------------------------------------|----|

|     | 1.1   | Features List for the Flexible Motherboard                                                                       | 8  |

|     | 1.2   | Benefits of a Flexible Motherboard                                                                               | 11 |

| 2.0 | Prod  | cessor Design Considerations                                                                                     | 12 |

|     | 2.1   | Overview of the Pentium <sup>®</sup> Processor with MMX™ Technology Family                                       | 12 |

|     | 2.2   | External Features and Differences                                                                                |    |

|     |       | 2.2.1 Bus Fraction (BF) Selection                                                                                | 14 |

|     |       | 2.2.2 Pinout Considerations                                                                                      |    |

|     |       | 2.2.3 Processor ID with the CPUID Instruction                                                                    |    |

|     | 2.3   | Electrical and Thermal Features and Differences                                                                  |    |

|     |       | 2.3.1 Thermal Analysis                                                                                           |    |

|     |       | 2.3.2 Split Power Supplies                                                                                       |    |

|     |       | 2.3.3 2.5 V Input and Output                                                                                     |    |

|     |       | 2.3.4 V <sub>IL3</sub> (MAX) and V <sub>IH3</sub> (MIN)                                                          |    |

|     |       | -                                                                                                                |    |

| 3.0 | Flex  | ible Motherboard Implementation                                                                                  |    |

|     | 3.1   | Overview of Voltage Supply and Split Power Planes                                                                | 21 |

|     | 3.2   | Voltage Supply and Split Power Planes Implementation                                                             |    |

|     |       | and Cost-savings Build Options                                                                                   |    |

|     |       | 3.2.1 Layout and Design of Sample Implementation                                                                 | 22 |

|     |       | 3.2.2 Board to Support All Members of the Pentium <sup>®</sup> Processor with MMX <sup>™</sup> Technology Family | 24 |

|     |       | 3.2.3 Board for the Low-Power Embedded Pentium <sup>®</sup> Processor                                            | 24 |

|     |       | with MMX™ Technology Only                                                                                        | 24 |

|     |       | 3.2.4 Board for the Embedded Pentium <sup>®</sup> Processor                                                      |    |

|     |       | with MMX™ Technology Only                                                                                        | 25 |

|     | 3.3   | Switching vs. Linear Voltage Regulators                                                                          | 26 |

|     |       | 3.3.1 General Principles Of Switching And Linear Voltage Regulators                                              |    |

|     |       | 3.3.2 Design Considerations for Voltage Supplies                                                                 |    |

|     |       | 3.3.2.1 Real Estate                                                                                              |    |

|     |       | 3.3.2.2 Tolerance                                                                                                |    |

|     |       | 3.3.2.4 Decoupling Capacitors                                                                                    |    |

|     |       | 3.3.2.5 Cost of Component                                                                                        |    |

|     | 3.4   | Split Power Plane Layout                                                                                         |    |

|     | 3.5   | Decoupling                                                                                                       |    |

|     |       | 3.5.1 Bulk Decoupling                                                                                            |    |

|     |       | 3.5.2 High Frequency Decoupling                                                                                  |    |

|     |       | 3.5.3 Decoupling Recommendations                                                                                 |    |

|     |       | 3.5.4 Placement of Decoupling Capacitors                                                                         |    |

|     | 3.6   | Signal Routing Guidelines                                                                                        |    |

|     | 3.7   | VCC2DET# Auto-Detect Circuit                                                                                     |    |

|     | 3.8   | BIOS/Software Considerations                                                                                     |    |

|     | 3.9   | Dual Processor Design Considerations                                                                             | 34 |

# Embedded Pentium Processor with MMX Technology Flexible Motherboard Design Guidelines

| 4.0     | Sock              | et 7 Pin Diagram                                                                                                            | . 35         |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------|

| 5.0     | Heat              | Transfer Fundamentals                                                                                                       | . 38         |

|         | 5.1<br>5.2        | Thermal TheoryThermal Interface Material Basics                                                                             |              |

| 6.0     | Vend              | ors and Device Suppliers                                                                                                    | 43           |

|         | 6.1<br>6.2<br>6.3 | Device Suppliers for Design Conversion                                                                                      | . 43<br>. 44 |

| 7.0     | Relat             | ed Resources                                                                                                                | .49          |

| Figures | 4                 | Fach added Destine ® Description with MANYTM Testine describe                                                               |              |

|         | 1                 | Embedded Pentium <sup>®</sup> Processor with MMX <sup>™</sup> Technology Family Flexible Motherboard                        | 7            |

|         | 2                 | Split Power Planes on a Flexible Motherboard for the Pentium <sup>®</sup> Processor with MMX <sup>™</sup> Technology Family |              |

|         | 3                 | I/O Interface for the Flexible Motherboard                                                                                  |              |

|         | 4                 | EAX Bit Assignments for CPUID                                                                                               |              |

|         | 5                 | EDX Bit Assignments for CPUID                                                                                               |              |

|         | 6                 | Basic Design of Sample Implementation                                                                                       | . 23         |

|         | 7                 | Board for the Embedded Pentium <sup>®</sup> Processor with MMX <sup>™</sup> Technology Only                                 | 25           |

|         | 8                 | Processor Power Island Layout                                                                                               |              |

|         | 9                 | Typical Capacitance Change vs. Temperature                                                                                  |              |

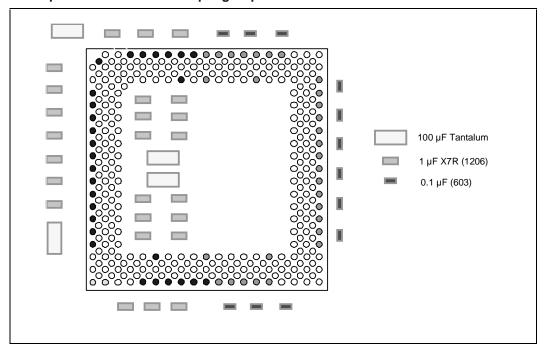

|         | 10                | Example of Processor Decoupling Capacitor Placement                                                                         |              |

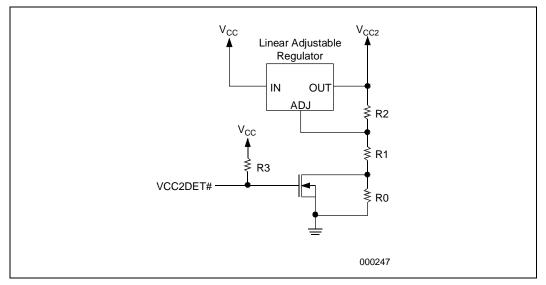

|         | 11                | VCC2DET# Auto-Detect Circuit                                                                                                |              |

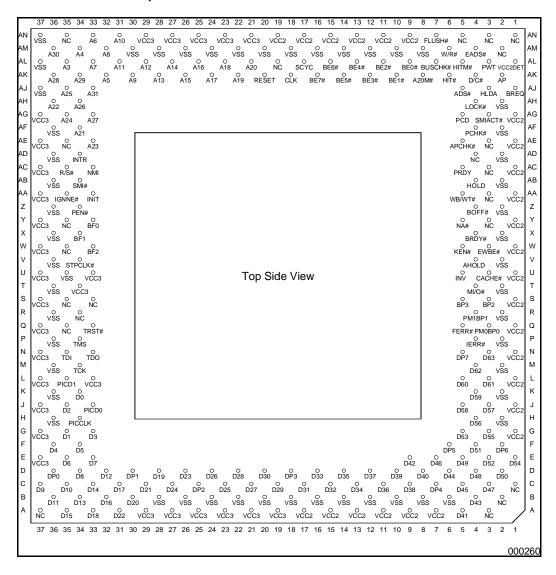

|         | 12                | Socket 7 Pinout—Top Side View                                                                                               |              |

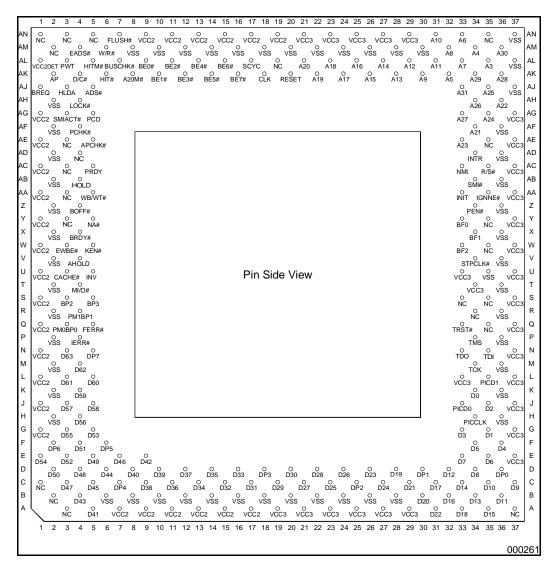

|         | 13                | Socket 7 Pinout—Pin Side View                                                                                               |              |

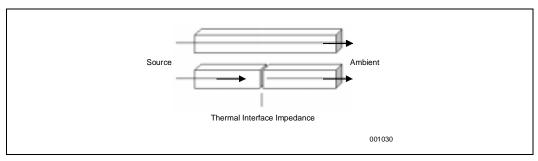

|         | 14                | Thermal Flow to Ambient Environment                                                                                         | 39           |

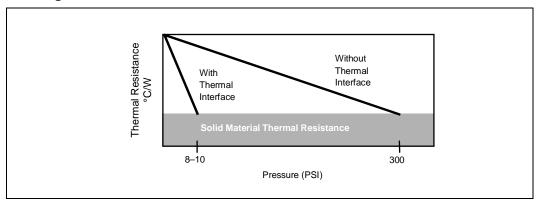

|         | 15                | Pressure Applied to Two Solids to Equal Thermal Resistance of a Single Solid                                                | . 39         |

# Embedded Pentium<sup>®</sup> Processor with MMX™ Technology Flexible Motherboard Design Guidelines

# Tables

| 1  | Key Differences in the Pentium <sup>®</sup> Processors with MMX™                     | 4.0 |

|----|--------------------------------------------------------------------------------------|-----|

| 2  | Technology Family  Bus Frequency Selections for the Embedded Pentium® Processor with | I 2 |

| 2  | MMX™ Technology Family                                                               | 14  |

| 3  | Quick Pin Reference for the Low-Power Embedded Pentium® Processor                    |     |

|    | with MMX™ Technology                                                                 | 16  |

| 4  | EDX Bit Assignment Definitions for CPUID                                             | 17  |

| 5  | Overshoot Specification Summary                                                      | 19  |

| 6  | Undershoot Specification Summary                                                     | 20  |

| 7  | Comparison Between Switching and Linear Voltage Regulators                           | 27  |

| 8  | Decoupling Recommendations for Processor Core and I/O Voltage Islands                | 31  |

| 9  | Socket 7 Pins that Differ from Socket 5                                              | 37  |

| 10 | Design Conversion Device Suppliers                                                   | 43  |

| 11 | Voltage Regulators                                                                   |     |

| 12 | Socket 7 Vendors                                                                     | 45  |

| 13 | Decoupling Capacitor Vendors                                                         | 45  |

| 14 | Resistor Vendors                                                                     |     |

| 15 | 3.3 V Clock Driver Suppliers                                                         |     |

| 16 | SRAM/TagRAM                                                                          | 47  |

| 17 | Thermal Interface, Heatsink, an Socket Suppliers                                     |     |

| 18 | Related Resources                                                                    | 49  |

|    |                                                                                      |     |

# 1.0 Introduction

This application note provides guidelines for designing a flexible motherboard that supports the Intel<sup>®</sup> Pentium<sup>®</sup> processor with MMX<sup>TM</sup> technology family.

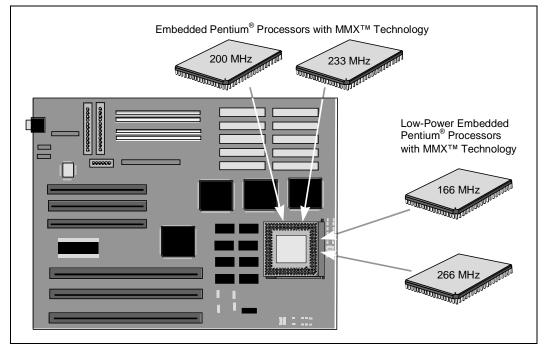

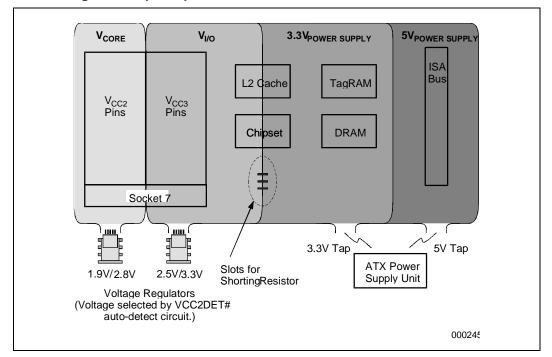

Figure 1 illustrates a flexible motherboard design that supports embedded Pentium processors with MMX technology at 200/233 MHz and the new low-power embedded Pentium processors with MMX technology at 166/266 MHz manufactured with Intel's 0.25 micron fabrication process. The 0.25 micron process enables the processor to achieve faster speeds at lower voltages, reducing power consumption and heat dissipation while improving performance. The main difference between the two processors is their core and I/O voltages. The embedded Pentium processor with MMX technology has a core voltage ( $V_{\rm CORE}$ ) of 2.8 V and an I/O voltage ( $V_{\rm L/O}$ ) of 3.3 V. The low-power embedded Pentium processor with MMX technology has a  $V_{\rm CORE}$  of 1.9 V and a  $V_{\rm L/O}$  of 2.5 V

Figure 1. Embedded Pentium<sup>®</sup> Processor with MMX™ Technology Family Flexible Motherboard

Note: This application note presents design information specific to the PPGA package of the low-power embedded Pentium processor with MMX technology. This processor is also offered in the High-Thermal, Low-Temperature Plastic Ball Grid Array (HL-PBGA) package. This document may be used as a reference for designs using the HL-PBGA device. For more information on the low-power embedded Pentium processor with MMX technology in the HL-PBGA package, refer to the Low-Power Embedded Pentium® Processor with MMX<sup>TM</sup> Technology datasheet (order number 273184). For details on the HL-PBGA package, refer to the Intel Packaging Handbook (order number 240800).

#### 1.1 Features List for the Flexible Motherboard

A Pentium processor with MMX technology flexible motherboard should support the following features:

#### • Split Power Islands

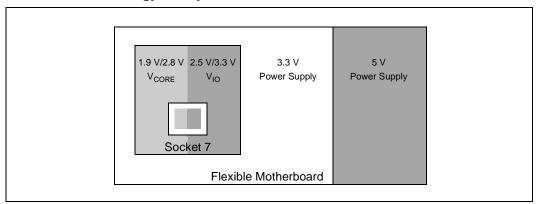

To accommodate split-plane processors, the flexible motherboard should have four separate power islands:  $V_{CORE}$  ( $V_{CC2}$ ),  $V_{I/O}$  ( $V_{CC3}$ ), 3.3 V (3.3 V power supply) and 5 V (5 V power supply).

The low-power embedded Pentium processor with MMX technology at 166/266 MHz uses the same split-power plane,  $V_{CORE}$  and  $V_{I/O}$ , as the embedded Pentium processor with MMX technology, except that the supply voltages are different.  $V_{CORE}$  and  $V_{I/O}$  for the embedded Pentium processor with MMX technology are 2.8 V and 3.3 V, respectively.  $V_{CORE}$  and  $V_{I/O}$  for the low-power embedded Pentium processor with MMX technology are 1.9 V and 2.5 V, respectively. Both processors require 3.3 V and 5 V power planes for external motherboard components such as DRAM (3.3 V) and the ISA bus (5 V).

Figure 2 illustrates the four power planes for the Pentium processor with MMX technology family.

Figure 2. Split Power Planes on a Flexible Motherboard for the Pentium<sup>®</sup> Processor with MMX™ Technology Family

## • 2.0 V/2.8 V Power Source for V<sub>CORE</sub> Plane

The  $V_{CORE}$  plane supplies the core voltage ( $V_{CC2}$ ) for the processor. The low-power embedded Pentium processors with MMX technology require 1.9 V ( $\pm 142$  mV) for core voltage. The embedded Pentium processors with MMX technology require 2.8 V ( $\pm 100$  mV).

The flexible motherboard can implement this dual voltage power plane with a single linear or switching voltage regulator. See "Switching vs. Linear Voltage Regulators" on page 26 for design considerations for choosing a voltage supply. V<sub>CC2</sub> pins for the low-power embedded Pentium processor with MMX technology are not 2.8 V-tolerant. Therefore, the flexible motherboard should have built-in precautions to ensure that the right voltage is supplied when a low-power embedded Pentium processor with MMX technology is installed in the socket.

Refer to "VCC2DET# Auto-Detect Circuit" on page 33 for an example of a safeguard circuit.

#### • 2.5 V/3.3 V Power Source for V<sub>I/O</sub> Plane

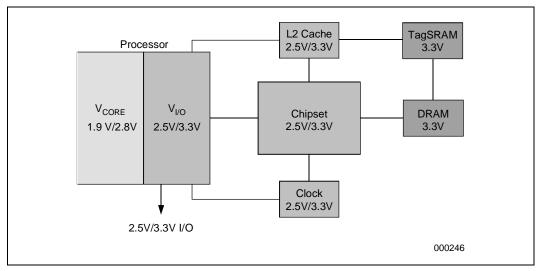

The  $V_{I/O}$  plane supplies the I/O voltage ( $V_{CC3}$ ) for the processor, clock, host controller, and L2 cache (SRAM). The low-power embedded Pentium processor with MMX technology requires 2.5 V (2.375 V–2.625 V) for the I/O. The embedded Pentium processor with MMX technology requires 3.3 V (3.135 V–3.6 V). The clock, host controller, and L2 cache are special dual-voltage components that can run at either voltage.

A dual-voltage power plane on the flexible motherboard can be implemented with a single linear or switching voltage regulator. Figure 3 illustrates the I/O interface on the flexible motherboard.

V<sub>CC3</sub> for the low-power embedded Pentium processor with MMX technology is not 3.3 V tolerant. Therefore, the flexible motherboard should have built-in precautions to ensure that the right voltage is supplied when a low-power embedded Pentium processor with MMX technology is installed in the socket.

Refer to "VCC2DET# Auto-Detect Circuit" on page 33 for an example of a safeguard circuit.

Figure 3. I/O Interface for the Flexible Motherboard

#### • 3.3 V Power Source

The flexible motherboard should provide a 3.3 V power plane for components such as the PCI bus, system memory (DRAM), and TagRAM (SRAM). The voltage for this plane can be from the 3.3 V source on the power supply unit or from a 3.3 V voltage regulator.

#### • 5 V Power Source

Components on the ISA bus, such as audio circuitry, keyboard/mouse controllers, and flash memory, require a  $5\ V$  plane.

#### Socket 7

The flexible motherboard should implement Socket 7. This processor socket accepts Socket 7 compatible processors in the Pentium processor with MMX technology family regardless of differences in their pin assignments or power plane implementation. Socket 7 is a 321-pin superset of the older 320-pin Socket 5 ZIF sockets. Socket 7 splits the 60  $V_{CC}$  pins on Socket 5 into 28  $V_{CC2}$  pins and 32  $V_{CC3}$  pins. These pins are connected appropriately to the processor core voltage island and processor I/O voltage island.

#### Local Decoupling

Pentium processors with MMX technology may cause rapid fluctuation in current during transitions between "idle" states and "active" states. The flexible motherboard should provide adequate decoupling capacitors near the processor socket to prevent violation of the voltage supply range specifications, as documented in "Decoupling" on page 29.

# Embedded Pentium<sup>®</sup> Processor with MMX<sup>™</sup> Technology Flexible Motherboard Design Guidelines

#### • Bus-to-Core Ratio

The flexible motherboard should provide jumpers for bus fraction pin strapping options that provide flexibility in configuring the ratio of external bus frequency to internal core frequency. The bus-to-core ratios can be 1/4, 2/7, 1/3, or 2/5. To support selecting between embedded Pentium processors with MMX technology and low-power embedded Pentium processors with MMX technology, jumpers should allow a high or low logic setting for three bus fraction pins (BF2, BF1 and BF0). When enabled, these pins should be pulled to logic high ( $V_{\rm I/O}$  voltage level).

#### • Thermal and Mechanical Specifications

The flexible motherboard should be designed to meet the thermal and mechanical specifications of the Socket 7 Specification, Rev. 3.0.

#### • BIOS Support

Each processor stepping is assigned a unique identification and feature signature. The CPUID instruction retrieves these signatures for identification. The flexible motherboard should provide a system BIOS capable of supporting all steppings for the Pentium processors with MMX technology. Using the CPUID instruction, the BIOS can determine whether the processor supports features such as the APIC. For more details, refer to "Processor ID with the CPUID Instruction" on page 16 and application note AP-485, *Intel Processor Identification with the CPUID Instruction* (order number 241618).

#### Multiple Voltage Clock Drivers

The flexible motherboard should include a clock driver that can drive clock inputs (CLK and PICCLK) on the processor at both 2.5 V and 3.3 V to ensure compatibility with all Pentium processors with MMX technology. The embedded Pentium processors with MMX technology require clock inputs of 3.3 V. The low-power embedded Pentium processors with MMX technology require clock inputs of 2.5 V.

#### • Auto-Detect Configuration Circuit

Although it is possible to design the flexible motherboard to use jumpers and resistors to manually configure the board for each type of processor, it is recommended that an auto-detect configuration circuit be used instead. The circuit makes the flexible motherboard more user-friendly. The user does not need to reconfigure the board manually or remember jumper settings.

The auto-detect circuit serves as a safeguard for the low-power embedded Pentium processor with MMX technology, which requires lower voltage levels than the embedded Pentium processor with MMX technology. This prevents incorrect voltage inputs to the processor, which could damage the processor and other components on the motherboard. Refer to "VCC2DET# Auto-Detect Circuit" on page 33 for more details.

## 1.2 Benefits of a Flexible Motherboard

A flexible motherboard design for the Pentium processor with MMX technology family offers several benefits:

#### • Provides price/performance options

One flexible design, when populated by different members of the Pentium processor with MMX technology family, can provide a wide range of price/performance options. Other assembly-time options for motherboard components can provide additional flexibility. For example, external caches may use asynchronous SRAM for cost effectiveness or pipelined burst SRAM for higher performance. Synchronous DRAM may replace Extended Data Out (EDO) DRAM as main memory to maintain performance in cost-effective platforms with optional external cache memory.

#### Reduces the design and validation effort for multiple designs

A flexible motherboard does not have to be revised for every proliferation of the processor, thus reducing design and validation efforts. Instead, one board is designed to accept various processors that can be populated at build-time.

#### · Reduces inventory and manufacturing costs

Only one motherboard design has to be manufactured and maintained in inventory, reducing overall inventory management and manufacturing costs. When product demand varies, the board can be populated with the processor that satisfies the current market demand.

#### · Reduces debug and technical support costs

Only one motherboard has to be debugged. Field engineers and other support personnel need only to be trained on one motherboard design, thus reducing technical support effort.

#### **Processor Design Considerations** 2.0

This section describes considerations for designing a flexible motherboard for the family of Pentium processors with MMX technology. The differences between the embedded Pentium processor with MMX technology and the low-power embedded Pentium processor with MMX technology are discussed.

#### Overview of the Pentium<sup>®</sup> Processor with MMX™ 2.1 **Technology Family**

Table 1 highlights the Pentium processor with MMX technology family's electrical and thermal specifications. Refer to "Related Resources" on page 49 to obtain specifications for each processor.

Key Differences in the Pentium<sup>®</sup> Processors with MMX™ Table 1. Technology Family (Sheet 1 of 2)

|                                 | Embedded Pentium <sup>®</sup> Processor with MMX™ Technology | Low-Power Embedded Pentium<br>Processor with MMX Technology <sup>1</sup> |

|---------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|

| Core Frequency (MHz)            | 200, 233                                                     | 166, 266                                                                 |

| Bus Frequency (MHz)             | 66                                                           | 66                                                                       |

| Frequency Ratio <sup>2</sup>    | 1/3, 2/7                                                     | 2/5, 1/4                                                                 |

| Clock Level                     | 3.3 V                                                        | 2.5 V                                                                    |

| Core Supply (V <sub>CC2</sub> ) | 2.8 V (±100 mV)                                              | 1.9 V (±142 mV)                                                          |

| I/O Supply (V <sub>CC3</sub> )  | 3.3 V (3.135 V-3.60 V)                                       | 2.5 V (2.375 – 2.625 V)                                                  |

| I <sub>CC2</sub> <sup>3,4</sup> | 6.50 A (233 MHz)<br>5.70 A (200 MHz)                         | 4.0 A (266 MHz)<br>2.5 A (166 MHz)                                       |

| I <sub>CC3</sub> 3,5            | 750 mA (233 MHz)<br>650 mA (200 MHz)                         | 380 mA (266 MHz)<br>380 mA (166 MHz)                                     |

| Max. Power <sup>5</sup>         | 17.0 W (233 MHz)<br>15.7 W (200 MHz)                         | 7.6 W (266 MHz)<br>4.5 W (166 MHz)                                       |

| V <sub>IL</sub>                 | 0.8 V                                                        | 0.5 V                                                                    |

| V <sub>IH</sub>                 | 2.0 V                                                        | V <sub>CC3</sub> – 0.7 V                                                 |

| V <sub>OH</sub>                 | N/A                                                          | V <sub>CC3</sub> – 0.2 V (I <sub>OH</sub> = 1 mA)                        |

- 1. All data for the low-power embedded Pentium processor with MMX technology are best estimates at the time of this document's publication. Refer to the Low-Power Embedded Pentium® Processor with MMX™ Technology datasheet (order number 273184) for the latest specifications.

- 2. Note that overshoot, undershoot and ringback are different between a embedded Pentium processor with MMX technology and a low-power embedded Pentium processor with MMX technology. Refer to "Overshoot, Undershoot and Ringback" on page 19.

- 3. The number shown represents worst case or maximum current/power.

- 4. I<sub>CC2</sub> refers to V<sub>CC2</sub> (core) supply current.

- 5. I<sub>CC3</sub> refers to V<sub>CC3</sub> (I/O) supply current.

6. Refer to the Low-Power Embedded Pentium<sup>®</sup> Processor with MMX™ Technology datasheet (order number 273184) for complete AC timing specifications.

# Table 1. Key Differences in the Pentium<sup>®</sup> Processors with MMX<sup>™</sup> Technology Family (Sheet 2 of 2)

|                              | Embedded Pentium <sup>®</sup> Processor<br>with MMX™ Technology | Low-Power Embedded Pentium<br>Processor with MMX Technology <sup>1</sup> |

|------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------|

| AC Timings <sup>6</sup>      | N/A                                                             | Abus and Dbus min/max valid delays have changed                          |

| No. of V <sub>CC2</sub> Pins | 25                                                              | 25                                                                       |

| No. of V <sub>CC3</sub> Pins | 28                                                              | 28                                                                       |

| External Plane Type          | Split                                                           | Split                                                                    |

| Internal Plane Type          | Split                                                           | Split                                                                    |

| Package Type                 | 296-pin PPGA                                                    | 296-pin PPGA                                                             |

#### NOTES:

- All data for the low-power embedded Pentium processor with MMX technology are best estimates at the time of this document's publication. Refer to the Low-Power Embedded Pentium<sup>®</sup> Processor with MMX<sup>™</sup> Technology datasheet (order number 273184) for the latest specifications.

- Note that overshoot, undershoot and ringback are different between a embedded Pentium processor with MMX technology and a low-power embedded Pentium processor with MMX technology. Refer to "Overshoot, Undershoot and Ringback" on page 19.

- 3. The number shown represents worst case or maximum current/power.

- 4. I<sub>CC2</sub> refers to V<sub>CC2</sub> (core) supply current.

- 5. I<sub>CC3</sub> refers to V<sub>CC3</sub> (I/O) supply current.

- Refer to the Low-Power Embedded Pentium<sup>®</sup> Processor with MMX<sup>™</sup> Technology datasheet (order number 273184) for complete AC timing specifications.

The embedded Pentium processor with MMX technology is a Socket 7, split core I/O processor with a core voltage of 2.8 V and an I/O voltage of 3.3 V. It operates at 200 and 233 MHz core speeds with a 66 MHz external bus. It introduced several architectural enhancements to the classic Pentium processor family: an increase from 8 Kbytes to 16 Kbytes internal data and code cache size, better branch prediction, and support for MMX technology.

The low-power embedded Pentium processor with MMX technology is a lower power version of the Pentium processor with MMX technology, capable of running at speeds up to 266 MHz with  $V_{CORE}$  at 1.9 V and  $V_{I/O}$  at 2.5 V. It is functionally identical to the Pentium processor with MMX technology with the following differences: voltage supplies, power consumption, no dual processing (DP) support, and no support for selectable buffer sizes. The low-power embedded Pentium processor with MMX technology is offered in a Socket 7 package, and is pin compatible with the embedded Pentium processor with MMX technology. See "Socket 7 Pin Diagram" on page 35 for pinouts.

The Intel430TX PCIset chipset directly supports the low-power embedded Pentium processor with MMX technology and the embedded Pentium processor with MMX technology. Level shifters can be used to interface the Intel430HX PCIset chipset to the low-power embedded Pentium processor with MMX technology. For more information, see *Interfacing the Low-Power Embedded Pentium Processor with MMX Technology to the 82439HX System Controller* (order number 273188).

#### 2.2 External Features and Differences

This section discusses some of the differences between the external features of the embedded Pentium processor with MMX technology and those of the low-power embedded Pentium processor with MMX technology.

# 2.2.1 Bus Fraction (BF) Selection

The BF configuration pins are provided to select the allowable bus-to-core ratios: 1/4, 2/7, 1/3, and 2/5. Processors multiply the input CLK to achieve the higher internal core frequencies. The internal clock multiplier requires a constant frequency CLK input to within  $\pm 250$  ps; therefore the CLK input cannot be changed dynamically.

The external bus frequency is set on power-up RESET through the CLK pin. All Pentium processors with MMX technology sample the BF2-BF0 pins on the falling edge of RESET to determine which bus-to-core ratio to use.

#### Warning:

Do not float the BF pins at RESET for processors running at 166, 200, 233 or 266 MHz. When the BF pins are left floating, these processors will be configured for an 1/2 bus-to-core frequency ratio, which is unsupported on these processors.

Table 2 summarizes the operation of the BF pins for the Pentium processor with MMX technology. The BF2 pin was added to support the 1/4 ratio for the low-power embedded Pentium processor with MMX technology running at 266 MHz.

Table 2. Bus Frequency Selections for the Embedded Pentium<sup>®</sup> Processor with MMX<sup>™</sup> Technology Family

| BF2 | BF1 | BF0 | Embedded Pentium <sup>®</sup> Processor with MMX Technology (200/233 MHz) Bus-to-Core Ratio | Low-Power Embedded Pentium Processor with MMX Technology (166/266 MHz) Bus-to-Core Ratio | Max Bus/Core<br>Frequency<br>(MHz) |

|-----|-----|-----|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------|

| 0   | 0   | 0   | Reserved                                                                                    | 2/5                                                                                      | 66/166                             |

| 0   | 0   | 1   | 1/3                                                                                         | Reserved                                                                                 | 66/200                             |

| 0   | 1   | 0   | Reserved <sup>†</sup>                                                                       | Reserved <sup>†</sup>                                                                    | 66/133                             |

| 0   | 1   | 1   | 2/7                                                                                         | Reserved                                                                                 | 66/233                             |

| 1   | 0   | 0   | Reserved                                                                                    | 1/4                                                                                      | 66/266                             |

| 1   | Х   | Х   | Reserved                                                                                    | Reserved                                                                                 | N/A                                |

<sup>†</sup> This is the default bus-to-core ratio for the embedded Pentium<sup>®</sup> processor with MMX<sup>™</sup> technology and the low-power embedded Pentium processor with MMX technology. If the BF pins are left floating, the processor will be configured for a 1/2 bus-to-core frequency ratio, which is unsupported on these processors.

#### 2.2.2 Pinout Considerations

The functional signals on the low-power embedded Pentium processor with MMX technology are compatible with the Pentium processor with MMX technology. However, some pin assignments have changed due to changes in the feature set. Table 3 provides a quick reference for pin changes. The major changes are described below in more detail.

### • $V_{CC2}$ , $V_{CC3}$

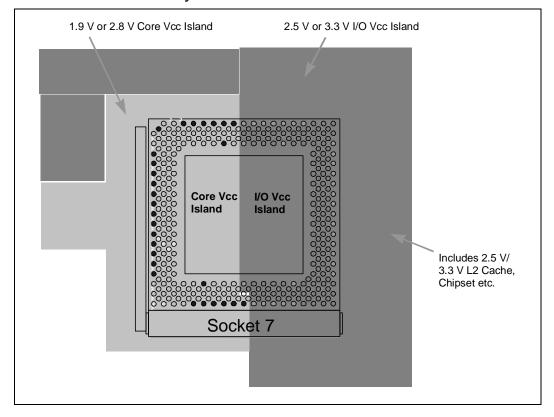

On the embedded Pentium processor with MMX technology, the  $V_{CC3}$  of the internal bus logic is isolated from the  $V_{CC2}$  of the core logic. This allows the core to run at a lower voltage (2.8 V) in order to obtain faster core frequencies and reduce overall power consumption. The low-power embedded Pentium processor with MMX technology is designed the same way, except that  $V_{CC2}$  is 1.9 V and  $V_{CC3}$  is 2.5 V. The voltage for the core logic is supplied through the  $V_{CC2}$  pins and the voltage for the bus logic is supplied through the  $V_{CC3}$  pins. Therefore, the motherboard design splits the processor power plane into two separate core voltage islands: one that can supply 1.9 V or 2.8 V ( $V_{CC2}$ ) and another that can supply 2.5 V or 3.3 V ( $V_{CC3}$ ).

#### • VCC2DET#

This signal is defined on the Pentium processor with MMX technology to indicate to the system which processor is installed in the processor socket. On the low-power embedded Pentium processor with MMX technology, the VCC2DET# pin is left floating (infinite impedance). For the embedded Pentium processor with MMX technology, the pin is internally connected to ground. A circuit designed to detect the VCC2DET# signal should have a weak pull-up resistor. This will cause the signal to be pulled high with a low-power embedded Pentium processor with MMX technology and to be driven low with an embedded Pentium processor with MMX technology. For a sample circuit, refer to "VCC2DET# Auto-Detect Circuit" on page 33.

One additional note is that the VCC2DET# pin is also defined as floating for Pentium processors at 100/133/166 MHz. There should be minimal or no issues from this overlap, because low-power embedded Pentium processor with MMX technology and Pentium processors at 100/133/166 MHz are not normally supported on a single motherboard design.

#### • BF2-BF0

The bus fraction selection pins determine the bus-to-core frequency ratio. The BF pins are sampled by the processor at RESET, and are not sampled by the processor again until another cold-boot (1 ms) assertion of RESET. The signal on the BF pins is not an indication of the bus speed, only the ratio of the processor core with respect to the bus. Table 2 summarizes the operation of the BF pins on Pentium processors with MMX technology.

#### · CLK, PICCLK

The low-power embedded Pentium processor with MMX technology supports input and output levels of 2.5 V only. The clock (CLK) and APIC clock (PICCLK) are not 3.3 V tolerant. The clock inputs to the processor on the flexible motherboard are driven by a dual voltage 2.5 V/3.3 V clock driver: 2.5 V for the low-power embedded Pentium processor with MMX technology and 3.3 V for embedded Pentium processor with MMX technology.

Table 3 lists the pin differences between the embedded Pentium processor with MMX technology and the low-power embedded Pentium processor with MMX technology. Square brackets around a signal name indicate that the signal is defined only at RESET.

Table 3. Quick Pin Reference for the Low-Power Embedded Pentium<sup>®</sup> Processor with MMX™ Technology

| Pin Name                                                                       | I/O    | Function                                                                                                                                                                                                                                                                                                                    |                                                                 |                     |                  |  |  |  |  |  |

|--------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------|------------------|--|--|--|--|--|

|                                                                                |        | The low-power embedded Pentium processor with MMX technology uses the BF0, BF1 and BF2 pins to determine the bus-to-core frequency ratio.                                                                                                                                                                                   |                                                                 |                     |                  |  |  |  |  |  |

| [BF0], [BF1], [BF2]                                                            | Input  | non-warm (1 ms)                                                                                                                                                                                                                                                                                                             | ampled at RESET, a<br>assertion of RESE<br>hile RESET is active | T. Additionally, BF |                  |  |  |  |  |  |

|                                                                                |        | When BF0, BF1 and BF2 are left floating, the low-power embedded Pentium processor with MMX technology defaults to a 1/2 bus-to-core ratio. The complete configuration table for BF pins is listed below. Bus Fraction functionality is further explained in "Overview of Voltage Supply and Split Power Planes" on page 21. |                                                                 |                     |                  |  |  |  |  |  |

|                                                                                |        | BF2                                                                                                                                                                                                                                                                                                                         | BF1                                                             | BF0                 | Fraction         |  |  |  |  |  |

|                                                                                |        | 0                                                                                                                                                                                                                                                                                                                           | 0                                                               | 0                   | 2/5              |  |  |  |  |  |

|                                                                                |        | 0                                                                                                                                                                                                                                                                                                                           | 0                                                               | 1                   | Reserved         |  |  |  |  |  |

|                                                                                |        | 0                                                                                                                                                                                                                                                                                                                           | 1                                                               | 0                   | 1/2 <sup>2</sup> |  |  |  |  |  |

|                                                                                |        | 0                                                                                                                                                                                                                                                                                                                           | 1                                                               | 1                   | Reserved         |  |  |  |  |  |

|                                                                                |        | 1                                                                                                                                                                                                                                                                                                                           | 0                                                               | 0                   | 1/4              |  |  |  |  |  |

|                                                                                |        | 1                                                                                                                                                                                                                                                                                                                           | X                                                               | X                   | Reserved         |  |  |  |  |  |

| VCC2DET#                                                                       | Output | The low-power embedded Pentium processor with MMX technology leaves this pin floating. The embedded Pentium processor with MMX technology drives the pin low.                                                                                                                                                               |                                                                 |                     |                  |  |  |  |  |  |

| CPUTYP, D/P#,<br>FRCMC#, PBGNT#,<br>PBREQ#, PHIT#,<br>PHITM#, BRDYC#,<br>ADSC# | N/A    | These pins have been removed from the low-power embedded Pentium processor with MMX technology.                                                                                                                                                                                                                             |                                                                 |                     |                  |  |  |  |  |  |

#### NOTES:

- Refer to the Low-Power Embedded Pentium<sup>®</sup> Processor with MMX<sup>™</sup> Technology datasheet (order number 273184) for complete pinout specifications.

- 2. Default bus-to-core ratio if BF2-BF0 pins are left floating. This bus fraction is not supported by the low-power embedded Pentium processor with MMX technology.

#### 2.2.3 Processor ID with the CPUID Instruction

The CPUID instruction allows the BIOS and software to determine the type and features of the microprocessor on which it is executing.

When executing CPUID, the low-power embedded Pentium processor with MMX technology behaves like the embedded Pentium processor with MMX technology:

- If the value in EAX is '0', then the 12-byte ASCII string "Genuine Intel" (little endian) is returned in EBX, EDX, and ECX. Also, a '1' is returned to EAX.

- If the value in EAX is '1', then the processor version is returned in EAX and the processor capabilities are returned in EDX. The values of EAX and EDX for the low-power embedded Pentium processor with MMX technology are given in Figure 4, Figure 5, and Table 4.

- If the value in EAX is neither '0' or '1', the low-power embedded Pentium processor with MMX technology writes '0' to all registers.

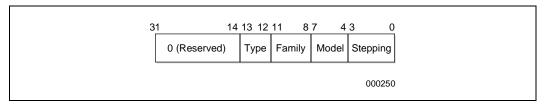

Figure 4. EAX Bit Assignments for CPUID

Figure 5. EDX Bit Assignments for CPUID

| 31       | 24 23 22    |          | 16 1        | 5 14 | 13          | 12               | 11 10 | 9       | 8           | 7     | 6           | 5           | 4           | 3           | 2      | 1           | 0           |

|----------|-------------|----------|-------------|------|-------------|------------------|-------|---------|-------------|-------|-------------|-------------|-------------|-------------|--------|-------------|-------------|

| Reserved | M<br>M<br>X | Reserved | C<br>N<br>C |      | P<br>G<br>E | M<br>T<br>R<br>R | Rsvd  | A P I C | C<br>X<br>8 | M C E | P<br>A<br>E | M<br>S<br>R | T<br>S<br>C | P<br>S<br>E | E<br>D | V<br>M<br>E | F<br>P<br>U |

|          |             |          |             |      |             |                  |       |         |             |       |             |             |             |             |        | 000         | )251        |

The following EAX and EDX values are defined for the CPUID instruction executed with EAX = '1'. The processor version EAX bit assignments are given in Figure 4.

Table 4. EDX Bit Assignment Definitions for CPUID

| Bit   | Value | Comments                                                    |

|-------|-------|-------------------------------------------------------------|

| 0     | 1     | FPU: Floating-Point Unit on-chip                            |

| 1     | 1     | VME: Virtual-8086 Mode Enhancements                         |

| 2     | 1     | DE: Debugging Extensions                                    |

| 3     | 1     | PSE: Page Size Extension                                    |

| 4     | 1     | TSC: Time Stamp Counter                                     |

| 5     | 1     | MSR: Pentium® Processor MSR                                 |

| 6     | 0     | PAE: Physical Address Extension                             |

| 7     | 1     | MCE: Machine Check Exception                                |

| 8     | 1     | CX8: CMPXCHG8B Instruction                                  |

| 98    | 1     | APIC: APIC on-chip <sup>†</sup>                             |

| 10–11 | R     | Reserved–Do not write to these bits or rely on their values |

| 12    | 0     | MTRR: Memory Type Range Registers                           |

| 13    | 0     | PGE: Page Global Enable                                     |

| 14    | 0     | MCA: Machine Check Architecture                             |

| 15    | 1     | CMOV: Conditional Move Instruction supported                |

| 16–22 | R     | Reserved–Do not write to these bits or rely on their values |

| 23    | 1     | Intel <sup>®</sup> Architecture MMX™ Technology supported   |

| 24–31 | R     | Reserved–Do not write to these bits or rely on their values |

<sup>†</sup> Indicates that APIC is present and hardware-enabled (software disabling does not affect this bit).

The family field is the same for all Pentium processors (family = 5H). The model field is different: the embedded Pentium processor with MMX technology model number is 4H, and the low-power embedded Pentium processor with MMX technology model number is 8H. The stepping field has the same format as for the Pentium processor. For the low-power embedded Pentium processor with MMX technology, the stepping field returns 1H for A-step and 2H for B-step. The type field is defined as '00'.

The EDX bit assignments are shown in Figure 5 and Table 4.

After masking the reserve bits, all products based on the low-power embedded Pentium processor with MMX technology will get a value of 0x008003BF (when the APIC is enabled at boot) or 0x008001BF (when the APIC is disabled using the APICEN boot pin) in EDX upon completion of the CPUID instruction.

## 2.3 Electrical and Thermal Features and Differences

This section discusses some of the electrical and thermal features of the low-power embedded Pentium processor with MMX technology and highlights their differences from the embedded Pentium processor with MMX technology.

# 2.3.1 Thermal Analysis

The low-power embedded Pentium processor with MMX technology consumes 7.6 W at 266 MHz. The embedded Pentium processor with MMX technology consumes 17.0 W at 233 MHz. The chassis, heatsink, and fan for the embedded Pentium processor with MMX technology must be capable of dissipating 17 watts of power (power dissipation at 233 MHz) in order for  $T_{CASE}$  of the processor to remain within the specified temperature range (0° C to 70° C). Therefore, the maximum factor in thermal considerations lies with the embedded Pentium processor with MMX technology at 233 MHz. If the thermal solution is designed to handle the heat dissipation for a Pentium processor with MMX technology at 233 MHz, thermal requirements are satisfied for low-power embedded Pentium processor with MMX technology.

# 2.3.2 Split Power Supplies

The low-power embedded Pentium processor with MMX technology uses the same split power planes,  $V_{CORE}$  and  $V_{I/O}$ , as the embedded Pentium processor with MMX technology, except the supply voltages have changed.  $V_{CORE}$  and  $V_{I/O}$  for the embedded Pentium processor with MMX technology are 2.8 V and 3.3 V, respectively, whereas  $V_{CORE}$  and  $V_{I/O}$  for the low-power embedded Pentium processor with MMX technology are 1.9 V and 2.5 V, respectively. Therefore,  $V_{CORE}$  pins must be connected to a voltage supply that can supply 1.9 V and 2.8 V, and  $V_{I/O}$  pins must be connected to a supply of 2.5 V and 3.3 V.

The  $V_{I/O}$  plane supply should supply approximately 2.0 A. This plane not only powers the  $V_{I/O}$  pins of the low-power embedded Pentium processor with MMX technology but also the host clock generator, chipset, L2 cache, and BF2-0 bus-to-core fraction pin pull-ups.

## 2.3.3 2.5 V Input and Output

The inputs and outputs of the low-power embedded Pentium processor with MMX technology are compatible with the 2.5 V JEDEC non-terminated digital interface standard. Both inputs and outputs are also 2.5 V TTL compatible, although the inputs cannot tolerate voltage swings above the 2.5 V  $V_{\rm IN3}$  max. For the low-power embedded Pentium processor with MMX technology outputs, the Pentium processor with MMX technology system support components should use 2.5 V JEDEC compatible inputs. This is because the low-power embedded Pentium processor with MMX technology drives signals according to the 2.5 V JEDEC TTL specification.

For the low-power embedded Pentium processor with MMX technology inputs, the voltage must not exceed the 2.5 V  $V_{IN3}$  max specification. System support components can consist of 2.5 V devices or open-collector devices. In an open-collector configuration, the external resistor may be biased with the 2.5 V  $V_{CC3}$ .

# 2.3.4 $V_{IL3}$ (MAX) and $V_{IH3}$ (MIN)

$V_{IL3}$  (MAX) for the low-power embedded Pentium processor with MMX technology is 0.5 V. This is a decrease from the embedded Pentium processor with MMX technology's specification of 0.8 V.  $V_{IH3}$  (MIN) for low-power embedded Pentium processor with MMX technology is  $V_{CC3} - 0.7$  V. This is a change from the 2.0 V specification for the embedded Pentium processor with MMX technology.

# 2.3.5 Overshoot, Undershoot and Ringback

Signal quality specifications for the low-power embedded Pentium processor with MMX technology are different from the embedded Pentium processor with MMX technology. These specifications must be met to ensure that the components read data properly and that incoming signals do not affect the reliability of the component.

Refer to Table 5 and Table 6 for a summary of overshoot, undershoot, and ringback specifications for the low-power embedded Pentium processor with MMX technology. For more detailed signal quality specifications, refer to the *Low-Power Embedded Pentium* \*\* *Processor with MMX*<sup>TM</sup> *Technology* datasheet (order number 273184).

#### Table 5. Overshoot Specification Summary

| Specification Name                         | Value                                       | Units |

|--------------------------------------------|---------------------------------------------|-------|

| Threshold Level (CLK and PICCLK)           | V <sub>CC3</sub> , nominal +0.3             | V     |

| Threshold Level (all other inputs)         | V <sub>CC3</sub> , nominal +0.5             | V     |

| Maximum Overshoot Level (CLK and PICCLK)   | V <sub>CC3</sub> , nominal +0.6             | V     |

| Maximum Overshoot Level (all other inputs) | V <sub>CC3</sub> , nominal +1.0             | V     |

| Maximum Threshold Duration                 | 20% of clock period above threshold voltage | ns    |

| Maximum Ringback                           | V <sub>CC3</sub> , nominal –0.7             | V     |

# Embedded Pentium Processor with MMX Technology Flexible Motherboard Design Guidelines

# Table 6. Undershoot Specification Summary

| Specification Name                          | Value                                       | Units |

|---------------------------------------------|---------------------------------------------|-------|

| Threshold Level                             | -0.3                                        | V     |

| Threshold Level (all other inputs)          | -0.5                                        | V     |

| Minimum Undershoot Level (CLK and PICCLK)   | -0.6                                        | V     |

| Minimum Undershoot Level (all other inputs) | -1.0                                        | V     |

| Maximum Threshold Duration                  | 20% of clock period below threshold voltage | ns    |

| Maximum Ringback                            | 0.5                                         | V     |

# 3.0 Flexible Motherboard Implementation

This chapter describes the implementation of a split plane flexible motherboard for the Pentium processors with MMX technology using Socket 7.

# 3.1 Overview of Voltage Supply and Split Power Planes

In order to support the Pentium processors with MMX technology with different voltage requirements, the flexible motherboard should include provisions for 1.9 V, 2.5 V, 2.8 V and 3.3 V supply voltages on three different power planes. Refer to Figure 2 on page 8 for a conceptual diagram of which power planes need which voltages.

The specific method for implementing the voltage supplies and partitioning the power planes depends on the actual design. Several options are feasible for designing a flexible motherboard for the Pentium processors with MMX technology. This section provides details for a design that provides flexibility and cost-savings options to the manufacturer.

For all designs,  $V_{CORE}$  must always be electrically isolated from all other power planes because all Pentium processors with MMX technology are split-plane processors, unlike the single-plane embedded Pentium processors. With the  $V_{L/O}$  and 3.3 V power supply planes, however, it is possible to connect the two together when an embedded Pentium processor with MMX technology is used because both run at 3.3 V. This method, which is discussed further in "Voltage Supply and Split Power Planes Implementation and Cost-savings Build Options" on page 22, may provide cost-saving options to the manufacturer.

The most cost-effective way to implement the dual voltages on  $V_{CORE}$  and  $V_{I/O}$  is to use 1.9 V/2.8 V and 2.5 V/3.3 V voltage regulators, respectively. Either a linear or switching voltage regulator can be used. Both options have advantages and disadvantages. The linear voltage regulator component is cheaper than the switching regulator. However, the linear voltage regulator generates more heat (dissipative nature), which may increase the cost of the thermal solution for the board. Also, linear regulators are not as reliable. Refer to "Switching vs. Linear Voltage Regulators" on page 26 for a more detailed comparison of switching and linear voltage regulators.

An auto-configure circuit based on the VCC2DET# signal can be implemented on the flexible motherboard to eliminate the need for jumper/resistor configuration and serve as a safeguard for the low-power embedded Pentium processor with MMX technology. Refer to "Pinout Considerations" on page 15 for a more detailed description of the VCC2DET# signal and how it can be used to safeguard the low-power embedded Pentium processor with MMX technology from higher voltage levels intended for the embedded Pentium processor with MMX technology.

In addition to supplying the correct voltage, the voltage supplies must supply enough current for all components on a particular power plane. The embedded Pentium processor with MMX technology at 233 MHz draws the most current (6.5 A) for its core. Therefore, the  $V_{CC2}$  supply voltage source must supply up to 6.5 A. As for the  $V_{I/O}$  plane, the 2.5 V/3.3 V dual-voltage regulator must supply approximately 2.0 A  $^1$  for the processor's I/O, L2 cache, and chipset.

Because the low-power embedded Pentium processor with MMX technology requires less power (4.0 A at 1.9 V for  $V_{CORE}$  and 380 mA at 2.5 V  $V_{I/O}$ ) than the embedded Pentium processor with MMX technology, a design that meets the requirements for the embedded Pentium processor with MMX technology is adequate for both processor types.

<sup>1.</sup> The 2.0 A value is derived from the 0.75 A required by the V<sub>CC3</sub> pins on the embedded Pentium<sup>®</sup> processor with MMX<sup>TM</sup> technology at 233 MHz, and an estimated 1.0 – 1.25 A for the L2 cache (512 Kbyte), chipset, host clock generator, and pull-ups for the BF[2:0] pins.

# 3.2 Voltage Supply and Split Power Planes Implementation and Cost-savings Build Options

This section discusses a sample flexible motherboard design for the Pentium processor with MMX technology family. The design allows the manufacturer to build motherboards that support all the members of the Pentium processor with MMX technology family or only one particular member. This flexibility can result in significant cost savings and increase the manufacturer's ability to adjust to market conditions without changing the motherboard design.

All three boards are based on one design, differing only in the components that are assembled on the board at build-time.

The conceptual design for the sample implementation is discussed first, followed by sections that detail the three boards and point out the flexibility and cost-savings features of each. Refer to "Switching vs. Linear Voltage Regulators" on page 26 for component options for voltage supplies.

## 3.2.1 Layout and Design of Sample Implementation

Figure 6 shows the basic layout for the sample implementation. The following list highlights the main features:

- $V_{CORE}$  and  $V_{I/O}$  are powered by a 1.9 V/2.8 V and 2.5 V/3.3 V voltage regulator, respectively.

- The L2 cache and chipset reside partially on the V<sub>I/O</sub> power plane and are powered by the 2.5 V/3.3 V voltage regulator.

- An auto-detect circuit driven by the VCC2DET# signal selects the correct voltage for the two dual-voltage regulators.

- The 3.3 V power supply plane is powered by the 3.3 V tap off the system power supply unit. DRAM, TagRAM, and other 3.3 V components reside on this power plane.

- The design is laid out to accept shorting resistors that can connect the V<sub>I/O</sub> and 3.3 V power supply power planes. This layout supports cost-savings build options. See "Board for the Embedded Pentium® Processor with MMX<sup>TM</sup> Technology Only" on page 25.

Figure 6. Basic Design of Sample Implementation

The embedded Pentium processor with MMX technology at 233 MHz draws the most current (6.5 A for  $I_{CC2}$  and 750 mA for  $I_{CC3}$ ) in the Pentium processor with MMX technology family and therefore sets the maximum current that the two dual-voltage regulators must supply. (For  $I_{CC3}$ , the power from the L2 cache and chipset must also be factored in to determine the size of the voltage regulator. Estimated current draw required by the L2 cache and chipset is 1.0 A–1.25 A.)

The auto-configurable regulator circuit triggered by the VCC2DET# signal (see "Pinout Considerations" on page 15) makes it possible to support any processor in the Pentium processor with MMX technology family without the need for jumper/resistor configuration. It also serves as a safeguard for the low-power embedded Pentium processor with MMX technology, which is not 2.8~V~or~3.3~V-tolerant for its  $V_{CORE}$  and  $V_{I/O}$  pins, respectively.

When an embedded Pentium processor with MMX technology is plugged into a Socket 7, the VCC2DET# signal is low, causing the auto-detect circuit to toggle the 1.9 V/2.8 V voltage regulator to 2.8 V ( $V_{CORE}$ ), and the 2.5 V/3.3 V voltage regulator to 3.3 V ( $V_{I/O}$ ).

When a low-power embedded Pentium processor with MMX technology is plugged into a Socket 7, the floating VCC2DET# signal is pulled high by the weak pull-up resistor in the autoconfigure circuit. This causes the 1.9 V/2.8 V voltage regulator to toggle to 1.9 V ( $V_{CORE}$ ), and the 2.5 V/3.3 V voltage regulator to toggle to 2.5 V ( $V_{IVO}$ ).

# 3.2.2 Board to Support All Members of the Pentium<sup>®</sup> Processor with MMX<sup>™</sup> Technology Family

Configuring the sample design to support all members of the Pentium processor with MMX technology family is straightforward. This board follows the basic layout and design from "Layout and Design of Sample Implementation" on page 22, with the following requirement: The slots designed for the shorting resistors to connect the  $V_{\rm I/O}$  and 3.3 V power supply plane must remain empty. In other words, the resistors are not assembled onto the board. This maintains three separate power planes at all times, which is necessary to support the low-power embedded Pentium processor with MMX technology.

With the exception of this requirement, the flexible motherboard design follows the design outlined in "Layout and Design of Sample Implementation" on page 22:

- 1.9 V/2.8 V and 2.5 V/3.3 V voltage regulators power the V<sub>CORE</sub> and V<sub>I/O</sub> power planes, respectively.

- 3.3 V power supply is powered from the 3.3 V tap off the system power supply unit.

- The auto-detect circuit driven by VCC2DET# selects the correct voltage level.

This is the most flexible of the options discussed in this document. This option offers two key advantages:

- This design gives the consumer an upgrade path from an embedded Pentium processor with MMX technology to a low-power embedded Pentium processor with MMX technology, without changing motherboards.

- From a manufacturer's perspective, this design offers the flexibility to adjust to changing market conditions with one motherboard. The decision of which processor to install in the system can be made at assembly time.

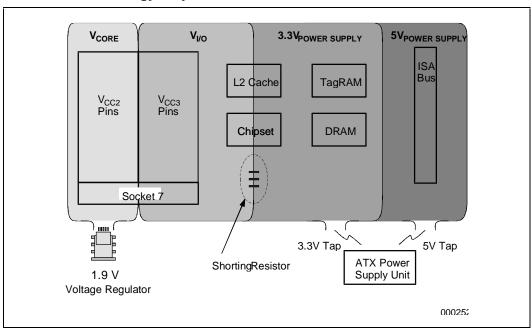

# 3.2.3 Board for the Low-Power Embedded Pentium<sup>®</sup> Processor with MMX<sup>™</sup> Technology Only

Building a board to support only the low-power embedded Pentium processor with MMX technology is also straightforward. In fact, from a motherboard design perspective, it is identical to the all-members board discussed in "Board to Support All Members of the Pentium® Processor with MMX<sup>TM</sup> Technology Family" above.

- 1.9 V and 2.5 V voltage regulators power the  $V_{CORF}$  and  $V_{I/O}$  power planes, respectively.

- 3.3 V power supply is powered from the 3.3 V tap off the system power supply unit.

- The auto-detect circuit driven by VCC2DET# selects the correct voltage level.

- Shorting resistor slots are left empty to maintain three separate power planes.

The primary reason for considering a board of this type is cost savings. The most compelling cost savings is in scaling back the thermal solution (e.g., heatsinks, fans) for the system. This is possible because the low-power embedded Pentium processor with MMX technology at 266 MHz consumes less power than the 233 MHz processor. Additional cost savings is possible using a 1.9 V voltage regulator that does not need to supply as much current, because  $I_{CC2}$  for the low-power processor at 266 MHz (4.0 A) is less than for the 233 MHz processor (6.5 A).

The 1.9 V and 2.5 V voltage regulator could be replaced with discrete 1.9 V and 2.5 V regulators, because this board supports only one processor. This provides some cost-savings, but the additional cost of changing the Bill of Materials (BOM) and modifying the assembly line to support this may outweigh the cost-savings.

# 3.2.4 Board for the Embedded Pentium<sup>®</sup> Processor with MMX<sup>™</sup> Technology Only

This board is based on the same design as the other options presented above. The main reason for considering this board is cost savings. This design takes advantage of the fact that with an embedded Pentium processor with MMX technology, both the  $V_{I/O}$  and 3.3 V power supply planes are at 3.3 V. This opens the possibility of connecting the  $V_{I/O}$  and 3.3 V power supply planes together, removing the need for one of the voltage regulators.

As shown in Figure 7, this design uses only one voltage regulator. Other features include:

- A 2.8 V voltage regulator to power the V<sub>CORE</sub> power plane

- Shorting resistor slots that are stuffed with the resistors in order to connect the  $V_{I/O}$  and 3.3 V power supply power plane

- $V_{I/O}$  and 3.3 V power supply power planes, which are powered from the 3.3 V tap off the system power supply unit<sup>1</sup>

Figure 7. Board for the Embedded Pentium<sup>®</sup> Processor with MMX<sup>™</sup> Technology Only

<sup>1.</sup> Powering the  $V_{CC3}$  pins on the embedded Pentium<sup>®</sup> processor with MMX<sup>TM</sup> technology with the 3.3 V supply from the power supply unit is possible because the ATX power supply's 3.3 V supply specification meets the processor's requirements. The processor requires  $V_{LO}$  to be between 3.135 V and 3.6 V. The ATX power supply guarantees its 3.3 V supply at 3.3 V  $\pm$ 4% (3.168 V $\pm$ 3.432 V).

# Embedded Pentium<sup>®</sup> Processor with MMX™ Technology Flexible Motherboard Design Guidelines

Stuffing the shorting resistors and removing the second voltage regulator normally used for the  $V_{I/O}$  plane are the most significant differences between this board design and the other designs. The voltage tap from the power supply unit will be able to handle the voltage draw from the processor's I/O, L2 cache, and chipset, and from all other 3.3 V components (e.g., DRAM).

The main cost savings with this design comes in not needing the second voltage regulator. This saves a significant amount on the Bill of Materials (BOM). This can all be done at build-time with one motherboard design.

The voltage regulator could be replaced with a discrete 2.8 V regulator because this board supports only one processor. This provides some cost-savings, but the additional cost of changing the Bill of Materials (BOM) and modifying the assembly line to support this may outweigh the cost-savings.

# 3.3 Switching vs. Linear Voltage Regulators

Both switching and linear voltage regulators can be used as voltage supplies for the flexible motherboard. Both regulators have advantages and disadvantages. This section highlights the general working principles of the two types of regulators and the factors that will affect your decision.

# 3.3.1 General Principles Of Switching And Linear Voltage Regulators

In dissipative regulation of voltage or current (as in a linear voltage regulator), power is lost in the form of heat. The dissipative element, a power transistor, is given the task of "soaking up" the excess power, which can result in heat dissipation problems. It does not matter how sophisticated the control electronics are in such a power supply; the dissipative element functions as a rheostat, which is a relatively simple method of regulating power.

In the switching power supply, a switching device is substituted for the dissipative device. Control or regulation of power is achieved by varying the duty cycle or repetition rate of the switch rather than its resistance. The ideal switch does not absorb or dissipate power—it is either completely on or completely off, with no intermediate resistive state to dissipate power. As a result, the overall efficiency of a switching regulator is much higher than conventional dissipative-type power supplies. A comparison is provided in Table 7.

| Table 7. Comparison Between Switching and Linear Voltage Regulators |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

| Feature                           | Switching Regulator                                                                                                                                   | Linear Regulator                                                                                                                                                         |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Efficiency                        | 65% to 85% is expected.                                                                                                                               | 25% to 50% is expected.                                                                                                                                                  |  |  |

| Overall Regulation                | 1% is common specification. Tighter regulation is usually difficult to achieve                                                                        | 1% is common. Much tighter regulation is available at greater cost.                                                                                                      |  |  |

| Ripple                            | 20 to 50 mV peak-to-peak is average. Smaller ripple voltage is usually difficult to achieve.                                                          | 5 mV peak-to-peak is average and lower values can be obtained at greater cost.                                                                                           |  |  |

| Temperature Rise                  | 20°C to 40°C is easily achieved.                                                                                                                      | 50° C to 100° C is average, depending upon heat dissipation techniques.                                                                                                  |  |  |

| Cost                              | Cost decreases with higher switch rates. There is a general tendency for costs to decrease as semiconductors evolve. Cost crossover keeps decreasing. | Small linear regulators have a cost advantage. However, considering all the factors in the overall system, other cost factors become very significant in larger ratings. |  |  |

| Reliability                       | More parts, but recent designs capitalize on ICS. Enhanced reliability obtained from cooler operation.                                                | Higher operating temperature often degrades reliability.                                                                                                                 |  |  |

| Power Density                     | 2.5 to 4 or 5 W per cubic inch for 20- to 50-<br>KHz switchers. Higher switching rates can<br>yield 25 to 75 W per cubic inch.                        | 0.3 to 1.0 W per cubic inch depending on power level, input voltage range, and heat dissipation hardware.                                                                |  |  |

| Isolation from<br>Line Transients | Very good, often greater than 60 dB.                                                                                                                  | Generally inferior to switching types. Noisy line often affects load.                                                                                                    |  |  |

| RFI and EMI                       | Can be troublesome. Requires attention to shielding, suppression and filtering.                                                                       | Less likely to be an adverse factor.                                                                                                                                     |  |  |

# 3.3.2 Design Considerations for Voltage Supplies

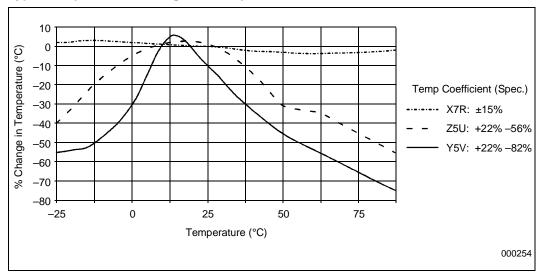

This section discusses design considerations that should be taken into account when choosing between switching and linear voltage regulators.