intel®

# Pentium<sup>®</sup> III Processor at 450 MHz, 500 MHz, and 550 MHz

Datasheet

# Product Features

- Available at 450 MHz, 500 MHz, and 550 MHz

- System bus frequency at 100 MHz

- Binary compatible with applications running on previous members of the Intel microprocessor line

- Dynamic execution micro architecture

- Dual Independent Bus architecture: Separate dedicated external System Bus and dedicated internal high-speed cache bus

- Streaming SIMD Extensions for enhanced video, sound and 3D performance

- Power Management capabilities

- -System Management mode

- -Multiple low-power states

- Intel Processor Serial Number

- Optimized for 32-bit applications running on advanced 32-bit operating systems

- Single Edge Contact Cartridge (S.E.C.C.) and S.E.C.C.2 packaging technology; the S.E.C. cartridges deliver high performance with improved handling protection and socketability

- Integrated high performance 16-Kbyte instruction and 16-Kbyte data, nonblocking, level-one cache

- Available with integrated 512-Kbyte unified, nonblocking, level-two cache

- Enables systems which are scaleable up to two processors

- Error-correcting code for System Bus data

The Pentium<sup>®</sup> III processor is designed for high-performance desktops and for workstations and servers. It is binary compatible with previous Intel Architecture processors. The Pentium III processor provides the best performance available for applications running on advanced operating systems such as Windows\* 95, Windows NT and UNIX\*. This is achieved by integrating the best attributes of Intel processors—the dynamic execution, Dual Independent Bus architecture plus Intel MMX<sup>TM</sup> technology—bringing a new level of performance for systems buyers. The Pentium III processor is scalable to two processors in a multiprocessor system and extends the power of today's Pentium II processor with performance headroom for business media, communication and internet capabilities. Systems based on Pentium III processors also include the latest features to simplify system management and lower the cost of ownership for large and small business environments. The Pentium III processor offers great performance for today's applications.

# intel

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium® III processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1999

\*Third-party brands and names are the property of their respective owners.

| 1.0 | Intro                       | duction                                                                                                                                                                             | 7                    |

|-----|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|     | 1.1<br>1.2                  | Terminology<br>1.1.1 S.E.C.C.2 and S.E.C.C. Packaged Processor Terminology<br>Related Documents                                                                                     | 8                    |

| 2.0 |                             | rical Specifications                                                                                                                                                                |                      |

| 2.0 | 2.1<br>2.2                  | Processor System Bus and VREF<br>Clock Control and Low Power States<br>2.2.1 Normal State—State 1                                                                                   | 10<br>11             |

|     |                             | <ul> <li>2.2.2 AutoHALT Powerdown State—State 2</li> <li>2.2.3 Stop-Grant State—State 3</li> <li>2.2.4 HALT/Grant Snoop State—State 4</li> <li>2.2.5 Sleep State—State 5</li> </ul> | 13<br>13             |

|     |                             | <ul><li>2.2.6 Deep Sleep State—State 6</li><li>2.2.7 Clock Control</li></ul>                                                                                                        |                      |

|     | 2.3<br>2.4                  | Power and Ground Pins<br>Decoupling Guidelines<br>2.4.1 Processor VCC <sub>CORF</sub> Decoupling                                                                                    | 15                   |

|     | 2.5                         | 2.4.2 Processor System Bus AGTL+ Decoupling<br>Processor System Bus Clock and Processor Clocking                                                                                    | 16                   |

|     |                             | 2.5.1 Mixing Processors of Different Frequencies                                                                                                                                    | 16                   |

|     | 2.6<br>2.7<br>2.8           | Voltage Identification<br>Processor System Bus Unused Pins<br>Processor System Bus Signal Groups                                                                                    | 18<br>18             |

|     | 2.9<br>2.10<br>2.11<br>2.12 | 2.8.1 Asynchronous vs. Synchronous for System Bus Signals<br>Test Access Port (TAP) Connection<br>Maximum Ratings<br>Processor DC Specifications<br>AGTL+ System Bus Specifications | 20<br>20<br>21       |

|     | 2.13                        | System Bus AC Specifications                                                                                                                                                        |                      |

| 3.0 | 3.1                         | em Bus Signal Simulations<br>System Bus Clock (BCLK) Signal Quality Specifications                                                                                                  | 35                   |

|     | 3.2<br>3.3                  | and Measurement Guidelines                                                                                                                                                          | 37<br>39<br>40<br>40 |

| 4.0 | Ther                        | mal Specifications and Design Considerations                                                                                                                                        | 41                   |

|     | 4.1                         | Thermal Specifications     4.1.1   Thermal Diode                                                                                                                                    |                      |

| 5.0 | S.E.C                       | C.C. and S.E.C.C.2 Mechanical Specifications                                                                                                                                        | 44                   |

|     | 5.1<br>5.2                  | S.E.C.C. Mechanical Specifications                                                                                                                                                  |                      |

|     | 5.3  | S.E.C.C.2 Structural Mechanical Specification                            | 57 |

|-----|------|--------------------------------------------------------------------------|----|

|     | 5.4  | Processor Package Materials Information                                  |    |

|     | 5.5  | Pentium <sup>®</sup> III Processor Signal Listing                        |    |

|     | 5.6  | Pentium <sup>®</sup> III Processor Core Pad to Substrate Via Assignments | 67 |

|     |      | 5.6.1 Processor Core Pad Via Assignments                                 | 67 |

|     |      | 5.6.2 Processor Core Signal Assignments                                  | 68 |

| 6.0 | Boxe | ed Processor Specifications                                              | 77 |

|     | 6.1  | Introduction                                                             | 77 |

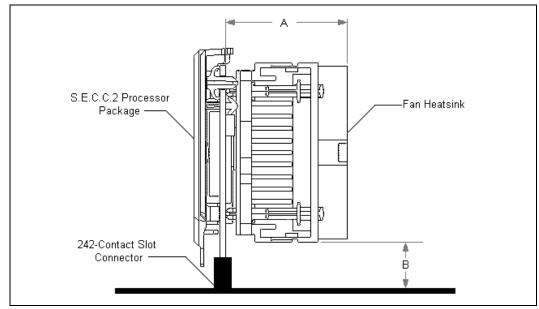

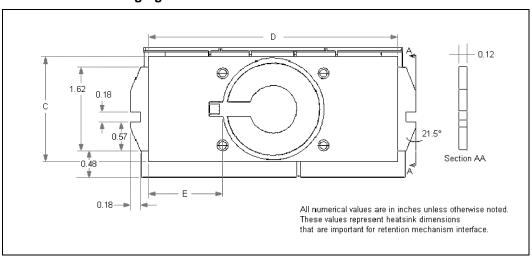

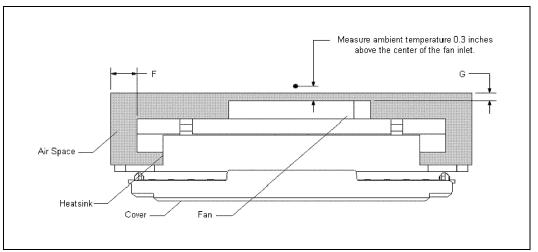

|     | 6.2  | Fan Heatsink Mechanical Specifications                                   | 78 |

|     |      | 6.2.1 Boxed Processor Fan Heatsink Dimensions                            | 78 |

|     |      | 6.2.2 Boxed Processor Fan Heatsink Weight                                |    |

|     |      | 6.2.3 Boxed Processor Retention Mechanism                                |    |

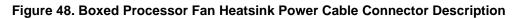

|     | 6.3  | Fan Heatsink Electrical Requirements                                     |    |

|     |      | 6.3.1 Fan Heatsink Power Supply                                          |    |

|     | 6.4  | Fan Heatsink Thermal Specifications                                      |    |

|     |      | 6.4.1 Boxed Processor Cooling Requirements                               | 82 |

| 7.0 | Pent | ium <sup>®</sup> III Processor Signal Description                        |    |

|     | 7.1  | Alphabetical Signals Reference                                           |    |

|     | 7.2  | Signal Summaries                                                         |    |

|     |      |                                                                          |    |

# Figures

| 1  | Second Level (L2) Cache Implementation                                 | 8  |

|----|------------------------------------------------------------------------|----|

| 2  | AGTL+ Bus Topology                                                     |    |

| 3  | Stop Clock State Machine                                               | 12 |

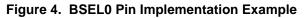

| 4  | BSEL0 Pin Implementation Example                                       | 20 |

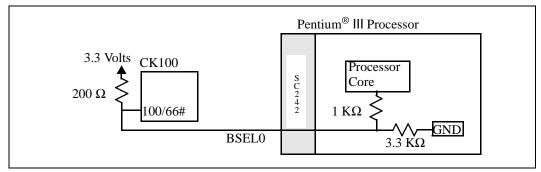

| 5  | BCLK to Core Logic Offset                                              | 31 |

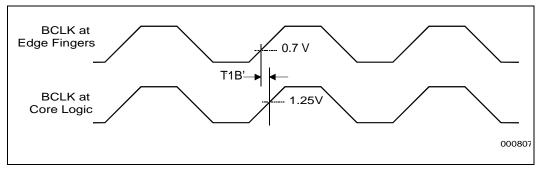

| 6  | BCLK, PICCLK, and TCK Generic Clock Waveform                           | 32 |

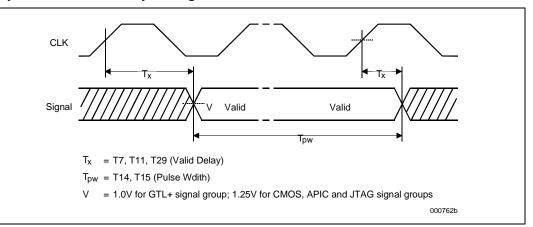

| 7  | System Bus Valid Delay Timings                                         | 33 |

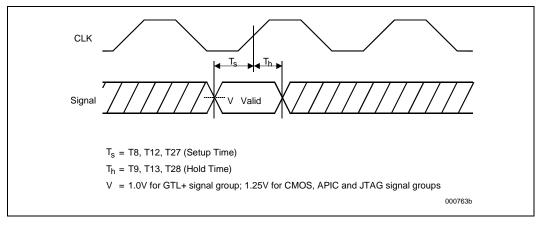

| 8  | System Bus Setup and Hold Timings                                      | 33 |

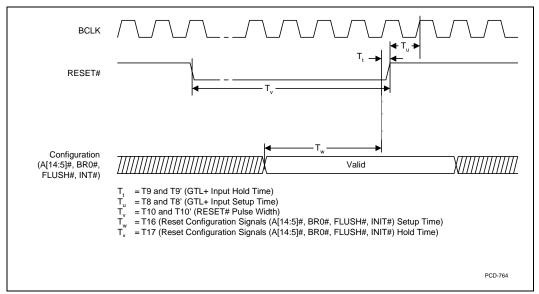

| 9  | System Bus Reset and Configuration Timings                             | 34 |

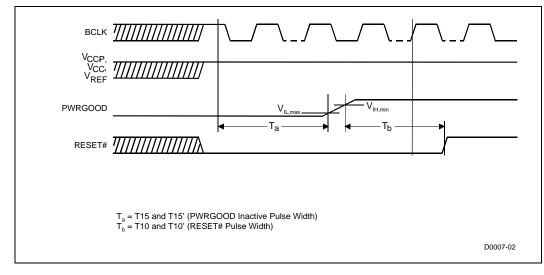

| 10 | Power-On Reset and Configuration Timings                               | 34 |

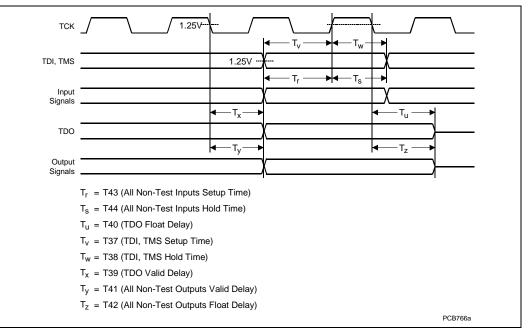

| 11 | Test Timings (TAP Connection)                                          | 35 |

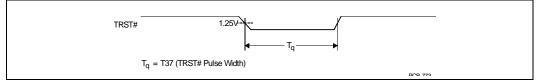

| 12 | Test Reset Timings                                                     | 35 |

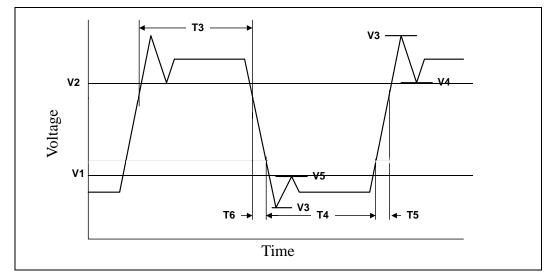

| 13 | BCLK, TCK, PICCLK Generic Clock Waveform at the Processor Core Pins    | 36 |

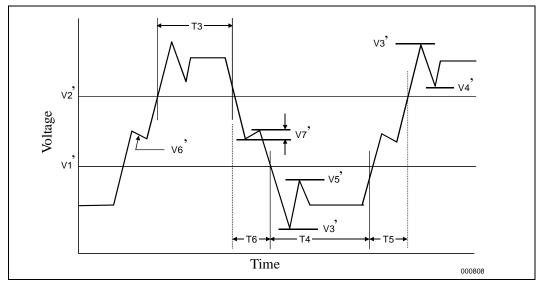

| 14 | BCLK, TCK, PICCLK Generic Clock Waveform at the Processor Edge Fingers | 37 |

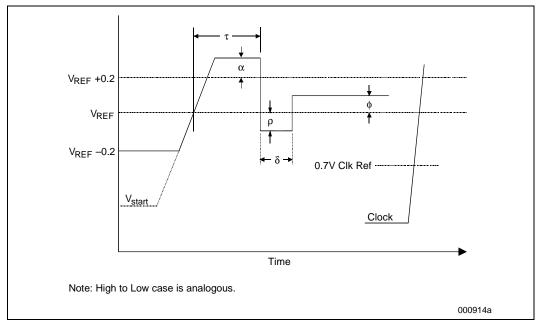

| 15 | Low to High AGTL+ Receiver Ringback Tolerance                          | 39 |

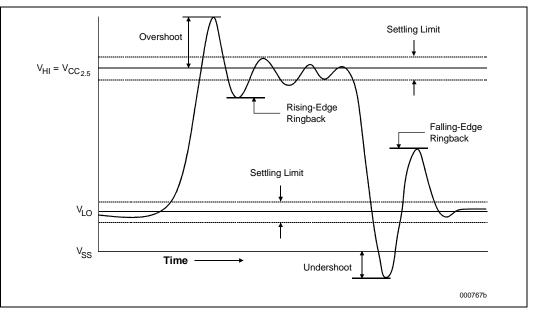

| 16 | Non-AGTL+ Overshoot/Undershoot, Settling Limit, and Ringback           | 39 |

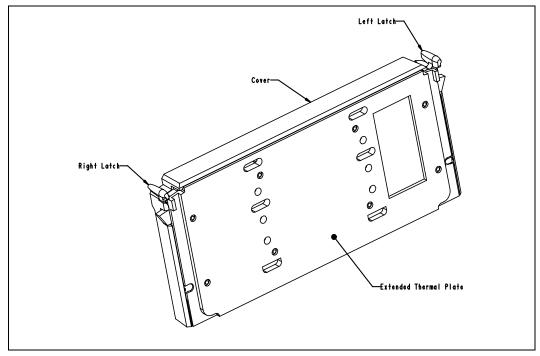

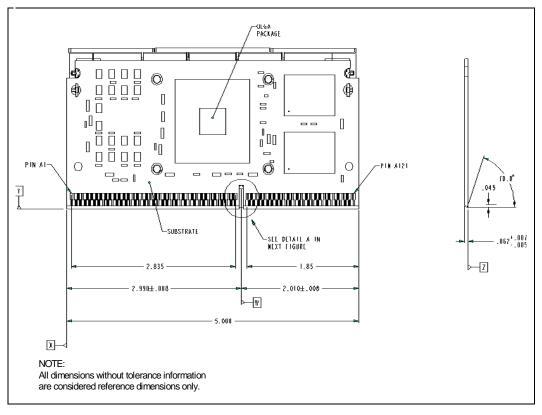

| 17 | S.E.C.Cartridge — 3-Dimensional View                                   | 41 |

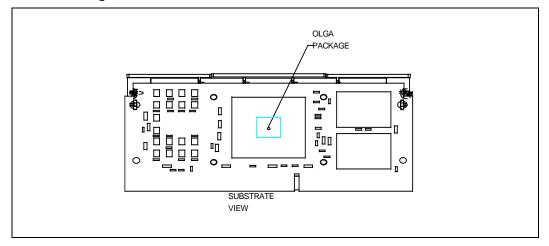

| 18 | S.E.C.Cartridge 2 — Substrate View                                     | 42 |

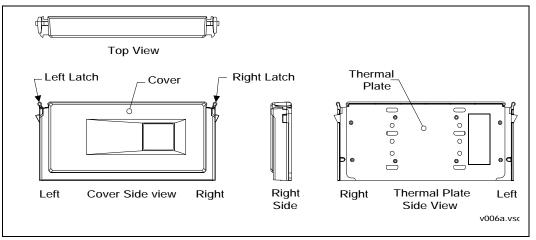

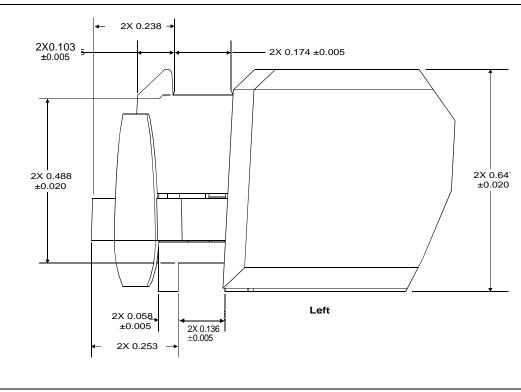

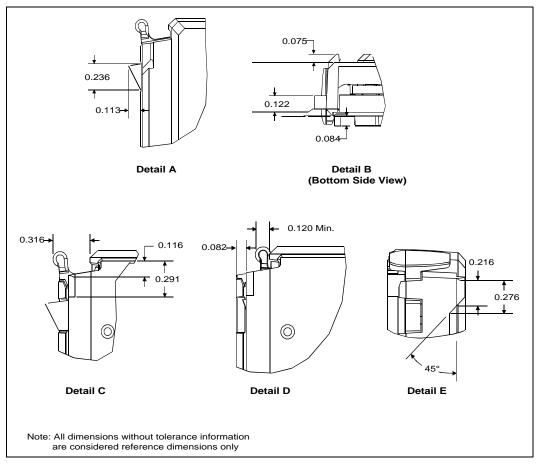

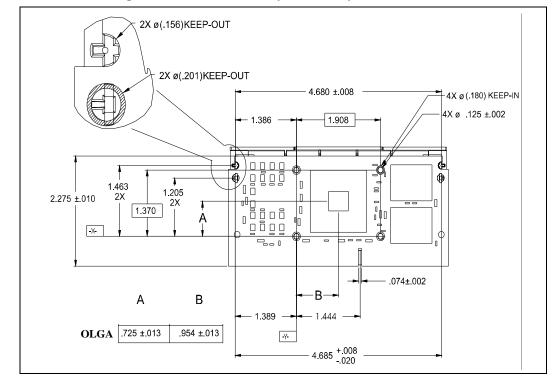

| 19 | S.E.C.C. Packaged Processor — Multiple Views                           | 45 |

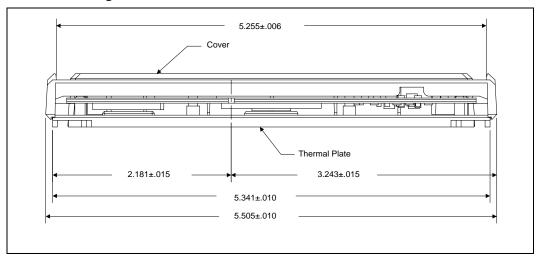

| 20 | S.E.C.C. Packaged Processor — Extended Thermal Plate Side Dimensions   | 45 |

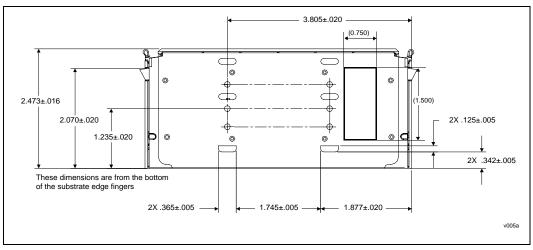

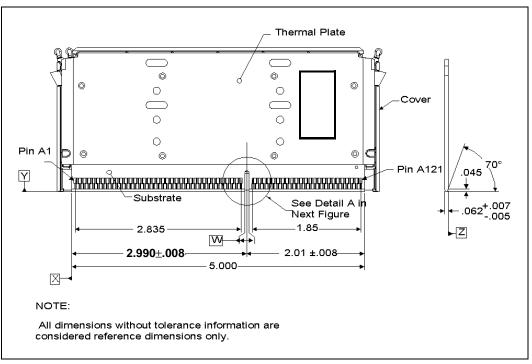

| 21 | S.E.C.C. Packaged Processor — Bottom View Dimensions                   | 46 |

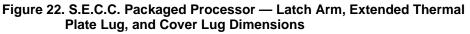

| 22 | S.E.C.C. Packaged Processor — Latch Arm, Extended Thermal              |    |

|    | Plate Lug, and Cover Lug Dimensions                                    | 46 |

| 23 | S.E.C.C. Packaged Processor — Latch Arm, Extended Thermal              |    |

|    | Plate, and Cover Detail Dimensions (Reference Dimensions Only)         | 47 |

# intel

| 24 | S.E.C.C. Packaged Processor — Extended Thermal Plate<br>Attachment Detail Dimensions | 48 |

|----|--------------------------------------------------------------------------------------|----|

| 25 | S.E.C.C. Packaged Processor — Extended Thermal Plate                                 |    |

|    | Attachment Detail Dimensions, Continued                                              | 49 |

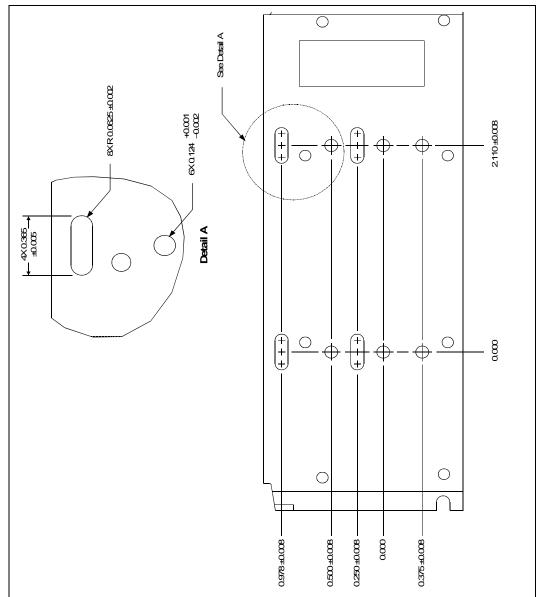

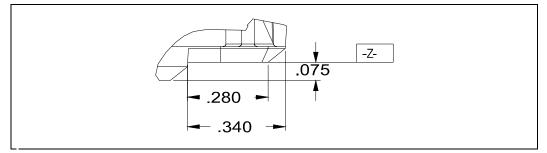

| 26 | S.E.C.C. Packaged Processor Substrate — Edge Finger                                  |    |

|    | Contact Dimensions                                                                   | 49 |

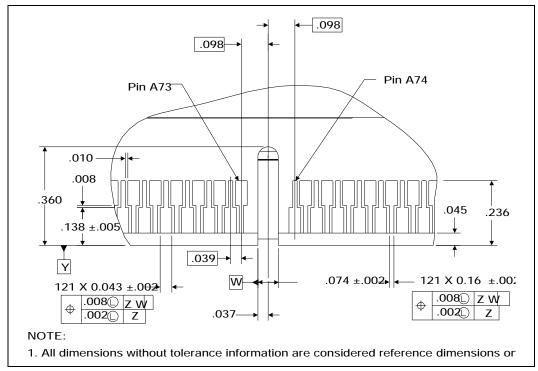

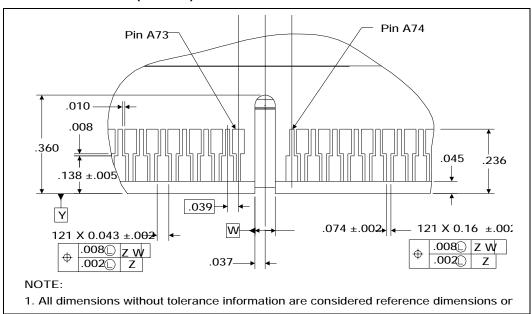

| 27 | S.E.C.C. Packaged Processor Substrate — Edge Finger                                  |    |

|    | Contact Dimensions, Detail A                                                         |    |

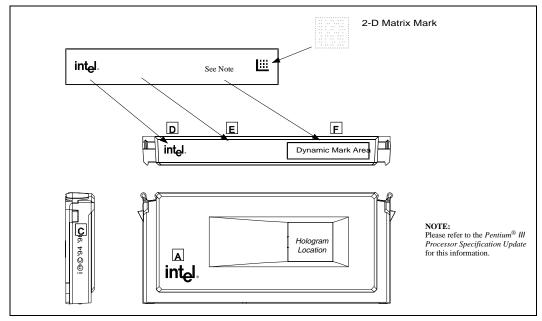

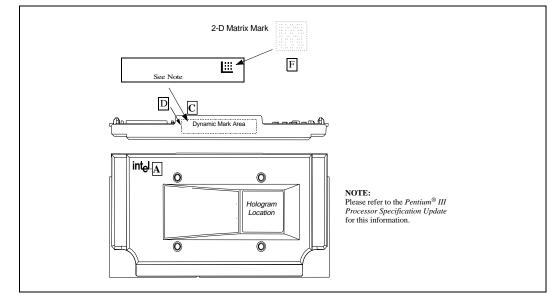

| 28 | Pentium® III Processor Markings (S.E.C.C. Packaged Processor)                        |    |

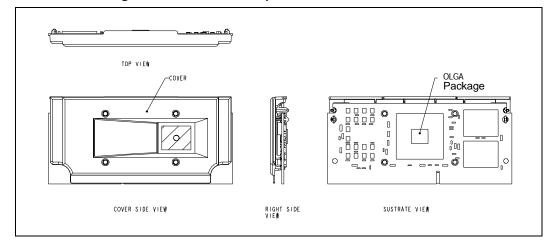

| 29 | S.E.C.C.2 Packaged Processor — Multiple Views                                        |    |

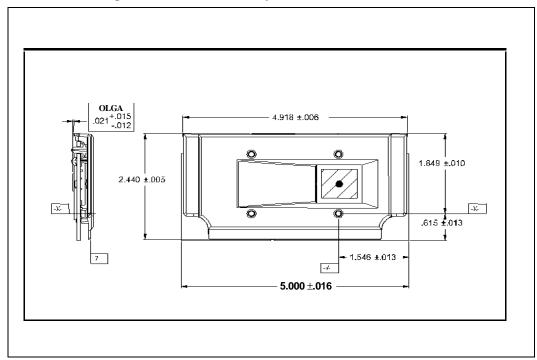

| 30 | S.E.C.C.2 Packaged Processor Assembly — Primary View                                 |    |

| 31 | S.E.C.C.2 Packaged Processor Assembly — Cover View with Dimensions                   |    |

| 32 | S.E.C.C.2 Packaged Processor Assembly — Heat Sink Attach Boss Section                |    |

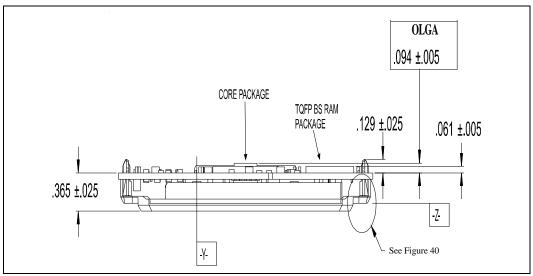

| 33 | S.E.C.C.2 Packaged Processor Assembly — Side View                                    |    |

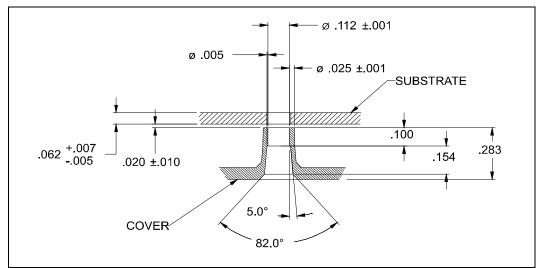

| 34 | Detail View of Cover in the Vicinity of the Substrate Attach Features                | 54 |

| 35 | S.E.C.C.2 Packaged Processor Substrate — Edge Finger                                 |    |

|    | Contact Dimensions                                                                   | 54 |

| 36 | S.E.C.C.2 Packaged Processor Substrate — Edge Finger                                 |    |

| 07 | Contact Dimensions (Detail A)                                                        | 55 |

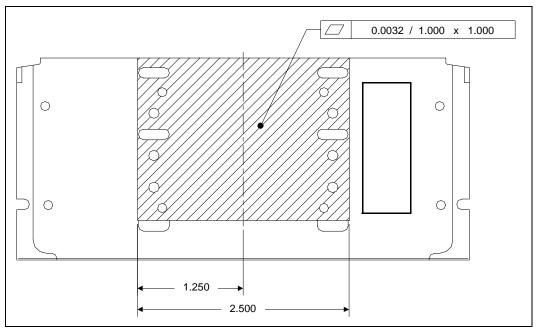

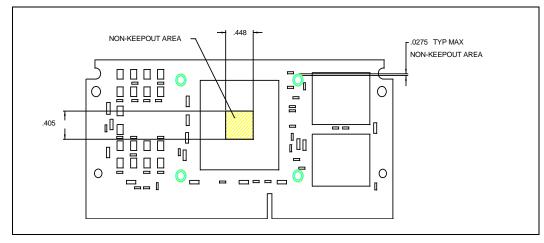

| 37 | S.E.C.C.2 Packaged Processor Substrate — Keep In Zones                               |    |

| 38 | S.E.C.C.2 Packaged Processor Substrate — Keep-Out Zone                               |    |

| 39 | Pentium® III Processor Markings (S.E.C.C.2 Package)                                  |    |

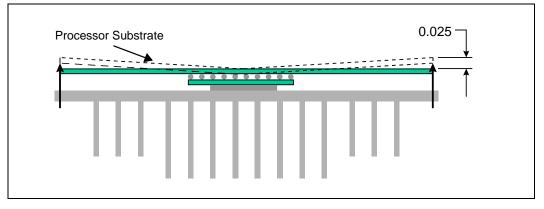

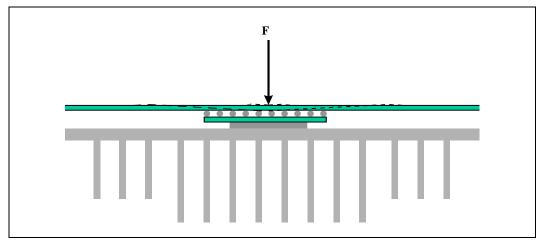

| 40 | Substrate Deflection Away From Heat Sink                                             |    |

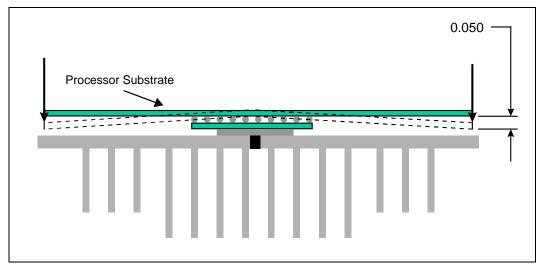

| 41 | Substrate Deflection Toward the Heatsink                                             |    |

| 42 | S.E.C.C.2 Packaged Processor Specifications                                          |    |

| 43 | Processor Core Pad Via Assignments                                                   | 67 |

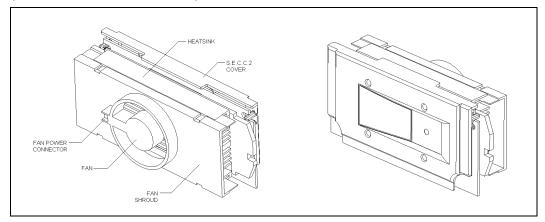

| 44 | Boxed Pentium <sup>®</sup> III Processor in the S.E.C.C.2 Packaging                  |    |

| 45 | (Fan Power Cable Not Shown)                                                          |    |

| 45 | Side View Space Requirements for the Boxed Processor<br>with S.E.C.C.2 Packaging     | 70 |

| 46 | Front View Space Requirements for the Boxed Processor                                |    |

| 40 | with S.E.C.C.2 Packaging                                                             | 79 |

| 47 | Top View Air Space Requirements for the Boxed Processor                              | 79 |

| 48 | Boxed Processor Fan Heatsink Power Cable Connector Description                       |    |

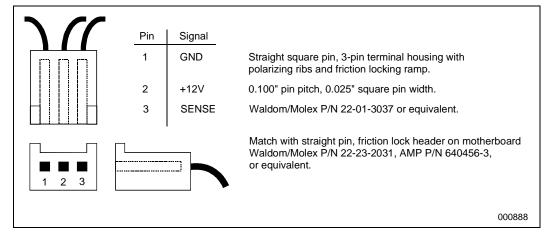

| 49 | Recommended Baseboard Power Header Placement Relative to                             |    |

|    | Fan Power Connector and Pentium <sup>®</sup> III Processor                           | 81 |

# Tables

| 1  | Related Documents                                                  | 9  |

|----|--------------------------------------------------------------------|----|

| 2  | Voltage Identification Definition                                  | 17 |

| 3  | System Bus Signal Groups                                           | 19 |

| 4  | Absolute Maximum Ratings                                           |    |

| 5  | Voltage and Current Specifications                                 | 22 |

| 6  | AGTL+ Signal Groups DC Specifications                              |    |

| 7  | Non-AGTL+ Signal Group DC Specifications                           |    |

| 8  | AGTL+ Bus Specifications                                           |    |

| 9  | System Bus AC Specifications (Clock) at the Processor Edge Fingers |    |

| 10 | System Bus AC Specifications (Clock) at Processor Core Pins        |    |

| 11 | Valid System Bus, Core Frequency, and Cache Bus Frequencies        |    |

| 12 | System Bus AC Specifications (AGTL+ Signal Group) at the           |    |

|    | Processor Edge Fingers                                             | 27 |

| 13 | System Bus AC Specifications (AGTL+ Signal Group) at the<br>Processor Core Pins | 27  |

|----|---------------------------------------------------------------------------------|-----|

| 14 | System Bus AC Specifications (CMOS Signal Group) at the                         |     |

|    | Processor Edge Fingers                                                          | 28  |

| 15 | System Bus AC Specifications (CMOS Signal Group) at the Processor Core Pins     | 28  |

| 16 | System Bus AC Specifications (Reset Conditions)                                 | 29  |

| 17 | System Bus AC Specifications (APIC Clock and APIC I/O) at the                   | _0  |

|    | Processor Edge Fingers                                                          | 29  |

| 18 | System Bus AC Specifications (APIC Clock and APIC I/O) at the                   |     |

|    | Processor Core Pins                                                             | 30  |

| 19 | System Bus AC Specifications (TAP Connection) at the                            |     |

|    | Processor Edge Fingers                                                          | 30  |

| 20 | System Bus AC Specifications (TAP Connection) at the                            |     |

|    | Processor Core Pins                                                             |     |

| 21 | BCLK Signal Quality Specifications for Simulation at the Processor Core         |     |

| 22 | BCLK Signal Quality Guidelines for Edge Finger Measurement                      | 37  |

| 23 | AGTL+ Signal Groups Ringback Tolerance Specifications                           |     |

|    | at the Processor Core                                                           | 38  |

| 24 | AGTL+ Signal Groups Ringback Tolerance Guidelines for Edge                      | ~ ~ |

| ~- | Finger Measurement                                                              | 38  |

| 25 | Signal Ringback Specifications for Non-AGTL+ Signal Simulation                  | 40  |

| ~~ | at the Processor Core                                                           |     |

| 26 | Signal Ringback Guidelines for Non-AGTL+ Signal Edge Finger Measurement         |     |

| 27 | Thermal Specifications for S.E.C.C. Packaged Processors                         |     |

| 28 | Thermal Specifications for S.E.C.C.2 Packaged Processors                        |     |

| 29 | Thermal Diode Parameters                                                        |     |

| 30 | Thermal Diode Interface                                                         |     |

| 31 | Description Table for Processor Markings (S.E.C.C. Packaged Processor)          |     |

| 32 | Description Table for Processor Markings (S.E.C.C.2 Packaged Processor)         |     |

| 33 | S.E.C.C.2 Pressure Specifications.                                              |     |

| 34 | S.E.C.C. Materials                                                              |     |

| 35 | S.E.C.C.2 Materials                                                             |     |

| 36 | Signal Listing in Order by Pin Number                                           |     |

| 37 | Signal Listing in Order by Signal Name                                          |     |

| 38 | Via Listing in Order by Signal Name                                             |     |

| 39 | Via Listing in Order by Via Location                                            |     |

| 40 | Boxed Processor Fan Heatsink Spatial Dimensions                                 |     |

| 41 | Fan Heatsink Power and Signal Specifications                                    |     |

| 42 | Baseboard Fan Power Connector Location                                          |     |

| 43 | Signal Description                                                              |     |

| 44 | Output Signals                                                                  |     |

| 45 | Input Signals                                                                   |     |

| 46 | Input/Output Signals (Single Driver)                                            |     |

| 47 | Input/Output Signals (Multiple Driver)                                          | 92  |

# intel®

# 1.0 Introduction

The Pentium<sup>®</sup> III processor is next in the Intel IA-32 processor line. The Pentium III processor, like the Pentium<sup>®</sup> II processor, implements a Dynamic Execution microarchitecture—a unique combination of multiple branch prediction, data flow analysis, and speculative execution. This enables these processors to deliver higher performance than the Pentium processor, while maintaining binary compatibility with all previous Intel Architecture processors. The Pentium III processor also executes MMX technology instructions for enhanced media and communication performance just as it's predecessor, the Pentium III processor. The Pentium III processor executes Streaming SIMD Extensions for enhanced floating point and 3-D application performance. In addition, the Pentium III processor extends the concept of processor identification with the addition of a processor serial number. Refer to the *Intel Processor Serial Number* (Order Number 245119) for more detailed information. The Pentium III processor utilizes multiple low-power states such as AutoHALT, Stop-Grant, Sleep, and Deep Sleep to conserve power during idle times.

The Pentium III processor utilizes the same multiprocessing system bus technology as the Pentium II processor. This allows for a higher level of performance for both uni-processor and twoway multiprocessor (2-way MP) systems. Memory is cacheable for 4 GB of addressable memory space, allowing significant headroom for desktop systems. Refer to the S-spec number table in the *Pentium*<sup>®</sup> *III Processor Specification Update* (Order Number 244453) to determine the cacheability for a given processor.

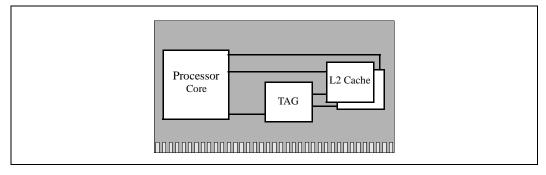

The Pentium III processor system bus operates in the same manner as the Pentium II processor system bus. The Pentium II processor system bus uses a variant of GTL+ signaling technology called Assisted Gunning Transceiver Logic (AGTL+) signaling technology. The Pentium III processor uses commercially available parts for the second level (L2) cache. The L2 cache is composed of a TagRAM and burst pipelined synchronous static RAM (BSRAM) memories and are implemented with multiple die. Transfer rates between a Pentium III processor's core and L2 cache are at one-half the processor core clock frequency and scale with the processor core frequency. Both the TagRAM and BSRAM receive clocked data directly from the Pentium III processor core. As with the Pentium II processor, the Pentium III processor has a dedicated L2 cache bus, thus maintaining the dual independent bus architecture to deliver high bus bandwidth and high performance (see Figure 1).

Pentium III processor offer either Single Edge Contact Cartridge (S.E.C.C.) or Single Edge Contact Cartridge 2 (S.E.C.C.2) package technology. These package technologies allow the L2 cache to remain tightly coupled to the processor, while enabling use of high volume commercial BSRAM components. The L2 cache is performance optimized and tested at the package level. The S.E.C.C. and S.E.C.C.2 packages utilize surface mounted technology and a substrate with an edge finger connection.

The S.E.C.C. package has the following features: an extended thermal plate, a cover, and a substrate with an edge finger connection. The extended thermal plate allows heatsink attachment or customized thermal solutions. The S.E.C.C.2 package has a cover and a substrate with an edge finger connection. This allows the thermal solutions to be placed directly onto the processor core package. The edge finger connection maintains socketability for system configuration. The edge finger connector is called the 'SC242 connector' in this and other documentation.

Figure 1. Second Level (L2) Cache Implementation

# 1.1 Terminology

In this document, a '#' symbol after a signal name refers to an active low signal. This means that a signal is in the active state (based on the name of the signal) when driven to a low level. For example, when FLUSH# is low, a flush has been requested. When NMI is high, a nonmaskable interrupt has occurred. In the case of signals where the name does not imply an active state but describes part of a binary sequence (such as *address* or *data*), the '#' symbol implies that the signal is inverted. For example, D[3:0] = 'HLHL' refers to a hex 'A', and D[3:0]# = 'LHLH' also refers to a hex 'A' (H= High logic level, L= Low logic level).

The term "system bus" refers to the interface between the processor, system core logic (a.k.a. the AGPset components), and other bus agents. The system bus is a multiprocessing interface to processors, memory, and I/O. The term "cache bus" refers to the interface between the processor and the L2 cache components (TagRAM and BSRAMs). The cache bus does NOT connect to the system bus, and is not visible to other agents on the system bus.

# 1.1.1 S.E.C.C.2 and S.E.C.C. Packaged Processor Terminology

The following terms are used often in this document and are explained here for clarification:

- **Pentium III processor**—The entire product including internal components, substrate, cover and in S.E.C.C. packaged processors, an extended thermal plate.

- S.E.C.C.—The processor package technology called "Single Edge Contact Cartridge."

- **S.E.C.C.2**—The follow-on to S.E.C.C. processor package technology. This differs from its predecessor in that it has no extended thermal plate, thus reducing thermal resistance.

- **Processor substrate**—The FR4 board on which components are mounted inside the S.E.C.C. or S.E.C.C.2 packaged processor (with or without components attached).

- **Processor core**—The processor's execution engine.

- **Extended Thermal Plate**—This S.E.C.C. package feature is the surface used to attach a heatsink or other thermal solution to the processor.

- Cover—The plastic casing that covers the backside of the substrate.

- Latch arms—An S.E.C.C. package feature which can be used as a means for securing the processor in a retention mechanism.

- **OLGA** Organic Land Grid Array. This package technology permits attaching the heatsink directly to the die.

Additional terms referred to in this and other related documentation:

- SC242—The 242-contact slot connector (previously referred to as Slot 1 connector) that the S.E.C.C. and S.E.C.C.2 plug into, just as the Pentium<sup>®</sup> Pro processor uses Socket 8.

- **Retention mechanism**—A mechanical piece which holds the S.E.C.C. or S.E.C.C.2 packaged processor in the SC242 connector.

- **Heatsink support**—The support pieces that are mounted on the baseboard to provide added support for heatsinks.

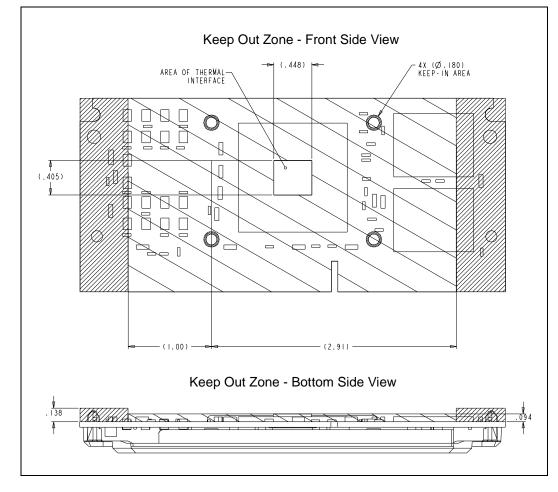

- **Keep-out zone**—The area on or near an S.E.C.C.2 packaged processor substrate that systems designs can not utilize.

- **Keep-in zone**—The area of the center of an S.E.C.C.2 packaged processor substrate that thermal solutions may utilize.

The L2 cache, TagRAM and BSRAM die, are industry designated names.

# 1.2 Related Documents

The reader of this specification should also be familiar with material and concepts in the documents listed in Table 1. These documents, and a complete list of Pentium III processor reference material, can be found on the Intel Developers' Insight web site located at http://developer.intel.com.

Table 1. Related Documents (Sheet 1 of 2)

| Document                                                                                                               | Intel Order Number |

|------------------------------------------------------------------------------------------------------------------------|--------------------|

| AP-485, Intel <sup>®</sup> Processor Identification and the CPUID Instruction                                          | 241618             |

| AP-585, Pentium <sup>®</sup> II Processor GTL+ Guidelines                                                              | 243330             |

| AP-588, Mechanical and Assembly Technology for S.E.C. Cartridge Processors                                             | 243333             |

| AP-589, Design for EMI                                                                                                 | 243334             |

| AP-826, Mechanical Assembly and Customer Manufacturing Technology for S.E.P. Packages                                  | 243748             |

| AP-902, S.E.C.C.2 Heatsink Installation and Removal                                                                    | 244454             |

| AP-903, Mechanical Assembly and Customer Manufacturing Technology for<br>Processor in S.E.C.C.2 Packages               | 244457             |

| AP-905, Pentium <sup>®</sup> III Processor Thermal Design Guidelines                                                   | 245087             |

| AP-906, 100 MHz AGTL+ Layout Guidelines for the Pentium <sup>®</sup> III Processor and Intel <sup>®</sup> 440BX AGPset | 245086             |

| AP-907, Pentium <sup>®</sup> III Processor Power Distribution Guidelines                                               | 245085             |

| Intel <sup>®</sup> Processor Serial Number                                                                             | 245119             |

| CK97 Clock Synthesizer Design Guidelines                                                                               | 243867             |

† These models are available in Viewlogic\* XTK\* model format (formerly known as QUAD format) at the Intel Developer's Website at http://developer.intel.com.

| Document                                                            | Intel Order Number |

|---------------------------------------------------------------------|--------------------|

| Intel <sup>®</sup> Architecture Software Developer's Manual         | 243193             |

| Volume I: Basic Architecture                                        | 243190             |

| Volume II: Instruction Set Reference                                | 243191             |

| Volume III: System Programming Guide                                | 243192             |

| P6 Family of Processors Hardware Developer's Manual                 | 244001             |

| Pentium <sup>®</sup> II Processor at 350, 400 and 450 MHz datasheet | 243657             |

| Pentium <sup>®</sup> II Processor Developer's Manual                | 243502             |

| Pentium <sup>®</sup> III Processor I/O Buffer Models                | Ť                  |

| Pentium <sup>®</sup> III Processor Specification Update             | 244453             |

| SC242 Bus Termination Card Design Guidelines                        | 243409             |

| Slot 1 Connector Specification                                      | 243397             |

| VRM 8.2 DC-DC Converter Design Guidelines                           | 243773             |

#### Table 1. Related Documents (Sheet 2 of 2)

† These models are available in Viewlogic\* XTK\* model format (formerly known as QUAD format) at the Intel Developer's Website at http://developer.intel.com.

# 2.0 Electrical Specifications

# 2.1 Processor System Bus and VREF

Most Pentium<sup>®</sup> III processor signals use a variation of the low voltage Gunning Transceiver Logic (GTL) signaling technology.

The Pentium Pro processor system bus specification is similar to the GTL specification, but was enhanced to provide larger noise margins and reduced ringing. The improvements are accomplished by increasing the termination voltage level and controlling the edge rates. This specification is different from the GTL specification, and is referred to as GTL+. For more information on GTL+ specifications, see the GTL+ buffer specification in the *Pentium*<sup>®</sup> *II Processor Developer's Manual* (Order Number 243502).

The Pentium III processor varies from the Pentium Pro processor in its output buffer implementation. The buffers that drive the system bus signals on the Pentium III processor are actively driven to  $VCC_{CORE}$  for one clock cycle after the low to high transition to improve rise times. These signals should still be considered open-drain and require termination to a supply that provides the high signal level. Because this specification is different from the standard GTL+ specification, it is referred to as AGTL+ in this and other documentation. AGTL+ logic and GTL+ logic are compatible with each other and may both be used on the same system bus. For more information on AGTL+ routing, see AP-906, *100 MHz AGTL+ Layout Guidelines for the Pentium*<sup>®</sup> III processor and Intel<sup>®</sup> 440BX AGPset (Order Number 245086).

AGTL+ inputs use differential receivers which require a reference signal ( $V_{REF}$ ).  $V_{REF}$  is used by the receivers to determine if a signal is a logical 0 or a logical 1, and is generated on the S.E.C.C. and S.E.C.C.2 packages for the processor core. Local  $V_{REF}$  copies should be generated on the baseboard for all other devices on the AGTL+ system bus. Termination (usually a resistor at each end of the

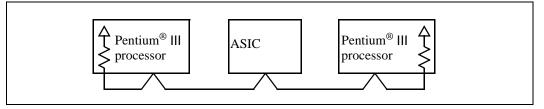

signal trace) is used to pull the bus up to the high voltage level and to control reflections on the transmission line. The processor contains termination resistors that provide termination for one end of the Pentium III processor system bus. These specifications assume another resistor at the end of each signal trace to ensure adequate signal quality for the AGTL+ signals; see Table 8 for the bus termination voltage specifications for AGTL+. Refer to the *Pentium<sup>®</sup> II Processor Developer's Manual* (Order Number 243502) for the GTL+ bus specification. Solutions exist for single-ended termination as well, though this implementation changes system design. Figure 2 is a schematic representation of AGTL+ bus topology with Pentium III processor.

The AGTL+ bus depends on incident wave switching. Therefore timing calculations for AGTL+ signals are based on flight time as opposed to capacitive deratings. Analog signal simulation of the Pentium III processor system bus including trace lengths is highly recommended when designing a system with a heavily loaded AGTL+ bus, especially for systems using a single set of termination resistors (i.e., those on the processor substrate). Such designs will not match the solution space allowed for by installation of termination resistors on the baseboard. See Intel's Developers' Website (http://developer.intel.com) to download the *Pentium*<sup>®</sup> *III Processor I/O Buffer Models, Viewlogic\* XTK\* model format* (formerly known as QUAD format).

# Figure 2. AGTL+ Bus Topology

# 2.2 Clock Control and Low Power States

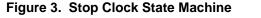

Pentium III processor allow the use of AutoHALT, Stop-Grant, Sleep, and Deep Sleep states to reduce power consumption by stopping the clock to internal sections of the processor, depending on each particular state. See Figure 3 for a visual representation of the Pentium III processor low power states.

For the processor to fully realize the low current consumption of the Stop-Grant, Sleep, and Deep Sleep states, a Model Specific Register (MSR) bit must be set. For the MSR at 02AH (Hex), bit 26 must be set to a '1' (this is the power on default setting) for the processor to stop all internal clocks during these modes. For more information, see the *Intel Architecture Software Developer's Manual, Volume 3: System Programming Guide* (Order Number 243192).

Due to the inability of processors to recognize bus transactions during the Sleep and Deep Sleep states, 2-way MP systems are not allowed to have one processor in Sleep/Deep Sleep state and the other processor in Normal or Stop-Grant state simultaneously.

# 2.2.1 Normal State—State 1

This is the normal operating state for the processor.

# 2.2.2 AutoHALT Powerdown State—State 2

AutoHALT is a low power state entered when the processor executes the HALT instruction. The processor will transition to the Normal state upon the occurrence of SMI#, BINIT#, INIT#, or LINT[1:0] (NMI, INTR). RESET# will cause the processor to immediately initialize itself.

The return from a System Management Interrupt (SMI) handler can be to either Normal Mode or the AutoHALT Power Down state. See the *Intel Architecture Software Developer's Manual, Volume III: System Programmer's Guide* (Order Number 243192) for more information.

FLUSH# will be serviced during the AutoHALT state, and the processor will return to the AutoHALT state.

The system can generate a STPCLK# while the processor is in the AutoHALT Power Down state. When the system deasserts the STPCLK# interrupt, the processor will return execution to the HALT state.

# 2.2.3 Stop-Grant State—State 3

The Stop-Grant state on the processor is entered when the STPCLK# signal is asserted.

Since the AGTL+ signal pins receive power from the system bus, these pins should not be driven (allowing the level to return to  $V_{TT}$ ) for minimum power drawn by the termination resistors in this state. In addition, all other input pins on the system bus should be driven to the inactive state.

BINIT# and FLUSH# will not be serviced during Stop-Grant state.

RESET# will cause the processor to immediately initialize itself, but the processor will stay in Stop-Grant state. A transition back to the Normal state will occur with the deassertion of the STPCLK# signal.

A transition to the HALT/Grant Snoop state will occur when the processor detects a snoop on the system bus (see Section 2.2.4). A transition to the Sleep state (see Section 2.2.5) will occur with the assertion of the SLP# signal.

While in Stop-Grant State, SMI#, INIT#, and LINT[1:0] will be latched by the processor, and only serviced when the processor returns to the Normal state. Only one occurrence of each event will be recognized and serviced upon return to the Normal state.

# 2.2.4 HALT/Grant Snoop State—State 4

The processor will respond to snoop transactions on the Pentium III processor system bus while in Stop-Grant state or in AutoHALT Power Down state. During a snoop transaction, the processor enters the HALT/Grant Snoop state. The processor will stay in this state until the snoop on the Pentium III processor system bus has been serviced (whether by the processor or another agent on the Pentium III processor system bus). After the snoop is serviced, the processor will return to the Stop-Grant state or AutoHALT Power Down state, as appropriate.

# 2.2.5 Sleep State—State 5

The Sleep state is a very low power state in which the processor maintains its context, maintains the phase-locked loop (PLL), and has stopped all internal clocks. The Sleep state can only be entered from the Stop-Grant state. Once in the Stop-Grant state, the SLP# pin can be asserted, causing the processor to enter the Sleep state. The SLP# pin is not recognized in the Normal or AutoHALT states.

Snoop events that occur while in Sleep State or during a transition into or out of Sleep state will cause unpredictable behavior.

In the Sleep state, the processor is incapable of responding to snoop transactions or latching interrupt signals. No transitions or assertions of signals (with the exception of SLP# or RESET#) are allowed on the system bus while the processor is in Sleep state. Any transition on an input signal before the processor has returned to Stop-Grant state will result in unpredictable behavior.

If RESET# is driven active while the processor is in the Sleep state, and held active as specified in the RESET# pin specification, then the processor will reset itself, ignoring the transition through Stop-Grant State. If RESET# is driven active while the processor is in the Sleep State, the SLP# and STPCLK# signals should be deasserted immediately after RESET# is asserted to ensure the processor correctly executes the Reset sequence.

While in the Sleep state, the processor is capable of entering its lowest power state, the Deep Sleep state, by stopping the BCLK input (see Section 2.2.6). Once in the Sleep or Deep Sleep states, the SLP# pin can be deasserted if another asynchronous system bus event occurs. The SLP# pin has a minimum assertion of one BCLK period.

# 2.2.6 Deep Sleep State—State 6

The Deep Sleep state is the lowest power state the processor can enter while maintaining context. The Deep Sleep state is entered by stopping the BCLK input (after the Sleep state was entered from the assertion of the SLP# pin). The processor is in Deep Sleep state immediately after BLCK is stopped. It is recommended that the BLCK input be held low during the Deep Sleep State. Stopping of the BCLK input lowers the overall current consumption to leakage levels.

To re-enter the Sleep state, the BLCK input must be restarted. A period of 1 ms (to allow for PLL stabilization) must occur before the processor can be considered to be in the Sleep state. Once in the Sleep state, the SLP# pin can be deasserted to re-enter the Stop-Grant state.

While in Deep Sleep state, the processor is incapable of responding to snoop transactions or latching interrupt signals. No transitions or assertions of signals are allowed on the system bus while the processor is in Deep Sleep state. Any transition on an input signal before the processor has returned to Stop-Grant state will result in unpredictable behavior.

# 2.2.7 Clock Control

The processor provides the clock signal to the L2 cache. During AutoHALT Power Down and Stop-Grant states, the processor will process a system bus snoop. The processor will not stop the clock to the L2 cache during AutoHALT Power Down or Stop-Grant states. Entrance into the Halt/Grant Snoop state will allow the L2 cache to be snooped, similar to the Normal state.

# intel

When the processor is in Sleep and Deep Sleep states, it will not respond to interrupts or snoop transactions. During the Sleep state, the clock to the L2 cache is not stopped. During the Deep Sleep state, the clock to the L2 cache is stopped. The clock to the L2 cache will be restarted only after the internal clocking mechanism for the processor is stable (i.e., the processor has re-entered Sleep state).

PICCLK should not be removed during the AutoHALT Power Down or Stop-Grant states. PICCLK can be removed during the Sleep or Deep Sleep states. When transitioning from the Deep Sleep state to the Sleep state, PICCLK must be restarted with BCLK.

# 2.3 Power and Ground Pins

The operating voltage of the processor die and of the L2 cache die differ from each other. There are two groups of power inputs on the Pentium III processor package to support this voltage difference between the components in the package. There are also five pins defined on the package for voltage identification (VID). These pins specify the voltage required by the processor core. These have been added to cleanly support voltage specification variations on current and future Pentium III processor.

For clean on-chip power distribution, Pentium III processor have 27 V<sub>CC</sub> (power) and 30 V<sub>SS</sub> (ground) inputs. The 27 V<sub>CC</sub> pins are further divided to provide the different voltage levels to the components. V<sub>CC<sub>CORE</sub> inputs for the processor core and some L2 cache components account for 19 of the V<sub>CC</sub> pins, while 4 V<sub>TT</sub> inputs (1.5 V) are used to provide an AGTL+ termination voltage to the processor and 3 V<sub>CC<sub>L2</sub></sub> inputs (3.3 V) are for use by the L2 cache TagRAM and BSRAMs. One V<sub>CC<sub>5</sub></sub> pin is provided for use by test equipment and tools. V<sub>CC<sub>5</sub></sub>, V<sub>CC<sub>L2</sub>, and V<sub>CC<sub>CORE</sub> must remain electrically separated from each other. On the circuit board, all V<sub>CC<sub>CORE</sub> pins must be connected to a voltage island and all V<sub>CC<sub>L2</sub></sub> pins must be connected to a separate voltage island (an island is a portion of a power plane that has been divided, or an entire plane). Similarly, all V<sub>ss</sub> pins must be connected to a system ground plane.</sub></sub></sub></sub>

# 2.4 Decoupling Guidelines

Due to the large number of transistors and high internal clock speeds, the processor is capable of generating large average current swings between low and full power states. This causes voltages on power planes to sag below their nominal values if bulk decoupling is not adequate. Care must be taken in the board design to ensure that the voltage provided to the processor remains within the specifications listed in Table 5. Failure to do so can result in timing violations or a reduced lifetime of the component.

# 2.4.1 Processor Vcc<sub>core</sub> Decoupling

Regulator solutions need to provide bulk capacitance with a low Effective Series Resistance (ESR) and keep an interconnect resistance from the regulator (or VRM pins) to the SC242 connector of less than 0.3 m $\Omega$ . This can be accomplished by keeping a maximum distance of 1.0 inches between the regulator output and SC242 connector. The recommended V<sub>CC<sub>CORE</sub> interconnect is a 2.0 inch wide by 1.0 inch long (maximum distance between the SC242 connector and the VRM connector) plane segment with a 1-ounce plating. Bulk decoupling for the large current swings when the part is powering on, or entering/exiting low power states, is provided on the voltage regulation module (VRM). If using Intel's enabled VRM solutions see developer.intel.com for the specification and a</sub>

list of qualified vendors. The  $V_{CC_{CORE}}$  input should be capable of delivering a recommended minimum  $dI_{CC_{CORE}}/dt$  (defined in Table 5) while maintaining the required tolerances (also defined in Table 5).

# 2.4.2 Processor System Bus AGTL+ Decoupling

The Pentium III processor contains high frequency decoupling capacitance on the processor substrate; bulk decoupling must be provided for by the system baseboard for proper AGTL+ bus operation. See AP-906, *100 MHz AGTL+ Layout Guidelines for the Pentium*<sup>®</sup> *III Processor and Intel*<sup>®</sup> 440BX AGPset (Order Number 245086), AP-907, *Pentium*<sup>®</sup> *III Processor Power Distribution Guidelines* (Order Number 245085), and the GTL+ buffer specification in the *Pentium*<sup>®</sup> *II Processor Developer's Manual* (Order Number 243502) for more information.

# 2.5 Processor System Bus Clock and Processor Clocking

The BCLK input directly controls the operating speed of the Pentium III processor system bus interface. All Pentium III processor system bus timing parameters are specified with respect to the rising edge of the BCLK input. See the *P6 Family of Processors Hardware Developer's Manual* (Order Number 244001) for further details.

# 2.5.1 Mixing Processors of Different Frequencies

In 2-way MP systems, mixing processors of different internal clock frequencies is not supported and has not been validated by Intel. Pentium III processor do not support a variable multiplier ratio; therefore, adjusting the ratio setting to a common clock frequency is not valid. However, mixing processors of the same frequency but of different steppings is supported.

# 2.6 Voltage Identification

There are five voltage identification pins on the SC242 connector. These pins can be used to support automatic selection of power supply voltages. These pins are not signals, but are either an open circuit or a short circuit to  $V_{ss}$  on the processor. The combination of opens and shorts defines the voltage required by the processor core. The VID pins are needed to cleanly support voltage specification variations on current and future Pentium III processor. VID[4:0] are defined in Table 2. A '1' in this table refers to an open pin and a '0' refers to a short to ground. The power supply must supply the voltage that is requested or disable itself.

To ensure a system is ready for current and future Pentium III processor, the range of values in **bold** in Table 2 should be supported. A smaller range will risk the ability of the system to migrate to a higher performance Pentium III processor and/or maintain compatibility with current Pentium III processor.

|      |      | F             | Processor Pins | 1    |                                  |

|------|------|---------------|----------------|------|----------------------------------|

| VID4 | VID3 | VID2          | VID1           | VID0 | Vcc <sub>core</sub> <sup>2</sup> |

|      |      | 01111 - 00110 |                | 1    | Reserved                         |

| 0    | 0    | 1             | 0              | 1    | 1.80                             |

| 0    | 0    | 1             | 0              | 0    | 1.85                             |

| 0    | 0    | 0             | 1              | 1    | 1.90                             |

| 0    | 0    | 0             | 1              | 0    | 1.95                             |

| 0    | 0    | 0             | 0              | 1    | 2.00                             |

| 0    | 0    | 0             | 0              | 0    | 2.05                             |

| 1    | 1    | 1             | 1              | 1    | No Core                          |

| 1    | 1    | 1             | 1              | 0    | 2.1                              |

| 1    | 1    | 1             | 0              | 1    | 2.2                              |

| 1    | 1    | 1             | 0              | 0    | 2.3                              |

| 1    | 1    | 0             | 1              | 1    | 2.4                              |

| 1    | 1    | 0             | 1              | 0    | 2.5                              |

| 1    | 1    | 0             | 0              | 1    | 2.6                              |

| 1    | 1    | 0             | 0              | 0    | 2.7                              |

| 1    | 0    | 1             | 1              | 1    | 2.8                              |

| 1    | 0    | 1             | 1              | 0    | 2.9                              |

| 1    | 0    | 1             | 0              | 1    | 3.0                              |

| 1    | 0    | 1             | 0              | 0    | 3.1                              |

| 1    | 0    | 0             | 1              | 1    | 3.2                              |

| 1    | 0    | 0             | 1              | 0    | 3.3                              |

| 1    | 0    | 0             | 0              | 1    | 3.4                              |

| 1    | 0    | 0             | 0              | 0    | 3.5                              |

### Table 2. Voltage Identification Definition

#### NOTES:

1. 0 = Processor pin connected to Vss.

1 = Open on processor; may be pulled up to TTL VIH on baseboard.

2. To ensure a system is ready for the Pentium III processor, the values in **BOLD** in Table 2 should be supported.

Note that the '11111' (all opens) ID can be used to detect the absence of a processor core in a given connector as long as the power supply used does not affect these lines. Detection logic and pull-ups should not affect VID inputs at the power source (see Section 7.0).

The VID pins should be pulled up to a TTL-compatible level with external resistors to the power source of the regulator only if required by the regulator or external logic monitoring the VID[4:0] signals. The power source chosen must be guaranteed to be stable whenever the supply to the voltage regulator is stable. This will prevent the possibility of the processor supply going above the specified  $V_{CC_{CORE}}$  in the event of a failure in the supply for the VID lines. In the case of a DC-to-DC converter, this can be accomplished by using the input voltage to the converter for the VID line pull-ups. A resistor of greater than or equal to  $10 \text{ k}\Omega$  may be used to connect the VID signals to the converter input. Note that no changes have been made to the physical connector between the Intelenabled VRM 8.1 and VRM 8.2 specifications, though pin definitions have changed.

# 2.7 **Processor System Bus Unused Pins**

All RESERVED pins must remain unconnected. Connection of these pins to  $V_{CC_{CORE}}$ ,  $V_{CC_{L2}}$ ,  $V_{ss}$ , or to any other signal (including each other) can result in component malfunction or incompatibility with future Pentium III processor. See Section 5.5 for a pin listing of the processor and the location of each RESERVED pin.

All TESTHI pins must be connected to 2.5 V via a 100 k $\Omega$  pull-up resistor.

PICCLK must be driven with a valid clock input and the PICD[1:0] lines must be pulled-up to 2.5 V even when the APIC will not be used. A separate pull-up resistor must be provided for each APIC data line.

For reliable operation, always connect unused inputs or bidirectional signals to an appropriate signal level. Unused AGTL+ inputs should be left as no connects; AGTL+ termination is provided on the processor. Unused active low CMOS inputs should be connected through a resistor to 2.5 V. Unused active high inputs should be connected through a resistor to ground ( $V_{ss}$ ). Unused outputs can be left unconnected. A resistor must be used when tying bidirectional signals to power or ground. When tying any signal to power or ground, a resistor will also allow for system testability. For unused pins, it is suggested that ~10 k $\Omega$  resistors be used for pull-ups (except for PICD[1:0] discussed above), and ~1 k $\Omega$  resistors be used as pull-downs.

# 2.8 Processor System Bus Signal Groups

In order to simplify the following discussion, the Pentium III processor system bus signals have been combined into groups by buffer type. All Pentium III processor system bus outputs are open drain and require a high-level source provided externally by the termination or pull-up resistor. However, the Pentium III processor includes on cartridge termination.

AGTL+ input signals have differential input buffers, which use V<sub>REF</sub> as a reference signal. AGTL+ output signals require termination to 1.5 V. In this document, the term "AGTL+ Input" refers to the AGTL+ input group as well as the AGTL+ I/O group when receiving. Similarly, "AGTL+ Output" refers to the AGTL+ output group as well as the AGTL+ I/O group when driving.

EMI pins may be connected to baseboard ground and/or to chassis ground through zero ohm  $(0\Omega)$  resistors. The  $0\Omega$  resistors should be placed in close proximity to the SC242 connector. The path to chassis ground should be short in length and have a low impedance.

The CMOS, Clock, APIC, and TAP inputs can each be driven from ground to 2.5 V. The CMOS, APIC, and TAP outputs are open drain and should be pulled high to 2.5 V. This ensures not only correct operation for current Pentium III processor, but compatibility with future Pentium III processor as well.

The groups and the signals contained within each group are shown in Table 3. Refer to Section 7.0 for a description of these signals.

# Table 3. System Bus Signal Groups

| Group Name               | Signals                                                                                                                                                                 |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AGTL+ Input              | BPRI#, BR1#, DEFER#, RESET#, RS[2:0]#, RSP#, TRDY#                                                                                                                      |  |  |  |

| AGTL+ Output             | RDY#                                                                                                                                                                    |  |  |  |

| AGTL+ I/O                | A[35:3]#, ADS#, AERR#, AP[1:0]#, BERR#, BINIT#, BNR#, BP[3:2]#, BPM[1:0]#,<br>BR0# <sup>1</sup> , D[63:0]#, DBSY#, DEP[7:0]#, DRDY#, HIT#, HITM#, LOCK#, REQ[4:0]#, RP# |  |  |  |

| CMOS Input⁵              | A20M#, FLUSH#, IGNNE#, INIT#, LINT0/INTR, LINT1/NMI, PREQ#, PWRGOOD <sup>2</sup> , SMI#, SLP# <sup>3</sup> , STPCLK#                                                    |  |  |  |

| CMOS Output⁵             | FERR#, IERR#, THERMTRIP# <sup>4</sup>                                                                                                                                   |  |  |  |

| System Bus Clock         | BCLK                                                                                                                                                                    |  |  |  |

| APIC Clock               | PICCLK                                                                                                                                                                  |  |  |  |

| APIC I/O <sup>5</sup>    | PICD[1:0]                                                                                                                                                               |  |  |  |

| TAP Input⁵               | TCK, TDI, TMS, TRST#                                                                                                                                                    |  |  |  |

| TAP Output⁵              | TDO                                                                                                                                                                     |  |  |  |

| Power/Other <sup>6</sup> | Vcc <sub>core</sub> , Vcc <sub>12</sub> , Vcc <sub>5</sub> , VID[4:0], VTT, Vss, SLOTOCC#, THERMDP, THERMDN, BSEL[1:0], EMI, TESTHI, Reserved                           |  |  |  |

#### NOTES:

- 1. The BR0# pin is the only BREQ# signal that is bidirectional. The internal BREQ# signals are mapped onto BR# pins after the agent ID is determined. See Section 7.0 for more information.

- 2. See Section 7.0 for information on the PWRGOOD signal.

- 3. See Section 7.0 for information on the SLP# signal.

- 4. See Section 7.0 for information on the THERMTRIP# signal.

- 5. These signals are specified for 2.5 V operation.

- 6.  $\mathsf{V}_{\mathsf{CC}_{\mathsf{CORE}}}$  is the power supply for the processor core.

- $V_{CC_{L2}}$  is the power supply for the L2 cache component core logic.

- VID[4:0] is described in Section 2.6.

$\ensuremath{\mathsf{V}}\xspace\pi$  is used to terminate the system bus and generate  $\ensuremath{\mathsf{VREF}}\xspace$  on the processor substrate.

Vss is system ground.

TESTHI should be connected to 2.5 V with a 100 k $\Omega$  resistor.

$Vcc_5$  is not connected to the Pentium III processor core. This supply is used for the test equipment and tools. SLOTOCC# is described in Section 7.0.

- BSEL[1:0] is described in Section 7.0.

- EMI pins are described in Section 7.0.

THERMDP, THERMDN are described in Section 7.0.

# 2.8.1 Asynchronous vs. Synchronous for System Bus Signals

All AGTL+ signals are synchronous to BCLK. All of the CMOS, Clock, APIC, and TAP signals can be applied asynchronously to BCLK.

All APIC signals are synchronous to PICCLK. All TAP signals are synchronous to TCK.

BSEL0 signal (also known as 100/66#) is used to select the system bus frequency for the Pentium III processor(s). A logic low will select a 66 MHz host bus frequency and a logic high will select a 100 MHz host bus frequency. The frequency is determined by the processor(s). All system bus agents must operate at the same frequency in a 2-way MP Pentium III processor configuration. In a 2-way MP system design, the BSEL0 signal must be connected to the BSEL0 pins of both Pentium III processor. The Pentium III processor operates at a 100 MHz system bus frequency; 66 MHz system bus operation is not supported.

On baseboards which support operation at either 66 or 100 MHz, this signal must be pulled up to 3.3V with a 200 $\Omega$  resistor (as shown in Figure 4 below) and provided as a frequency selection signal to the clock driver/synthesizer. Refer to the CK97 Clock Synthesizer Design Guidelines (Order Number 243867) for more details. This signal can also be incorporated into RESET# logic on the baseboard if only 100 MHz operation is supported (thus forcing the RESET# signal to remain active as long as the BSEL0 signal is low).

# 2.9 Test Access Port (TAP) Connection

Due to the voltage levels supported by other components in the Test Access Port (TAP) logic, it is recommended that the Pentium III processor be first in the TAP chain and followed by any other components within the system. A translation buffer should be used to connect to the rest of the chain unless one of the other components is capable of accepting a 2.5 V input. Similar considerations must be made for TCK, TMS, and TRST#. Two copies of each signal may be required with each driving a different voltage level.

The Debug Port should be placed at the start and end of the TAP chain with the TDI of the first component coming from the Debug Port and the TDO from the last component going to the Debug Port. In a 2-way MP system, be cautious when including an empty SC242 connector in the scan chain. All connectors in the scan chain must have a processor installed to complete the chain or the system must support a method to bypass the empty connectors; SC242 terminator substrates should not connect TDI to TDO in order to avoid placing the TDO pull-up resistors in parallel. See *Slot 1 Bus Terminator Card Design Guidelines* (Order Number 243409) for more details.

# 2.10 Maximum Ratings

Table 4 contains Pentium III processor stress ratings only. Functional operation at the absolute maximum and minimum is not implied nor guaranteed. The processor should not receive a clock while subjected to these conditions. Functional operating conditions are given in the AC and DC tables in Section 2.11 and Section 2.13. Extended exposure to the maximum ratings may affect device reliability. Furthermore, although the processor contains protective circuitry to resist damage from static electric discharge, one should always take precautions to avoid high static voltages or electric fields.

# intel®

| Symbol                   | Parameter                                         | Min  | Мах                       | Unit                       | Notes |

|--------------------------|---------------------------------------------------|------|---------------------------|----------------------------|-------|

| TSTORAGE                 | Processor storage temperature                     | -40  | 85                        | °C                         |       |

| VCC <sub>(AII)</sub>     | Any processor supply voltage with respect to Vss  | -0.5 | Operating voltage + 1.0   | V                          | 1, 2  |

| Vin <sub>AGTL</sub>      | AGTL+ buffer DC input voltage with respect to Vss | -0.3 | VCC <sub>CORE</sub> + 0.7 | V                          |       |

| Vin <sub>CMOS</sub>      | CMOS buffer DC input voltage with respect to Vss  | -0.3 | 3.3                       | V                          | 3     |

| Ivid                     | Max VID pin current                               |      | 5                         | mA                         |       |

| ISLOTOCC                 | Max SLOTOCC# pin<br>current                       |      | 5                         | mA                         |       |

| Mech Max<br>Latch Arms   | Mechanical integrity of latch arms                |      | 50                        | Cycles                     | 4, 7  |

| Mech Max<br>Edge Fingers | Mechanical integrity of processor edge fingers    |      | 50                        | Insertions/<br>Extractions | 5, 6  |

# Table 4. Absolute Maximum Ratings

#### NOTES:

- 1. Operating voltage is the voltage to which the component is designed to operate. See Table 5.

- 2. This rating applies to the Vcc<sub>coRE</sub>, Vcc<sub>L2</sub>, Vcc<sub>5</sub>, and any input (except as noted below) to the processor.

- 3. Parameter applies to CMOS, APIC, and TAP bus signal groups only.

- 4. The mechanical integrity of the latch arms is specified to last a maximum of 50 cycles.

- 5. The electrical and mechanical integrity of the processor edge fingers are specified to last for 50 insertion/extraction cycles.

- 6. While insertion/extraction cycling above 50 insertions will cause an increase in the contact resistance (above 0.1Ω) and a degradation in the material integrity of the edge finger gold plating, it is possible to have processor functionality above the specified limit. The actual number of insertions before processor failure will vary based upon system configuration and environmental conditions.

- 7. This specification only applies to S.E.C.C. packaged processors.

# 2.11 Processor DC Specifications

The processor DC specifications in this section are defined at the Pentium III processor edge fingers and at the SC242 connector pins. See Section 7.0 for the processor edge finger signal definitions and Section 5.0 for the signal listing.

Most of the signals on the Pentium III processor system bus are in the AGTL+ signal group. These signals are specified to be terminated to 1.5 V. The DC specifications for these signals are listed in Table 6.

To allow connection with other devices, the Clock, CMOS, APIC, and TAP signals are designed to interface at non-AGTL+ levels. The DC specifications for these pins are listed in Table 7.

Table 5 through Table 8 list the DC specifications for Pentium III processor. Specifications are valid only while meeting specifications for case temperature, clock frequency, and input voltages. Care should be taken to read all notes associated with each parameter.

| Symbol                                         | Parameter                                                              | Core<br>Freq                  | Min    | Тур  | Max                  | Unit        | Notes <sup>1</sup>                           |

|------------------------------------------------|------------------------------------------------------------------------|-------------------------------|--------|------|----------------------|-------------|----------------------------------------------|

| VCC <sub>CORE</sub>                            | Vcc for processor core                                                 |                               |        | 2.00 |                      | V           | 2, 3, 4, 5                                   |

| VCC <sub>L2</sub>                              | Vcc for second level cache                                             |                               | 3.135  | 3.3  | 3.465                | V           | 3.3 V ±5% <sup>9</sup>                       |

| V <sub>TT</sub>                                | AGTL+ bus termination voltage                                          |                               | 1.365  | 1.50 | 1.635                | V           | 1.5 ±9% <sup>6</sup>                         |

| Baseboard<br>Tolerance,<br>Static              | Processor core voltage<br>static tolerance level at<br>SC242 pins      |                               | -0.070 |      | 0.070                | V           | 2, 7                                         |

| Baseboard<br>Tolerance,<br>Transient           | Processor core voltage<br>transient tolerance<br>level at SC242 pins   |                               | -0.140 |      | 0.140                | V           | 2, 7                                         |

| Vcc <sub>core</sub><br>Tolerance,<br>Static    | Processor core voltage<br>static tolerance level at<br>edge fingers    |                               | -0.085 |      | 0.085                | V           | 2, 8                                         |

| Vcc <sub>core</sub><br>Tolerance,<br>Transient | Processor core voltage<br>transient tolerance<br>level at edge fingers |                               | -0.170 |      | 0.170                | V           | 2, 8                                         |

| ICC <sub>CORE</sub>                            | Icc for processor core                                                 | 450 MHz<br>500 MHz<br>550 MHz |        |      | 14.5<br>16.1<br>17.0 | A<br>A<br>A | 2, 3, 10, 11<br>2, 3, 10, 11<br>2, 3, 10, 11 |

| ICC <sub>L2</sub>                              | Icc for second level cache                                             | 450 MHz<br>500 MHz<br>550 MHz |        |      | 1.08<br>1.21<br>1.33 | A<br>A<br>A | 2, 9, 10<br>2, 9, 10<br>2, 9, 10<br>2, 9, 10 |

| Ινττ                                           | Termination voltage supply current                                     |                               |        |      | 2.7                  | А           | 12                                           |

| ISGnt                                          | Icc Stop-Grant for<br>processor core                                   | 450 MHz<br>500 MHz<br>550 MHz |        |      | 1.2<br>1.4<br>1.54   | A<br>A<br>A | 2, 10, 13<br>2, 10, 13<br>2, 10, 13          |

| ISG <sub>ntL2</sub>                            | Icc Stop-Grant for second level cache                                  |                               |        |      | 0.1                  | А           | 2, 9, 10                                     |

| ISLP                                           | Icc Sleep for processor core                                           | 450 MHz<br>500 MHz<br>550 MHz |        |      | 0.80<br>0.90<br>1.00 | A<br>A<br>A | 2, 10<br>2, 10<br>2, 10                      |

| ISL <sub>PL2</sub>                             | Icc Sleep for second level cache                                       |                               |        |      | 0.1                  | А           | 2, 9, 10                                     |

| Idslp                                          | Icc Deep Sleep for<br>processor core                                   | 450 MHz<br>500 MHz<br>550 MHz |        |      | 0.50<br>0.50<br>1.00 | A<br>A<br>A | 2, 9, 10                                     |

| IDSL <sub>PL2</sub>                            | Icc Deep Sleep for second level cache                                  |                               |        |      | 0.1                  | А           | 2, 9, 10                                     |

| dIcc <sub>core</sub> /dt                       | Power supply current slew rate                                         |                               |        |      | 20                   | A/µs        | 2, 14, 15, 16                                |

| dIcc <sub>∟2</sub> /dt                         | L2 cache power supply current slew rate                                |                               |        |      | 1                    | A/µs        | 14, 15, 16                                   |

# Table 5. Voltage and Current Specifications (Sheet 1 of 2)

| Table 5. | Voltage and Cu | rrent Specifications | (Sheet 2 of 2) |

|----------|----------------|----------------------|----------------|

|----------|----------------|----------------------|----------------|

| Symbol                  | Parameter                     | Core<br>Freq | Min  | Тур  | Мах  | Unit | Notes <sup>1</sup>               |

|-------------------------|-------------------------------|--------------|------|------|------|------|----------------------------------|

| dlcc <sub>vtt</sub> /dt | Termination current slew rate |              |      |      | 8    | A/µs | See<br>Table 8 <sup>14, 15</sup> |

| VCC5                    | 5 V supply voltage            |              | 4.75 | 5.00 | 5.25 | V    | 5 V ±5% <sup>16, 17</sup>        |

| ICC5                    | Icc for 5 V supply voltage    |              |      | 1.0  |      | А    | 17                               |

#### NOTES:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

- This specification applies to Pentium III processors. For baseboard compatibility information on Pentium II processors, refer to the *Pentium<sup>®</sup> II Processor at 350, 400 and 450 MHz* datasheet (Order Number 243657).

- Vcc<sub>CORE</sub> and Icc<sub>CORE</sub> supply the processor core and the TagRAM and BSRAM I/O buffers.

A variable voltage source should exist on all systems in the event that a different voltage is required. See Section 2.6 and Table 1 for more information.

- 5. Use the Typical Voltage specification with the Tolerance specifications to provide correct voltage regulation to the processor.

- V<sub>TT</sub> must be held to 1.5 V ±9%. It is recommended that V<sub>TT</sub> be held to 1.5 V ±3% while the Pentium III processor system bus is idle. This is measured at the processor edge fingers.

- 7. These are the tolerance requirements, across a 20 MHz bandwidth, at the SC242 connector pin on the bottom side of the baseboard. The requirements at the SC242 connector pins account for voltage drops (and impedance discontinuities) across the connector, processor edge fingers, and to the processor core. Vcc<sub>CORE</sub> must return to within the static voltage specification within 100 μs after a transient event; see the VRM 8.2 DC-DC Converter Design Guidelines (Order Number 243773) for further details.

- 8. These are the tolerance requirements, across a 20 MHz bandwidth, at the processor edge fingers. The requirements at the processor edge fingers account for voltage drops (and impedance discontinuities) at the processor edge fingers and to the processor core. Vcc<sub>CORE</sub> must return to within the static voltage specification within 100 μs after a transient event.

- V<sub>CCL2</sub> and I<sub>CCL2</sub> supply the second level cache. Unless otherwise noted, this specification applies to all Pentium III processor cache sizes. Systems should be designed for these specifications, even if a smaller cache size is used.

- 10.Max lcc measurements are measured at Vcc max voltage, 95 °C ±2 °C, under maximum signal loading conditions. The Max lcc currents specified do not occur simultaneously under the stress measurement condition.

- 11. Voltage regulators may be designed with a minimum equivalent internal resistance to ensure that the output voltage, at maximum current output, is no greater than the nominal (i.e., typical) voltage level of Vcc<sub>CORE</sub> (Vcc<sub>CORE\_TYP</sub>). In this case, the maximum current level for the regulator, Icc<sub>CORE\_REG</sub>, can be reduced from the specified maximum current Icc<sub>CORE\_MAX</sub> and is calculated by the equation:

Icc<sub>CORE\_REG</sub> = Icc<sub>CORE\_MAX</sub> × Vcc<sub>CORE\_TYP</sub> / (Vcc<sub>CORE\_TYP</sub> + Vcc<sub>CORE</sub> Tolerance, Transient)

- 12. The current specified is the current required for a single Pentium III processor. A similar amount of current is drawn through the termination resistors on the opposite end of the AGTL+ bus, unless single-ended termination is used (see Section 2.1).

- 13. The current specified is also for AutoHALT state.

- 14.Maximum values are specified by design/characterization at nominal Vcc<sub>CORE</sub> and nominal Vcc<sub>L2</sub>.

- 15.Based on simulation and averaged over the duration of any change in current. Use to compute the maximum inductance tolerable and reaction time of the voltage regulator. This parameter is not tested.

- 16.dlcc/dt specifications are measured and specified at the SC242 connector pins.

- 17.Vcc<sub>5</sub> and Icc<sub>5</sub> are not used by the Pentium III processors. The Vcc<sub>5</sub> supply is used for the test equipment and tools.

| Symbol | Parameter              | Min  | Max   | Unit | Notes <sup>1,4,5</sup> |

|--------|------------------------|------|-------|------|------------------------|

| VIL    | Input Low Voltage      | -0.3 | 0.82  | V    |                        |