# INTEL® CELERON™ PROCESSOR MOBILE MODULE: MOBILE MODULE CONNECTOR 2 (MMC-2)

- Intel<sup>®</sup> Mobile Celeron<sup>™</sup> Processor with core frequency running at 300 MHz

- On-die, 2<sup>nd</sup> level cache (128K)

- System bus speed at 66 MHz

- Processor core voltage regulation supports input voltages from 5V to 21V

- Above 80 percent peak efficiency

- Integrated Active Thermal Feedback (ATF) system

- ACPI Rev. 1.0 compliant

- Internal A/D digital signaling (SMBUS) across the module interface

- Programmable trip point interrupt or poll mode for temperature reading

- Supports single AGP 66 MHz 3.3V device

- Thermal transfer plate for heat dissipation

- Intel<sup>®</sup> 443BX Host Bridge system controller

- DRAM controller supports EDO and SDRAM at 3.3V

- Supports PCI CLKRUN# protocol

- SDRAM clock support and self-refresh of EDO or SDRAM during Suspend mode

- 3.3V only PCI bus control, Rev 2.1 compliant

The Intel® Celeron™ processor mobile module connector 2 (MMC-2) is a highly integrated assembly containing an Intel Celeron mobile processor and its immediate system level support.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life-saving, or life-sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® Celeron™ processor mobile modules may contain design defects or errors known as errata. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel's website at <a href="http://www.intel.com">http://www.intel.com</a>

Copyright © Intel Corporation1998.

\*Third-party brands and names are the property of their respective owners.

# CONTENTS

| 1.0.<br>2.0.<br>3.0.<br>3.1<br>3.1.1. | INTRODUCTION                                               | <b>5</b><br><b>7</b><br>7 | 4.6.<br>4.6.1.<br>4.6.2. |                                  |

|---------------------------------------|------------------------------------------------------------|---------------------------|--------------------------|----------------------------------|

| 3.1.2.                                | Memory (109 Signals)                                       | 9                         |                          | Mea                              |

| 3.1.3.                                | AGP (60 Signals)                                           | 10                        | 4.7                      | Voltage Regulat                  |

| 3.1.4.                                | PCI (58 Signals)                                           | 12                        | 4.7.1.                   | Voltage Regula                   |

| 3.1.5.                                | Geyserville (4 Signals)                                    | 13                        | 4.7.2.                   |                                  |

| 3.1.6.                                | Processor/PIIX4E/M Sideband (8 Signals)                    | 14                        |                          | 4.7.2.1. Volta                   |

| 3.1.7.                                | Power Management (7 Signals)                               | 15                        | 4.7.3.                   | Sequ<br>Power Planes: I          |

| 3.1.8.                                | Clock (9 Signals)                                          | 16                        | 4.7.4.                   |                                  |

| 3.1.9.                                | Voltages (54 Signals)                                      | 17                        |                          | 4.7.4.1. Slew                    |

| 3.1.10.                               | ITP/JTAG (9 Signals)                                       | 18                        |                          | Desc                             |

| 3.1.11                                | Miscellaneous (82 Signals)                                 |                           |                          | 4.7.4.2. Und                     |

| 3.2.                                  | Connector Pin Assignments                                  |                           |                          | 4.7.4.3. Over                    |

| 3.3.                                  | Pin and Pad Assignments                                    |                           |                          | 4.7.4.3. Over                    |

| <b>4.0.</b><br>4.1.                   | FUNCTIONAL DESCRIPTION<br>Celeron™ Processor Mobile Module |                           |                          | 4.7.4.4. Ove                     |

| 4.1.                                  | L2 Cache                                                   |                           | 4.0                      | Desc                             |

| 4.3.                                  | The 443BX Host Bridge System Controller                    |                           | 4.8.<br>4.9              | Active Thermal<br>Thermal Sensor |

| 4.3.1.                                | Memory Organization                                        | 23                        | 5.0.                     | MECHANICAL                       |

| 4.3.2.                                | Reset Strap Options                                        | 24                        | 5.1.                     | Module Dimens                    |

| 4.3.3.                                | PCI Interface                                              | 24                        | 5.1.2.                   | MMC-2 Pin 1 Lo                   |

| 4.3.4.                                | AGP Interface                                              | 24                        | 5.1.3.                   | Printed Circuit E                |

| 4.4.                                  | Power Management                                           | 24                        | 5.1.4.                   | Height Restriction               |

| 4.4.1.                                | Clock Control Architecture                                 | 24                        | 5.2.                     | Thermal Transfe                  |

| 4.4.2.                                | Normal State                                               | 26                        | 5.3.                     | Module Physica                   |

| 4.4.3.                                | Auto Halt State                                            | 26                        | 5.3.1.                   | Module Mountin                   |

| 4.4.4.                                | Stop Grant State                                           | 26                        | 5.3.2.<br><b>6.0.</b>    | Module Weight THERMAL SPE        |

| 4.4.5.                                | Quick Start State                                          | 26                        | 6.1.                     | Thermal Design                   |

| 4.4.6.                                | HALT/Grant Snoop State                                     | 26                        | 6.2                      | Thermal Sensor                   |

| 4.4.7.                                | Sleep State                                                | 26                        | 7.0.                     | LABELING INF                     |

| 4.4.8.<br>4.5.                        | Deep Sleep State Typical POS/STR Power                     |                           | 8.0.                     | ENVIRONMEN'                      |

| 4.6.            | Electrical Requirements2  |                                                                                    |  |

|-----------------|---------------------------|------------------------------------------------------------------------------------|--|

| 4.6.1.          | DC Requi                  | rements28                                                                          |  |

| 4.6.2. AC Requi |                           | rements29                                                                          |  |

| 4.              | .6.2.1.                   | System Bus Clock (BCLK) Signal Quality Specifications and Measurement Guidelines30 |  |

| 4.7             | Voltage R                 | egulator30                                                                         |  |

| 4.7.1.          | Voltage R                 | egulator Efficiency30                                                              |  |

| 4.7.2.          | Control of                | the Voltage Regulator31                                                            |  |

| 4.              | .7.2.1.                   | Voltage Signal Definition and Sequencing32                                         |  |

| 4.7.3.          | Power Pla                 | anes: Bulk Capacitance Requirements33                                              |  |

| 4.7.4.          | Surge Cu                  | rrent Guidelines34                                                                 |  |

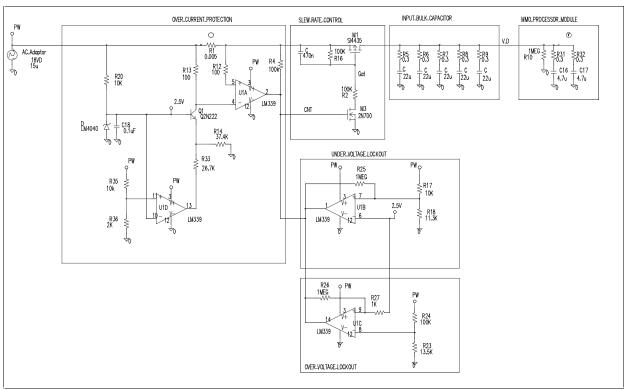

| 4.              | .7.4.1.                   | Slew-Rate Control: Circuit                                                         |  |

|                 | 7.40                      | Description36                                                                      |  |

| 4.              | .7.4.2.                   | Under Voltage Lockout: Circuit Description (V_uv_lockout)37                        |  |

| 4               | 7.4.3.                    | Over Voltage Lockout: Circuit                                                      |  |

|                 |                           | Description (V_ov_lockout)37                                                       |  |

| 4.              | .7.4.4.                   | Over Current Protection: Circuit                                                   |  |

| 4.0             | A - (* <b>T</b> b         | Description38                                                                      |  |

| 4.8.<br>4.9     |                           | ermal Feedback                                                                     |  |

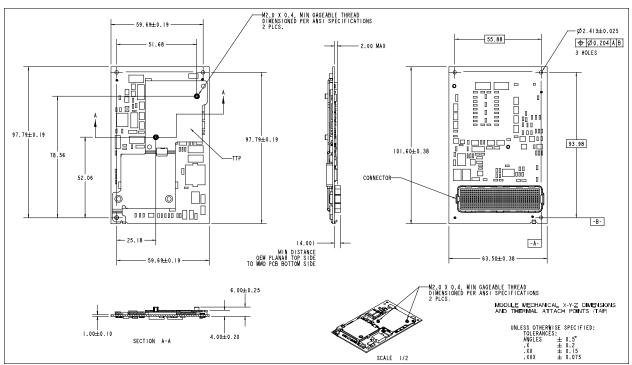

| 5.0.            | MFCHAN                    | Sensor Configuration Register39 IICAL SPECIFICATION39                              |  |

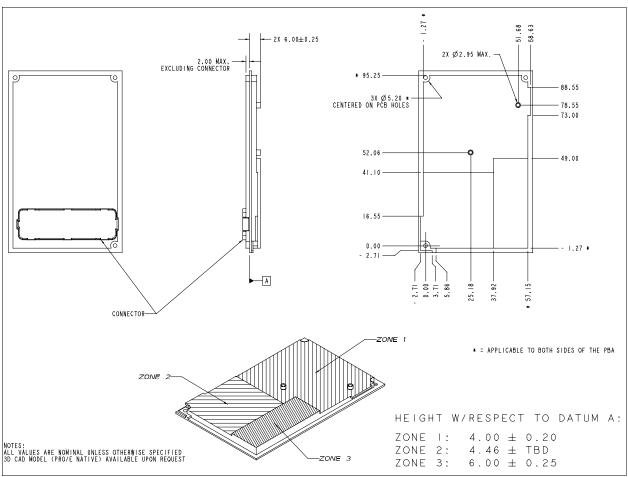

| 5.1.            |                           | imensions39                                                                        |  |

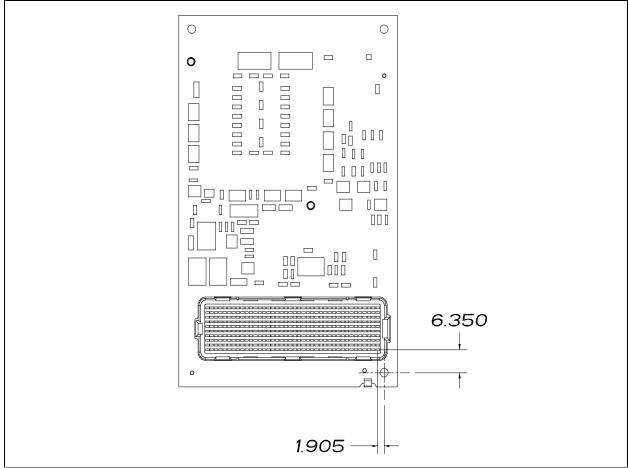

| 5.1.2.          | MMC-2 P                   | in 1 Location40                                                                    |  |

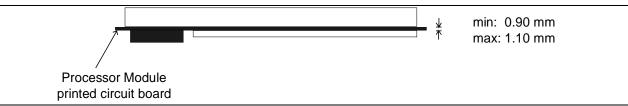

| 5.1.3.          | Printed C                 | ircuit Board Thickness41                                                           |  |

| 5.1.4.          | Height Re                 | estrictions41                                                                      |  |

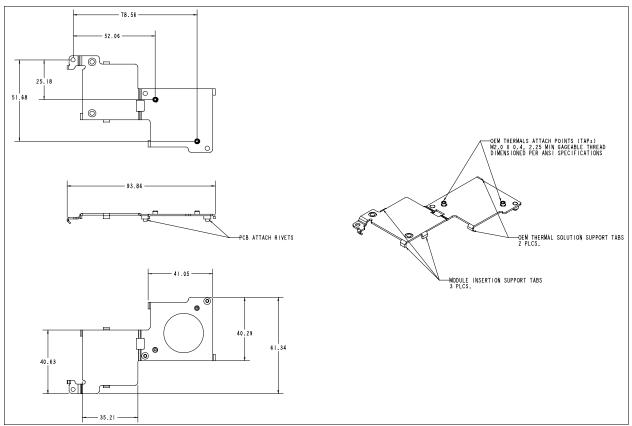

| 5.2.            | Thermal                   | Fransfer Plate42                                                                   |  |

| 5.3.            | Module P                  | hysical Support44                                                                  |  |

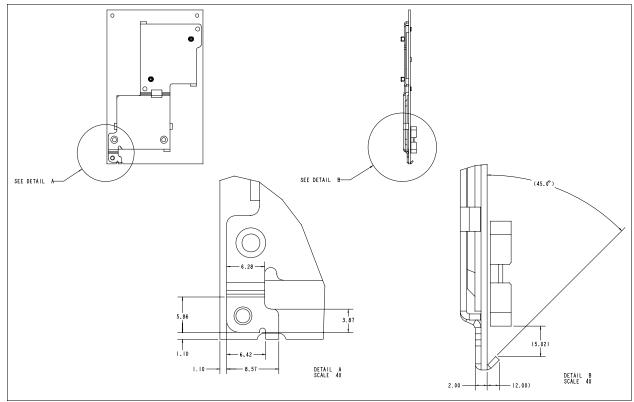

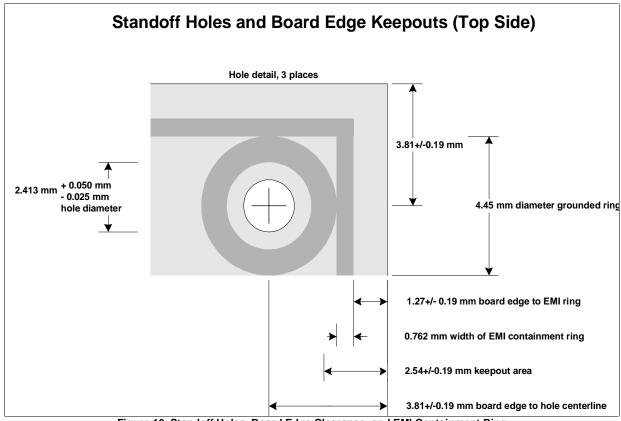

| 5.3.1.          | Module M                  | lounting Requirements44                                                            |  |

| 5.3.2.          | Module W                  | /eight44                                                                           |  |

| 6.0.            |                           | L SPECIFICATION45                                                                  |  |

| 6.1.            |                           | Design Power45                                                                     |  |

| 6.2             | Thermal Sensor Setpoint45 |                                                                                    |  |

| 7.0.<br>8.0.    |                           | G INFORMATION47 IMENTAL STANDARDS48                                                |  |

| 0.0.            | FIANIVOL                  | 41VILIVIAL 3 I ANDARDS40                                                           |  |

# INTEL® CELERON™ PROCESSOR MOBILE MODULE MMC-2

| FIGURES                                              |

|------------------------------------------------------|

| Figure 1. Block Diagram Of The Celeron Processor     |

| Mobile Module6                                       |

| Figure 2. 400-Pin Connector Footprint Pad Numbers,   |

| Module Secondary Side22                              |

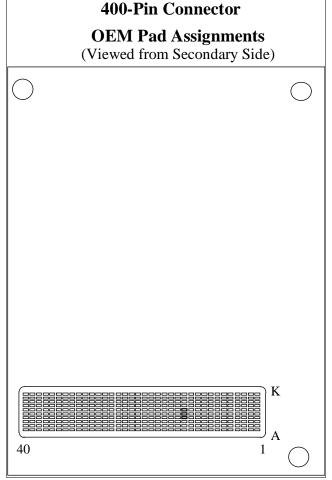

| Figure 3. Mobile Celeron Processor Clock             |

| Control States25                                     |

| Figure 4. Bclk, Tck, Picclk Generic Clock Waveform   |

| at the Processor Core Pins30                         |

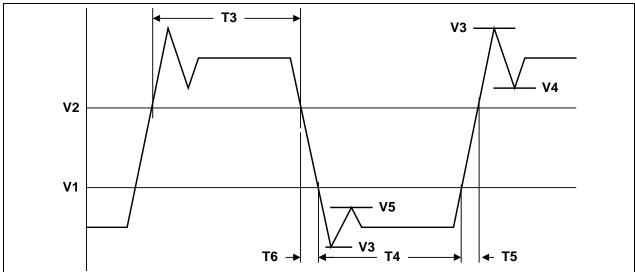

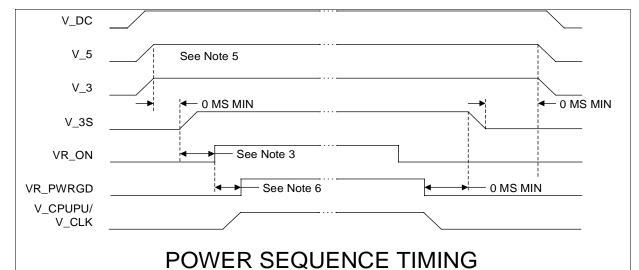

| Figure 5. Power-On Sequence Timing33                 |

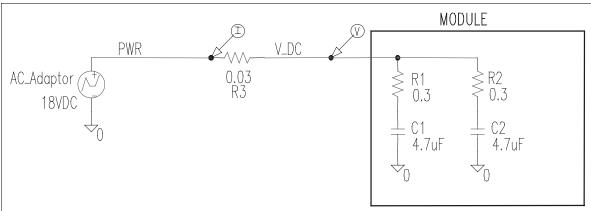

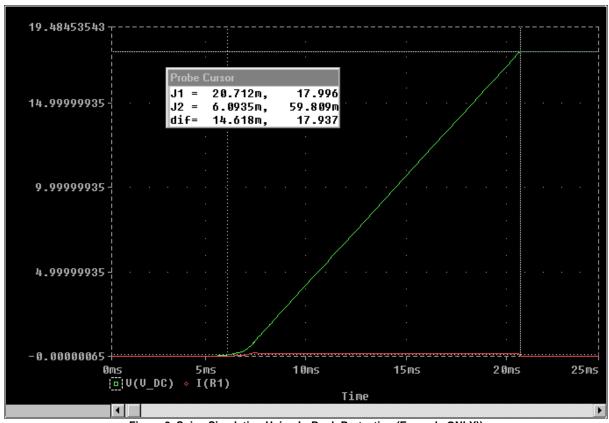

| Figure 6. Instantaneous In-Rush Current Model34      |

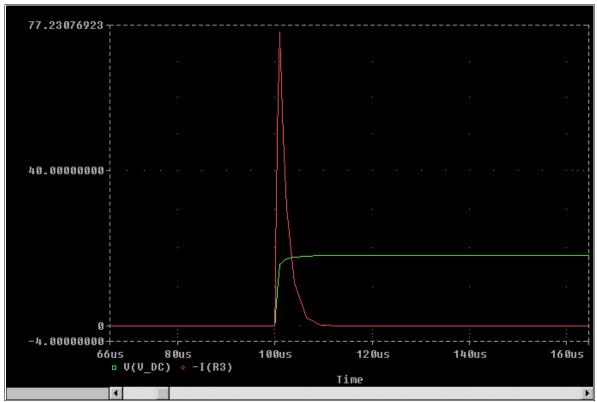

| Figure 7. Instantaneous In-Rush Current35            |

| Figure 8. Over Current Protection Circuit36          |

| Figure 9. Spice Simulation Using In-Rush Protection  |

| (Example Only))37                                    |

| Figure 10. Board Dimensions With 400-Pin Connector   |

| Orientation40                                        |

| Figure 11. Board Dimensions With 400-Pin Connector-  |

| Pin 1 Orientation41                                  |

| Figure 12. Printed Circuit Board Thickness41         |

| Figure 13. Celeron Process Mobile Module 3-D         |

| Keep-Out Zone42                                      |

| Figure 14. Celeron Processor Mobile Module           |

| Thermal Transfer Plate43                             |

| Figure 15. Celeron Processor Mobile Module           |

| Thermal Transfer Plate44                             |

| Figure 16. Standoff Holes, Board Edge Clearance, and |

| EMI Containment Ring45                               |

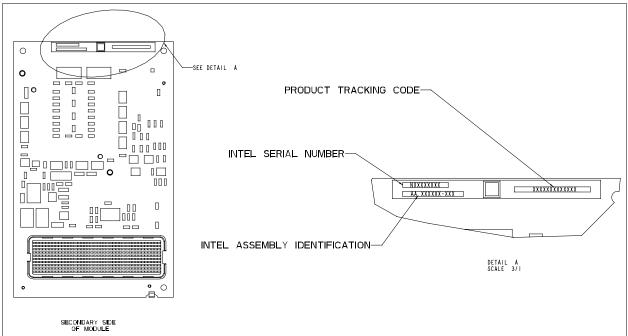

| Figure 17. Celeron Processor Mobile Module           |

| Product Tracking Information 47                      |

| TABLES                                                   |     |

|----------------------------------------------------------|-----|

| Table 1. Connector Signal Summary                        | 7   |

| Table 2. Memory Signal Descriptions                      | 9   |

| Table 3. AGP Signal Descriptions                         | 10  |

| Table 4. PCI Signal Descriptions                         | 12  |

| Table 5. Geyserville Descriptions                        | 13  |

| Table 6. Processor/PIIX4E/M Sideband Signal Descriptions | 14  |

| Table 7. Power Management Signal Descriptions            | 15  |

| Table 8. Clock Signal Descriptions                       | 16  |

| Table 9. Voltage Descriptions                            | 17  |

| Table 10. ITP/JTAG Pins                                  | .18 |

| Table 11. Miscellaneous Pins                             | 18  |

| Table 12. Connector Pin Assignments                      | 19  |

| Table 13. Connector Specifications                       | 23  |

| Table 14. Configuration Straps for the 443BX Host Bridge |     |

| System Controller                                        | 24  |

| Table 15. Mobile Celeron Processor Clock State           |     |

| Characteristics                                          | 27  |

| Table 16. Mobile Celeron POS/STR Power                   | 27  |

| Table 17. Celeron Processor Mobile Module Power          |     |

| Specifications 1                                         | 28  |

| Table 18. Celeron Processor Mobile Module AC             |     |

| Specifications (BCLK)                                    | 29  |

| Table 19. BCLK Signal Quality Specifications at the      |     |

| Processor Core 1                                         | 30  |

| Table 20. Typical Voltage Regulator Efficiency           | 31  |

| Table 21. Voltage Signal Definitions and Sequences       | 32  |

| Table 22. Capacitance Requirement per Power Plane        | 33  |

| Table 23. Thermal Sensor SMBus Address Table             | 39  |

| Table 24. Thermal Sensor Configuration Register          | 39  |

| Table 25. Celeron Processor MMC-2 Maximum Power          |     |

| Specifications                                           | 46  |

| Table 26 Environmental Standards                         | 10  |

#### 1.0. INTRODUCTION

This document provides the technical information for integrating the Celeron™ Processor Mobile Module Connector 2 (MMC-2) into the latest notebook systems for today's notebook market.

Building around the Celeron processor mobile module design gives the system manufacturer these advantages:

- Avoids complexities associated with designing highspeed processor core logic boards.

- Provides an upgrade path from previous Intel mobile modules using a standard interface.

#### 2.0. ARCHITECTURE OVERVIEW

The Celeron™ processor mobile module is a highly integrated assembly containing the mobile Celeron processor core with an on-die L2 cache, the Intel®443BX Host Bridge system controller, and system level support. The Celeron processor mobile module runs at 300 MHz with a 66-MHz system bus speed.

The PIIX4E/M PCI/ISA Bridge is one of two large-scale integrated devices of the Intel 440BX AGPset. A notebook's system electronics must include a PIIX4E/M device to connect to the Celeron processor mobile module. The PIIX4E/M provides extensive power management capabilities and supports the 443BX Host Bridge, which is the second integrated device. Key features of the Intel 443BX Host Bridge include the DRAM controller, which supports EDO at 3.3V with a burst read at 7-2-2-2 (60 ns) or SDRAM at 3.3V with a burst read at 8-1-1-1 (66 MHz, CL=2).

The 443BX Host Bridge also provides a PCI CLKRUN# signal to request PIIX4E/M to regulate the PCI clock on the PCI bus. The 82443Bx clock enables Self-Refresh mode of EDO or SDRAM during Suspend mode, and is compatible with SMRAM (C\_SMRAM) and Extended SMRAM (E\_SMRAM) modes of power management. E\_SMRAM mode supports write-back cacheable SMRAM up to 1 MB.

A thermal transfer plate (TTP) on the 443BX Host Bridge and the mobile Celeron processor provides heat dissipation and a standard thermal attach point for the notebook manufacturer's thermal solution.

An on-board voltage regulator converts the system DC voltage to the processor's core and I/O voltage. Isolating the processor voltage requirements allows the system manufacturer to incorporate different processor variants into a single notebook system.

Supporting input voltages from 5V to 21V, the processor core voltage regulation enables an above 80 percent peak efficiency and decouples processor voltage requirements from the system.

The Celeron processor mobile module also incorporates Active Thermal Feedback (ATF) sensing, compliant to the ACPI Rev 1.0 specification. A system management bus (SMBus, which is thermal sensor compliant, supports the internal and external temperature sensing with programmable trip points.

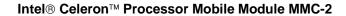

Figure 1 illustrates the block diagram of the Celeron processor mobile module.

Figure 1. Block Diagram of the Celeron™ Processor Mobile Module

# 3.0. MODULE CONNECTOR INTERFACE

Table 1 provides a list of signals by category and the corresponding number of signals in each category.

For proper signal termination, please contact your Intel sales representative for further information.

# 3.1 Signal Definitions

The signals are variably defined for compatibility with future Intel mobile modules.

**Table 1. Connector Signal Summary**

| Signal Group                | Number |

|-----------------------------|--------|

| Memory                      | 109    |

| AGP                         | 60     |

| PCI                         | 58     |

| Processor/PIIX4E/M Sideband | 8      |

| Geyserville Technology      | 4      |

| Power Management            | 7      |

| Clocks                      | 9      |

| Voltage: V_DC               | 20     |

| Voltage: V_3S               | 9      |

| Voltage: V_5                | 3      |

| Voltage: V_3                | 16     |

| Voltage: VCCAGP             | 4      |

| Voltage: V_CPUPU            | 1      |

| Voltage: V_CLK              | 1      |

| ITP/JTAG                    | 9      |

| Module ID                   | 4      |

| Ground                      | 45     |

| Reserved                    | 33     |

| Total                       | 400    |

# 3.1.1. Signal List

The following notations are used to denote the signal type:

| l | Input | pin |

|---|-------|-----|

|---|-------|-----|

O Output pin

O D Open Drain Output pin. This pin requires a pull up resistor.

I D Open Drain Input pin. This pin requires a pull up resistor.

I/O D Input / Open Drain Output pin. This pin requires a pull up resistor.

I/O Bi-directional Input / Output pin

The signal description also includes the type of buffer used for a particular signal:

GTL+ Open Drain GTL+ interface signal.

PCI PCI bus interface signals.

AGP AGP interface signals.

CMOS The CMOS buffers are Low Voltage TTL compatible signals. They are also 3.3V outputs with 5.0V tolerant

inputs.

# 3.1.2. Memory (109 Signals)

Table 2 lists the memory interface signals.

**Table 2. Memory Signal Descriptions**

| Table 2. Memory Signal Descriptions |             |         |                                                                                                                                                                                   |  |

|-------------------------------------|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                | Type        | Voltage | Description                                                                                                                                                                       |  |

| MECC[7:0]                           | I/O<br>CMOS | V_3     | Memory ECC Data: These signals carry Memory ECC data during access to DRAM. These pins are implemented on the MMC-2.                                                              |  |

| RASA[5:0]# or                       | 0           | V_3     | Row Address Strobe (EDO): These pins select the DRAM row.                                                                                                                         |  |

| CSA[5:0]#                           | CMOS        |         | Chip Select (SDRAM): These pins activate the SDRAMs. SDRAM accepts any command when its CS# pin is active low.                                                                    |  |

| CASA[7:0]# or DQMA[7:0]             | O<br>CMOS   | V_3     | Column Address Strobe (EDO): These pins select the DRAM column.                                                                                                                   |  |

|                                     |             |         | Input/Output Data Mask (SDRAM): These pins act as synchronized output enables during a read cycle and as a byte mask during a write cycle.                                        |  |

| MAB[9:0]#                           | 0           | V_3     | Memory Address (EDO/SDRAM): This is the row and column                                                                                                                            |  |

| MAB[10]                             | CMOS        |         | address for DRAM. The 443BX Host Bridge system controller has two identical sets of address lines (MAA and MAB#). The Celeron                                                     |  |

| MAB[12:11]#                         |             |         | processor mobile module supports only the MAB set of address lines. For additional addressing features, please refer to the <i>Intel</i> ®                                        |  |

| MAB[13]                             |             |         | 440BX AGPset Datasheet.                                                                                                                                                           |  |

| MWEA#                               | O<br>CMOS   | V_3     | Memory Write Enable (EDO/SDRAM): MWEA# should be used as the write enable for the memory data bus.                                                                                |  |

| SRASA#                              | O<br>CMOS   | V_3     | SDRAM Row Address Strobe (SDRAM): When active low, this signal latches Row Address on the positive edge of the clock. This signal also allows Row access and pre-charge.          |  |

| SCASA#                              | O<br>CMOS   | V_3     | SDRAM Column Address Strobe (SDRAM): When active low, this signal latches Column Address on the positive edge of the clock. This signal also allows Column access.                |  |

| CKE[5:0]                            | O<br>CMOS   | V_3     | SDRAM Clock Enable (SDRAM): SDRAM clock enable pin. When these signals are deasserted, SDRAM enters power-down mode. Each row is individually controlled by its own clock enable. |  |

| MD[63:0]                            | I/O         | V_3     | Memory Data: These signals are connected to the DRAM data bus.                                                                                                                    |  |

|                                     | CMOS        |         | They are not terminated on the Celeron™ processor mobile module.                                                                                                                  |  |

# 3.1.3. AGP (60 Signals)

Table 3 lists the AGP interface signals.

**Table 3. AGP Signal Descriptions**

| Name        | Type       | Voltage | able 3. AGP Signal Descriptions  Description                                                                                                                                                                                                                      |

|-------------|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GAD[31:0]   | I/O<br>AGP | V_3     | AGP Address/Data: The standard AGP address and data lines. This bus functions in the same way as the PCI AD[31:0] bus. The address is driven with FRAME# assertion and data is driven or received in following clocks.                                            |

| GC/BE[3:0]# | I/O<br>AGP | V_3     | AGP Command/Byte Enable: This bus carries the command information during AGP cycles when PIPE# is used. During an AGP write, this bus contains byte enable information. The command is driven with FRAME# assertion and byte enables corresponding to supplied or |

|             |            |         | requested data are driven on the following clocks.                                                                                                                                                                                                                |

| GFRAME#     | I/O<br>AGP | V_3     | AGP Frame: Not used during AGP transactions. Remains deasserted by an internal pullup resistor. Assertion indicates the address phase of a PCI transfer. Negation indicates that the cycle initiator desires one more data transfer.                              |

| GDEVSEL#    | I/O<br>AGP | V_3     | AGP Device Select: Same function as PCI DEVSEL#. Not used during AGP transactions. The 443BX Host Bridge system controller drives this signal when a PCI initiator is attempting to access DRAM. DEVSEL# is asserted at medium decode time.                       |

| GIRDY#      | I/O<br>AGP | V_3     | AGP Initiator Ready: Indicates the AGP compliant target is ready to provide ALL write data for the current transaction. Asserted when the initiator is ready for a data transfer.                                                                                 |

| GTRDY#      | I/O<br>AGP | V_3     | AGP Target Ready: Indicates the AGP compliant master is ready to provide ALL write data for the current transaction. Asserted when the target is ready for a data transfer.                                                                                       |

| GSTOP#      | I/O<br>AGP | V_3     | AGP Stop: Same function as PCI STOP#. Not used during AGP transactions. Asserted by the target to request the master to stop the current transaction.                                                                                                             |

| GREQ#       | I<br>AGP   | V_3     | AGP Request: AGP master requests for AGP.                                                                                                                                                                                                                         |

| GGNT#       | O<br>AGP   | V_3     | <b>AGP Grant</b> : Same function as on PCI. Additional information is provided on the ST[2:0] bus. PCI Grant: Permission is given to the master to use PCI.                                                                                                       |

| GPAR        | I/O<br>AGP | V_3     | AGP Parity: A single parity bit is provided over GAD[31:0] and GC/BE[3:0]. This signal is not used during AGP transactions.                                                                                                                                       |

| PIPE#       | I<br>AGP   | V_3     | <b>Pipelined Request</b> : Asserted by the current master to indicate a full width address that is to be queued by the target. The master queues one request each rising clock edge while PIPE# is asserted.                                                      |

| SBA[7:0]    | I<br>AGP   | V_3     | <b>Sideband Address</b> : This bus provides an additional conduit to pass address and commands to the 443BX Host Bridge System Controller from the AGP master.                                                                                                    |

| RBF#        | l<br>AGP   | V_3     | Read Buffer Full: Indicates if the master is ready to accept previously requested, low-priority read data.                                                                                                                                                        |

| ST[2:0]     | O<br>AGP   | V_3     | Status Bus: Provides information from the arbiter to an AGP Master on what it may do. These bits only have meaning when GGNT is asserted.                                                                                                                         |

# Intel® Celeron™ Processor Mobile Module MMC-2

| ADSTB[B:A] | I/O<br>AGP | _   | AD Bus Strobes: Provide timing for double-clocked data on the GAD bus. The agent that is providing data drives these signals. These are identical copies of each other. |

|------------|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBSTB      | I<br>AGP   | V_3 | <b>Sideband Strobe</b> : Provides timing for a sideband bus. The SBA[7:0] (AGP master) drives the sideband strobe.                                                      |

# 3.1.4. PCI (58 Signals)

Table 4 lists the PCI interface signals.

Table 4. PCI Signal Descriptions

| Name       | Type         | Voltage | Table 4. PCI Signal Descriptions  Description                                                                                                                                                                                                                                                                                                                                                     |

|------------|--------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]   | I/O<br>PCI   | V_3     | Address/Data: The standard PCI address and data lines. The address is driven with FRAME# assertion and data is driven or received in the following clocks.                                                                                                                                                                                                                                        |

| C/BE[3:0]# | I/O<br>PCI   | V_3     | <b>Command/Byte Enable:</b> The command is driven with FRAME# assertion and byte enables corresponding to supplied or requested data are driven on the following clocks.                                                                                                                                                                                                                          |

| FRAME#     | I/O<br>PCI   | V_3     | Frame: Assertion indicates the address phase of a PCI transfer. Negation indicates that the cycle initiator desires one more data transfer.                                                                                                                                                                                                                                                       |

| DEVSEL#    | I/O<br>PCI   | V_3     | <b>Device Select:</b> the 443BX Host Bridge drives This signal when a PCI initiator is attempting to access DRAM. DEVSEL# is asserted at medium decode time.                                                                                                                                                                                                                                      |

| IRDY#      | I/O<br>PCI   | V_3     | Initiator Ready: Asserted when the initiator is ready for data transfer.                                                                                                                                                                                                                                                                                                                          |

| TRDY#      | I/O<br>PCI   | V_3     | Target Ready: Asserted when the target is ready for a data transfer.                                                                                                                                                                                                                                                                                                                              |

| STOP#      | I/O<br>PCI   | V_3     | <b>Stop:</b> Asserted by the target to request the master to stop the current transaction.                                                                                                                                                                                                                                                                                                        |

| PLOCK#     | I/O<br>PCI   | V_3     | <b>Lock</b> : Indicates an exclusive bus operation and may require multiple transactions to complete. When LOCK# is asserted, non-exclusive transactions may proceed. The 443BX supports lock for CPU initiated cycles only. PCI initiated locked cycles are not supported.                                                                                                                       |

| REQ[4:0]#  | I<br>PCI     | V_3     | PCI Request: PCI master requests for PCI.                                                                                                                                                                                                                                                                                                                                                         |

| GNT[4:0]#  | O<br>PCI     | V_3     | PCI Grant: Permission is given to the master to use PCI.                                                                                                                                                                                                                                                                                                                                          |

| PHOLD#     | I<br>PCI     | V_3     | PCI Hold: This signal comes from the expansion bridge; it is the bridge request for PCI. The 443BX Host Bridge will drain the DRAM write buffers, drain the processor-to-PCI posting buffers, and acquire the host bus before granting the request via PHLDA#. This ensures that GAT timing is met for ISA masters. The PHOLD# protocol has been modified to include support for passive release. |

| PHLDA#     | O<br>PCI     | V_3     | <b>PCI Hold Acknowledge:</b> This signal is driven by the 443BX Host Bridge to grant PCI to the expansion bridge. The PHLDA# protocol has been modified to include support for passive release.                                                                                                                                                                                                   |

| PAR        | I/O<br>PCI   | V_3     | Parity: A single parity bit is provided over AD[31:0] and C/BE[3:0]#.                                                                                                                                                                                                                                                                                                                             |

| SERR#      | I/O<br>PCI   | V_3     | System Error: The 443BX asserts this signal to indicate an error condition. Please refer to the Intel <sup>®</sup> 440BX AGPset Datasheet for further information.                                                                                                                                                                                                                                |

| CLKRUN#    | I/O D<br>PCI | V_3     | Clock Run: An open-drain output and input. The 443BX Host Bridge requests the central resource (PIIX4E/M) to start or maintain the PCI clock by asserting CLKRUN#. The 443BX Host Bridge tri-states CLKRUN# upon deassertion of Reset (since CLK is running upon deassertion of Reset).                                                                                                           |

| PCI_RST#   | I<br>CMOS    | V_3     | Reset: When asserted, this signal asynchronously resets the 443BX Host Bridge. The PCI signals also tri-state, compliant with PCI Rev 2.1 specifications.                                                                                                                                                                                                                                         |

# 3.1.5. Geyserville (4 Signals)

Table 5 lists the Geyserville signal definitions.

**Table 5. Geyserville Descriptions**

| Name         | Туре      | Voltage | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G_LO/HI#     | I<br>CMOS | V_3     | Geyserville State Transition: Generated by the PIIX4E/M, this signal defines a Geyserville state change to the Geyserville state machine. This signal is not implemented on the current Celeron™ processor mobile modules, and is defined for future upgrade purposes only.                                                                                                                                                                                              |

| G_CPU_STP#   | I<br>CMOS | V_3     | Geyserville CPU_STP#: The CPU_STP# signal gated by the Geyserville state machine becomes G_CPU_STP#. This signal is not implemented on the current Celeron™ processor mobile modules, and is defined for future upgrade purposes only.                                                                                                                                                                                                                                   |

| VRChgng#     | O<br>CMOS | V_3     | Voltage Changing: A Geyserville state machine signal that indicates that the actual state change is in progress – the VR setpoint has changed and the VR is settling. When this signal deasserts, the new state is sent to the processor. System electronics will use this signal to generate an SCI to force a transition out of deep sleep. This signal is not implemented on the current Celeron™ processor mobile modules, and is defined for upgrade purposes only. |

| G_SUS_STAT1# | O<br>CMOS | V_3     | G_SUS_STAT1#: The SUS_STAT1# signal gated by the Geyserville control logic. G_SUS_STAT1# should be used in place of the SUS_STAT1# signal in the system electronics design. This signal is not implemented on the current Celeron™ processor mobile modules, and is defined for upgrade purposes only.                                                                                                                                                                   |

# 3.1.6. Processor/PIIX4E/M Sideband (8 Signals)

Table 6 lists the mobile Celeron<sup>TM</sup> processor and PIIX4E/M sideband signals at the connector interface. The voltage level for these signals is determined by  $V\_CPUPU$ , which is supplied by the Celeron<sup>TM</sup> processor mobile module.

Table 6. Processor/PIIX4E/M Sideband Signal Descriptions

| Name    | Туре        | Voltage | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|-------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FERR#   | O<br>CMOS   | V_CPUPU | Numeric Coprocessor Error: This pin functions as a FERR# signal supporting coprocessor errors. This signal is tied to the coprocessor error signal on the processor and is driven by the processor to the PIIX4E/M.                                                                                                                                                                                                 |

| IGNNE#  | I D<br>CMOS | V_CPUPU | Ignore Error: This open drain signal is connected to the ignore error pin on the processor and is driven by the PIIX4E/M.                                                                                                                                                                                                                                                                                           |

| INIT#   | I D<br>CMOS | V_CPUPU | <b>Initialization:</b> INIT# is asserted by the PIIX4E/M to the processor for system initialization. This signal is an open drain.                                                                                                                                                                                                                                                                                  |

| INTR    | I D<br>CMOS | V_CPUPU | <b>Processor Interrupt:</b> INTR is driven by the PIIX4E/M to signal the processor that an interrupt request is pending and needs to be serviced. This signal is an open drain.                                                                                                                                                                                                                                     |

| NMI     | I D<br>CMOS | V_CPUPU | Non-Maskable Interrupt: NMI is used to force a non-maskable interrupt to the processor. The PIIX4E/M ISA bridge generates a NMI when either SERR# or IOCHK# is asserted, depending on how the NMI Status and Control Register is programmed. This signal is an open drain.                                                                                                                                          |

| A20M#   | I D<br>CMOS | V_CPUPU | Address Bit 20 Mask: When enabled, this open drain signal causes the processor to emulate the address wraparound at one MB, which occurs on the Intel® 8086 processor.                                                                                                                                                                                                                                              |

| SMI#    | I D<br>CMOS | V_CPUPU | System Management Interrupt: SMI# is an active low synchronous output from the PIIX4E/M that is asserted in response to one of many enabled hardware or software events. The SMI# open drain signal can be an asynchronous input to the processor. However, in this chip set SMI# is synchronous to PCLK.                                                                                                           |

| STPCLK# | I D<br>CMOS | V_CPUPU | Stop Clock: STPCLK# is an active low synchronous open drain output from the PIIX4E/M that is asserted in response to one of many hardware or software events. STPCLK# connects directly to the processor and is synchronous to PCICLK. When the processor samples STPCLK# asserted, it responds by entering a low power state (Quick Start). The processor will only exit this mode when this signal is deasserted. |

# 3.1.7. Power Management (7 Signals)

Table 7 lists the power management signals. The SM\_CLK and SM\_DATA signals refer to the two-wire serial SMBus

interface. Although this interface is currently used solely for the digital thermal sensor, the SMBus contains reserved serial addresses for future use. See section 4.9 for more details.

Table 7. Power Management Signal Descriptions

| Name       | Туре          | Voltage                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|------------|---------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SUS_STAT1# | I<br>CMOS     | V_3ALWAYS<br>(See Note) | Suspend Status: This signal connects to the SUS_STAT1# output of PIIX4E/M. It provides information on host clock status and is asserted during all suspend states.                                                                                                                                                                                                                                                                                                             |  |  |

| VR_ON      | I<br>CMOS     | V_3S                    | VR_ON: Voltage regulator ON. This 3.3V (5V tolerant) signal controls the operation of the voltage regulator. VR_ON should be generated as a function of the PIIX4E/M SUSB# signal which is used for controlling the "Suspend State B" voltage planes. This signal should be driven by a digital signal with a rise/fall time of less than or equal to 1us. See Figure 5 in section 4.7.2.1. of this document for proper sequencing of VR_ON. (VIL (max)=0.4V, VIH (min)=3.0V). |  |  |

| VR_PWRGD   | 0             | V_3                     | VR_PWRGD: This signal is driven high by the Celeron™ processor mobile module to indicate that the voltage regulator is stable. The signal is pulled low using a 100K resistor when inactive. It can be used in some combination to generate the system PWRGOOD signal.                                                                                                                                                                                                         |  |  |

| BXPWROK    | I<br>CMOS     | V_3                     | Power OK to BX: This signal must go active 1 mS after the V_3 power rail is stable, and 1 ms prior to deassertion of PCIRST#.                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SM_CLK     | I/O D<br>CMOS | V_3                     | <b>Serial Clock:</b> This clock signal is used on the SMBus interface to the digital thermal sensor.                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| SM_DATA    | I/O D<br>CMOS | V_3                     | Serial Data: Open-drain data signal on the SMBus interface to the digital thermal sensor.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| ATF_INT#   | O D<br>CMOS   | V_3                     | ATF Interrupt: This signal is an open-drain output signal of the digital thermal sensor.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

#### NOTE:

V\_3ALWAYS: 3.3V voltage supply. It is generated whenever V\_DC is available and supplied to PIIX4E/M resume well.

# 3.1.8. Clock (9 Signals)

Table 8 lists the clock signals.

**Table 8. Clock Signal Descriptions**

| Name      | Type      | Voltage | le 8. Clock Signal Descriptions  Description                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----------|-----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PCLK      | I<br>PCI  | V_3     | PCI Clock In: PCLK, an input to the Celeron processor mobile module, is one of the system's PCI clocks. This clock is used by all of the 443BX Host Bridge logic in the PCI clock domain. This clock is stopped when the PIIX4E/M PCI_STP# signal is asserted and/or during all suspend states.                                                                                                                   |  |  |

| HCLK[1:0] | I<br>CMOS | V_CLK   | Host Clock In: These clocks are inputs to the Celeron™ processor mobile module from the CK97-M clock source (p. 30). The processor and the 443BX Host Bridge system controller use HCLK[0]. This clock is stopped when the PIIX4E/M CPU_STP# signal is asserted and/or during all suspend states.                                                                                                                 |  |  |

| DCLKO     | O<br>CMOS | V_3     | SDRAM Clock Out: 66 MHz SDRAM clock reference generated internally by the 443BX Host Bridge system controller onboard PLL. It feeds an external buffer that produces multiple copies for the SODIMMs.                                                                                                                                                                                                             |  |  |

| DCLKRD    | I<br>CMOS | V_CLK   | SDRAM Read Clock: Feedback reference from the SDRAM clock buffer. The 443BX Host Bridge System Controller uses this clock when reading data from the SDRAM array. This signal is not implemented on the Celeron™ processor mobile module.                                                                                                                                                                         |  |  |

| DCLKWR    | I<br>CMOS | V_CLK   | SDRAM Write Clock: Feedback reference from the SDRAM clock buffer. The 443BX Host Bridge system controller uses this clock when writing data to the SDRAM array.                                                                                                                                                                                                                                                  |  |  |

| GCLKIN    | I<br>CMOS | V_3     | AGP Clock In: The GCLKIN input is a feedback reference from the GCLKO signal.                                                                                                                                                                                                                                                                                                                                     |  |  |

| GCLKO     | O<br>CMOS | V_3     | AGP Clock Out: This signal is generated by the 443BX Host Bridge system controller onboard PLL from the HCLK0 host clock reference. The frequency of GCLK0 is 66MHz. The GCLKO output is used to feed both the PLL reference input pins on the 443BX Host Bridge system controller and the AGP device. The board layout must maintain complete symmetry on loading and trace geometry to minimize AGP clock skew. |  |  |

| FQS       | O<br>CMOS | V_3S    | Frequency Select: This output indicates the desired host clock frequency for the Celeron™ processor mobile module.                                                                                                                                                                                                                                                                                                |  |  |

|           |           |         | FQS=0 indicates 66MHz                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|           |           |         | FQS=1 indicates 100MHz (for future Intel mobile modules)                                                                                                                                                                                                                                                                                                                                                          |  |  |

# 3.1.9. Voltages (54 Signals)

Table 9 lists the voltage signal definitions.

**Table 9. Voltage Descriptions**

| Name    | Туре | Number  | Description                                                                                                                                                                                                                          |  |  |

|---------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|         |      | of Pins |                                                                                                                                                                                                                                      |  |  |

| V_DC    | 1    | 20      | <b>DC Input:</b> 5V – 21V                                                                                                                                                                                                            |  |  |

| V_3S    | I    | 9       | SUSB# controlled 3.3V: Power-managed 3.3V supply. An output of the voltage regulator on the system electronics. This rail is off during STR, STD, and Soff. This rail is not used on the Celeron™ processor mobile module.           |  |  |

| V_5     | _    | 3       | <b>SUSC# controlled 5V:</b> Power-managed 5V supply. An output of the voltage regulator on the system electronics. This rail is off during STD and Soff.                                                                             |  |  |

| V_3     | I    | 16      | <b>SUSC# controlled 3.3V:</b> Power-managed 3.3V supply. An output of the voltage regulator on the system electronics. This rail is off during STD and Soff.                                                                         |  |  |

| VCCAGP  | I    | 4       | AGP I/O Voltage: This voltage rail is not implemented on the current Celeron™ processor mobile modules, and is defined for upgrade purposes only. We recommend that this voltage rail be connected to V_3 on the system electronics. |  |  |

| V_CPUPU | 0    | 1       | Processor I/O Ring: Driven by the Celeron™ processor mobile module to power processor interface signals such as the PIIX4E/M open-drain pullups for the processor/PIIX4E/M sideband signals.                                         |  |  |

| V_CLK   | 0    | 1       | Processor Clock Rail: Driven by the Celeron™ processor mobile module to power CK100-M VDDCPU rail.                                                                                                                                   |  |  |

# 3.1.10. ITP/JTAG (9 Signals)

Table 10 lists the ITP/JTAG signals, which the system manufacturer can use to implement a JTAG chain and ITP port if desired.

Table 10. ITP/JTAG Pins

| Name      | Туре | Voltage | Description                                                                                                                                                                 |  |  |

|-----------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TDO       | 0    | V_CPUPU | JTAG Test Data Out: Serial output port. TAP instructions and data are shifted out of the processor from this port.                                                          |  |  |

| TDI       | I    | V_CPUPU | JTAG Test Data In: Serial input port. TAP instructions and data are shifted into the processor from this port.                                                              |  |  |

| TMS       | _    | V_CPUPU | JTAG Test Mode Select: Controls the TAP controller change sequence.                                                                                                         |  |  |

| TCLK      | _    | V_CPUPU | JTAG Test Clock: Testability clock for clocking the JTAG boundary scan sequence.                                                                                            |  |  |

| TRST#     | I    | V_CPUPU | JTAG Test Reset: Asynchronously resets the TAP controller in the processor.                                                                                                 |  |  |

| FS_RESET# | 0    | GTL+    | Processor Reset: Processor reset status to the ITP.                                                                                                                         |  |  |

| VTT       | 0    | V_Core  | <b>GTL+ Termination Voltage:</b> Used by the POWERON pin on the ITP debug port to determine when target system is on. POWERON pin is pulled up using a 1KΩ resistor to VTT. |  |  |

| FS_PREQ#  | I    | V_CPUPU | <b>Debug Mode Request:</b> Driven by the ITP – makes request to enter debug mode.                                                                                           |  |  |

| FS_PRDY#  | 0    | GTL+    | <b>Debug Mode Ready:</b> Driven by the processor – informs the ITP that the processor is in debug mode.                                                                     |  |  |

#### NOTE:

Recommendation: DBREST# (reset target system) on the ITP debug port can be "logically ANDed" with VR\_PWRGD TO PIIX4E/M's PWROK.

# 3.1.11 Miscellaneous (82 Signals)

Table 11 lists the miscellaneous signal pins.

Table 11. Miscellaneous Pins

| Name              | Type | Number | Description                                                                                                                |  |

|-------------------|------|--------|----------------------------------------------------------------------------------------------------------------------------|--|

| Module<br>ID[3:0] | 0    | 4      | Module Revision ID: These pins track the revision level of the Celeron™ processor mobile module. A 100K pullup resistor to |  |

|                   | CMOS |        | V_3S must be placed on the system electronics for these signals.                                                           |  |

| Ground            | I    | 45     | Ground.                                                                                                                    |  |

| Reserved          | RSVD | 33     | Unallocated Reserved pins and should not be connected.                                                                     |  |

#### **Connector Pin Assignments** 3.2.

Table 12 lists the signals for each pin of the MMC-2 to the system electronics. Refer to Section 3.3 for the pin assignments of the pads on the connector.

|      |           | Table 12. Connector Pin Assignments |          |            |          |  |  |  |

|------|-----------|-------------------------------------|----------|------------|----------|--|--|--|

| Pin# | Row       | Row                                 | Row      | Row        | Row      |  |  |  |

|      | Α         | В                                   | С        | D          | E        |  |  |  |

| 1    | SBA5      | ADSTBB                              | Gnd      | GAD31      | SBA7     |  |  |  |

| 2    | GAD25     | GAD24                               | SBA6     | SBA4       | SBA0     |  |  |  |

| 3    | GAD30     | GAD29                               | GAD26    | GAD27      | Gnd      |  |  |  |

| 4    | Gnd       | VCCAGP                              | GAD4     | GAD6       | GAD8     |  |  |  |

| 5    | RBF#      | GAD1                                | GAD3     | GAD5       | GC/BE0#  |  |  |  |

| 6    | BXPWROK   | Reserved                            | GAD2     | ADSTBA     | Gnd      |  |  |  |

| 7    | MD0       | MD1                                 | V_3      | CLKRUN#    | GAD7     |  |  |  |

| 8    | MD2       | MD33                                | Gnd      | MD32       | GAD0     |  |  |  |

| 9    | MD36      | MD4                                 | MD3      | MD35       | MD34     |  |  |  |

| 10   | MD7       | MD38                                | MD37     | MD6        | MD5      |  |  |  |

| 11   | MD41      | MD42                                | MD40     | MD39       | MD8      |  |  |  |

| 12   | MD43      | MD11                                | Gnd      | MD10       | MD9      |  |  |  |

| 13   | MD14      | MD45                                | MD44     | MD13       | MD12     |  |  |  |

| 14   | MECC4     | MECC0                               | MD15     | MD47       | MD46     |  |  |  |

| 15   | SCASA#    | WEA#                                | MECC5    | Reserved   | Gnd      |  |  |  |

| 16   | Gnd       | MID1                                | DQMA0    | DQMA1      | Reserved |  |  |  |

| 17   | V_3       | DQMA4                               | MID0     | DQMA5      | CSA0#    |  |  |  |

| 18   | CSA1#     | CSA2#                               | CSA4#    | CSA3#      | Gnd      |  |  |  |

| 19   | SRASA#    | CSA5#                               | MAB0#    | MAB1#      | Reserved |  |  |  |

| 20   | Reserved  | Reserved                            | MAB2#    | Reserved   | MAB3#    |  |  |  |

| 21   | Reserved  | MAB4#                               | Gnd      | Reserved   | MAB6#    |  |  |  |

| 22   | Reserved  | Reserved                            | MAB5#    | Reserved   | MAB7#    |  |  |  |

| 23   | MAB8#     | Reserved                            | Reserved | MAB9#      | MAB10    |  |  |  |

| 24   | Reserved  | MAB11#                              | MAB12#   | Reserved   | DCLKO    |  |  |  |

| 25   | MAB13     | V_3                                 | Gnd      | CKE0       | DCLKRD   |  |  |  |

| 26   | CKE1      | MID2                                | CKE3     | CKE4       | Gnd      |  |  |  |

| 27   | CKE5      | CKE2                                | MID3     | G_CPU_STP# | VRChgng# |  |  |  |

| 28   | Reserved  | G_LO/HI#                            | DQMA2    | DCLKWR     | Gnd      |  |  |  |

| 29   | Gnd       | VTT                                 | Reserved | FS_PREQ#   | DQMA3    |  |  |  |

| 30   | FS_RESET# | V_3                                 | MD26     | Gnd        | MD25     |  |  |  |

| 31   | FS_PRDY#  | Gnd                                 | MD58     | MD57       | MD60     |  |  |  |

| Pin# | Row          | Row      | Row      | Row      | Row      |

|------|--------------|----------|----------|----------|----------|

|      | Α            | В        | С        | D        | E        |

| 32   | G_SUS_STAT1# | SMCLK    | TDO      | TCLK     | FERR#    |

| 33   | Reserved     | SMDAT    | TDI      | TMS      | IGNNE#   |

| 34   | Reserved     | FQS      | Reserved | TRST#    | ATF_INT# |

| 35   | Reserved     | V_5      | V_3S     | V_3S     | V_3S     |

| 36   | V_CPUPU      | V_5      | V_3S     | V_3S     | V_3S     |

| 37   | V_CLK        | V_5      | V_3S     | V_3S     | V_3S     |

| 38   | Reserved     | Reserved | Reserved | Reserved | Reserved |

| 39   | V_DC         | V_DC     | V_DC     | V_DC     | V_DC     |

| 40   | V_DC         | V_DC     | V_DC     | V_DC     | V_DC     |

| Pin# | Row      | Row     | Row      | Row     | Row     |

|------|----------|---------|----------|---------|---------|

|      | F        | G       | Н        | J       | К       |

| 1    | GREQ#    | Gnd     | PIPE#    | SBA3    | Gnd     |

| 2    | ST0      | ST1     | SBA1     | SBSTB   | GCLKI   |

| 3    | GGNT#    | ST2     | SBA2     | Gnd     | GCLKO   |

| 4    | GAD13    | GSTOP#  | GAD16    | GAD20   | GAD23   |

| 5    | GAD12    | GPAR    | GAD18    | GAD17   | GC/BE3# |

| 6    | GAD10    | GAD15   | GFRAME#  | Gnd     | GAD22   |

| 7    | GAD11    | GC/BE1# | GTRDY#   | GC/BE2# | GAD21   |

| 8    | GAD9     | GAD14   | GDEVSEL# | GIRDY#  | GAD19   |

| 9    | Gnd      | VCCAGP  | Gnd      | VCCAGP  | GAD28   |

| 10   | AD0      | AD4     | AD2      | AD3     | AD1     |

| 11   | Gnd      | C/BE0#  | AD6      | Gnd     | AD5     |

| 12   | VCCAGP   | AD10    | AD7      | AD8     | AD9     |

| 13   | MECC1    | AD13    | Gnd      | AD12    | AD11    |

| 14   | SERR#    | PAR     | AD15     | C/BE1#  | AD14    |

| 15   | AD16     | TRDY#   | STOP#    | DEVSEL# | PLOCK#  |

| 16   | AD19     | Gnd     | AD17     | Gnd     | AD18    |

| 17   | AD23     | AD30    | AD24     | C/BE2#  | AD21    |

| 18   | AD27     | AD22    | C/BE3#   | AD26    | PCLK    |

| 19   | PCI_RST# | Gnd     | AD20     | AD28    | Gnd     |

| 20   | Reserved | PHOLD#  | AD31     | AD29    | AD25    |

| 21   | IRDY#    | FRAME#  | Gnd      | REQ1#   | REQ0#   |

| 22   | Gnd      | GNT2#   | REQ2#    | REQ3#   | GNT3#   |

| 23   | GNT1#    | GNT4#   | GNT0#    | REQ4#   | Gnd     |

| 24   | Gnd      | PHLDA#  | Gnd      | V_3     | MD59    |

# Intel® Celeron™ Processor Mobile Module MMC-2

| Pin# | Row<br>F | Row<br>G   | Row<br>H | Row<br>J | Row<br>K |

|------|----------|------------|----------|----------|----------|

| 25   | DQMA6    | MECC7      | MD50     | MD51     | MD54     |

| 26   | MECC2    | MD48       | MD18     | MD52     | MD24     |

| 27   | DQMA7    | MD16       | MD19     | Gnd      | MD23     |

| 28   | MECC6    | MD17       | MD21     | MD53     | MD55     |

| 29   | MECC3    | MD49       | MD20     | MD22     | MD56     |

| 30   | MD27     | MD28       | Gnd      | MD62     | MD63     |

| 31   | Gnd      | MD29       | MD61     | MD30     | MD31     |

| 32   | SMI#     | INTR       | VR_ON    | Gnd      | Gnd      |

| 33   | NMI      | SUS_STAT1# | VR_PWRGD | Gnd      | HCLK0    |

| 34   | A20M#    | STPCLK#    | INIT#    | Gnd      | Gnd      |

| 35   | V_3      | V_3        | V_3      | Gnd      | HCLK1    |

| 36   | V_3      | V_3        | V_3      | Gnd      | Gnd      |

| 37   | V_3      | V_3        | V_3      | V_3      | V_3      |

| 38   | Reserved | Reserved   | Reserved | Reserved | Reserved |

| 39   | V_DC     | V_DC       | V_DC     | V_DC     | V_DC     |

| 40   | V_DC     | V_DC       | V_DC     | V_DC     | V_DC     |

## 3.3. Pin and Pad Assignments

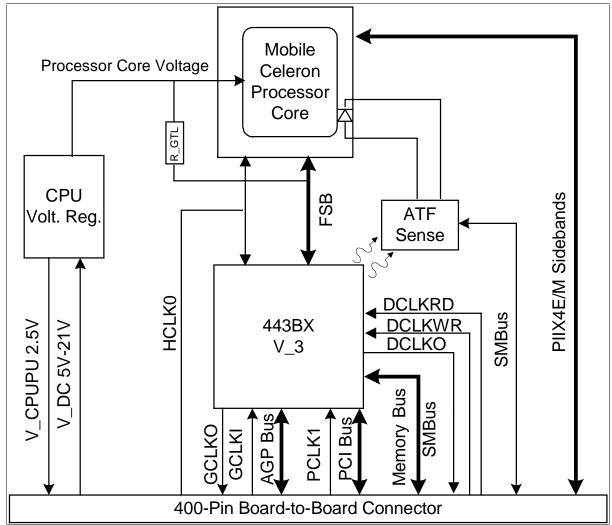

The MMC-2 is a 400-pin, 1.27mm pitch, and BGA style surface mount connector. MMC-2 has three different sized mating receptacles. Refer to section 5.1.4, *Height Requirements*, for size information. Contact your local Intel sales representative for additional information.

Figure 2 shows the pad assignments from the secondary side of the  $Celeron^{TM}$  processor mobile module.

Figure 2. 400-Pin Connector Footprint Pad Numbers, Module Secondary Side

Table 13 summarizes some of the key specifications for the connector.

**Table 13. Connector Specifications**

| Parameter  | Condition               | Specification                          |  |

|------------|-------------------------|----------------------------------------|--|

| Material   | Contact                 | Copper Alloy                           |  |

|            | Housing                 | Thermo Plastic Molded<br>Compound: LCP |  |

| Electrical | Current                 | 0.5A                                   |  |

|            | Voltage                 | 50 VAC                                 |  |

|            | Insulation Resistance   | 100 MΩ min. at 500 VDC                 |  |

|            | Termination Resistance  | 10 mΩ max.                             |  |

|            | Capacitance             | 5 pF max. per contact                  |  |

| Mechanical | Mating Cycles           | 50 cycles                              |  |

|            | Connector Mating Force  | 2.0 oz max. per contact                |  |

|            | Contact Un-mating Force | 1.5 oz min. per contact                |  |

#### 4.0. FUNCTIONAL DESCRIPTION

#### 4.1. Celeron<sup>TM</sup> Processor Mobile Module

The Celeron™ processor mobile module supports the mobile Celeron processor core with on-die L2 cache running at 300 MHz with a system bus speed of 66 MHz.

#### 4.2. L2 Cache

The mobile Celeron™ processor has 128K of on-die L2 cache that is 4-way set associative and runs at the speed of the processor core.

## 4.3. The 443BX Host Bridge System Controller

Intel's 443BX Host Bridge system controller is a highly integrated device that combines the mobile Celeron<sup>TM</sup> processor bus controller, the DRAM controller, and the PCI bus controller into one component. The 443BX Host Bridge has multiple power management features designed specifically for notebook systems such as:

- CLKRUN#, a feature that enables controlling of the PCI clock on or off.

- The 443BX Host Bridge suspend modes, which include Suspend-to-RAM (STR), Suspend-to-Disk (STD), and Powered-On-Suspend (POS).

- System Management RAM (SMRAM) power management modes which include Compatible SMRAM (C\_SMRAM) and Extended SMRAM (E\_SMRAM).

C\_SMRAM is the traditional SMRAM feature implemented in all Intel PCI chipsets. E\_SMRAM is a new feature that supports write-back cacheable SMRAM space up to 1 MB. To minimize power consumption while the system is idle, the internal

443BX Host Bridge clock is turned off (gated off) when there is no processor and PCI activity. This is accomplished by setting the G\_CLK enable bit in the power management register in the 443BX through the system BIOS.

The Celeron™ processor mobile module supports only the 443BX Host Bridge features in mobile legacy mode. Refer to Intel's latest revision of the 443BX Host Bridge specification for complete details.

# 4.3.1. Memory Organization

The memory interface of the 443BX Host Bridge, supporting standard mode memory configurations and modes of operation, is available at MMC-2. This allows for the following:

- One set of memory control signals, sufficient to support up to three SO\_DIMM sockets and six banks of SDRAM at 66MHz.

- One CKE signal for each bank.

Memory features not supported by the 443BX Host Bridge system controller standard MMC-2 Mode are:

- Support for 8 banks of memory.

- Second set of memory address lines (MAA[13:0]).

- 100 MHz SDRAM (and PSB).

DRAM technologies supported by the 443BX Host Bridge system controller include EDO and SDRAM. These memory types may not be mixed in the system, so that all DRAM in all rows (RAS[5:0]#) must be of the same technology. The 443BX Host Bridge system controller targets 60 ns EDO DRAMs and 66 MHz SDRAMs.

# int<sub>e</sub>l.

#### INTEL® CELERON™ PROCESSOR MOBILE MODULE MMC-2